# Polyphase Multifunction Energy Metering IC with Serial Port

## ADE7754

#### FEATURES

High Accuracy, Supports IEC 687/61036 Compatible with 3-Phase/3-Wire, 3-Phase/4-Wire and any Type of 3-Phase Services Less than 0.1% Error in Active Power Measurement over a Dynamic Range of 1000 to 1 Supplies Active Energy, Apparent Energy, Voltage RMS, Current RMS, and Sampled Waveform Data **Digital Power, Phase, and Input Offset Calibration On-Chip Temperature Sensor (±4°C Typical after Calibration) On-Chip User Programmable Thresholds for Line Voltage** SAG and Overdrive Detections SPI Compatible Serial Interface with Interrupt Request Line (IRQ) Pulse Output with Programmable Frequency Proprietary ADCs and DSP Provide High Accuracy over Large Variations in Environmental Conditions and Time

Single 5 V Supply

#### **GENERAL DESCRIPTION**

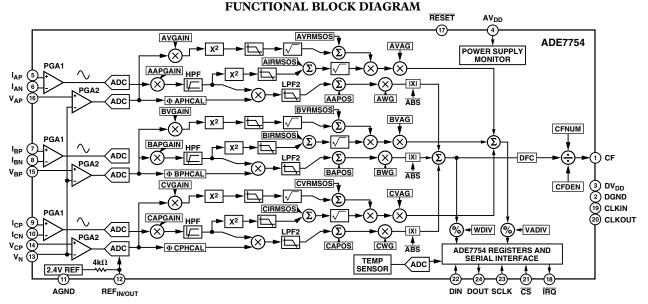

The ADE7754 is a high accuracy polyphase electrical energy measurement IC with a serial interface and a pulse output. The ADE7754 incorporates second order  $\Sigma$ - $\Delta$  ADCs, reference circuitry, temperature sensor, and all the signal processing required to perform active, apparent energy measurements, and rms calculation.

The ADE7754 provides different solutions for measuring active and apparent energy from the six analog inputs, thus enabling

the use of the ADE7754 in various power meter services such as 3-phase/4-wire, 3-phase/3-wire, and 4-wire delta.

In addition to rms calculation, active and apparent power information, the ADE7754 provides system calibration features for each phase (i.e., channel offset correction, phase calibration, and gain calibration). The CF logic output provides instantaneous active power information.

The ADE7754 has a waveform sample register that enables access to ADC outputs. The part also incorporates a detection circuit for short duration low or high voltage variations. The voltage threshold levels and the duration (number of half line cycles) of the variation are user programmable.

A zero-crossing detection is synchronized with the zero-crossing point of the line voltage of each of the three phases. The information collected is used to measure each line's period. It is also used internally to the chip in the line active energy and line apparent energy accumulation modes. This permits faster and more accurate calibration of the power calculations. This signal is also useful for synchronization of relay switching.

Data is read from the ADE7754 via the SPI serial interface. The interrupt request output ( $\overline{IRQ}$ ) is an open-drain, active low logic output. The  $\overline{IRQ}$  output goes active low when one or more interrupt events have occurred in the ADE7754. A status register indicates the nature of the interrupt.

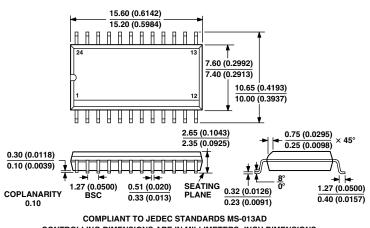

The ADE7754 is available in a 24-lead SOIC package.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

| Contents                                                 |     |

|----------------------------------------------------------|-----|

| Contents GENERAL DESCRIPTION                             | . 1 |

| FEATURES                                                 | . 1 |

| SPECIFICATIONS                                           | . 3 |

| TIMING CHARACTERISTICS                                   | . 4 |

| ABSOLUTE MAXIMUM RATINGS                                 |     |

| ORDERING GUIDE                                           |     |

| PIN CONFIGURATION                                        |     |

| PIN FUNCTION DESCRIPTIONS                                |     |

|                                                          |     |

| TYPICAL PERFORMANCE CHARACTERISTICS                      |     |

| TERMINOLOGY                                              |     |

| Measurement Error                                        |     |

| Phase Error Between Channels                             |     |

| Power Supply Rejection                                   | . 9 |

| ADC Offset Error                                         | . 9 |

| Gain Error                                               | . 9 |

| Gain Error Match                                         | . 9 |

| POWER SUPPLY MONITOR                                     |     |

| ANALOG INPUTS                                            |     |

| ANALOG-TO-DIGITAL CONVERSION                             |     |

| Antialias Filter                                         |     |

| CURRENT CHANNEL ADC                                      | 10  |

| CURRENT CHANNEL ADC                                      | 11  |

| Current Channel ADC Gain Adjust                          | 11  |

| Current Channel Sampling                                 | 11  |

| VOLTAGE CHANNEL ADC                                      |     |

| ZERO-CROSSING DETECTION                                  |     |

| Zero-Crossing Timeout                                    | 13  |

| PERIOD MEASUREMENT                                       | 13  |

| LINE VOLTAGE SAG DETECTION                               | 13  |

| PEAK DETECTION                                           |     |

| Peak Level Set                                           |     |

| TEMPERATURE MEASUREMENT                                  |     |

| PHASE COMPENSATION                                       |     |

| ROOT MEAN SQUARE MEASUREMENT                             |     |

| ROUT MEAN SQUARE MEASUREMENT                             | 15  |

| Current RMS Calculation                                  |     |

| Current RMS Gain Adjust                                  |     |

| Current RMS Offset Compensation                          |     |

| Voltage RMS Calculation                                  |     |

| Voltage RMS Gain Adjust                                  |     |

| Voltage RMS Offset Compensation                          | 17  |

| ACTIVE POWER CALCULATION                                 | 17  |

| Power Offset Calibration                                 | 18  |

| Reverse Power Information                                | 18  |

| TOTAL ACTIVE POWER CALCULATION                           | 18  |

| ENERGY CALCULATION                                       | 19  |

| Integration Times Under Steady Load                      | 20  |

|                                                          | 20  |

| Energy to Frequency Conversion                           |     |

| No Load Threshold                                        | 21  |

| Mode Selection of the Sum of the Three Active Energies . | 22  |

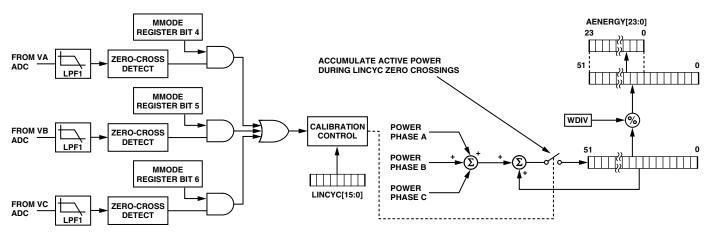

| LINE ENERGY ACCUMULATION                                 | 22  |

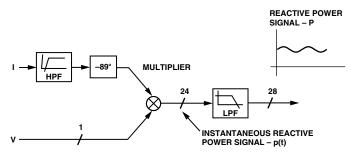

| REACTIVE POWER CALCULATION                               | 23  |

| TOTAL REACTIVE POWER CALCULATION                         | 24  |

| Reactive Energy Accumulation Selection                   | 24  |

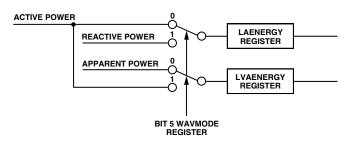

| APPARENT POWER CALCULATION                               | 24  |

| Apparent Power Offset Calibration                        | 25  |

| TOTAL APPARENT POWER CALCULATION                         | 25  |

| APPARENT ENERGY CALCULATION                              | 26  |

| Integration Times under Steady Load                      | 26  |

| LINE APPARENT ENERGY ACCUMULATION                        | 26  |

| LINE IN TRACTOR EVENOT ACCOMULATION                      | 20  |

| ENERGIES SCALING                                       |

|--------------------------------------------------------|

| CHECK SUM REGISTER 27                                  |

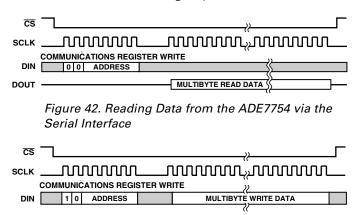

| SERIAL INTERFACE                                       |

| Serial Write Operation                                 |

| Serial Read Operation                                  |

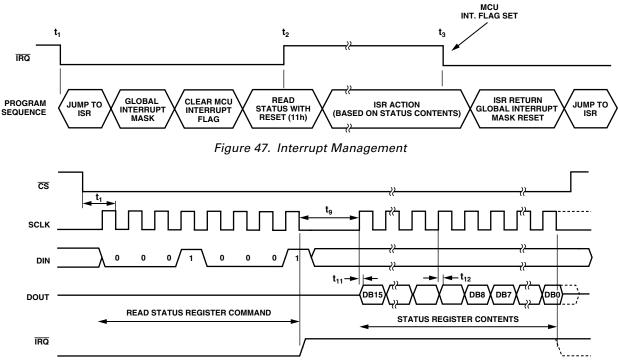

| INTERRUPTS                                             |

| Using Interrupts with an MCU                           |

| Interrupt Timing 30                                    |

| ACCESSING THE ADE7754 ON-CHIP REGISTERS 31             |

| Communications Register 31                             |

| Operational Mode Register (0Ah) 35                     |

| Gain Register (18h) 36                                 |

| CFNUM Register (25h) 36                                |

| Measurement Mode Register (0Bh) 37                     |

| Waveform Mode Register (0Ch)                           |

| Watt Mode Register (0Dh) 38                            |

| VA Mode Register (0Eh) 38                              |

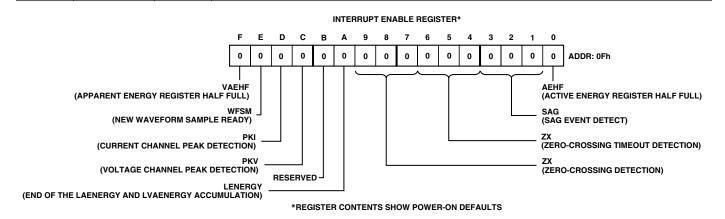

| Interrupt Enable Register(0Fh) 39                      |

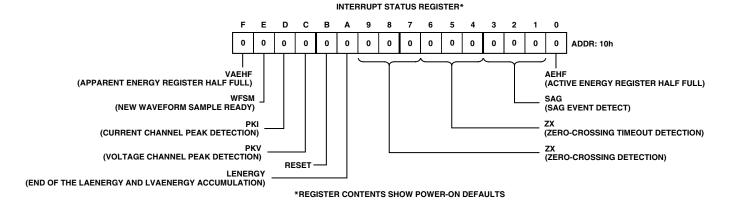

| Interrupt Status Register (10h)/Reset Interrupt Status |

| Register (11h) 40                                      |

| OUTLINE DIMENSIONS 41                                  |

|                                                        |

#

| Parameters                                                               | Spec            | Unit          | Test Conditions/Comments                                         |

|--------------------------------------------------------------------------|-----------------|---------------|------------------------------------------------------------------|

| ACCURACY                                                                 |                 |               |                                                                  |

| Active Power Measurement Error                                           | 0.1             | % typ         | Over a dynamic range 1000 to 1                                   |

| Phase Error between Channels                                             |                 |               |                                                                  |

| (PF = 0.8 Capacitive)                                                    | ±0.05           | ° max         | Phase lead 37°                                                   |

| (PF = 0.5 Inductive)                                                     | ±0.05           | ° max         | Phase lag 60°                                                    |

| AC Power Supply Rejection <sup>1</sup>                                   |                 |               |                                                                  |

| Output Frequency Variation                                               | 0.01            | % typ         | $IAP/N = IBP/N = ICP/N = \pm 100 \text{ mV rms}$                 |

| DC Power Supply Rejection <sup>1</sup>                                   |                 |               |                                                                  |

| Output Frequency Variation                                               | 0.01            | % typ         | $IAP/N = IBP/N = ICP/N = \pm 100 \text{ mV rms}$                 |

| Active Power Measurement Bandwidth                                       | 14              | kHz typ       |                                                                  |

| V <sub>rms</sub> Measurement Error                                       | 0.5             | % typ         | Over dynamic range of 20 to 1                                    |

| V <sub>rms</sub> Measurement Bandwidth                                   | 260             | Hz typ        |                                                                  |

| I <sub>rms</sub> Measurement Error                                       | 2               | % typ         | Over dynamic range of 100 to 1                                   |

| I <sub>rms</sub> Measurement Bandwidth                                   | 14              | kHz           |                                                                  |

| ANALOG INPUTS                                                            |                 |               |                                                                  |

| Maximum Signal Levels                                                    | ±500            | mV peak max   | Differential input: $V_{AP}-V_N$ , $V_{BP}-V_N$ , $V_{CP}-V_N$ , |

|                                                                          |                 | int pour mun  | $I_{AP}-I_{AN}, I_{BP}-I_{BN}, I_{CP}-I_{CN}$                    |

| Input Impedance (DC)                                                     | 370             | $k\Omega$ min | AP ANJ BP BNJ CP CN                                              |

| Bandwidth (–3 dB)                                                        | 14              | kHz typ       |                                                                  |

| ADC Offset Error <sup>1</sup>                                            | 25              | mV max        | Uncalibrated error; See Terminology for details.                 |

| Gain Error <sup>1</sup>                                                  | $\pm 8$         | % typ         | External 2.5 V reference                                         |

| Gain Error Match <sup>1</sup>                                            | $\pm 3$         | % typ         | External 2.5 V reference                                         |

| REFERENCE INPUT                                                          |                 |               |                                                                  |

|                                                                          | 2.6             | V max         | 2.4 V + 8%                                                       |

| $REF_{IN/OUT}$ Input Voltage Range                                       | 2.0             | V min         | 2.4  V + 8%                                                      |

| Input Impedance                                                          | 3.7             | $k\Omega$ max | 2.4  V = 8/8                                                     |

| Input Inpedance<br>Input Capacitance                                     | 10              | pF max        |                                                                  |

| TEMPERATURE SENSOR                                                       | ±4              | °C            | Calibrated dc offset                                             |

|                                                                          | <u> </u>        | 0             |                                                                  |

| ON-CHIP REFERENCE<br>Reference Error                                     | +200            | we V we are   |                                                                  |

|                                                                          | $\pm 200$<br>30 | mV max        |                                                                  |

| Temperature Coefficient                                                  | 50              | ppm/°C typ    |                                                                  |

| CLKIN                                                                    |                 |               |                                                                  |

| Input Clock Frequency                                                    | 10              | MHz typ       |                                                                  |

| LOGIC INPUTS                                                             |                 |               |                                                                  |

| $\overline{\text{RESET}}$ , DIN, SCLK, CLKIN, and $\overline{\text{CS}}$ |                 |               |                                                                  |

| Input High Voltage, V <sub>INH</sub>                                     | 2.4             | V min         | $DV_{DD} = 5 V \pm 5\%$                                          |

| Input Low Voltage, V <sub>INL</sub>                                      | 0.8             | V max         | $DV_{DD}$ = 5 V ± 5%                                             |

| Input Current, I <sub>IN</sub>                                           | ±3              | μA max        | Typical 10 nA, $V_{IN} = 0$ V to $DV_{DD}$                       |

| Input Capacitance, C <sub>IN</sub>                                       | 10              | pF max        |                                                                  |

| LOGIC OUTPUTS                                                            |                 |               |                                                                  |

| CF, IRQ, DOUT, and CLKOUT                                                |                 |               |                                                                  |

| Output High Voltage, V <sub>OH</sub>                                     | 4               | V min         | $DV_{DD} = 5 V \pm 5\%$                                          |

| Output Low Voltage, V <sub>OL</sub>                                      | 1               | V max         | $DV_{DD} = 5 V \pm 5\%$                                          |

| POWER SUPPLY                                                             |                 |               | For specified performance                                        |

| AV <sub>DD</sub>                                                         | 4.75            | V min         | 5  V - 5%                                                        |

| 11 UU                                                                    | 5.25            | V max         | 5 V - 5%                                                         |

| $\mathrm{DV}_{\mathrm{DD}}$                                              | 4.75            | V min         | 5 V - 5%                                                         |

| טע י ש                                                                   | 5.25            | V max         | 5 V - 5%<br>5 V + 5%                                             |

| AI <sub>DD</sub>                                                         | 5.25<br>7       | mA max        | At 5.25 V                                                        |

| DI <sub>DD</sub>                                                         | 18              | mA max        | At 5.25 V<br>At 5.25 V                                           |

| DIDD                                                                     | 10              | IIIA IIIdX    | 11L J.2J V                                                       |

NOTES

<sup>1</sup>See Terminology section for explanation of specifications.

<sup>2</sup>See plots in the Typical Performance Characteristics section.

Specifications subject to change without notice.

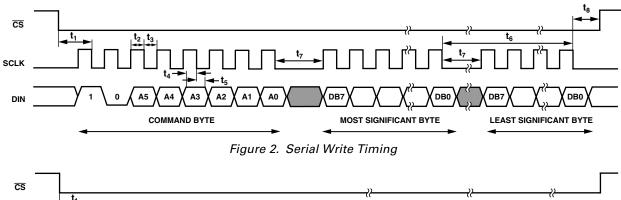

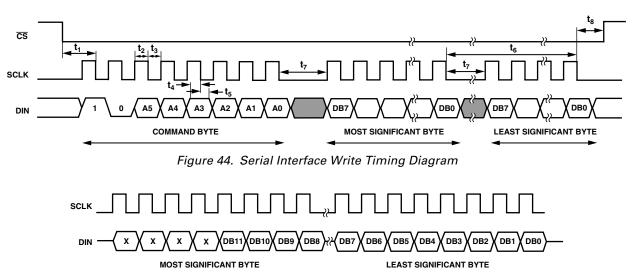

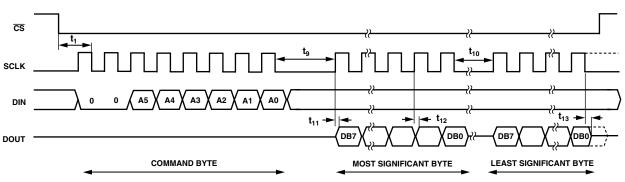

### **TIMING CHARACTERISTICS**<sup>1, 2</sup> ( $AV_{DD} = DV_{DD} = 5 V \pm 5\%$ , AGND = DGND = 0 V, On-Chip Reference, CLKIN = 10 MHz XTAL, T<sub>MIN</sub> to T<sub>MAX</sub> = -40°C to +85°C, unless otherwise noted.)

| Parameter                    | Spec | Unit     | Test Conditions/Comments                                                                     |  |

|------------------------------|------|----------|----------------------------------------------------------------------------------------------|--|

| Write Timing                 |      |          |                                                                                              |  |

| t <sub>1</sub>               | 50   | ns (min) | CS Falling Edge to First SCLK Falling Edge                                                   |  |

| t <sub>2</sub>               | 50   | ns (min) | SCLK Logic High Pulsewidth                                                                   |  |

| t <sub>3</sub>               | 50   | ns (min) | SCLK Logic Low Pulsewidth                                                                    |  |

| t <sub>4</sub>               | 10   | ns (min) | Valid Data Setup Time before Falling Edge of SCLK                                            |  |

| t <sub>5</sub>               | 5    | ns (min) | Data Hold Time after SCLK Falling Edge                                                       |  |

| t <sub>6</sub>               | 400  | ns (min) | Minimum Time between the End of Data Byte Transfers                                          |  |

| t <sub>7</sub>               | 50   | ns (min) | Minimum Time between Byte Transfers during a Serial Write                                    |  |

| t <sub>8</sub>               | 100  | ns (min) | CS Hold Time after SCLK Falling Edge                                                         |  |

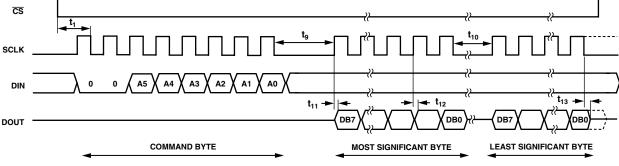

| Read Timing                  |      |          |                                                                                              |  |

| $t_{9}^{3}$                  | 4    | μs (min) | Minimum Time between Read Command (i.e., a Write to Communication<br>Register) and Data Read |  |

| t <sub>10</sub>              | 50   | ns (min) | Minimum Time between Data Byte Transfers during a Multibyte Read                             |  |

| $t_{11}^{4}$                 | 30   | ns (min) | Data Access Time after SCLK Rising Edge following a Write to the<br>Communications Register  |  |

| t <sub>12</sub> <sup>5</sup> | 100  | ns (max) | Bus Relinquish Time after Falling Edge of SCLK                                               |  |

|                              | 10   | ns (min) |                                                                                              |  |

| $t_{13}^{5}$                 | 100  | ns (max) | Bus Relinquish Time after Rising Edge of $\overline{CS}$                                     |  |

|                              | 10   | ns (min) |                                                                                              |  |

NOTES

<sup>1</sup>Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns

(10% to 90%) and timed from a voltage level of 1.6 V.

<sup>2</sup>See timing diagrams below and Serial Interface section of this data sheet. <sup>3</sup>Minimum time between read command and data read for all registers except wavmode register, which is  $t_9 = 500$  ns min.

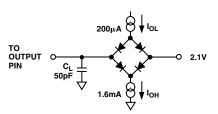

<sup>4</sup>Measured with the load circuit in Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

<sup>5</sup>Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit in Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. The time quoted in the timing characteristics is the true bus relinquish time of the part and is independent of the bus loading.

Figure 1. Load Circuit for Timing Specifications

Figure 3. Serial Read Timing

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = +25^{\circ}C, unless otherwise noted.)$                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>DD</sub> to AGND $\dots \dots \dots$ |

| $DV_{DD}$ to DGND                                                                                                                            |

| $DV_{DD}$ to $AV_{DD}$                                                                                                                       |

| Analog Input Voltage to AGND                                                                                                                 |

| $I_{AP}$ , $I_{AN}$ , $I_{BP}$ , $I_{BN}$ , $I_{CP}$ , $I_{CN}$ , $V_{AP}$ , $V_{BP}$ , $V_{CP}$ , $V_N$ –6 V to +6 V                        |

| Reference Input Voltage to AGND $-0.3$ V to AV <sub>DD</sub> + 0.3 V                                                                         |

| Digital Input Voltage to DGND $\dots$ -0.3 V to DV <sub>DD</sub> + 0.3 V                                                                     |

| Digital Output Voltage to DGND $-0.3$ V to DV <sub>DD</sub> + 0.3 V                                                                          |

| Operating Temperature Range                                                                                                                  |

| Industrial                                                                                                                                   |

| Storage Temperature Range            | °C |

|--------------------------------------|----|

| Junction Temperature 150°            | °C |

| 24-Lead SOIC, Power Dissipation 88 m | W  |

| $\theta_{JA}$ Thermal Impedance      | W  |

| Lead Temperature, Soldering          |    |

| Vapor Phase (60 sec) 215°            | °C |

| Infrared (15 sec) 220°               | Ċ  |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model                                      | Package Description          | Package Option*                                    |

|--------------------------------------------|------------------------------|----------------------------------------------------|

| ADE7754AR<br>ADE7754ARRL<br>EVAL-ADE7754EB | 24-Lead SOIC<br>24-Lead SOIC | RW-24<br>RW-24 in Reel<br>ADE7754 Evaluation Board |

\*RW = Small Outline (Wide Body Package in Tubes)

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADE7754 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CF       | Calibration Frequency Logic Output. This pin provides active power information. This output<br>is intended to be used for operational and calibration purposes. The full-scale output frequency<br>can be scaled by writing to the CFNUM and CFDEN registers. See the Energy to Frequency<br>Conversion section.                                                                                            |

| 2       | DGND     | This pin provides the ground reference for the digital circuitry in the ADE7754 (i.e. multiplier, filters, and a digital-to-frequency converter). Because the digital return currents in the ADE7754 are small, this pin can be connected to the analog ground plane of the whole system. However high bus capacitance on the DOUT pin may result in noisy digital current, which could affect performance. |

| Pin No.                 | Mnemonic                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3                       | DV <sub>DD</sub>                                           | Digital Power Supply. The supply voltage should be maintained at 5 V $\pm$ 5% for specified operation. This pin should be decoupled to DGND with a 10 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor.                                                                                                                                                                                                                                                                                                                         |  |  |

| 4                       | AV <sub>DD</sub>                                           | Analog Power Supply. The supply should be maintained at 5 V $\pm$ 5% for specified operation. Even effort should be made to minimize power supply ripple and noise at this pin through the use of proper decoupling. The TPCs chart the power supply rejection performance. This pin should be decoupled AGND with a 10 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor.                                                                                                                                                       |  |  |

| 5, 6;<br>7, 8;<br>9, 10 | $I_{AP}, I_{AN};$<br>$I_{BP}, I_{BN};$<br>$I_{CP}, I_{CN}$ | Analog Inputs for Current Channel. This channel is intended for use with the current transducer<br>is referenced in this document as the current channel. These inputs are fully differential voltage<br>inputs with maximum differential input signal levels of $\pm 0.5$ V, $\pm 0.25$ V, and $\pm 0.125$ V, depending<br>on the gain selections of the internal PGA. See the Analog Inputs section.                                                                                                                                       |  |  |

|                         |                                                            | All inputs have internal ESD protection circuitry. An overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 11                      | AGND                                                       | Analog Ground Reference. Used for ADCs, temperature sensor, and reference. This pin should be tied to the analog ground plane or the quietest ground reference in the system. This quiet ground reference should be used for all analog circuitry such as anti-aliasing filters and current and voltage transducers. To keep ground noise around the ADE7754 to a minimum, the quiet ground plane should be connected only to the digital ground plane at one point. It is acceptable to place the entire device on the analog ground plane. |  |  |

| 12                      | REF <sub>IN/OUT</sub>                                      | This pin provides access to the on-chip voltage reference, which has a nominal value of 2.4 V $\pm$ 8% and a typical temperature coefficient of 30 ppm/°C. An external reference source may also be connected at this pin. In either case, this pin should be decoupled to AGND with a 1 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                          |  |  |

| 13, 14;<br>15, 16       | $V_N$ , $V_{CP}$ ;<br>$V_{BP}$ , $V_{AP}$                  | Analog Inputs for the Voltage Channel. This channel is intended for use with the voltage transducer<br>and is referenced as the voltage channel in this document. These inputs are single-ended voltage<br>inputs with maximum signal level of $\pm 0.5$ V with respect to V <sub>N</sub> for specified operation. These<br>inputs are voltage inputs with maximum differential input signal levels of $\pm 0.5$ V, $\pm 0.25$ V, and<br>$\pm 0.125$ V, depending on the gain selections of the internal PGA. See the Analog Inputs section. |  |  |

|                         |                                                            | All inputs have internal ESD protection circuitry. An overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 17                      | RESET                                                      | Reset. A logic low on this pin holds the ADCs and digital circuitry (including the serial interface) in a reset condition.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 18                      | ĪRQ                                                        | Interrupt Request Output. This is an active low, open-drain logic output. Maskable interrupts include active energy register at half level, apparent energy register at half level, and waveform sampling at up to 26 kSPS. See the Interrupts section.                                                                                                                                                                                                                                                                                      |  |  |

| 19                      | CLKIN                                                      | Master Clock for ADCs and Digital Signal Processing. An external clock can be provided at this logic input. Alternatively, a parallel resonant AT crystal can be connected across CLKIN and CLKOUT to provide a clock source for the ADE7754. The clock frequency for specified operation is 10 MHz. Ceramic load capacitors of 22 pF to 33 pF should be used with the gate oscillator circuit. Refer to the crystal manufacturer's data sheet for load capacitance requirements.                                                            |  |  |

| 20                      | CLKOUT                                                     | A crystal can be connected across this pin and CLKIN as described above to provide a clock source for the ADE7754. The CLKOUT pin can drive one CMOS load when an external clock is supplied at CLKIN, or a crystal is used.                                                                                                                                                                                                                                                                                                                 |  |  |

| 21                      | CS                                                         | Chip Select. Part of the 4-wire serial interface. This active low logic input allows the ADE7754 to share the serial bus with several other devices. See the Serial Interface section.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 22                      | DIN                                                        | Data Input for the Serial Interface. Data is shifted in at this pin on the falling edge of SCLK. See the Serial Interface section.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 23                      | SCLK                                                       | Serial Clock Input for the Synchronous Serial Interface. All serial data transfers are synchronized to this clock. See the Serial Interface section. The SCLK has a Schmidt-trigger input for use with a clock source that has a slow edge transition time (e.g., opto-isolator outputs).                                                                                                                                                                                                                                                    |  |  |

| 24                      | DOUT                                                       | Data Output for the Serial Interface. Data is shifted out at this pin on the rising edge of SCLK. This logic output is normally in a high impedance state unless it is driving data onto the serial data bus. See the Serial Interface section.                                                                                                                                                                                                                                                                                              |  |  |

### **Typical Performance Characteristics–ADE7754**

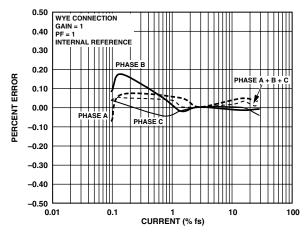

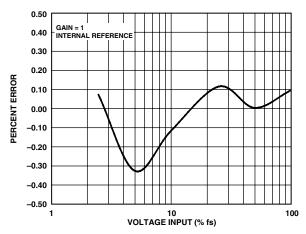

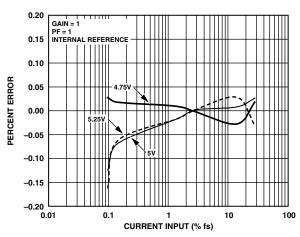

TPC 1. Real Power Error as a Percentage of Reading with Gain = 1 and Internal Reference (WYE Connection)

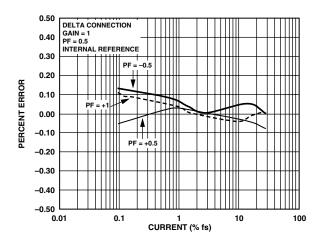

TPC 2. Real Power Error as a Percentage of Reading over Power Factor with Internal Reference (DELTA Connection)

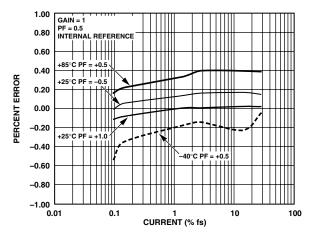

TPC 3. Real Power Error as a Percentage of Reading over Power Factor with Internal Reference (Gain = 1)

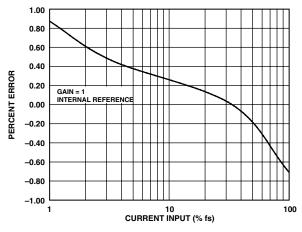

TPC 4. Current RMS Error as a Percentage of Reading with Internal Reference (Gain = 1)

*TPC 5. Voltage RMS Error as a Percentage of Reading with Internal Reference (Gain = 1)*

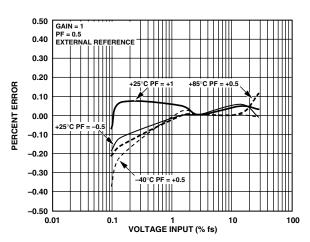

TPC 6. Real Power Error as a Percentage of Reading over Power Factor with External Reference (Gain = 1)

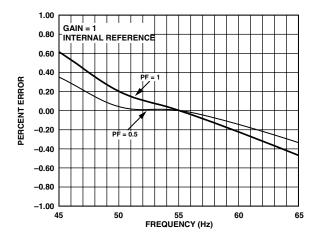

TPC 7. Real Power Error as a Percentage of Reading over Input Frequency with Internal Reference

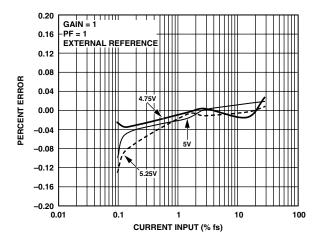

TPC 8. Real Power Error as a Percentage of Reading over Power Supply with External Reference (Gain = 1)

TPC 9. Real Power Error as a Percentage of Reading over Power Supply with Internal Reference (Gain = 1)

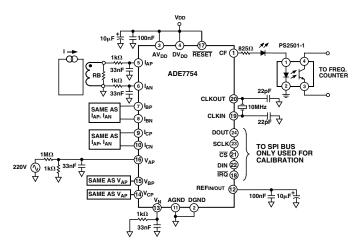

TPC 10. Test Circuit for Performance Curves

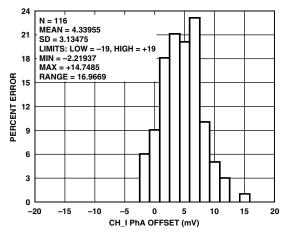

TPC 11. Current Channel Offset Distribution (Gain = 1)

#### TERMINOLOGY

#### **Measurement Error**

Percentage Fron -

The error associated with the energy measurement made by the ADE7754 is defined by the formula

$$\left(\frac{Energy \ Registered \ by \ ADE7754 - True \ Energy}{True \ Energy} \times 100\%\right)$$

#### **Phase Error Between Channels**

The HPF (high-pass filter) in the current channel has a phase lead response. To offset this phase response and equalize the phase response between channels, a phase correction network is placed in the current channel. The phase correction network ensures a phase match between the current channels and voltage channels to within  $\pm 0.1^{\circ}$  over a range of 45 Hz to 65 Hz and  $\pm 0.2^{\circ}$  over a range of 40 Hz to 1 kHz. This phase mismatch between the voltage and the current channels can be reduced further with the phase calibration register in each phase.

#### **Power Supply Rejection**

This quantifies the ADE7754 measurement error as a percentage of reading when power supplies are varied. For the ac PSR measurement, a reading at nominal supplies (5 V) is taken. A second reading is obtained using the same input signal levels when an ac (175 mV rms/100 Hz) signal is introduced onto the supplies. Any error introduced by this ac signal is expressed as a percentage of reading. See the Measurement Error definition above.

For the dc PSR measurement, a reading at nominal supplies (5 V) is taken. A second reading is obtained using the same input signal levels when the power supplies are varied  $\pm 5\%$ . Any error introduced is again expressed as a percentage of reading.

#### ADC Offset Error

This refers to the dc offset associated with the analog inputs to the ADCs. It means that with the analog inputs connected to AGND, the ADCs still see a dc analog input signal. The magnitude of the offset depends on the gain and input range selection (see the TPCs). However, when HPFs are switched on, the offset is removed from the current channels and the power calculation is unaffected by this offset.

#### **Gain Error**

The gain error in the ADE7754 ADCs is defined as the difference between the measured ADC output code (minus the offset) and the ideal output code. See the Current Channel ADC and the Voltage Channel ADC sections. The difference is expressed as a percentage of the ideal code.

#### **Gain Error Match**

Gain error match is defined as the gain error (minus the offset) obtained when switching between a gain of 1, 2, or 4. It is expressed as a percentage of the output ADC code obtained under a gain of 1.

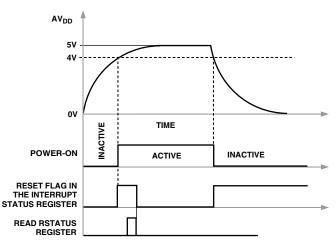

#### POWER SUPPLY MONITOR

The ADE7754 contains an on-chip power supply monitor. The analog supply  $(AV_{DD})$  is continuously monitored by the ADE7754. If the supply is less than  $4 V \pm 5\%$ , the ADE7754 goes into an inactive state (i.e., no energy is accumulated when the supply voltage is below 4 V). This is useful to ensure correct device operation at power-up and during power-down. The power supply monitor has built-in hysteresis and filtering, providing a high degree of immunity to false triggering due to noisy supplies.

Figure 4. On-Chip Power Supply Monitoring

The RESET bit in the interrupt status register is set to Logic 1 when AV<sub>DD</sub> drops below 4 V  $\pm$  5%. The RESET flag is always masked by the interrupt enable register and cannot cause the IRQ pin to go low. The power supply and decoupling for the part should ensure that the ripple at AV<sub>DD</sub> does not exceed 5 V  $\pm$  5% as specified for normal operation.

#### ANALOG INPUTS

The ADE7754 has six analog inputs, divisible into two channels: current and voltage. The current channel consists of three pairs of fully differential voltage inputs:  $I_{AP}$ ,  $I_{AN}$ ;  $I_{BP}$ ,  $I_{BN}$ ; and  $I_{CP}$ ,  $I_{CN}$ . The fully differential voltage input pairs have a maximum differential voltage of  $\pm 0.5$  V. The voltage channel has three single-ended voltage inputs:  $V_{AP}$ ,  $V_{BP}$ , and  $V_{CP}$ . These single-ended voltage inputs have a maximum input voltage of  $\pm 0.5$  V with respect to  $V_N$ . Both the current channel and the voltage channel have a PGA (programmable gain amplifier) with possible gain selections of 1, 2, or 4. The same gain is applied to all the inputs of each channel.

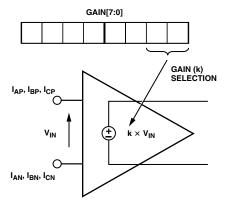

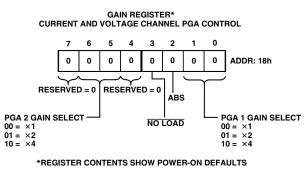

The gain selections are made by writing to the gain register. Bits 0 and 1 select the gain for the PGA in the fully differential current channel. The gain selection for the PGA in the single-ended voltage channel is made via Bits 5 and 6. Figure 5 shows how a gain selection for the current channel is made using the gain register.

Figure 5. PGA in Current Channel

Figure 6 shows how the gain settings in PGA 1 (current channel) and PGA 2 (voltage channel) are selected by various bits in the gain register. The no-load threshold and sum of the absolute value can also be selected in the gain register. See Table X.

Figure 6. Analog Gain Register

#### ANALOG-TO-DIGITAL CONVERSION

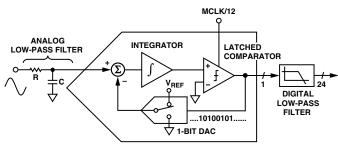

The ADE7754 carries out analog-to-digital conversion using second order  $\Sigma$ - $\Delta$  ADCs. The block diagram in Figure 7 shows a first order (for simplicity)  $\Sigma$ - $\Delta$  ADC. The converter is made up of two parts, the  $\Sigma$ - $\Delta$  modulator and the digital low-pass filter.

Figure 7. First Order ( $\Sigma$ - $\Delta$ ) ADC

A  $\Sigma$ - $\Delta$  modulator converts the input signal into a continuous serial stream of 1s and 0s at a rate determined by the sampling clock. In the ADE7754, the sampling clock is equal to CLKIN/12. The 1-bit DAC in the feedback loop is driven by the serial data stream. The DAC output is subtracted from the input signal. If the loop gain is high enough, the average value of the DAC output (and therefore the bit stream) will approach that of the input signal level. For any given input value in a single sampling interval, the data from the 1-bit ADC is virtually meaningless. Only when a large number of samples are averaged will a meaningful result be obtained. This averaging is carried out in the second part of the ADC, the digital low-pass filter. Averaging a large number of bits from the modulator, the low-pass filter can produce 24-bit data-words that are proportional to the input signal level.

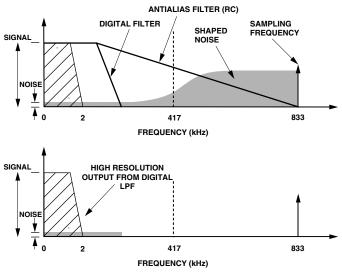

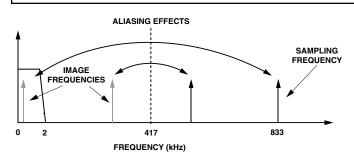

The  $\Sigma$ - $\Delta$  converter uses two techniques to achieve high resolution from what is essentially a 1-bit conversion technique. The first is oversampling; the signal is sampled at a rate (frequency) many times higher than the bandwidth of interest. For example, the sampling rate in the ADE7754 is CLKIN/12 (833 kHz), and the band of interest is 40 Hz to 2 kHz. Oversampling

spreads the quantization noise (noise due to sampling) over a wider bandwidth. With the noise spread more thinly over a wider bandwidth, the quantization noise in the band of interest is lowered. See Figure 8.

Oversampling alone is not an efficient enough method to improve the signal to noise ratio (SNR) in the band of interest. For example, an oversampling ratio of 4 is required to increase the SNR by only 6 dB (1 bit). To keep the oversampling ratio at a reasonable level, the quantization noise can be shaped so that most of the noise lies at the higher frequencies. In the  $\Sigma$ - $\Delta$ modulator, the noise is shaped by the integrator, which has a high-pass type of response for the quantization noise. The result is that most of the noise is at the higher frequencies, where it can be removed by the digital low-pass filter. This noise shaping is shown in Figure 8.

Figure 8. Noise Reduction Due to Oversampling and Noise Shaping in the Analog Modulator

#### **Antialias Filter**

Figure 7 shows an analog low-pass filter (RC) on the input to the modulator. This filter is used to prevent aliasing, an artifact of all sampled systems. Frequency components in the input signal to the ADC that are higher than half the sampling rate of the ADC appear in the sampled signal at a frequency below half the sampling rate. Figure 9 illustrates the effect; frequency components (arrows shown in black) above half the sampling frequency (also known as the Nyquist frequency), i.e., 417 kHz, get imaged or folded back down below 417 kHz (arrows shown in gray). This happens with all ADCs, regardless of the architecture. In the example shown, only frequencies near the sampling frequency, i.e., 833 kHz, will move into the band of interest for metering, i.e., 40 Hz to 2 kHz. This allows use of a very simple LPF (low-pass filter) to attenuate these high frequencies (near 900 kHz) and thus prevent distortion in the band of interest. A simple RC filter (single pole) with a corner frequency of 10 kHz produces an attenuation of approximately 40 dBs at 833 kHz. See Figure 9. This is sufficient to eliminate the effects of aliasing.

*Figure 9. ADC and Signal Processing in Current Channel or Voltage Channel*

#### CURRENT CHANNEL ADC

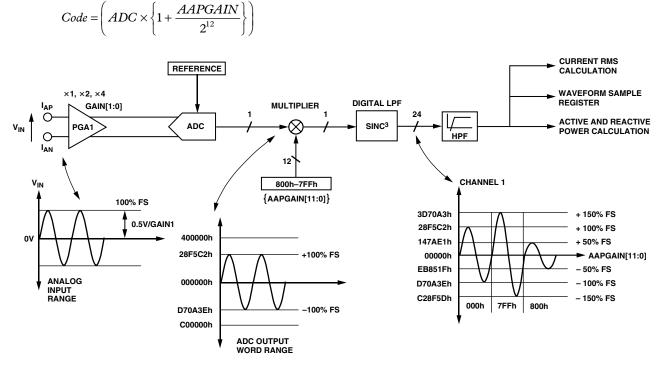

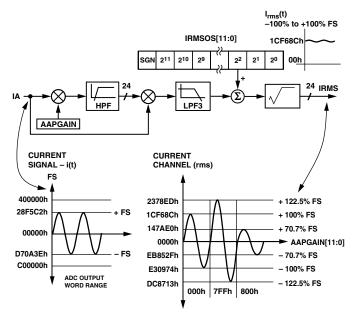

Figure 10 shows the ADC and signal processing chain for the input IA of the current channels (which are the same for IB and IC). In waveform sampling mode, the ADC outputs are signed twos complement 24-bit data-word at a maximum of 26 kSPS (kilo samples per second). The output of the ADC can be scaled by  $\pm 50\%$  by using the APGAINs register. While the ADC outputs are 24-bit twos complement value, the maximum full-scale positive value from the ADC is limited to 400000h (+4,194,304d). The maximum full-scale negative value is limited to C00000h (-4,194,304d). If the analog inputs are overranged, the ADC output code clamps at these values. With the specified full-scale analog input signal of  $\pm 0.5$  V, the ADC produces an output code between D70A3Eh (-2,684,354) and 28F5C2h (+2,684,354), as illustrated in Figure 10, which also shows a full-scale voltage signal being applied to the differential inputs I<sub>AP</sub> and I<sub>AN</sub>.

#### **Current Channel ADC Gain Adjust**

The ADC gain in each phase of the current channel can be adjusted using the multiplier and active power gain register (AAPGAIN[11:0], BAPGAIN, and CAPGAIN). The gain of the ADC is adjusted by writing a twos complement 12-bit word to the active power gain register. The following expression shows how the gain adjustment is related to the contents of that register: For example, when 7FFh is written to the active power gain register, the ADC output is scaled up by 50%: 7FFh = 2047d, 2047/212 = 0.5. Similarly, 800h = -2047d (signed twos complement) and ADC output is scaled by -50%. These two examples are illustrated in Figure 10.

#### **Current Channel Sampling**

The waveform samples of the current channel inputs may also be routed to the waveform register (wavmode register to select the speed and the phase) to be read by the system master (MCU). The active energy and apparent energy calculation remains uninterrupted during waveform sampling.

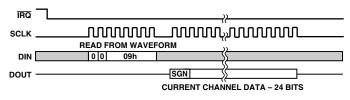

When in waveform sample mode, one of four output sample rates may be chosen using Bits 3 and 4 of the WAVMODE register (DTRT[1:0] mnemonic). The output sample rate may be 26.0 kSPS, 13.0 kSPS, 6.5 kSPS, or 3.3 kSPS. See the Waveform Mode Register section. By setting the WSMP bit in the interrupt enable register to Logic 1, the interrupt request output  $\overline{IRQ}$  will go active low when a sample is available. The timing is shown in Figure 11. The 24-bit waveform samples are transferred from the ADE7754 one byte (eight bits) at a time, with the most significant byte shifted out first.

Figure 11. Waveform Sampling Current Channel

The interrupt request output  $\overline{IRQ}$  stays low until the interrupt routine reads the reset status register. See the Interrupt section.

Note that if the WSMP bit in the interrupt enable register is not set to Logic 1, no data is available in the waveform register.

Figure 10. ADC and Signal Processing in Current Channel

#### **VOLTAGE CHANNEL ADC**

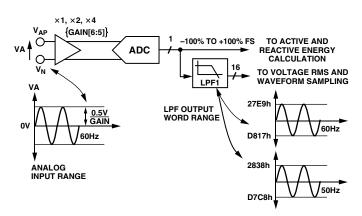

Figure 12 shows the ADC and signal processing chain for the input VA in voltage channel (which is the same for VB and VC).

Figure 12. ADC and Signal Processing in Voltage Channel

For energy measurements, the output of the ADC (one bit) is passed directly to the multiplier and is not filtered. This solution avoids a wide-bits multiplier and does not affect the accuracy of the measurement. An HPF is not required to remove any dc offset since it is only required to remove the offset from one channel to eliminate errors in the power calculation.

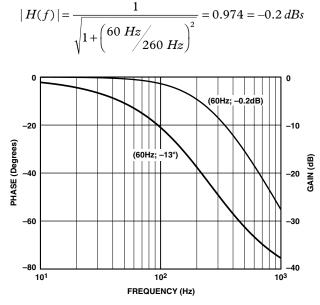

In the voltage channel, the samples may also be routed to the WFORM register (WAVMODE to select VA, VB, or VC and sampling frequency). However, before being passed to the waveform register, the ADC output is passed through a single-pole, low-pass filter with a cutoff frequency of 260 Hz. The plots in Figure 13 show the magnitude and phase response of this filter. The filter output code of any inputs of the voltage channel swings between D70Bh (-10,485d) and 28F5h (+10,485d) for full-scale sine wave inputs. This has the effect of attenuating the signal. For example, if the line frequency is 60 Hz, the signal at the output of LPF1 will be attenuated by 3%.

Figure 13. Magnitude and Phase Response of LPF1

Note that LPF1 does not affect the power calculation because it is used only in the waveform sample mode and rms calculation.

In waveform sample mode, one of four output sample rates can be chosen by using Bits 3 and 4 of the WAVMODE register. The available output sample rates are 26 kSPS, 13.5 kSPS, 6.5 kSPS, or 3.3 kSPS. The interrupt request output IRQ signals a new sample availability by going active low. The voltage waveform register is a twos complement 16-bit register. Because the waveform register is a 24-bit signed register, the waveform data from the voltage input is located in the 16 LSB of the waveform register. The sign of the 16-bit voltage input value is not extended to the upper byte of the waveform register. The upper byte is instead filled with zeros. 24-bit waveform samples are transferred from the ADE7754 one byte (eight bits) at a time, with the most significant byte shifted out first. The timing is the same as that for the current channels and is shown in Figure 11.

#### ZERO-CROSSING DETECTION

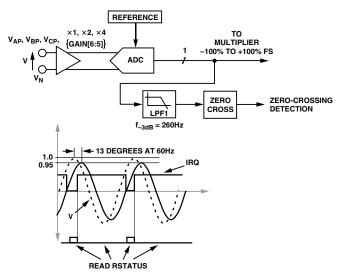

The ADE7754 has rising edge zero-crossing detection circuits for each of voltage channels ( $V_{AP}$ ,  $V_{BP}$ , and  $V_{CP}$ ). Figure 14 shows how the zero-cross signal is generated from the output of the ADC of the voltage channel.

Figure 14. Zero-Crossing Detection on Voltage Channel

The zero-crossing interrupt is generated from the output of LPF1, which has a single pole at 260 Hz (CLKIN = 10 MHz). As a result, there is a phase lag between the analog input signal of the voltage channel and the output of LPF1. The phase response of this filter is shown in the Voltage Channel ADC section. The phase lag response of LPF1 results in a time delay of approximately 0.6 ms (@ 60 Hz) between the zero crossing on the analog inputs of voltage channel and the falling of IRQ.

When one phase crosses zero from negative to positive values (rising edge), the corresponding flag in the interrupt status register (Bits 7 to 9) is set Logic 1. An active low in the  $\overline{IRQ}$  output also appears if the corresponding ZX bit in the interrupt enable register is set to Logic 1.

The flag in the interrupt status register is reset to 0 when the interrupt status register with reset (RSTATUS) is read. Each phase has its own interrupt flag and enable bit in the interrupt register. In addition to the enable bits, the zero-crossing detection interrupt of each phase is enabled/disabled by setting the ZXSEL bits of the MMODE register (Address 0Bh) to Logic 1 or 0, respectively.

#### **Zero-Crossing Timeout**

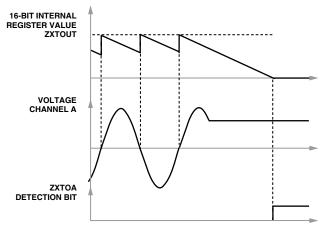

Each zero-crossing detection has an associated internal timeout register (not accessible to the user). This unsigned, 16-bit register is decremented (1 LSB) every 384/CLKIN seconds. The registers are reset to a common user programmed value (i.e., zero cross timeout register—ZXTOUT, Address 12h) every time a zero crossing is detected on its associated input. The default value of ZXTOUT is FFFFh. If the internal register decrements to zero before a zero crossing at the corresponding input is detected, it indicates an absence of a zero crossing in the time determined by the ZXTOUT. The ZXTO detection bit of the corresponding phase in the interrupt status register is then switched on (Bits 4 to 6). An active low on the IRQ output also appears if the SAG enable bit for the corresponding phase in the interrupt enable register is set to Logic 1.

In addition to the enable bits, the zero-crossing timeout detection interrupt of each phase is enabled/disabled by setting the ZXSEL bits of the MMODE register (Address 0Bh) to Logic 1 or Logic 0, respectively. When the zero-crossing timeout detection is disabled by this method, the ZXTO flag of the corresponding phase is switched on all the time.

Figure 15 shows the mechanism of the zero-crossing timeout detection when the line voltage A stays at a fixed dc level for more than CLKIN/384  $\times$  ZXTOUT seconds.

Figure 15. Zero-Crossing Timeout Detection

#### PERIOD MEASUREMENT

The ADE7754 also provides the period measurement of the line voltage. The period is measured on the phase specified by Bits 0 to 1 of the MMODE register. The period register is an unsigned 15-bit register and is updated every period of the selected phase. Bits 0 and 1 and Bits 4 to 6 of the MMODE register select the phase for the period measurement; both selections should indicate the same phase. The ZXSEL bits of the MMODE register (Bits 4 to 6) enable the phases on which the period measurement can be done. The PERDSEL bits select the phase for period measurement within the phases selected by the ZXSEL bits. The resolution of this register is  $2.4 \,\mu\text{s}/\text{LSB}$  when CLKIN = 10 MHz, which is 0.014% when the line frequency is 60 Hz. When the line frequency is 60 Hz, the value of the period register is approximately 6944d. The length of the register enables the measurement of line frequencies as low as 12.7 Hz.

#### LINE VOLTAGE SAG DETECTION

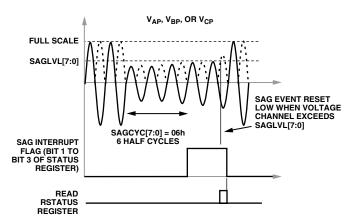

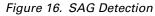

The ADE7754 can be programmed to detect when the absolute value of the line voltage of any phase drops below a certain peak value for a number of half cycles. All phases of the voltage channel are controlled simultaneously. This condition is illustrated in Figure 16.

Figure 16 shows a line voltage falling below a threshold set in the SAG level register (SAGLVL[7:0]) for nine half cycles. Since the SAG cycle register indicates a six half-cycle threshold (SAGCYC[7:0]=06h), the SAG event is recorded at the end of the sixth half-cycle by setting the SAG flag of the corresponding phase in the interrupt status register (Bits 1 to 3 in the interrupt status register). If the SAG enable bit is set to Logic 1 for this phase (Bits 1 to 3 in the interrupt enable register), the IRQ logic output goes active low. See the Interrupts section. All the phases are compared to the same parameters defined in the SAGLVL and SAGCYC registers.

#### SAG Level Set

The content of the SAG level register (one byte) is compared to the absolute value of the most significant byte output from the voltage channel ADC. Thus, for example, the nominal maximum code from the voltage channel ADC with a full-scale signal is 28F5h. See the Voltage Channel ADC section.

Therefore, writing 28h to the SAG level register puts the SAG detection level at full scale and sets the SAG detection to its most sensitive value.

Writing 00h puts the SAG detection level at 0. The detection of a decrease of an input voltage is in this case hardly possible. The detection is made when the content of the SAGLVL register is greater than the incoming sample.

#### PEAK DETECTION

The ADE7754 also can be programmed to detect when the absolute value of the voltage or the current channel of one phase exceeds a certain peak value. Figure 17 illustrates the behavior of the peak detection for the voltage channel.

Figure 17. Peak Detection

Bits 2 and 3 of the measurement mode register define the phase supporting the peak detection. Current and voltage of this phase can be monitored at the same time. Figure 17 shows a line voltage exceeding a threshold set in the voltage peak register (VPEAK[7:0]). The voltage peak event is recorded by setting the PKV flag in the interrupt status register. If the PKV enable bit is set to Logic 1 in the interrupt enable register, the IRQ logic output goes active low. See the Interrupts section.

#### Peak Level Set

The contents of the VPEAK and IPEAK registers compare to the absolute value of the most significant byte output of the selected voltage and current channels, respectively. Thus, for example, the nominal maximum code from the current channel ADC with a full-scale signal is 28F5C2h. See the Current Channel Sampling section. Therefore, writing 28h to the IPEAK register will put the current channel peak detection level at full scale and set the current peak detection to its least sensitive value. Writing 00h puts the current channel detection level at zero. The detection is done when the content of the IPEAK register is smaller than the incoming current channel sample.

#### **TEMPERATURE MEASUREMENT**

The ADE7754 also includes an on-chip temperature sensor. A temperature measurement is made every 4/CLKIN seconds. The output from the temperature sensing circuit is connected to an ADC for digitizing. The resulting code is processed and placed into the temperature register (TEMP[7:0]) which can be read by the user and has an address of 08h. See the Serial Interface section. The contents of the temperature register are signed (twos complement) with a resolution of 4°C/LSB. The temperature register produces a code of 00h when the ambient temperature register = (temperature (°C) – 129)/4. The temperature in the ADE7754 has an offset tolerance of approximately  $\pm$ 5°C. The error can be easily calibrated out by an MCU.

#### PHASE COMPENSATION

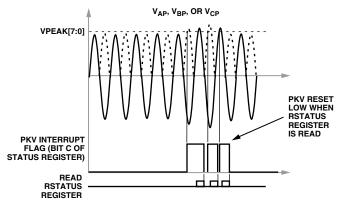

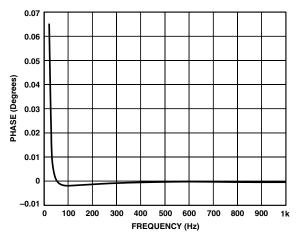

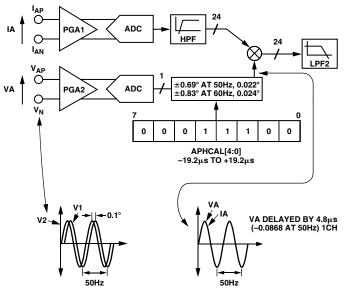

When the HPFs are disabled, the phase difference between the current channel (IA, IB, and IC) and the voltage channel (VA, VB, and VC) is zero from dc to 3.3 kHz. When the HPFs are enabled, the current channels have a phase response as shown in Figure 18a and 18b. The magnitude response of the filter is shown in Figure 18c. As seen from in the plots, the phase response is almost zero from 45 Hz to 1 kHz. This is all that is required in typical energy measurement applications.

Figure 18a. Phase Response of the HPF and Phase Compensation (10 Hz to 1 kHz)

Figure 18b. Phase Response of the HPF and Phase Compensation (40 Hz to 70 Hz)

Figure 18c. Gain Response of HPF and Phase Compensation (Deviation of Gain as % of Gain at 54 Hz)

Despite being internally phase compensated, the ADE7754 must work with transducers that may have inherent phase errors. For example, a phase error of  $0.1^{\circ}$  to  $0.3^{\circ}$  is not uncommon for a CT (current transformer). These phase errors can vary from part to part, and they must be corrected in order to perform accurate power calculations. The errors associated with phase mismatch are particularly noticeable at low power factors. The ADE7754 provides a means of digitally calibrating these small phase errors. The ADE7754 allows a small time delay or time advance to be introduced into the signal processing chain to compensate for small phase errors. Because the compensation is in time, this technique should be used only for small phase errors in the range of  $0.1^{\circ}$  to  $0.5^{\circ}$ . Correcting large phase errors using a time shift technique can introduce significant phase errors at higher harmonics.

The phase calibration registers (APHCAL, BPHCAL, and CPHCAL) are twos complement, 5-bit signed registers that can vary the time delay in the voltage channel signal path from  $-19.2 \ \mu$ s to  $+19.2 \ \mu$ s (CLKIN = 10 MHz). One LSB is equivalent to 1.2  $\mu$ s. With a line frequency of 50 Hz, this gives a phase resolution of  $0.022^{\circ}$  at the fundamental (i.e.,  $360^{\circ} \times 1.2 \ \mu$ s  $\times$  50 Hz).

Figure 19 illustrates how the phase compensation is used to remove a  $0.091^{\circ}$  phase lead in IA of the current channel caused by an external transducer. In order to cancel the lead  $(0.091^{\circ})$ in IA of the current channel, a phase lead must also be introduced into VA of the voltage channel. The resolution of the phase adjustment allows the introduction of a phase lead of  $0.086^{\circ}$ . The phase lead is achieved by introducing a time advance into VA. A time advance of 4.8 µs is made by writing -4 (1Ch) to the time delay block (APHCAL[4:0]), thus reducing the amount of time delay by 4.8 µs. See the Calibration of a 3-Phase Meter Based on the ADE7754 Application Note AN-624.

Figure 19. Phase Calibration

#### ROOT MEAN SQUARE MEASUREMENT

Root Mean Square (rms) is a fundamental measurement of the magnitude of an ac signal. Its definition can be practical or mathematical. Defined practically, the rms value assigned to an ac signal is the amount of dc required to produce an equivalent amount of heat in the same load. Mathematically the rms value of a continuous signal f(t) is defined as

$$F_{rms} = \sqrt{\frac{1}{T} \times \int_{0}^{T} f^{2}(t)dt}$$

(1)

For time sampling signals, rms calculation involves squaring the signal, taking the average, and obtaining the square root:

$$F_{rms} = \sqrt{\frac{1}{N} \times \sum_{i=1}^{N} f^2(i)}$$

(2)

The method used to calculate the rms value in the ADE7754 is to low-pass filter the square of the input signal (LPF3) and take the square root of the result.

With

$$V(t) = V_{rms} \times \sqrt{2} \times \sin(\omega t)$$

then

$$V(t) \times V(t) = V_{rms}^{2} - V_{rms}^{2} \times \cos(2\omega t)$$

The rms calculation is simultaneously processed on the six analog input channels. Each result is available on separate registers.

#### **Current RMS Calculation**

Figure 20 shows the detail of the signal processing chain for the rms calculation on one of the phases of the current channel. The current channel rms value is processed from the samples used in the current channel waveform sampling mode. Note that the APGAIN adjustment affects the result of the rms calculation. See the Current RMS Gain Adjust section. The current rms values are stored in unsigned 24-bit registers (AIRMS, BIRMS, and CIRMS). One LSB of the current rms register is equivalent to 1 LSB of a current waveform sample. The update rate of the current rms measurement is CLKIN/12. With the specified full-scale analog input signal of 0.5 V, the ADC produces an output code which is approximately  $\pm 2,684,354d$ . See the Current Channel ADC section. The equivalent rms values of a full-scale ac signal is 1,898,124d. With offset calibration, the current rms measurement provided in the ADE7754 is accurate within  $\pm 2\%$  for signal input between full scale and full scale/100.

#### Figure 20. Current RMS Signal Processing

Note that a crosstalk between phases can appear in the ADE7754 current rms measurements. This crosstalk follows a specific

pattern. Current rms measurements of Phase A are corrupted by the signal on the Phase C current input, current rms measurements of Phase B are corrupted by the signal on the Phase A current input, and current rms measurements of Phase C are corrupted by the signal on the Phase B current input. This crosstalk is present only on the current rms measurements and does not affect the regular active power measurements. The level of the crosstalk is dependent on the level of the noise source and the phase angle between the noise source and the corrupted signal. The level of the crosstalk can be reduced by writing 01F7h to the address 3Dh. This 16-bit register is reserved for factory operation and should not be written to any other value. When the current inputs are 120° out of phase and the register 3Dh is set to 01F7h, the level of the current rms crosstalk is below 2%.

#### Current RMS Gain Adjust

The active power gain registers (AAPGAIN[11:0], BAPGAIN, and CAPGAIN) affect the active power and current rms values. Calibrating the current rms measurements with these registers is not recommended. The conversion of the current rms registers values to amperes has to be done in an external microcontroller with a specific ampere/LSB constant for each phase. See the Calibration of a 3-Phase Meter Based on the ADE7754 Application Note AN-624. Due to gain mismatches between phases, the calibration of the ampere/LSB constant has to be done separately for each phase. One-point calibration is sufficient for this calibration. The active power gain registers ease the calibration of the active energy calculation in MODE 1 and 2 of the WATMODE register.

If the APGAIN registers are used for active power calibration (WATMOD bits in WATMode register = 1 or 2), the current rms values are changed by the active power gain register value as described in the expression

Current rms register Phase

$$A = \left( rms \times \sqrt{1 + \frac{AAPGAIN}{2^{12}}} \right)$$

For example, when 7FFh is written to the active power gain register, the ADC output is scaled up by 22.5%. Similarly, 800h = -2047d (signed twos complement) and ADC output is scaled by 29.3%. These two examples are illustrated in Figure 20.

#### **Current RMS Offset Compensation**

The ADE7754 incorporates a current rms offset compensation for each phase (AIRMSOS, BIRMSOS, and CIRMSOS). These are 12-bit twos complement signed registers that can be used to remove offsets in the current rms calculations. An offset may exist in the rms calculation due to input noises that are integrated in the dc component of  $V^2(t)$ . The offset calibration will allow the contents of the I<sub>RMS</sub> registers to be maintained at zero when no current is being consumed.

n LSB of the current rms offset are equivalent to  $32768 \times n$  LSB of the square of the current rms register. Assuming that the maximum value from the current rms calculation is 1,898,124 decimal with full-scale ac inputs, then 1 LSB of the current rms offset represents 0.0058% of measurement error at -40 dB below full scale.

$$I_{rms} = \sqrt{I_{rms_0}^2 + IRMSOS \times 32768}$$

where  $I_{rmso}$  is the rms measurement without offset correction.

The current rms offset compensation should be done by testing the rms results at two non-zero input levels. One measurement can be

done close to full scale and the other at approximately full scale/ 100. The current offset compensation can then be derived using these measurements. See the Calibration of a 3-Phase Meter Based on the ADE7754 Application Note AN-624.

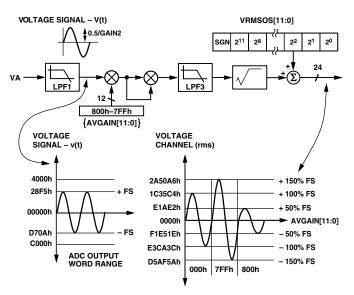

#### Voltage RMS Calculation

Figure 21 shows the details of the signal processing chain for the rms calculation on one of the phases of the voltage channel. The voltage channel rms value is processed from the samples used in the voltage channel ADC can be scaled by  $\pm 50\%$  by changing VGAIN registers to perform an overall apparent power calibration. See the Apparent Power Calculation section. The VGAIN adjustment affects the rms calculation because it is done before the rms signal processing. The voltage rms values are stored in unsigned 24-bit registers (AVRMS, BVRMS, and CVRMS). 256 LSB of the voltage rms register is approximately equivalent to one LSB of a voltage waveform sample. The update rate of the voltage rms measurement is CLKIN/12.

With the specified full-scale ac analog input signal of 0.5 V, the LPF1 produces an output code that is approximately  $\pm 10,217$  decimal at 60 Hz. See the Voltage Channel ADC section. The equivalent rms value of a full-scale ac signal is approximately 7,221d (1C35h), which gives a voltage rms value of 1,848,772d (1C35C4h) in the V<sub>RMS</sub> register. With offset calibration, the voltage rms measurement provided in the ADE7754 is accurate within  $\pm 0.5\%$  for signal input between full scale and full scale/20.

Figure 21. Voltage RMS Signal Processing

#### Voltage RMS Gain Adjust

The voltage gain registers (AVGAIN[11:0], BVGAIN, and CVGAIN) affect the apparent power and voltage rms values. Calibrating the voltage rms measurements with these registers is not recommended. The conversion of the voltage rms registers values to volts has to be done in an external microcontroller with a specific volt/LSB constant for each phase. See the Calibration of a 3-Phase Meter Based on the ADE7754 Application Note AN-624. Due to gain mismatches between phases, the calibration of the volt/LSB constant has to be done separately for each phase. One point calibration is sufficient for this calibration. The voltage gain registers are aimed to ease the calibration of the apparent energy calculation in MODE 1 and MODE 2 of the VAMODE register. If the VGAIN registers are used for apparent power calibration (WATMOD bits in VAMODE register = 1 or 2), the voltage rms values are changed by voltage gain register value as described in the expression

*Voltage rms register Phase A* =

$$\left( rms \times \left\{ 1 + \frac{AVGAIN}{2^{12}} \right\} \right)$$

For example, when 7FFh is written to the voltage gain register, the ADC output is scaled up by +50%. 7FFh = 2047d, 2047/ $2^{12}$  = 0.5. Similarly, 800h = -2047d (signed twos complement) and ADC output is scaled by -50%. These two examples are illustrated in Figure 21.

#### Voltage RMS Offset Compensation

The ADE7754 incorporates a voltage rms offset compensation for each phase (AVRMSOS, BVRMSOS, and CVRMSOS). These are 12-bit twos complement signed registers that can be used to remove offsets in the voltage rms calculations. An offset may exist in the rms calculation due to input noises and offsets in the input samples. The offset calibration allows the contents of the  $V_{RMS}$  registers to be maintained at zero when no voltage is applied.

n LSB of the voltage rms offset are equivalent to  $64 \times$  n LSB of the voltage rms register. Assuming that the maximum value from the voltage rms calculation is 1,898,124 decimal with full-scale ac inputs, then 1 LSB of the voltage rms offset represents 0.07% of measurement error at -26 dB below full scale.

$$V_{rms} = V_{rms_0} + VRMSOS \times 64$$

where  $V_{rmso}$  is the rms measurement without offset correction.

The voltage rms offset compensation should be done by testing the rms results at two non-zero input levels. One measurement can be done close to full scale and the other at approximately full scale/10. The voltage offset compensation can then be derived from these measurements. See the Calibration of a 3-Phase Meter Based on the ADE7754 Application Note AN-624.

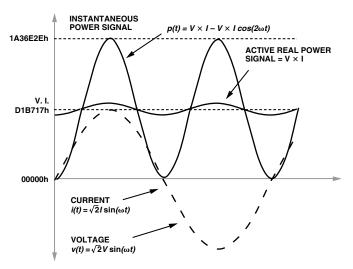

#### ACTIVE POWER CALCULATION

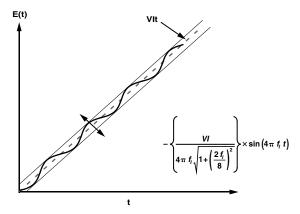

Electrical power is defined as the rate of energy flow from source to load. It is given by the product of the voltage and current waveforms. The resulting waveform is called the instantaneous power signal and it is equal to the rate of energy flow at every instant of time. The unit of power is the watt or joules/sec. Equation 5 gives an expression for the instantaneous power signal in an ac system.

$$v(t) = \sqrt{2V}\sin(\omega t) \tag{3}$$

$$i(t) = \sqrt{2I}\sin(\omega t) \tag{4}$$

where V = rms voltage and I = rms current.

$$p(t) = v(t) \times i(t)$$

$$p(t) = VI - VI \cos(2\omega t)$$

(5)

The average power over an integral number of line cycles (n) is given by the expression in Equation 6.

$$P = \frac{1}{nT} \int_{0}^{nT} p(t)dt = VI$$

(6)

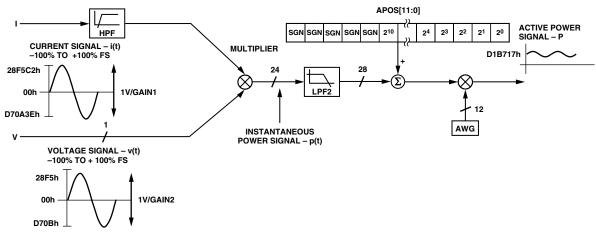

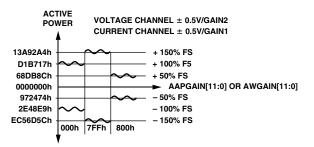

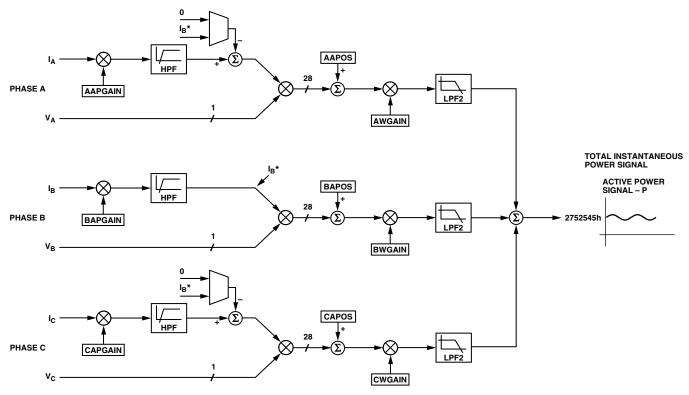

where T is the line cycle period. P is referred to as the active or real power. Note that the active power is equal to the dc component of the instantaneous power signal p(t) in Equation 5 (i.e., VI). This is the relationship used to calculate active power in the ADE7754 for each phase. The instantaneous power signal p(t)is generated by multiplying the current and voltage signals in each phase. The dc component of the instantaneous power signal in each phase (A, B, and C) is then extracted by LPF2 (low-pass filter) to obtain the active power information on each phase. This process is illustrated in Figure 22. In a polyphase system, the total electrical power is simply the sum of the real power in all active phases. The solutions available to process the total active power are discussed in the following section.

Figure 22. Active Power Calculation

Since LPF2 does not have an ideal brick wall frequency response (see Figure 23), the active power signal has some ripple due to the instantaneous power signal. This ripple is sinusoidal and has a frequency equal to twice the line frequency. Since the ripple is sinusoidal in nature, it is removed when the active power signal is integrated to calculate the energy. See the Energy Calculation section.

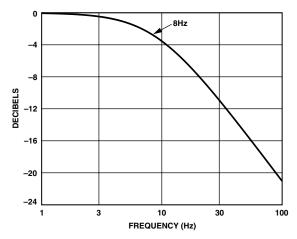

Figure 23. Frequency Response of the LPF Used to Filter Instantaneous Power in Each Phase

Figure 24. Active Power Signal Processing

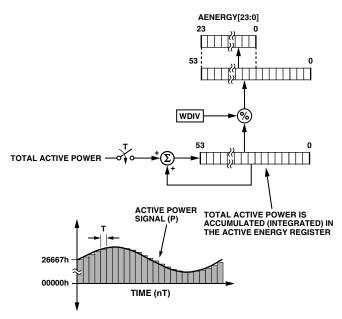

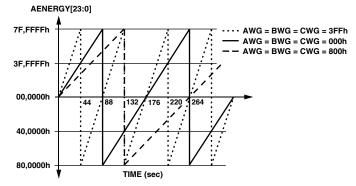

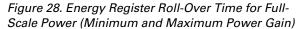

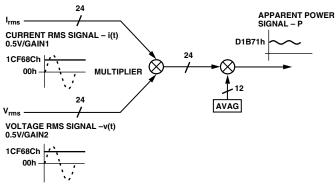

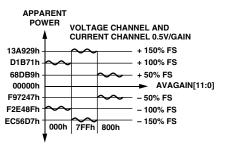

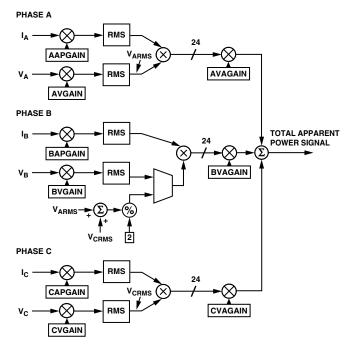

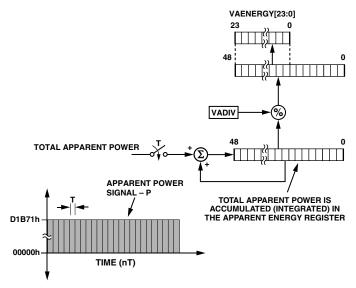

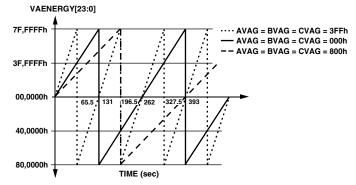

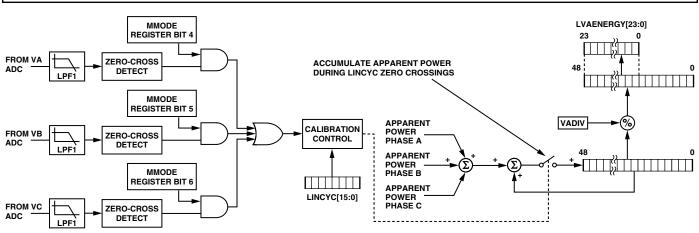

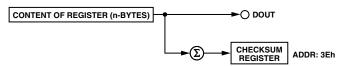

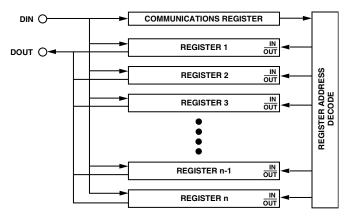

Figure 24 shows the signal processing in each phase for the active power in the ADE7754.