# **Synchronous-Buck Power Stage**

Check for Samples: UCD74106

#### **FEATURES**

- Fully Integrated Power Switches With Drivers for Single and Multiphase Synchronous Buck Converters

- Full Compatibility With TI Fusion Digital Power Supply Controllers, (UCD91xx and UCD92xx Families)

- Compatible With Analog Domain Controllers

- Wide Input Voltage Range:

- 4.5 V to 18 V

- Operational Down to 2.2-V Input With an External Bias Supply

- Up to 6-A Output Current

- Operational to 2-MHz Switching Frequency

- Current Limit With Current Limit Flag

- Onboard Regulated 6-V Driver Supply From VIN

- Thermal Protection and Monitoring

#### **APPLICATIONS**

- Digitally-Controlled Synchronous-Buck Power Stage for Single and Multi-Phase Applications

- High Efficiency Small Size Regulators for Desktop, Server, Telecom and Notebook Applications

- Synchronous-Buck Power Stages

# **DESCRIPTION**

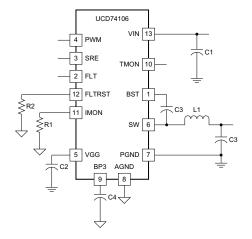

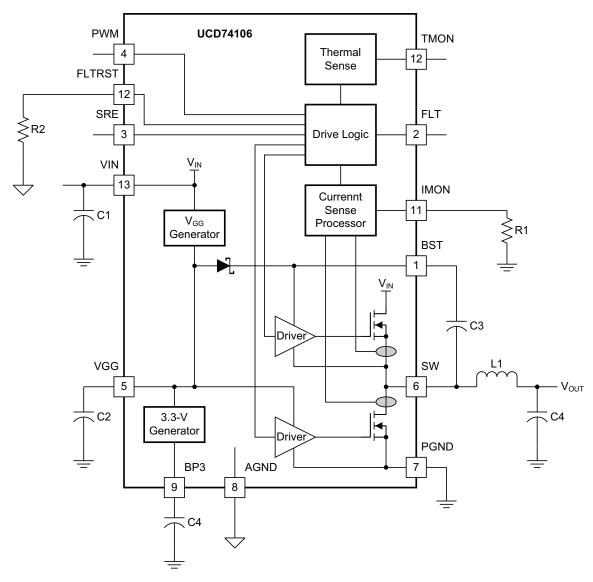

The UCD74106 is a complete power system ready to drive a buck power supply (Figure 1). High-side MOSFETs, low-side MOSFETs, drivers, current sensing circuitry and necessary protection functions are all integrated into one monolithic solution to facilitate minimum size and maximum efficiency. Driver circuits provide high charge and discharge current for the high-side NMOS switch and the low-side NMOS synchronous rectifier in a synchronous buck circuit. The MOSFET gates are driven to 6.25 V by an internally regulated  $V_{\rm GG}$  supply. The internal  $V_{\rm GG}$  regulator can be disabled to permit the user to supply an independent gate drive voltage. This flexibility allows a wide power conversion input voltage range of 2.2 V to 18 V. Internal Under Voltage Lockout (UVLO) logic insures  $V_{\rm GG}$  is good before allowing chip operation.

A drive logic block allows operation in one of two modes. In synchronous mode, the logic block uses the PWM signal to control both the high-side and low-side gate drive signals. Dead time is optimized to prevent cross conduction. The synchronous rectifier enable (SRE) pin controls whether or not the low-side FET is turned on when the PWM signal is low.

# Simplified Application Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **DESCRIPTION (CONT.)**

On-board current sense amplifiers monitor the current to safeguard the power stage from sudden high current loads. In the event of an over-current fault, the output power stage is turned off and the Fault Flag (FLT) is asserted to alert the controller.

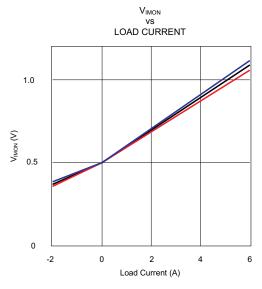

Output current is measured and monitored by a precision integrated current sense element. This method provides an accuracy of ±5%. The amplified signal is available for use by the controller on the IMON pin. The IMON pin has a positive offset so that both positive (sourcing) and negative (sinking) current can be sensed.

If the die temperature exceeds 150°C, the temperature sensor initiates a thermal shutdown that halts output switching and sets the FLT flag. Normal operation resumes when the die temperature falls below the thermal hysteresis band and the Fault Flag is re-set by the controller.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### Table 1. ORDERING INFORMATION

| OPERATING<br>TEMPERATURE<br>RANGE, T <sub>A</sub> | PIN COUNT | ORDERABLE PART<br>NUMBER | SUPPLY       | PACKAGE  | TOP SIDE MARKING |

|---------------------------------------------------|-----------|--------------------------|--------------|----------|------------------|

| –40°C to 125°C                                    | 12 nin    | UCD74106RGMR             | Reel of 2500 | QFN      | UCD74106         |

| -40 C to 125 C                                    | 13-pin    | UCD74106RGMT Reel of 250 |              | 00074100 |                  |

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                           |                   | MIN  | MAX     | UNIT |

|-------------------------------------------|-------------------|------|---------|------|

| Supply voltage, VIN                       |                   | -0.3 | 20      |      |

| Particular POT                            | DC                | -0.3 | SW + 7  |      |

| Boot voltage, BST                         | AC <sup>(2)</sup> |      | 34      |      |

| Gate supply voltage, VGG                  |                   | -0.3 | 7       | V    |

| Switch voltage, SW                        | DC                | -2   | VIN + 1 |      |

|                                           | AC <sup>(2)</sup> |      | 34      |      |

| Analog outputs, TMON, IMON                |                   | -0.3 | 3.6     |      |

| Digital I/O's, PWM, SRE, FLT, FLTRST      |                   | -0.3 | 5.5     | V    |

| Junction temperature, T <sub>J</sub>      |                   | -55  | 150     | 00   |

| Storage temperature, T <sub>stq</sub>     |                   | -65  | 150     | °C   |

| ESD rating, Human Body Model (HBM)        |                   |      | 2000    |      |

| ESD rating, Charged Device Model (CDM)    |                   |      | 500     | V    |

| Lead temperature Reflow soldering, 10 sec |                   |      | 300     | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. Consult company packaging information for thermal limitations and considerations of packages.

(2) AC levels are limited to within 5 ns.

## THERMAL INFORMATION

|                  |                                                             | UCD74106 |       |

|------------------|-------------------------------------------------------------|----------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | RGM      | UNITS |

|                  |                                                             | 13 PINS  |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 70.2     |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 47.3     |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 11.0     | 90044 |

| Ψлт              | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.9      | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter (6)            | 11.0     |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.9      |       |

- For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 |                                        |                          | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------|--------------------------|-----|-----|-----|------|

| $V_{\text{IN}}$ | Power input voltage                    | Internally generated VGG | 4.5 | 12  | 18  |      |

|                 |                                        | Externally supplied VGG  | 2.2 | 12  | 18  | V    |

| $V_{G}$         | Externally supplied gate drive voltage |                          |     | 6.2 |     | •    |

| G               |                                        |                          | 4.5 | 0.2 |     |      |

| $T_{J}$         | Operating junction temperature range   |                          | -40 |     | 125 | ∘C   |

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12 V; 1  $\mu F$  from BP3 to GND, 0.22  $\mu F$  from BST to SW, 4.7  $\mu F$  from VGG to PGND,  $T_A = T_J = -40^{\circ}C$  to 125°C (unless otherwise noted).

| PARAMETER          |                                        | AMETER TEST CONDITION                                                 |      | TYP  | MAX  | UNITS |

|--------------------|----------------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| Supply             |                                        |                                                                       |      |      |      |       |

|                    | Supply current                         | Outputs not switching, V <sub>IN</sub> = 2.2 V, V <sub>GG</sub> = 5 V |      | 4    |      | 0     |

|                    | Supply current                         | Outputs not switching, V <sub>IN</sub> = 12 V,                        |      | 4    |      | mA    |

| Gate Dr            | ive Under Voltage Lockout              |                                                                       |      |      |      |       |

|                    | VGG UVLO ON                            | BP3 rising                                                            |      | 4.0  |      | V     |

|                    | VGG UVLO OFF                           | BP3 falling                                                           |      | 3.8  |      | V     |

|                    | VGG UVLO hysteresis                    |                                                                       |      | 200  |      | mV    |

| VGG Su             | pply Generator                         |                                                                       |      |      |      |       |

|                    | VGG                                    | V <sub>IN</sub> = 7 to 14 V                                           | 5.2  | 6.25 | 6.8  | V     |

|                    | VGG drop out                           | $V_{IN}$ = 4.5 to 7 V, $I_{VGG}$ < 20 mA                              |      |      | 200  | mV    |

| BP3 Su             | pply Voltage                           |                                                                       |      |      |      |       |

|                    | BP3                                    | I <sub>DD</sub> = 0 to 10 mA                                          | 3.15 | 3.3  | 3.45 | V     |

| Input Si           | gnal (PWM, SRE)                        |                                                                       |      |      |      |       |

| V <sub>IH</sub>    | Positive-going input threshold voltage |                                                                       |      |      | 2.3  |       |

| V <sub>IL</sub>    | Negative-going input threshold voltage |                                                                       | 1    |      |      | V     |

|                    | Tristate condition                     |                                                                       | 1.4  |      | 1.9  |       |

| t <sub>HLD_R</sub> | 3-state hold-off time                  | V <sub>PWM</sub> = 1.65 V                                             |      |      | 200  | ns    |

|                    | I <sub>PWM</sub> input current         | V <sub>PWM</sub> = 5.0 V                                              |      | 250  |      |       |

|                    |                                        | V <sub>PWM</sub> = 3.3 V                                              |      | 165  |      |       |

|                    |                                        | V <sub>PWM</sub> = 0 V                                                |      | -165 |      |       |

|                    | I <sub>SRE</sub> input current         | V <sub>SRE</sub> = 5.0 V                                              |      | 1    |      | μA    |

|                    |                                        | V <sub>SRE</sub> = 3.3 V                                              |      | 1    |      |       |

|                    |                                        | V <sub>SRE</sub> = 0 V                                                |      | 1    |      |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12 V; 1  $\mu F$  from BP3 to GND, 0.22  $\mu F$  from BST to SW, 4.7  $\mu F$  from VGG to PGND,  $T_A = T_J = -40^{\circ}C$  to 125°C (unless otherwise noted).

| PARA   | METER                                                               | TEST CONDITION                                                               | MIN   | TYP   | MAX   | UNITS |

|--------|---------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|-------|

| FAUL1  | Flag (FLT)                                                          |                                                                              |       |       |       |       |

| FLT    | Output high level                                                   | I <sub>OH</sub> = 500 μA                                                     | 2.7   |       |       | V     |

|        | Output low level                                                    | I <sub>OL</sub> = 500 μA                                                     |       |       | 0.6   | V     |

| Currer | t Limit                                                             |                                                                              |       |       |       |       |

|        | Over current threshold                                              | PWM frequency = 1 MHz, V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 1.2 V      | 6.7   | 7.5   | 8.2   | А     |

| Currer | t Sense Amplifier                                                   |                                                                              |       |       |       |       |

|        | Gain <sup>(1)</sup>                                                 | $I_{MON}/I_{SW}$ , $0.3 \le V(I_{MON}) \le 1.3 V$                            | 4.106 | 4.322 | 4.538 | μΑ/Α  |

|        | Zero amp load offset                                                | $0 \le V(I_{MON}) \le 3.1 \text{ V}, R_{IMON} = 22.6 \text{ k}\Omega$        |       | 22.1  |       | μΑ    |

|        | Thermal Sense                                                       |                                                                              |       |       |       |       |

|        | Thermal shutdown <sup>(1)</sup>                                     |                                                                              |       | 155   |       | °C    |

|        | Thermal shutdown hysteresis (1)                                     |                                                                              |       | 30    |       | - 'C  |

|        | Temperature sense T <sup>(1)</sup>                                  | Gain                                                                         |       | 10    |       | mV/°C |

|        | Temperature sense T offset                                          | $T_J = 25 \text{ °C}, -100  \mu\text{A} \leq I_{TMON} \leq 100  \mu\text{A}$ |       | 750   |       | mV    |

|        | POWER Drive Train                                                   |                                                                              |       |       |       |       |

|        | Propagation delay from PWM to switch node going high <sup>(1)</sup> |                                                                              |       | 20    |       |       |

|        | High-side MOSFET turn on – dead Time <sup>(1)</sup>                 |                                                                              | 3     | 5     | 15    | ns    |

|        | Low-side MOSFET turn on – dead time <sup>(1)</sup>                  |                                                                              | 3     | 7     | 15    |       |

|        | Min PWM pulse width <sup>(1)</sup>                                  |                                                                              |       | 20(2) |       |       |

<sup>(1)</sup> As designed and characterized, not fully tested in production.

(2) There is no inherent limit on the minimum pulse width. Depending on the board layout, partial enhancement of the high-side FET may be observed for shorter pulse widths.

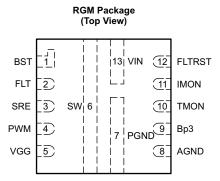

# **DEVICE INFORMATION**

## **BLOCK DIAGRAM**

Figure 1. Typical Block Diagram

# **TERMINAL FUNCTIONS**

| TERMINAL |     | 1/0 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWM      | 4   | ı   | 20-kΩ input capable of accepting 3.3-V or 5-V logic level signals up to 2 MHz. A Schmitt trigger input comparator desensitizes this pin from external noise. This pin controls the state of the high-side MOSFET and the low-side MOSFET when SRE is high. When PWM is in HiZ state the output power stage is turned off within 200 ns.                                                                                                                                              |

| SRE      | 3   | I   | Synchronous rectifier enable input. High impedance digital input capable of accepting 3.3-V or 5-V logic level signals used to control the synchronous rectifier switch. An appropriate anti-cross-conduction delay is used during synchronous mode.                                                                                                                                                                                                                                 |

| BST      | 1   | I   | Charge pump capacitor connection. It provides a floating supply for the high-side driver. Connect a 0.22-µF ceramic capacitor from this pin to SW.                                                                                                                                                                                                                                                                                                                                   |

| VGG      | 5   | I/O | Gate drive voltage for the power MOSFETs. For $V_{IN} > 4.5$ V, the internal $V_{GG}$ generator can be used. For $V_{IN} < 4.5$ V, this pin should be driven from an external bias supply. In all cases, bypass this pin with a 4.7- $\mu$ F (min), 10-V (min) ceramic capacitor to PGND.                                                                                                                                                                                            |

| BP3      | 9   | 0   | Output of internal 3.3-V LDO regulator for powering internal logic circuits. Bypass this pin with 1 µF (min) to AGND . This LDO is supplied by the VGG pin.                                                                                                                                                                                                                                                                                                                          |

| IMON     | 11  | 0   | Current sense monitor output. Provides a current source output that is proportional to the current flowing in the low-side MOSFET. The gain on this pin is equal to 4.32 $\mu$ A/A. The IMON pin should be connected to a 22.6-k $\Omega$ resistor to AGND to produce a voltage proportional to the power-stage load current. The IMON pin sources 22.1 $\mu$ A at no load. This provides a pedestal that permits the reporting of negative (sinking) current.                       |

| TMON     | 10  | 0   | Temperature sense pin. The voltage on this pin is proportional to the die temperature. The gain is 10 mV/°C . At $T_J = 25$ °C, the output voltage has an offset of 0.75 V. When the die temperature reaches the thermal shutdown threshold, this pin is pulled to BP3 and power FETs are switched off. Normal operation resumes when the die temperature falls below the thermal hysteresis band.                                                                                   |

| FLT      | 2   | 0   | Fault flag. This signal is a 3.3-V digital output which is latched high when the load current exceeds the current limit trip point. When tripped both high side and low side are latched off. See FLT clear protocol as defined by FLTRST. Additionally, if the die temperature exceeds 150°C, $V_{\rm IN}$ and/or $V_{\rm GG}$ is outside of UVLO limits, the output switching will be halted and FLT flag is set. Normal operation resumes after fault clear sequence is complete. |

| FLTRST   | 12  | I   | Fault reset mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PGND     | 7   | -   | Shared power ground return for the buck power stage                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SW       | 6   |     | Switching node of the buck power stage and square wave input to the buck inductor. Electrically this is the connection of the high-side MOSFET source to the low-side MOSFET drain.                                                                                                                                                                                                                                                                                                  |

| VIN      | 13  | -   | Input voltage to the buck power stage and driver circuit                                                                                                                                                                                                                                                                                                                                                                                                                             |

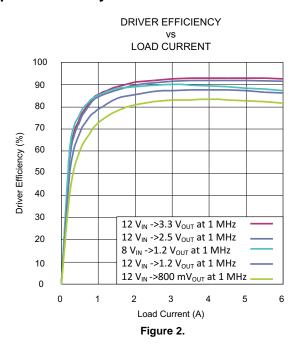

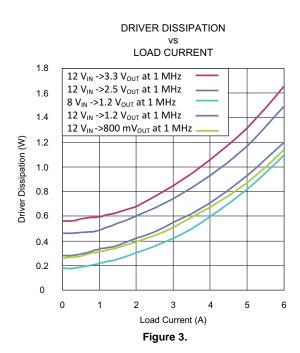

## **TYPICAL CHARACTERISTICS**

# **Typical Efficiency**

## **PWM and SRE Behavior**

The PWM and SRE (Synchronous Rectifier Enable) pins control the high-side and low-side drivers, as described in Table 2.

Table 2. PWM and SRE Behavior

|            | PWM = High        | PWM = Low         | PWM = HiZ          |

|------------|-------------------|-------------------|--------------------|

| SRE = High | HS = ON, LS = OFF | HS = OFF, LS = ON | HS = OFF, LS = OFF |

| SRE = Low  | HS = ON LS = OFF  | HS = OFF LS = OFF | HS = OFF IS = OFF  |

#### **Fault Modes**

## **Fault Reset Mode**

The Fault Reset Mode can be programmed with the FLTRST pin, as described in Table 3

# Table 3.

| Mode | FLTRST | FLT Clear          |

|------|--------|--------------------|

| 1    | GND    | PWM = HiZ          |

| 2    | BP3    | PWM = 0. $SRE = 0$ |

| 3    | Open   | PWM = 1 pulse      |

## MODE 1

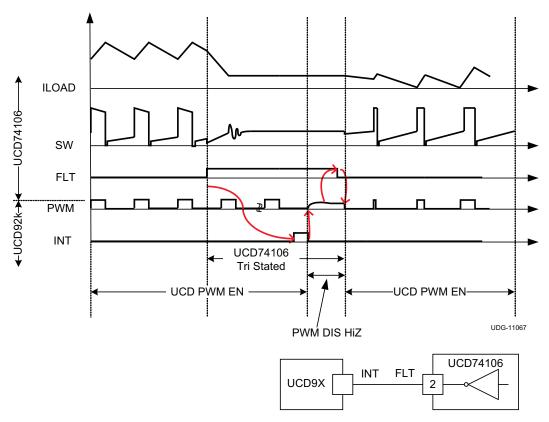

Figure 4. Fault Handshake Protocol, (PWM HiZ)

# **NOTE**

## Handshake Sequence:

- 1. UCD74106 detects fault condition FLT flag is set

- 2. FLT flag generates UCD interrupt

- 3. UCD releases PWM -HiZ state

- 4. UCD74106 detects (HiZ) as FLT clear; if fault condition is no longer present then flag is cleared

- 5. If FLT clears UCD responds to the Start command, Else PWM stays in HiZ state

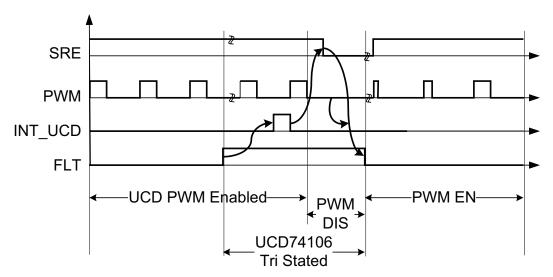

#### MODE 2

Figure 5. Fault Handshake Protocol, (PWM SRE)

## **NOTE**

## Handshake Sequence:

- 1. UCD74106 detects fault condition FLT is set

- 2. FLT flag generates interrupt

- 3. UCD sets SRE low AND stops PWM

- 4. UCD74106 reads (SRE and PWM) = low as FLT clear; if fault condition is no longer present then flag is cleared.

- 5. If FLT clears UCD responds to the Start command, Else (PWM and SRE) = low

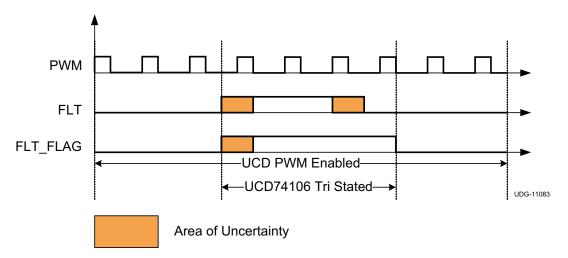

#### MODE 3

Figure 6. Fault Handshake Protocol, (PWM pulses)

### **NOTE**

#### No Handshake Re-Set:

- 1. UCD74106 detects fault condition FL\_FLAG is set

- 2. No action on UCD side.

- 3. UCD74106 reads one complete PWM pulse without FLT being present and re-sets FLT\_FLAG signal on the falling edge of PWM.

- 4. Within the area of uncertainty: FLT rising edge to FLT\_FLAG rising edge delay is zero (gate delay only).

- 5. PWM falling edge to FLT\_FLAG falling edge delay is zero (gate delay only).

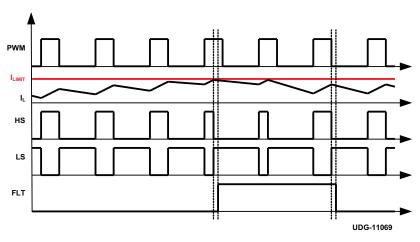

The high-side current limit fault behavior shown in Figure 7.

Figure 7.

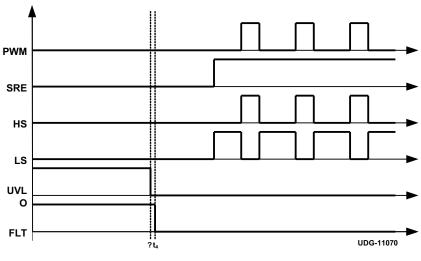

In general, FLT is always cleared by the first complete PWM pulse (a rising and a falling edge) without a fault present. This is true for all faults including UV and OT. The only exception to this occurs during start up where FLT will self clear once UVLO is disabled, as shown in Figure 8. However, if a subsequent under voltage condition occurs the fault must be cleared by one complete PWM pulse without a fault, as shown in Figure 7.

Figure 8.

# **IMON Behavior**

The plot in Figure 9 shows how the voltage on the IMON pin will behave with a 22.6-k $\Omega$  resistor. The solid dark line represents the typical behavior and the shaded region represents the tolerance band due too gain.

Figure 9.

Figure 10.

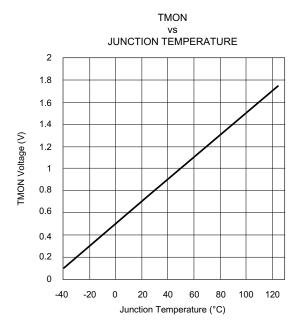

#### **TMON Behavior**

The voltage on this pin is proportional to the die temperature:

$$T_{MON} = T_{OFFSET} + T_{GAIN} \times T_{J}$$

(1)

**Table 4. Temperature Sense Definitions**

| NAME                | DESCRIPTION                          |

|---------------------|--------------------------------------|

| T <sub>MON</sub>    | Voltage from TMON pin to GND         |

| T <sub>OFFSET</sub> | Thermal sense T offset               |

| T <sub>GAIN</sub>   | Thermal sense T gain                 |

| T <sub>1</sub>      | Device internal junction temperature |

Figure 11.

If the junction temperature exceeds approximately 155°C, the device will enter thermal shutdown. This will assert the FLT pin, both MOSFETs will be turned off and the switch node will become high impedance. When the junction temperature cools by approximately 30°C, the device will exit thermal shutdown and resume switching as directed by the PWM and SRE pins.

#### APPLICATION INFORMATION

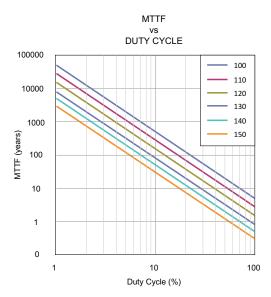

# **Operating Frequency**

Switching frequency is a key place to start the design of any DC/DC converter. This will set performance limits on things such as: maximum efficiency, minimum size, and achievable closed loop bandwidth. A higher switching frequency is, generally, going to yield a smaller design at the expense of a lower efficiency. The size benefit is principally a result of the smaller inductor and capacitor energy storage elements needed to maintain ripple and transient response requirements. The additional losses result from a variety of factors, however, one of the largest contributors is the loss incurred by switching the MOSFETs on and off. The integrated nature of the UCD74106 makes these losses drastically smaller and subsequently enables excellent efficiency from a few hundred kHz up to the low MHz. For a reasonable trade off of size versus efficiency, 750 kHz is a good place to start.

#### **VGG**

If 4.5 V <  $V_{IN} \le 6$  V then a simple efficiency enhancement can be achieved by connecting  $V_{GG}$  directly to  $V_{IN}$ . This allows the solution to bypass the drop-out voltage of the internal  $V_{GG}$  linear regulator, subsequently improving the enhancement of the MOSFETs. When doing this it is critical to make sure that  $V_{GG}$  never exceeds the absolute maximum rating of 7 V.

### Inductor selection

There are three main considerations in the selection of an inductor once the switching frequency has been determined. Any real world design is an iterative trade off of each of these factors.

- 1. The electrical value which in turn is driven by:

- (a) RMS current

- (b) The maximum desired output ripple voltage

- (c) The desired transient response of the converter

- 2. Losses

- (a) Copper (PCu)

- (b) Core (Pfe)

- 3. Saturation characteristics of the core

#### **Inductance Value**

The principle equation used to determine the inductance is:

$$v_{L}(t) = L \frac{di_{L}(t)}{dt}$$

(2)

During the on time of the converter the inductance can be solved to be:

$$L = \frac{V_{IN} - V_{OUT}}{\Delta I} \frac{D}{f_{S}}$$

(3)

### **Table 5. Definitions**

| V <sub>IN</sub>  | Input voltage                                                       |

|------------------|---------------------------------------------------------------------|

| V <sub>OUT</sub> | Output voltage                                                      |

| f <sub>S</sub>   | Switching frequency                                                 |

| D                | Duty cycle (V <sub>OUT</sub> /V <sub>IN</sub> for a buck converter) |

| ΔΙ               | The target peak-to-peak inductor current                            |

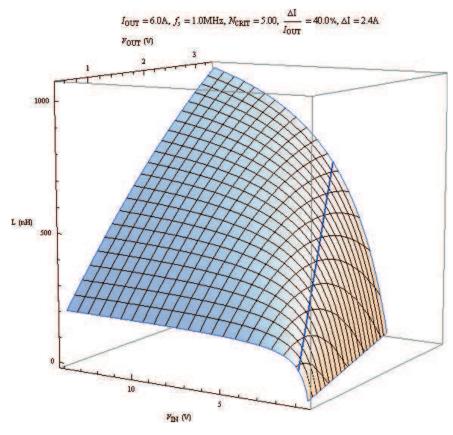

In general, it is desirable to make  $\Delta I$  large to improve transient response and small to reduce output ripple voltage and RMS current. A number of considerations go into this however,  $\Delta I = 0.4~I_{OUT}$  results in a small  $I_{LRMS}$  without an unnecessary penalty on transient response. It also creates a reasonable ripple current that most practical capacitor banks can handle. Here  $I_{OUT}$  is defined as the maximum expected steady state current.

Plugging these assumptions into the above inductance equation results in:

$$L = 5 \frac{V_{IN} - V_{OUT}}{2 \times I_{OUT}} \frac{D}{f_S}$$

(4)

For example, plotting this result as a function of  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  results in:

- $I_{OUT} = 6.0 \text{ A}$

- $f_S = 1.0 \text{ MHz}$

- N<sub>CRIT</sub> = 5

- $\Delta I/I_{OUT} = 40\%$

- ∆I = 2.4 A

- V<sub>OUT</sub> (V)

Figure 12. V<sub>IN</sub> and V<sub>OUT</sub>

#### **NOTE**

The maximum inductance occurs at the maximum  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  shown in Figure 12. In general, this inductance value should be used in order to keep the inductor ripple current from becoming too large over the range of supported  $V_{\text{IN}}$  and  $V_{\text{OUT}}$ .

#### Inductor Losses and Saturation

The current rating of an inductor is based on two things, the current necessary to raise the component temperature by 40°C and the current level necessary to reduce the inductance to 80% of its initial value (saturation current). The current rating is the lower of these two numbers. Both of these factors are influenced by the choice of core material. Popular materials currently in use are: ferrite, powdered alloy and powdered iron.

Ferrite is regarded as the highest performance material and as such is the lowest loss and the highest cost. Solid ferrite all by itself will saturate with a relatively small amount of current. This can be addressed by inserting a gap into the core. This, in effect, makes the inductor behave in a linear manner over a wide DC current range. However, once the inductance begins to roll off, these gapped materials exhibit a "sharp" saturation characteristic. In other words the inductance value reduces rapidly with increases in current above the saturation level. This can be dangerous if not carefully considered, in that the current can rise to dangerous levels.

Powdered iron has the advantage of lower cost and a soft saturation characteristic; however, its losses can be very large as switching frequencies increase. This can make it undesirable for a UCD74106 based application where higher switching frequency may be desired. It's also worth noting that many powdered iron cores exhibit an aging characteristic where the core losses increase over time. This is a wear out mechanism that needs to be considered when using these materials.

The powdered alloy cores bring the soft saturation characteristics of powered iron with considerable improvements in loss without the wear-out mechanism observed in powered iron. These benefits come at a cost premium.

In general the following relative figure of merits can be made:

FERRITE

POWDERED ALLOY

POWDERED IRON

COST

High

Medium

Low

LOSS

Low

Medium

High

SATURATION

Rapid

Soft

Soft

**Table 6. Core Material Choices**

When selecting an inductor with an appropriate core it's important to have in mind the following:

- I<sub>LRMS</sub>, maximum RMS current

- ΔI, maximum peak-to-peak current

- · I<sub>MAX</sub>, maximum peak current

The RMS current can be determined by the following equation:

$$I_{LRMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I^2}{12}}$$

(5)

When the 40% ripple constraint is used at maximum load current, this equation simplifies to:  $I_{LRMS} \approx I_{OUT}$ .

It is widely recognized that the Steinmetz equation (P<sub>fe</sub>) is a good representation of core losses for sinusoidal stimulation. It is important to recognize that this approximation applies to sinusoidal excitation only. This is a reasonable assumption when working with converters whose duty cycles are near 50%, however, when the duty cycle becomes narrow this estimate may no longer be valid and considerably more loss may result.

$$P_{fe} = k \times f^{\alpha} \times B_{AC}^{\beta}$$

(6)

The principle drivers in this equation are the material and its respective geometry  $(k, \alpha, \beta)$ , the peak AC flux density  $(B_{AC})$  and the excitation frequency (f). The frequency is simply the switching frequency of the converter while the constant k, can be computed based on the effective core volume  $(V_e)$  and a specific material constant  $(k_{fe})$ .

$$k = k_{fe} \times V_e \tag{7}$$

The AC flux density (B<sub>AC</sub>) is related to the conventional inductance specifications by the following relationship:

$$B_{AC} = \frac{L}{A_e \times N} \frac{\Delta I}{2}$$

(8)

Where L is the inductance,  $A_e$ , is the effective cross sectional area that the flux takes through the core and N is the number of turns.

Some inductor manufactures use the inductor  $\Delta I$  as a figure of merit for this loss, since all of the other terms are a constant for a given component. They may provide a plot of core loss versus  $\Delta I$  for various frequencies where  $\Delta I$  can be calculated as:

$$\Delta I = \frac{V_{IN} - V_{OUT}}{L} \frac{D}{f_S}$$

(9)

$I_{MAX}$  has a direct impact on the saturation level. A good rule of thumb is to add 15% of head room to the maximum steady state peak value to provide some room for transients.

$$I_{MAX} = 1.15 \times \left(I_{OUT} + \frac{\Delta I}{2}\right) \tag{10}$$

For example for a 6-A design has the following:

Table 7. 6-A Design: Inductor Current Requirements

| lout              | 6 A   |

|-------------------|-------|

| I <sub>LRMS</sub> | 6 A   |

| ΔΙ                | 2.4 A |

| I <sub>MAX</sub>  | 9.6 A |

Armed with this data one can now approach the inductor datasheet to select a part with a saturation limit above 9 A and current heating limit above 6 A. Furthermore total losses can be estimated based on the datasheet DCR value ( $I_{LRMS}^2 \times DCR$ ) and the core loss curves for a given frequency and  $\Delta I$ .

### **Input Capacitance**

Due to the non-zero impedance of the power planes of the input voltage rail, it is necessary to add some local capacitance near the UCD74106 to ensure that the voltage at this node is quiet and stable. The primary things to consider are:

- · The radiated fields generated by the di/dt and dv/dt from this node

- RMS currents capability needed in the capacitors

- · The AC voltage present and respective susceptibility of any device connected to this node

$$I_{CINRMS} = \sqrt{I_{OUT}^2 \times D \times (1 - D) + \frac{\Delta I^2}{12} \times D}$$

(11)

As a point of reference if  $\Delta I = 0.4 I_{OUT}$  this places the worst case  $I_{CINRMS}$  at approximately 3 A. This corresponds to a duty cycle of approximately 50%. Other duty cycles can result in a significantly lower RMS current.

A good input capacitor would be a 22-µF X5R ceramic capacitor. Equally important as selecting the proper capacitor is placing and routing that capacitor. It is crucial that the decoupling be placed as close as possible to both the power pin (VIN) and ground (PGND). It is important to recognize that each power stage should have its own local decoupling. One 22-µF capacitor should be placed across each VIN and PGND pair. The proximity of the capacitance to these pins will reduce the radiated fields mentioned above.

# **Output Capacitance**

The goal of the output capacitor bank is to keep the output voltage within regulation limits during steady state and transient conditions.

The total AC RMS current flowing through the capacitor bank can be calculated as:

$$I_{\text{COUTRMS}} = \frac{\Delta I}{\sqrt{12}} \tag{12}$$

For a single type of output capacitor the output ripple voltage wave form can be approximated by the following equation:

$$V_{OUT}(t) = I_{C}(t) \times esr + \frac{1}{C} \int_{0}^{t} I_{C}(\tau) \times d\tau$$

(13)

Where

$$I_{C}(t) = \begin{cases} \frac{\Delta I \times f_{S}}{D} \times t - \frac{\Delta I}{2} & t < \frac{D}{f_{S}} \\ \frac{\Delta I \times f_{S}}{1 - D} \times \left(t - \frac{D}{f_{S}}\right) + \frac{\Delta I}{2} & \text{otherwise} \end{cases}$$

(14)

After substitution and simplification yields:

$$V_{OUT}(t) = \begin{cases} esr \times \left(\frac{\Delta I \times f_S}{D} \times t - \frac{\Delta I}{2}\right) + \frac{1}{C} \times \left(\frac{t \times \Delta I \times \left(f_S \times t - D\right)}{2 \times D} - \frac{\Delta I \times \left(1 - 2 \times D\right)}{12 \times f_S}\right) & t < \frac{D}{f_S} \\ esr \times \left(\frac{\Delta I \times f_S}{1 - D} \times \left(t - \frac{D}{f_S}\right) + \frac{\Delta I}{2}\right) + \frac{1}{C} \times \left(\frac{\Delta I \times \left(f_S \times t - 1\right) \times \left(D - f_S \times t\right)}{2 \times \left(1 - D\right) \times f_S} - \frac{\Delta I \times \left(1 - 2 \times D\right)}{12 \times f_S}\right) & \text{otherwise} \end{cases}$$

$$(15)$$

The term in this equation multiplied by the esr gives the ripple voltage component due to esr and the term multiplied by 1/C gives the ripple voltage component due to the change in charge on the capacitor plates. In the case were the esr component dominates the peak-to-peak output voltage can be approximated as:

$$V_{PPesr} \approx \Delta I \times esr$$

(16)

When the charge term dominates the peak-to-peak voltage ripple becomes:

$$V_{PPQ} \approx \frac{\Delta I}{8 \times C \times f_{S}}$$

(17)

It's tempting to simply add these two results together for the case where the voltage ripple is significantly influenced by both the capacitance and the esr. However, this will yield an overly pessimistic result, in that it does not account for the phase difference between these terms.

Using the ripple voltage equations and the RMS current equation should give a design that safely meets the steady state output requirements. However, additional capacitance is often needed to meet transient requirements and the specific local decoupling requirements of any device that is being powered off of this voltage. This is not just a function of the capacitor bank but also the dynamics of the control loop. See the UCD9240 Compensation Cookbook for additional details (TI Literature Number SLUA497).

### Decoupling

It is necessary that  $V_{GG}$  and BP3 have their own local capacitance as physically close as possible to these pins. The  $V_{GG}$  capacitor should be connected as close as possible to the VGG pin and PGND with a 4.7- $\mu$ F ceramic capacitor. The BP3 capacitor should be connected as close as possible to BP3 pin and AGND with a 1- $\mu$ F ceramic capacitor.

The UCD74106 also supports the ability to operate from input voltages down to 2.2 V. In these cases an additional supply rail must be connected to  $V_{GG}$ . Potential external bias supply generators for low VIN operation: TPS63000, TPS61220.

#### **Current Sense**

An appropriate resistor must be connected to the current sense output pins to convert the IMON current to a voltage. In the case of the UCD92xx digital controllers, these parts have a full scale current monitor range of 0 V to 2 V. This range can be maximized to make full use of the current monitoring resolution inside the controller.

$$\frac{V_{MON(min)}}{I_{OFFSET} + I_{MIN} \times I_{GAIN}} \le R_{MON} \le \frac{V_{MON(max)}}{I_{OFFSET} + I_{MAX} \times I_{GAIN}}$$

(18)

**Table 8. Current Sense Definitions**

| NAME                  | DESCRIPTION                                  |

|-----------------------|----------------------------------------------|

| R <sub>MON</sub>      | Resistor from IMON pin to GND                |

| V <sub>MON(min)</sub> | Minimum voltage for IMON (typically, 0.2 V)  |

| V <sub>MON(max)</sub> | Maximum voltage for IMON (typically, 1.8 V)  |

| I <sub>MIN</sub>      | Minimum load current to sense                |

| I <sub>MAX</sub>      | Maximum load current to sense                |

| I <sub>OFFSET</sub>   | Current sense amplifier zero amp load offset |

| I <sub>GAIN</sub>     | Current sense amplifier gain                 |

The recommended 22.6-k $\Omega$  resistor can be used to keep IMON within range for sensing load currents below -2 A to above 6 A.

In some applications it may be necessary to filter the IMON signal. The UCD74106 IMON pin is a current source output, so a capacitor to ground in parallel with the current-to-voltage conversion resistor is all that is required. As a rule of thumb, placing the corner frequency of the filter at 20% of the switching frequency should be sufficient.

For example, if the switching frequency is 500 kHz or higher, the ripple frequency will be easily rejected with a corner frequency of approximately 100 kHz. With a 100-kHz pole point, the filter time constant is 1.6  $\mu$ s. A fast current transient should be detected within 4.8  $\mu$ s.

$$C_{MON} = \frac{1}{2 \times \pi \times R_{MON} \times 20\% \times f_{S}}$$

(19)

## **Layout Recommendations**

The primary thermal cooling path is from the VIN, GND, and the SW stripes on the bottom of the package. Wide copper traces should connect to these nodes. 1-ounce copper should be the minimum thickness of the top layer; however, 2 ounce is better. Multiple thermal vias should be placed near the GND stripes which connect to a PCB ground plane. There is room to place multiple 10 mil (0.25 mm) diameter vias next to the VIN and GND stripes under the package.

For input bypassing, the 22-µF input ceramic caps should be connected as close as possible to the VIN and GND stripes. If possible, the input caps should be placed directly under the UCD74106 using multiple 10-mil vias to bring the VIN and GND connections to the back side of the board. Minimizing trace inductance in the bypass path is extremely important to reduce the amplitude of ringing on the switching node.

# **REVISION HISTORY**

| Changes from Original (May, 2011) to Revision A                                | Page |

|--------------------------------------------------------------------------------|------|

| Changed Wide Input Voltage Range from 14 V to 18 V                             | 1    |

| Added updated ABSOLUTE MAXIMUM RATINGS information                             | 2    |

| Changed Power input voltage max rating from 16 V to 18 V                       | 3    |

| <ul> <li>Changed Output high level max rating from 4 mA to 500 μA.</li> </ul>  | 5    |

| <ul> <li>Changed Output low level max rating from -4 mA to -500 μA.</li> </ul> | 5    |

| Changed GND to AGND                                                            | 7    |

| Changed 4.4 to 4.32.                                                           | 7    |

| Changed GND to AGND.                                                           | 7    |

| Changed 12 mV/°C to 10 mV/°C.                                                  | 7    |

| Changed LS = ON to LS = OFF.                                                   | 8    |

# PACKAGE OPTION ADDENDUM

6-Feb-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty |                            | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing            |      | Qty            | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| UCD74106RGMR     | ACTIVE | VQFN-HR      | RGM                | 13   | 3000           | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | 74106          | Samples |

| UCD74106RGMT     | ACTIVE | VQFN-HR      | RGM                | 13   | 250            | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | 74106          | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

6-Feb-2020

# PACKAGE MATERIALS INFORMATION

www.ti.com 3-Aug-2017

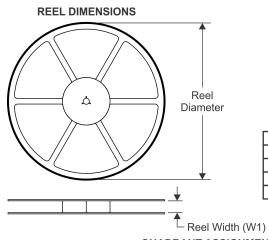

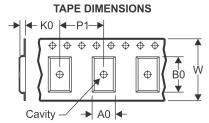

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

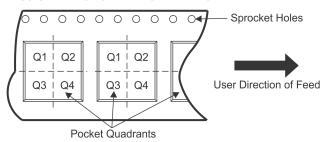

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UCD74106RGMR | VQFN-<br>HR     | RGM                | 13 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| UCD74106RGMT | VQFN-<br>HR     | RGM                | 13 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 3-Aug-2017

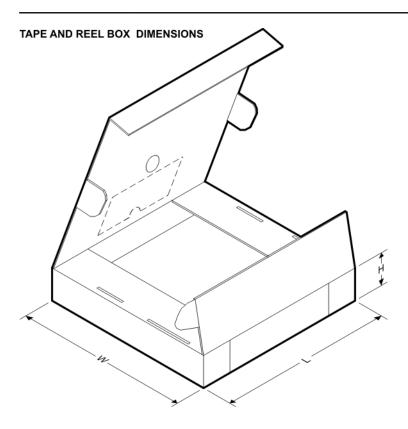

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCD74106RGMR | VQFN-HR      | RGM             | 13   | 3000 | 367.0       | 367.0      | 35.0        |

| UCD74106RGMT | VQFN-HR      | RGM             | 13   | 250  | 210.0       | 185.0      | 35.0        |

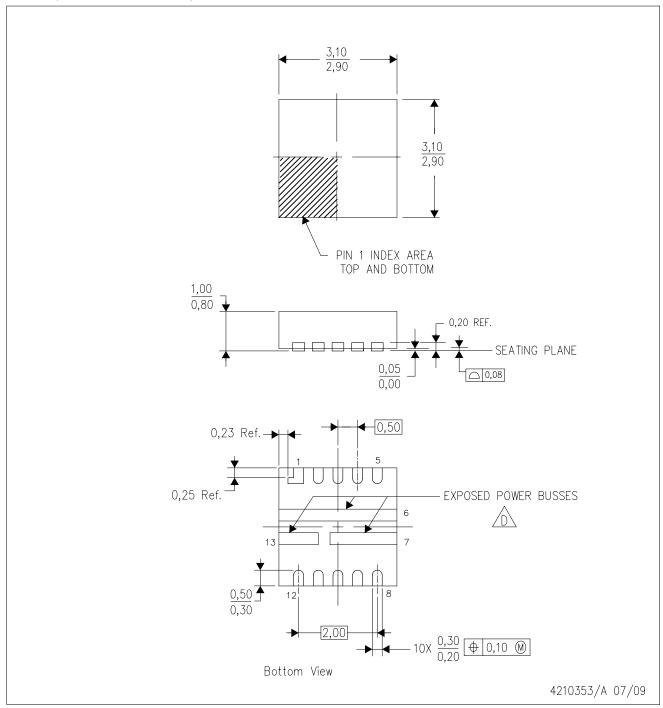

RGM (S-PVQFN-N13)

PLASTIC QUAD FLATPACK NO-LEAD

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- Ç. Quad Flatpack, No-leads (QFN) package configuration.

- 🛆 See the Product Data Sheet for details regarding the exposed power buss dimensions.

- E. RoHS exempt flip chip application. Internal solder joints may contain Pb.

- F. Exposed terminals are Pb-free

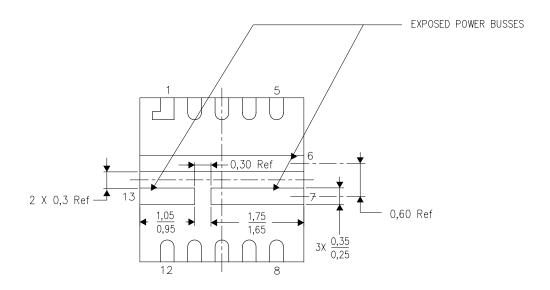

## THERMAL PAD MECHANICAL DATA

RGM (S-PVQFN-N13)

### THERMAL INFORMATION

This package incorporates an exposed and partitioned thermal pad that functions electrically as distinct power busses. The power busses must be soldered directly to the printed circuit board (PCB). After soldering, the PCB electrically connects the power busses. In addition, the PCB can be used as a heatsink that can be enhanced with the use of thermal vias.

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed power buss dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Power Buss Dimensions

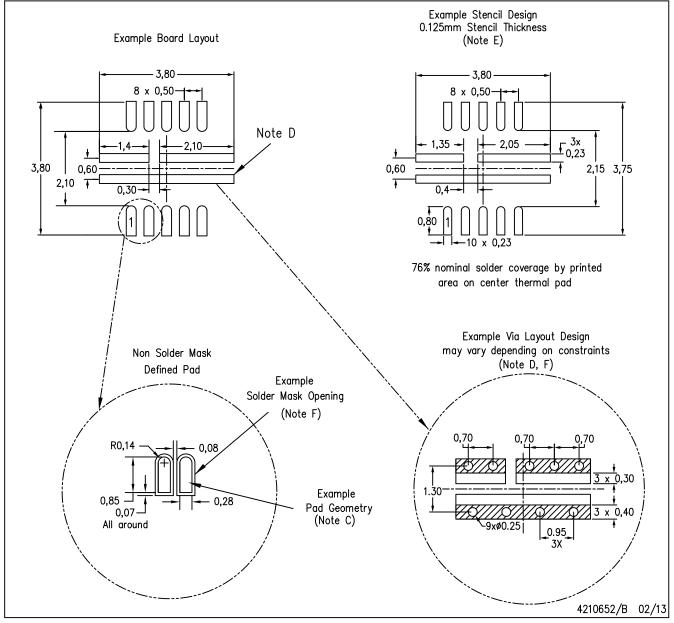

# RGM (R-PVQFN-N13)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated