# RENESAS

# DATASHEET

#### ISL28005

Micropower, Rail-to-Rail Input Current Sense Amplifier with Voltage Output

FN6973 Rev 5.00 October 24, 2013

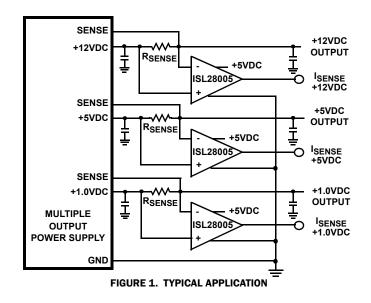

The ISL28005 is a micropower, uni-directional high-side and low-side current sense amplifier featuring a proprietary rail-torail input current sensing amplifier. The ISL28005 is ideal for high-side current sense applications where the sense voltage is usually much higher than the amplifier supply voltage. The device can be used to sense voltages as high as 28V when operating from a supply voltage as low as 2.7V. The micropower ISL28005 consumes only 50µA of supply current when operating from a 2.7V to 28V supply.

The ISL28005 features a common-mode input voltage range from OV to 28V. The proprietary architecture extends the input voltage sensing range down to OV, making it an excellent choice for low-side ground sensing applications. The benefit of this architecture is that a high degree of total output accuracy is maintained over the entire OV to 28V common mode input voltage range.

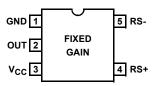

The ISL28005 is available in fixed (100V/V, 50V/V and 20V/V) gains in the space saving 5 Ld SOT-23 package. The parts operate over the extended temperature range from -40 °C to +125 °C.

#### **Features**

| Low Power Consumption           | 50µА,Тур    |

|---------------------------------|-------------|

| Supply Range                    | 2.7V to 28V |

| Wide Common Mode Input          | 0V to 28V   |

| Fixed Gain Versions             |             |

| - ISL28005-100                  | 100V/V      |

| - ISL28005-50                   | 50V/V       |

| - ISL28005-20                   | 20V/V       |

| Operating Temperature Range40°C | to +125°C   |

| • Package 5                     | Ld SOT-23   |

|                                 |             |

#### **Applications**

- Power Management/Monitors

- Power Distribution and Safety

- DC/DC, AC/DC Converters

- Battery Management/Charging

- Automotive Power Distribution

### **Related Literature**

- See AN1531 for "ISL28005 Evaluation Board User's Guide"

- See <u>AN1567</u> for "ISL28005, ISL28006 Unidirectional Current Sense Amplifiers"

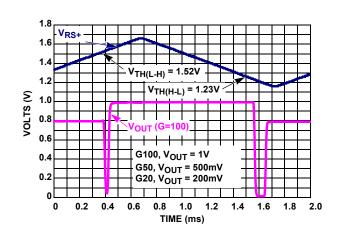

FIGURE 2. HIGH-SIDE AND LOW-SIDE THRESHOLD VOLTAGE

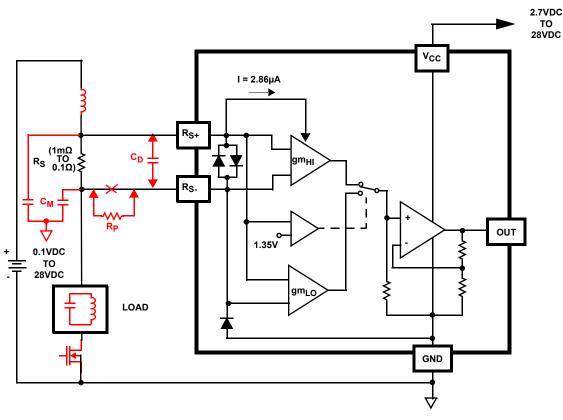

### **Block Diagram**

### **Pin Configuration**

### **Pin Descriptions**

| ISL28005<br>(5 ld S0T-23) | PIN<br>NAME     | DESCRIPTION                          |

|---------------------------|-----------------|--------------------------------------|

| 1                         | GND             | Power Ground                         |

| 2                         | OUT             | Amplifier Output                     |

| 3                         | V <sub>CC</sub> | Positive Power Supply                |

| 4                         | RS+             | Sense Voltage Non-inverting Input    |

| 5                         | RS-             | Sense Voltage Inverting Input        |

| RS-<br>TY<br>RS+          | > [             | CAPACITIVELY<br>COUPLED<br>ESD CLAMP |

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | GAIN                | PART MARKING           | PACKAGE<br>Tape & Reel<br>(Pb-Free) | PKG.<br>DWG. # |  |

|--------------------------------|---------------------|------------------------|-------------------------------------|----------------|--|

| ISL28005FH100Z-T7              | 100V/V              | BDEA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| ISL28005FH100Z-T7A             | 100V/V              | BDEA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| ISL28005FH50Z-T7               | 50V/V               | BDDA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| ISL28005FH50Z-T7A              | 50V/V               | BDDA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| SL28005FH20Z-T7                | 20V/V               | BDCA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| SL28005FH20Z-T7A               | 20V/V               | BDCA (Note 4)          | 5 Ld SOT-23                         | P5.064A        |  |

| SL28005FH-100EVAL1Z            | 100V/V Evaluation B | Board                  |                                     |                |  |

| SL28005FH-50EVAL1Z             | 50V/V Evaluation Bo | 50V/V Evaluation Board |                                     |                |  |

| SL28005FH-20EVAL1Z             | 20V/V Evaluation Bo | pard                   |                                     |                |  |

NOTES:

1. Please refer to  $\underline{\text{TB347}}$  for details on reel specifications.

These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL28005. For more information on MSL please see techbrief TB363.

4. The part marking is located on the bottom of the part.

#### **Absolute Maximum Ratings**

| Max Supply Voltage                                                            | 28V               |

|-------------------------------------------------------------------------------|-------------------|

| Max Differential Input Current                                                | 20mA              |

| Max Differential Input Voltage                                                | ±0.5V             |

| Max Input Voltage (RS+, RS-)                                                  | . GND-0.5V to 30V |

| Max Input Current for Input Voltage <gnd -0.5v<="" td=""><td>±20mA</td></gnd> | ±20mA             |

| Output Short-Circuit Duration                                                 | Indefinite        |

| ESD Rating                                                                    |                   |

| Human Body Model                                                              | 4kV               |

| Machine Model                                                                 |                   |

| Charged Device Model                                                          | <b>1</b> .5kV     |

#### **Thermal Information**

| Thermal Resistance (Typical)                      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------------------------------------------------|------------------------|------------------------|

| 5 Ld SOT-23 (Notes 5, 6)                          | 190                    | 90                     |

| Maximum Storage Temperature Range                 | 6                      | 5°C to +150°C          |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                        | +150°C                 |

| Pb-Free Reflow Profile                            |                        | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe          | eflow.asp              |                        |

#### **Recommended Operating Conditions**

Ambient Temperature Range (T<sub>A</sub>) .....-40°C to +125°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 6. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

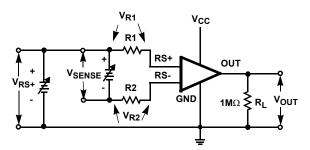

**Electrical Specification**  $V_{CC} = 12V$ ,  $V_{RS+} = 0V$  to 28V,  $V_{SENSE} = 0V$ ,  $R_{LOAD} = 1M\Omega$ ,  $T_A = +25^{\circ}C$  unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization.

| PARAMETER                            | DESCRIPTION                              | CONDITIONS                                                             | MIN<br>(Note 7)     | ТҮР   | MAX<br>(Note 7)   | UNIT |

|--------------------------------------|------------------------------------------|------------------------------------------------------------------------|---------------------|-------|-------------------|------|

| V <sub>OS</sub>                      | Input Offset Voltage<br>(Notes 8, 9)     | $V_{CC} = V_{RS}^{+} = 12V,$<br>$V_{S}^{-} = 20mV \text{ to } = 100mV$ | -500<br><b>-500</b> | 60    | 500<br><b>500</b> | μV   |

|                                      |                                          | $V_{CC} = 12V, V_{RS} + = 0.2V, V_{S} = 20mV, V_{S} = 100mV$           | -3<br>- <b>3.3</b>  | -1.2  | 3<br><b>3.3</b>   | mV   |

| I <sub>RS</sub> +, I <sub>RS</sub> - | Leakage Current                          | V <sub>CC</sub> = 0V, V <sub>RS+</sub> = 28V                           |                     | 0.041 | 1.2<br><b>1.5</b> | μA   |

| I <sub>RS</sub> +                    | Gain = 100 + Input Bias Current          | V <sub>RS</sub> + = 2V, V <sub>SENSE</sub> = 5mV                       |                     | 4.7   | 6<br>7            | μΑ   |

|                                      |                                          | V <sub>RS</sub> + = 0V, v <sub>SENSE</sub> = 5mV                       | -500<br><b>-600</b> | -425  |                   | nA   |

|                                      | Gain = 50, Gain = 20 +Input Bias Current | $V_{RS}$ + = 2V, $V_{SENSE}$ = 5mV                                     |                     | 4.7   | 6<br><b>8</b>     | μA   |

|                                      |                                          | V <sub>RS</sub> + = 0V, v <sub>SENSE</sub> = 5mV                       | -700<br><b>-840</b> | -432  |                   | nA   |

| I <sub>RS</sub> -                    | Input Bias Current                       | V <sub>RS</sub> + = 2V, v <sub>SENSE</sub> = 5mV                       |                     | 5     | 50<br><b>75</b>   | nA   |

|                                      |                                          | V <sub>RS</sub> + = 0V, v <sub>SENSE</sub> = 5mV                       | -125<br><b>-130</b> | -45   |                   | nA   |

| CMRR                                 | Common Mode Rejection Ratio              | $V_{RS}$ + = 2V to 28V                                                 | 105                 | 115   |                   | dB   |

| PSRR                                 | Power Supply Rejection Ratio             | $V_{CC}$ = 2.7V to 28V, $V_{RS}$ + = 2V                                | 90                  | 105   |                   | dB   |

| VF <sub>S</sub>                      | Full-scale Sense Voltage                 | V <sub>CC</sub> = 28V, V <sub>RS</sub> + = 0.2V, 12V                   | 200                 |       |                   | mV   |

| G                                    | Gain<br>(Note 8)                         | ISL28005-100                                                           |                     | 100   |                   | V/V  |

|                                      |                                          | ISL28005-50                                                            |                     | 50    |                   | V/V  |

|                                      |                                          | ISL28005-20                                                            |                     | 20    |                   | V/V  |

**Electrical Specification**  $V_{CC} = 12V$ ,  $V_{RS+} = 0V$  to 28V,  $V_{SENSE} = 0V$ ,  $R_{LOAD} = 1M\Omega$ ,  $T_A = +25^{\circ}C$  unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization. (Continued)

| PARAMETER          | DESCRIPTION                                                      | CONDITIONS                                                                             | MIN<br>(Note 7)     | ТҮР   | MAX<br>(Note 7)   | UNIT |

|--------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|-------|-------------------|------|

| G <sub>A</sub>     | Gain = 100 Gain Accuracy<br>(Note 10)                            | $V_{CC} = V_{RS}$ + = 12V, $V_{SENSE}$ = 20mV to 100mV                                 | -2<br>-3            |       | 2<br>3            | %    |

|                    |                                                                  | $V_{CC} = 12V, V_{RS} + = 0.1V,$<br>$V_{SENSE} = 20mV$ to 100mV                        |                     | -0.25 |                   | %    |

|                    | Gain = 50, Gain = 20 Gain Accuracy<br>(Note 10)                  | $V_{CC} = V_{RS}$ + = 12V, $V_{SENSE}$ = 20mV to<br>100mV                              | -2<br>-3            |       | 2<br>3            | %    |

|                    |                                                                  | V <sub>CC</sub> = 12V, V <sub>RS</sub> + = 0.1V,<br>V <sub>SENSE</sub> = 20mV to 100mV | -3<br>-4            | -0.31 | 3<br>4            | %    |

| V <sub>OA</sub>    | Gain = 100 Total Output Accuracy<br>(Note 11)                    | V <sub>CC</sub> = V <sub>RS</sub> + = 12V, V <sub>SENSE</sub> = 100mV                  | -2.5<br><b>-2.7</b> |       | 2.5<br><b>2.7</b> | %    |

|                    |                                                                  | $V_{CC} = 12V, V_{RS}^{+} = 0.1V, V_{SENSE} = 100mV$                                   |                     | -1.25 |                   | %    |

|                    | Gain = 50, Gain = 20 Total Output<br>Accuracy (Note 11)          | V <sub>CC</sub> = V <sub>RS</sub> + = 12V, V <sub>SENSE</sub> = 100mV                  | -2.5<br><b>-2.7</b> |       | 2.5<br><b>2.7</b> | %    |

|                    |                                                                  | $V_{CC} = 12V, V_{RS} + = 0.1V,$<br>$V_{SENSE} = 100mV$                                | -6<br>-7            | -1.41 | 6<br>7            | %    |

| v <sub>oH</sub>    | Output Voltage Swing, High<br>V <sub>CC</sub> - V <sub>OUT</sub> | $I_0 = -500 \mu A, V_{CC} = 2.7V$<br>$V_{SENSE} = 100 mV$<br>$V_{RS}^{+} = 2V$         |                     | 39    | 50                | mV   |

| V <sub>OL</sub>    | Output Voltage Swing, Low<br>V <sub>OUT</sub>                    | $I_0 = 500 \mu A$ , $V_{CC} = 2.7V$<br>$V_{SENSE} = 0V$ , $V_{RS} + = 2V$              |                     | 30    | 50                | mV   |

| R <sub>OUT</sub>   | Output Resistance                                                | $V_{CC} = V_{RS}^+ = 12V, V_{SENSE} = 100mV$<br>$I_{OUT} = 10\mu A \text{ to } 1mA$    |                     | 6.5   |                   | Ω    |

| I <sub>SC+</sub>   | Short Circuit Sourcing Current                                   | $V_{CC} = V_{RS}^{+} = 5V, R_{L}^{-} = 10\Omega$                                       |                     | 4.8   |                   | mA   |

| I <sub>SC-</sub>   | Short Circuit Sinking Current                                    | $V_{CC} = V_{RS} + = 5V, R_L = 10\Omega$                                               |                     | 8.7   |                   | mA   |

| I <sub>CC</sub>    | Gain = 100<br>Supply Current                                     | V <sub>RS</sub> + > 2V, V <sub>SENSE</sub> = 5mV                                       |                     | 50    | 59<br><b>62</b>   | μA   |

|                    | Gain = 50, 20<br>Supply Current                                  | V <sub>RS</sub> + > 2V, V <sub>SENSE</sub> = 5mV                                       |                     | 50    | 62<br><b>63</b>   | μA   |

| V <sub>CC</sub>    | Supply Voltage                                                   | Guaranteed by PSRR                                                                     | 2.7                 |       | 28                | v    |

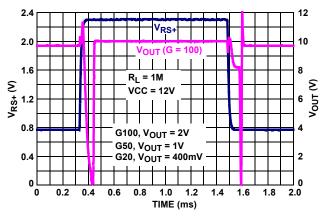

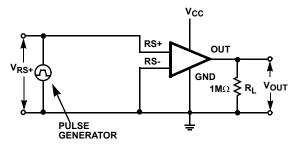

| SR                 | Gain = 100 Slew Rate                                             | Pulse on RS+ pin,<br>V <sub>OUT</sub> = 8V <sub>P-P</sub><br>(see Figure 25)           | 0.58                | 0.76  |                   | V/µs |

|                    | Gain = 50 Slew Rate                                              | Pulse on RS+ pin,<br>V <sub>OUT</sub> = 8V <sub>P-P</sub><br>(see Figure 25)           | 0.58                | 0.67  |                   | V/µs |

|                    | Gain = 20 Slew Rate                                              | Pulse on RS+ pin,<br>V <sub>OUT</sub> = 3.5V <sub>P-P</sub><br>(see Figure 25)         | 0.50                | 0.67  |                   | V/µs |

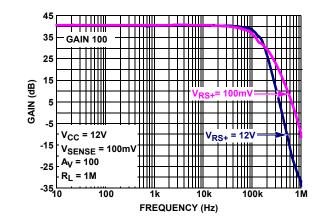

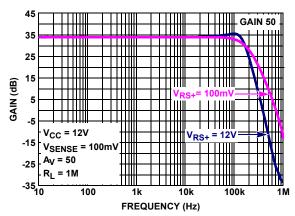

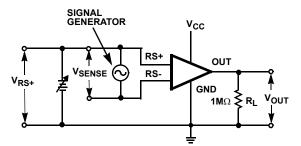

| BW <sub>-3dB</sub> | Gain = 100<br>-3dB Bandwidth                                     | V <sub>RS</sub> + = 12V, 0.1V, V <sub>SENSE</sub> = 100mV                              |                     | 110   |                   | kHz  |

|                    | Gain = 50<br>-3dB Bandwidth                                      | V <sub>RS</sub> + = 12V, 0.1V, V <sub>SENSE</sub> = 100mV                              |                     | 160   |                   | kHz  |

|                    | Gain = 20<br>-3dB Bandwidth                                      | V <sub>RS</sub> + = 12V, 0.1V, V <sub>SENSE</sub> = 100mV                              |                     | 180   |                   | kHz  |

**Electrical Specification**  $V_{CC} = 12V$ ,  $V_{RS+} = 0V$  to 28V,  $V_{SENSE} = 0V$ ,  $R_{LOAD} = 1M\Omega$ ,  $T_A = +25^{\circ}C$  unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization. (Continued)

| PARAMETER               | DESCRIPTION                               | CONDITIONS                                                                          | MIN<br>(Note 7) | ТҮР | MAX<br>(Note 7) | UNIT |

|-------------------------|-------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-----|-----------------|------|

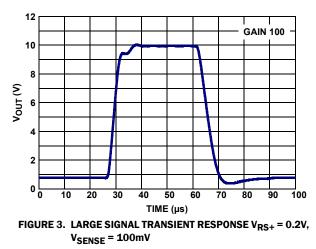

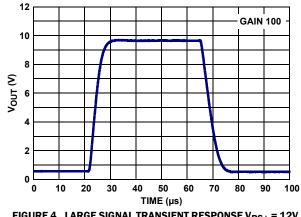

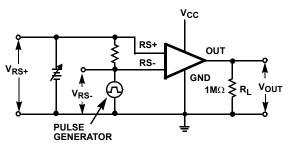

| t <sub>s</sub>          | Output Settling Time to 1% of Final Value | $V_{CC} = V_{RS}$ + = 12V, $V_{OUT}$ = 10V step,<br>$V_{SENSE}$ >7mV                |                 | 15  |                 | μs   |

|                         |                                           | $V_{CC} = V_{RS}$ + = 0.2V, $V_{OUT}$ = 10V step,<br>$V_{SENSE}$ >7mV               |                 | 20  |                 | μs   |

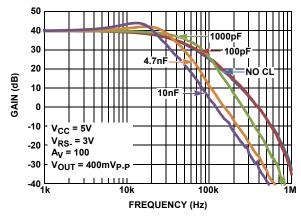

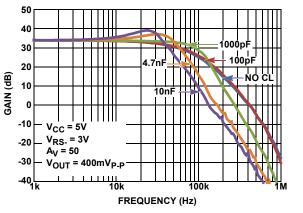

|                         | Capacitive-Load Stability                 | No sustained oscillations                                                           |                 | 300 |                 | pF   |

| t <sub>s Power-up</sub> | Power-Up Time to 1% of Final Value        | $V_{CC} = V_{RS}^{+} = 12V, V_{SENSE} = 100mV$                                      |                 | 15  |                 | μs   |

|                         |                                           | V <sub>CC</sub> = 12V, V <sub>RS</sub> + = 0.2V<br>V <sub>SENSE</sub> = 100mV       |                 | 50  |                 | μs   |

|                         | Saturation Recovery Time                  | V <sub>CC</sub> = V <sub>RS</sub> + = 12V, V <sub>SENSE</sub> = 100mV,<br>overdrive |                 | 10  |                 | μs   |

NOTES:

- 7. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 8. DEFINITION OF TERMS:

- V<sub>SENSE</sub>A = V<sub>SENSE</sub> @100mV

- V<sub>SENSE</sub>B = V<sub>SENSE</sub> @20mV

- V<sub>OUT</sub>A = V<sub>OUT</sub>@V<sub>SENSE</sub>A = 100mV

- V<sub>OUT</sub>B = V<sub>OUT</sub>@V<sub>SENSE</sub>B = 20mV

• G = GAIN =

$$\begin{pmatrix} V_{OUT}A - V_{OUT}B \\ V_{SENSE}A - V_{SENSE}B \end{pmatrix}$$

9. V<sub>OS</sub> is extrapolated from the gain measurement. V<sub>OS</sub> = V<sub>SENSE</sub>A  $-\frac{V_{OUT}A}{G}$

10. % Gain Accuracy =

$$G_A = \left(\frac{G_{MEASURED} - G_{EXPECTED}}{G_{EXPECTED}}\right) \times 100$$

11. Output Accuracy %  $V_{OA} = \left(\frac{VOUT_{MEASURED} - VOUT_{EXPECTED}}{-VOUT_{EXPECTED}}\right) \times 100$  where  $V_{OUT} = V_{SENSE} X$  GAIN and  $V_{SENSE} = 100 \text{mV}$

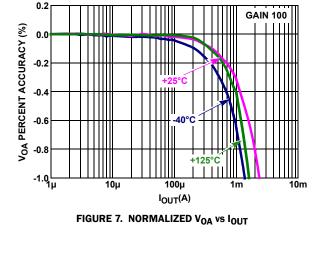

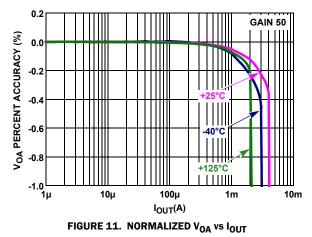

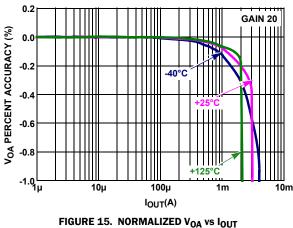

### Typical Performance Curves $v_{CC} = 12V$ , $R_L = 1M$ , unless otherwise specified.

### Typical Performance Curves $v_{CC} = 12V$ , $R_L = 1M$ , unless otherwise specified. (Continued)

FIGURE 6. V<sub>OUT</sub> vs V<sub>RS+</sub>, V<sub>SENSE</sub> = 20mV TRANSIENT RESPONSE

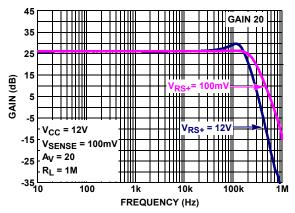

FIGURE 8. GAIN vs FREQUENCY V<sub>RS+</sub>= 100mV/12V, V<sub>SENSE</sub> = 100mV, V<sub>OUT</sub> = 250mV<sub>P-P</sub>

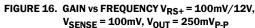

FIGURE 9. CAPACITIVE LOAD DRIVE GAIN vs FREQUENCY

### Typical Performance Curves $v_{CC} = 12V$ , $R_L = 1M$ , unless otherwise specified. (Continued)

FIGURE 12. GAIN vs FREQUENCY  $V_{RS+}$  = 100mV/12V, V<sub>SENSE</sub> = 100mV, V<sub>OUT</sub> = 250mV<sub>P-P</sub>

FIGURE 13. CAPACITIVE LOAD DRIVE GAIN vs FREQUENCY

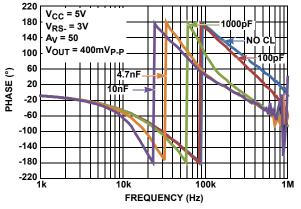

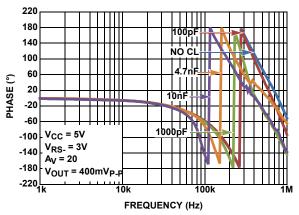

FIGURE 14. CAPACITIVE LOAD DRIVE PHASE vs FREQUENCY

## Typical Performance Curves $v_{CC} = 12V$ , $R_L = 1M$ , unless otherwise specified. (Continued)

FIGURE 17. CAPACITIVE LOAD DRIVE GAIN vs FREQUENCY

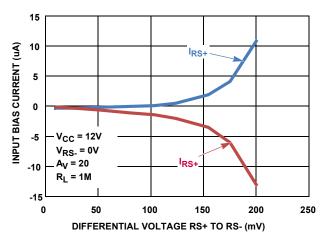

FIGURE 19. LOW-SIDE CURRENT SENSING INPUT BIAS CURRENTS

### **Test Circuits and Waveforms**

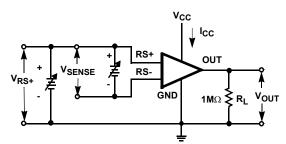

FIGURE 21. ICC. VOS, VOA, CMRR, PSRR, GAIN ACCURACY

FIGURE 18. CAPACITIVE LOAD DRIVE PHASE vs FREQUENCY

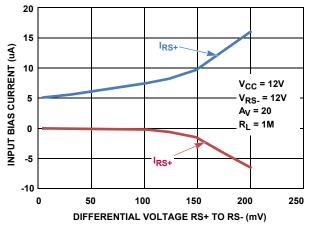

FIGURE 20. HIGH-SIDE CURRENT SENSING INPUT BIAS CURRENTS

FIGURE 22. INPUT BIAS CURRENT, LEAKAGE CURRENT

#### Test Circuits and Waveforms (Continued)

FIGURE 23. SLEW RATE, t<sub>s</sub>, SATURATION RECOVERY TIME

FIGURE 24. GAIN vs FREQUENCY

FIGURE 25. SLEW RATE

### **Applications Information**

#### **Functional Description**

The ISL28005-20, ISL28005-50 and ISL28005-100 are single supply, uni-directional current sense amplifiers with fixed gains of 20V/V, 50V/V and 100V/V respectively.

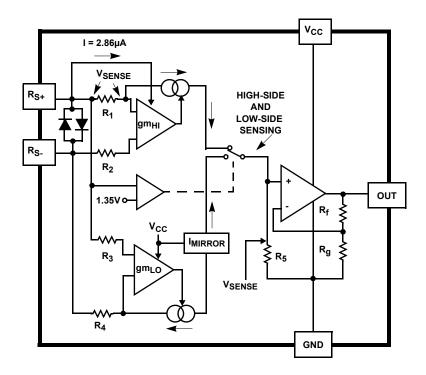

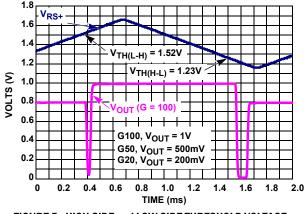

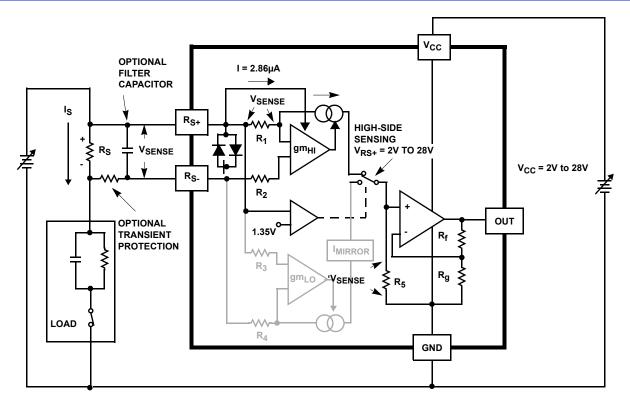

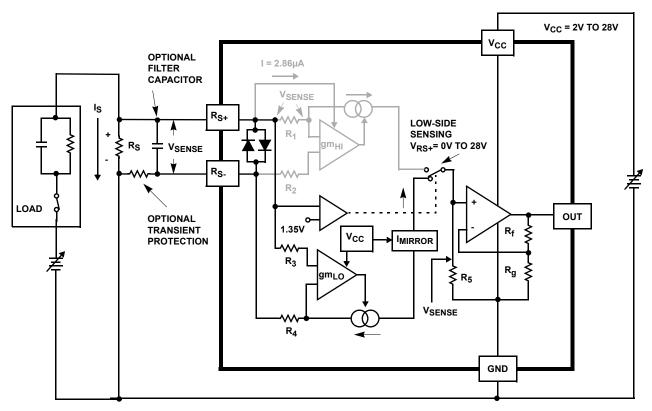

The ISL28005 is a 2-stage amplifier. Figure 26 shows the active circuitry for high-side current sense applications where the sense voltage is between 1.35V to 28V. Figure 27 shows the active circuitry for ground sense applications where the sense voltage is between 0V to 1.35V.

The first stage is a bi-level trans-conductance amp and level translator. The gm stage converts the low voltage drop (V<sub>SENSE</sub>) sensed across an external milli-ohm sense resistor, to a current (@ gm = 21.3µA/V). The trans-conductance amplifier forces a current through R<sub>1</sub> resulting to a voltage drop across R<sub>1</sub> that is equal to the sense voltage (V<sub>SENSE</sub>). The current through R<sub>1</sub> is mirrored across R<sub>5</sub> creating a ground-referenced voltage at the input of the second amplifier equal to V<sub>SENSE</sub>.

The second stage is responsible for the overall gain and frequency response performance of the device. The fixed gains (20, 50, 100) are set with internal resistors R<sub>f</sub> and R<sub>g</sub>. The only external component needed is a current sense resistor (typically 0.001 $\Omega$  to 0.01 $\Omega$ , 1W to 2W).

The transfer function is given in Equation 1.

$$V_{OUT} = GAIN \times (I_SR_S + V_{OS})$$

Where  $\mathsf{I}_S\mathsf{R}_S$  is the product of the load current and the sense resistor and is equal to  $\mathsf{V}_{SENSE}.$

When the sensed input voltage is >1.35V, the gm<sub>HI</sub> amplifier path is selected and the input gm stage derives its ~2.86 $\mu$ A

supply current from the input source through the RS+ terminal. When the sense voltage at R<sub>S</sub>+ drops below the 1.35V threshold, the gm<sub>LO</sub> amplifier is enabled for Low Side current sensing. The gm<sub>LO</sub> input bias current reverses, flowing out of the RS- pin. Since the gm<sub>LO</sub> amplifier is sensing voltage around ground, it cannot source current to R5. A current mirror referenced off Vcc supplies the current to the second stage for generating a ground referenced output voltage. See Figures 19 and 20 for typical input bias currents for High and Low side current sensing.

(EQ. 1)

FIGURE 27. LOW-SIDE CURRENT DETECTION

#### **Hysteretic Comparator**

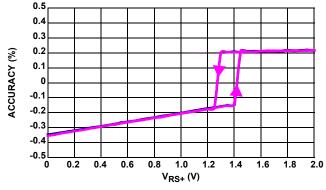

The input trans-conductance amps are under control of a hysteretic comparator operating from the incoming source voltage on the RS+ pin (see Figure 28). The comparator monitors the voltage on RS+ and switches the sense amplifier from the low-side gm amp to the high-side gm amplifier whenever the input voltage at R<sub>S</sub>+ increases above the 1.35V threshold. Conversely, a decreasing voltage on the RS+ pin, causes the hysteric comparator to switch from the high-side gm amp to the low-side gm amp as the voltage decreases below 1.35V. It is that low-side sense gm amplifier that gives the ISL28005 the proprietary ability to sense current all the way to OV. Negative voltages on the R<sub>S</sub>+ or R<sub>S</sub>- are beyond the sensing voltage range of this amplifier.

FIGURE 28. GAIN ACCURACY vs  $V_{RS+} = 0V TO 2V$

#### **Typical Application Circuit**

Figure 30 shows the basic application circuit and optional protection components for switched-load applications. For applications where the load and the power source is permanently connected, only an external sense resistor is needed. For applications where fast transients are caused by hot plugging the source or load, external protection components may be needed. The external current limiting resistor ( $R_P$ ) in Figure 30 may be required to limit the peak current through the internal ESD diodes to < 20mA. This condition can occur in applications that experience high levels of in-rush current causing high peak voltages that can damage the internal ESD diodes. An  $R_P$  resistor

value of 100 $\Omega$  will provide protection for a 2V transient with the maximum of 20mA flowing through the input while adding only an additional 13 $\mu$ V (worse case over-temperature) of V<sub>OS</sub>. Refer to the following formula:

$((R_P \times I_{RS-}) = (100\Omega \times 130nA) = 13\mu V)$

Switching applications can generate voltage spikes that can overdrive the amplifier input and drive the output of the amplifier into the rails, resulting in a long overload recovery time. Capacitors  $C_M$  and  $C_D$  filter the common mode and differential voltage spikes.

#### **Error Sources**

There are 3 dominant error sources: gain error, input offset voltage error and Kelvin voltage error (see Figure 29). The gain error is dominated by the internal resistance matching tolerances. The remaining errors appear as sense voltage errors at the input to the amplifier. They are  $V_{OS}$  of the amplifier and Kelvin voltage errors. If the transient protection resistor is added, an additional  $V_{OS}$  error can result from the IxR voltage due to input bias current. The limiting resistor should only be added to the R<sub>S</sub>- input, due to the high-side gm amplifier (gm<sub>HI</sub>) sinking several micro amps of current through the RS+ pin.

#### **Layout Guidelines**

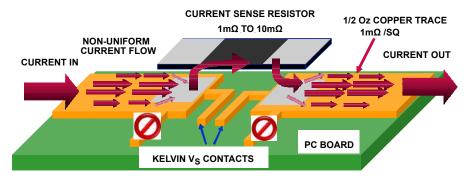

#### **Kelvin Connected Sense Resistor**

The source of Kelvin voltage errors is illustrated in Figure 29. The resistance of 1/2 oz. copper is ~1m $\Omega$  per square with a TC of ~3900ppm/°C (0.39%/°C). When you compare this unwanted parasitic resistance with the total of 1m $\Omega$  to 10m $\Omega$  resistance of the sense resistor, it is easy to see why the sense connection must be chosen very carefully. For example, consider a maximum current of 20A through a 0.005 $\Omega$  sense resistor, generating a V<sub>SENSE</sub> = 0.1 and a full scale output voltage of 10V (G = 100). Two side contacts of only 0.25 square per contact puts the V<sub>SENSE</sub> input about 0.5 x 1m $\Omega$  away from the resistor end capacitor. If only 10A the 20A total current flows through the kelvin path to the resistor, you get an error voltage of 10mV (10A x 0.5sq x 0.001 $\Omega$ /sq. = 10mV) added to the 100mV sense voltage for a sense voltage error of 10% (0.110V - 0.1)/0.1V) x 100.

FIGURE 29. PC BOARD CURRENT SENSE KELVIN CONNECTION

FIGURE 30. TYPICAL APPLICATION CIRCUIT

#### **Overall Accuracy (V<sub>OA</sub> %)**

$V_{OA}$  is defined as the total output accuracy Referred-to-Output (RTO). The output accuracy contains all offset and gain errors, at a single output voltage. Equation 2 is used to calculate the % total output accuracy.

$$V_{OA} = 100 \times \left( \frac{V_{OUT} \text{actual} - V_{OUT} \text{expected}}{V_{OUT} \text{expected}} \right)$$

(EQ. 2)

where

V<sub>OUT</sub> Actual = V<sub>SENSE</sub> x GAIN

Example: Gain = 100, For 100mV V<sub>SENSE</sub> input we measure 10.1V. The overall accuracy ( $V_{OA}$ ) is 1% as shown in Equation 3.

$$V_{OA} = 100 \times \left(\frac{10.1 - 10}{10}\right) = 1 \text{ percent}$$

(EQ. 3)

#### **Power Dissipation**

It is possible to exceed the +150 °C maximum junction temperatures under certain load and power supply conditions. It is therefore important to calculate the maximum junction temperature ( $T_{JMAX}$ ) for all applications to determine if power supply voltages, load conditions, or package type need to be modified to remain in the safe operating area. These parameters are related using Equation 4:

$$T_{JMAX} = T_{MAX} + \theta_{JA} x PD_{MAXTOTAL}$$

(EQ. 4)

where:

- +  $P_{DMAXTOTAL}$  is the sum of the maximum power dissipation of each amplifier in the package ( $PD_{MAX}$ )

- PD<sub>MAX</sub> for each amplifier can be calculated using Equation 5:

$$PD_{MAX} = V_{S} \times I_{qMAX} + (V_{S} - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_{L}}$$

(EQ. 5)

where:

- T<sub>MAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of 1 amplifier

- V<sub>CC</sub> = Total supply voltage

- I<sub>aMAX</sub> = Maximum quiescent supply current of 1 amplifier

- V<sub>OUTMAX</sub> = Maximum output voltage swing of the application

- R<sub>L</sub> = Load resistance

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE              | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 24, 2013  | FN6973.5 | Added eight new Typical Performance Curves         1. Av = 100 Capacitive Load Drive Gain vs Freq         2. Av = 100 Capacitive Load Drive Phase vs Freq         3. Av = 50 Capacitive Load Drive Gain vs Freq         4. Av = 50 Capacitive Load Drive Phase vs Freq         5. Av = 20 Capacitive Load Drive Phase vs Freq         6. Av = 20 Capacitive Load Drive Phase vs Freq         7. High Side Operation Input Bias Currents         8. Low Side Operation Input Bias Currents         Under Electrical Specifications Table:         Changed parameter from Is to Icc to clarify supply current.                                                                                                                                                                                                                                                                                                     |

| April 11, 2011    | FN6973.4 | Corrected location of the load in Figure 27. Moved Load from the ground side of the input sense circuit to the high side of the voltage source.<br>Updated note in Min Max column of spec table from "Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested." to "Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design."                                                                                                                                                                                                                                                                                                                                                                                                     |

| September 2, 2010 | FN6973.3 | Added -T7A tape and reel package options to Ordering Information Table for all packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| May 12, 2010      | FN6973.2 | Added Note 4 to Part Marking Column in "Ordering Information" on page 3.<br>Corrected hyperlinks in Notes 1 and 3 in "Ordering Information" on page 3.<br>Corrected ISL28005 hyperlink in "About Intersil" on page 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| April 12, 2010    |          | Added Eval boards to ordering info.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| April 7, 2010     |          | Added "Related Literature" on page 1<br>Updated Package Drawing Number in the "Ordering Information" on page 3 from MDP0038 to P50.64A.<br>Revised package outline drawing from MDP0038 to P5.064A on page 16. MDP0038 package contained 2 packages for both<br>the 5 and 6 Ld SOT-23. MDP0038 was obsoleted and the packages were separated and made into 2 separate package<br>outline drawings; P5.064A and P6.064A. Changes to the 5 Ld SOT-23 were to move dimensions from table onto drawing,<br>add land pattern and add JEDEC reference number.                                                                                                                                                                                                                                                                                                                                                          |

| February 3, 2010  | FN6973.1 | <ul> <li>-Page1:<br/>Edited last sentence of paragraph 2.<br/>Moved order of GAIN listings from 20, 50, 100 to 100, 50, 20 in the 3rd paragraph.<br/>Under Featuresremoved "Low Input Offset Voltage 250µV,max"<br/>Under Features moved order of parts listing from 20, 50, 100 (from top to bottom) to 100, 50, 20.</li> <li>-Page 3:<br/>Removed coming soon on ISL28005FH50Z and ISL28005FH20Z and changes the order or listing them to 100, 50, 20.</li> <li>-Page 5:<br/>VOA test. Under conditions columndeleted "20mV to". It now reads Vsense = 100mV<br/>SR test. Under conditions columndeleted what was there. It now reads Pulse on RS+pin, See Figure 25</li> <li>-Page 6:<br/>ts test. Removed Gain = 100 and Gain = 100V/V in both description and conditions columns respectively.</li> <li>-Page 9<br/>Added Figure 25 and adjusted figure numbers to account for the added figure.</li> </ul> |

| December 14, 2022 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| December 14, 2009 | FN6973.0 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at <u>www.intersil.com</u>.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <u>www.intersil.com</u>. You may report errors or suggestions for improving this datasheet by visiting <u>www.intersil.com/en/support/ask-an-expert.html</u>. Reliability reports are also available from our website at <u>http://www.intersil.com/en/support/qualandreliability.html#reliability</u>

© Copyright Intersil Americas LLC 2009-2013. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6973 Rev 5.00 October 24, 2013

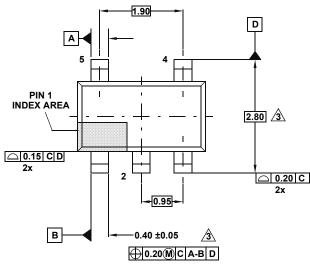

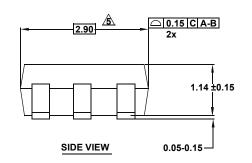

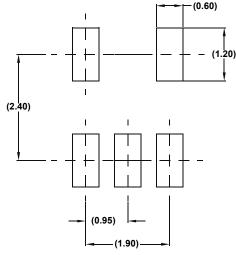

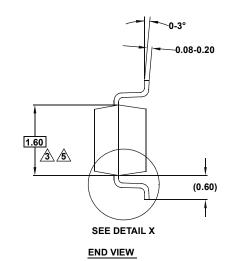

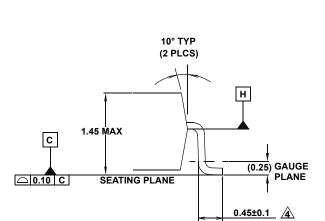

#### **Package Outline Drawing**

#### P5.064A

5 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE Rev 0, 2/10

TOP VIEW

TYPICAL RECOMMENDED LAND PATTERN

DETAIL "X"

NOTES:

- 1. Dimensions are in millimeters.

- Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 3. Dimension is exclusive of mold flash, protrusions or gate burrs.

- 4. Foot length is measured at reference to guage plane.

- **5.** This dimension is measured at Datum "H".

- 6. Package conforms to JEDEC MO-178AA.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**Renesas Electronics:**

<u>ISL28005FH100Z-T7</u> <u>ISL28005FH100Z-T7A</u> <u>ISL28005FH20Z-T7</u> <u>ISL28005FH20Z-T7A</u> <u>ISL28005FH50Z-T7A</u>