# ANALOG DEVICES

## MicroConverter<sup>®</sup>, Dual-Channel 16-Bit ADCs with Embedded Flash MCU

# **ADuC816**

#### **FEATURES**

**High-Resolution Sigma-Delta ADCs Dual 16-Bit Independent ADCs Programmable Gain Front End** 16-Bit No Missing Codes, Primary ADC 13-Bit p-p Resolution @ 20 Hz, 20 mV Range 16-Bit p-p Resolution @ 20 Hz, 2.56 V Range Memory 8 Kbytes On-Chip Flash/EE Program Memory 640 Bytes On-Chip Flash/EE Data Memory Flash/EE, 100 Year Retention, 100 Kcycles Endurance 256 Bytes On-Chip Data RAM 8051-Based Core 8051-Compatible Instruction Set (12.58 MHz Max) 32 kHz External Crystal, On-Chip Programmable PLL **Three 16-Bit Timer/Counters** 26 Programmable I/O Lines 11 Interrupt Sources, Two Priority Levels Power Specified for 3 V and 5 V Operation Normal: 3 mA @ 3 V (Core CLK = 1.5 MHz) Power-Down: 20 μA (32 kHz Crystal Running) **On-Chip Peripherals On-Chip Temperature Sensor 12-Bit Voltage Output DAC Dual Excitation Current Sources Reference Detect Circuit Time Interval Counter (TIC) UART Serial I/O** I<sup>2</sup>C<sup>®</sup>-Compatible and SPI<sup>®</sup> Serial I/O Watchdog Timer (WDT), Power Supply Monitor (PSM)

### **APPLICATIONS**

Intelligent Sensors (IEEE1451.2-Compatible) Weigh Scales **Portable Instrumentation Pressure Transducers** 4-20 mA Transmitters

#### **GENERAL DESCRIPTION**

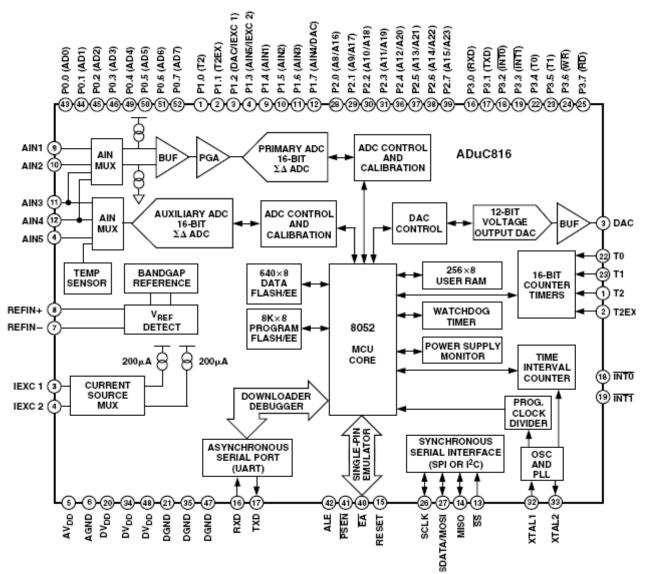

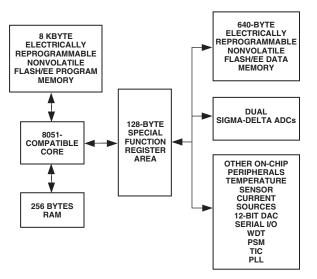

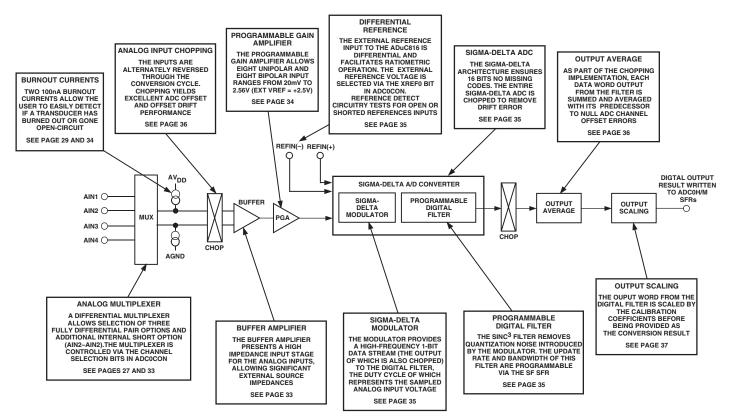

The ADuC816 is a complete smart transducer front-end, integrating two high-resolution sigma-delta ADCs, an 8-bit MCU, and program/data Flash/EE Memory on a single chip. This low power device accepts low-level signals directly from a transducer.

The two independent ADCs (Primary and Auxiliary) include a temperature sensor and a PGA (allowing direct measurement of low-level signals). The ADCs with on-chip digital filtering are

MicroConverter is a registered trademark of Analog Devices, Inc.

SPI is a registered trademark of Motorola, Inc.

I<sup>2</sup>C is a registered trademark of Philips Semiconductors, Inc.

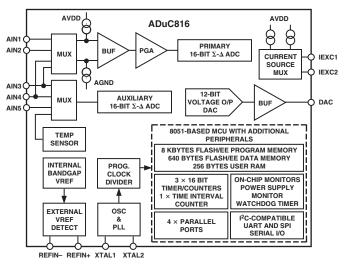

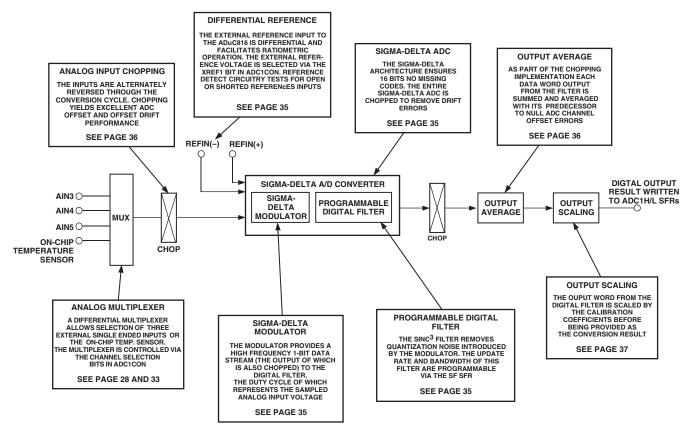

#### FUNCTIONAL BLOCK DIAGRAM

intended for the measurement of wide dynamic range, low frequency signals, such as those in weigh scale, strain gauge, pressure transducer, or temperature measurement applications. The ADC output data rates are programmable and the ADC output resolution will vary with the programmed gain and output rate.

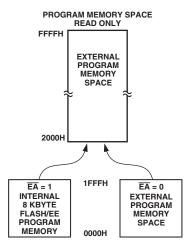

The device operates from a 32 kHz crystal with an on-chip PLL generating a high-frequency clock of 12.58 MHz. This clock is, in turn, routed through a programmable clock divider from which the MCU core clock operating frequency is generated. The microcontroller core is an 8052 and therefore 8051-instructionset-compatible. The microcontroller core machine cycle consists of 12 core clock periods of the selected core operating frequency. 8 Kbytes of nonvolatile Flash/EE program memory are provided on-chip. 640 bytes of nonvolatile Flash/EE data memory and 256 bytes RAM are also integrated on-chip.

The ADuC816 also incorporates additional analog functionality with a 12-bit DAC, current sources, power supply monitor, and a bandgap reference. On-chip digital peripherals include a watchdog timer, time interval counter, three timers/counters, and three serial I/O ports (SPI, UART, and I<sup>2</sup>C-compatible).

On-chip factory firmware supports in-circuit serial download and debug modes (via UART), as well as single-pin emulation mode via the  $\overline{EA}$  pin. A functional block diagram of the ADuC816 is shown above with a more detailed block diagram shown in Figure 12.

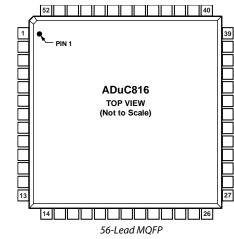

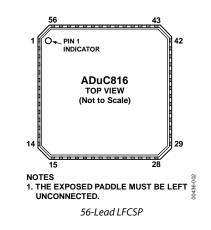

The part operates from a single 3 V or 5 V supply. When operating from 3 V supplies, the power dissipation for the part is below 10 mW. The ADuC816 is housed in 52-lead MOFP and 56-lead LFCSP packages.

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2001-2016 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

Rev. B

### TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                |

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                                                                                                |

| TIMING SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                                                                                                |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                                                               |

| ORDERING GUIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                                                                                               |

| PIN FUNCTION DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                                               |

| ADuC816 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                                                               |

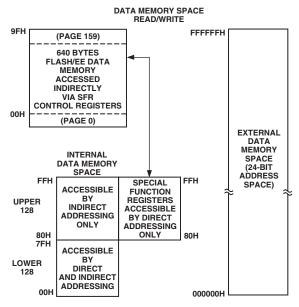

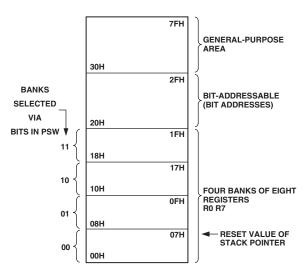

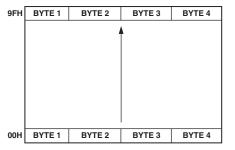

| MEMORY ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                                                               |

| OVERVIEW OF MCU-RELATED SFRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| B SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                               |

| SPECIAL FUNCTION REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                                                                               |

| SFR INTERFACE TO THE PRIMARY AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| AUXILIARY ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                               |

| ADCMODE (ADC Mode Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26                                                                                                                               |

| ADC0CON (Primary ADC Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                                                                               |

| ADC0H/ADC0M (Primary ADC Conversion Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                               |

| ADC1H/ADC1L (Auxiliary ADC Conversion Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                                                                               |

| OF0H/OF0M (Primary ADC Offset Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                                                                               |

| OF1H/OF1L (Auxiliary ADC Offset Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| · •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                               |

| GN0H/GN0M (Primary ADC Gain Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                               |

| Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                                               |

| PRIMARY AND AUXILIARY ADC CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31                                                                                                                               |

| DESCRIPTION OVERVIEW Primary ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| Primary ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                               |

| Primary ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                               |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31<br>32                                                                                                                         |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>33                                                                                                                   |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31<br>32<br>33<br>33                                                                                                             |

| Primary ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31<br>32<br>33<br>33<br>33                                                                                                       |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31<br>32<br>33<br>33<br>33<br>33<br>33                                                                                           |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34                                                                                     |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs                                                                                                                                                                                                                                                                                                                                                                                                                      | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34                                                                               |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents                                                                                                                                                                                                                                                                                                                                                                                                  | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34                                                                         |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents                                                                                                                                                                                                                                                                                                                                                                           | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34                                                                               |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents                                                                                                                                                                                                                                                                                                                                                                                                  | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34                                                                         |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input                                                                                                                                                                                                                                                                                                                                                        | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34                                                                   |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34                                                             |

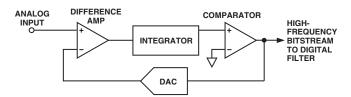

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator                                                                                                                                                                                                                                                                                                           | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>35                                                       |

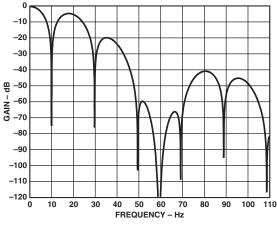

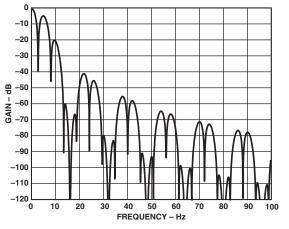

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter                                                                                                                                                                                                                                                                                         | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35                                                 |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping                                                                                                                                                                                                                                                                         | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>35<br>36                                     |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration                                                                                                                                                                                                                                                          | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>35<br>36<br>36                               |

| Primary ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33                                                 |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview                                                                                                                                                                                               | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>34                                           |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816                                                                                                                                     | 31<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34                                           |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816<br>ADuC816 Flash/EE Memory Reliability                                                                                              | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>36<br>37<br>37<br>37<br>37                         |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816<br>ADuC816 Flash/EE Memory Reliability<br>Using the Flash/EE Program Memory                                                                                | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>36<br>37<br>37<br>37<br>37<br>38                   |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816<br>ADuC816 Flash/EE Program Memory<br>Flash/EE Program Memory<br>Flash/EE Program Memory Security                                                          | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>37<br>37<br>38<br>38       |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816<br>ADuC816 Flash/EE Program Memory<br>Flash/EE Program Memory<br>Flash/EE Program Memory Security<br>Using the Flash/EE Data Memory | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>39 |

| Primary ADC<br>Auxiliary ADC<br>PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE<br>Analog Input Channels<br>Primary and Auxiliary ADC Inputs<br>Analog Input Ranges<br>Programmable Gain Amplifier<br>Bipolar/Unipolar Inputs<br>Burnout Currents<br>Excitation Currents<br>Reference Input<br>Reference Detect<br>Sigma-Delta Modulator<br>Digital Filter<br>ADC Chopping<br>Calibration<br>NONVOLATILE FLASH/EE MEMORY<br>Flash/EE Memory Overview<br>Flash/EE Memory and the ADuC816<br>ADuC816 Flash/EE Program Memory<br>Flash/EE Program Memory<br>Flash/EE Program Memory Security                                                          | 31<br>32<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>37<br>37<br>38<br>38       |

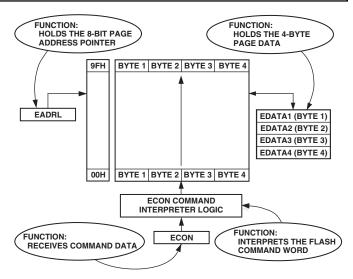

| Using the Flash/EE Memory Interface              | 40       |

|--------------------------------------------------|----------|

| Erase-All<br>Program a Byte                      | 40<br>40 |

| USER INTERFACE TO OTHER ON-CHIP ADuC816          | 40       |

| PERIPHERALS                                      | 41       |

| DAC                                              | 41       |

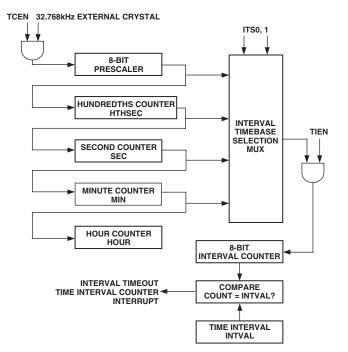

| On-Chip PLL                                      | 42<br>43 |

|                                                  | 43<br>46 |

| Watchdog Timer       Power Supply Monitor        | 40       |

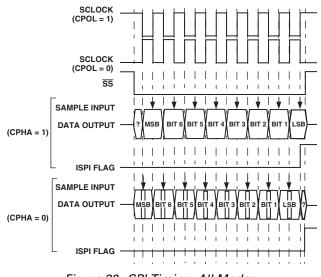

| SERIAL PERIPHERAL INTERFACE                      | 48       |

| MISO (Master In, Slave Out Data I/O Pin), Pin 14 | 48       |

| MOSI (Master Out, Slave In Pin), Pin 27          | 48       |

| SCLOCK (Serial Clock I/O Pin), Pin 26            | 48       |

| SS (Slave Select Input Pin), Pin 13              | 48       |

| Using the SPI Interface                          | 49       |

| SPI Interface—Master Mode                        | 49       |

| SPI Interface—Slave Mode                         | 49       |

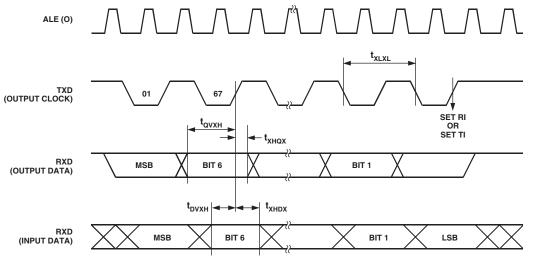

| I <sup>2</sup> C-COMPATIBLE INTERFACE            | 50       |

| 8051-COMPATIBLE ON-CHIP PERIPHERALS              | 51       |

| Parallel I/O Ports 0–3                           | 51       |

| Timers/Counters                                  | 51       |

| TIMER/COUNTER 0 AND 1 OPERATING MODES            | 54       |

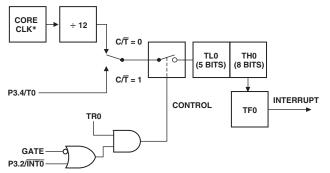

| Mode 0 (13-Bit Timer/Counter)                    | 54       |

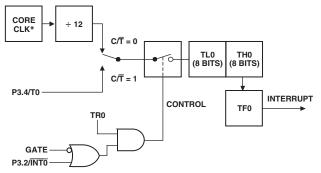

| Mode 1 (16-Bit Timer/Counter)                    | 54       |

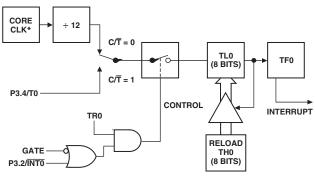

| Mode 2 (8-Bit Timer/Counter with Autoreload)     | 54       |

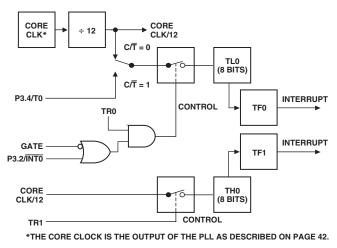

| Mode 3 (Two 8-Bit Timer/Counters)                | 54       |

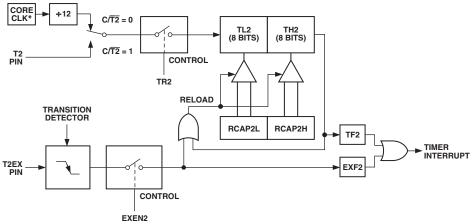

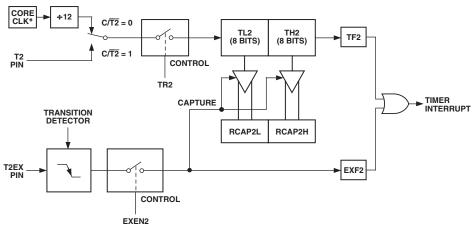

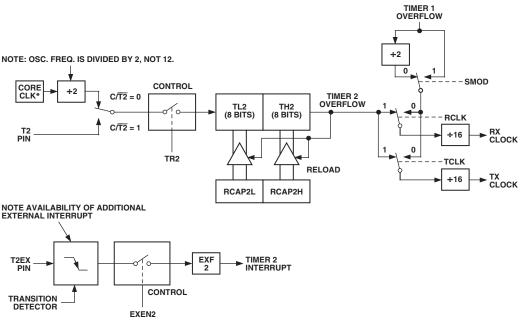

| Timer/Counter 2 Data Registers                   | 55<br>55 |

| TH2 and TL2<br>RCAP2H and RCAP2L                 | 55       |

| Timer/Counter 2 Operating Modes                  | 55<br>56 |

| 16-Bit Autoreload Mode                           | 56       |

| 16-Bit Capture Mode                              | 56       |

| UART SERIAL INTERFACE                            | 57       |

| SBUF                                             | 57       |

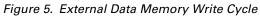

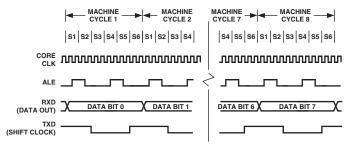

| Mode 0: 8-Bit Shift Register Mode                | 58       |

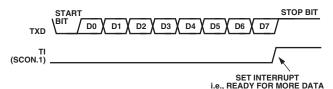

| Mode 1: 8-Bit UART, Variable Baud Rate           | 58       |

| Mode 2: 9-Bit UART with Fixed Baud Rate          | 58       |

| Mode 3: 9-Bit UART with Variable Baud Rate       | 58       |

| UART Serial Port Baud Rate Generation            | 58       |

| Timer 1 Generated Baud Rates                     | 59       |

| Timer 2 Generated Baud Rates                     | 59       |

| INTERRUPT SYSTEM                                 | 60       |

| Interrupt Priority                               | 61       |

| ADuC816 HARDWARE DESIGN CONSIDERATIONS           |          |

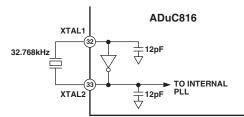

| Clock Oscillator                                 | 62       |

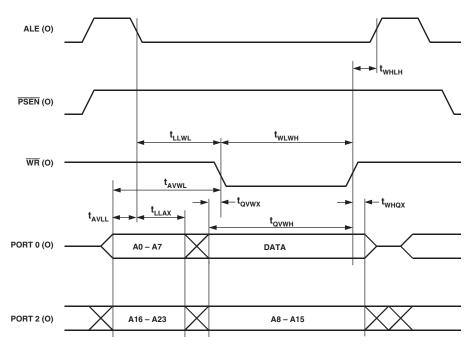

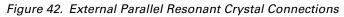

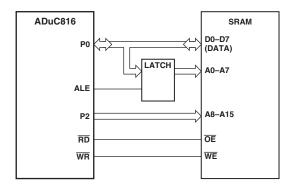

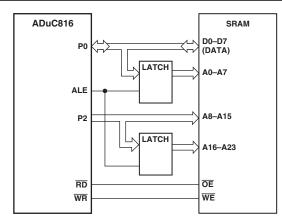

| External Memory Interface                        | 62       |

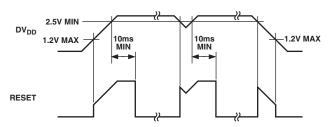

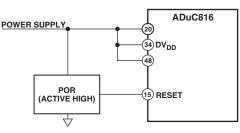

| Power-On Reset Operation                         | 63       |

| Power Supplies                                   | 63<br>64 |

| Power Consumption Power-Saving Modes             | 64<br>64 |

| Grounding and Board Layout Recommendations       | 64       |

| ADuC816 System Self-Identification               | 65       |

| OTHER HARDWARE CONSIDERATIONS                    | 65       |

| In-Circuit Serial Download Access                | 65       |

| Embedded Serial Port Debugger                    | 65       |

| Single-Pin Emulation Mode                        | 65       |

| Enhanced-Hooks Emulation Mode                    | 66       |

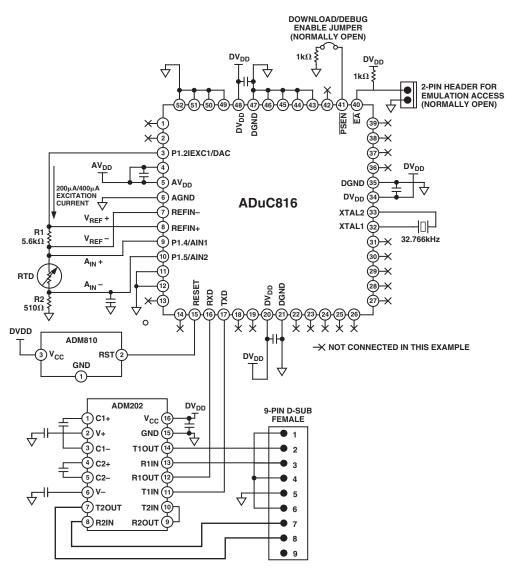

| Typical System Configuration                     | 66       |

| QUICKSTART DEVELOPMENT SYSTEM                    | 67       |

| Download—In-Circuit Serial Downloader            | 67       |

| DeBug—In-Circuit Debugger                        | 67       |

| ADSIM—Windows Simulator                          | 67       |

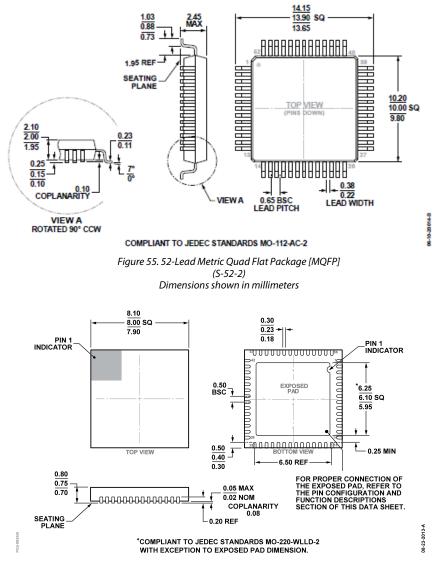

| OUTLINE DIMENSIONS                               | 68       |

# $\begin{tabular}{l} \textbf{SPECIFICATIONS}^1 & (AV_{DD} = 2.7 \text{ V to } 3.6 \text{ V or } 4.75 \text{ V to } 5.25 \text{ V}, DV_{DD} = 2.7 \text{ V to } 3.6 \text{ V or } 4.75 \text{ V to } 5.25 \text{ V}, \\ \textbf{REFIN}(+) = 2.5 \text{ V}; \ \textbf{REFIN}(-) = \textbf{AGND}; \ \textbf{AGND} = \textbf{DGND} = 0 \text{ V}; \ \textbf{XTAL1}/\textbf{XTAL2} = 32.768 \text{ kHz Crystal; all specifications } \textbf{T}_{MIN} \text{ to } \textbf{T}_{MAX} \text{ unless otherwise noted.}) \\ \end{tabular}$

| Parameter                                                | ADuC816BS          | Unit                  | <b>Test Conditions/Comments</b>                                              |

|----------------------------------------------------------|--------------------|-----------------------|------------------------------------------------------------------------------|

| ADC SPECIFICATIONS                                       |                    |                       |                                                                              |

| Conversion Rate                                          | 5.4                | Hz min                | On Both Channels                                                             |

|                                                          | 105                | Hz max                | Programmable in 0.732 ms Increments                                          |

| Primary ADC                                              |                    |                       |                                                                              |

| No Missing Codes <sup>2</sup>                            | 16                 | Bits min              | 20 Hz Update Rate                                                            |

| Resolution                                               | 13                 | Bits p-p typ          | Range = $\pm 20$ mV, 20 Hz Update Rate                                       |

|                                                          | 16                 | Bits p-p typ          | Range = $\pm 2.56$ V, 20 Hz Update Rate                                      |

|                                                          |                    |                       | p-p Resolution at this Range/Update Rate                                     |

|                                                          |                    |                       | Setting Is Limited Only by the Number of                                     |

|                                                          |                    |                       | Bits Available from ADC                                                      |

| Output Noise                                             | See Table IX and X |                       | Output Noise Varies with Selected                                            |

|                                                          | in ADC Description |                       | Update Rate and Gain Range                                                   |

| Integral Nonlinearity                                    | ±1                 | LSB max               |                                                                              |

| Offset Error                                             | ±3                 | μV typ                |                                                                              |

| Offset Error Drift                                       | $\pm 10$           | nV/°C typ             |                                                                              |

| Full-Scale Error <sup>3</sup>                            | ±10                | μV typ                | Range = $\pm 20 \text{ mV}$ to $\pm 640 \text{ mV}$                          |

|                                                          | 0.5                | LSB typ               | Range = $\pm 1.28$ V to $\pm 2.56$ V                                         |

| Gain Error Drift <sup>4</sup>                            | $\pm 0.5$          | ppm/°C typ            |                                                                              |

| ADC Range Matching                                       | ±0.5               | LSB typ               | AIN = 18  mV                                                                 |

| Power Supply Rejection (PSR)                             | 95                 | dBs typ               | AIN = $7.8 \text{ mV}$ , Range = $\pm 20 \text{ mV}$                         |

|                                                          | 80                 | dBs typ               | AIN = 1 V, Range = $\pm 2.56$ V                                              |

| Common-Mode DC Rejection                                 |                    |                       |                                                                              |

| On AIN                                                   | 95                 | dBs typ               | At DC, AIN = $7.8 \text{ mV}$ , Range = $\pm 20 \text{ mV}$                  |

|                                                          | 90                 | dBs typ               | At DC, AIN = 1 V, Range = $\pm 2.56$ V                                       |

| On REFIN                                                 | 90                 | dBs typ               | At DC, AIN = 1 V, Range = $\pm 2.56$ V                                       |

| Common-Mode 50 Hz/60 Hz Rejection <sup>2</sup>           |                    |                       | 20 Hz Update Rate                                                            |

| On AIN                                                   | 95                 | dBs typ               | $50 \text{ Hz}/60 \text{ Hz} \pm 1 \text{ Hz}$ , AIN = 7.8 mV,               |

|                                                          |                    |                       | Range = $\pm 20 \text{ mV}$                                                  |

|                                                          | 90                 | dBs typ               | $50 \text{ Hz}/60 \text{ Hz} \pm 1 \text{ Hz}$ , AIN = 1 V,                  |

|                                                          | 0.0                | ID (                  | Range = $\pm 2.56$ V                                                         |

| On REFIN                                                 | 90                 | dBs typ               | $50 \text{ Hz}/60 \text{ Hz} \pm 1 \text{ Hz}, \text{AIN} = 1 \text{ V},$    |

| Normal Made 50 Ha/60 Ha Dejection <sup>2</sup>           |                    |                       | Range = $\pm 2.56$ V                                                         |

| Normal Mode 50 Hz/60 Hz Rejection <sup>2</sup><br>On AIN | 60                 | dDo trup              | 50 $H_{\pi}/60$ $H_{\pi} \pm 1$ $H_{\pi}$ 20 $H_{\pi}$ Undate Date           |

| On REFIN                                                 | 60                 | dBs typ<br>dBs typ    | 50 Hz/60 Hz ±1 Hz, 20 Hz Update Rate<br>50 Hz/60 Hz ±1 Hz, 20 Hz Update Rate |

| Auxiliary ADC                                            | 00                 | dbs typ               | $50 \text{ Hz}/60 \text{ Hz} \pm 1 \text{ Hz}$ , $20 \text{ Hz}$ Updale Kale |

| No Missing Codes <sup>2</sup>                            | 16                 | Bits min              |                                                                              |

| Resolution                                               | 16                 | Bits p-p typ          | Range = $\pm 2.5$ V, 20 Hz Update Rate                                       |

| Output Noise                                             | See Table XI       | bits p-p typ          | Output Noise Varies with Selected                                            |

| Output Noise                                             | in ADC Description |                       | Update Rate                                                                  |

| Integral Nonlinearity                                    | $\pm 1$            | LSB max               |                                                                              |

| Offset Error                                             | -2                 | LSB typ               |                                                                              |

| Offset Error Drift                                       |                    | $\mu V/^{\circ}C$ typ |                                                                              |

| Full-Scale Error <sup>5</sup>                            | -2.5               | LSB typ               |                                                                              |

| Gain Error Drift <sup>4</sup>                            | $\pm 0.5$          | ppm/°C typ            |                                                                              |

| Power Supply Rejection (PSR)                             | 80                 | dBs typ               | AIN = 1 V, 20 Hz Update Rate                                                 |

| Normal Mode 50 Hz/60 Hz Rejection <sup>2</sup>           |                    | abstyp                |                                                                              |

| On AIN                                                   | 60                 | dBs typ               | 50 Hz/60 Hz ±1 Hz                                                            |

| On REFIN                                                 | 60                 | dBs typ               | $50 \text{ Hz}/60 \text{ Hz} \pm 1 \text{ Hz}$ , 20 Hz Update Rate           |

|                                                          |                    | ·····JF               |                                                                              |

| DAC PERFORMANCE                                          |                    |                       |                                                                              |

| DC Specifications <sup>6</sup>                           | 10                 | D.,                   |                                                                              |

| Resolution                                               | 12                 | Bits                  |                                                                              |

| Relative Accuracy                                        | ±3                 | LSB typ               |                                                                              |

| Differential Nonlinearity                                | -1                 | LSB max               | Guaranteed 12-Bit Monotonic                                                  |

| Offset Error                                             | ±50                | mV max                |                                                                              |

| Gain Error <sup>7</sup>                                  | ±1                 | % max                 | AV <sub>DD</sub> Range                                                       |

|                                                          | ±1                 | % typ                 | V <sub>REF</sub> Range                                                       |

| AC Specifications <sup>2, 6</sup>                        | 1.5                |                       |                                                                              |

| Voltage Output Settling Time                             | 15                 | μs typ                | Settling Time to 1 LSB of Final Value                                        |

| Digital-to-Analog Glitch Energy                          | 10                 | nVs typ               | 1 LSB Change at Major Carry                                                  |

# ADuC816-SPECIFICATIONS<sup>1</sup>

| Parameter                                         | ADuC816BS                          | Unit           | Test Conditions/Comments                                                    |

|---------------------------------------------------|------------------------------------|----------------|-----------------------------------------------------------------------------|

| INTERNAL REFERENCE                                |                                    |                |                                                                             |

| ADC Reference                                     |                                    | <b></b>        |                                                                             |

| Reference Voltage                                 | $1.25 \pm 1\%$                     | V min/max      | Initial Tolerance @ $25^{\circ}$ C, V <sub>DD</sub> = 5 V                   |

| Power Supply Rejection                            | 45                                 | dBs typ        |                                                                             |

| Reference Tempco                                  | 100                                | ppm/°C typ     |                                                                             |

| DAC Reference                                     |                                    |                |                                                                             |

| Reference Voltage                                 | $2.5 \pm 1\%$                      | V min/max      | Initial Tolerance @ $25^{\circ}$ C, V <sub>DD</sub> = 5 V                   |

| Power Supply Rejection                            | 50                                 | dBs typ        |                                                                             |

| Reference Tempco                                  | ±100                               | ppm/°C typ     |                                                                             |

| ANALOG INPUTS/REFERENCE INPUTS                    |                                    |                |                                                                             |

| Primary ADC                                       |                                    |                |                                                                             |

| Differential Input Voltage Ranges <sup>8, 9</sup> |                                    |                | External Reference Voltage = 2.5 V                                          |

|                                                   |                                    |                | RN2, RN1, RN0 of ADC0CON Set to                                             |

| Bipolar Mode (ADC0CON.3 = $0$ )                   | ±20                                | mV             | 0 0 0 (Unipolar Mode 0 mV to 20 mV)                                         |

|                                                   | $\pm 40$                           | mV             | 0 0 1 (Unipolar Mode 0 mV to 40 mV)                                         |

|                                                   | ±80                                | mV             | 0 1 0 (Unipolar Mode 0 mV to 80 mV)                                         |

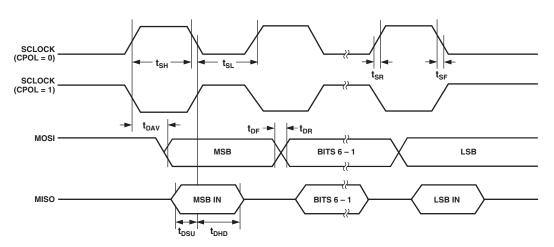

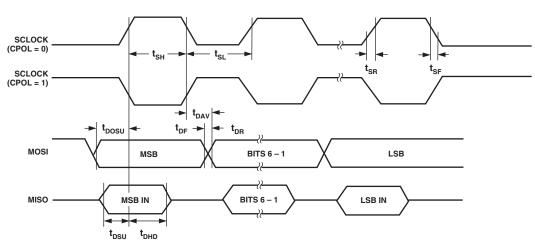

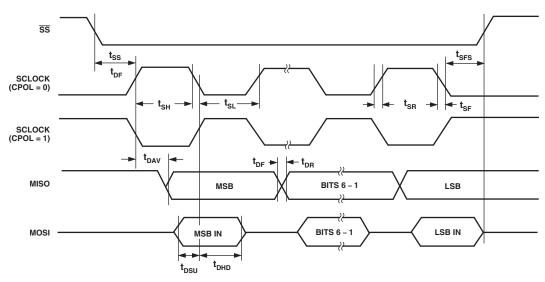

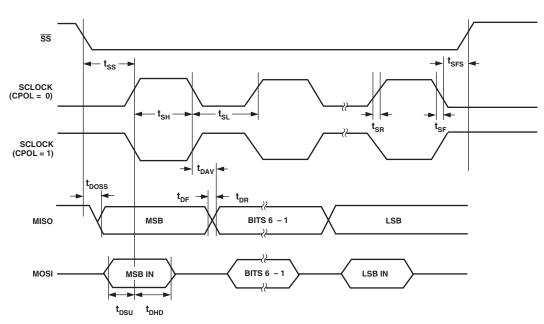

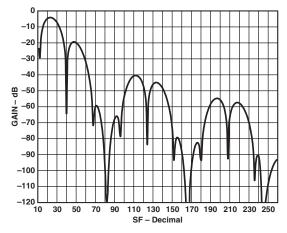

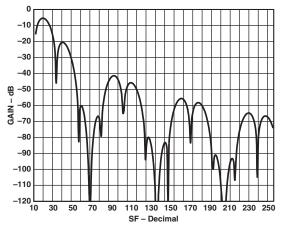

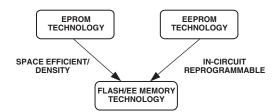

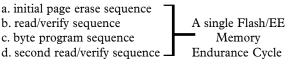

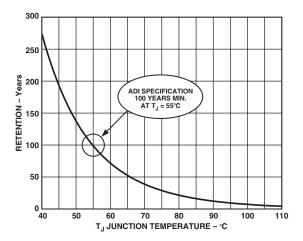

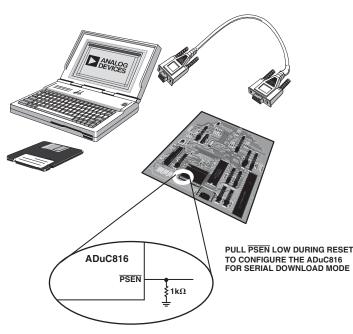

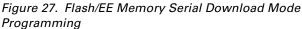

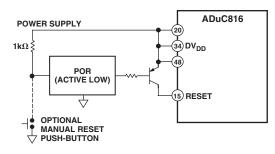

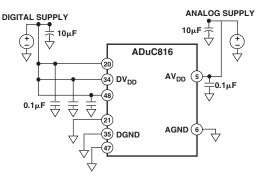

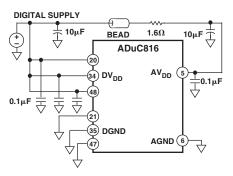

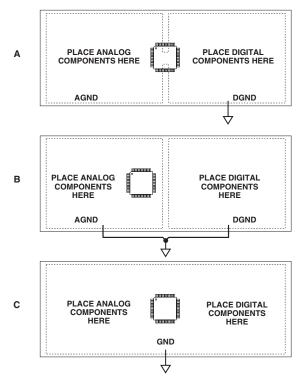

|                                                   | $\pm 160$                          | mV             | 0 1 1 (Unipolar Mode 0 mV to 160 mV)                                        |