# RENESAS

# DATASHEET

ISL3150E, ISL3152E, ISL3153E, ISL3155E, ISL3156E, ISL3158E Large 3V Output Swing, 16.5kV ESD, Full Fail-Safe, 1/8 Unit Load, RS-485/RS-422 Transceivers

FN6363 Rev.5.00 Jun 3, 2020

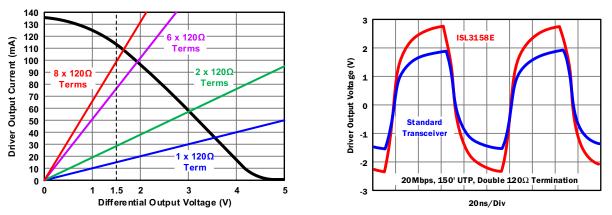

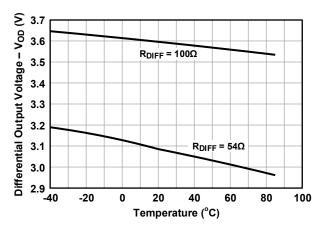

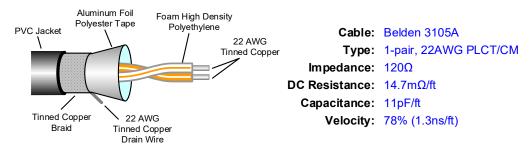

The ISL315xE family of 5V powered RS-485/RS-422 transceivers features high output drive and high ESD protection. The devices withstand  $\pm 16.5$ kV IEC61000-4-2 ESD strikes without latch-up. The large output voltage of 3.1V typical into a 54 $\Omega$  load provides high noise immunity, and enables the drive of up to 8000ft long bus segments, or eight 120 $\Omega$  terminations in a star topology.

These devices possess less than  $125\mu$ A bus input currents, thus constituting a true 1/8 unit load. The high output drive combined with the low bus input currents allows for connecting up to 512 transceivers on the same bus.

The receiver inputs feature a full fail-safe design that turns the receiver outputs high when the bus inputs are open or shorted.

The ISL315xE family includes half and full-duplex transceivers with active-high driver-enable pins and active-low receiver enable pins. These transceivers support data rates of 115kbps, 1Mbps, and 20Mbps. Their performance is characterized from -40°C to +85°C.

#### **Related Literature**

For a full list of related documents, visit our website

• <u>ISL3150E</u>, <u>ISL3152E</u>, <u>ISL3153E</u>, <u>ISL3155E</u>, <u>ISL3156E</u>, and <u>ISL3158E</u> product pages

#### Features

- High V<sub>OD</sub>: 3.1V (Typ) into  $R_D = 54\Omega$

- $\bullet$  Low bus currents: 125 $\mu A$  constitutes a true 1/8 unit load

- Allows for up to 512 transceivers on the bus

- ±16.5kV ESD protection on bus I/O pins

- High transient overvoltage tolerance of  $\pm 100V$

- Full fail-safe outputs for open or shorted inputs

- Hot plug capability driver and receiver outputs remain high-impedance during power-up and power-down

- Supported data rates: 115kbps, 1Mbps, 20Mbps

- Low supply current (driver disabled): 550µA

- Ultra-low shutdown current: 70nA

#### Applications

- Automated utility e-meter reading systems

- High node count systems

- PROFIBUS and Fieldbus systems in factory automation

- · Security camera networks

- Lighting, elevator, and HVAC control systems in building automation

- · Industrial process control networks

- Networks with star topology

- · Long-haul networks in coal mines and oil rigs

# Contents

| 1.                                                  | Overview                                                                                                                                                                                                                              | 3                                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1.1                                                 | Typical Operating Circuit                                                                                                                                                                                                             | 3                                 |

| 1.2                                                 | Ordering Information                                                                                                                                                                                                                  | 3                                 |

| 1.3                                                 | Pin Configurations                                                                                                                                                                                                                    | 5                                 |

| 1.4                                                 | Pin Descriptions.                                                                                                                                                                                                                     | 5                                 |

| 2.                                                  | Specifications.                                                                                                                                                                                                                       | 6                                 |

| 2.1                                                 | Absolute Maximum Ratings                                                                                                                                                                                                              | 6                                 |

| 2.2                                                 | Thermal Information                                                                                                                                                                                                                   | 6                                 |

| 2.3                                                 | Recommended Operating Conditions                                                                                                                                                                                                      | 6                                 |

| 2.4                                                 | Electrical Specifications                                                                                                                                                                                                             | 7                                 |

| -                                                   |                                                                                                                                                                                                                                       |                                   |

| 3.                                                  | Test Circuits and Waveforms 1                                                                                                                                                                                                         | 1                                 |

| 4.                                                  | Performance Curves                                                                                                                                                                                                                    | 4                                 |

|                                                     |                                                                                                                                                                                                                                       |                                   |

| 5.                                                  | Device Description                                                                                                                                                                                                                    | 7                                 |

| <b>5.</b><br>5.1                                    | <b>Device Description.</b>                                                                                                                                                                                                            |                                   |

| -                                                   |                                                                                                                                                                                                                                       | 7                                 |

| 5.1                                                 | Overview                                                                                                                                                                                                                              | 7<br>7                            |

| 5.1<br>5.2                                          | Overview                                                                                                                                                                                                                              | 7<br>7<br>7                       |

| 5.1<br>5.2<br>5.3                                   | Overview       1         Functional Block Diagram       1         Operating Modes       1                                                                                                                                             | 7<br>7<br>7<br>8                  |

| 5.1<br>5.2<br>5.3<br>5.4                            | Overview       1         Functional Block Diagram       1         Operating Modes       1         Device Features       1         Application Information       2                                                                     | 7<br>7<br>8<br><b>1</b>           |

| 5.1<br>5.2<br>5.3<br>5.4<br><b>6.</b>               | Overview       1         Functional Block Diagram       1         Operating Modes       1         Device Features       1                                                                                                             | 7<br>7<br>8<br><b>1</b><br>1      |

| 5.1<br>5.2<br>5.3<br>5.4<br><b>6.</b><br>6.1        | Overview       1         Functional Block Diagram       1         Operating Modes       1         Device Features       1         Application Information       2         Network Design       2                                      | 7<br>7<br>7<br>8<br><b>1</b><br>1 |

| 5.1<br>5.2<br>5.3<br>5.4<br><b>6.</b><br>6.1<br>6.2 | Overview       1         Functional Block Diagram       1         Operating Modes       1         Device Features       1         Application Information       2         Network Design       2         Transient Protection       2 | 7<br>7<br>7<br>8<br>1<br>6<br>6   |

# 1. Overview

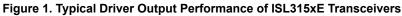

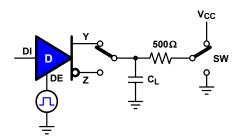

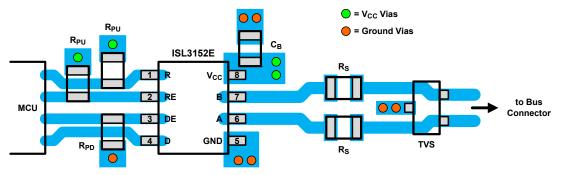

# 1.1 Typical Operating Circuit

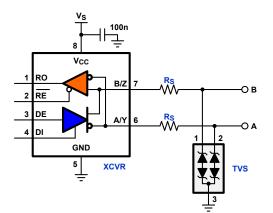

Figure 2. Typical Operating Circuits of Half-Duplex and Full-Duplex Transceivers

## 1.2 Ordering Information

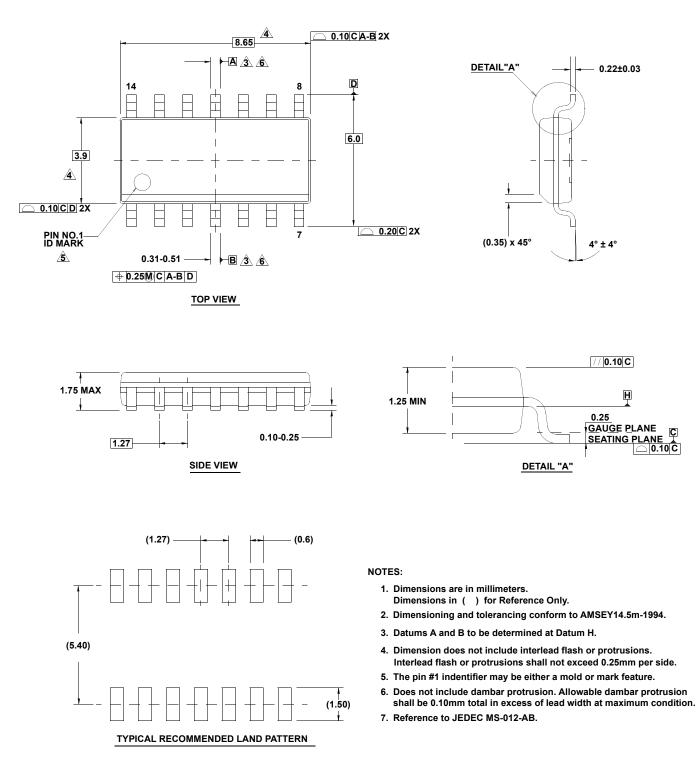

| Part Number ( <u>Notes 2, 3</u> )                                             | Part Marking | Temp. Range (°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant) | Pkg. Dwg. # |

|-------------------------------------------------------------------------------|--------------|------------------|--------------------------------------------|-----------------------------|-------------|

| ISL3150EIBZ                                                                   | 3150EIBZ     | -40 to +85       | -                                          | 14 Ld SOIC                  | M14.15      |

| ISL3150EIBZ-T                                                                 | 3150EIBZ     | -40 to +85       | 2.5k                                       | 14 Ld SOIC                  | M14.15      |

| ISL3150EIBZ-T7A                                                               | 3150EIBZ     | -40 to +85       | 250                                        | 14 Ld SOIC                  | M14.15      |

| ISL3150EIUZ                                                                   | 3150Z        | -40 to +85       | -                                          | 10 Ld MSOP                  | M10.118     |

| ISL3150EIUZ-T                                                                 | 3150Z        | -40 to +85       | 2.5k                                       | 10 Ld MSOP                  | M10.118     |

| ISL3150EIUZ-T7A                                                               | 3150Z        | -40 to +85       | 250                                        | 10 Ld MSOP                  | M10.118     |

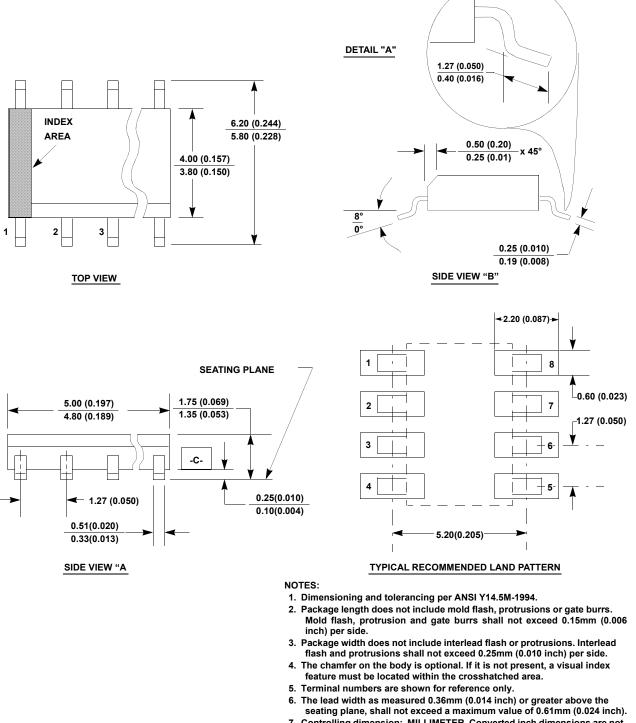

| ISL3152EIBZ                                                                   | 3152EIBZ     | -40 to +85       | -                                          | 8 Ld SOIC                   | M8.15       |

| ISL3152EIBZ-T                                                                 | 3152EIBZ     | -40 to +85       | 2.5k                                       | 8 Ld SOIC                   | M8.15       |

| ISL3152EIBZ-T7                                                                | 3152EIBZ     | -40 to +85       | 1k                                         | 8 Ld SOIC                   | M8.15       |

| ISL3152EIBZ-T7A                                                               | 3152EIBZ     | -40 to +85       | 250                                        | 8 Ld SOIC                   | M8.15       |

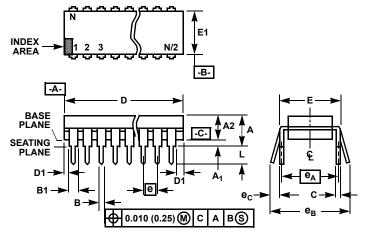

| ISL3152EIPZ (No longer<br>available, recommended<br>replacement: ISL3152EIBZ) | ISL3152 EIPZ | -40 to +85       | -                                          | 8 Ld PDIPs                  | E8.3        |

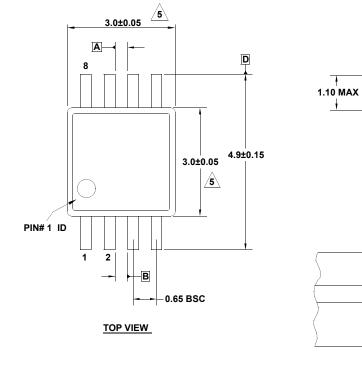

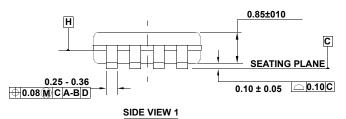

| ISL3152EIUZ                                                                   | 3152Z        | -40 to +85       | -                                          | 8 Ld MSOP                   | M8.118      |

| ISL3152EIUZ-T                                                                 | 3152Z        | -40 to +85       | 2.5k                                       | 8 Ld MSOP                   | M8.118      |

| ISL3152EIUZ-T7A                                                               | 3152Z        | -40 to +85       | 250                                        | 8 Ld MSOP                   | M8.118      |

| ISL3153EIBZ-T                                                                 | 3153EIBZ     | -40 to +85       | 2.5k                                       | 14 Ld SOIC                  | M14.15      |

| ISL3153EIUZ                                                                   | 3153Z        | -40 to +85       | -                                          | 10 Ld MSOP                  | M10.118     |

| ISL3153EIUZ-T                                                                 | 3153Z        | -40 to +85       | 2.5k                                       | 10 Ld MSOP                  | M10.118     |

| ISL3153EIUZ-T7A                                                               | 3153Z        | -40 to +85       | 250                                        | 10 Ld MSOP                  | M10.118     |

| ISL3155EIBZ                                                                   | 3155EIBZ     | -40 to +85       | -                                          | 8 Ld SOIC                   | M8.15       |

| ISL3155EIBZ-T                                                                 | 3155EIBZ     | -40 to +85       | 2.5k                                       | 8 Ld SOIC                   | M8.15       |

| ISL3155EIBZ-T7A                                                               | 3155EIBZ     | -40 to +85       | 250                                        | 8 Ld SOIC                   | M8.15       |

| ISL3155EIUZ                                                                   | 3155Z        | -40 to +85       | -                                          | 8 Ld MSOP                   | M8.118      |

| ISL3155EIUZ-T                                                                 | 3155Z        | -40 to +85       | 2.5k                                       | 8 Ld MSOP                   | M8.118      |

| Part Number ( <u>Notes 2, 3</u> ) | Part Marking | Temp. Range (°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant) | Pkg. Dwg. # |

|-----------------------------------|--------------|------------------|--------------------------------------------|-----------------------------|-------------|

| ISL3156EIBZ                       | 3156EIBZ     | -40 to +85       | -                                          | 14 Ld SOIC                  | M14.15      |

| ISL3156EIBZ-T                     | 3156EIBZ     | -40 to +85       | 2.5k                                       | 14 Ld SOIC                  | M14.15      |

| ISL3156EIBZ-T7A                   | 3156EIBZ     | -40 to +85       | 250                                        | 14 Ld SOIC                  | M14.15      |

| ISL3156EIUZ                       | 3156Z        | -40 to +85       | -                                          | 10 Ld MSOP                  | M10.118     |

| ISL3156EIUZ-T                     | 3156Z        | -40 to +85       | 2.5k                                       | 10 Ld MSOP                  | M10.118     |

| ISL3156EIUZ-T7A                   | 3156Z        | -40 to +85       | 250                                        | 10 Ld MSOP                  | M10.118     |

| ISL3158EIBZ                       | 3158EIBZ     | -40 to +85       | -                                          | 8 Ld SOIC                   | M8.15       |

| ISL3158EIBZ-T                     | 3158EIBZ     | -40 to +85       | 2.5k                                       | 8 Ld SOIC                   | M8.15       |

| ISL3158EIBZ-T7A                   | 3158EIBZ     | -40 to +85       | 250                                        | 8 Ld SOIC                   | M8.15       |

| ISL3158EIUZ                       | 3158Z        | -40 to +85       | -                                          | 8 Ld MSOP                   | M8.118      |

| ISL3158EIUZ-T                     | 3158Z        | -40 to +85       | 2.5k                                       | 8 Ld MSOP                   | M8.118      |

| ISL3158EIUZ-T7A                   | 3158Z        | -40 to +85       | 250                                        | 8 Ld MSOP                   | M8.118      |

Notes:

1. Refer to <u>TB347</u> for details about reel specifications.

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the product information pages for the <u>ISL3150E</u>, <u>ISL3152E</u>, <u>ISL3153E</u>, <u>ISL3153E</u>, <u>ISL3153E</u>, <u>ISL3158E</u>. For more information about MSL, see <u>TB363</u>.

| Part Number | Duplex | Data Rate (Mbps) | Rise/Fall Time (ns) | Tx/Rx Skew (ns) | Bus ESD (kV) | Pin Count |

|-------------|--------|------------------|---------------------|-----------------|--------------|-----------|

| ISL3150E    | Full   | 0.115            | 1100                | 12/4            | ±10          | 10, 14    |

| ISL3152E    | Half   | 0.115            | 1100                | 12/4            | ±16          | 8         |

| ISL3153E    | Full   | 1                | 150                 | 3/4             | ±10          | 10, 14    |

| ISL3155E    | Half   | 1                | 150                 | 3/4             | ±16          | 8         |

| ISL3156E    | Full   | 20               | 8                   | 0.2/2.5         | ±10          | 10, 14    |

| ISL3158E    | Half   | 20               | 8                   | 0.2/2.5         | ±16          | 8         |

#### Table 1. Key Differences of Device Features

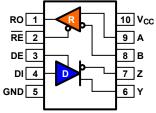

#### **1.3 Pin Configurations**

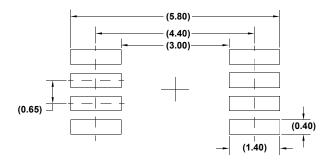

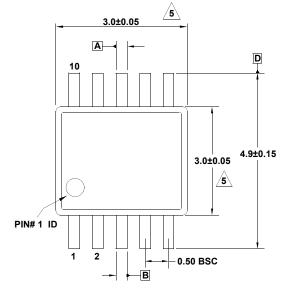

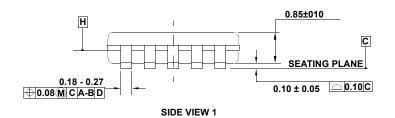

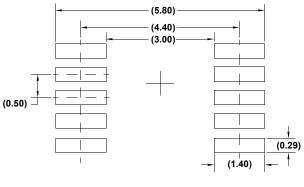

ISL3152E, ISL3155E, ISL3158E (8 Ld MSOP, 8 Ld SOIC, 8 Ld PDIP) Top View

ISL3150E, ISL3153E, ISL3156E (10 Ld MSOP) Top View

ISL3150E, ISL3153E, ISL3156E (14 Ld SOIC) Top View 14 V<sub>CC</sub> NC 1 RO 2 13 NC RE 3 12 A 11 B DE 4 10 Z DI 5 9 Y GND 6 GND 7 8 NC

## 1.4 Pin Descriptions

| 8 Ld<br>SOIC | 10 Ld<br>MSOP | 14 Ld<br>SOIC | Pin<br>Name     | Function                                                                                                                                       |

|--------------|---------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 1             | 2             | RO              | Receiver output: If A-B ≥ -50mV, RO is high; If A-B ≤ -200mV, RO is low. RO is Fail-safe<br>High if A and B are unconnected (open) or shorted. |

| 2            | 2             | 3             | RE              | Receiver output enable. RO is enabled when $\overline{\text{RE}}$ is low; RO is high impedance when $\overline{\text{RE}}$ is high.            |

| 3            | 3             | 4             | DE              | Driver output enable. The driver outputs, Y and Z, are enabled by bringing DE high. They are high impedance when DE is low.                    |

| 4            | 4             | 5             | DI              | Driver input. A low on DI forces output Y low and output Z high. Similarly, a high on DI forces output Y high and output Z low.                |

| 5            | 5             | 6, 7          | GND             | Ground connection.                                                                                                                             |

| 6            | -             | -             | A/Y             | Non-inverting receiver input and non-inverting driver output. Pin is an input if DE = 0; pin is an output if DE = 1.                           |

| 7            | -             | -             | B/Z             | Inverting receiver input and inverting driver output. Pin is an input if DE = 0; pin is an output if DE = 1.                                   |

| -            | 6             | 9             | Y               | Non-inverting driver output.                                                                                                                   |

| -            | 7             | 10            | Z               | Inverting driver output.                                                                                                                       |

| -            | 8             | 11            | В               | Inverting receiver input.                                                                                                                      |

| -            | 9             | 12            | А               | Non-inverting receiver input.                                                                                                                  |

| 8            | 10            | -             | V <sub>CC</sub> | System power supply input (4.5V to 5.5V).                                                                                                      |

| -            | _             | 1, 8, 13      | NC              | No connection.                                                                                                                                 |

# 2. Specifications

## 2.1 Absolute Maximum Ratings

| Parameter ( <u>Note 4</u> )                                                            | Minimum                                    | Maximum               | Unit |  |  |

|----------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|------|--|--|

| V <sub>CC</sub> to Ground                                                              |                                            | 7                     | V    |  |  |

| Input Voltages at DI, DE, RE                                                           | -0.3                                       | V <sub>CC</sub> + 0.3 | V    |  |  |

| Bus I/O Voltages at A/Y, B/Z, A, B, Y, Z                                               | -9                                         | 13                    | V    |  |  |

| Transient Pulse Voltages through $100\Omega$ at A/Y, B/Z, A, B, Y, Z ( <u>Note 5</u> ) |                                            | ±100                  | V    |  |  |

| RO                                                                                     | -0.3                                       | V <sub>CC</sub> + 0.3 | V    |  |  |

| Short Circuit Duration at Y, Z                                                         |                                            | Continuous            |      |  |  |

| ESD Rating                                                                             | See "Electrical Specifications" on page 8. |                       |      |  |  |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty. **Notes:**

4. Absolute Maximum ratings mean the device will not be damaged if operated under these conditions. It does not guarantee performance.

5. Tested according to TIA/EIA-485-A, Section 4.2.6 (±100V for 15µs at a 1% duty cycle).

## 2.2 Thermal Information

| Thermal Resistance (Typical, <u>Note 6</u> ) | θ <sub>JA</sub> (°C/W) |

|----------------------------------------------|------------------------|

| 8 Ld SOIC                                    | 105                    |

| 8 Ld MSOP, PDIP                              | 140                    |

| 10 Ld MSOP                                   | 130                    |

| 14 Ld SOIC                                   | 130                    |

#### Note:

6.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u> for details.

| Parameter                                      | Minimum | Maximum          | Unit |

|------------------------------------------------|---------|------------------|------|

| Maximum Junction Temperature (Plastic Package) |         | +150             | °C   |

| Maximum Storage Temperature Range              | -65     | +150             | °C   |

| Pb-Free Reflow Profile ( <u>Note 7</u> )       | S       | See <u>TB493</u> |      |

Note:

7. Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

## 2.3 Recommended Operating Conditions

| Parameter                         | Minimum | Maximum | Unit |

|-----------------------------------|---------|---------|------|

| Supply Voltage                    | 4.5     | 5.5     | V    |

| Temperature Range                 | -40     | +85     | °C   |

| Bus Pin Common-Mode Voltage Range | -7      | +12     | V    |

## 2.4 Electrical Specifications

Test Conditions:  $V_{CC}$  = 4.5V to 5.5V; unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C (<u>Note 8</u>). Boldface limits apply across the operating temperature range, -40°C to +85°C.

| Parameter                                                       | Symbol            | Test Co                                                                                       | nditions                                         | Temp<br>(°C) | Min<br>( <u>Note 16</u> ) | Тур  | Max ( <u>Note 16</u> ) | Unit |

|-----------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|---------------------------|------|------------------------|------|

| DC Characteristics                                              |                   | •                                                                                             |                                                  |              |                           | -    |                        |      |

| Driver Differential Output<br>Voltage (No load)                 | V <sub>OD1</sub>  |                                                                                               |                                                  | Full         | -                         | -    | V <sub>cc</sub>        | V    |

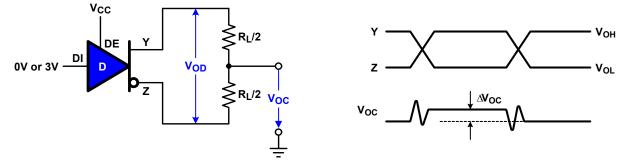

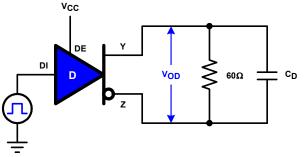

| Driver Differential Output                                      | V <sub>OD2</sub>  | R <sub>L</sub> = 100Ω (RS-422) ( <u>Figure 3</u> )                                            |                                                  | Full         | 2.8                       | 3.6  | -                      | V    |

| Voltage (Loaded)                                                |                   | R <sub>L</sub> = 54Ω (RS-485)                                                                 | (Figure 3)                                       | Full         | 2.4                       | 3.1  | v <sub>cc</sub>        | V    |

|                                                                 |                   | R <sub>L</sub> = 15Ω (Eight 120<br>( <u>Note 17</u> )                                         | $\Omega$ terminations)                           | +25          | -                         | 1.65 | -                      | V    |

|                                                                 |                   | $R_L = 60\Omega$ , $-7V \le V_{CN}$                                                           | <sub>A</sub> ≤ 12V ( <u>Figure 4</u> )           | Full         | 2.4                       | 3    | -                      | V    |

| Change in Magnitude of<br>Driver Differential Output<br>Voltage | ΔV <sub>OD</sub>  | R <sub>L</sub> = 54Ω or 100Ω ( <u>F</u>                                                       | Figure <u>3</u> )                                | Full         | -                         | 0.01 | 0.2                    | V    |

| Driver Common-Mode Output<br>Voltage                            | V <sub>OC</sub>   | $R_L = 54\Omega \text{ or } 100\Omega \text{ (f}$                                             | Figure 3)                                        | Full         | -                         | -    | 3.15                   | V    |

| Change in Magnitude of<br>Driver Common-Mode Output<br>Voltage  | ΔV <sub>OC</sub>  | R <sub>L</sub> = 54Ω or 100Ω ( <u>F</u>                                                       | R <sub>L</sub> = 54Ω or 100Ω ( <u>Figure 3</u> ) |              | -                         | 0.01 | 0.2                    | V    |

| Logic Input High Voltage                                        | V <sub>IH</sub>   | DE, DI, RE                                                                                    |                                                  | Full         | 2                         | -    | -                      | V    |

| Logic Input Low Voltage                                         | V <sub>IL</sub>   | DE, DI, RE                                                                                    | DE, DI, RE                                       |              | -                         | -    | 0.8                    | V    |

| DI Input Hysteresis Voltage                                     | V <sub>HYS</sub>  |                                                                                               |                                                  | +25          | -                         | 100  | -                      | mV   |

| Logic Input Current                                             | I <sub>IN1</sub>  | DE, DI, RE                                                                                    |                                                  | Full         | -2                        | -    | 2                      | μA   |

| Input Current (A, B, A/Y, B/Z)                                  | I <sub>IN2</sub>  | $DE = 0V, V_{CC} = 0V$                                                                        | V <sub>IN</sub> = 12V                            | Full         | -                         | 70   | 125                    | μA   |

|                                                                 |                   | or 5.5V                                                                                       | V <sub>IN</sub> = -7V                            | Full         | -75                       | 55   | -                      | μA   |

| Output Leakage Current                                          | I <sub>IN3</sub>  | $\overline{RE}$ = 0V, DE = 0V,                                                                | V <sub>IN</sub> = 12V                            | Full         | -                         | 1    | 40                     | μA   |

| (Y, Z) (Full Duplex Versions<br>Only)                           |                   | V <sub>CC</sub> = 0V or 5.5V                                                                  | V <sub>IN</sub> = -7V                            | Full         | -40                       | -9   | -                      | μA   |

| Output Leakage Current                                          | I <sub>IN4</sub>  | $\overline{\text{RE}} = V_{\text{CC}}, \text{DE} = 0V,$                                       | V <sub>IN</sub> = 12V                            | Full         | -                         | 1    | 20                     | μA   |

| (Y, Z) in Shutdown Mode (Full Duplex)                           |                   | V <sub>CC</sub> = 0V or 5.5V                                                                  | V <sub>IN</sub> = -7V                            | Full         | -20                       | -9   | -                      | μA   |

| Driver Short-Circuit Current,<br>V <sub>O</sub> = High or Low   | I <sub>OSD1</sub> | $\begin{array}{l} DE = V_{CC},  \text{-7V} \leq V_{Y} \\ (\underline{Note \ 10}) \end{array}$ | or V <sub>Z</sub> ≤ 12V                          | Full         | -                         | -    | ±250                   | mA   |

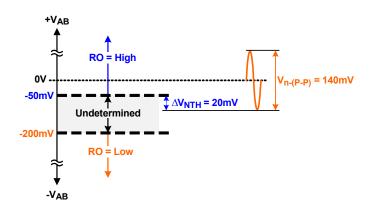

| Receiver Differential<br>Threshold Voltage                      | V <sub>TH</sub>   | -7V ≤ V <sub>CM</sub> ≤ 12V                                                                   |                                                  | Full         | -200                      | -90  | -50                    | mV   |

| Receiver Input Hysteresis                                       | ΔV <sub>TH</sub>  | V <sub>CM</sub> = 0V                                                                          |                                                  | +25          | -                         | 20   | -                      | mV   |

| Receiver Output High Voltage                                    | V <sub>OH</sub>   | I <sub>O</sub> = -8mA, V <sub>ID</sub> = -50                                                  | mV                                               | Full         | V <sub>CC</sub> - 1.2     | 4.3  | -                      | V    |

| Receiver Output Low Voltage                                     | V <sub>OL</sub>   | I <sub>O</sub> = -8mA, V <sub>ID</sub> = -200mV                                               |                                                  | Full         | -                         | 0.25 | 0.4                    | V    |

| Receiver Output Low Current                                     | I <sub>OL</sub>   | V <sub>O</sub> = 1V, V <sub>ID</sub> = -200mV                                                 |                                                  | Full         | 20                        | 28   | -                      | mA   |

| Three-State (High<br>Impedance) Receiver Output<br>Current      | I <sub>OZR</sub>  | $0.4 V \le V_0 \le 2.4 V$                                                                     |                                                  | Full         | -1                        | 0.03 | 1                      | μA   |

| Receiver Input Resistance                                       | R <sub>IN</sub>   | -7V ≤ V <sub>CM</sub> ≤ 12V                                                                   |                                                  | Full         | 96                        | 160  | -                      | kΩ   |

Test Conditions:  $V_{CC}$  = 4.5V to 5.5V; unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C (<u>Note 8</u>). Boldface limits apply across the operating temperature range, -40°C to +85°C. (Continued)

| Parameter                                     | Symbol                             | Test Co                                                                                                | nditions                                                            | Temp<br>(°C) | Min<br>( <u>Note 16</u> ) | Тур   | Max ( <u>Note 16</u> ) | Unit |

|-----------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------|---------------------------|-------|------------------------|------|

| Receiver Short-Circuit<br>Current             | I <sub>OSR</sub>                   | $0V \le V_O \le V_{CC}$                                                                                |                                                                     | Full         | ±7                        | 65    | ±85                    | mA   |

| Supply Current                                | •                                  |                                                                                                        |                                                                     | •            |                           |       |                        |      |

| No-Load Supply Current<br>( <u>Note 9</u> )   | I <sub>CC</sub>                    | Half duplex versions, DE = $V_{CC}$ , $\overline{RE} = X$ ,<br>DI = 0V or $V_{CC}$                     |                                                                     | Full         | -                         | 650   | 800                    | μA   |

|                                               |                                    | All versions, DE = 0 <sup>1</sup><br>duplex versions, DE<br>DI = 0V or V <sub>CC</sub>                 |                                                                     | Full         | -                         | 550   | 700                    | μA   |

| Shutdown Supply Current                       | I <sub>SHDN</sub>                  | $DE = 0V, \overline{RE} = V_{CC},$                                                                     | DI = 0V or V <sub>CC</sub>                                          | Full         | -                         | 0.07  | 3                      | μA   |

| ESD Performance                               |                                    |                                                                                                        |                                                                     |              | •                         |       |                        |      |

| RS-485 Pins (A, Y, B, Z, A/Y,                 |                                    | IEC61000-4-2, Half duplex                                                                              |                                                                     | +25          | -                         | ±16.5 | -                      | kV   |

| B/Z)                                          |                                    | Air-Gap Discharge<br>Method                                                                            | Full duplex                                                         | +25          | -                         | ±10   | -                      | kV   |

|                                               |                                    | IEC61000-4-2, Cont<br>Method                                                                           | act Discharge                                                       | +25          | -                         | ±9    | -                      | kV   |

|                                               |                                    | Human Body Model,<br>GND                                                                               | from bus pins to                                                    | +25          | -                         | ±16.5 | -                      | kV   |

| All Pins                                      |                                    | Human Body Model, per MIL-STD-883<br>Method 3015<br>Machine Model                                      |                                                                     | +25          | -                         | ±7    | -                      | kV   |

|                                               |                                    |                                                                                                        |                                                                     | +25          | -                         | 400   | -                      | V    |

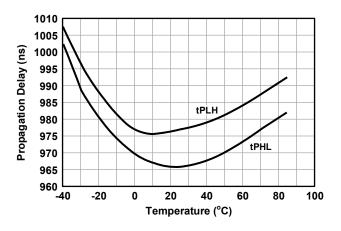

| Driver Switching Characteris                  | stics (115kl                       | ops Versions; ISL31                                                                                    | 50E, ISL3152E)                                                      | •            |                           | •     |                        |      |

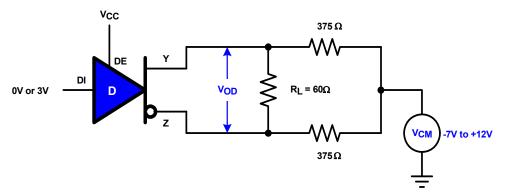

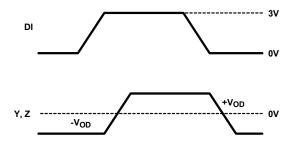

| Driver Differential Output<br>Delay           | t <sub>PLH,</sub> t <sub>PHL</sub> | $R_{DIFF} = 54\Omega, C_L = 1$                                                                         | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF ( <u>Figure 5</u> ) |              | 500                       | 970   | 1300                   | ns   |

| Driver Differential Output<br>Skew            | t <sub>SKEW</sub>                  | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 1                                                            | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF ( <u>Figure 5</u> ) |              | -                         | 12    | 50                     | ns   |

| Driver Differential Rise or<br>Fall Time      | t <sub>R</sub> , t <sub>F</sub>    | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 1                                                            | $R_{DIFF} = 54\Omega, C_{L} = 100pF (Figure 5)$                     |              | 700                       | 1100  | 1600                   | ns   |

| Maximum Data Rate                             | f <sub>MAX</sub>                   | C <sub>D</sub> = 820pF ( <u>Figure</u>                                                                 | <u>7</u> , <u>Note 18</u> )                                         | Full         | 115.2                     | 2000  | -                      | kbps |

| Driver Enable to Output High                  | t <sub>ZH</sub>                    | $R_{L} = 500\Omega, C_{L} = 100$<br>(Figure 6, Note 11)                                                | 0pF, SW = GND                                                       | Full         | -                         | 300   | 600                    | ns   |

| Driver Enable to Output Low                   | t <sub>ZL</sub>                    | $R_L = 500\Omega, C_L = 100$<br>( <u>Figure 6</u> , <u>Note 11</u> )                                   | 0pF, SW = V <sub>CC</sub>                                           | Full         | -                         | 130   | 500                    | ns   |

| Driver Disable from Output<br>Low             | t <sub>LZ</sub>                    | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 15μ<br>( <u>Figure 6</u> )                                     | bF, SW = V <sub>CC</sub>                                            | Full         | -                         | 50    | 65                     | ns   |

| Driver Disable from Output<br>High            | t <sub>HZ</sub>                    | $R_L = 500\Omega$ , $C_L = 15pF$ ,<br>SW = GND ( <u>Figure 6</u> )                                     |                                                                     | Full         | -                         | 35    | 60                     | ns   |

| Time to Shutdown                              | t <sub>SHDN</sub>                  | ( <u>Note 13</u> )                                                                                     |                                                                     | Full         | 60                        | 160   | 600                    | ns   |

| Driver Enable from Shutdown<br>to Output High | t <sub>ZH(SHDN)</sub>              | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>( <u>Figure 6, Notes 13, 14</u> )           |                                                                     | Full         | -                         | -     | 250                    | ns   |

| Driver Enable from Shutdown<br>to Output Low  | t <sub>ZL(SHDN)</sub>              | $R_L$ = 500Ω, $C_L$ = 100pF, SW = V <sub>CC</sub><br>( <u>Figure 6</u> , <u>Notes 13</u> , <u>14</u> ) |                                                                     | Full         | -                         | -     | 250                    | ns   |

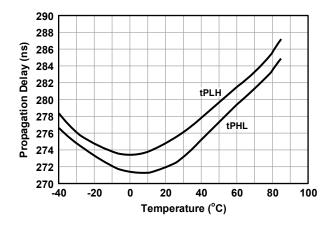

| Driver Switching Characteris                  | stics (1Mbp                        | os Versions; ISL3153                                                                                   | BE, ISL3155E)                                                       |              |                           |       |                        |      |

| Driver Differential Output<br>Delay           | t <sub>PLH,</sub> t <sub>PHL</sub> | $R_{DIFF} = 54\Omega, C_L = 1$                                                                         | 00pF ( <u>Figure 5</u> )                                            | Full         | 150                       | 270   | 400                    | ns   |

| Test Conditions: $V_{CC}$ = 4.5V to 5.5V; unless otherwise specified. Typical values are at $V_{CC}$ = 5V, $T_A$ = +25°C (Note 8). Boldface limits |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| apply across the operating temperature range, -40°C to +85°C. (Continued)                                                                          |

| Parameter                                           | Symbol                                 | Test Conditions                                                                                          | Temp<br>(°C) | Min<br>( <u>Note 16</u> ) | Тур | Max ( <u>Note 16</u> ) | Unit |

|-----------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|---------------------------|-----|------------------------|------|

| Driver Differential Output<br>Skew                  | t <sub>SKEW</sub>                      | $R_{DIFF} = 54\Omega, C_L = 100pF (Figure 5)$                                                            | Full         | -                         | 3   | 10                     | ns   |

| Driver Differential Rise or<br>Fall Time            | t <sub>R</sub> , t <sub>F</sub>        | $R_{DIFF} = 54\Omega, C_L = 100pF (Figure 5)$                                                            | Full         | 150                       | 325 | 450                    | ns   |

| Maximum Data Rate                                   | f <sub>MAX</sub>                       | C <sub>D</sub> = 820pF ( <u>Figure 7</u> , <u>Note 18</u> )                                              | Full         | 1                         | 8   | -                      | Mbps |

| Driver Enable to Output High                        | t <sub>ZH</sub>                        | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>( <u>Figure 6, Note 11</u> )                  | Full         | -                         | 110 | 200                    | ns   |

| Driver Enable to Output Low                         | t <sub>ZL</sub>                        | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = V <sub>CC</sub><br>( <u>Figure 6, Note 11</u> )      | Full         | -                         | 60  | 200                    | ns   |

| Driver Disable from Output<br>Low                   | t <sub>LZ</sub>                        | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = $V_{CC}$<br>( <u>Figure 6</u> )                                  | Full         | -                         | 50  | 65                     | ns   |

| Driver Disable from Output<br>High                  | t <sub>HZ</sub>                        | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = GND<br>( <u>Figure 6</u> )                                       | Full         | -                         | 35  | 60                     | ns   |

| Time to Shutdown                                    | t <sub>SHDN</sub>                      | ( <u>Note 13</u> )                                                                                       | Full         | 60                        | 160 | 600                    | ns   |

| Driver Enable from Shutdown to Output High          | t <sub>ZH(SHDN)</sub>                  | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>( <u>Figure 6, Notes 13, 14</u> )             | Full         | -                         | -   | 250                    | ns   |

| Driver Enable from Shutdown to Output Low           | t <sub>ZL(SHDN)</sub>                  | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = V <sub>CC</sub><br>( <u>Figure 6, Notes 13, 14</u> ) | Full         | -                         | -   | 250                    | ns   |

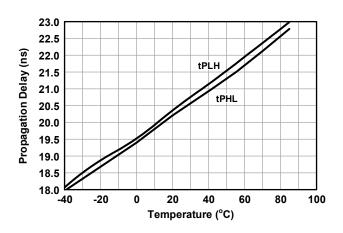

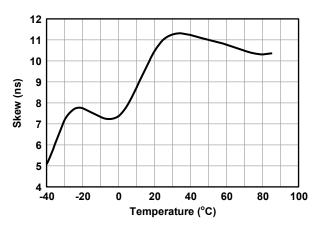

| Driver Switching Characteris                        | stics (20Mb                            | ps Versions; ISL3156E, ISL3158E)                                                                         |              |                           |     |                        |      |

| Driver Differential Output<br>Delay                 | t <sub>PLH,</sub> t <sub>PHL</sub>     | $R_{DIFF} = 54\Omega, C_{L} = 100pF (Figure 5)$                                                          | Full         | -                         | 21  | 30                     | ns   |

| Driver Differential Output<br>Skew                  | t <sub>SKEW</sub>                      | $R_{DIFF} = 54\Omega, C_L = 100pF (Figure 5)$                                                            | Full         | -                         | 0.2 | 3                      | ns   |

| Driver Differential Rise or Fall<br>Time            | t <sub>R</sub> , t <sub>F</sub>        | $R_{DIFF} = 54\Omega, C_{L} = 100pF (Figure 5)$                                                          | Full         | -                         | 12  | 16                     | ns   |

| Maximum Data Rate                                   | f <sub>MAX</sub>                       | C <sub>D</sub> = 470pF ( <u>Figure 7</u> , <u>Note 18</u> )                                              | Full         | 20                        | 55  | -                      | Mbps |

| Driver Enable to Output High                        | t <sub>ZH</sub>                        | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>( <u>Figure 6, Note 11</u> )                  | Full         | -                         | 30  | 45                     | ns   |

| Driver Enable to Output Low                         | t <sub>ZL</sub>                        | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = V <sub>CC</sub><br>( <u>Figure 6, Note 11</u> )      | Full         | -                         | 28  | 45                     | ns   |

| Driver Disable from Output<br>Low                   | t <sub>LZ</sub>                        | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>( <u>Figure 6</u> )                           | Full         | -                         | 50  | 65                     | ns   |

| Driver Disable from Output<br>High                  | t <sub>HZ</sub>                        | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = GND<br>( <u>Figure 6</u> )                                       | Full         | -                         | 38  | 60                     | ns   |

| Time to Shutdown                                    | t <sub>SHDN</sub>                      | ( <u>Note 13</u> )                                                                                       | Full         | 60                        | 160 | 600                    | ns   |

| Driver Enable from Shutdown to Output High          | t <sub>ZH(SHDN)</sub>                  | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>( <u>Figure 6, Notes 13</u> , <u>14</u> )     | Full         | -                         | -   | 200                    | ns   |

| Driver Enable from Shutdown to Output Low           | t <sub>ZL(SHDN)</sub>                  | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = V <sub>CC</sub><br>( <u>Figure 6, Notes 13, 14</u> ) | Full         | -                         | -   | 200                    | ns   |

| Receiver Switching Characte                         | eristics (11                           | 5kbps and 1Mbps Versions; ISL3150E                                                                       | through IS   | SL3155E)                  |     |                        |      |

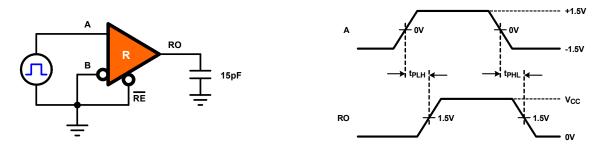

| Maximum Data Rate                                   | f <sub>MAX</sub>                       | ( <u>Figure 8, Note 18</u> )                                                                             | Full         | 1                         | 12  | -                      | Mbps |

| Receiver Input to Output<br>Delay                   | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | (Figure 8)                                                                                               | Full         | -                         | 100 | 150                    | ns   |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub> | t <sub>SKD</sub>                       | ( <u>Figure 8</u> )                                                                                      | Full         | -                         | 4   | 10                     | ns   |

| Parameter                                           | Symbol                                 | Test Conditions                                                                                                   | Temp<br>(°C) | Min<br>( <u>Note 16</u> ) | Тур | Max ( <u>Note 16</u> ) | Unit |

|-----------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|-----|------------------------|------|

| Receiver Enable to Output<br>Low                    | t <sub>ZL</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>(Figure 9, Note 12)                                     | Full         | -                         | 9   | 20                     | ns   |

| Receiver Enable to Output<br>High                   | t <sub>ZH</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND<br>( <u>Figure 9</u> , <u>Note 12</u> )                                | Full         | -                         | 7   | 20                     | ns   |

| Receiver Disable from Output<br>Low                 | t <sub>LZ</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>(Figure 9)                                              | Full         | -                         | 8   | 15                     | ns   |

| Receiver Disable from Output<br>High                | t <sub>HZ</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND<br>(Figure 9)                                                          | Full         | -                         | 8   | 15                     | ns   |

| Time to Shutdown                                    | t <sub>SHDN</sub>                      | ( <u>Note 13</u> )                                                                                                | Full         | 60                        | 160 | 600                    | ns   |

| Receiver Enable from<br>Shutdown to Output High     | t <sub>ZH(SHDN)</sub>                  | R <sub>L</sub> = 1kΩ, C <sub>L</sub> = 15pF, SW = GND<br>( <u>Figure 9, Notes 13, 15</u> )                        | Full         | -                         | -   | 200                    | ns   |

| Receiver Enable from<br>Shutdown to Output Low      | t <sub>ZL(SHDN)</sub>                  | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>( <u>Figure 9</u> , <u>Notes 13</u> , <u>15</u> )       | Full         | -                         | -   | 200                    | ns   |

| Receiver Switching Characte                         | eristics (20                           | Mbps Versions; ISL3156E, ISL3158E)                                                                                | •            |                           |     |                        | •    |

| Maximum Data Rate                                   | f <sub>MAX</sub>                       | ( <u>Figure 8, Note 18</u> )                                                                                      | Full         | 20                        | 30  | -                      | Mbps |

| Receiver Input to Output<br>Delay                   | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | (Figure 8)                                                                                                        | Full         | -                         | 33  | 45                     | ns   |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub> | t <sub>SKD</sub>                       | ( <u>Figure 8</u> )                                                                                               | Full         | -                         | 2.5 | 5                      | ns   |

| Receiver Enable to Output<br>Low                    | t <sub>ZL</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>( <u>Figure 9</u> , <u>Note 12</u> )                    | Full         | -                         | 8   | 15                     | ns   |

| Receiver Enable to Output<br>High                   | t <sub>ZH</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND<br>( <u>Figure 9</u> , <u>Note 12</u> )                                | Full         | -                         | 7   | 15                     | ns   |

| Receiver Disable from Output<br>Low                 | t <sub>LZ</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub><br>( <u>Figure 9</u> )                                     | Full         | -                         | 8   | 15                     | ns   |

| Receiver Disable from Output<br>High                | t <sub>HZ</sub>                        | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND<br>( <u>Figure 9</u> )                                                 | Full         | -                         | 8   | 15                     | ns   |

| Time to Shutdown                                    | t <sub>SHDN</sub>                      | ( <u>Note 13</u> )                                                                                                | Full         | 60                        | 160 | 600                    | ns   |

| Receiver Enable from<br>Shutdown to Output High     | t <sub>ZH(SHDN)</sub>                  | R <sub>L</sub> = 1kΩ, C <sub>L</sub> = 15pF, SW = GND<br>( <u>Figure 9</u> ), ( <u>Notes 13</u> , <u>15</u> )     | Full         | -                         | -   | 200                    | ns   |

| Receiver Enable from<br>Shutdown to Output Low      | t <sub>ZL(SHDN)</sub>                  | R <sub>L</sub> = 1kΩ, C <sub>L</sub> = 15pF, SW = V <sub>CC</sub><br>( <u>Figure 9</u> ), ( <u>Notes 13, 15</u> ) | Full         | -                         | -   | 200                    | ns   |

Test Conditions:  $V_{CC} = 4.5V$  to 5.5V; unless otherwise specified. Typical values are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$  (Note 8). Boldface limits apply across the operating temperature range, -40°C to +85°C. (Continued)

#### Notes:

8. All currents in to device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

9. Supply current specification is valid for loaded drivers when DE = 0V.

- 10. Applies to peak current. See "Performance Curves" beginning on page 14 for more information.

- 11. Keep  $\overline{RE} = 0$  to prevent the device from entering SHDN.

- 12. The  $\overline{\text{RE}}$  signal high time must be short enough (typically <100ns) to prevent the device from entering SHDN.

- 13. Transceivers are put into shutdown by bringing RE high and DE low. If the inputs are in this state for less than 60ns, the parts are guaranteed not to enter shutdown. If the inputs are in this state for at least 600ns, the parts are guaranteed to have entered shutdown. See <u>"Low Current Shutdown Mode" on page 20</u>.

- 14. Keep  $\overline{RE} = V_{CC}$ , and set the DE signal low time >600ns to ensure that the device enters SHDN.

- 15. Set the  $\overline{\text{RE}}$  signal high time >600ns to ensure that the device enters SHDN.

- 16. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

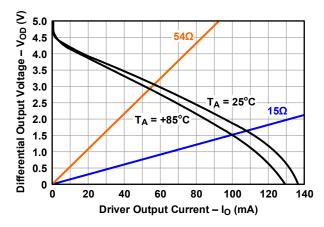

- 17. See Figure 11 on page 14 for more information and for performance over temperature.

- 18. Limits established by characterization and are not production tested.

# 3. Test Circuits and Waveforms

Figure 3. Measurement of Driver Differential Output Voltage with Differential Load

Figure 4. Measurement of Driver Differential Output Voltage with Common-Mode Load

Figure 5. Measurement of Driver Propagation Delay and Differential Transition Times

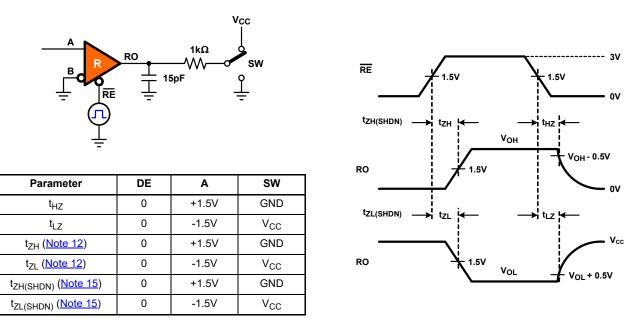

| Parameter             | Output | RE                   | DI  | sw              | C <sub>L</sub><br>(pF) |

|-----------------------|--------|----------------------|-----|-----------------|------------------------|

| t <sub>HZ</sub>       | Y/Z    | Х                    | 1/0 | GND             | 15                     |

| t <sub>LZ</sub>       | Y/Z    | Х                    | 0/1 | V <sub>CC</sub> | 15                     |

| t <sub>ZH</sub>       | Y/Z    | 0 ( <u>Note 11</u> ) | 1/0 | GND             | 100                    |

| t <sub>ZL</sub>       | Y/Z    | 0 ( <u>Note 11</u> ) | 0/1 | $V_{CC}$        | 100                    |

| t <sub>ZH(SHDN)</sub> | Y/Z    | 1 ( <u>Note 14</u> ) | 1/0 | GND             | 100                    |

| t <sub>ZL(SHDN)</sub> | Y/Z    | 1 ( <u>Note 14</u> ) | 0/1 | $V_{CC}$        | 100                    |

Figure 6. Measurement of Driver Enable and Disable Times

Figure 7. Measurement of Driver Data Rate

Figure 8. Measurement of Receiver Propagation Delay and Data Rate

Figure 9. Measurement of Receiver Enable and Disable Times

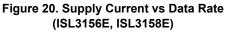

# 4. Performance Curves

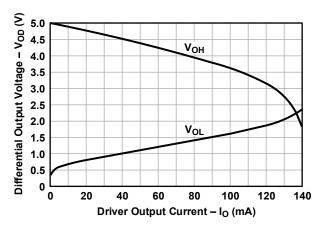

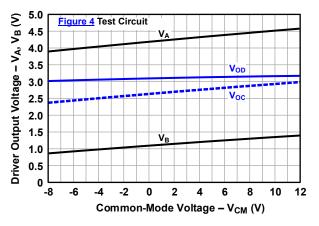

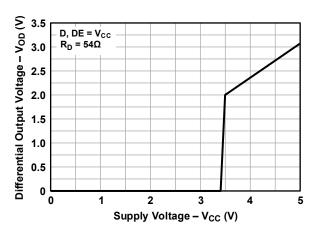

$V_{CC}$  = 5V,  $T_A$  = +25°C; Unless otherwise specified

Figure 10. Driver Output High and Low Voltages vs Output Current

Figure 12. Driver Output Voltages vs Common-Mode Voltage

Figure 14. Driver Output Voltage vs Supply Voltage

Figure 11. Driver Differential Output Voltage vs Output Current

Figure 13. Driver Differential Output Voltage vs Temperature

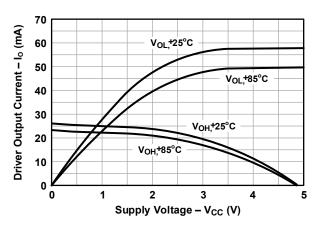

Figure 15. Receiver Output Voltage vs Output Current

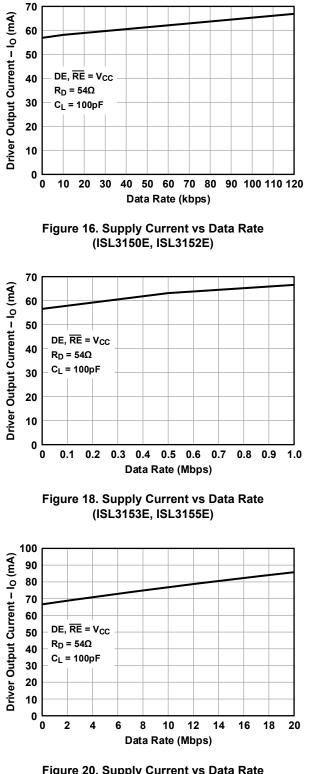

$V_{CC}$  = 5V,  $T_A$  = +25°C; Unless otherwise specified (Continued)

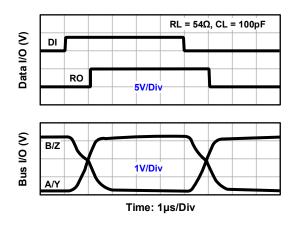

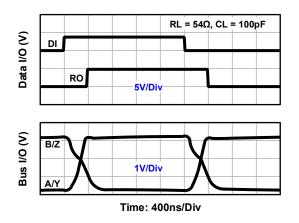

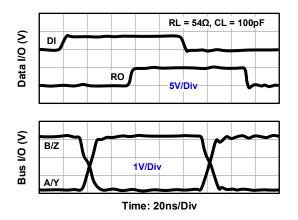

Figure 17. Waveforms (ISL3150E, ISL3152E)

Figure 19. Waveforms (ISL3153E, ISL3155E)

Figure 21. Waveforms (ISL3156E, ISL3158E)

$V_{CC}$  = 5V,  $T_A$  = +25°C; Unless otherwise specified (Continued)

Figure 22. Differential Rise/Fall Times vs Temperature (ISL3150E, ISL3152E)

Figure 24. Differential Rise/Fall Times vs Temperature (ISL3153E, ISL3155E)

Figure 26. Differential Rise/Fall Times vs Temperature (ISL3156E, ISL3158E)

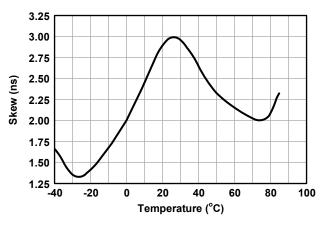

Figure 23. Differential Propagation Delay vs Temperature (ISL3150E, ISL3152E)

Figure 25. Differential Propagation Delay vs Temperature (ISL3153E, ISL3155E)

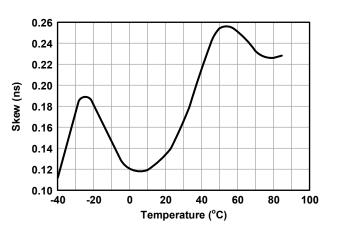

# 5. Device Description

#### 5.1 Overview

The ISL3150E, ISL3153E, and ISL3156E are full-duplex RS-485 transceivers, and the ISL3152E, ISL3155E, and ISL3158E are half-duplex RS-485 transceivers. All transceivers feature a large output signal swing that is 60% higher than standard compliant transceivers. The devices are available in three speed grades suitable for data transmission up to 115kbps, 1Mbps, and 20Mbps.

Each transceiver has an active-high driver enable and an active-low receiver enable function. A shutdown current as low as 70nA can be accomplished by disabling both the driver and receiver for more than 600ns.

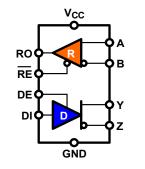

#### 5.2 Functional Block Diagram

Figure 28. Block Diagram ISL3150E, ISL3153E, ISL3156E

Figure 29. Block Diagram ISL3152E, ISL3155E, ISL3158E

## 5.3 Operating Modes

#### 5.3.1 Driver Operation

A logic high at the driver enable pin, DE, activates the driver and causes the differential driver outputs, Y and Z, to follow the logic states at the data input, DI.

A logic high at DI causes Y to turn high and Z to turn low. In this case, the differential output voltage, defined as  $V_{OD} = V_Y - V_Z$ , is positive. A logic low at DI reverses the output states reverse, turning Y low and Z high, thus making  $V_{OD}$  negative.

A logic low at DE disables the driver, making Y and Z high-impedance. In this condition the logic state at DI is irrelevant. To ensure the driver remains disabled after device power-up, it is recommended to connect DE through a  $1k\Omega$  to  $10k\Omega$  pull-down resistor to ground.

|                                                                 |         |    | -      |    |    |

|-----------------------------------------------------------------|---------|----|--------|----|----|

|                                                                 | Outputs |    | Inputs |    |    |

| Function                                                        | Z       | Y  | DI     | DE | RE |

| Actively drives bus high                                        | L       | Н  | Н      | Н  | Х  |

| Actively drives bus low                                         | Н       | L  | L      | Н  | Х  |

| Driver disabled, outputs high-impedance                         | Z       | Z  | х      | L  | L  |

| Shutdown mode: driver and receiver disabled for more than 600ns | Z*      | Z* | Х      | L  | Н  |

Table 2. Driver Truth Table

Note:\* See Shutdown mode explanation in "Low Current Shutdown Mode" on page 20.

#### 5.3.2 Receiver Operation

A logic low at the receiver enable pin,  $\overline{\text{RE}}$ , activates the receiver and causes its output, RO, to follow the bus voltage at the differential receiver inputs, A and B. Here, the bus voltage is defined as  $V_{AB} = V_A - V_B$ .

For  $V_{AB} \ge -0.05V$ , RO turns high, and for  $V_{AB} \le -0.2V$ , RO turns low. For input voltages between -50mV and -200mV, the state of RO is undetermined, and thus could be high or low.

A logic high at  $\overline{\text{RE}}$  disables the receiver, making RO high-impedance. In this condition the polarity and magnitude of the input voltage is irrelevant. To ensure the receiver output remains high when the receiver is disabled, it is recommended to connect RO, using a 1k $\Omega$  to 10k $\Omega$  pull-up resistor to V<sub>CC</sub>.

To enable the receiver to immediately monitor the bus traffic after device power-up, connect  $\overline{\text{RE}}$  through a 1k $\Omega$  to 10k $\Omega$  pull-down resistor to ground.

| Inputs |    | Inputs                           |              |                                                                 |

|--------|----|----------------------------------|--------------|-----------------------------------------------------------------|

| RE     | DE | A – B                            | RO           | Function                                                        |

| L      | Х  | V <sub>AB</sub> ≥ -0.05V         | Н            | RO is data-driven high                                          |

| L      | Х  | -0.05V > V <sub>AB</sub> > -0.2V | Undetermined | Actively drives bus low                                         |

| L      | Х  | $V_{AB} \le -0.2V$               | L            | RO is data-driven low                                           |

| L      | Х  | Inputs Open/Shorted              | Н            | RO is failsafe-high                                             |

| Н      | Н  | Х                                | Z            | Receiver disabled, RO is high-impedance                         |

| Н      | L  | Х                                | Z*           | Shutdown mode: driver and receiver disabled for more than 600ns |

Table 3. Receiver Truth Table

Note:\* See Shutdown mode explanation in "Low Current Shutdown Mode" on page 20.

## 5.4 Device Features

## 5.4.1 Large Output Signal Swing

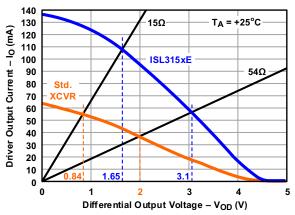

The ISL315xE family has a 60% larger differential output voltage swing than standard RS-485 transceivers. It delivers a minimum  $V_{OD}$  of 2.4V across a 54 $\Omega$  differential load, or 1.65V across a 15 $\Omega$  differential load. Figure 30 shows that the  $V_{OD}$  at 54 $\Omega$  is more than 50% higher than that of a standard transceiver.

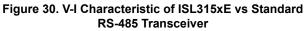

Figure 31. Unit Load and Transceiver Drive of ISL315xE vs Standard RS-485 Transceiver

<u>Figure 31</u> compares the maximum number of unit loads and bus transceivers when choosing an ISL315xE over a standard transceiver. The RS-485 standard specifies a minimum total common-mode load resistance of  $R_{CM} = 375\Omega$  between each signal conductor and ground. Because one unit load (1UL) is equivalent to  $12k\Omega$ , the total common-mode resistance of  $375\Omega$  yields  $12k\Omega/375\Omega = 32$  ULs.

For an ISL315xE transceiver however,  $R_{CM}$  can be as small as 188 $\Omega$ , resulting in a total common-mode load of  $12k\Omega/188\Omega = 64$  ULs. This means the driver of an ISL315xE transceiver can drive up to 64 x 1UL transceivers or 512 x 1/8UL transceivers.

The advantages of such superior drive capability are:

- Up to 900mV higher noise immunity (2.4V vs 1.5V V<sub>OD</sub>)

- Up to twice the maximum cable length of standard transceivers (~8000ft vs 4000ft)

- The design of star configurations or other multi-terminated nonstandard network topologies

#### 5.4.2 Driver Overload Protection

The RS-485 specification requires drivers to survive worst case bus contentions undamaged. The ISL315xE transceivers meet this requirement through driver output short circuit current limits and on-chip thermal shutdown circuitry.

The driver output stages incorporate short-circuit current limiters that ensure that the output current never exceeds the RS-485 specification, even at the common-mode voltage range extremes.

In the event of a major short-circuit conditions, the devices also include a thermal shutdown feature that disables the drivers whenever the temperature becomes excessive. This eliminates the power dissipation, allowing the die to cool. The drivers automatically re-enable after the die temperature drops about 15°C. If the contention persists, the thermal shutdown/re-enable cycle repeats until the fault is cleared. The receivers stay operational during thermal shutdown.

#### 5.4.3 Full-Failsafe Receiver

The differential receivers of the ISL315xE family are full-failsafe, meaning their outputs turn logic high when:

- The receiver inputs are open (floating) due to a faulty bus node connector

- The receiver inputs are shorted due to an insulation break of the bus cable

- The receiver input voltage is close to 0V due to a terminated bus not being actively driven

Full-failsafe switching is accomplished by offsetting the maximum receiver input threshold to -50mV. Figure 32 shows that, in addition to the threshold offset, the receiver also has an input hysteresis,  $\Delta V_{TH}$ , of 20mV. The combination of offset and hysteresis allows the receiver to maintain its output high, even in the presence of 140mV<sub>P-P</sub> differential noise, without the need for external failsafe biasing resistors.

Figure 32. Full-Failsafe Performance with High Noise Immunity

## 5.4.4 Low Current Shutdown Mode

The ISL315xE transceivers use a fraction of the power required by their bipolar counterparts, but also include a shutdown feature that reduces the already low quiescent  $I_{CC}$  to a 70nA trickle. These devices enter shutdown whenever the receiver and the driver are simultaneously disabled ( $\overline{RE} = V_{CC}$  and DE = GND) for a period of at least 600ns. Disabling both the driver and the receiver for less than 60ns guarantees that the transceiver will not enter shutdown.

Note that driver and receiver enable times increase when the transceiver enables from shutdown. Refer to Notes 10 to 14 at the end of "Electrical Specifications" on page 10.

## 5.4.5 Hot Plug Function

When the equipment powers up, there is a period of time where the controller driving the RS-485 enable lines is unable to ensure that the driver and receiver outputs are kept disabled. If the equipment is connected to the bus, a driver activating prematurely during power-up may crash the bus. To avoid this scenario, the ISL315xE devices incorporate a Hot Plug function. During power-up and power-down, the Hot Plug function disables the driver and receiver outputs regardless of the states of DE and  $\overline{RE}$ . When V<sub>CC</sub> reaches ~3.4V, the enable pins are released. This gives the controller the chance to stabilize and drive the RS-485 enable lines to the proper states.

## 5.4.6 High ESD Protection

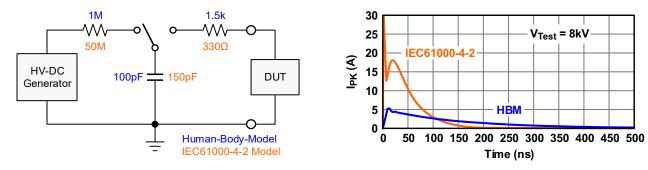

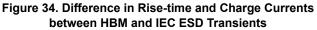

The bus pins of the ISL315xE transceivers have on-chip ESD protection against  $\pm 16.5$ kV HBM, and  $\pm 9$ kV contact and  $\pm 16.5$ kV air-discharge according to IEC61000-4-2. The difference between the HBM and IEC ESD ratings lies in the test severity, as both standards aim for different application environments.

HBM ESD ratings are component level ratings, used in semiconductor manufacturing in which component handling can cause ESD damage to a single device. Because component handling is performed in a controlled ESD environment, the ESD stress upon a component is drastically reduced. These factors make the HBM test the less severe ESD test.

IEC ESD ratings are system level ratings. These are required in the uncontrolled field environment, where for example, a charged end user can subject handheld equipment to ESD levels of more than 40kV by touching connector pins when plugging or unplugging cables.

The main differences between the HBM and the IEC 61000-4-2 standards are the number of strikes applied during testing and the generator models (Figure 33), which create differences in the waveforms' rise times and peak currents (Figure 34).

Figure 33. Generator Models for HBM and IEC ESD Tests

The IEC model has 50% higher charge capacitance ( $C_S$ ) and 78% lower discharge resistance ( $R_D$ ) than the HBM model, thus producing shorter transient rise times and higher discharge currents. The ESD ratings of the ISL315xE transceivers exceed test level 4 of the IEC61000-4-2 standard, which significantly increases equipment robustness.

# 6. Application Information

#### 6.1 Network Design

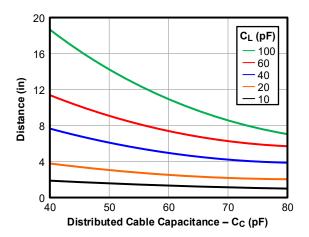

Designing a reliable RS-485 network requires the consideration of a variety of factors that ultimately determine the network performance. These include network topology, cable type, data rate and/or cable length, stub length, distance between network nodes, and line termination.

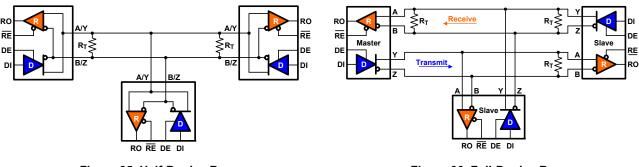

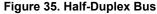

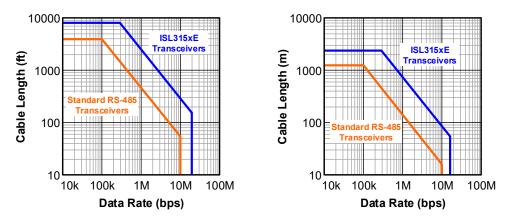

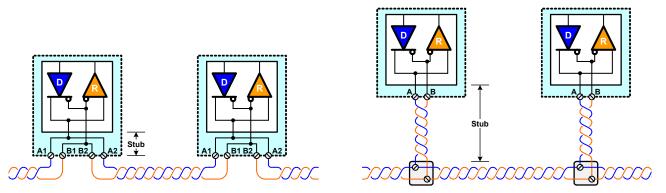

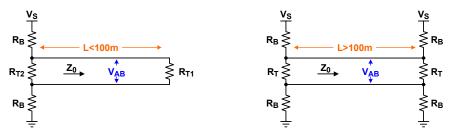

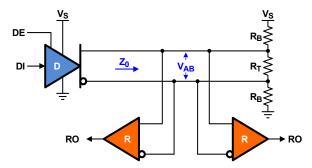

The main difference between network designs is dictated by their modes of data exchange between bus nodes, which can be half-duplex or full-duplex (Figures 35 and 36).

Figure 36. Full-Duplex Bus

**Half-duplex networks** use only a single signal-pair of cables between one master node and multiple slave nodes, which allows the nodes to either transmit or receive data, but never both at the same time. Its reduced cabling effort makes these networks well suited for covering long distances of up to several thousands of feet. To maintain high signal integrity, the applied data rates range from as low as 9.6kbps up to 115kbps. This requires transceivers with long driver output transition times, typically in the range of microseconds, to ensure low EMI in the presence of large cable inductances.

To prevent signal reflections of the bus lines, each cable end must be terminated with a resistor,  $R_T$ , whose value should match the characteristic cable impedance,  $Z_0$ .

**Full-duplex networks**, on the other hand, aim for high data throughput. These networks use two signal-pairs to support the simultaneous transmitting and receiving of data. The signal pair denoted as the transmit path connects the driver output of the master node to the receiver inputs of multiple slave nodes. The other pair connects the driver outputs of the slave nodes with the receiver input of the master node.