### SiM3U1xx/SiM3C1xx Reference Manual

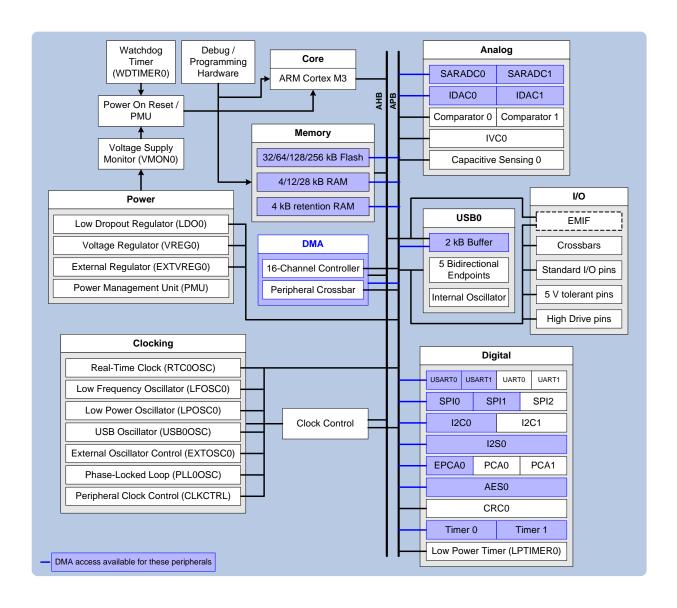

This reference manual accompanies several documents to provide the complete description of SiM3U1xx/SiM3C1xx devices, part of the Silicon Laboratories 32-bit ARM Cortex-M3 family of microcontrollers.

This document provides the detailed description for all peripherals available on all SiM3U1xx/SiM3C1xx devices. The peripheral mix varies across different members of the device families. Refer to the device data sheet for details on the specific peripherals available for each member of the device family. In the event that the device data sheet and this document contain conflicting information, the device data sheet should be considered the authoritative source.

## **Table of Contents**

| 1. | Related Documents and Conventions                                               |    |

|----|---------------------------------------------------------------------------------|----|

|    | 1.1. Related Documents                                                          | 11 |

|    | 1.2. Conventions                                                                |    |

| 2. | Memory Organization                                                             | 12 |

|    | 2.1. Flash Region                                                               | 13 |

|    | 2.2. RAM Region                                                                 | 14 |

|    | 2.3. Peripheral Region                                                          | 15 |

|    | 2.4. External Memory                                                            | 16 |

|    | 2.5. Cortex-M3 Internal Peripherals                                             | 16 |

| 3. | SiM3U1xx/SiM3C1xx Register Memory Map                                           | 17 |

| 4. | Interrupts                                                                      |    |

|    | 4.1. System Exceptions                                                          |    |

|    | 4.2. Interrupt Vector Table                                                     | 35 |

|    | 4.3. Priorities                                                                 |    |

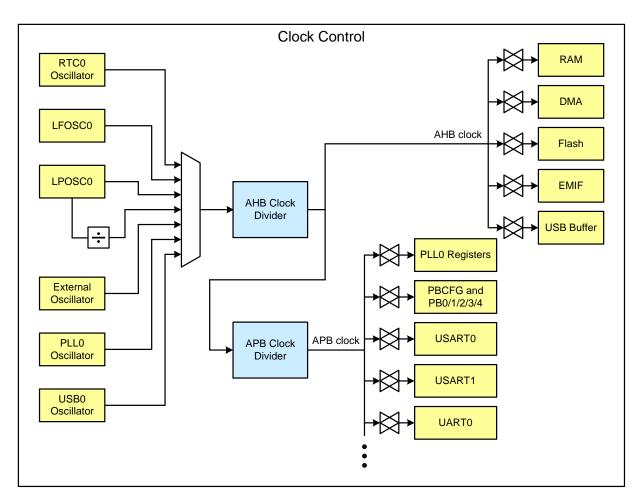

| 5. | Clock Control (CLKCTRL0)                                                        | 43 |

|    | 5.1. Clock Control Features                                                     | 43 |

|    | 5.2. CLKCTRL0 Registers                                                         | 45 |

|    | 5.3. CLKCTRL0 Register Memory Map                                               |    |

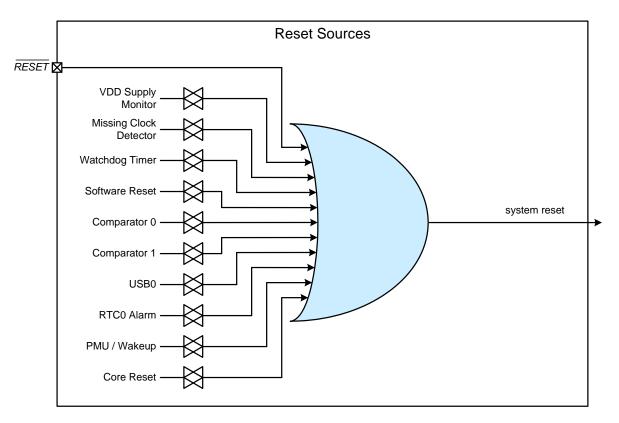

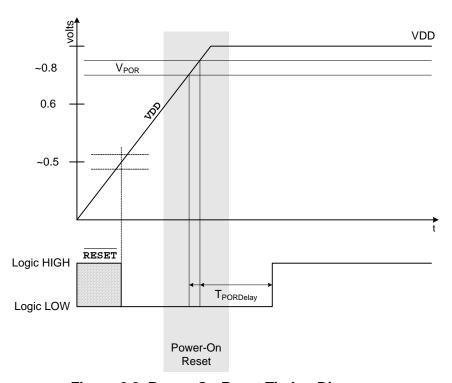

| 6. | Reset Sources (RSTSRC0)                                                         | 55 |

|    | 6.1. Reset Sources Features                                                     |    |

|    | 6.2. RSTSRC0 Registers                                                          |    |

|    | 6.3. RSTSRC0 Register Memory Map                                                |    |

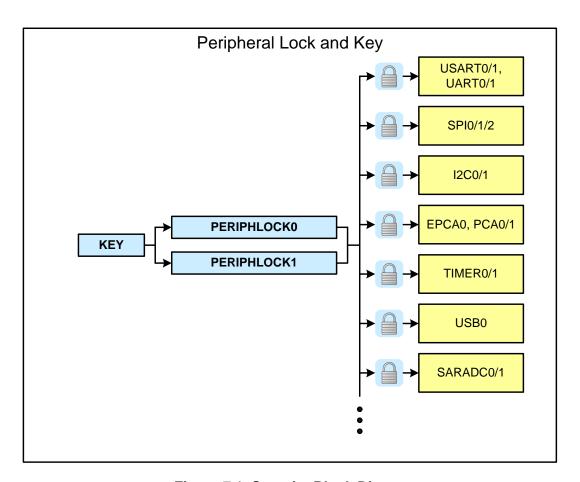

| 7. | Register Security (LOCK0)                                                       |    |

|    | 7.1. Security Features                                                          |    |

|    | 7.2. LOCK0 Registers                                                            |    |

|    | 7.3. LOCK0 Register Memory Map                                                  |    |

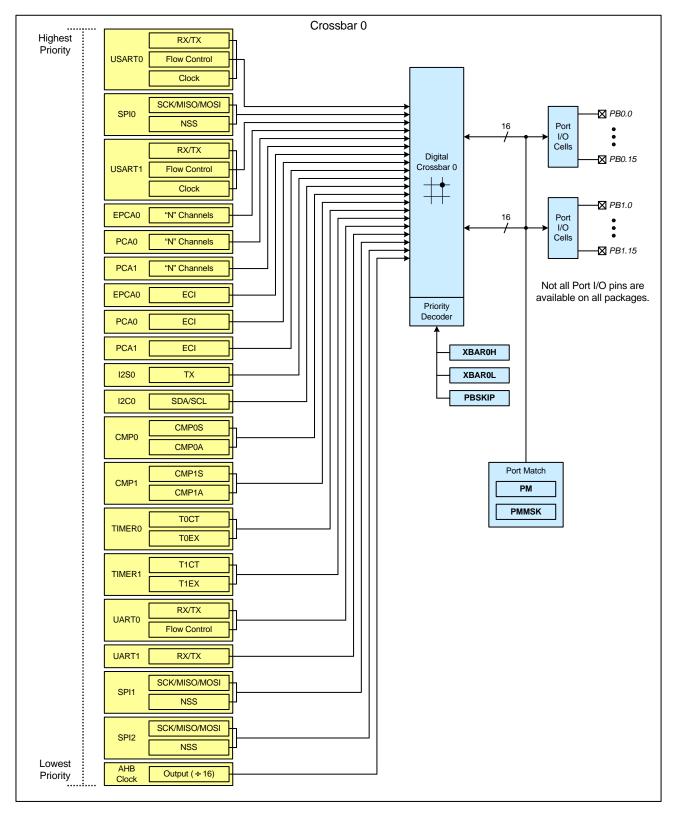

| 8. | Port I/O Configuration                                                          |    |

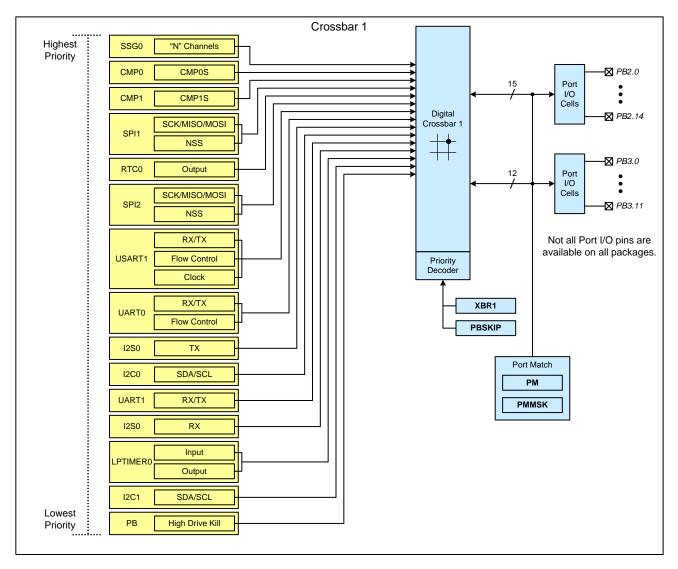

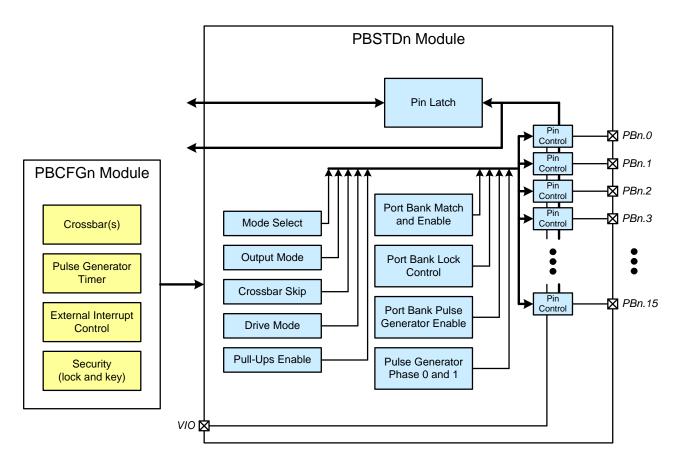

|    | 8.1. Port Bank Description                                                      |    |

|    | 8.2. Crossbars                                                                  |    |

|    | 8.3. Port Bank Standard (PBSTD) Features                                        |    |

|    | 8.4. Standard Modes of Operation                                                |    |

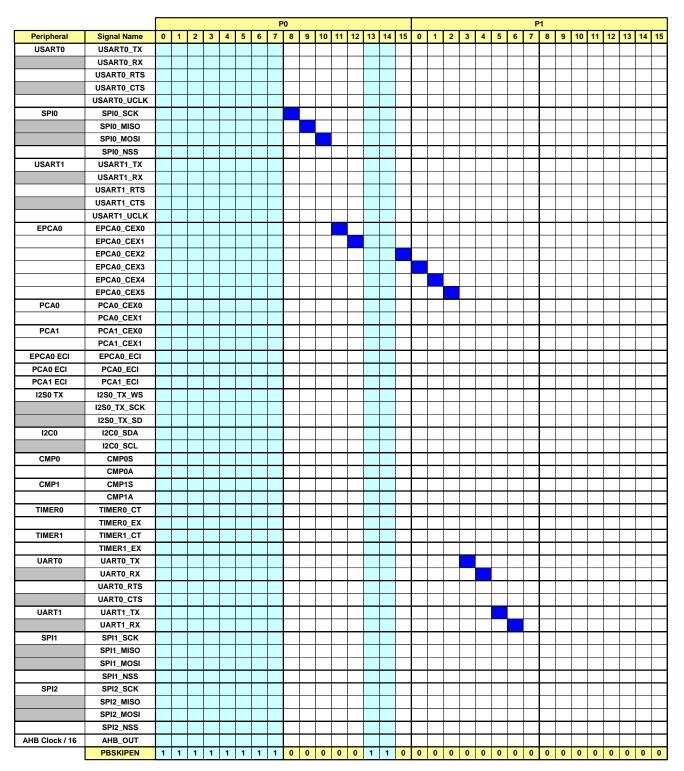

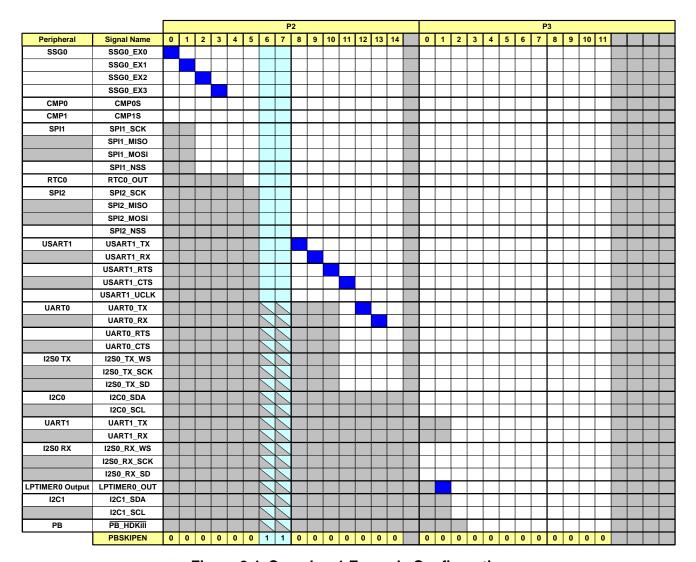

|    | 8.5. Assigning Standard Port Bank Pins to Analog and Digital Functions          | 86 |

|    | 8.6. Standard Port Match and Capacitive Sensing (CAPSENSE0) Activity Monitoring |    |

|    | 8.7. Standard Port Bank Pulse Generator                                         |    |

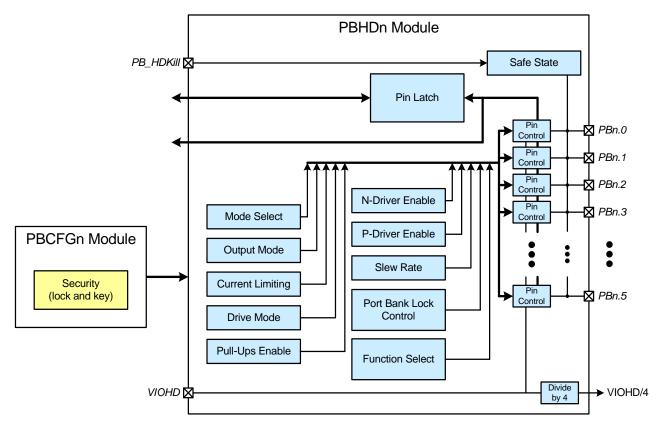

|    | 8.8. High Drive (PBHD) Features                                                 |    |

|    | 8.9. High Drive Modes of Operation                                              |    |

|    | 8.10.High Drive Configuration Procedure                                         |    |

|    | 8.11.High Drive Function Selection                                              |    |

|    | 8.12.Port Bank Security                                                         |    |

|    | 8.13.Ports and Power Mode 9                                                     |    |

|    | 8.14.Debugging Interfaces                                                       |    |

|    | 8.15.External Memory Interface (EMIF)                                           |    |

|    | 8.16.External Interrupts                                                        |    |

|    | 8.17.PBCFG0 Registers                                                           | 99 |

|     | 8.18.PBCFG0 Register Memory Map                                     | 11       | 12       |

|-----|---------------------------------------------------------------------|----------|----------|

|     | 8.19.PBSTD0, PBSTD1, PBSTD2, and PBSTD3 Registers                   |          |          |

|     | 8.20.PBSTDn Register Memory Map                                     |          |          |

|     | 8.21.PBHD4 Registers                                                |          |          |

|     | 8.22.PBHD4 Register Memory Map                                      |          |          |

| 9.  | Power                                                               |          |          |

| •   | 9.1. Power Modes                                                    |          |          |

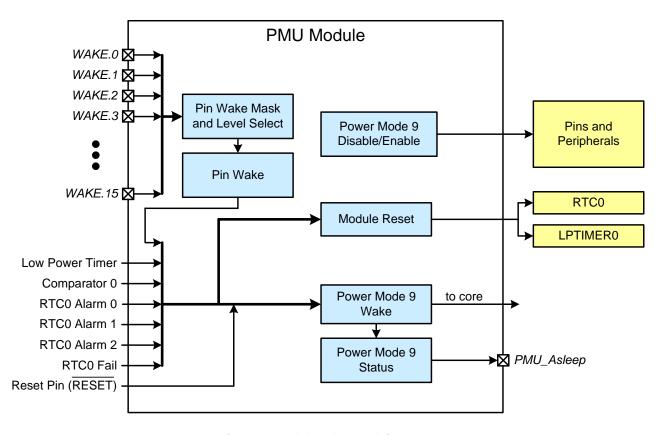

|     | 9.2. Power Management Unit (PMU0)                                   |          |          |

|     | 9.3. PMU0 Registers                                                 |          |          |

|     | 9.4. PMU0 Register Memory Map                                       |          |          |

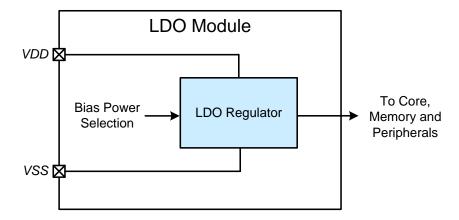

| 10  | .Core Voltage Regulator (LDO0)                                      |          |          |

|     | 10.1.Core Voltage Regulator Features                                |          |          |

|     | 10.2.Functional Description                                         |          |          |

|     | 10.3.LDO0 Registers                                                 |          |          |

|     | 10.4.LDO0 Register Memory Map                                       |          |          |

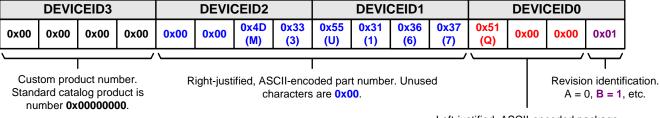

| 11  | Device Identification (DEVICEID0) and Universally Unique Identifier | 16       | ,<br>32  |

| • • | 11.1.Device ID Features                                             |          |          |

|     | 11.2.Universally Unique Identifier (UUID)                           |          |          |

|     | 11.3.DEVICEID0 Registers                                            |          |          |

|     | 11.4.DEVICEID0 Register Memory Map                                  |          |          |

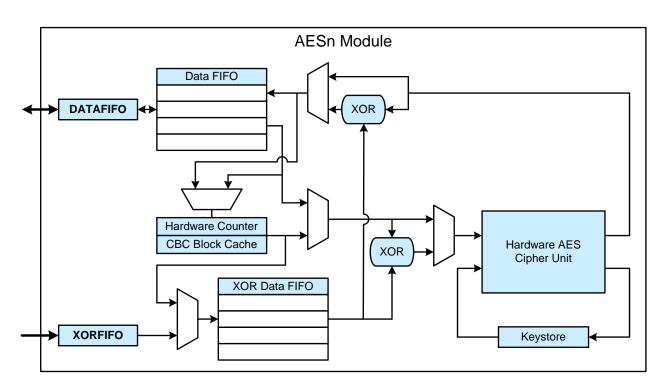

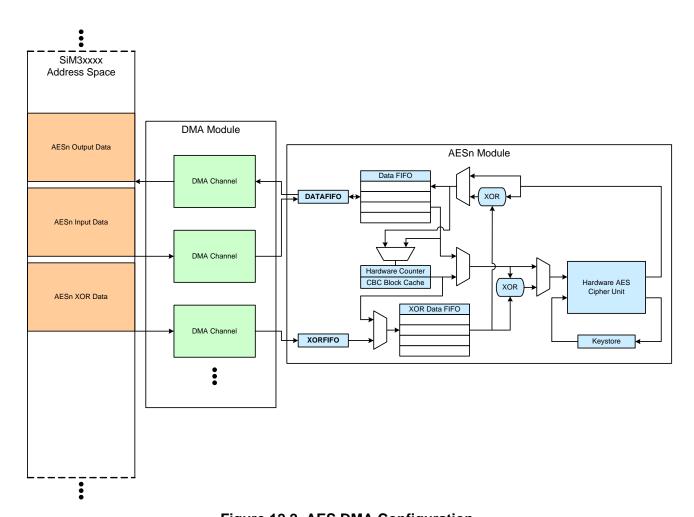

| 12  | Advanced Encryption Standard (AES0)                                 | 16       | ),<br>30 |

| 12  | 12.1.AES Features                                                   |          |          |

|     | 12.2.Overview                                                       |          |          |

|     | 12.3.Interrupts                                                     |          |          |

|     | 12.4.Debug Mode                                                     |          |          |

|     | 12.5.DMA Configuration and Usage                                    |          |          |

|     | 12.6.Using the AES0 Module for Electronic Codebook (ECB)            |          |          |

|     | 12.7.Using the AES0 Module for Cipher Block Chaining (CBC)          |          |          |

|     | 12.8.Using the AES0 Module for Counter (CTR)                        |          |          |

|     | 12.9.Performing "In-Place" Ciphers                                  |          |          |

|     | 12.10.Using the AES0 Module in Software Mode                        | 15       | ,U<br>27 |

|     | 12.11.AES0 Registers                                                |          |          |

|     | 12.12.AES0 Register Memory Map                                      |          |          |

| 12  | Capacitive Sensing (CAPSENSE0)                                      |          |          |

| 13  | 13.1.Capacitive Sensing Features                                    |          |          |

|     | 13.2.Overview                                                       |          |          |

|     | 13.3.Measurement Overview                                           | 21       | 10       |

|     | 13.4.Conversion and Input Modes                                     |          |          |

|     | 13.5.Conversion Rate                                                |          |          |

|     | 13.6.Accumulation Modes                                             |          |          |

|     | 13.7.Measuring Multiple Channels in a Single Measurement            |          |          |

|     |                                                                     |          |          |

|     | 13.8.Pin Monitoring                                                 |          |          |

|     | 13.9.Compare Threshold                                              |          |          |

|     | 13.10.Interrupts                                                    |          |          |

|     | 13.11.Additional Options                                            |          |          |

|     | 13.12.Taking a Measurement                                          | <b>∠</b> | ı        |

| 13.13.CAPSENSE0 Registers                        | 220 |

|--------------------------------------------------|-----|

| 13.14.CAPSENSE0 Register Memory Map              | 230 |

| 14. Comparator (CMP0 and CMP1)                   |     |

| 14.1.Comparator Features                         |     |

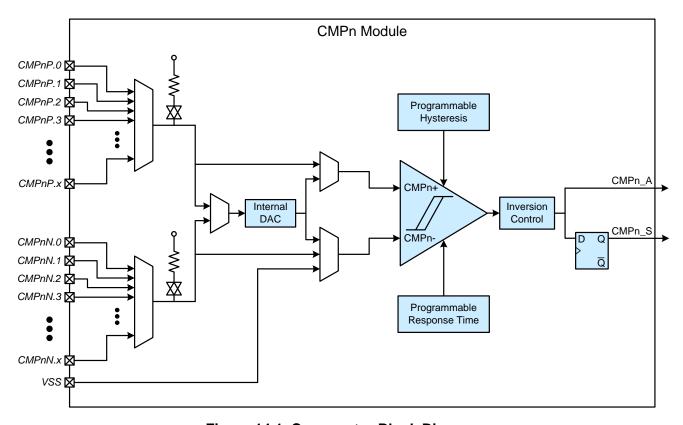

| 14.2.Overview                                    | 233 |

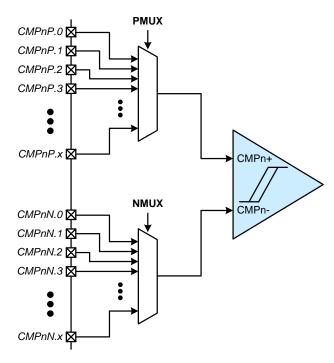

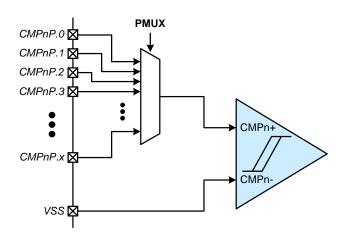

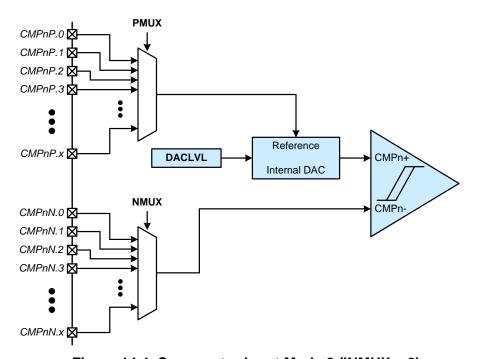

| 14.3.Inputs                                      | 233 |

| 14.4.Outputs                                     |     |

| 14.5.Response Time                               | 240 |

| 14.6.Hysteresis                                  | 240 |

| 14.7.Interrupts and Flags                        | 240 |

| 14.8.CMP0 and CMP1 Registers                     |     |

| 14.9.CMPn Register Memory Map                    | 246 |

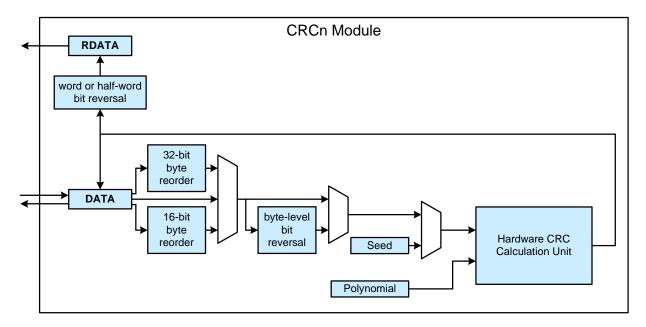

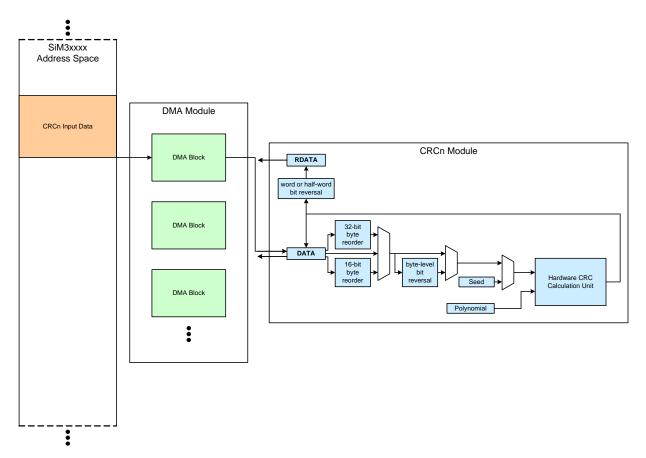

| 15. Cyclic Redundancy Check (CRC0)               | 247 |

| 15.1.CRC Features                                |     |

| 15.2.Overview                                    | 248 |

| 15.3.Interrupts                                  | 248 |

| 15.4.DMA Configuration and Usage                 | 248 |

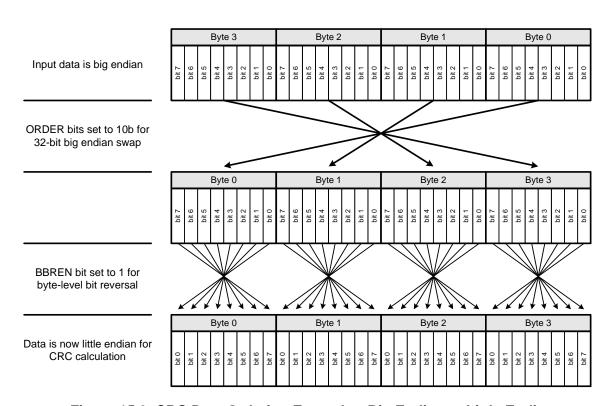

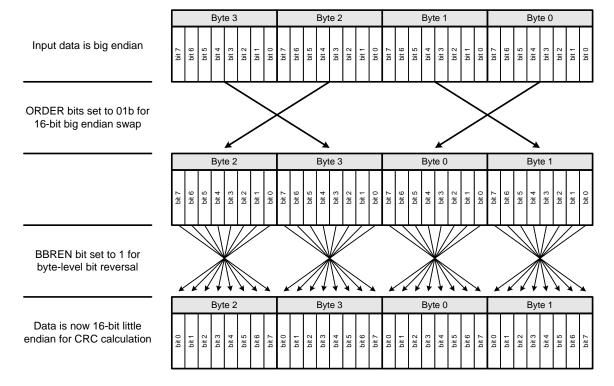

| 15.5.Byte-Level Bit Reversal and Byte Reordering | 249 |

| 15.6.CRC0 Registers                              | 252 |

| 15.7.CRC0 Register Memory Map                    | 256 |

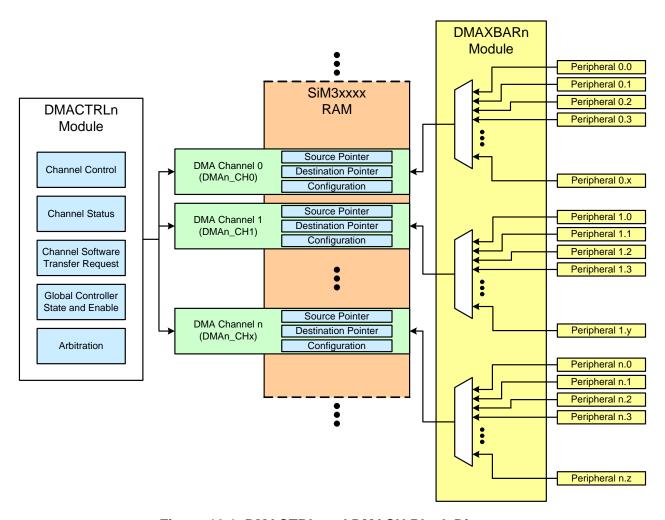

| 16. DMA Controller (DMACTRL0)                    | 257 |

| 16.1.DMA Controller Features                     | 257 |

| 16.2.Overview                                    | 259 |

| 16.3.Interrupts                                  | 259 |

| 16.4.Configuring a DMA Channel                   | 259 |

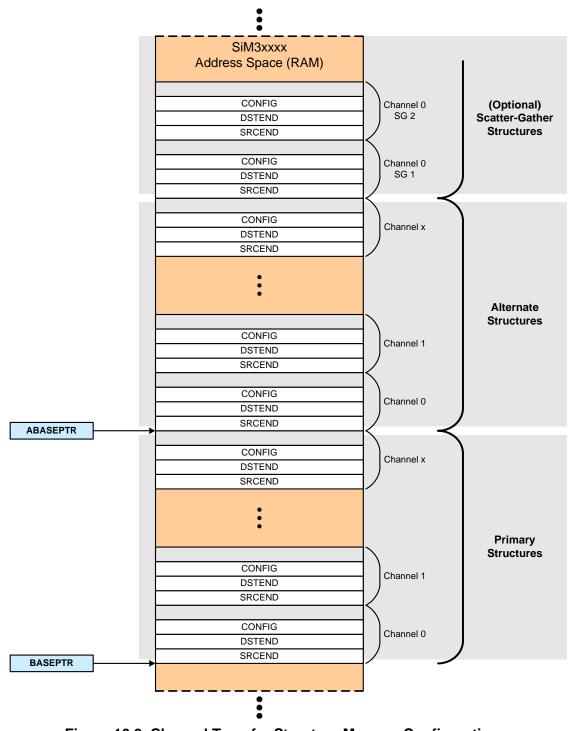

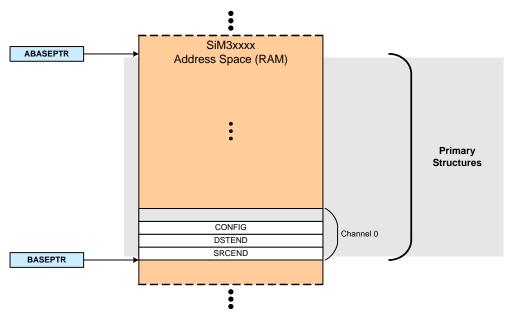

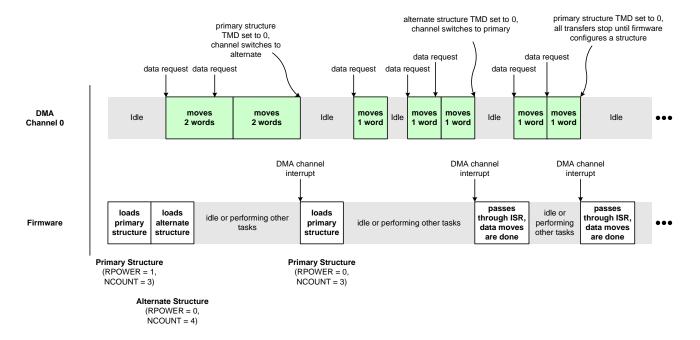

| 16.5.DMA Channel Transfer Structures             | 260 |

| 16.6.Transfer Types                              |     |

| 16.7.Data Requests                               |     |

| 16.8.Masking Channels                            | 273 |

| 16.9.Errors                                      | 273 |

| 16.10.Arbitration                                | 274 |

| 16.11.DMACTRL0 Registers                         |     |

| 16.12.DMACTRL0 Register Memory Map               |     |

| 17. DMA Crossbar (DMAXBAR0)                      |     |

| 17.1.DMA Crossbar Features                       |     |

| 17.2.Channel Priority                            |     |

| 17.3.DMAXBAR0 Registers                          |     |

| 17.4.DMAXBAR0 Register Memory Map                |     |

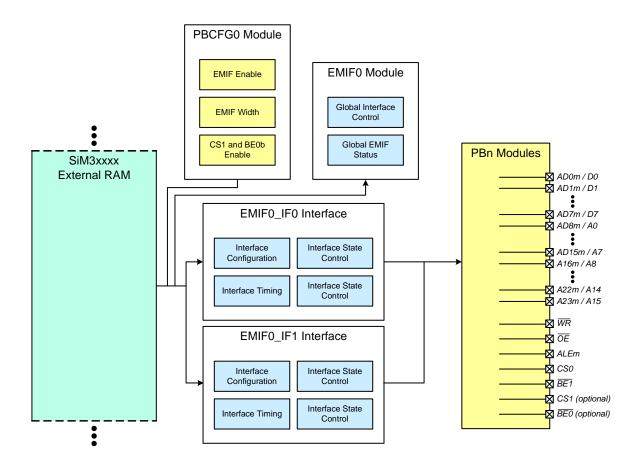

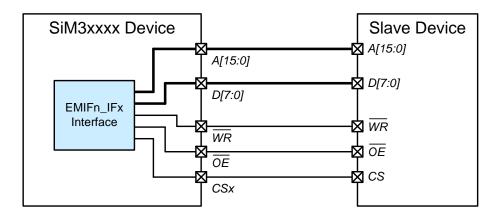

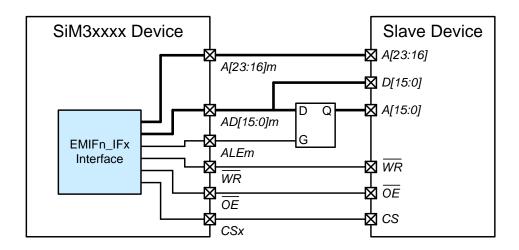

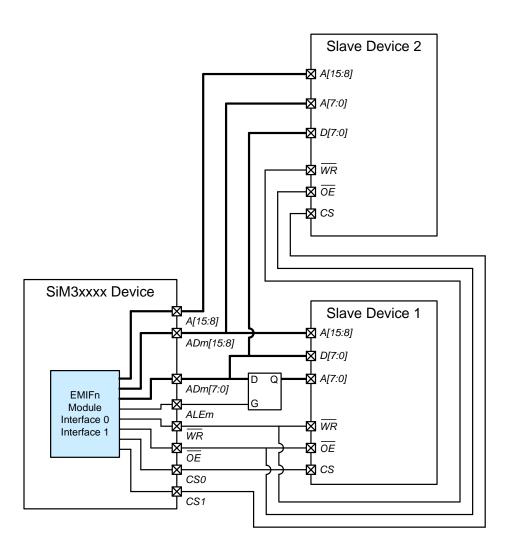

| 18. External Memory Interface (EMIF0)            |     |

| 18.1.EMIF Features                               |     |

| 18.2.Overview                                    |     |

| 18.3.Signal Descriptions                         |     |

| 18.4.Memory Interface                            |     |

| 18.5.Non-Multiplexed Output Mode                 |     |

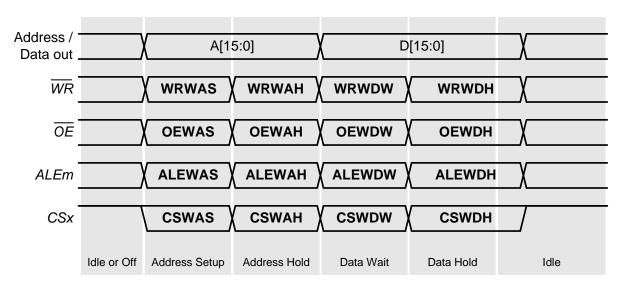

| 18.6.Multiplexed Output Mode                     |     |

| 18.7.Mixing Configurations                       | 331 |

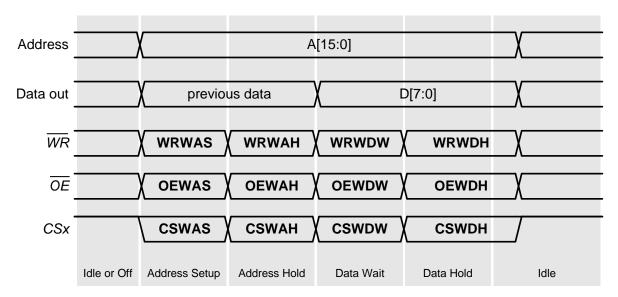

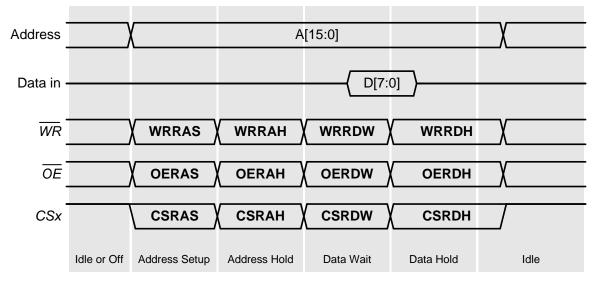

|    | 18.8.Transaction Timing                         | 332 |

|----|-------------------------------------------------|-----|

|    | 18.9.Idle and Off States                        |     |

|    | 18.10.Additional Features                       | 334 |

|    | 18.11.Configuring the External Memory Interface | 334 |

|    | 18.12.EMIF0 Registers                           |     |

|    | 18.13.EMIF0 Register Memory Map                 |     |

|    | 18.14.EMIF0_IFx Registers                       |     |

|    | 18.15.EMIFn_IFx Register Memory Map             | 348 |

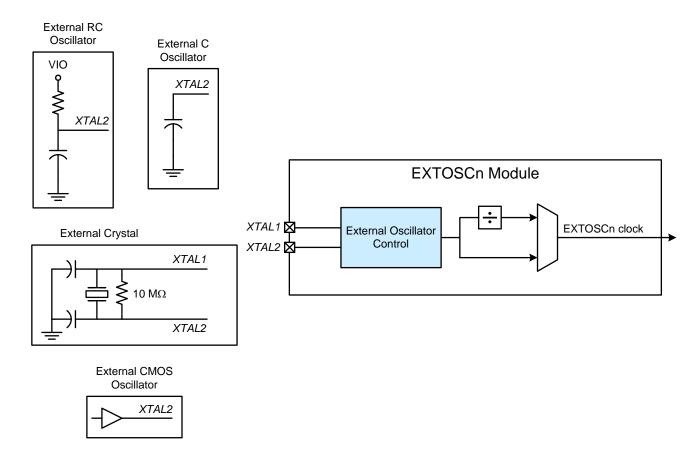

| 19 | . External Oscillator (EXTOSC0)                 |     |

|    | 19.1.External Oscillator Features               |     |

|    | 19.2.Introduction                               | 351 |

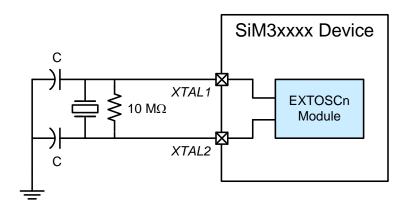

|    | 19.3.External Crystal Oscillator                | 351 |

|    | 19.4.External CMOS Oscillator                   |     |

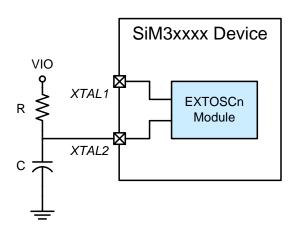

|    | 19.5.External RC Oscillator                     | 353 |

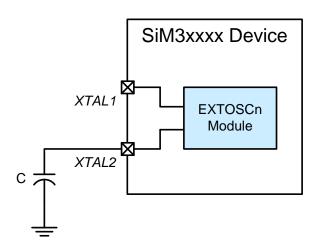

|    | 19.6.External C Oscillator                      | 355 |

|    | 19.7.EXTOSC0 Registers                          | 357 |

|    | 19.8.EXTOSC0 Register Memory Map                | 359 |

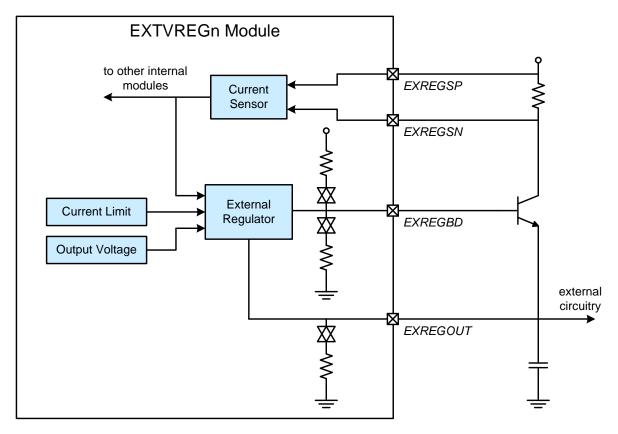

| 20 | .External Regulator (EXTVREG0)                  |     |

|    | 20.1.External Regulator Features                |     |

|    | 20.2.Overview                                   | 361 |

|    | 20.3.Operating Modes                            | 361 |

|    | 20.4.Current Sensing                            | 363 |

|    | 20.5.Current Limiting                           | 365 |

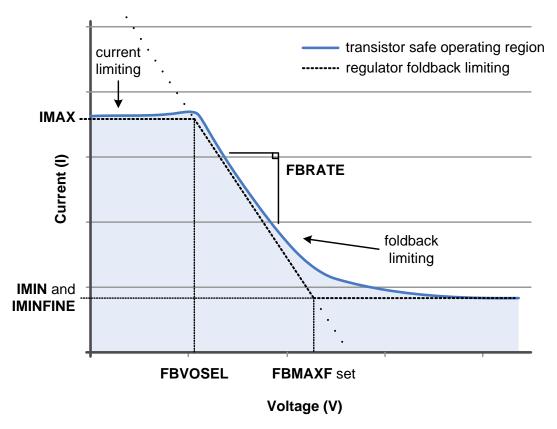

|    | 20.6.Foldback Limiting                          |     |

|    | 20.7.Regulator Stability                        |     |

|    | 20.8.Configuring the External Regulator         | 368 |

|    | 20.9.EXTVREGO Registers                         |     |

|    | 20.10.EXTVREG0 Register Memory Map              |     |

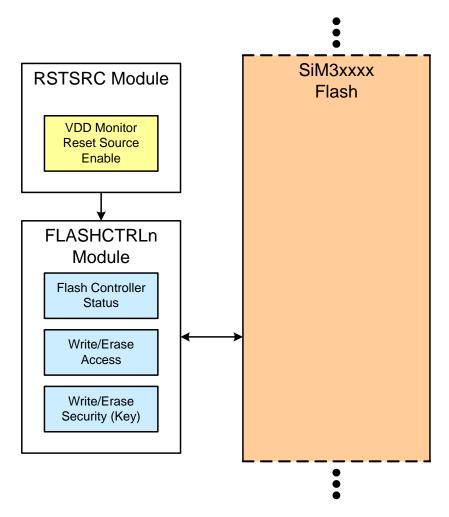

| 21 | .Flash Controller (FLÄSHCTRL0)                  |     |

|    | 21.1.Flash Controller Features                  |     |

|    | 21.2.Overview                                   | 379 |

|    | 21.3.Flash Read Control                         | 379 |

|    | 21.4.Flash Write and Erase Control              | 380 |

|    | 21.5.FLASHCTRL0 Registers                       |     |

|    | 21.6.FLASHCTRL0 Register Memory Map             |     |

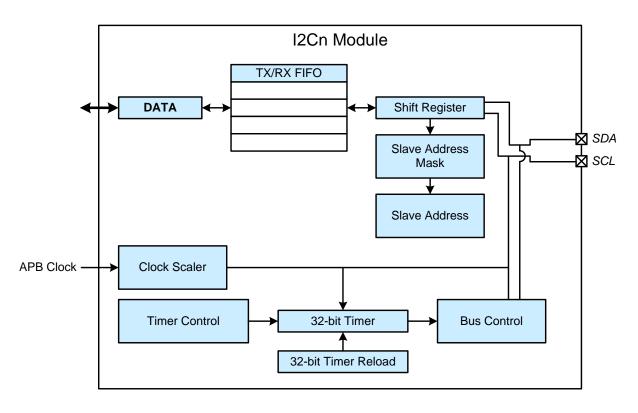

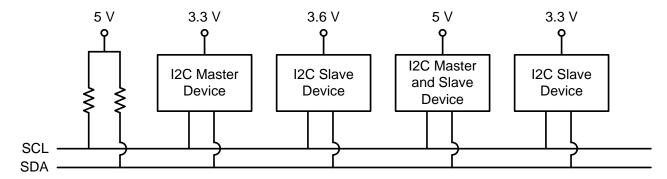

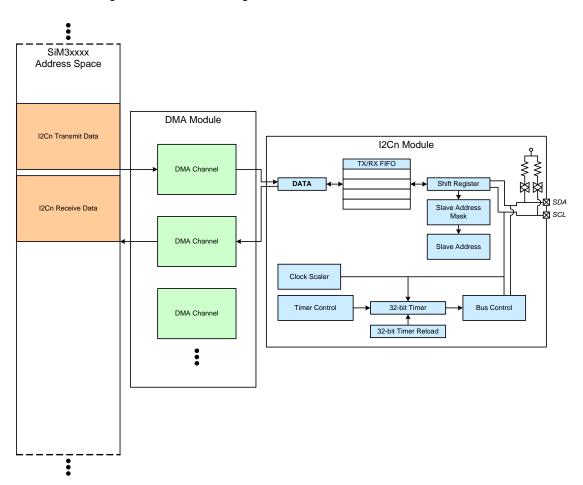

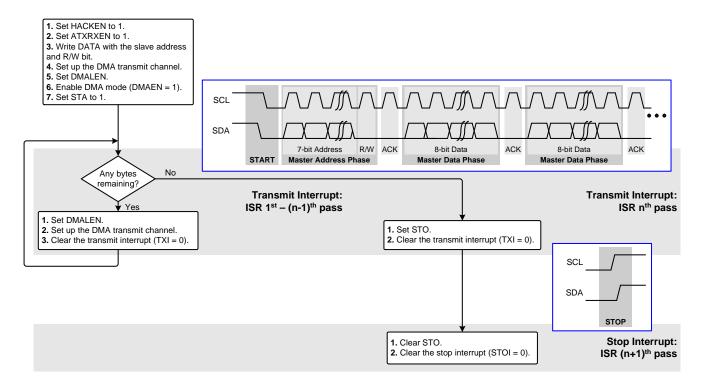

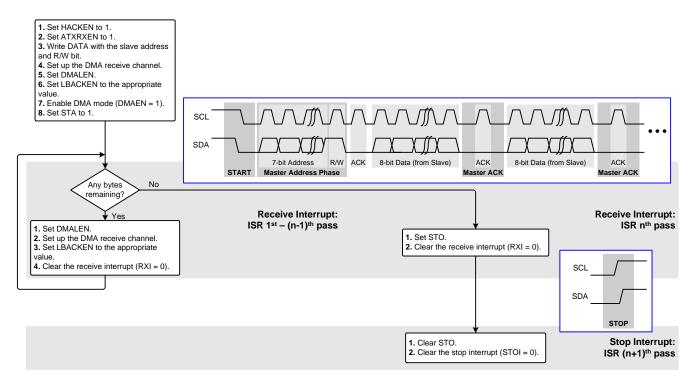

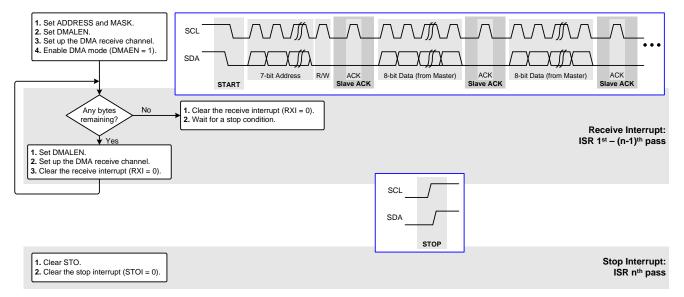

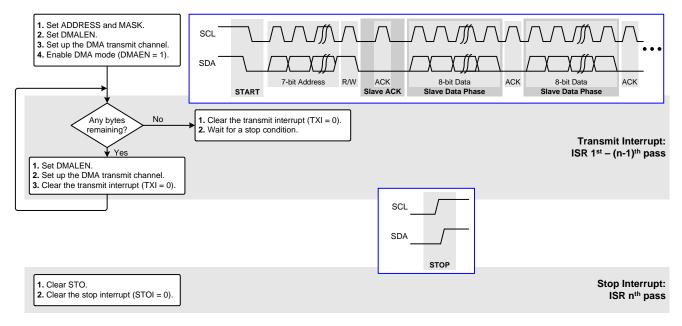

| 22 | .Inter-Integrated Circuit Bus (I2C0 and I2C1)   |     |

|    | 22.1.I2C Features                               |     |

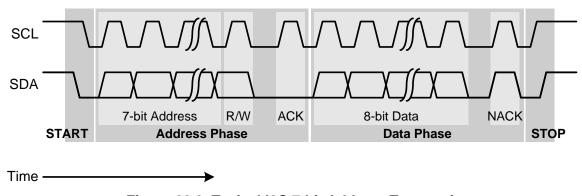

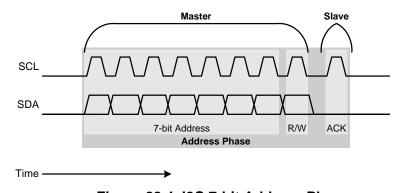

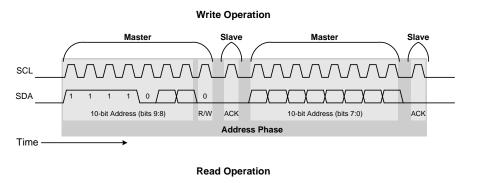

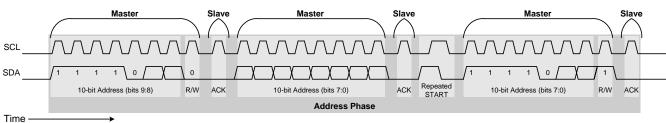

|    | 22.2.I2C Protocol                               | 392 |

|    | 22.3.Clocking                                   | 396 |

|    | 22.4.Operational Modes                          |     |

|    | 22.5.Error Handling                             |     |

|    | 22.6.Additional Features                        |     |

|    | 22.7.Debug Mode                                 |     |

|    | 22.8.DMA Configuration and Usage                |     |

|    | 22.9.I2C0 and I2C1 Registers                    |     |

|    | 22.10.I2Cn Register Memory Map                  |     |

|    |                                                 |     |

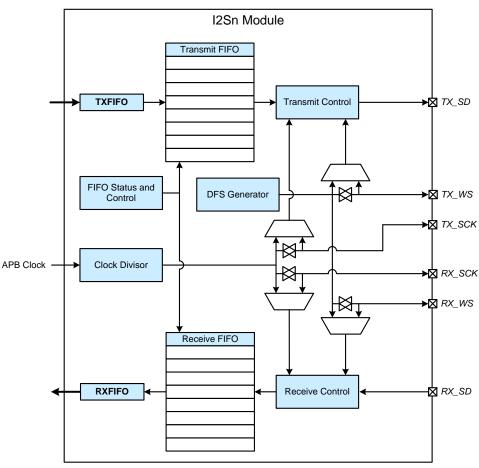

| 23 | .Integrated Interchip Sound (I2S0)                                          | 433 |

|----|-----------------------------------------------------------------------------|-----|

|    | 23.1.I2S Features                                                           | 433 |

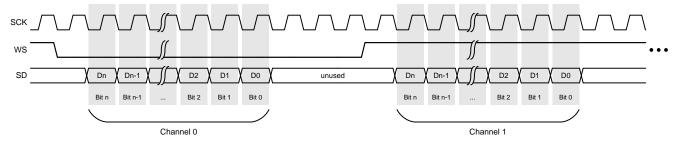

|    | 23.2.Signal Descriptions and Protocol Overview                              | 434 |

|    | 23.3.Clocking                                                               | 434 |

|    | 23.4.Clock (SCK) Signal Formatting                                          | 435 |

|    | 23.5. Word Select or Frame Sync (WS) Signal Formatting                      | 435 |

|    | 23.6.Basic Data (SD) Signal Formatting                                      | 436 |

|    | 23.7.Left-Justified and Longer-Delay Formats                                | 436 |

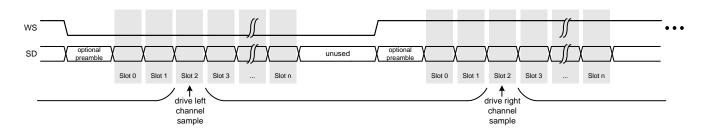

|    | 23.8.Time-Division Multiplexing (TDM)                                       | 437 |

|    | 23.9.Transmitter and Receiver                                               | 438 |

|    | 23.10.Interrupts and Flags                                                  | 439 |

|    | 23.11.Debug Mode                                                            | 439 |

|    | 23.12.Module Reset                                                          | 439 |

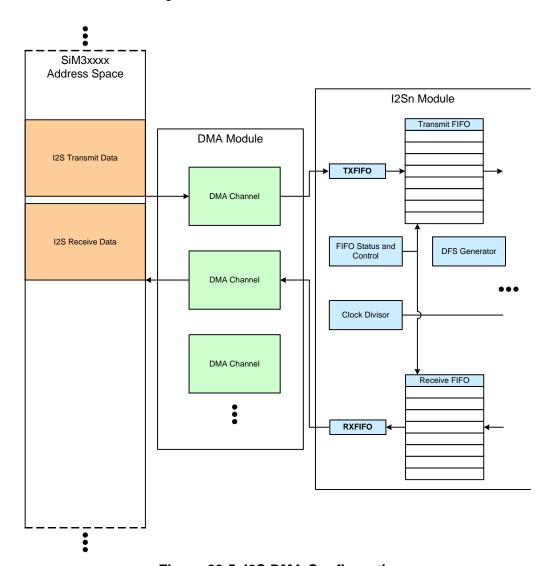

|    | 23.13.DMA Usage and Configuration                                           | 440 |

|    | 23.14.I2S0 Registers                                                        |     |

|    | 23.15.I2S0 Register Memory Map                                              |     |

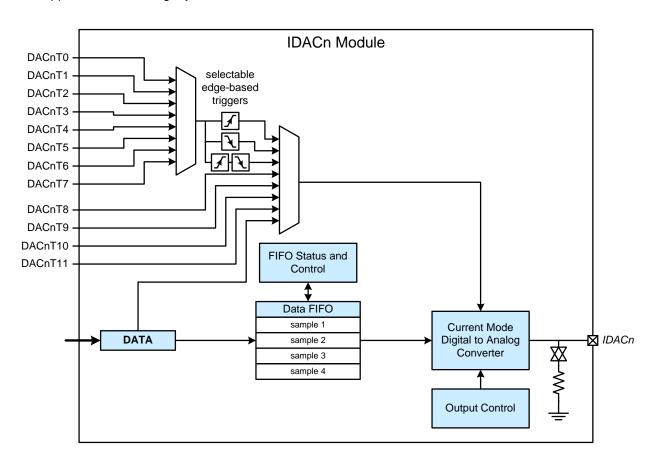

| 24 | .Current Mode Digital-to-Analog Converter (IDAC0 and IDAC1)                 |     |

|    | 24.1.IDAC Features                                                          |     |

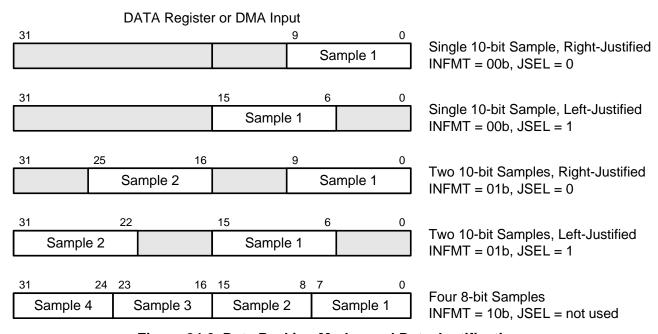

|    | 24.2.IDAC Setup                                                             | 464 |

|    | 24.3.Using the IDAC in On-Demand Mode                                       |     |

|    | 24.4.Using the IDAC in Periodic FIFO-Only Mode                              |     |

|    | 24.5.Using the IDAC in Periodic FIFO Wrap Mode                              |     |

|    | 24.6. Using the IDAC in Periodic DMA Mode (on select IDAC peripherals only) |     |

|    | 24.7.Adjusting the IDAC Output Current                                      |     |

|    | 24.8.Debug Mode                                                             |     |

|    | 24.9.IDAC0 and IDAC1 Registers                                              |     |

|    | 24.10.IDACn Register Memory Map                                             |     |

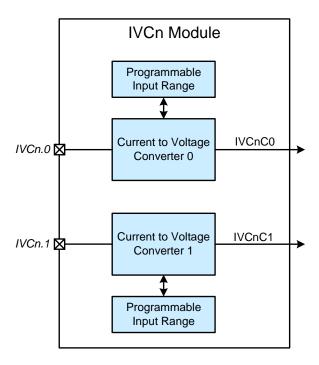

| 25 | .Current-to-Voltage Converter (IVC0)                                        |     |

|    | 25.1.IVC Features                                                           |     |

|    | 25.2.Functional Description                                                 |     |

|    | 25.3.Configuration                                                          |     |

|    | 25.4.IVC0 Registers                                                         |     |

|    | 25.5.IVC0 Register Memory Map                                               |     |

| 26 | .Low Power Oscillator (LPOSC0)                                              |     |

|    | 26.1.Low Power Oscillator Features                                          |     |

|    | 26.2.Operation                                                              |     |

|    | 26.3.LPOSC0 Registers                                                       |     |

|    | 26.4.LPOSC0 Register Memory Map                                             |     |

| 27 | Low Power Timer (LPTIMER0)                                                  |     |

|    | 27.1.Low Power Timer Features                                               |     |

|    | 27.2.Clocking                                                               |     |

|    | 27.3.Configuring the Timer                                                  |     |

|    | 27.4.Interrupts                                                             |     |

|    | 27.5.Output                                                                 |     |

|    | 27.6.Automatic Reset                                                        |     |

|    | 27.7.Debug Mode                                                             |     |

| 27.8.LPTIMER0 Registers                                   | 494 |

|-----------------------------------------------------------|-----|

| 27.9.LPTIMER0 Register Memory Map                         |     |

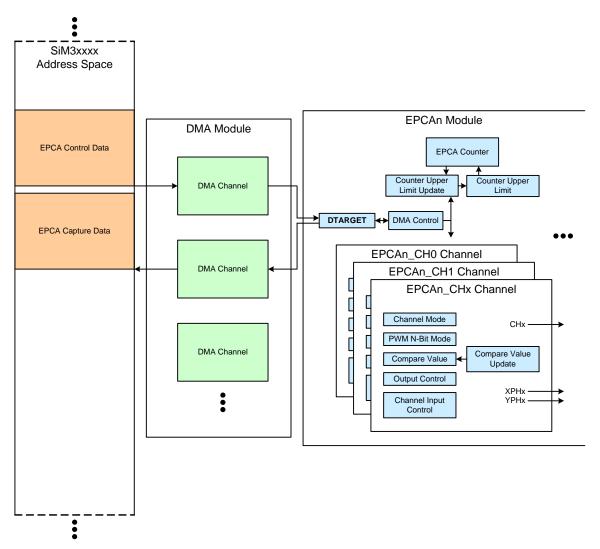

| 28. Enhanced Programmable Counter Array (EPCA0)           |     |

| 28.1.Enhanced Programmable Counter Array Features         |     |

| 28.2.Module Overview                                      |     |

| 28.3.Clocking                                             |     |

| 28.4.Interrupts                                           |     |

| 28.5.Outputs                                              |     |

| 28.6.Triggers                                             |     |

| 28.7.Operational Modes                                    |     |

| 28.8.DMA Configuration and Usage                          |     |

| 28.9.EPCA0 Registers                                      |     |

| 28.10.EPCA0 Register Memory Map                           |     |

| 28.11.EPCA0_CH0-5 Registers                               |     |

| 28.12.EPCAn_CHx Register Memory Map                       |     |

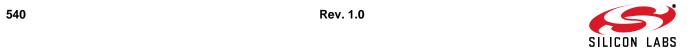

| 29. Programmable Counter Array (PCA0 and PCA1)            |     |

| 29.1.Programmable Counter Array (1 CA0 and 1 CA1)         |     |

| 29.2.Module Overview                                      |     |

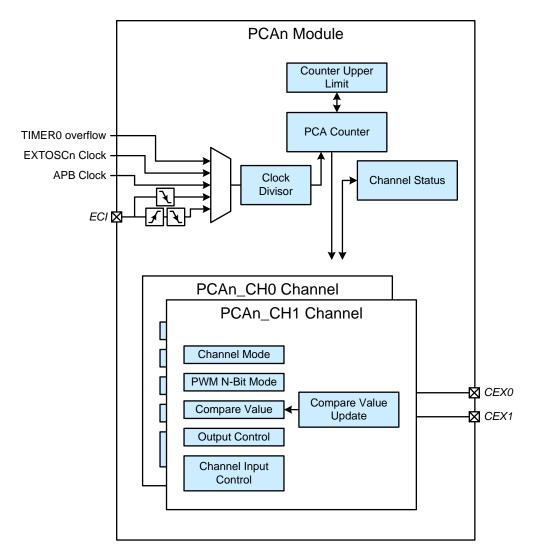

| 29.3.Clocking                                             |     |

| 29.4.Interrupts                                           |     |

| 29.5.Outputs                                              |     |

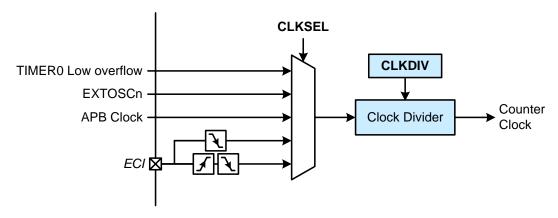

| 29.6.Operational Modes                                    |     |

| ·                                                         |     |

| 29.7.PCA0 and PCA1 Registers                              |     |

| 29.8.PCAn Register Memory Map                             |     |

| 29.9.PCA0_CH0-1 and PCA1_CH0-1 Registers                  |     |

| 29.10.PCAn_CHx Register Memory Map                        |     |

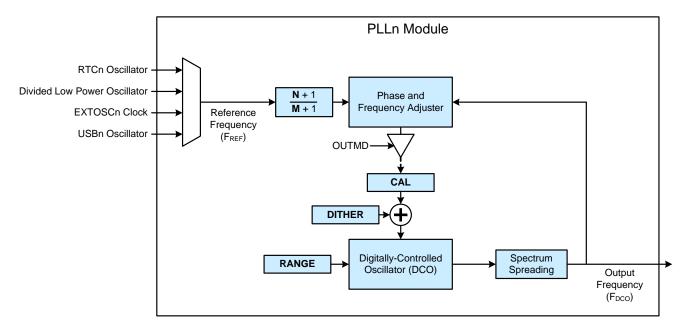

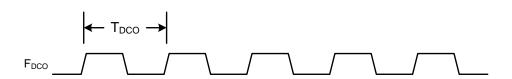

| 30. Phase-Locked Loop (PLL0)                              |     |

| 30.1.PLL Features                                         |     |

| 30.2.Overview                                             |     |

| 30.3.Interrupts                                           |     |

| 30.4.Output Modes                                         |     |

| 30.5.Additional Features                                  |     |

| 30.6.Advanced Setup Examples                              |     |

| 30.7.PLL0 Registers                                       |     |

| 30.8.PLL0 Register Memory Map                             |     |

| 31. Real Time Clock and Low Frequency Oscillator (RTC0)   |     |

| 31.1.RTC Features                                         |     |

| 31.2.Overview                                             |     |

| 31.3.Clocking                                             |     |

| 31.4.Accessing the Timer                                  |     |

| 31.5.Alarms                                               |     |

| 31.6.Interrupts                                           |     |

| 31.7.Usage Models                                         |     |

| 31.8.RTC0 Registers                                       |     |

| 31.9.RTC0 Register Memory Map                             |     |

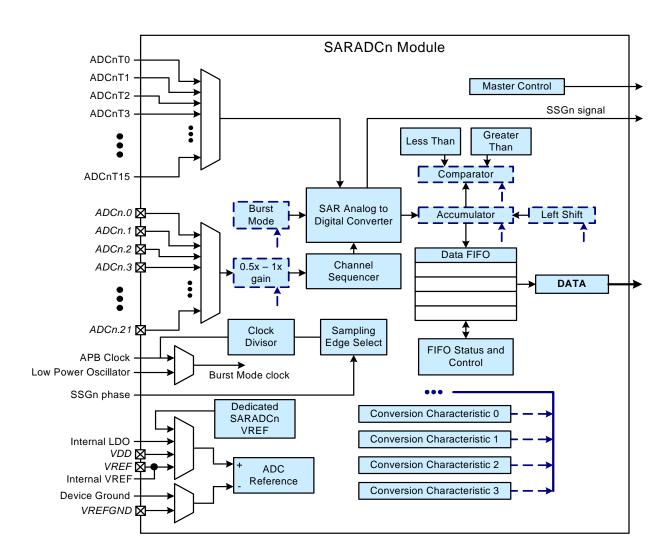

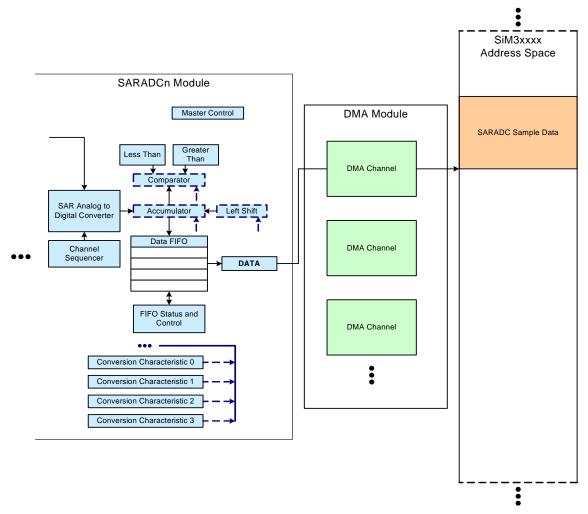

| 32. SAR Analog-to-Digital Converter (SARADC0 and SARADC1) |     |

| 32.1.SARADC Features                                      | 615 |

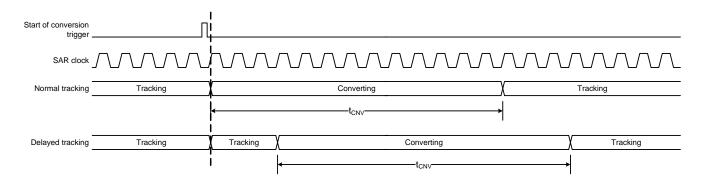

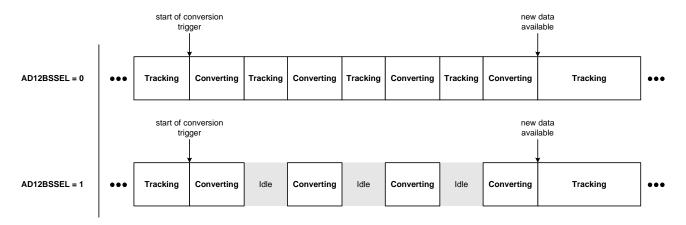

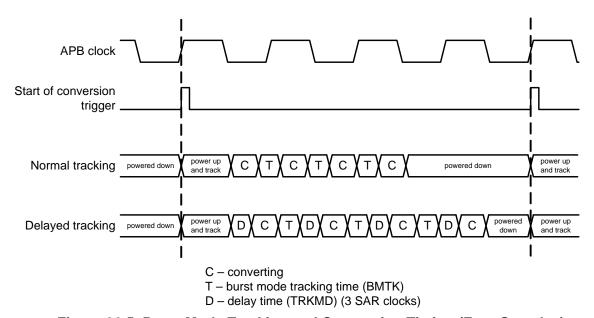

| 32.3.Burst Mode                                                           | 617     |

|---------------------------------------------------------------------------|---------|

|                                                                           |         |

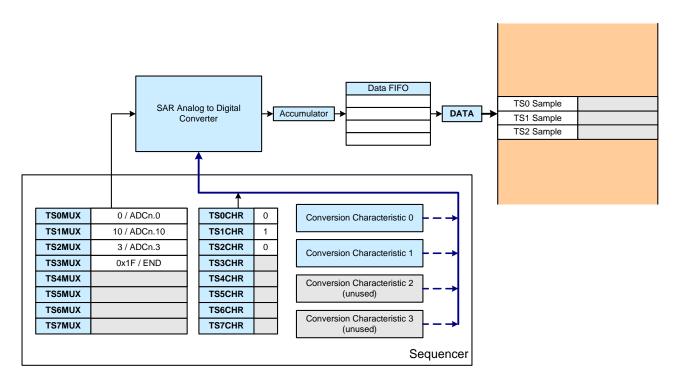

| 32.4.Channel Sequencer                                                    | 622     |

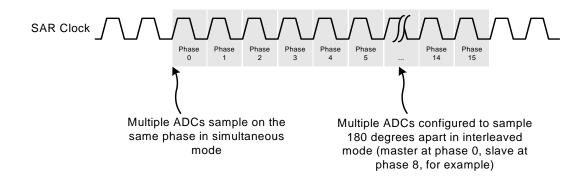

| 32.5.Sample Sync Generator                                                | 626     |

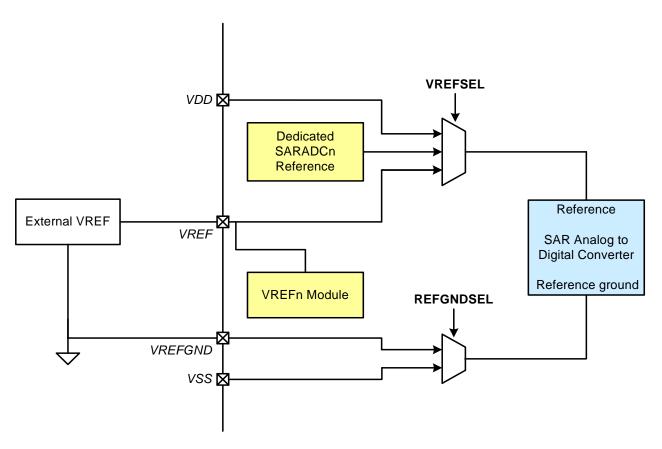

| 32.6.Voltage Reference Configuration                                      | 627     |

| 32.7.Power Configuration                                                  |         |

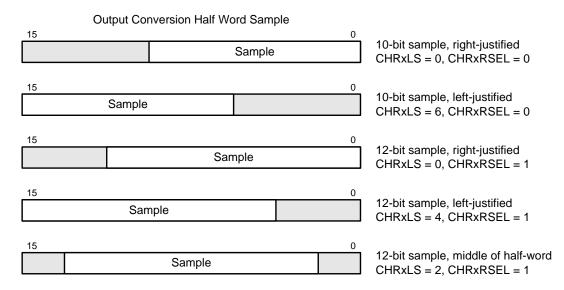

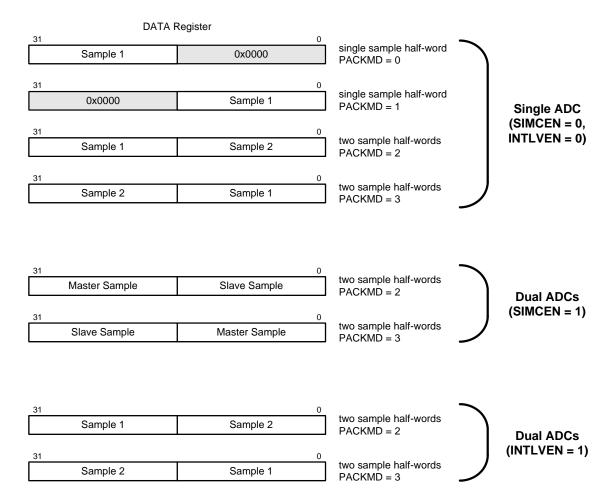

| 32.8. Data Output                                                         |         |

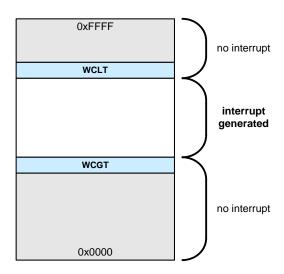

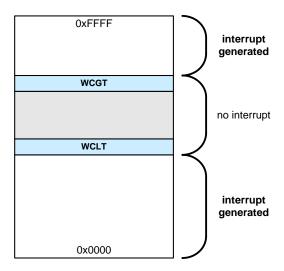

| 32.9.Interrupts                                                           | 632     |

| 32.10.DMA Configuration and Usage                                         | 634     |

| 32.11.SARADC0 and SARADC1 Registers                                       | 635     |

| 32.12.SARADCn Register Memory Map                                         | 656     |

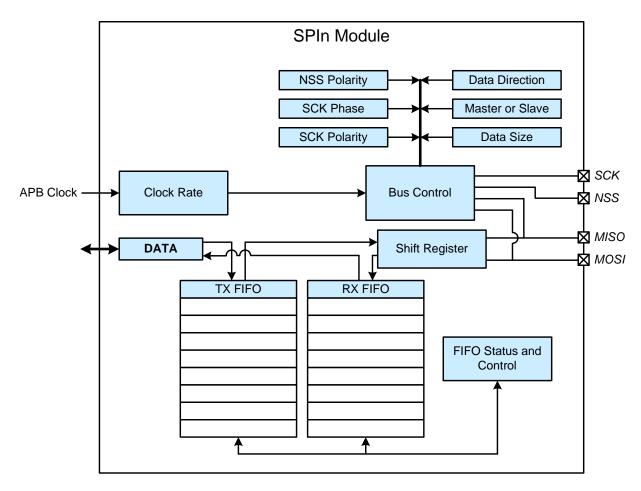

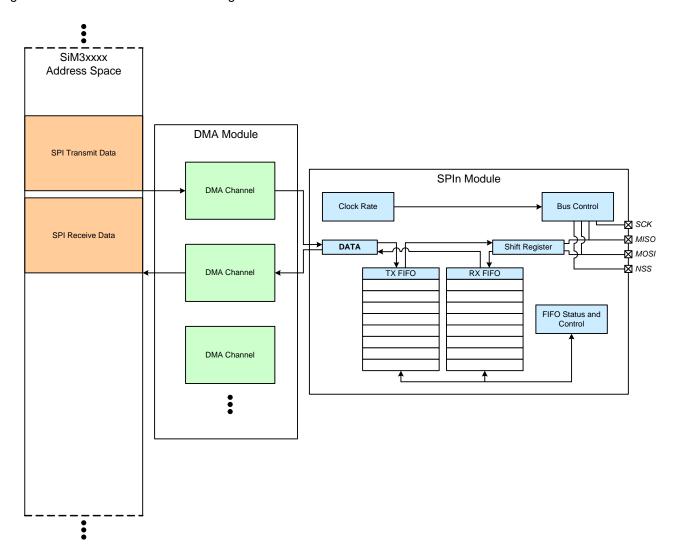

| 33. Serial Peripheral Interface (SPI0, SPI1 and SPI2)                     | 659     |

| 33.1.SPI Features                                                         |         |

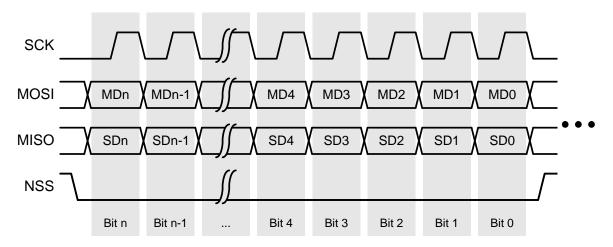

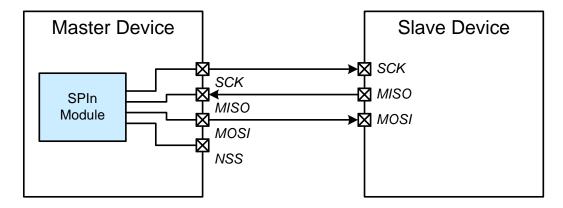

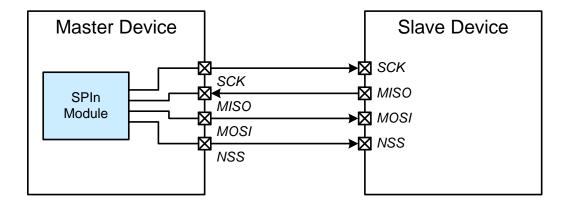

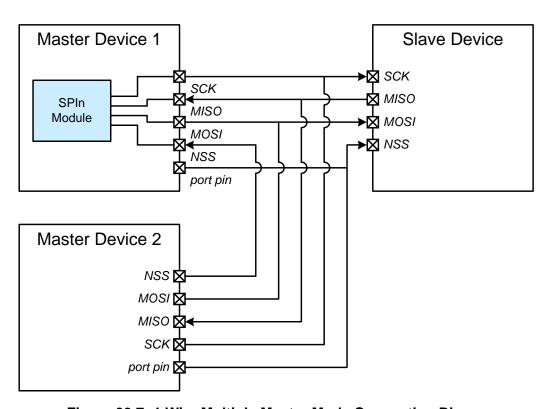

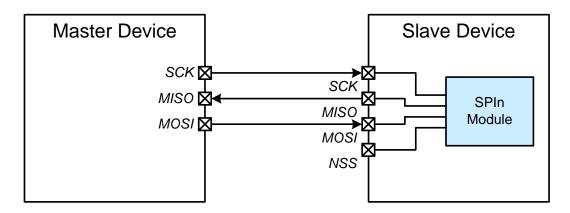

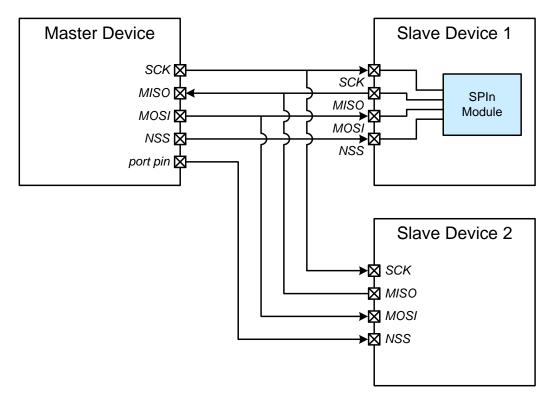

| 33.2.Signal Descriptions                                                  | 660     |

| 33.3.Clocking                                                             | 661     |

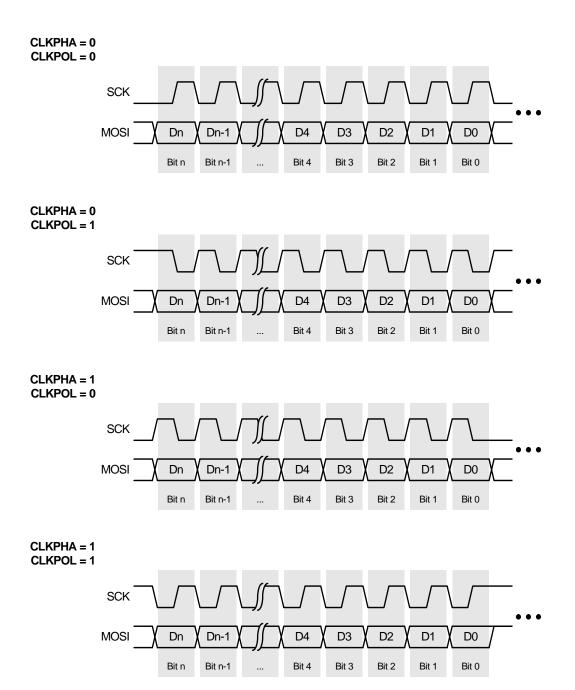

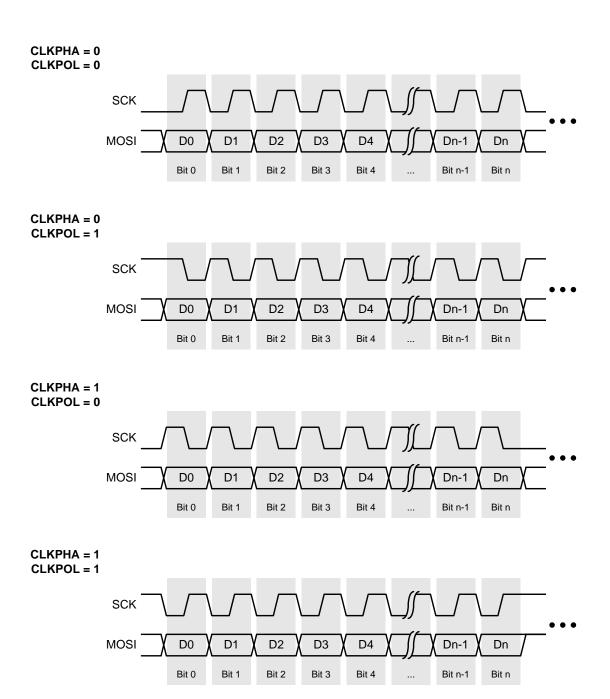

| 33.4.Signal Format                                                        | 661     |

| 33.5.Master Mode Configurations and Data Transfer                         | 664     |

| 33.6.Slave Mode Configurations and Data Transfer                          | 666     |

| 33.7.Interrupts                                                           | 668     |

| 33.8.Debug Mode                                                           | 668     |

| 33.9.Module Reset                                                         | 668     |

| 33.10.DMA Configuration and Usage                                         | 669     |

| 33.11.SPI0, SPI1 and SPI2 Registers                                       | 670     |

| 33.12.SPIn Register Memory Map                                            | 679     |

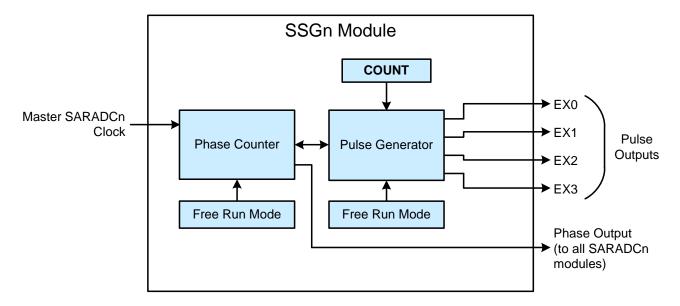

| 34. Sample Sync Generator (SSG0)                                          | 680     |

| 34.1.SSG Features                                                         |         |

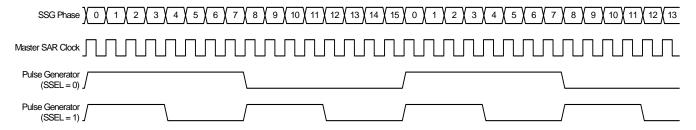

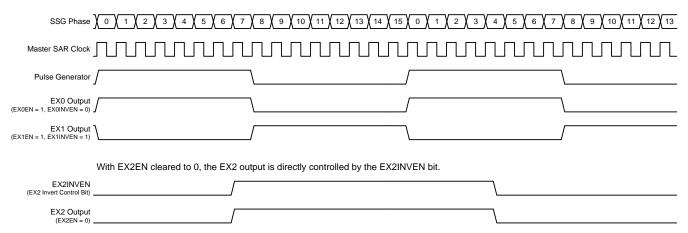

| 34.2.Phase Generator                                                      | 681     |

| 34.3.Pulse Generator                                                      | 681     |

| 34.4.SSG0 Registers                                                       | 685     |

| 34.5.SSG0 Register Memory Map                                             | 689     |

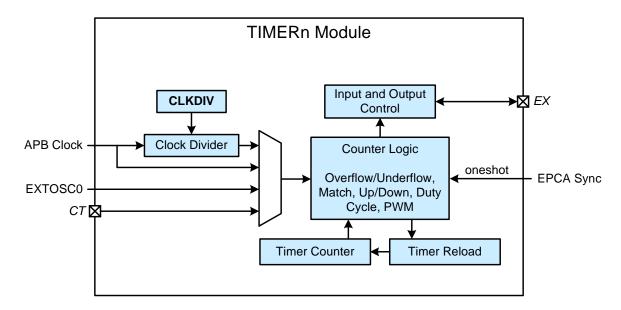

| 35. Timers (TIMER0 and TIMER1)                                            | 690     |

| 35.1.Timer Features                                                       |         |

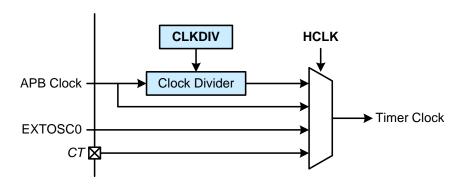

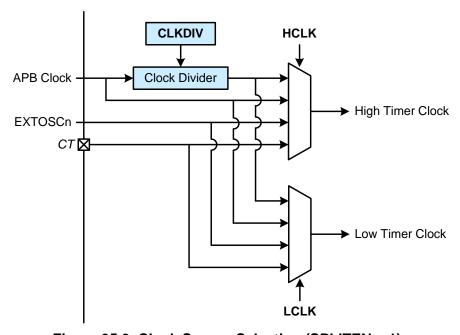

| 35.2.Clocking                                                             | 691     |

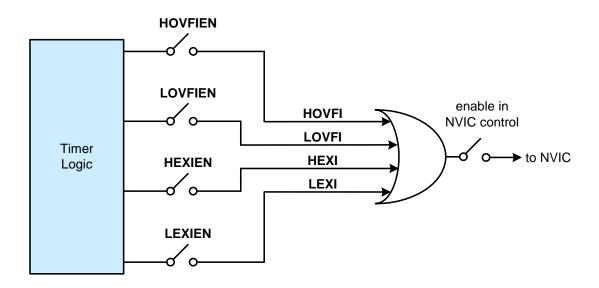

| 35.3.Configuring Timer Interrupts                                         |         |

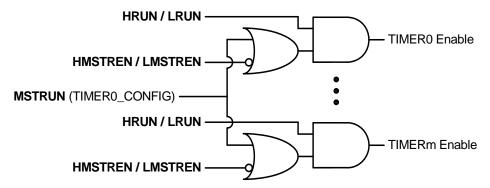

| 35.4.Timer Synchronization                                                | 693     |

| 35.5.Timer Modes                                                          |         |

| 35.6.TIMER0 and TIMER1 Registers                                          |         |

| 35.7.TIMERn Register Memory Map                                           |         |

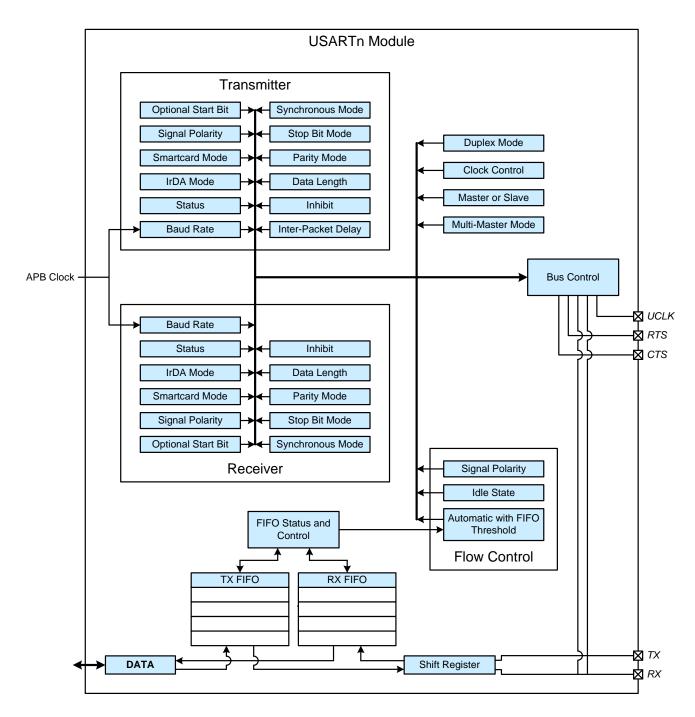

| 36. Universal Synchronous/Asynchronous Receiver/Transmitter (USART0 and U | SART1). |

| 712                                                                       |         |

| 36.1.USART Features                                                       |         |

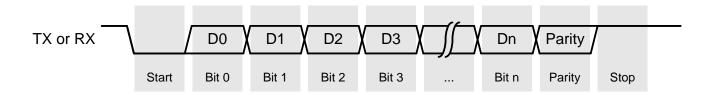

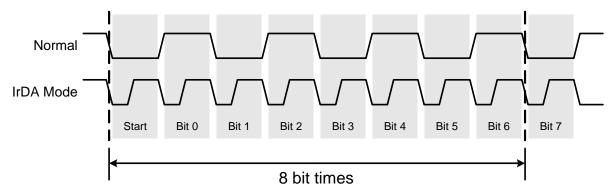

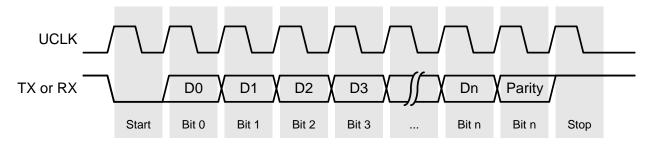

| 36.2.Basic Data Format                                                    |         |

|                                                                           | 714     |

| 36.3.Baud Rate                                                            |         |

| 36.3.Baud Rate36.4.Interrupts                                             | 715     |

| 36.3.Baud Rate                                                            | 715     |

| 36.7.Sending Data                                                 | 717 |

|-------------------------------------------------------------------|-----|

| 36.8.Receiving Data                                               |     |

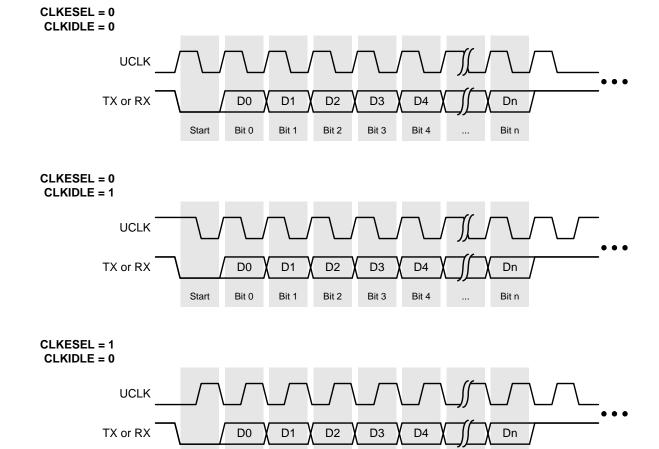

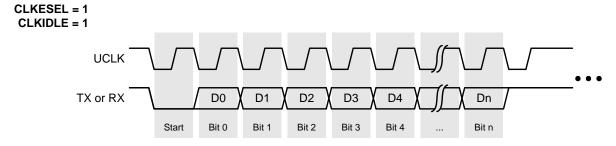

| 36.9.Synchronous Communications                                   |     |

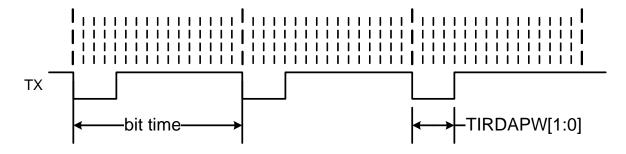

| 36.10.Additional Communication Support                            |     |

| 36.11.DMA Configuration and Usage                                 |     |

| 36.12.USART0 and USART1 Registers                                 |     |

| 36.13.USARTn Register Memory Map                                  |     |

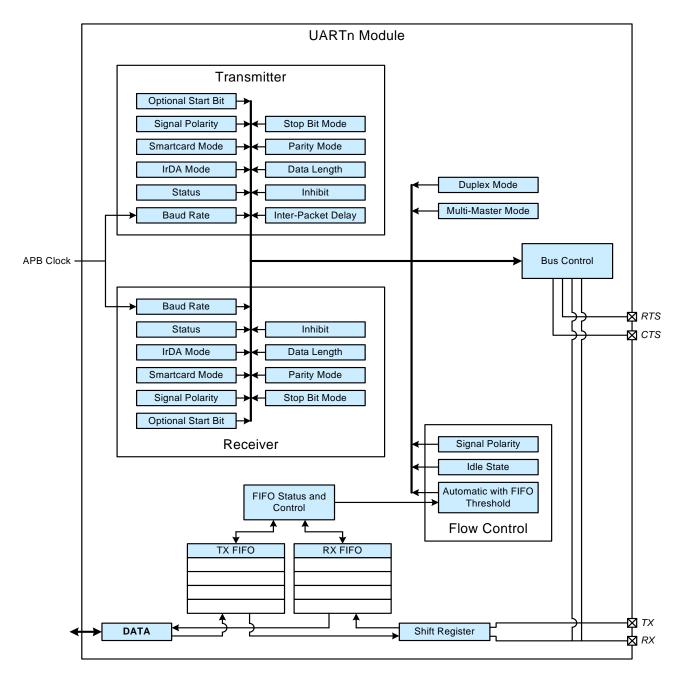

| 37. Universal Asynchronous Receiver/Transmitter (UART0 and UART1) | 747 |

| 37.1.UART Features                                                |     |

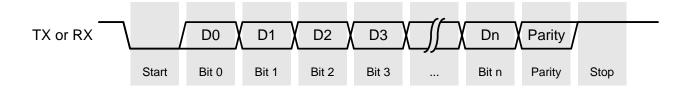

| 37.2.Basic Data Format                                            |     |

| 37.3.Baud Rate                                                    |     |

| 37.4.Interrupts                                                   |     |

| 37.5.Flow Control                                                 |     |

| 37.6.Debug Mode                                                   |     |

| 37.7.Sending Data                                                 |     |

| 37.8.Receiving Data                                               |     |

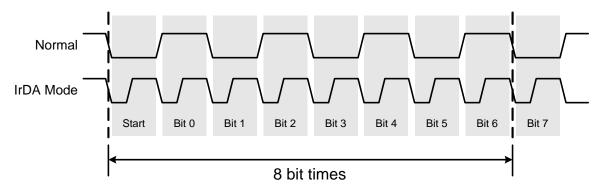

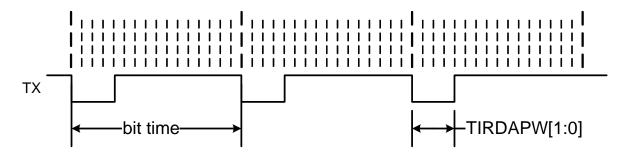

| 37.9.Additional Communication Support                             |     |

| 37.10.UART0 and UART1 Registers                                   |     |

| 37.11.UARTn Register Memory Map                                   |     |

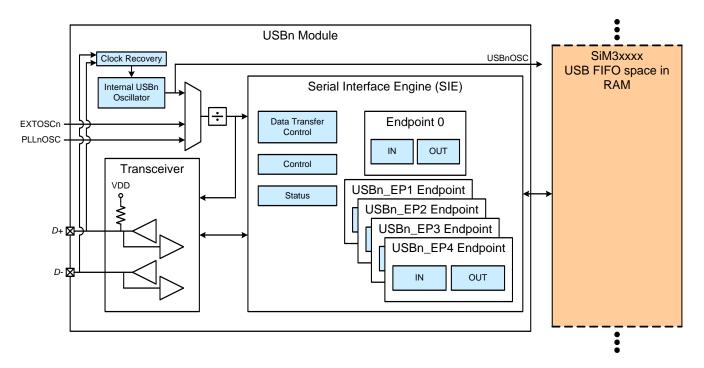

| 38. Universal Serial Bus Controller (USB0)                        | 773 |

| 38.1.USB Features                                                 |     |

| 38.2.Overview                                                     |     |

| 38.3.Clocking                                                     |     |

| 38.4.Endpoints                                                    |     |

| 38.5.USB Transceiver                                              |     |

| 38.6.FIFO Management                                              |     |

| 38.7.Function Addressing                                          |     |

| 38.8.Function Configuration and Control                           |     |

|                                                                   |     |

| 38.9.Interrupts                                                   |     |

| 38.10.The Serial Interface Engine                                 | 702 |

| ·                                                                 |     |

| 38.12.Configuring Endpoints 1-4                                   |     |

| 38.13.Controlling Endpoints 1-4 IN                                |     |

| 38.14.Controlling Endpoints 1-4 OUT                               |     |

| 38.15.DMA Configuration and Usage                                 |     |

| 38.16.USB0 Registers                                              |     |

| 38.17.USB0 Register Memory Map                                    |     |

| 38.18.USB0_EP1-4 Registers                                        |     |

| 38.19.USBn_EPx Register Memory Map                                |     |

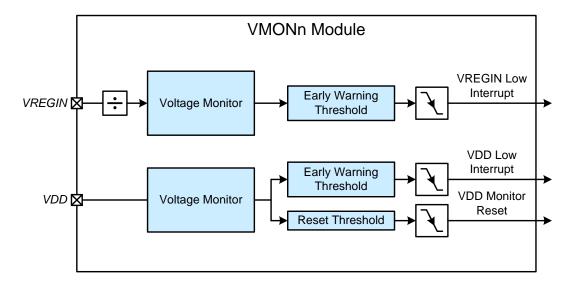

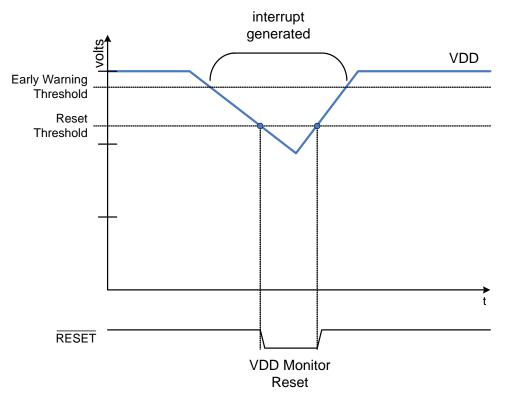

| 39. Voltage Supply Monitor (VMON0)                                |     |

| 39.1.Voltage Supply Monitor Features                              |     |

| 39.2.VDD Supply Monitoring                                        |     |

| 39.3.VREGIN Pin Monitoring                                        |     |

| 39.4.VMON0 Registers                                              |     |

| 39.5.VMON0 Register Memory Map                                    |     |

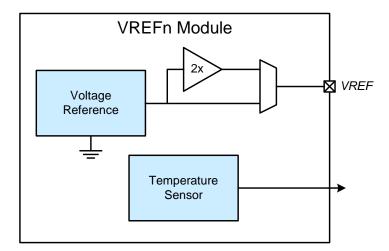

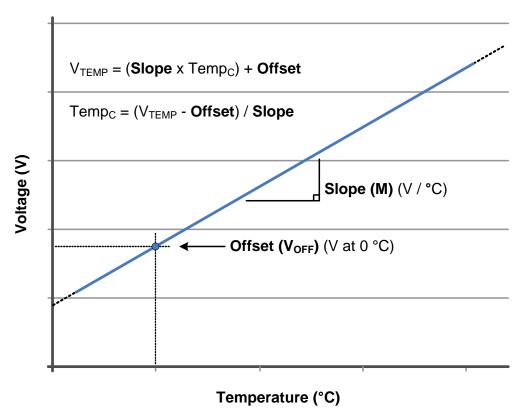

| 40. Voltage Reference and Temperature Sensor (VREF0)              | 838 |

| 40.1.Voltage Reference Features                     | 838 |

|-----------------------------------------------------|-----|

| 40.2.Functional Description                         |     |

| 40.3.VREF0 and Temperature Sensor Registers         |     |

| 40.4.VREF0 Register Memory Map                      |     |

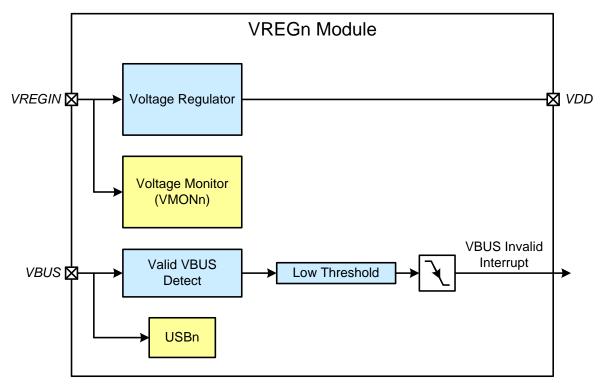

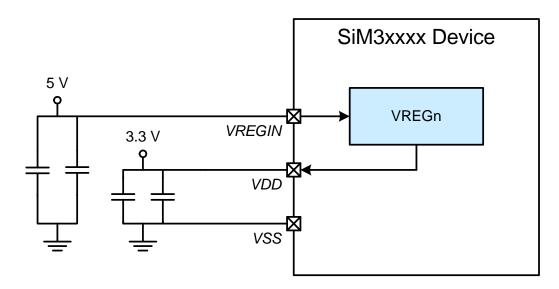

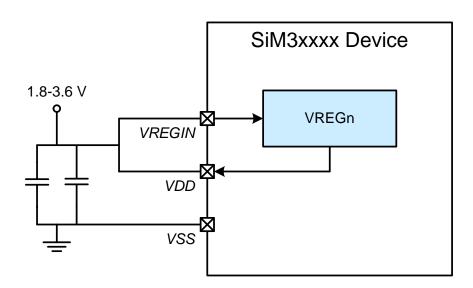

| 41. Voltage Regulator (VREG0)                       |     |

| 41.1.Voltage Regulator Features                     |     |

| 41.2.Operational Modes                              |     |

| 41.3.Interrupts and Flags                           |     |

| 41.4.VREG0 Registers                                |     |

| 41.5.VREG0 Register Memory Map                      |     |

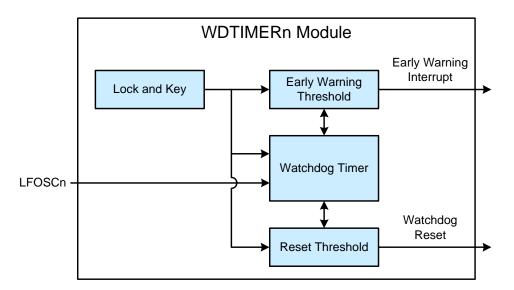

| 42. Watchdog Timer (WDTIMER0)                       |     |

| 42.1.Watchdog Timer Features                        |     |

| 42.2.Overview                                       |     |

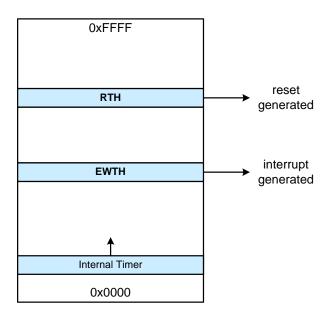

| 42.3.Lock and Key Interface                         | 849 |

| 42.4.Setting the Early Warning and Reset Thresholds |     |

| 42.5.Interrupts and Flags                           |     |

| 42.6.Debug Mode                                     |     |

| 42.7.WDTIMER0 Registers                             |     |

| 42.8.WDTIMER0 Register Memory Map                   |     |

| Document Change List                                |     |

| One to at lafe and the                              | 200 |

### 1. Related Documents and Conventions

#### 1.1. Related Documents

#### 1.1.1. SiM3U1xx and SiM3C1xx Data Sheets

The Silicon Laboratories SiM3U1xx and SiM3C1xx Data Sheets provide specific information for each device family, including electrical characteristics, mechanical characteristics, and ordering information.

### 1.1.2. Hardware Access Layer (HAL) API Description

The Silicon Laboratories Hardware Access Layer (HAL) API provides functions to modify and read each bit in the SiM3U1xx and SiM3C1xx devices. This description can be found in the SiM3xxxx HAL API Reference Manual.

#### 1.1.3. ARM Cortex-M3 Reference Manual

The ARM-specific features like the Nested Vector Interrupt Controller are described in the ARM Cortex-M3 reference documentation. The online reference manual can be found online at the following link: http://infocenter.arm.com/help/topic/com.arm.doc.subset.cortexm.m3/index.html#cortexm3.

#### 1.2. Conventions

The block diagrams in this document use the following formatting conventions:

Figure 1.1. Block Diagram Conventions

## 2. Memory Organization

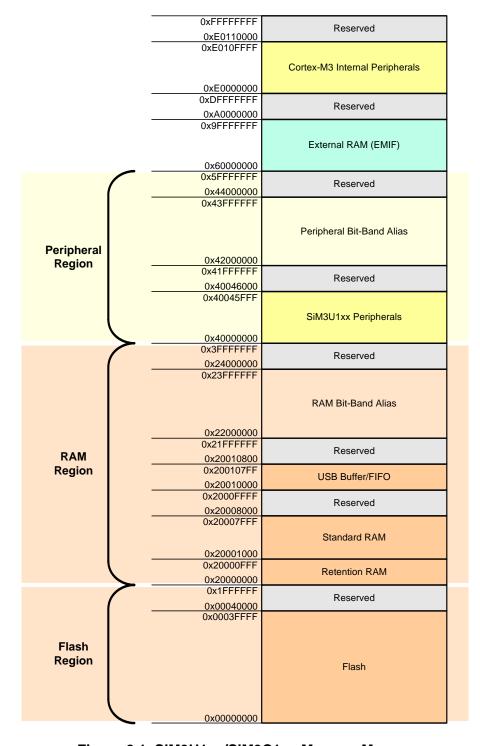

The memory organization of the SiM3U1xx/SiM3C1xx devices follows the standard ARM Cortex-M3 structure, shown in Figure 2.1. There is one 32-bit memory space shared amongst the flash, RAM, SiM3U1xx/SiM3C1xx Peripherals, External Memory, and M3 Peripherals. The unused memory addresses are reserved and should not be accessed.

Figure 2.1. SiM3U1xx/SiM3C1xx Memory Map

### 2.1. Flash Region

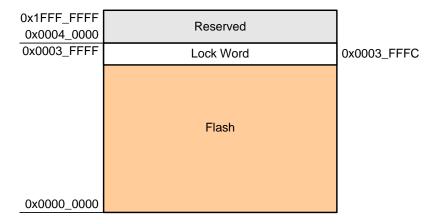

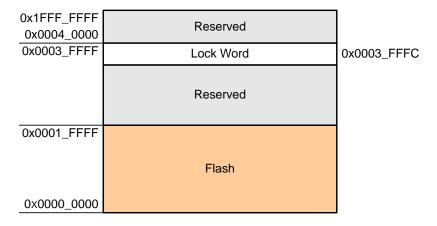

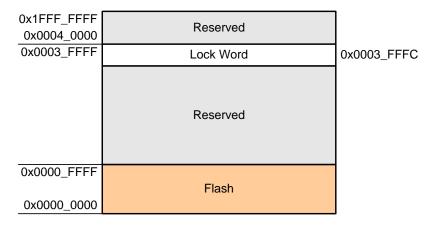

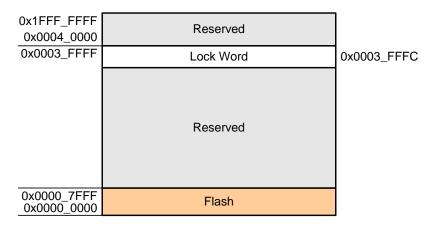

The SiM3U1xx/SiM3C1xx devices implement 256, 128, 64, or 32 kB of flash which is accessible starting at 0x00000000. The flash can be read using standard ARM instructions. The FLASHCTRL0 module should be used to write and erase flash from firmware.

The flash block can be locked by writing to the lock word located at 0x0003FFFC. A value of 0xFFFFFFFF or 0x00000000 at this location will unlock the flash. Any other value written to this location will lock the entire flash from external (debugger) or firmware writes or reads until:

- An erase operation is initiated from firmware.

- An erase operation is initiated through the debug port (SWD/JTAG).

- Firmware writes 0x00000000 to the lock word.

The DMA can access all of flash.

Figure 2.2. SiM3U16x Flash Memory Map (256 kB)

Figure 2.3. SiM3U15x Flash Memory Map (128 kB)

Figure 2.4. SiM3U14x Flash Memory Map (64 kB)

Figure 2.5. SiM3U13x Flash Memory Map (32 kB)

### 2.2. RAM Region

14

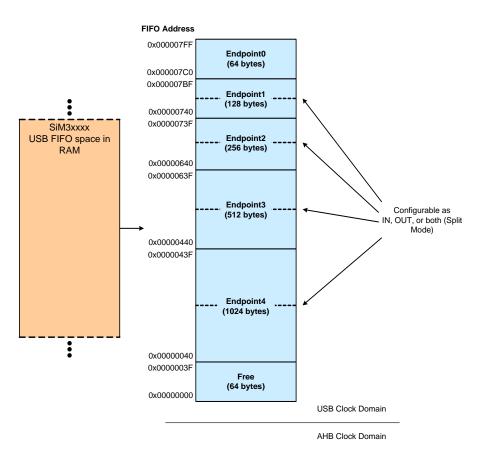

The RAM Region of SiM3U1xx/SiM3C1xx devices has the following areas: Standard RAM, Retention RAM, USB Buffer/FIFO RAM, and the RAM Bit-Banded Alias.

The Standard RAM region implements 28 kB (SiM3U16x and SiM3U15x), 12 kB (SiM3U14x), or 4 kB (SiM3U13x) of RAM and starts at location 0x20001000.

The SiM3U1xx/SiM3C1xx devices implement 4 kB of Retention RAM located at address 0x20000000. This RAM will retain it's value in Power Mode 9 as long as the VDD Monitor has not caused a reset.

The USB Buffer/FIFO RAM should be used by the USB0 Module and not accessed directly. If the USB0 Module is not in use, the clocks to this memory can be disabled to save power.

The RAM Bit-Band Alias region can be used to perform sets or clears of individual bits in the RAM. Each bit in the RAM region is represented by the least-significant bit at the word-aligned bit-band alias address.

### 2.3. Peripheral Region

The SiM3U1xx/SiM3C1xx peripheral registers are located starting at address 0x4000\_0000. Registers for a specific module are typically located together in the peripheral region of memory to facilitate structure access from firmware. Each register may have up to four access methods, implemented as four separate locations in memory. The four possible access methods are named ALL, SET, CLR, and MSK.

The register's ALL access address is the primary access point for any register. Individual bits may be Read/Write (RW), Read-Only (RO), or Write-Only (WO). The ALL access address is implemented for all registers, and where absolute memory addresses are given in the documentation, they refer to the ALL address. For registers with write access, the ALL address will directly write all bits of the register. A read of the ALL address will read the current value in the register.

The SET and CLR addresses provide bit-wise, atomic write access to set and clear bits in the register without colliding with hardware. Writing a 1 to a bit in the SET address will set the corresponding bit, and writing a 1 to a bit in the CLR address will clear the corresponding bit. A write of 0 to either SET or CLR will have no effect on the corresponding bit. For registers implementing SET and CLR access methods, the SET address is at offset 0x4, and the CLR address is at offset 0x8 from the register's ALL access address. SET and CLR access are not implemented on every register.

The MSK address allows a write to a specific range of bits in the register. The upper 16 bits act as a mask for writing a value in the lower 16 bits of the register. For example, a write of 0x0F000400 to the MASK address would write a value of 4 to bits [11:8] of the register, while none of the rest of the bits are modified. For registers implementing the MSK access method, the MSK address is at offset 0xC from the registers ALL access address. MSK access is implemented for only a small set of registers which may require atomic, simultaneous writes of both 1s and 0s (such as port output registers).

Many control and status registers are supported by the SET and CLR access methods. The Peripheral Bit-Band Alias region can also be used to perform sets or clears of individual bits in the peripheral registers, which results in a read-modify-write operation on the bus. Each bit in the registers region is represented by the least-significant bit at the word-aligned bit-band alias address. When supported, it is recommended to use the SET and CLR registers instead of the Bit-Band Alias region to change individual bits in a register.

Each peripheral is discussed in detail in the corresponding chapter. The register map for the SiM3U1xx/SiM3C1xx devices can be found in "3. SiM3U1xx/SiM3C1xx Register Memory Map". Detailed descriptions of each register and the bit fields within can be found in the specific peripheral section for that register.

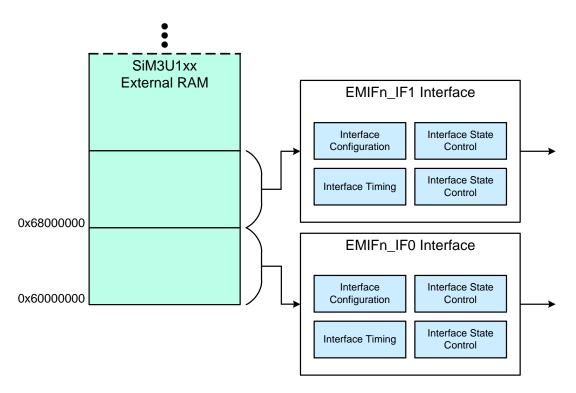

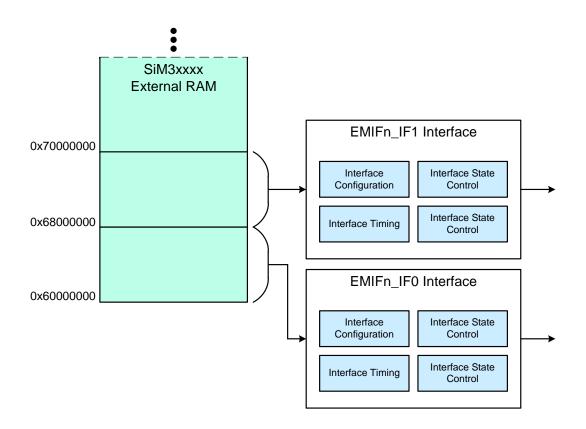

### 2.4. External Memory

The EMIF Module accesses the External Memory Region. The EMIF module on the SiM3U1xx/SiM3C1xx devices supports two interfaces accessed at addresses 0x60000000 and 0x68000000, as shown in Figure 2.6.

Figure 2.6. SiM3U1xx/SiM3C1xx External Memory Map

More information on the timing and configuration of this module can be found in the EMIF Module documentation.

### 2.5. Cortex-M3 Internal Peripherals

The Cortex-M3 Internal Peripherals space includes standard M3 functions, such as the NVIC and ETM. For more information on these functions of the ARM core, consult the ARM Cortex-M3 Reference Manual.

## 3. SiM3U1xx/SiM3C1xx Register Memory Map

This section details the register memory map for the SiM3U1xx/SiM3C1xx devices. Registers are listed in address order, beginning with 0x4000\_0000

Table 3.1. Register Memory Map

|                  |                                |                         |            | (8x       | )xC        |

|------------------|--------------------------------|-------------------------|------------|-----------|------------|

| Register Name    | Title                          | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

| USART0 Registers |                                |                         |            |           |            |

| USART0_CONFIG    | Module Configuration           | 0x4000_0000             | Υ          | Υ         |            |

| USART0_MODE      | Module Mode Select             | 0x4000_0010             | Υ          | Υ         |            |

| USART0_FLOWCN    | Flow Control                   | 0x4000_0020             | Υ          | Υ         |            |

| USART0_CONTROL   | Module Control                 | 0x4000_0030             | Υ          | Υ         |            |

| USART0_IPDELAY   | Inter-Packet Delay             | 0x4000_0040             |            |           |            |

| USARTO_BAUDRATE  | Transmit and Receive Baud Rate | 0x4000_0050             |            |           |            |

| USART0_FIFOCN    | FIFO Control                   | 0x4000_0060             | Υ          | Υ         |            |

| USARTO_DATA      | FIFO Input/Output Data         | 0x4000_0070             |            |           |            |

| USART1 Registers |                                |                         |            |           |            |

| USART1_CONFIG    | Module Configuration           | 0x4000_1000             | Υ          | Υ         |            |

| USART1_MODE      | Module Mode Select             | 0x4000_1010             | Υ          | Υ         |            |

| USART1_FLOWCN    | Flow Control                   | 0x4000_1020             | Υ          | Υ         |            |

| USART1_CONTROL   | Module Control                 | 0x4000_1030             | Υ          | Υ         |            |

| USART1_IPDELAY   | Inter-Packet Delay             | 0x4000_1040             |            |           |            |

| USART1_BAUDRATE  | Transmit and Receive Baud Rate | 0x4000_1050             |            |           |            |

| USART1_FIFOCN    | FIFO Control                   | 0x4000_1060             | Υ          | Υ         |            |

| USART1_DATA      | FIFO Input/Output Data         | 0x4000_1070             |            |           |            |

| UART0 Registers  |                                |                         |            |           |            |

| UART0_CONFIG     | Module Configuration           | 0x4000_2000             | Υ          | Υ         |            |

| UART0_MODE       | Module Mode Select             | 0x4000_2010             | Υ          | Υ         |            |

| UART0_FLOWCN     | Flow Control                   | 0x4000_2020             | Υ          | Υ         |            |

| UART0_CONTROL    | Module Control                 | 0x4000_2030             | Υ          | Υ         |            |

| UART0_IPDELAY    | Inter-Packet Delay             | 0x4000_2040             |            |           |            |

| UART0_BAUDRATE   | Transmit and Receive Baud Rate | 0x4000_2050             |            |           |            |

Table 3.1. Register Memory Map

| Register Name   | Title                          | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|-----------------|--------------------------------|-------------------------|------------|-----------|------------|

| UART0_FIFOCN    | FIFO Control                   | 0x4000_2060             | Υ          | Υ         |            |

| UART0_DATA      | FIFO Input/Output Data         | 0x4000_2070             |            |           |            |

| UART1 Registers |                                |                         |            |           |            |

| UART1_CONFIG    | Module Configuration           | 0x4000_3000             | Υ          | Υ         |            |

| UART1_MODE      | Module Mode Select             | 0x4000_3010             | Υ          | Υ         |            |

| UART1_FLOWCN    | Flow Control                   | 0x4000_3020             | Υ          | Υ         |            |

| UART1_CONTROL   | Module Control                 | 0x4000_3030             | Υ          | Υ         |            |

| UART1_IPDELAY   | Inter-Packet Delay             | 0x4000_3040             |            |           |            |

| UART1_BAUDRATE  | Transmit and Receive Baud Rate | 0x4000_3050             |            |           |            |

| UART1_FIFOCN    | FIFO Control                   | 0x4000_3060             | Υ          | Υ         |            |

| UART1_DATA      | FIFO Input/Output Data         | 0x4000_3070             |            |           |            |

| SPI0 Registers  |                                |                         |            |           |            |

| SPI0_DATA       | Input/Output Data              | 0x4000_4000             |            |           |            |

| SPI0_CONTROL    | Module Control                 | 0x4000_4010             | Υ          | Υ         |            |

| SPI0_CONFIG     | Module Configuration           | 0x4000_4020             | Υ          | Υ         |            |

| SPI0_CLKRATE    | Module Clock Rate Control      | 0x4000_4030             |            |           |            |

| SPI0_FSTATUS    | FIFO Status                    | 0x4000_4040             |            |           |            |

| SPI1 Registers  |                                |                         |            |           |            |

| SPI1_DATA       | Input/Output Data              | 0x4000_5000             |            |           |            |

| SPI1_CONTROL    | Module Control                 | 0x4000_5010             | Υ          | Υ         |            |

| SPI1_CONFIG     | Module Configuration           | 0x4000_5020             | Υ          | Υ         |            |

| SPI1_CLKRATE    | Module Clock Rate Control      | 0x4000_5030             |            |           |            |

| SPI1_FSTATUS    | FIFO Status                    | 0x4000_5040             |            |           |            |

**Table 3.1. Register Memory Map**

| Register Name  | Title                     | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | ()*0+) MSK |

|----------------|---------------------------|-------------------------|------------|-----------|------------|

| SPI2 Registers |                           |                         |            |           |            |

| SPI2_DATA      | Input/Output Data         | 0x4000_6000             |            |           |            |

| SPI2_CONTROL   | Module Control            | 0x4000_6010             | Υ          | Υ         |            |

| SPI2_CONFIG    | Module Configuration      | 0x4000_6020             | Υ          | Υ         |            |

| SPI2_CLKRATE   | Module Clock Rate Control | 0x4000_6030             |            |           |            |

| SPI2_FSTATUS   | FIFO Status               | 0x4000_6040             |            |           |            |

| I2C0 Registers |                           |                         |            |           |            |

| I2C0_CONTROL   | Module Control            | 0x4000_9000             | Υ          | Υ         |            |

| I2C0_CONFIG    | Module Configuration      | 0x4000_9010             | Υ          | Υ         |            |

| I2C0_SADDRESS  | Slave Address             | 0x4000_9020             |            |           |            |

| I2C0_SMASK     | Slave Address Mask        | 0x4000_9030             |            |           |            |

| I2C0_DATA      | Data Buffer Access        | 0x4000_9040             |            |           |            |

| I2C0_TIMER     | Timer Data                | 0x4000_9050             |            |           |            |

| I2C0_TIMERRL   | Timer Reload Values       | 0x4000_9060             |            |           |            |

| I2C0_SCONFIG   | SCL Signal Configuration  | 0x4000_9070             |            |           |            |

| I2C0_I2CDMA    | DMA Configuration         | 0x4000_9080             |            |           |            |

| I2C1 Registers |                           |                         |            |           |            |

| I2C1_CONTROL   | Module Control            | 0x4000_A000             | Υ          | Υ         |            |

| I2C1_CONFIG    | Module Configuration      | 0x4000_A010             | Υ          | Υ         |            |

| I2C1_SADDRESS  | Slave Address             | 0x4000_A020             |            |           |            |

| I2C1_SMASK     | Slave Address Mask        | 0x4000_A030             |            |           |            |

| I2C1_DATA      | Data Buffer Access        | 0x4000_A040             |            |           |            |

| I2C1_TIMER     | Timer Data                | 0x4000_A050             |            |           |            |

| I2C1_TIMERRL   | Timer Reload Values       | 0x4000_A060             |            |           |            |

| I2C1_SCONFIG   | SCL Signal Configuration  | 0x4000_A070             |            |           |            |

Table 3.1. Register Memory Map

| Register Name      | Title                           | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|--------------------|---------------------------------|-------------------------|------------|-----------|------------|

| EPCA0 Registers    |                                 |                         |            |           |            |

| EPCA0_CH0_MODE     | Channel Capture/Compare Mode    | 0x4000_E000             |            |           |            |

| EPCA0_CH0_CONTROL  | Channel Capture/Compare Control | 0x4000_E010             | Υ          | Υ         |            |

| EPCA0_CH0_CCAPV    | Channel Compare Value           | 0x4000_E020             |            |           |            |

| EPCA0_CH0_CCAPVUPD | Channel Compare Update Value    | 0x4000_E030             |            |           |            |

| EPCA0_CH1_MODE     | Channel Capture/Compare Mode    | 0x4000_E040             |            |           |            |

| EPCA0_CH1_CONTROL  | Channel Capture/Compare Control | 0x4000_E050             | Υ          | Υ         |            |

| EPCA0_CH1_CCAPV    | Channel Compare Value           | 0x4000_E060             |            |           |            |

| EPCA0_CH1_CCAPVUPD | Channel Compare Update Value    | 0x4000_E070             |            |           |            |

| EPCA0_CH2_MODE     | Channel Capture/Compare Mode    | 0x4000_E080             |            |           |            |

| EPCA0_CH2_CONTROL  | Channel Capture/Compare Control | 0x4000_E090             | Υ          | Υ         |            |

| EPCA0_CH2_CCAPV    | Channel Compare Value           | 0x4000_E0A0             |            |           |            |

| EPCA0_CH2_CCAPVUPD | Channel Compare Update Value    | 0x4000_E0B0             |            |           |            |

| EPCA0_CH3_MODE     | Channel Capture/Compare Mode    | 0x4000_E0C0             |            |           |            |

| EPCA0_CH3_CONTROL  | Channel Capture/Compare Control | 0x4000_E0D0             | Υ          | Υ         |            |

| EPCA0_CH3_CCAPV    | Channel Compare Value           | 0x4000_E0E0             |            |           |            |

| EPCA0_CH3_CCAPVUPD | Channel Compare Update Value    | 0x4000_E0F0             |            |           |            |

| EPCA0_CH4_MODE     | Channel Capture/Compare Mode    | 0x4000_E100             |            |           |            |

| EPCA0_CH4_CONTROL  | Channel Capture/Compare Control | 0x4000_E110             | Υ          | Υ         |            |

| EPCA0_CH4_CCAPV    | Channel Compare Value           | 0x4000_E120             |            |           |            |

| EPCA0_CH4_CCAPVUPD | Channel Compare Update Value    | 0x4000_E130             |            |           |            |

| EPCA0_CH5_MODE     | Channel Capture/Compare Mode    | 0x4000_E140             |            |           |            |

| EPCA0_CH5_CONTROL  | Channel Capture/Compare Control | 0x4000_E150             | Υ          | Υ         |            |

| EPCA0_CH5_CCAPV    | Channel Compare Value           | 0x4000_E160             |            |           |            |

| EPCA0_CH5_CCAPVUPD | Channel Compare Update Value    | 0x4000_E170             |            |           |            |

| EPCA0_MODE         | Module Operating Mode           | 0x4000_E180             |            |           |            |

| EPCA0_CONTROL      | Module Control                  | 0x4000_E190             | Υ          | Υ         |            |

SILICON LABS

**Table 3.1. Register Memory Map**

| Table 3.1. Register Memory Map |                                  |                         |            |           |            |  |  |  |  |

|--------------------------------|----------------------------------|-------------------------|------------|-----------|------------|--|--|--|--|

| Register Name                  | Title                            | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |  |  |  |  |

| EPCA0_STATUS                   | Module Status                    | 0x4000_E1A0             | Υ          | Υ         |            |  |  |  |  |

| EPCA0_COUNTER                  | Module Counter/Timer             | 0x4000_E1B0             |            |           |            |  |  |  |  |

| EPCA0_LIMIT                    | Module Upper Limit               | 0x4000_E1C0             |            |           |            |  |  |  |  |

| EPCA0_LIMITUPD                 | Module Upper Limit Update Value  | 0x4000_E1D0             |            |           |            |  |  |  |  |

| EPCA0_DTIME                    | Phase Delay Time                 | 0x4000_E1E0             |            |           |            |  |  |  |  |

| EPCA0_DTARGET                  | DMA Transfer Target              | 0x4000_E200             |            |           |            |  |  |  |  |

| PCA0 Registers                 | ·                                |                         |            |           |            |  |  |  |  |

| PCA0_CH0_MODE                  | Channel Capture/Compare Mode     | 0x4000_F000             |            |           |            |  |  |  |  |

| PCA0_CH0_CONTROL               | Channel Capture/Compare Control  | 0x4000_F010             | Υ          | Υ         |            |  |  |  |  |

| PCA0_CH0_CCAPV                 | Channel Compare Value            | 0x4000_F020             |            |           |            |  |  |  |  |

| PCA0_CH0_CCAPVUPD              | Channel Compare Update Value     | 0x4000_F030             |            |           |            |  |  |  |  |

| PCA0_CH1_MODE                  | Channel Capture/Compare Mode     | 0x4000_F040             |            |           |            |  |  |  |  |

| PCA0_CH1_CONTROL               | Channel Capture/Compare Control  | 0x4000_F050             | Υ          | Υ         |            |  |  |  |  |

| PCA0_CH1_CCAPV                 | Channel Compare Value            | 0x4000_F060             |            |           |            |  |  |  |  |

| PCA0_CH1_CCAPVUPD              | Channel Compare Update Value     | 0x4000_F070             |            |           |            |  |  |  |  |

| PCA0_MODE                      | Module Operating Mode            | 0x4000_F180             |            |           |            |  |  |  |  |

| PCA0_CONTROL                   | Module Control                   | 0x4000_F190             | Υ          | Υ         |            |  |  |  |  |

| PCA0_STATUS                    | Module Status                    | 0x4000_F1A0             | Υ          | Υ         |            |  |  |  |  |

| PCA0_COUNTER                   | Module Counter/Timer             | 0x4000_F1B0             |            |           |            |  |  |  |  |

| PCA0_LIMIT                     | Module Counter/Timer Upper Limit | 0x4000_F1C0             |            |           |            |  |  |  |  |

| PCA1 Registers                 | ·                                |                         |            |           |            |  |  |  |  |

| PCA1_CH0_MODE                  | Channel Capture/Compare Mode     | 0x4001_0000             |            |           |            |  |  |  |  |

| PCA1_CH0_CONTROL               | Channel Capture/Compare Control  | 0x4001_0010             | Υ          | Υ         |            |  |  |  |  |

| PCA1_CH0_CCAPV                 | Channel Compare Value            | 0x4001_0020             |            |           |            |  |  |  |  |

| PCA1_CH0_CCAPVUPD              | Channel Compare Update Value     | 0x4001_0030             |            |           |            |  |  |  |  |

| PCA1_CH1_MODE                  | Channel Capture/Compare Mode     | 0x4001_0040             |            |           |            |  |  |  |  |

| PCA1_CH1_CONTROL               | Channel Capture/Compare Control  | 0x4001_0050             | Υ          | Υ         |            |  |  |  |  |

Table 3.1. Register Memory Map

| Register Name     | Title                                 | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|-------------------|---------------------------------------|-------------------------|------------|-----------|------------|

| PCA1_CH1_CCAPV    | Channel Compare Value                 | 0x4001_0060             |            |           |            |

| PCA1_CH1_CCAPVUPD | Channel Compare Update Value          | 0x4001_0070             |            |           |            |

| PCA1_MODE         | Module Operating Mode                 | 0x4001_0180             |            |           |            |

| PCA1_CONTROL      | Module Control                        | 0x4001_0190             | Υ          | Υ         |            |

| PCA1_STATUS       | Module Status                         | 0x4001_01A0             | Υ          | Υ         |            |

| PCA1_COUNTER      | Module Counter/Timer                  | 0x4001_01B0             |            |           |            |

| PCA1_LIMIT        | Module Counter/Timer Upper Limit      | 0x4001_01C0             |            |           |            |

| TIMER0 Registers  |                                       |                         |            |           |            |

| TIMER0_CONFIG     | High and Low Timer Configuration      | 0x4001_4000             | Υ          | Υ         |            |

| TIMER0_CLKDIV     | Module Clock Divider Control          | 0x4001_4010             |            |           |            |

| TIMER0_COUNT      | Timer Value                           | 0x4001_4020             |            |           |            |

| TIMER0_CAPTURE    | Timer Capture/Reload Value            | 0x4001_4030             |            |           |            |

| TIMER1 Registers  |                                       |                         |            |           |            |

| TIMER1_CONFIG     | High and Low Timer Configuration      | 0x4001_5000             | Υ          | Υ         |            |

| TIMER1_CLKDIV     | Module Clock Divider Control          | 0x4001_5010             |            |           |            |

| TIMER1_COUNT      | Timer Value                           | 0x4001_5020             |            |           |            |

| TIMER1_CAPTURE    | Timer Capture/Reload Value            | 0x4001_5030             |            |           |            |

| USB0 Registers    |                                       |                         |            |           |            |

| USB0_FADDR        | Function Address                      | 0x4001_8000             |            |           |            |

| USB0_POWER        | Power Control                         | 0x4001_8010             |            |           |            |

| USB0_IOINT        | IN/OUT Endpoint Interrupt Flags       | 0x4001_8020             |            | Υ         |            |

| USB0_CMINT        | Common Interrupt Flags                | 0x4001_8030             |            | Υ         |            |

| USB0_IOINTE       | IN/OUT Endpoint Interrupt Control     | 0x4001_8040             |            |           |            |

| USB0_CMINTEPE     | Common Interrupt and Endpoint Control | 0x4001_8050             |            |           |            |

| USB0_CRCONTROL    | Clock Recovery Control                | 0x4001_8060             |            |           |            |

| USB0_FRAME        | Frame Number                          | 0x4001_8070             |            |           |            |

| USB0_TCONTROL     | Transceiver Control                   | 0x4001_8200             |            |           |            |

SILICON LABS

**Table 3.1. Register Memory Map**

| Register Name      | Title                                  | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|--------------------|----------------------------------------|-------------------------|------------|-----------|------------|

| USB0_CLKSEL        | Module Clock Select                    | 0x4001_8300             |            |           |            |

| USB0_OSCCONTROL    | Oscillator Control                     | 0x4001_8310             | Υ          | Υ         |            |

| USB0_AFADJUST      | Oscillator Additional Frequency Adjust | 0x4001_8320             | Υ          | Υ         |            |

| USB0_FADJUST       | Oscillator Frequency Adjust            | 0x4001_8330             |            |           |            |

| USB0_DMAFIFO       | DMA Data FIFO Access                   | 0x4001_8400             |            |           |            |

| USB0_DMACONTROL    | DMA Control                            | 0x4001_8410             |            |           |            |

| USB0_EP0CONTROL    | Endpoint 0 Control                     | 0x4001_8810             |            |           |            |

| USB0_EP0COUNT      | Endpoint 0 Data Count                  | 0x4001_8820             |            |           |            |

| USB0_EP0FIFO       | Endpoint 0 Data FIFO Access            | 0x4001_8830             |            |           |            |

| USB0_EP1_EPMPSIZE  | Endpoint Maximum Packet Size           | 0x4001_8880             |            |           |            |

| USB0_EP1_EPCONTROL | Endpoint Control                       | 0x4001_8890             |            |           |            |

| USB0_EP1_EPCOUNT   | Endpoint Data Count                    | 0x4001_88A0             |            |           |            |

| USB0_EP1_EPFIFO    | Endpoint Data FIFO Access              | 0x4001_88B0             |            |           |            |

| USB0_EP2_EPMPSIZE  | Endpoint Maximum Packet Size           | 0x4001_8900             |            |           |            |

| USB0_EP2_EPCONTROL | Endpoint Control                       | 0x4001_8910             |            |           |            |

| USB0_EP2_EPCOUNT   | Endpoint Data Count                    | 0x4001_8920             |            |           |            |

| USB0_EP2_EPFIFO    | Endpoint Data FIFO Access              | 0x4001_8930             |            |           |            |

| USB0_EP3_EPMPSIZE  | Endpoint Maximum Packet Size           | 0x4001_8980             |            |           |            |

| USB0_EP3_EPCONTROL | Endpoint Control                       | 0x4001_8990             |            |           |            |

| USB0_EP3_EPCOUNT   | Endpoint Data Count                    | 0x4001_89A0             |            |           |            |

| USB0_EP3_EPFIFO    | Endpoint Data FIFO Access              | 0x4001_89B0             |            |           |            |

| USB0_EP4_EPMPSIZE  | Endpoint Maximum Packet Size           | 0x4001_8A00             |            |           |            |

| USB0_EP4_EPCONTROL | Endpoint Control                       | 0x4001_8A10             |            |           |            |

| USB0_EP4_EPCOUNT   | Endpoint Data Count                    | 0x4001_8A20             |            |           |            |

| USB0_EP4_EPFIFO    | Endpoint Data FIFO Access              | 0x4001_8A30             |            |           |            |

Table 3.1. Register Memory Map

| Register Name      | Title                                   | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|--------------------|-----------------------------------------|-------------------------|------------|-----------|------------|

| SARADC0 Registers  |                                         |                         |            |           |            |

| SARADC0_CONFIG     | Module Configuration                    | 0x4001_A000             | Υ          | Υ         |            |

| SARADC0_CONTROL    | Measurement Control                     | 0x4001_A010             | Υ          | Υ         |            |

| SARADC0_SQ7654     | Channel Sequencer Time Slots 4-7 Setup  | 0x4001_A020             |            |           |            |

| SARADC0_SQ3210     | Channel Sequencer Time Slots 0-3 Setup  | 0x4001_A030             |            |           |            |

| SARADC0_CHAR32     | Conversion Characteristic 2 and 3 Setup | 0x4001_A040             | Υ          | Υ         |            |

| SARADC0_CHAR10     | Conversion Characteristic 0 and 1 Setup | 0x4001_A050             | Υ          | Υ         |            |

| SARADC0_DATA       | Output Data Word                        | 0x4001_A060             |            |           |            |

| SARADC0_WCLIMITS   | Window Comparator Limits                | 0x4001_A070             |            |           |            |

| SARADC0_ACC        | Accumulator Initial Value               | 0x4001_A080             |            |           |            |

| SARADC0_STATUS     | Module Status                           | 0x4001_A090             | Υ          | Υ         |            |

| SARADC0_FIFOSTATUS | FIFO Status                             | 0x4001_A0A0             |            |           |            |

| SARADC1 Registers  |                                         |                         |            |           |            |

| SARADC1_CONFIG     | Module Configuration                    | 0x4001_B000             | Υ          | Υ         |            |

| SARADC1_CONTROL    | Measurement Control                     | 0x4001_B010             | Υ          | Υ         |            |

| SARADC1_SQ7654     | Channel Sequencer Time Slots 4-7 Setup  | 0x4001_B020             |            |           |            |

| SARADC1_SQ3210     | Channel Sequencer Time Slots 0-3 Setup  | 0x4001_B030             |            |           |            |

| SARADC1_CHAR32     | Conversion Characteristic 2 and 3 Setup | 0x4001_B040             | Υ          | Υ         |            |

| SARADC1_CHAR10     | Conversion Characteristic 0 and 1 Setup | 0x4001_B050             | Υ          | Υ         |            |

| SARADC1_DATA       | Output Data Word                        | 0x4001_B060             |            |           |            |

| SARADC1_WCLIMITS   | Window Comparator Limits                | 0x4001_B070             |            |           |            |

| SARADC1_ACC        | Accumulator Initial Value               | 0x4001_B080             |            |           |            |

| SARADC1_STATUS     | Module Status                           | 0x4001_B090             | Υ          | Υ         |            |

| SARADC1_FIFOSTATUS | FIFO Status                             | 0x4001_B0A0             |            |           |            |

| SSG0 Registers     |                                         |                         |            |           |            |

| SSG0_CONFIG        | Module Configuration                    | 0x4001_E000             |            |           |            |

| SSG0_CONTROL       | Module Control                          | 0x4001_E010             | Υ          | Υ         |            |

SILICON LABS

**Table 3.1. Register Memory Map**

| Register Name       | Title                          | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|---------------------|--------------------------------|-------------------------|------------|-----------|------------|

| CMP0 Registers      |                                |                         |            |           |            |

| CMP0_CONTROL        | Module Control                 | 0x4001_F000             | Υ          | Υ         |            |

| CMP0_MODE           | Input and Module Mode          | 0x4001_F010             | Υ          | Υ         |            |

| CMP1 Registers      |                                |                         |            |           |            |

| CMP1_CONTROL        | Module Control                 | 0x4002_0000             | Υ          | Υ         |            |

| CMP1_MODE           | Input and Module Mode          | 0x4002_0010             | Υ          | Υ         |            |

| CAPSENSE0 Registers |                                |                         |            |           |            |

| CAPSENSE0_CONTROL   | Module Control                 | 0x4002_3000             | Υ          | Υ         |            |

| CAPSENSE0_MODE      | Measurement Mode               | 0x4002_3010             | Υ          | Υ         |            |

| CAPSENSE0_DATA      | Measurement Data               | 0x4002_3020             |            |           |            |

| CAPSENSE0_SCAN      | Channel Scan Enable            | 0x4002_3030             |            |           |            |

| CAPSENSE0_CSTH      | Compare Threshold              | 0x4002_3040             |            |           |            |

| CAPSENSE0_MUX       | Mux Channel Select             | 0x4002_3050             |            |           |            |

| EMIF0 Registers     |                                |                         |            |           |            |

| EMIF0_CONTROL       | Module Control                 | 0x4002_6000             | Υ          | Υ         |            |

| EMIF0_STATUS        | Module Status                  | 0x4002_6020             |            |           |            |

| EMIF0_IF0_CONFIG    | Interface Configuration        | 0x4002_6080             | Υ          | Υ         |            |

| EMIF0_IF0_IFRT      | Interface Read Timing          | 0x4002_6090             |            |           |            |

| EMIF0_IF0_IFWT      | Interface Write Timing         | 0x4002_60A0             |            |           |            |

| EMIF0_IF0_IFRCST    | Interface Read Control States  | 0x4002_60B0             |            |           |            |

| EMIF0_IF0_IFWCST    | Interface Write Control States | 0x4002_60C0             |            |           |            |

| EMIF0_IF1_CONFIG    | Interface Configuration        | 0x4002_6100             | Υ          | Υ         |            |

| EMIF0_IF1_IFRT      | Interface Read Timing          | 0x4002_6110             |            |           |            |

| EMIF0_IF1_IFWT      | Interface Write Timing         | 0x4002_6120             |            |           |            |

| EMIF0_IF1_IFRCST    | Interface Read Control States  | 0x4002_6130             |            |           |            |

| EMIF0_IF1_IFWCST    | Interface Write Control States | 0x4002_6140             |            |           |            |

Table 3.1. Register Memory Map

| Register Name  | Title                         | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|----------------|-------------------------------|-------------------------|------------|-----------|------------|

| AES0 Registers |                               |                         |            |           |            |

| AES0_CONTROL   | Module Control                | 0x4002_7000             | Υ          | Υ         |            |

| AES0_XFRSIZE   | Number of Blocks              | 0x4002_7010             |            |           |            |

| AES0_DATAFIFO  | Input/Output Data FIFO Access | 0x4002_7020             |            |           |            |

| AES0_XORFIFO   | XOR Data FIFO Access          | 0x4002_7030             |            |           |            |

| AES0_HWKEY0    | Hardware Key Word 0           | 0x4002_7040             |            |           |            |

| AES0_HWKEY1    | Hardware Key Word 1           | 0x4002_7050             |            |           |            |

| AES0_HWKEY2    | Hardware Key Word 2           | 0x4002_7060             |            |           |            |

| AES0_HWKEY3    | Hardware Key Word 3           | 0x4002_7070             |            |           |            |

| AES0_HWKEY4    | Hardware Key Word 4           | 0x4002_7080             |            |           |            |

| AES0_HWKEY5    | Hardware Key Word 5           | 0x4002_7090             |            |           |            |

| AES0_HWKEY6    | Hardware Key Word 6           | 0x4002_70A0             |            |           |            |

| AES0_HWKEY7    | Hardware Key Word 7           | 0x4002_70B0             |            |           |            |

| AES0_HWCTR0    | Hardware Counter Word 0       | 0x4002_70C0             |            |           |            |

| AES0_HWCTR1    | Hardware Counter Word 1       | 0x4002_70D0             |            |           |            |

| AES0_HWCTR2    | Hardware Counter Word 2       | 0x4002_70E0             |            |           |            |

| AES0_HWCTR3    | Hardware Counter Word 3       | 0x4002_70F0             |            |           |            |

| AES0_STATUS    | Module Status                 | 0x4002_7100             | Υ          | Υ         |            |

| CRC0 Registers |                               |                         |            |           |            |

| CRC0_CONTROL   | Module Control                | 0x4002_8000             | Υ          | Υ         |            |

| CRC0_DATA      | Input/Result Data             | 0x4002_8010             |            |           |            |

| CRC0_RDATA     | Bit-Reversed Output Data      | 0x4002_8020             |            |           |            |

**Table 3.1. Register Memory Map**

| Register Name    | Title                       | Address<br>(ALL Access) | SET (+0x4) | CLR(+0x8) | MSK (+0xC) |

|------------------|-----------------------------|-------------------------|------------|-----------|------------|

| RTC0 Registers   |                             | I                       |            |           |            |

| RTC0_CONFIG      | RTC Configuration           | 0x4002_9000             | Υ          | Υ         |            |

| RTC0_CONTROL     | RTC Control                 | 0x4002_9010             | Υ          | Υ         |            |

| RTC0_ALARM0      | RTC Alarm 0                 | 0x4002_9020             |            |           |            |

| RTC0_ALARM1      | RTC Alarm 1                 | 0x4002_9030             |            |           |            |

| RTC0_ALARM2      | RTC Alarm 2                 | 0x4002_9040             |            |           |            |

| RTC0_SETCAP      | RTC Timer Set/Capture Value | 0x4002_9050             |            |           |            |

| RTC0_LFOCONTROL  | LFOSC Control               | 0x4002_9060             |            |           |            |

| PBCFG0 Registers |                             |                         |            |           |            |

| PBCFG0_CONTROL0  | Global Port Control 0       | 0x4002_A000             | Υ          | Υ         |            |

| PBCFG0_CONTROL1  | Global Port Control 1       | 0x4002_A010             | Υ          | Υ         |            |

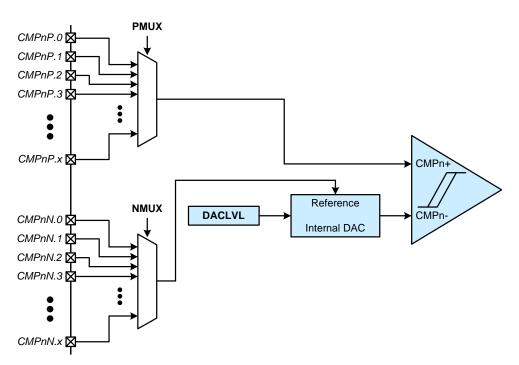

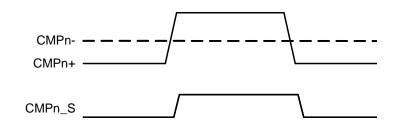

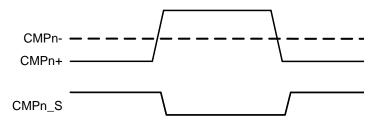

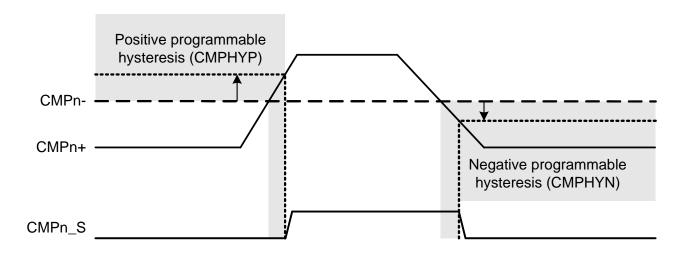

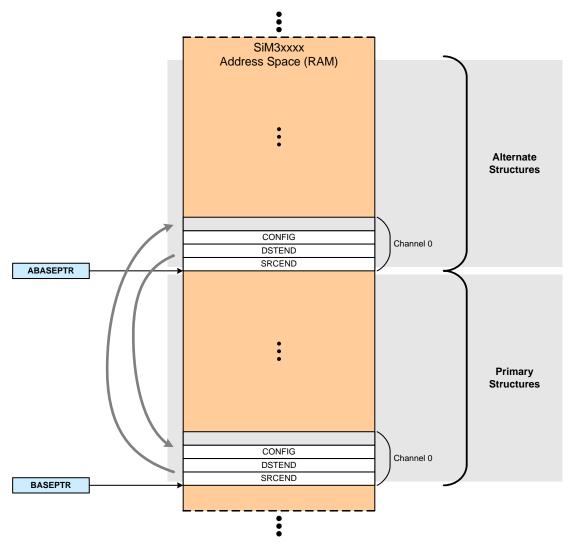

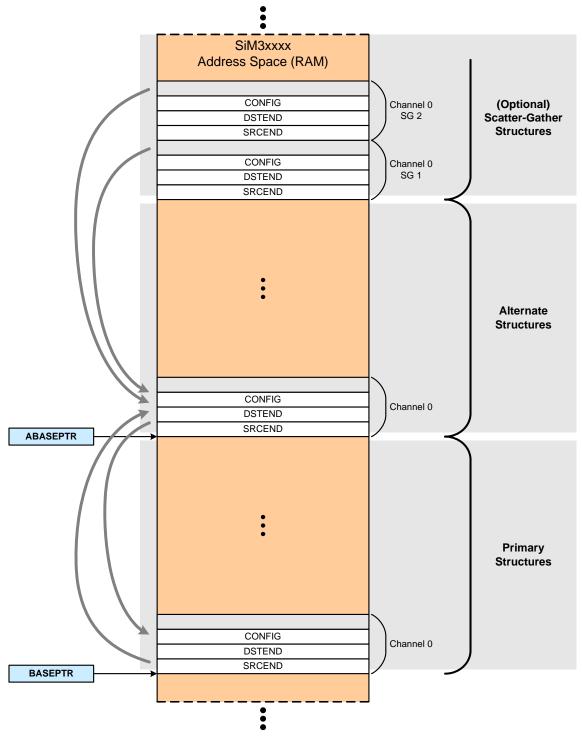

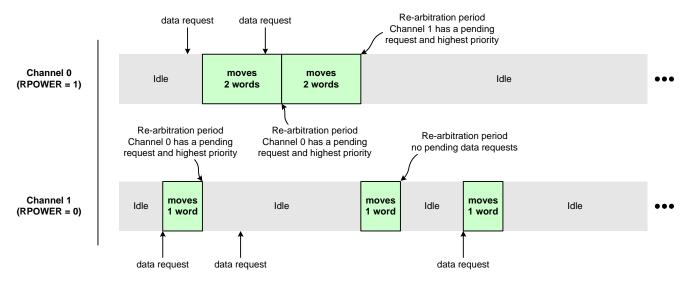

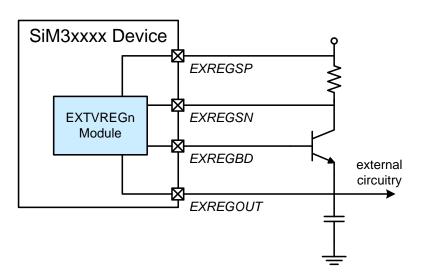

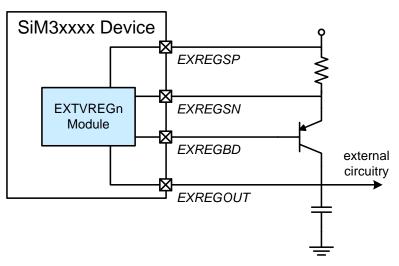

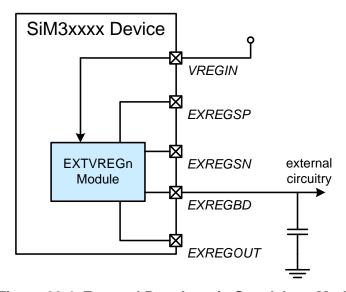

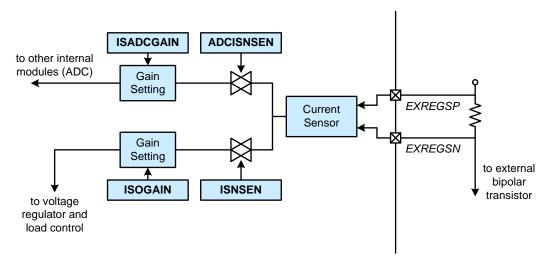

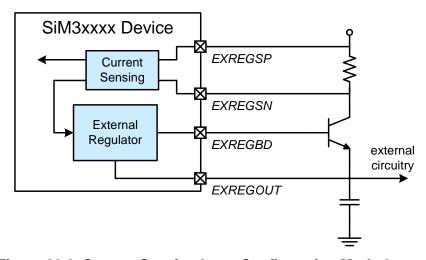

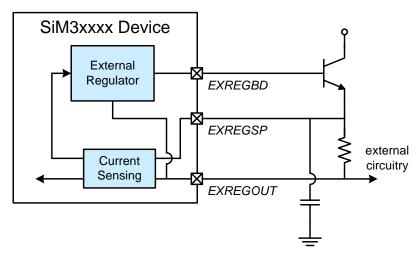

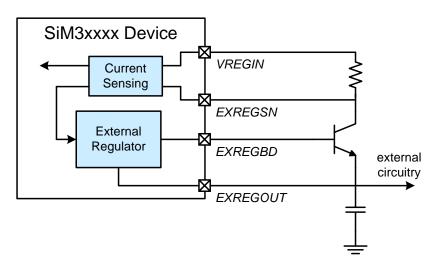

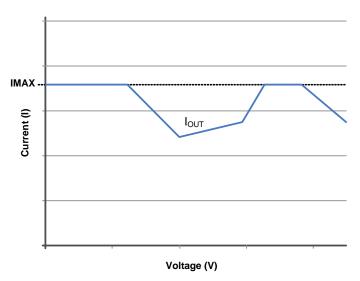

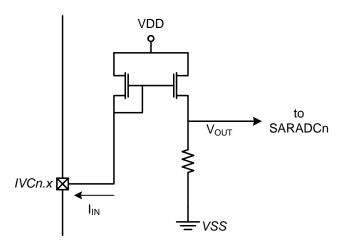

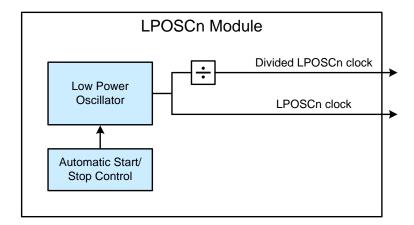

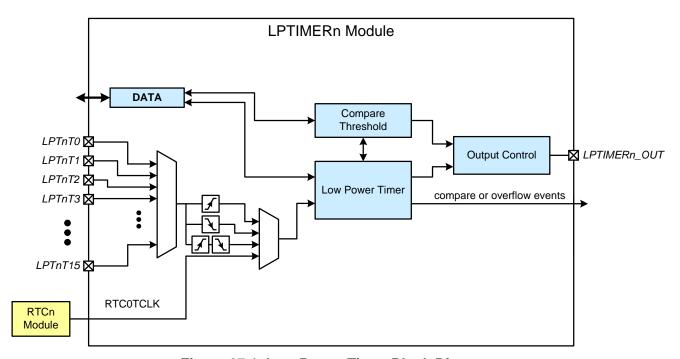

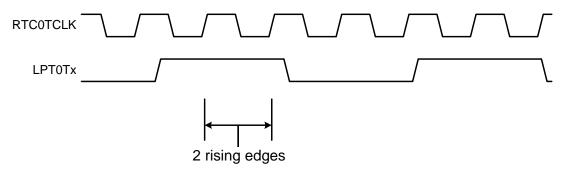

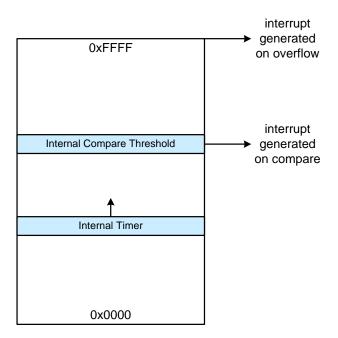

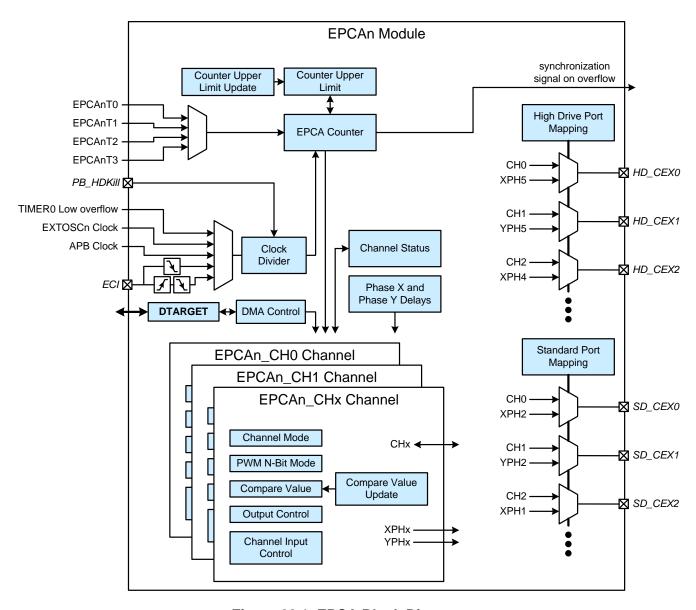

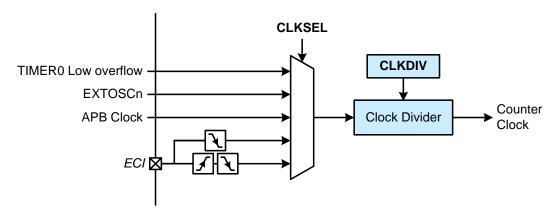

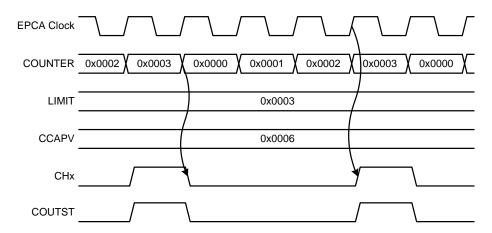

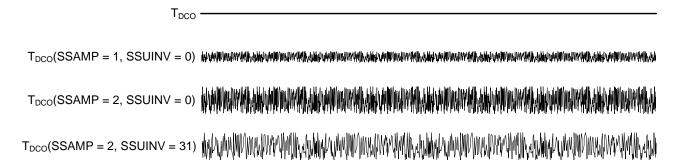

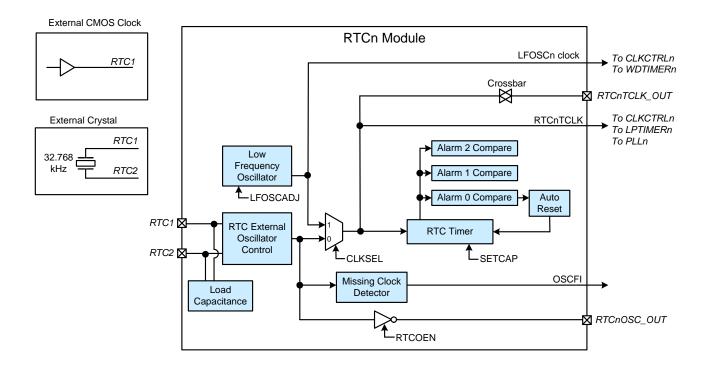

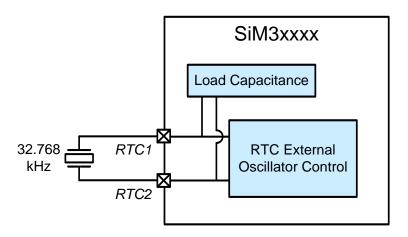

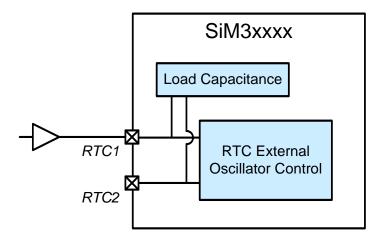

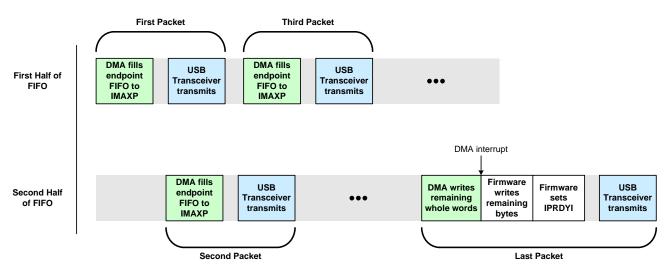

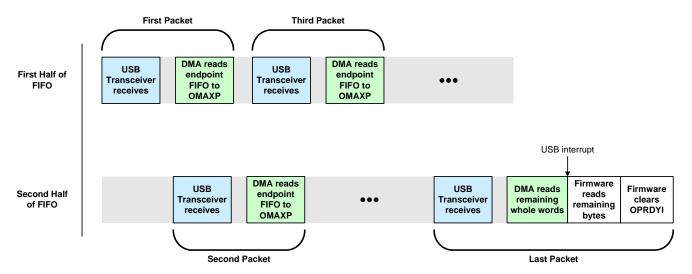

| PBCFG0_XBAR0L    | Crossbar 0 Control (Low)    | 0x4002_A020             | Υ          | Υ         |            |