# LMR61428 SIMPLE SWITCHER® 14Vout, 2.85A Step-Up Voltage Regulator in VSSOP

Check for Samples: LMR61428

#### **FEATURES**

- 1.2V to 14V Input Voltage

- Adjustable Output Voltage up to 14V

- Switch Current up to 2.85A

- Up to 2 MHz Switching Frequency

- Low Shutdown Iq, <1μA</li>

- Cycle-by-Cycle Current Limiting

- VSSOP Packaging (3.0 x 5.0 x 1.09mm)

- WEBENCH<sup>®</sup> Enabled

#### PERFORMANCE BENEFITS

- Extremely Easy to Use

- Tiny Overall Solution Reduces System Cost

#### **APPLICATIONS**

- Boost/SEPIC Conversions from 3.3V, 5V, and 12V

- Space Constrained Applications

- LCD Displays

- LED Applications

### **System Performance**

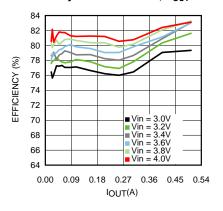

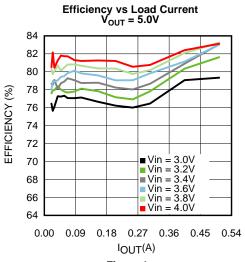

Efficiency vs Load Current, Vout = 5V

#### **DESCRIPTION**

The LMR61428 is a step-up DC-DC switching regulator for battery-powered and low input voltage systems that can achieve efficiencies up to 90%. It has a wide input voltage range from 1.2V to 14V and a possible regulated output voltage range of 1.24V to 14V. It has an internal  $0.17\Omega$  N-Channel MOSFET power switch.

The high switching frequency of up to 2MHz of the LMR61428 allows for tiny surface mount inductors and capacitors. Because of the unique constant-duty-cycle gated oscillator topology very high efficiencies are realized over a wide load range. The supply current is reduced to  $80\mu A$  because of the BiCMOS process technology. In the shutdown mode, the supply current is less than  $2.5\mu A$ . The LMR61428 is available in a VSSOP-8 package.

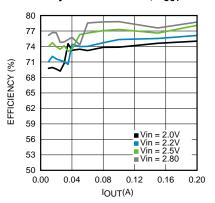

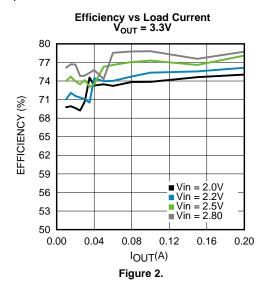

Efficiency vs Load Current, Vout = 3.3V

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SIMPLE SWITCHER, WEBENCH are registered trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

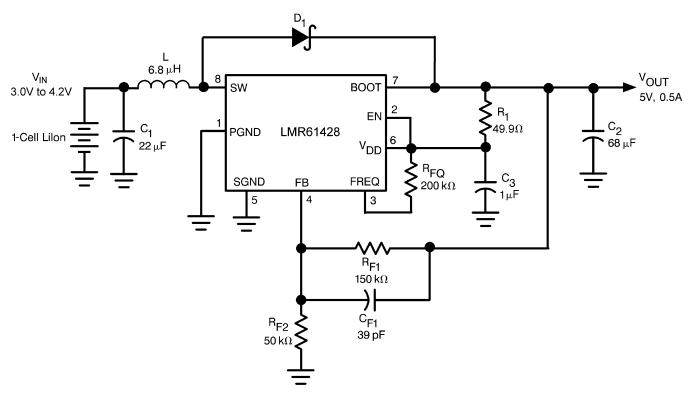

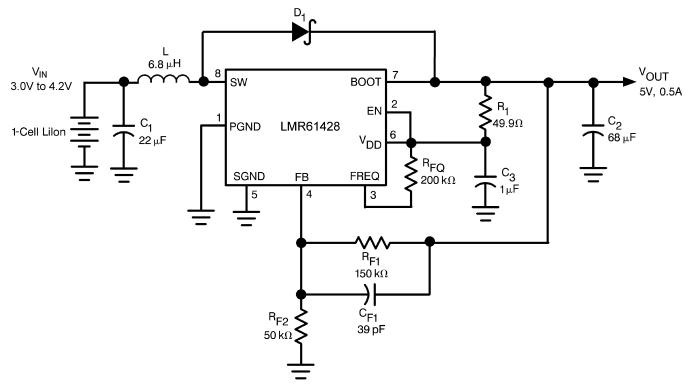

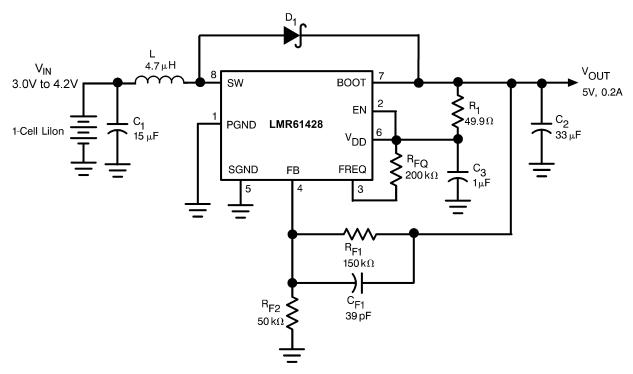

### **Typical Application Circuit**

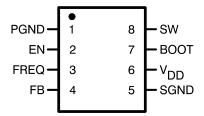

### **Connection Diagram**

VSSOP Package (Top View) See Package Number DGK

#### **PIN DESCRIPTION**

| Pin | Name     | Function                                                                                                                                     |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PGND     | Power Ground                                                                                                                                 |

| 2   | EN       | Active-Low Shutdown Input                                                                                                                    |

| 3   | FREQ     | Frequency Adjust. An external resistor connected between this pin and Pin 6 (V <sub>DD</sub> ) sets the switching frequency of the LMR61428. |

| 4   | FB       | Output Voltage Feedback                                                                                                                      |

| 5   | SGND     | Signal Ground                                                                                                                                |

| 6   | $V_{DD}$ | Power Supply for Internal Circuitry                                                                                                          |

| 7   | BOOT     | Bootstrap Supply for the Gate Drive of Internal MOSFET Power Switch                                                                          |

| 8   | SW       | Drain of the Internal MOSFET Power Switch                                                                                                    |

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **Absolute Maximum Ratings**(1)(2)

| −0.5 V to 14.5V |

|-----------------|

| −0.5V to 10V    |

| 100μΑ           |

| 240°C/W         |

| 150°C           |

| −65°C to +150°C |

| 260°C           |

| 500mW           |

| 2kV             |

|                 |

- (1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>jmax</sub> (maximum junction temperature), θ<sub>JA</sub> (junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is P<sub>dmax</sub> = (T<sub>jmax</sub> T<sub>A</sub>)/ θ<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower.

- (4) The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. For Pin 8 (SW) the ESD rating is 1.5 kV

### Operating Conditions<sup>(1)</sup>

| V <sub>DD</sub> Pin                   | 2.5V to 5V           |

|---------------------------------------|----------------------|

| FB, EN Pins                           | 0 to V <sub>DD</sub> |

| BOOT Pin                              | 0 to 10V             |

| Ambient Temperature (T <sub>A</sub> ) | −40°C to +85°C       |

(1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

#### **Electrical Characteristics**

Limits in standard typeface are for  $T_J = 25^{\circ}\text{C}$ , and limits in **boldface** type apply over the full operating temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Unless otherwise specified:  $V_{DD} = V_{OUT} = 3.3V$ .

| Symbol               | Parameter                                       | Condition                                                    | Min                | Тур  | Max                 | Units |  |

|----------------------|-------------------------------------------------|--------------------------------------------------------------|--------------------|------|---------------------|-------|--|

| V <sub>IN_ST</sub>   | Minimum Start-Up Supply Voltage                 | I <sub>LOAD</sub> = 0mA                                      |                    | 1.1  | 1.2                 | V     |  |

| V <sub>IN_OP</sub>   | Minimum Operating Supply Voltage (once started) | $I_{LOAD} = 0mA$                                             |                    | 0.65 |                     | V     |  |

| V <sub>FB</sub>      | FB Pin Voltage                                  |                                                              | 1.2028             | 1.24 | 1.2772              | V     |  |

| V <sub>OUT_MAX</sub> | Maximum Output Voltage                          |                                                              |                    | 14   |                     | V     |  |

| V <sub>HYST</sub>    | Hysteresis Voltage <sup>(2)</sup>               | At Feedback Pin                                              |                    | 30   | 45                  | mV    |  |

| η                    | Efficiency                                      | $V_{IN} = 3.6V; V_{OUT} = 5V; I_{LOAD} = 0.5A$               |                    | 87   |                     | 0/    |  |

|                      |                                                 | $V_{IN} = 2.5V; V_{OUT} = 3.3V; I_{LOAD} = 0.2A$             |                    | 87   |                     | %     |  |

| D                    | Switch Duty Cycle                               |                                                              | 60                 | 70   | 80                  | %     |  |

| I <sub>DD</sub>      | Operating Quiescent Current <sup>(3)</sup>      | FB Pin > 1.3V; EN Pin at V <sub>DD</sub>                     |                    | 80   | 110                 | μΑ    |  |

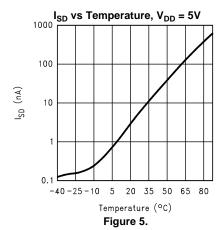

| I <sub>SD</sub>      | Shutdown Quiescent Current (4)                  | V <sub>DD</sub> , BOOT and SW Pins at 5.0V;<br>EN Pin <200mV |                    | 0.01 | 2.5                 | μΑ    |  |

| I <sub>CL</sub>      | Switch Peak Current Limit                       |                                                              |                    | 2.85 |                     | Α     |  |

| R <sub>DS_ON</sub>   | MOSFET Switch On Resistance                     |                                                              |                    | 0.17 |                     | Ω     |  |

| Enable Section       | on                                              |                                                              |                    |      | <u>"</u>            |       |  |

| V <sub>EN_LO</sub>   | EN Pin Voltage Low <sup>(5)</sup>               |                                                              |                    |      | 0.15V <sub>DD</sub> | V     |  |

| V <sub>EN_HI</sub>   | EN Pin Voltage High <sup>(5)</sup>              |                                                              | 0.7V <sub>DD</sub> |      |                     | V     |  |

Output in regulation,  $V_{OUT} = V_{OUT}$  (NOMINAL)  $\pm$  5% This is the hysteresis value of the internal comparator used for the gated-oscillator control scheme. This is the current into the  $V_{DD}$  pin.

This is the total current into pins  $V_{DD}$ , BOOT, SW and FREQ. When the EN pin is below  $V_{EN\_LO}$ , the regulator is shut down; when it is above  $V_{EN\_HI}$ , the regulator is operating.

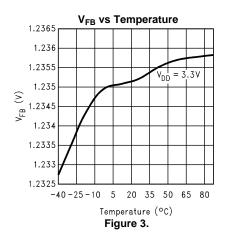

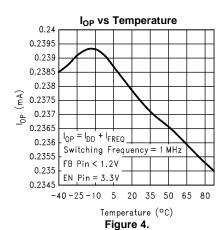

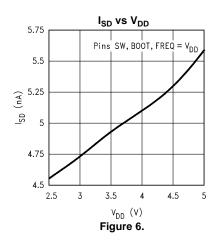

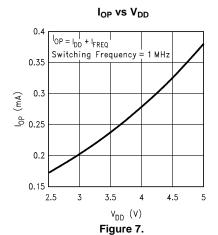

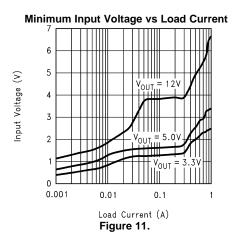

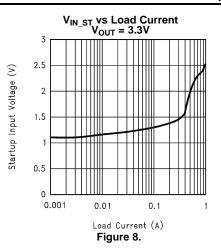

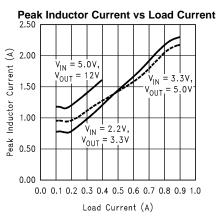

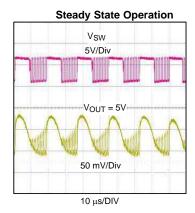

#### TYPICAL PERFORMANCE CHARACTERISTICS

All curves taken at T<sub>A</sub> = 25°C, unless specified otherwise.

Figure 1.

Copyright © 2012–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Figure 10.

Figure 12.

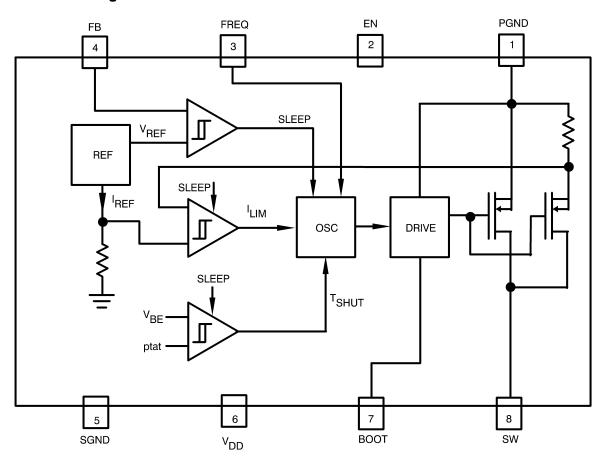

### **Simplified Block Diagram**

Figure 13. Block Diagram

#### **DETAILED DESCRIPTION**

#### **OPERATING PRINCIPLE**

The LMR61428 is designed to provide step-up DC-DC voltage regulation in battery-powered and low-input voltage systems. It combines a step-up switching regulator, N-channel power MOSFET, built-in current limit, thermal limit, and voltage reference in a single 8-pin VSSOP package. The switching DC-DC regulator boosts an input voltage between 1.2V and 14V to a regulated output voltage between 1.24V and 14V that is limited by a fixed maximum duty cylcle of 70%. The LMR61428 starts from a low 1.1V input and remains operational down to 0.65V.

This device is optimized for use in cellular phones and other applications requiring a small size, low profile, as well as low quiescent current for maximum battery life during stand-by and shutdown. A high-efficiency gated-oscillator topology offers an output of up to 1A.

Additional features include a built-in peak switch current limit, and thermal protection circuitry.

#### **GATED OSCILLATOR CONTROL SCHEME**

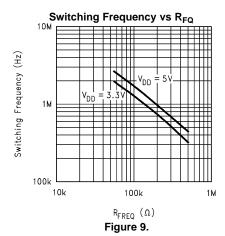

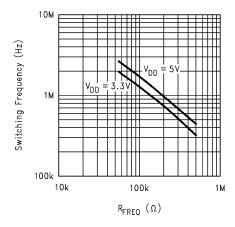

A unique gated oscillator control scheme enables the LMR61428 to have an ultra-low quiescent current and provides a high efficiency over a wide load range. The switching frequency of the internal oscillator is programmable using an external resistor and can be set between 300 kHz and 2 MHz.

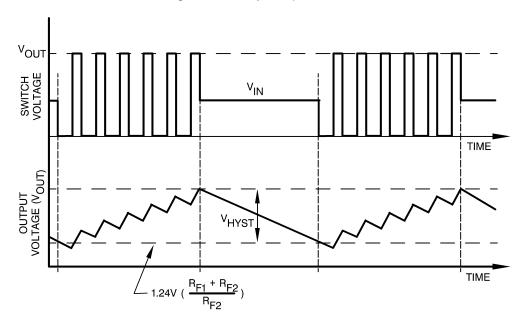

This control scheme uses a hysteresis window to regulate the output voltage. When the output voltage is below the upper threshold of the window, the LMR61428 switches continuously with a fixed duty cycle of 70% at the switching frequency selected by the user. During the first part of each switching cycle, the internal N-channel MOSFET switch is turned on. This causes the current to ramp up in the inductor and store energy. During the second part of each switching cycle, the MOSFET is turned off. The voltage across the inductor reverses and forces current through the diode to the output filter capacitor and the load. Thus when the LMR61428 switches continuously, the output voltage starts to ramp up. When the output voltage hits the upper threshold of the window, the LMR61428 stops switching completely. This causes the output voltage to droop because the energy stored in the output capacitor is depleted by the load. When the output voltage hits the lower threshold of the hysteresis window, the LMR61428 starts switching continuously again causing the output voltage to ramp up towards the upper threshold. Figure 14 shows the switch voltage and output voltage waveforms.

Because of this type of control scheme, the quiescent current is inherently very low. At light loads the gated oscillator control scheme offers a much higher efficiency compared to the conventional PWM control scheme.

Figure 14. Typical Step-Up Regulator Waveforms

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

#### **LOW VOLTAGE START-UP**

The LMR61428 can start-up from input voltages as low as 1.1V. On start-up, the control circuitry switches the N-channel MOSFET continuously at 70% duty cycle until the output voltage reaches 2.5V. After this output voltage is reached, the normal step-up regulator feedback and gated oscillator control scheme take over. Once the device is in regulation it can operate down to a 0.65V input, since the internal power for the IC can be bootstrapped from the output using the  $V_{DD}$  pin.

#### **SHUTDOWN**

The LMR61428 features a shutdown mode that reduces the quiescent current to less than an ensured  $2.5\mu A$  over temperature. This extends the life of the battery in battery powered applications. During shutdown, all feedback and control circuitry is turned off. The regulator's output voltage drops to one diode drop below the input voltage. Entry into the shutdown mode is controlled by the active-low logic input pin EN (Pin 2). When the logic input to this pin pulled below  $0.15V_{DD}$ , the device goes into shutdown mode. The logic input to this pin should be above  $0.7V_{DD}$  for the device to work in normal step-up mode.

#### **OUTPUT VOLTAGE RIPPLE FREQUENCY**

A major component of the output voltage ripple is due to the hysteresis used in the gated oscillator control scheme. The frequency of this voltage ripple is proportional to the load current. The frequency of this ripple does not necessitate the use of larger inductors and capacitors. The size of these components is determined by the switching frequency of the oscillator which can be set upto 2MHz using an external resistor.

#### INTERNAL CURRENT LIMIT AND THERMAL PROTECTION

An internal cycle-by-cycle current limit serves as a protection feature. This is set high enough (2.85A typical, approximately 4A maximum) so as not to come into effect during normal operating conditions. An internal thermal protection circuitry disables the MOSFET power switch when the junction temperature (T<sub>J</sub>) exceeds about 160°C. The switch is re-enabled when T<sub>J</sub> drops below approximately 135°C.

#### **Design Procedure**

#### **SETTING THE OUTPUT VOLTAGE**

The output voltage of the step-up regulator can be set between 1.24V and 14V. But because of the gated oscillator scheme, the maximum possible input to output boost ratio is fixed. For a boost regulator,

$$V_{OUT} / V_{IN} = 1 / [1-D]$$

(1)

The LMR61428 has a fixed duty cycle, D, of 70% typical. Therefore,

$$V_{OUT} / V_{IN} = 1 / 0.3$$

(2)

This sets the maximum possible boost ratio of  $V_{IN}$  to  $V_{OUT}$  to about 3 times. The user can now estimate what the minimum design inputs should be in order to achieve a desired output, or what the output would be when a certain minimum input is applied. E.g. If the desired  $V_{OUT}$  was 14V, then the least  $V_{IN}$  should be higher than  $V_{OUT}$  / 3. If the input voltage fell below this threshold, the output voltage would not be regulated because of the fixed duty cycle. If the minimum  $V_{IN}$  was ensured at 2V, the max possible  $V_{OUT}$  would be  $V_{IN}$  \* 3.

The  $V_{OUT}$  is set by connecting a feedback resistive divider made of  $R_{F1}$  and  $R_{F2}$ . The feedback resistor values are selected as follows:

$$R_{F2} = R_{F1} / [(V_{OUT} / 1.24) - 1]$$

(3)

A value of  $150k\Omega$  is suggested for  $R_{F1}$ . Then,  $R_{F2}$  can be selected using the above equation. A 39pF capacitor ( $C_{ff}$ ) connected across  $R_{F1}$  helps in feeding back most of the AC ripple at  $V_{OUT}$  to the FB pin. This helps reduce the peak-to-peak output voltage ripple as well as improve the efficiency of the step-up regulator, because a set hysteresis of 30mV at the FB pin is used for the gated oscillator control scheme.

#### **BOOTSTRAPPING**

When the output voltage ( $V_{OUT}$ ) is between 2.5V and 5.0V a bootstrapped operation is suggested. This is achieved by connecting the  $V_{DD}$  pin (Pin 6) to  $V_{OUT}$ . However if the  $V_{OUT}$  is outside this range, the  $V_{DD}$  pin should be connected to a voltage source whose range is between 2.5V and 5V. This can be the input voltage ( $V_{IN}$ ),  $V_{OUT}$  stepped down using a linear regulator, or a different voltage source available in the system. This is referred to as non-bootstrapped operation. The maximum acceptable voltage at the BOOT pin (Pin 7) is 10V.

#### SETTING THE SWITCHING FREQUENCY

The switching frequency of the oscillator is selected by choosing an external resistor ( $R_{FQ}$ ) connected between FREQ and  $V_{DD}$  pins. See the following graph, Figure 15, for choosing the  $R_{FQ}$  value to achieve the desired switching frequency. A high switching frequency allows the use of very small surface mount inductors and capacitors and results in a very small solution size. A switching frequency between 300kHz and 2MHz is recommended.

Figure 15. Switching Frequency vs R<sub>FQ</sub>

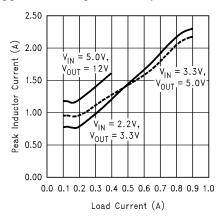

#### INDUCTOR SELECTION

The LMR61428's high switching frequency enables the use of a small surface mount inductor. A 6.8 $\mu$ H shielded inductor is suggested for a typical application. The inductor should have a saturation current rating higher than the peak current it will experience during circuit operation (see the following graph, Peak Inductor vs Load Current). Less than 100m $\Omega$  ESR is suggested for high efficiency.

Figure 16. Peak Inductor Current vs Load Current

Open-core inductors cause flux linkage with circuit components and interfere with the normal operation of the circuit. They should be avoided. For high efficiency, choose an inductor with a high frequency core material, such as ferrite, to reduce the core losses. To minimize radiated noise, use a toroid, pot core or shielded core inductor. The inductor should be connected to the SW pin as close to the IC as possible. See Connection Diagram.

#### **OUTPUT DIODE SELECTION**

A Schottky diode should be used for the output diode. The forward current rating of the diode should be higher than the load current, and the reverse voltage rating must be higher than the output voltage. Do not use ordinary rectifier diodes, since slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer.

#### INPUT AND OUTPUT FILTER CAPACITORS SELECTION

While tantalum chip capacitors are recommended for the input and output filter capacitors, ceramic caps can also be used. A  $22\mu F$  capacitor is suggested for the input filter capacitor. It should have a DC working voltage rating higher than the maximum input voltage. A  $68\mu F$  tantalum capacitor is suggested for the output capacitor. The DC working voltage rating should be greater than the output voltage. Very high ESR values (>3 $\Omega$ ) should be avoided.

#### PC BOARD LAYOUT

High switching frequencies and high peak currents make a proper layout of the PC board an important part of design. Poor design can cause excessive EMI and ground-bounce, both of which can cause malfunction and loss of regulation by corrupting voltage feedback signal and injecting noise into the control section.

Power components - such as the inductor, input and output filter capacitors, and output diode - should be placed as close to the regulator IC as possible, and their traces should be kept short, direct and wide. The ground pins of the input and output filter capacitors and the PGND and SGND pins of LMR61428 should be connected using short, direct and wide traces. The voltage feedback network ( $R_{fbt}$ ,  $R_{fbb}$ , and  $C_{ff}$ ) should be kept very close to the FB pin. Noisy traces, such as from the SW pin, should be kept away from the FB and  $V_{DD}$  pins. The traces that run between  $V_{out}$  and the FB pin of the IC should be kept away from the inductor flux. Always provide sufficient copper area to dissipate the heat due to power loss in the circuitry and prevent the thermal protection circuitry in the IC from shutting the IC down. Additional ground planes as intermediate levels help with shielding and improve EMI mitigation.

### **Application Examples**

Figure 17. EXAMPLE 1. 5V/0.5A Step-Up Regulator

| U1 | Texas Instruments | LMR61428XMM               |

|----|-------------------|---------------------------|

| C1 | Vishay/Sprague    | 595D226X06R3B2T, Tantalum |

| C2 | Vishay/Sprague    | 595D686X0010C2T, Tantalum |

| D1 | Motorola          | MBRS140T3                 |

| L  | Coilcraft         | DT1608C-682               |

Figure 18. EXAMPLE 2. 2mm Tall 5V/0.2A Step-Up Regulator for Low Profile Applications

| U1 | Texas Instruments | LMR61428XMM               |

|----|-------------------|---------------------------|

| C1 | Vishay/Sprague    | 592D156X06R3B2T, Tantalum |

| C2 | Vishay/Sprague    | 592D336X06R3C2T, Tantalum |

| D1 | Motorola          | MBRS140T3                 |

| L  | Vishay/Dale       | ILS-3825-03               |

### SNVS815A -JUNE 2012-REVISED APRIL 2013

### **REVISION HISTORY**

| Ch | anges from Original (April 2013) to Revision A     | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 13   |

### PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device  | Status | Package Type | _       | Pins | _    |                            | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|-------------------|--------|--------------|---------|------|------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                   | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| LMR61428XMM/NOPB  | ACTIVE | VSSOP        | DGK     | 8    | 1000 | Green (RoHS<br>& no Sb/Br) | SN               | Level-1-260C-UNLIM | -40 to 85    | SN1B           | Samples |

| LMR61428XMMX/NOPB | ACTIVE | VSSOP        | DGK     | 8    | 3500 | Green (RoHS<br>& no Sb/Br) | SN               | Level-1-260C-UNLIM | -40 to 85    | SN1B           | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

6-Feb-2020

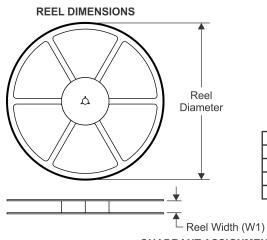

### PACKAGE MATERIALS INFORMATION

www.ti.com 8-Apr-2013

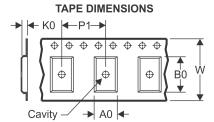

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

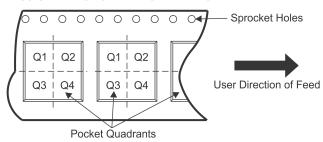

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMR61428XMM/NOPB  | VSSOP           | DGK                | 8 | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMR61428XMMX/NOPB | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 8-Apr-2013

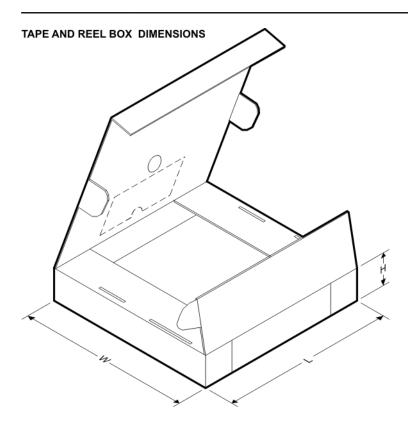

#### \*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMR61428XMM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 210.0       | 185.0      | 35.0        |

| LMR61428XMMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

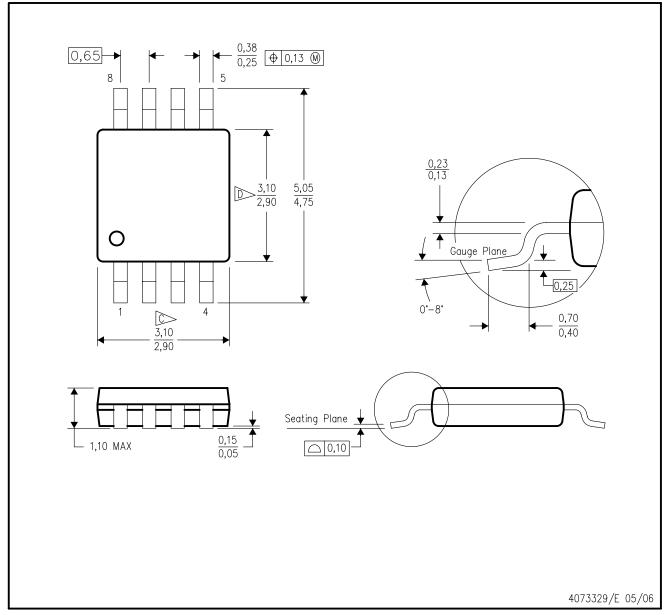

# DGK (S-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

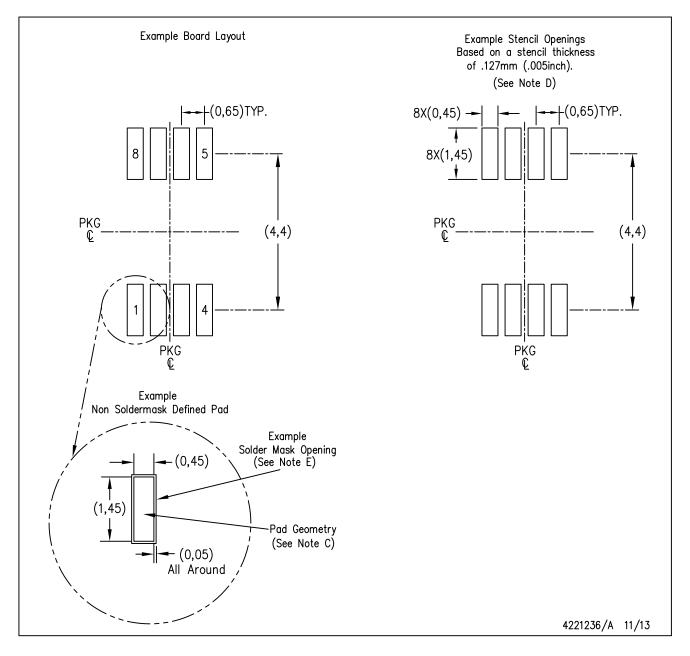

# DGK (S-PDSO-G8)

### PLASTIC SMALL OUTLINE PACKAGE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated