# ANALOG DEVICES

# 16-Bit, 200 MSPS/500 MSPS TxDAC+<sup>®</sup> with $2\times/4\times/8\times$ Interpolation and Signal Processing

# AD9786

### FEATURES

16-bit resolution, 200 MSPS input data rate IMD 90 dBc @10 MHz Noise spectral density (NSD): -164 dBm/Hz @ 10 MHz WCDMA ACLR = 80 dBc @ 40 MHz IF  $DNL = \pm 0.3 LSB$  $INL = \pm 0.6 LSB$ Selectable 2×/4×/8× interpolation filters Selectable f<sub>DAC</sub>/2, f<sub>DAC</sub>/4, f<sub>DAC</sub>/8 modulation modes Single- or dual-channel signal processing Selectable image rejection Hilbert transform **Flexible calibration engine Direct IF transmission features** Serial control interface Versatile clock and data interface 3.3 V-compatible digital interface **On-chip 1.2 V reference** 80-lead, thermally enhanced, TQFP\_EP package

### **APPLICATIONS**

Base stations: multicarrier WCDMA, GSM/EDGE, TD-SCDMA, IS136, TETRA Instrumentation RF signal generators, arbitrary waveform generators HDTV transmitters Broadband wireless systems Digital radio links Satellite systems

### **PRODUCT HIGHLIGHTS**

- 1. 16-bit, high speed, interpolating TxDAC+.

- 2. 2×/4×/8× user-selectable interpolating filter. The filter eases data rate and output signal reconstruction filter requirements.

- 3. 200 MSPS input data rate.

- 4. Ultra high speed, 500 MSPS DAC conversion rate.

- 5. Flexible clock with single-ended or differential input. CMOS, 1 V p-p sine wave, and LVPECL capability.

- 6. Complete CMOS DAC function. It operates from a 3.1 V to 3.5 V single analog (AVDD) supply, 2.5 V digital supply, and a 3.3 V digital (DRVDD) supply. The DAC full-scale current can be reduced for lower power operation, and a sleep mode is provided for low power idle periods.

- On-chip voltage reference. The AD9786 includes a 1.20 V temperature-compensated band gap voltage reference.

- 8. Multichip synchronization. Multiple AD9786 DACs can be synchronized to a single master AD9786 to ease timing design requirements and optimize image reject transmit performance.

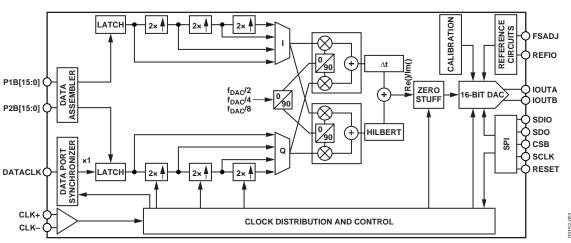

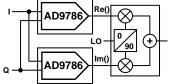

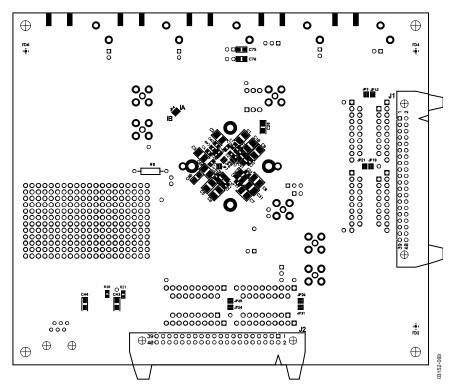

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Figure 1.

# **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Product Highlights                           |

| Functional Block Diagram 1                   |

| Revision History                             |

| General Description                          |

| Specifications                               |

| DC Specifications                            |

| Dynamic Specifications                       |

| Digital Specifications7                      |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions9 |

| Clock                                        |

| Analog10                                     |

| Data                                         |

| Serial Interface                             |

| Terminology                                  |

| Typical Performance Characteristics          |

| Serial Control Interface                     |

| General Operation of the Serial Interface    | 20 |

|----------------------------------------------|----|

| Serial Interface Port Pin Descriptions       | 20 |

| MSB/LSB Transfers                            | 21 |

| Notes on Serial Port Operation               | 21 |

| Mode Control (via Serial Port)               | 22 |

| Digital Filter Specifications                | 26 |

| Digital Interpolation Filter Coefficients    | 26 |

| Clock/Data Timing                            | 27 |

| Real and Complex Signals                     | 32 |

| Modulation Modes                             | 33 |

| Power Dissipation                            | 38 |

| Hilbert Transform Implementation             | 40 |

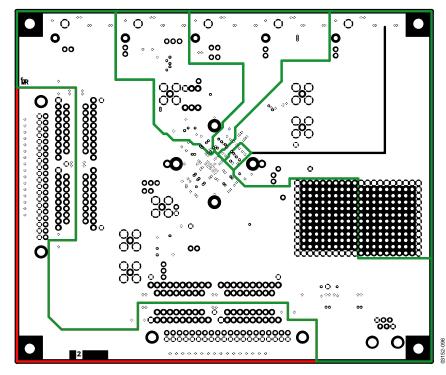

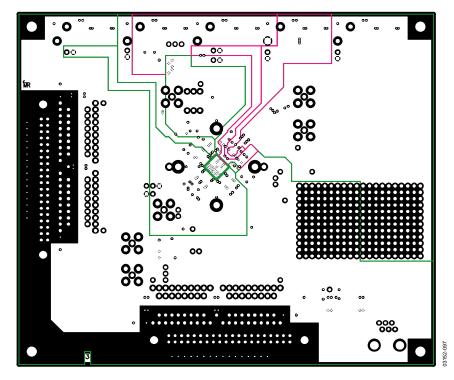

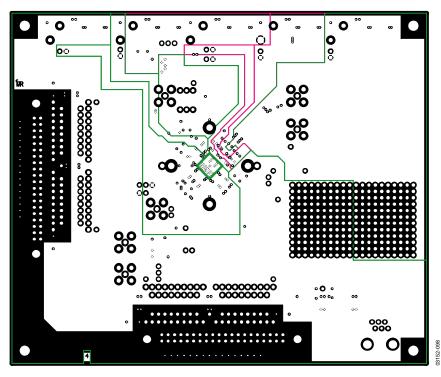

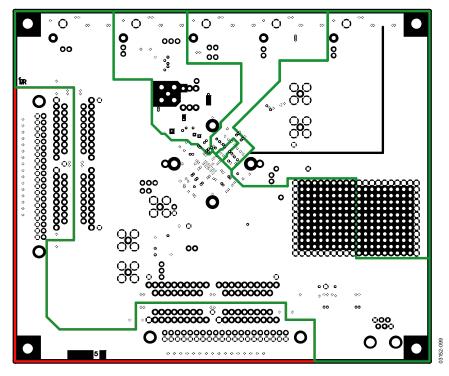

| Operating the AD9786 Rev. F Evaluation Board | 44 |

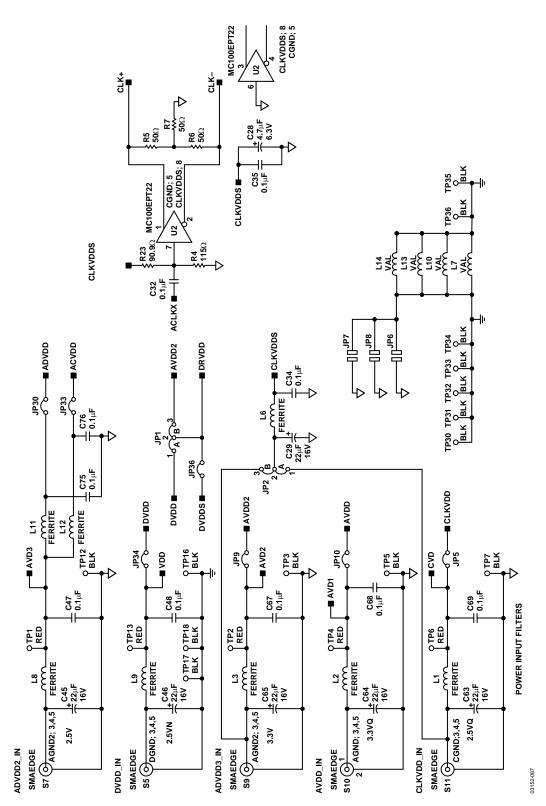

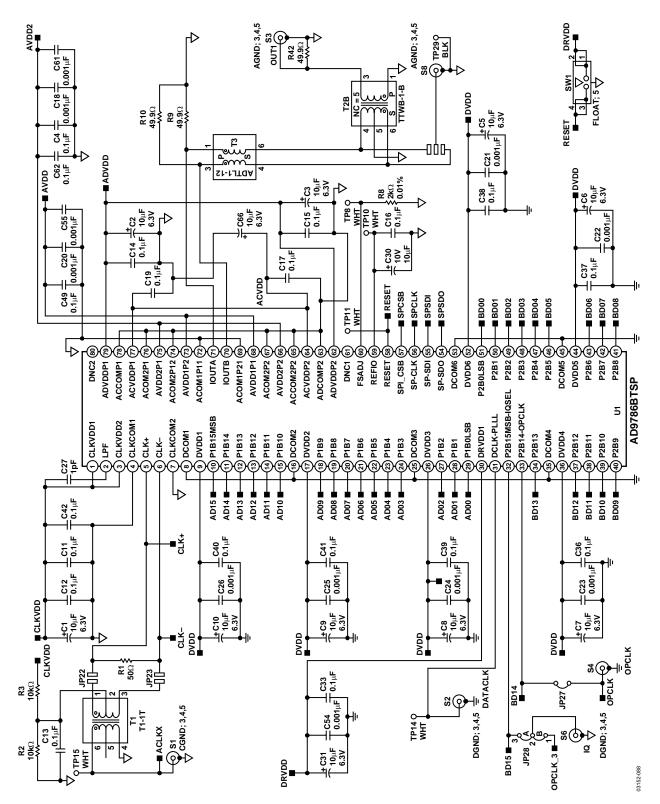

| Power Supplies                               | 44 |

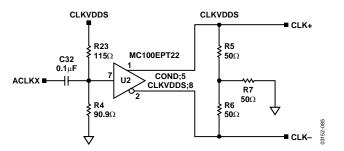

| PECL Clock Driver                            | 44 |

| Data Inputs                                  | 45 |

| Serial Port                                  | 45 |

| Analog Output                                | 45 |

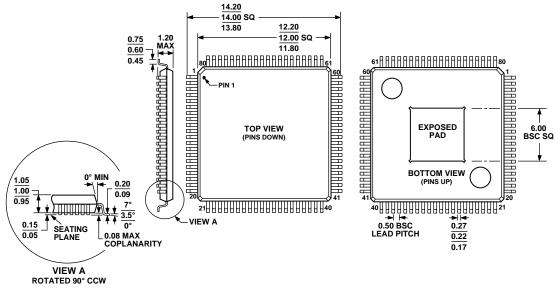

| Outline Dimensions                           | 55 |

| Ordering Guide                               | 55 |

### **REVISION HISTORY**

| 10/05—Rev. A to Rev. B                |           |

|---------------------------------------|-----------|

| Updated Format                        | Universal |

| Changes to Figure 1                   | 1         |

| Changes to Table 2                    | 6         |

| Changes to Table 3                    | 7         |

| Changes to External Sync Mode Section |           |

| Updated Outline Dimensions            | 58        |

| Changes to Ordering Guide             | 58        |

|                                       |           |

### 2/05—Rev. 0 to Rev. A

| Changed DRVDD Supply RangeU         | Jniversal |

|-------------------------------------|-----------|

| Changes to DC Specifications        | 4         |

| Changes to Dynamic Specifications   | 5         |

| Changes to Digital Specifications   |           |

| Changes to Absolute Maximum Ratings | 7         |

| Change to Figure 2                  | 8         |

| Replaced Figure 13                  | 14        |

| Replaced Figure 14                  | 14        |

| Replaced Figure 16                  |           |

| Replaced Figure 21                  | 16        |

| Replaced Figure 22                  | 16        |

| Replaced Figure 26                           | 16 |

|----------------------------------------------|----|

| Replaced Figure 27                           | 17 |

| Changes to Table 15                          |    |

| Change to Figure 44                          |    |

| Replaced Figure 45                           | 26 |

| Change to Figure 47                          |    |

| Change to Figure 48                          |    |

| Change to Figure 51                          | 29 |

| Change to Figure 52                          |    |

| Change to Figure 53                          |    |

| Change to DATAADJUST Synchronization Section |    |

| Changes to Power Dissipation Section         | 40 |

| Changes to Table 37                          | 42 |

| Changes to Data Inputs Section               | 46 |

| Change to Figure 88                          | 49 |

| Replaced Figure 95                           | 55 |

| Updated Outline Dimensions                   | 60 |

| Changes to Ordering Guide                    | 60 |

|                                              |    |

7/04—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The AD9786 is a 16-bit, high speed, CMOS DAC with  $2\times/4\times/8\times$  interpolation and signal processing features tuned for communications applications. It offers state-of-the-art distortion and noise performance. The AD9786 was developed to meet the demanding performance requirements of multicarrier and third-generation base stations. The selectable interpolation filters simplify interfacing to a variety of input data rates while also taking advantage of oversampling performance gains. The modulation modes allow convenient bandwidth placement and selectable sideband suppression.

The flexible clock interface accepts a variety of input types such as 1 V p-p sine wave, CMOS, and LVPECL in single-ended or differential mode. Internal dividers generate the required data rate interface clocks.

The AD9786 provides a differential current output, supporting single-ended or differential applications; it provides a nominal full-scale current from 10 mA to 20 mA. The AD9786 is manufactured on an advanced, low cost, 0.25  $\mu$ m CMOS process.

### **SPECIFICATIONS**

### DC SPECIFICATIONS

T<sub>MIN</sub> to T<sub>MAX</sub>; AVDD1, AVDD2, DRVDD = 3.3 V; ACVDD, ADVDD, CLKVDD, DVDD = 2.5 V; I<sub>OUTFS</sub> = 20 mA, unless otherwise noted.

Table 1.

| Parameter                                                        | Min  | Тур    | Max     | Unit          |

|------------------------------------------------------------------|------|--------|---------|---------------|

| RESOLUTION                                                       |      | 16     |         | Bits          |

| DC Accuracy <sup>1</sup>                                         |      |        |         |               |

| Integral Nonlinearity                                            |      | ±0.6   |         | LSB           |

| Differential Nonlinearity                                        |      | ±0.3   |         | LSB           |

| ANALOG OUTPUT                                                    |      |        |         |               |

| Offset Error                                                     |      | ±0.015 | ±0.0175 | % of FSR      |

| Gain Error (with Internal Reference)                             |      | ±1.5   |         | % of FSR      |

| Full-Scale Output Current <sup>2</sup>                           | 10   |        | 20      | mA            |

| Output Compliance Range                                          | -1.0 |        | +1.0    | V             |

| Output Resistance                                                |      | 10     |         | MΩ            |

| REFERENCE OUTPUT                                                 |      |        |         |               |

| Reference Voltage                                                | 1.15 | 1.23   | 1.30    | V             |

| Reference Output Current <sup>3</sup>                            |      | 1      |         | μΑ            |

| REFERENCE INPUT                                                  |      |        |         |               |

| Input Compliance Range                                           | 0.1  |        | 1.25    | V             |

| Reference Input Resistance (External Reference Mode)             |      | 10     |         | MΩ            |

| Small Signal Bandwith                                            |      | 200    |         | kHz           |

| TEMPERATURE COEFFICIENTS                                         |      |        |         |               |

| Unipolar Offset Drift                                            |      | 0      |         | ppm of FSR/°C |

| Gain Drift (with Internal Reference)                             |      | ±4     |         | ppm of FSR/°C |

| Reference Voltage Drift                                          |      | ±30    |         | ppm/°C        |

| POWER SUPPLY                                                     |      |        |         |               |

| AVDD1, AVDD2                                                     |      |        |         |               |

| Voltage Range                                                    | 3.1  | 3.3    | 3.5     | V             |

| Analog Supply Current (I <sub>AVDD1</sub> + I <sub>AVDD2</sub> ) |      | 50     |         | mA            |

| Iavdd1 + Iavdd2 in Sleep Mode                                    |      | 18     |         | mA            |

| ACVDD, ADVDD                                                     |      |        |         |               |

| Voltage Range                                                    | 2.35 | 2.5    | 2.65    | V             |

| Analog Supply Current (I <sub>ACVDD</sub> + I <sub>ADVDD</sub> ) |      | 2.5    |         | mA            |

| CLKVDD                                                           |      |        |         |               |

| Voltage Range                                                    | 2.35 | 2.5    | 2.65    | V             |

| Clock Supply Current (I <sub>CLKVDD</sub> )                      |      | 12     |         | mA            |

| DVDD                                                             |      |        |         |               |

| Voltage Range                                                    | 2.35 | 2.5    | 2.65    | V             |

| Digital Supply Current (I <sub>DVDD</sub> )                      |      | 52.5   |         | mA            |

| DRVDD                                                            |      |        |         |               |

| Voltage Range                                                    | 3.1  | 3.3    | 3.5     | V             |

| Digital Supply Current (I <sub>DRVDD</sub> )                     |      | 5.3    |         | μA            |

| Nominal Power Dissipation <sup>4</sup>                           |      | 1.25   |         | W             |

| OPERATING RANGE                                                  | -40  |        | +85     | °C            |

$^1$  Measured at  $I_{\text{OUTA}}$  driving a virtual ground.  $^2$  Nominal full-scale current,  $I_{\text{OUTFS}}$  is 32× the  $I_{\text{REF}}$  current.

<sup>3</sup> Use an external amplifier to drive any external load.

$^{4}$  Measured under the following conditions:  $f_{DATA} = 125$  MSPS,  $f_{DAC} = 500$  MSPS,  $4 \times$  interpolation,  $f_{DAC}/4$  modulation, Hilbert off.

### **DYNAMIC SPECIFICATIONS**

$T_{MIN}$  to  $T_{MAX}$ ; AVDD1, AVDD2, DRVDD = 3.3 V; ACVDD, ADVDD, CLKVDD, DVDD = 2.5 V;  $I_{OUTFS}$  = 20 mA; differential transformer coupled output; 50  $\Omega$  doubly terminated, unless otherwise noted.

| Parameter                                                                                        | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| DYNAMIC PERFORMANCE                                                                              |     |      |     |        |

| Minimum DAC Output Update Rate                                                                   |     |      | 20  | MHz    |

| Maximum DAC Output Update Rate (f <sub>DAC</sub> )                                               | 500 |      |     | MSPS   |

| AC LINEARITY/BASEBAND MODE                                                                       |     |      |     |        |

| Spurious-Free Dynamic Range (SFDR) to Nyquist ( $f_{OUT} = 0 \text{ dBFS}$ )                     |     |      |     |        |

| $f_{DATA} = 100$ MSPS; $f_{OUT} = 5$ MHz, 4×, 2× Interpolation                                   |     | 93   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT</sub> = 10 MHz                                          |     | 85   |     | dBc    |

| $f_{DATA} = 200 \text{ MSPS}; f_{OUT} = 25 \text{ MHz}$                                          |     | 78   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT</sub> = 50 MHz                                          |     | 78   |     | dBc    |

| Two-Tone Intermodulation (IMD) to Nyquist ( $f_{OUT1} = f_{OUT2} = -6 \text{ dBFS}$ )            |     |      |     |        |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 5 MHz; f <sub>OUT2</sub> = 6 MHz               |     | 85   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 15 MHz; f <sub>OUT2</sub> = 16 MHz             |     | 85   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 25 MHz; f <sub>OUT2</sub> = 26 MHz             |     | 84   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 45 MHz; f <sub>OUT2</sub> = 46 MHz             |     | 80   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 65 MHz; f <sub>OUT2</sub> = 66 MHz             |     | 78   |     | dBc    |

| f <sub>DATA</sub> = 200 MSPS; f <sub>OUT1</sub> = 85 MHz; f <sub>OUT2</sub> = 86 MHz             |     | 75   |     | dBc    |

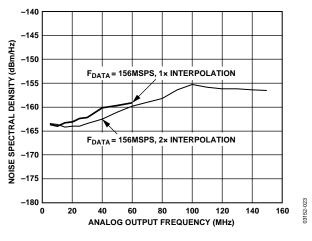

| Noise Power Spectral Density (NPSD)                                                              |     |      |     |        |

| f <sub>DATA</sub> = 156 MSPS; f <sub>OUT</sub> = 10 MHz; 0 dBFS, 8 Tones, Separation = 500 kHz   |     | -164 |     | dBm/Hz |

| $f_{DATA} = 156$ MSPS; $f_{OUT} = 50$ MHz; 0 dBFS, 8 Tones, Separation = 500 kHz                 |     | -161 |     | dBm/Hz |

| Adjacent Channel Power Ratio (ACLR)                                                              |     |      |     |        |

| WCDMA ACLR with 3.84 MHz BW, Single Carrier                                                      |     |      |     |        |

| IF = 21 MHz, $f_{DATA}$ = 122.88 MSPS, 4× Interpolation                                          |     | 80   |     | dB     |

| IF = 224.76 MHz, $f_{DATA}$ = 122.88 MSPS, 4× Interpolation, High-Pass Interpolation Filter Mode |     | 72   |     | dB     |

### **DIGITAL SPECIFICATIONS**

$T_{MIN}$  to  $T_{MAX}$ ; AVDD1, AVDD2, DRVDD = 3.3 V; ACVDD, ADVDD, CLKVDD, DVDD = 2.5 V;  $I_{OUTFS}$  = 20 mA, unless otherwise noted. **Table 3.**

| Parameter                                                                  | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------|------|-----|------|------|

| DIGITAL INPUTS                                                             |      |     |      |      |

| Logic 1 Voltage                                                            | 1.6  |     |      | V    |

| Logic 0 Voltage                                                            |      | 0   | 0.9  | V    |

| Logic 1 Current                                                            | -10  |     | +10  | μΑ   |

| Logic 0 Current                                                            | -10  |     | +10  | μΑ   |

| Input Capacitance                                                          |      | 5   |      | pF   |

| CLOCK INPUTS <sup>1</sup>                                                  |      |     |      |      |

| Input Voltage Range                                                        | 0    |     | 2.65 | V    |

| Common-Mode Voltage                                                        | 0.75 | 1.5 | 2.25 | V    |

| Differential Voltage                                                       | 0.5  | 1.5 |      | V    |

| Latch Pulse Width (t <sub>LPW</sub> )                                      | 5    |     |      | ns   |

| Data Setup Time to DACCLK Out in Master Mode (ts)                          | -0.5 |     |      | ns   |

| Data Hold Time to DACCLK Out in Master Mode ( $t_{\mbox{\scriptsize H}}$ ) | 2.9  |     |      | ns   |

<sup>1</sup> See the Clock/Data Timing section for setup and hold times in various timing modes.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| 1 able 4.                     |                               |                      |

|-------------------------------|-------------------------------|----------------------|

| Parameter                     | With Respect to               | Rating               |

| AVDD1, AVDD2,                 | AGND1, AGND2,                 | –0.3 V to +3.6 V     |

| DRVDD                         | ACGND, ADGND,<br>CLKGND, DGND |                      |

| ACVDD, ADVDD,                 | AGND1, AGND2,                 | –0.3 V to +2.8 V     |

| CLKVDD, DVDD                  | ACGND, ADGND,<br>CLKGND, DGND |                      |

| AGND1, AGND2,                 | AGND1, AGND2,                 | –0.3 V to +0.3 V     |

| ACGND, ADGND,<br>CLKGND, DGND | ACGND, ADGND,<br>CLKGND, DGND |                      |

| REFIO, FSADJ                  | AGND1                         | -0.3 to AVDD1 + 0.3  |

| IOUTA, IOUTB                  | AGND1                         | -1.0 to AVDD1 +0.3   |

| P1B15 to P1B0,                | DGND                          | -0.3 to DRVDD + 0.3  |

| P2B15 to P2B0, RESET          |                               |                      |

| DATACLK                       | DGND                          | -0.3 to DRVDD + 0.3  |

| CLK+, CLK–                    | CLKGND                        | -0.3 to CLKVDD + 0.3 |

| CSB, SCLK,                    | DGND                          | -0.3 to DRVDD + 0.3  |

| SDIO, SDO                     |                               |                      |

| Junction                      |                               | –65°C to +125°C      |

| Temperature Range             |                               |                      |

| Storage                       |                               | 150°C                |

| Temperature                   |                               |                      |

| Lead Temperature              |                               | 300°C                |

| (10 sec)                      |                               |                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 5. Thermal Resistance

| Package Type <sup>1</sup>            | Αιθ  | Unit |

|--------------------------------------|------|------|

| 80-lead TQFP_EP (Thermally Enhanced) | 23.5 | °C/W |

|                                      | 2010 |      |

<sup>1</sup>With thermal pad soldered to PCB.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

CLOCK

Table 6. Clock Pin Function Descriptions

| Pin  |            |           |              |                                                                                                                                                  |  |  |  |  |

|------|------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.  | Mnemonic   | Direction | Descriptio   | escription                                                                                                                                       |  |  |  |  |

| 5, 6 | CLK+, CLK– | T         | Differential | Differential Clock Input.                                                                                                                        |  |  |  |  |

| 2    | DNC        |           | Do Not Cor   | inect.                                                                                                                                           |  |  |  |  |

| 31   | DATACLK    | I/O       | DCLKEXT      |                                                                                                                                                  |  |  |  |  |

|      |            |           | 0x02[3]      | Mode                                                                                                                                             |  |  |  |  |

|      |            |           | 0            | Pin configured for input of channel data rate or synchronizer clock. Internal clock synchronizer can be turned on or off with DCLKCRC (0x02[2]). |  |  |  |  |

|      |            |           | 1            | Pin configured for output of channel data rate or synchronizer clock.                                                                            |  |  |  |  |

| 1, 3 | CLKVDD     |           | Clock Doma   | ain 2.5 V.                                                                                                                                       |  |  |  |  |

| 4, 7 | CLKGND     |           | Clock Doma   | ain 0 V.                                                                                                                                         |  |  |  |  |

### ANALOG

Table 7. Analog Pin Function Descriptions

| Pin No. | Mnemonic     | Direction | Description                          |

|---------|--------------|-----------|--------------------------------------|

| 59      | REFIO        | Α         | Reference.                           |

| 60      | FSADJ        | А         | Full-Scale Adjust.                   |

| 70, 71  | IOUTB, IOUTA | А         | Differential DAC Output Currents.    |

| 61      | DNC          |           | Do Not Connect.                      |

| 62, 79  | ADVDD        |           | Analog Domain Digital Content 2.5 V. |

| 63, 78  | ADGND        |           | Analog Domain Digital Content 0 V.   |

| 64, 77  | ACVDD        |           | Analog Domain Clock Content 2.5 V.   |

| 65, 76  | ACGND        |           | Analog Domain Clock Content 0 V.     |

| 66, 75  | AVDD2        |           | Analog Domain Clock Switching 3.3 V. |

| 67, 74  | AGND2        |           | Analog Domain Switching 0 V.         |

| 68, 73  | AVDD1        |           | Analog Domain Quiet 3.3 V.           |

| 69, 72  | AGND1        |           | Analog Domain Quiet 0 V.             |

| 80      | DNC          |           | Do Not Connect.                      |

### DATA

Table 8. Data Pin Function Descriptions

| Pin No.                   | Mnemonic           | Direction | Description        |                         |                                                      |                                                              |  |  |  |

|---------------------------|--------------------|-----------|--------------------|-------------------------|------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| 10 to 15, 18 to           | P1B15 to P1B0      | 1         | Input Data Port    | Input Data Port 1.      |                                                      |                                                              |  |  |  |

| 24, 27 to 29              |                    |           | ONEPORT            |                         |                                                      |                                                              |  |  |  |

|                           |                    |           | 0x02[6]            | Mode                    |                                                      |                                                              |  |  |  |

|                           |                    |           | 0                  | Latched c               | lata route                                           | d for I channel processing.                                  |  |  |  |

|                           |                    |           | 1                  | Latched o               | lata demu                                            | ltiplexed by IQSEL and routed for                            |  |  |  |

|                           |                    |           |                    | interleave              | ed I/Q proo                                          | cessing.                                                     |  |  |  |

| 32                        | IQSEL/P2B15        | I         | ONEPORT            | IQPOL                   | IQSEL/                                               |                                                              |  |  |  |

|                           |                    |           | 0x02[6]            | 0x02[1]                 | P2B15                                                | Mode (IQPOL = 0)                                             |  |  |  |

|                           |                    |           | 0                  | Х                       | Х                                                    | Latched data routed to Q channel Bit 15<br>(MSB) processing. |  |  |  |

|                           |                    |           | 1                  | 0                       | 0                                                    | Latched data on Data Port 1 routed to C channel processing.  |  |  |  |

|                           |                    |           | 1                  | 0                       | 1                                                    | Latched data on Data Port 1 routed to I channel processing.  |  |  |  |

|                           |                    |           | 1                  | 1                       | 0                                                    | Latched data on Data Port 1 routed to I channel processing.  |  |  |  |

|                           |                    |           | 1                  | 1                       | 1                                                    | Latched data on Data Port 1 routed to C channel processing.  |  |  |  |

| 33                        | ONEPORTCLOCK/P2B14 | I/O       | ONEPORT<br>0x02[6] |                         |                                                      |                                                              |  |  |  |

|                           |                    |           | 0                  | Latched c               | Latched data routed for Q channel Bit 14 processing. |                                                              |  |  |  |

|                           |                    |           | 1                  | Pin config<br>data rout |                                                      | output of clock at twice the channel                         |  |  |  |

| 34, 37 to 43,<br>46 to 51 | P2B13 to P2B0      | I         | Input Data Port    | 2, Bit 13 to B          | it 0.                                                |                                                              |  |  |  |

| 30                        | DRVDD              |           | Digital Output P   | Pin Supply, 3.          | 3 V.                                                 |                                                              |  |  |  |

| 9, 17, 26,<br>36, 44, 52  | DVDD               |           | Digital Domain,    | 2.5 V.                  |                                                      |                                                              |  |  |  |

| 8, 16, 25,<br>35, 45, 53  | DGND               |           | Digital Domain,    | 0 V.                    |                                                      |                                                              |  |  |  |

### SERIAL INTERFACE

| Pin No. | Mnemonic | Direction | Descr  | iption          |                                                                             |

|---------|----------|-----------|--------|-----------------|-----------------------------------------------------------------------------|

| 54      | SDO      | 0         |        | SDIODIR         |                                                                             |

|         |          |           | CSB    | 0x00[7]         | Mode                                                                        |

|         |          |           | 1      | Х               | High impedance.                                                             |

|         |          |           | 0      | 0               | Serial data output.                                                         |

|         |          |           | 0      | 1               | High impedance.                                                             |

| 55      | SDIO     | I/O       |        | SDIODIR         |                                                                             |

|         |          |           | CSB    | 0x00[7]         | Mode                                                                        |

|         |          |           | 1      | Х               | High impedance.                                                             |

|         |          |           | 0      | 0               | Serial data output.                                                         |

|         |          |           | 0      | 1               | Serial data input/output depending on Bit 7 of the serial instruction byte. |

| 56      | SCLK     | 1         | Serial | Interface Clo   | ick.                                                                        |

| 57      | CSB      | 1         | Serial | Interface Chi   | ip Select.                                                                  |

| 58      | RESET    | 1         | Reset  | s entire chip t | to default state.                                                           |

### TERMINOLOGY

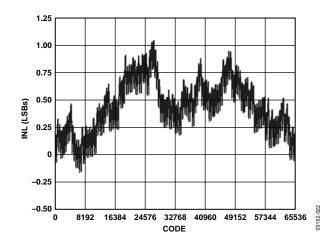

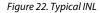

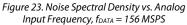

### Linearity Error (Integral Nonlinearity or INL)

Linearity error is defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero to full scale.

### Differential Nonlinearity (DNL)

DNL is the measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

### Monotonicity

A D/A converter is monotonic if the output either increases or remains constant as the digital input increases.

### **Offset Error**

The deviation of the output current from the ideal of zero is called offset error. For  $I_{OUTA}$ , 0 mA output is expected when the inputs are all 0s. For  $I_{OUTB}$ , 0 mA output is expected when all inputs are set to 1.

### **Gain Error**

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1, minus the output when all inputs are set to 0.

#### **Output Compliance Range**

The range of allowable voltage at the output of a current-output DAC. Operation beyond the maximum compliance limits can cause either output stage saturation or breakdown, resulting in nonlinear performance.

### **Temperature Drift**

Temperature drift is specified as the maximum change from the ambient (+25°C) value to the value at either  $T_{MIN}$  or  $T_{MAX}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per degree Celsius. For reference drift, the drift is reported in ppm per degree Celsius.

#### **Power Supply Rejection**

The maximum change in the full-scale output as the supplies are varied from minimum to maximum specified voltages.

#### Settling Time

The time required for the output to reach and remain within a specified error band about its final value, measured from the start of the output transition.

#### Glitch Impulse

Asymmetrical switching times in a DAC give rise to undesired output transients that are quantified by a glitch impulse. It is specified as the net area of the glitch in pV-sec.

#### Spurious-Free Dynamic Range (SFDR)

The difference between the rms amplitude of the output signal and the amplitude of the peak spurious signal over the specified bandwidth. The units are often in dBc (dB with respect to the carrier).

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured fundamental. It is expressed as a percentage or in decibels.

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

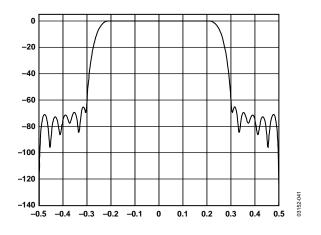

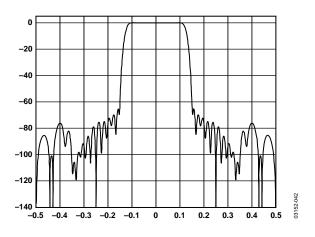

#### **Interpolation Filter**

If the digital inputs to the DAC are sampled at a multiple rate of  $f_{DATA}$  (interpolation rate), a digital filter can be constructed that has a sharp transition band near  $f_{DATA}/2$ . Images that would typically appear around  $f_{DAC}$  (output data rate) can be greatly suppressed.

#### **Pass Band**

Frequency band in which any input applied therein passes unattenuated to the DAC output.

#### **Stop-Band Rejection**

The amount of attenuation of a frequency outside the pass band applied to the DAC, relative to a full-scale signal applied at the DAC input within the pass band.

#### **Group Delay**

Number of input clocks between an impulse applied at the device input and peak DAC output current. A half-band FIR filter has constant group delay over its entire frequency range

#### **Impulse Response**

Response of the device to an impulse applied to the input.

#### Adjacent Channel Leakage Ratio (ACLR)

A ratio in dBc between the measured power within a channel relative to its adjacent channel.

#### **Complex Modulation**

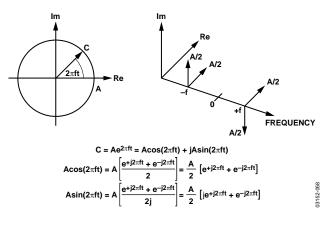

The process of passing the real and imaginary components of a signal through a complex modulator (transfer function =  $e^{jwt}$  = coswt + jsinwt) and realizing real and imaginary components on the modulator output.

#### **Hilbert Transform**

A function with unity gain over all frequencies, but with a phase shift of 90° for negative frequencies and a phase shift of -90° for positive frequencies. Although this function cannot be implemented ideally, it can be approximated with a short FIR filter with enough accuracy to be very useful in single sideband radio architectures.

#### **Complex Image Rejection**

In a traditional two-part upconversion, two images are created around the second IF frequency. These images are redundant and have the effect of wasting transmitter power and system bandwidth. By placing the real part of a second complex modulator in series with the first complex modulator, either the upper or lower frequency image near the second IF can be rejected.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_{MIN}$  to  $T_{MAX}$ ; AVDD1, AVDD2, DRVDD = 3.3 V; ACVDD, ADVDD, CLKVDD, DVDD = 2.5 V;  $I_{OUTFS}$  = 20 mA; differential transformer coupled output; 50  $\Omega$  doubly terminated, unless otherwise noted.

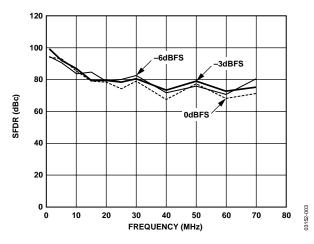

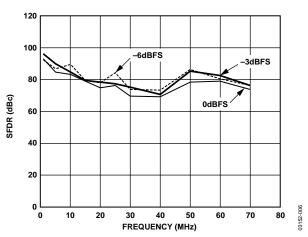

Figure 3. SFDR vs. Frequency,  $f_{DATA} = 200$  MSPS, 1× Interpolation

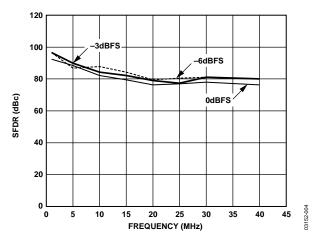

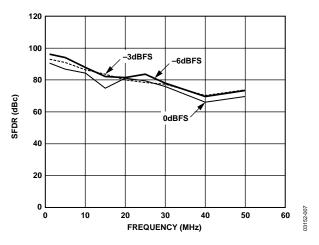

Figure 4. SFDR vs. Frequency,  $f_{DATA} = 100$  MSPS, 4× Interpolation

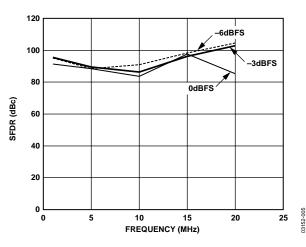

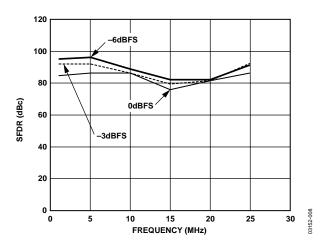

Figure 5. SFDR vs. Frequency, f<sub>DATA</sub> = 50 MSPS, 8× Interpolation

Figure 6. SFDR vs. Frequency,  $f_{DATA} = 200$  MSPS, 2× Interpolation

Figure 7. SFDR vs. Frequency,  $f_{DATA} = 125$  MSPS, 4× Interpolation

Figure 8. SFDR vs. Frequency,  $f_{DATA} = 62.5$  MSPS, 8× Interpolation

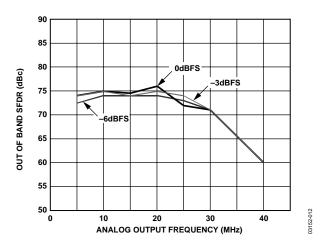

Figure 9. Out-of-Band SFDR,  $f_{DATA} = 200$  MSPS, 2× Interpolation

Figure 10. Out-of-Band SFDR,  $f_{DATA} = 125$  MSPS, 4× Interpolation

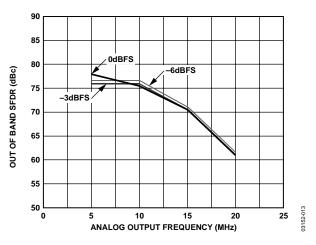

Figure 11. Out-of-Band SFDR,  $f_{DATA} = 62.5$  MSPS,  $8 \times$  Interpolation

Figure 12. Out-of-Band SFDR,  $f_{DATA} = 100$  MSPS, 4× Interpolation

Figure 13. Out-of-Band SFDR,  $f_{DATA} = 50$  MSPS, 8× Interpolation

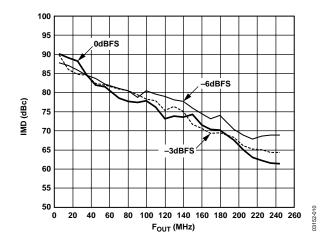

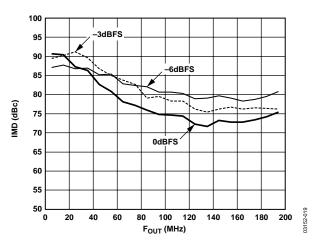

Figure 14. Third-Order IMD vs. Frequency,  $f_{DATA} = 160$  MSPS, 1× Interpolation

Figure 15. Third-Order IMD vs. Frequency,  $f_{DATA} = 160$  MSPS, 2× Interpolation

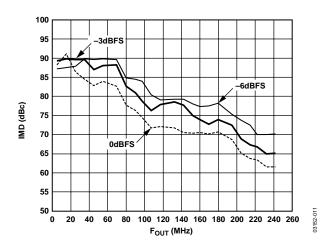

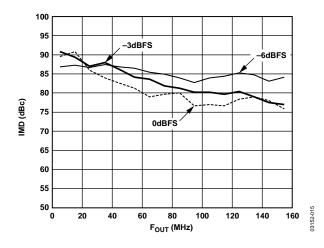

Figure 16. Third-Order IMD vs. Frequency,  $f_{DATA} = 200$  MSPS, 2× Interpolation

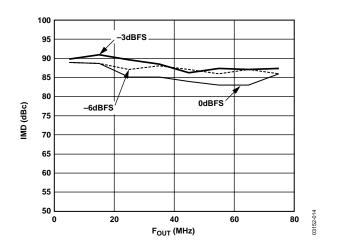

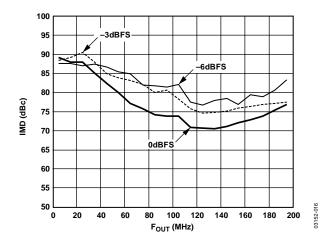

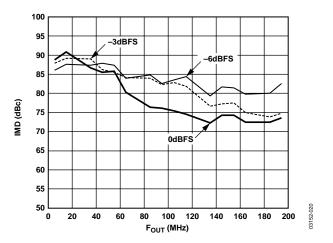

Figure 17. Third-Order IMD vs. Frequency,  $f_{DATA} = 125$  MSPS, 4× Interpolation

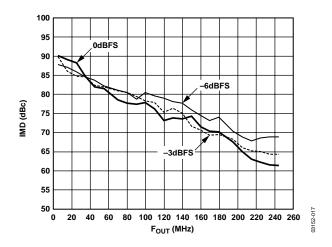

Figure 18. Third-Order IMD vs. Frequency,  $f_{DATA} = 200$  MSPS, 1x Interpolation

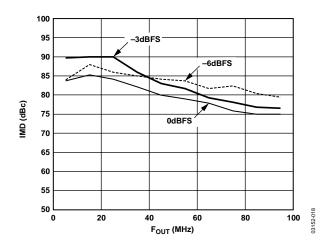

Figure 19. Third-Order IMD vs. Frequency,  $f_{DATA} = 100$  MSPS, 4× Interpolation

Figure 20. Third-Order IMD vs. Frequency,  $f_{DATA} = 50$  MSPS, 8× Interpolation

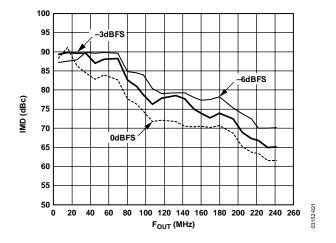

Figure 21. Third-Order IMD vs. Frequency,  $f_{DATA} = 62.5$  MSPS, 8× Interpolation

Figure 24. Typical DNL

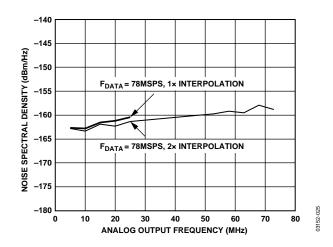

Figure 25. Noise Spectral Density vs. Analog Input Frequency, f<sub>DATA</sub> = 78 MSPS

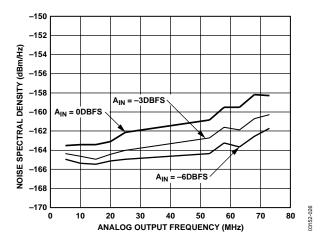

Figure 26. Noise Spectral Density vs. Analog Input Frequency,  $f_{DATA} = 78$  MSPS, 2x Interpolation

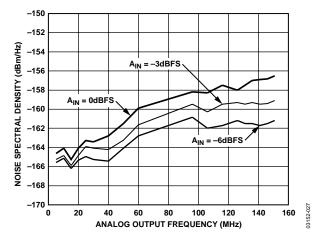

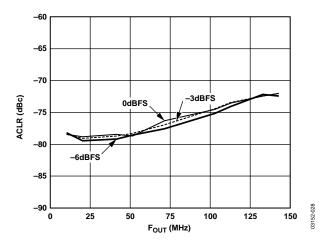

Figure 28. ACLR for First Adjacent Band vs. Frequency,  $f_{DATA} = 61.44$  MSPS, 4× Interpolation

Figure 29. ACLR for First Adjacent Band vs. Frequency,  $f_{DATA} = 76.8$  MSPS, 4× Interpolation

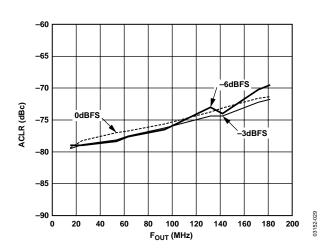

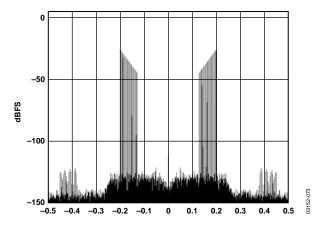

Figure 30. Two Tones Around 23 MHz,  $f_{DATA} = 200$  MSPS,  $2 \times$  Interpolation, Low-Pass Digital Filter Mode

Figure 31. Two Tones Around 177 MHz, f<sub>DATA</sub> = 200 MSPS, 2× Interpolation, High-Pass Digital Filter Mode

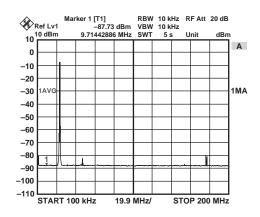

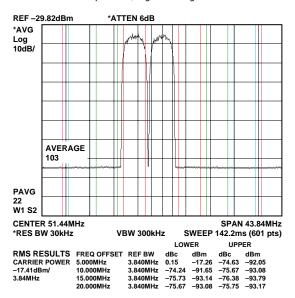

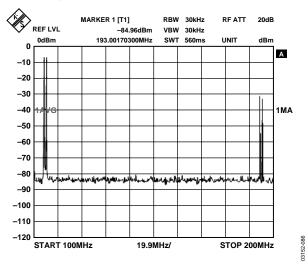

Figure 32. ACLR for Two WCDMA Carriers @ 51.44 MHz,  $f_{DATA} = 61.44$  MSPS, 4× Interpolation 03152-032

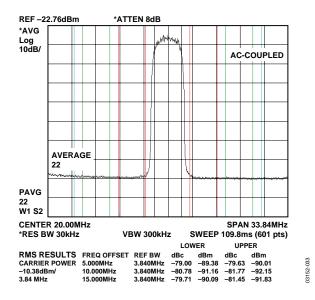

Figure 33. ACLR for Single WCDMA Carrier @ 20 MHz,  $f_{DATA} = 61.44$  MSPS, 4× Interpolation

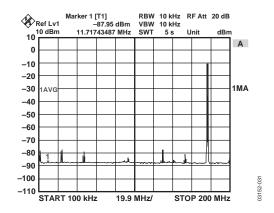

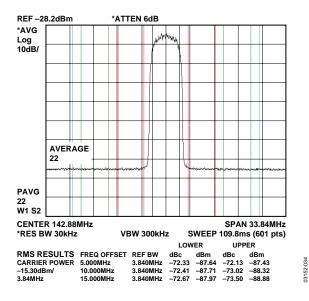

Figure 34. ACLR for Single WCDMA Carrier @ 142.88 MHz,  $f_{DATA} = 61.44$  MSPS, 4× Interpolation

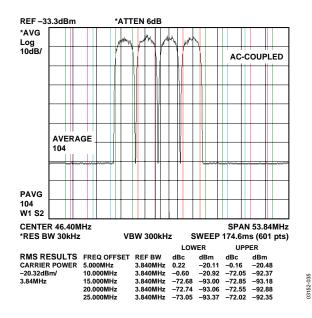

Figure 35. ACLR for Four WCDMA Carriers Near 50 MHz,  $f_{DATA} = 61.44$  MSPS, 4× Interpolation

### SERIAL CONTROL INTERFACE

Figure 36. AD9786 SPI Port Interface

The AD9786 serial port is a flexible, synchronous serial communications port, allowing easy interface to many industry-standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola SPI<sup>®</sup> and Intel<sup>®</sup> SSR protocols. The interface allows read/write access to all registers that configure the AD9786. Singleor multiple-byte transfers are supported, as well as MSB-first or LSB-first transfer formats. The AD9786 serial interface port can be configured as a single pin I/O (SDIO), or as two unidirectional pins for input/output (SDIO/SDO).

### **GENERAL OPERATION OF THE SERIAL INTERFACE**

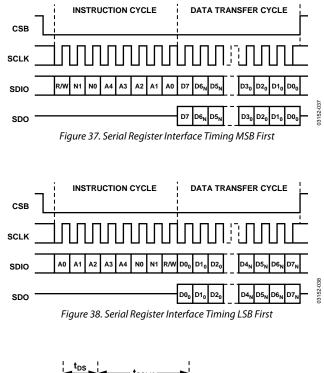

There are two phases to a communication cycle with the AD9786. Phase 1 is the instruction cycle, which is the writing of an instruction byte into the AD9786, coincident with the first eight SCLK rising edges. The instruction byte provides the AD9786 serial port controller with information regarding the data transfer cycle, which is Phase 2 of the communication cycle. The Phase 1 instruction byte defines whether the upcoming data transfer is a read or a write, the number of bytes in the data transfer, and the starting register address for the first byte of the data transfer. The first eight SCLK rising edges of each communication cycle are used to write the instruction byte into the AD9786.

A logic high on the CSB pin, followed by a logic low, resets the SPI port timing to the initial state of the instruction cycle. This is true regardless of the present state of the internal registers or the other signal levels present at the inputs to the SPI port. If the SPI port is in the midst of an instruction cycle or a data transfer cycle, none of the present data is written.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9786 and the system controller. Phase 2 of the communication cycle is a transfer of 1, 2, 3, or 4 data bytes, as determined by the instruction byte. Using one multibyte transfer is the preferred method. Single-byte data transfers are useful to reduce CPU overhead when register access requires one byte only. Registers change immediately upon writing to the last bit of each transfer byte.

### Instruction Byte

$R/\overline{W}$ , Bit 7 of the instruction byte, determines whether a read or a write data transfer occurs after the instruction byte write. Logic high indicates a read operation; Logic 0 indicates a write operation. N1 and N0, Bit 6 and Bit 5 of the instruction byte, determine the number of bytes to be transferred during the data transfer cycle (see Table 10).

| N1 | N2 | Description      |

|----|----|------------------|

| 0  | 0  | Transfer 1 byte  |

| 0  | 1  | Transfer 2 bytes |

| 1  | 0  | Transfer 3 bytes |

| 1  | 1  | Transfer 4 bytes |

The bit decodes are shown as follows:

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10  |

| R/W | N1 | N0 | A4 | A3 | A2 | A1 | A0  |

A4, A3, A2, A1, and A0 (Bit 4, Bit 3, Bit 2, Bit 1, and Bit 0) of the instruction byte determine which register is accessed during the data transfer portion of the communication cycle. For multibyte transfers, this address is the starting byte address. The remaining register addresses are generated by the AD9786.

### SERIAL INTERFACE PORT PIN DESCRIPTIONS

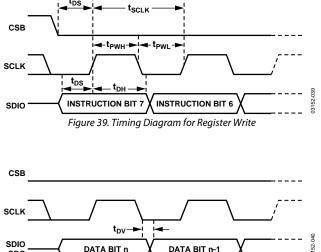

**SCLK—Serial Clock**. The serial clock pin is used to synchronize data to and from the AD9786 and to run the internal state machines. The maximum frequency of SCLK is 20 MHz. All data input to the AD9786 is registered on the rising edge of SCLK. All data is driven out of the AD9786 on the falling edge of SCLK.

**CSB**—**Chip Select**. Active low input starts and gates a communication cycle. It allows more than one device to be used on the same serial communication lines. The SDO and SDIO pins go to a high impedance state when this input is high. Chip select should stay low during the entire communication cycle.

**SDIO—Serial Data I/O**. Data is always written into the AD9786 on this pin. However, this pin can be used as a bidirectional data line. The configuration of this pin is controlled by Bit 7 of Register Address 0x00. The default is Logic 0, which configures the SDIO pin as unidirectional.

**SDO**—**Serial Data Out**. Data is read from this pin for protocols that use separate lines for transmitting and receiving data. In the case where the AD9786 operates in a single bidirectional I/O mode, this pin does not output data and is set to a high impedance state.

### **MSB/LSB TRANSFERS**

The AD9786 serial port can support both MSB-first or LSB-first data formats. This functionality is controlled by register address DATADIR (0x00[6]). The default is MSB first. When this bit is set active high, the AD9786 serial port is in LSB-first format. That is, if the AD9786 is in LSB-first mode, the instruction byte must be written from least significant bit to most significant bit. Multibyte data transfers in MSB-first format can be completed by writing an instruction byte that includes the register address of the most significant byte. In MSB-first mode, the serial port internal byte address generator decrements for each byte required of the multibyte communication cycle. Multibyte data transfers in LSB-first format can be completed by writing an instruction byte that includes the register address of the least significant byte. In LSB-first mode, the serial port internal byte address generator increments for each byte required of the multibyte communication cycle.

The AD9786 serial port controller address increments from 0x1F to 0x00 for multibyte I/O operations if the MSB-first mode is active. The serial port controller address decrements from 0x00 to 0x1F for multibyte I/O operations if the LSB-first mode is active.

### NOTES ON SERIAL PORT OPERATION

The AD9786 serial port configuration bits reside in Bit 6 and Bit 7 of Register Address 0x00. Note that the configuration changes immediately upon writing to the last bit of the register. For multibyte transfers, writing to this register might occur during the middle of a communication cycle. Care must be taken to compensate for this new configuration for the remaining bytes of the current communication cycle.

The same considerations apply to setting the software reset SWRST (0x00[5]) bit. All other registers are set to their default values, but the software reset does not affect the bits in Register Address 0x00 and Register Address 0x04.

It is recommended to use only single-byte transfers when changing serial port configurations or initiating a software reset.

Figure 40. Timing Diagram for Register Read

SDO

# MODE CONTROL (VIA SERIAL PORT) Table 11.

| Address  |    | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2       | Bit 1       | Bit 0       |

|----------|----|------------|------------|------------|------------|------------|-------------|-------------|-------------|

| COMMS    | 00 | SDIODIR    | DATADIR    | SWRST      | SLEEP      | PDN        |             |             | EXREF       |

| FILTER   | 01 | INTERP[1]  | INTERP[0]  |            |            | ZSTUFF     | HPFX8       | HPFX4       | HPFX2       |

| DATA     | 02 | DATAFMT    | ONEPORT    | DCLKSTR    | DCLKPOL    | DCLKEXT    | DCLKCRC     | IQPOL       | CRAYDIN     |

| MODULATE | 03 | CHANNEL    | HILBERT    | MODDUAL    | SIDEBAND   | MOD[1]     | MOD[0]      |             |             |

| RESERVED | 04 | Reserved   | Reserved   | Reserved   | Reserved   | Reserved   | Reserved    | Reserved    | Reserved    |

| DCLKCRC  | 05 | DATAADJ[3] | DATAADJ[2] | DATAADJ[1] | DATAADJ[0] | MODSYNC    | MODADJ[2]   | MODADJ[1]   | MODADJ[0]   |

|          | 06 |            |            |            | Rese       | erved      |             |             |             |

|          | 07 |            |            |            | Rese       | erved      |             |             |             |

|          | 08 |            |            |            | Rese       | erved      |             |             |             |

|          | 09 |            | Reserved   |            |            |            |             |             |             |

|          | 0A |            | Reserved   |            |            |            |             |             |             |

|          | 0B |            |            |            | Rese       | erved      |             |             |             |

|          | 0C |            |            |            | Rese       | erved      |             |             |             |

|          | 0D |            |            |            | Rese       | erved      |             |             |             |

| CALMEMCK | 0E |            |            | CALMEM[1]  | CALMEN[0]  |            | CALCKDIV[2] | CALCKDIV[2] | CALCKDIV[2] |

| MEMRDWR  | 0F | CALSTAT    | CALEN      | XFERSTAT   | XFEREN     | SMEMWR     | SMEMRD      | FMEMRD      | UNCAL       |

| MEMADDR  | 10 | MEMADDR[7] | MEMADDR[6] | MEMADDR[5] | MEMADDR[4] | MEMADDR[3] | MEMADDR[2]  | MEMADDR[1]  | MEMADDR[0]  |

| MEMDATA  | 11 |            |            | MEMDATA[5] | MEMDATA[4] | MEMDATA[3] | MEMDATA[2]  | MEMDATA[1]  | MEMDATA[0]  |

| DCRCSTAT | 12 |            |            |            |            |            | DCRCSTAT[2] | DCRCSTAT[1] | DCRCSTAT[0] |

#### Table 12.

| COMMS(00) | Bit | Direction | Default | Description                                                               |

|-----------|-----|-----------|---------|---------------------------------------------------------------------------|

| SDIODIR   | 7   | 1         | 0       | 0: SDIO pin configured for input only during data transfer                |

|           |     |           |         | 1: SDIO configured for input or output during data transfer               |

| DATADIR   | 6   | 1         | 0       | 0: Serial data uses MSB-first format                                      |

|           |     |           |         | 1: Serial data uses LSB-first format                                      |

| SWRST     | 5   | 1         | 0       | 1: Default all serial register bits, except Address 0x00 and Address 0x04 |

| SLEEP     | 4   | 1         | 0       | 1: DAC output current off                                                 |

| PDN       | 3   | 1         | 0       | 1: All analog and digital circuitry, except serial interface, off         |

| EXREF     | 0   | I         | 0       | 0: Internal band gap reference                                            |

|           |     |           |         | 1: External reference                                                     |

| Table 13.   |       |           |         |                                                     |

|-------------|-------|-----------|---------|-----------------------------------------------------|

| FILTER(01)  | Bit   | Direction | Default | Description                                         |

| INTERP[1:0] | [7:6] | I         | 00      | 00: No interpolation                                |

|             |       |           |         | 01: Interpolation 2×                                |

|             |       |           |         | 10: Interpolation 4×                                |

|             |       |           |         | 11: Interpolation 8×                                |

| ZSTUFF      | 3     | I         | 0       | 1: Zero stuffing on                                 |

| HPFX8       | 2     | I         | 0       | 0: ×8 interpolation filter configured for low-pass  |

|             |       |           |         | 1: ×8 interpolation filter configured for high-pass |

| HPFX4       | 1     | I         | 0       | 0: ×4 interpolation filter configured for low-pass  |

|             |       |           |         | 1: ×4 interpolation filter configured for high-pass |

| HPFX2       | 0     | I         | 0       | 0: ×2 interpolation filter configured for low-pass  |

|             |       |           |         | 1: ×2 interpolation filter configured for high-pass |

### Table 14.

| DATA(02) | Bit | Direction | Default | Description                                                                                       |

|----------|-----|-----------|---------|---------------------------------------------------------------------------------------------------|

| DATAFMT  | 7   | 1         | 0       | 0: Twos complement data format                                                                    |

|          |     |           |         | 1: Unsigned binary input data format                                                              |

| ONEPORT  | 6   | 1         | 0       | 0: I and Q input data onto Port 1 and Port 2, respectively                                        |

|          |     |           |         | 1: I and Q input data interleaved onto Port 1                                                     |

| DCLKSTR  | 5   | I         | 0       | 0: DATACLK pin, 12 mA drive strength                                                              |

|          |     |           |         | 1: DATACLK pin, 24 mA drive strength                                                              |

| DCLKPOL  | 4   | 1         | 0       | 0: Input data latched on DATACLK/DACCLK rising edge (dependent on mode)                           |

|          |     |           |         | 1: Input data latched on DATACLK/DACCLK falling edge (dependent on mode)                          |

| DCLKEXT  | 3   | I         | 0       | 0: DATACLK pin inputs channel data rate or modulator synchronizer clock                           |

|          |     |           |         | 1: DATACLK pin outputs channel data rate or modulator synchronizer clock                          |

| DCLKCRC  | 2   | I         | 0       | 0: With DATACLK pin as input, DATACLK clock recovery off                                          |

|          |     |           |         | 1: With DATACLK pin as input, DATACLK clock recovery on                                           |

| IQPOL    | 1   | I         | 0       | 0: In one-port mode, IQSEL = 1 latches data into I channel, IQSEL = 0 latches data into Q channel |

|          |     |           |         | 1: In one-port mode, IQSEL = 0 latches data into I channel, IQSEL = 1 latches data into Q channel |

| GRAYDIN  | 0   | 1         | 0       | 0: Gray decoder off                                                                               |

|          |     |           |         | 1: Gray decoder on                                                                                |

#### Table 15.

| MODULATE(03) | Bit   | Direction | Default | Description                              |                    |                                          |  |

|--------------|-------|-----------|---------|------------------------------------------|--------------------|------------------------------------------|--|

| CHANNEL      | 7     | I         | 0       | MODDUAL                                  | CHANNEL            |                                          |  |

|              |       |           |         | 0x03[5]                                  | 0x03[7]            |                                          |  |

|              |       |           |         | 0                                        | 0                  | I channel processing routed to DAC       |  |

|              |       |           |         | 0                                        | 1                  | Q channel processing routed to DAC       |  |

|              |       |           |         | 1                                        | 0                  | Modulator real output routed to DAC      |  |

|              |       |           |         | 1                                        | 1                  | Modulator imaginary output routed to DAC |  |

| HILBERT      | 6     | I         | 0       | 1: With MODDUAL on, Hilbert transform on |                    |                                          |  |

| MODDUAL      | 5     | I         | 0       | 0: Modulator u                           | ses a single chann | nel                                      |  |

|              |       |           |         | 1: Modulator u                           | ses both I and Q c | hannels                                  |  |

| SIDEBAND     | 4     | I         | 0       | 0: With MODD                             | JAL on, upper side | eband rejected                           |  |

|              |       |           |         | 1: With MODD                             | JAL on, lower side | band rejected                            |  |

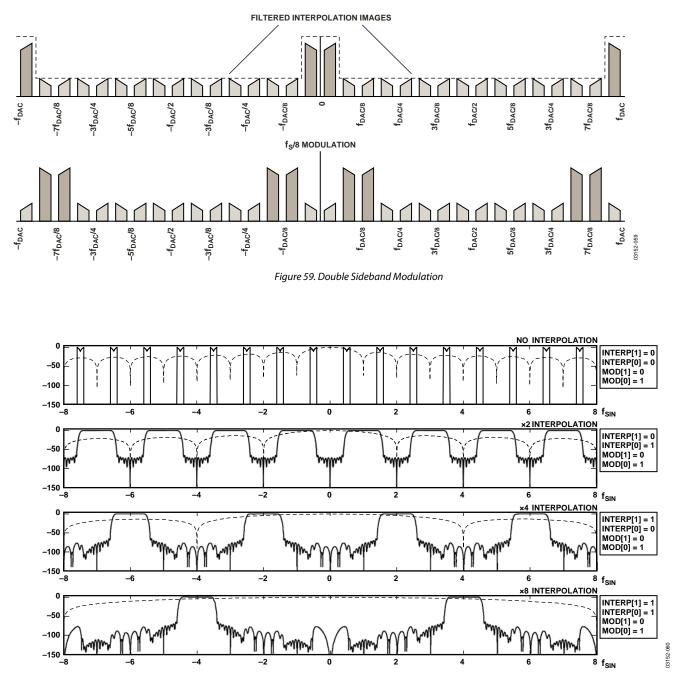

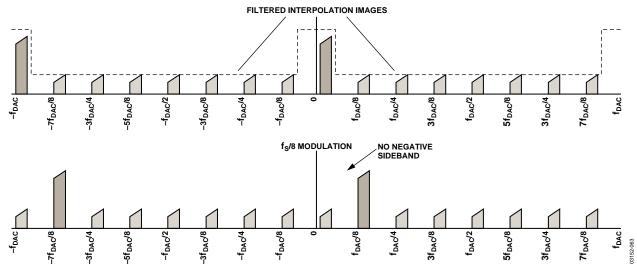

| MOD[1:0]     | [3:2] | I         | 00      | 00: No modula                            | tion               |                                          |  |

|              |       |           |         | 01: fs/2 modula                          | ition              |                                          |  |

|              |       |           |         | 10: fs/4 modula                          | ition              |                                          |  |

|              |       |           |         | 11: fs/8 modula                          | ition              |                                          |  |

| DCLKCRC(05)  | Bit   | Direction | Default | Desci                                    | Description          |                      |                      |                              |

|--------------|-------|-----------|---------|------------------------------------------|----------------------|----------------------|----------------------|------------------------------|

| DATAADJ[3:0] | [7:4] | I         | 0000    | DATA                                     | CLK offset (†        | wos comp             | olement r            | epresentation)               |

|              |       |           |         | 0111:                                    | +7                   | -                    |                      |                              |

|              |       |           |         | :                                        |                      |                      |                      |                              |

|              |       |           |         | 0000:                                    | 0                    |                      |                      |                              |

|              |       |           |         | :                                        | 0                    |                      |                      |                              |

|              |       |           | 00      | 1000:                                    |                      |                      |                      |                              |

| MODSYNC      | 3     | 1         | 00      |                                          | annel data r         |                      |                      |                              |

|              |       |           |         | 1: State machine clock synchronizer mode |                      |                      |                      |                              |

| MODADJ[2:0]  | [2:0] | I         | 000     |                                          | <b>f</b> s/ <b>8</b> | <b>f</b> s/ <b>4</b> | <b>f</b> s/ <b>2</b> | Modulator coefficient offset |

|              |       |           |         | 000                                      | 1                    | 1                    | 1                    |                              |

|              |       |           |         | 001                                      | +1/√2                | 0                    | -1                   |                              |

|              |       |           |         | 010                                      | 0                    | -1                   | 1                    |                              |

|              |       |           |         | 011                                      | -1/√2                | 0                    | -1                   |                              |

|              |       |           |         | 100                                      | -1                   | +1                   | +1                   |                              |

|              |       |           |         | 101                                      | -1/√2                | 0                    | -1                   |                              |

|              |       |           |         | 110                                      | 0                    | -1                   | +1                   |                              |

|              |       |           |         | 111                                      | +1/√2                | 0                    | -1                   |                              |

| Table 17.    |       |           |         |                             |

|--------------|-------|-----------|---------|-----------------------------|

| VERSION(0D)  | Bit   | Direction | Default | Description                 |

| VERSION[3:0] | [3:0] | 0         |         | Hardware version identifier |

### Table 18.

| CALMEMCK(OE)  | Bit   | Direction | Default | Description                                           |

|---------------|-------|-----------|---------|-------------------------------------------------------|

| CALMEM        | [5:4] | 0         | 00      | Calibration memory                                    |

|               |       |           |         | 00: Uncalibrated                                      |

|               |       |           |         | 01: Self-calibration                                  |

|               |       |           |         | 10: Factory calibration                               |

|               |       |           |         | 11: User input                                        |

| CALCKDIV[2:0] | [2:0] | I         | 00      | Calibration clock divide ratio from channel data rate |

|               |       |           |         | 000: /32                                              |

|               |       |           |         | 001:/64                                               |

|               |       |           |         | :                                                     |

|               |       |           |         | 110: /2048                                            |

|               |       |           |         | 111:/4096                                             |

| Table 19.   |     |           |         |                                                |

|-------------|-----|-----------|---------|------------------------------------------------|

| MEMRDWR(OF) | Bit | Direction | Default | Description                                    |

| CALSTAT     | 7   | 0         | 0       | 0: Self-calibration cycle not complete         |

|             |     |           |         | 1: Self-calibration cycle complete             |

| CALEN       | 6   | 1         | 0       | 1: Self-calibration in progress                |

| XFERSTAT    | 5   | 0         | 0       | 0: Factory memory transfer not complete        |

|             |     |           |         | 1: Factory memory transfer complete            |

| XFEREN      | 4   | 1         | 0       | 1: Factory memory transfer in progress         |

| SMEMWR      | 3   | 1         | 0       | 1: Write static memory data from external port |

| SMEMRD      | 2   | 1         | 0       | 1: Read static memory to external port         |

| FMEMRD      | 1   | 1         | 0       | 1: Read factory memory data to external port   |

| UNCAL       | 0   | 1         | 0       | 1: Use uncalibrated                            |

#### Table 20.

| MEMADDR(10)   | Bit   | Direction | Default  | Description                                        |

|---------------|-------|-----------|----------|----------------------------------------------------|

| MEMADDR [7:0] | [7:0] | I/O       | 00000000 | Address of factory or static memory to be accessed |

#### Table 21.

| 1 4010 210    |       |           |         |                                         |

|---------------|-------|-----------|---------|-----------------------------------------|

| MEMDATA(11)   | Bit   | Direction | Default | Description                             |

| MEMDATA [5:0] | [5:0] | I/O       | 000000  | Data or factory or static memory access |

#### Table 22.

| DCRCSTAT(12) | Bit | Direction | Default | Description                                                  |  |

|--------------|-----|-----------|---------|--------------------------------------------------------------|--|

| DCRCSTAT (2) | 2   | 0         | 0       | 0: With DATACLK CRC on, lock has never been achieved         |  |

|              |     |           |         | 1: With DATACLK CRC on, lock has been achieved at least once |  |

| DCRCSTAT(1)  | 1   | 0         | 0       | 0: With DATACLK CRC on, system is currently not locked       |  |

|              |     |           |         | 1: With DATACLK CRC on, system is currently locked           |  |

| DCRCSTAT(0)  | 0   | 0         | 0       | 0: With DATACLK CRC on, system is currently locked           |  |

|              |     |           |         | 1: With DATACLK CRC on, system lost lock due to jitter       |  |

### **DIGITAL FILTER SPECIFICATIONS**

### DIGITAL INTERPOLATION FILTER COEFFICIENTS

Table 23. Stage 1 Interpolation Filter Coefficients

| Lower Coefficient | Upper Coefficient | Integer Value |

|-------------------|-------------------|---------------|

| H(1)              | H(43)             | 9             |

| H(2)              | H(42)             | 0             |

| H(3)              | H(41)             | -27           |

| H(4)              | H(40)             | 0             |

| H(5)              | H(39)             | 65            |

| H(6)              | H(38)             | 0             |

| H(7)              | H(37)             | –131          |

| H(8)              | H(36)             | 0             |

| H(9)              | H(35)             | 239           |

| H(10)             | H(34)             | 0             |

| H(11)             | H(33)             | -407          |

| H(12)             | H(32)             | 0             |

| H(13)             | H(31)             | 665           |

| H(14)             | H(30)             | 0             |

| H(15)             | H(29)             | –1070         |

| H(16)             | H(28)             | 0             |

| H(17)             | H(27)             | 1764          |

| H(18)             | H(26)             | 0             |

| H(19)             | H(25)             | -3273         |

| H(20)             | H(24)             | 0             |

| H(21)             | H(23)             | 10358         |

| H(22)             |                   | 16384         |

#### Table 24. Stage 2 Interpolation Filter Coefficients

| Lower Coefficient | Upper Coefficient | Integer Value |

|-------------------|-------------------|---------------|

| H(1)              | H(19)             | 19            |

| H(2)              | H(18)             | 0             |

| H(3)              | H(17)             | -120          |

| H(4)              | H(16)             | 0             |

| H(5)              | H(15)             | 436           |

| H(6)              | H(14)             | 0             |

| H(7)              | H(13)             | -1284         |

| H(8)              | H(12)             | 0             |

| H(9)              | H(11)             | 5045          |

| H(10)             |                   | 8192          |

| Lower Coefficient | Upper Coefficient | Integer Value |

|-------------------|-------------------|---------------|

| H(1)              | H(11)             | 7             |

| H(2)              | H(10)             | 0             |

| H(3)              | H(9)              | -53           |

| H(4)              | H(8)              | 0             |

| H(5)              | H(7)              | 302           |

| H(6)              |                   | 512           |

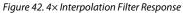

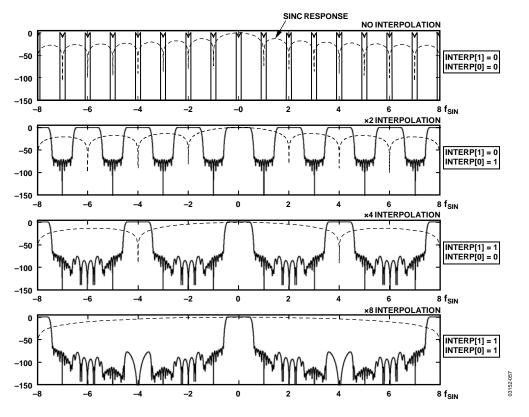

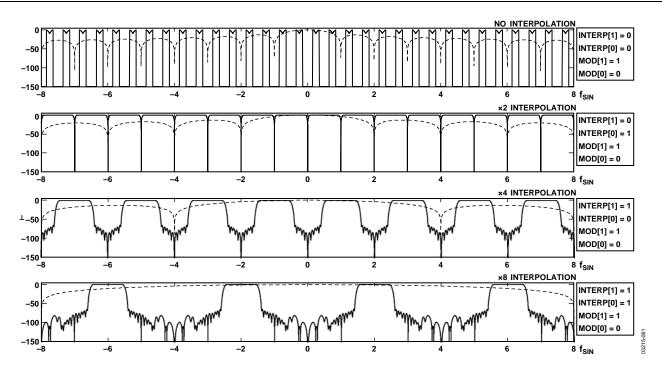

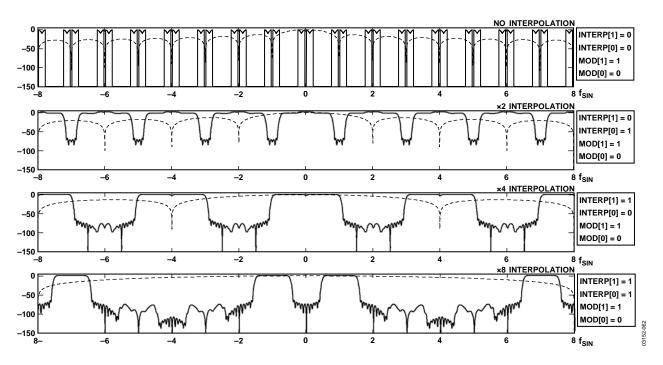

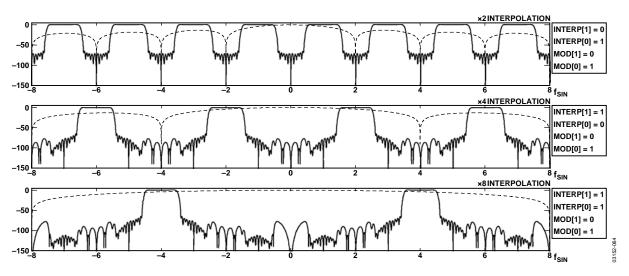

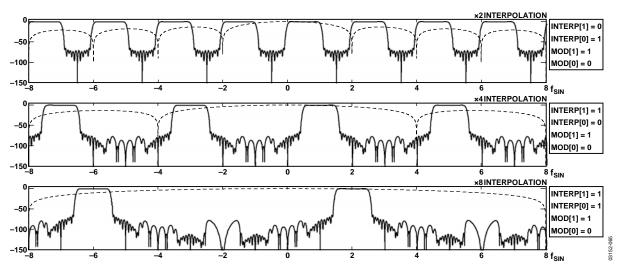

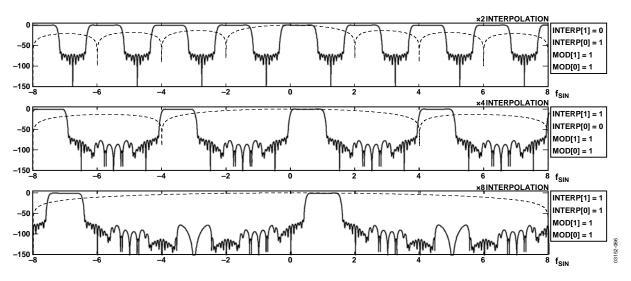

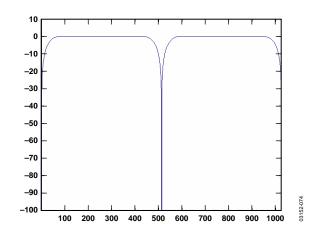

Figure 41. 2× Interpolation Filter Response

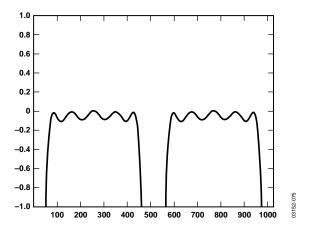

Figure 43.8× Interpolation Filter Response

### **CLOCK/DATA TIMING**

| DCLKEXT<br>0x02, Bit 3 | MODSYNC<br>0x05, Bit 3 | DCLKCRC<br>0x02, Bit 2 | Mode               | Function                                                |

|------------------------|------------------------|------------------------|--------------------|---------------------------------------------------------|

| 1                      | 0                      | Х                      | DATACLK Master     | Channel data rate clock output                          |

| 1                      | 1                      | X                      | Modulator Master   | Modulator synchronization<br>DATACLK output             |

| 0                      | 0                      | 0                      | External Sync Mode | DATACLK inactive, DACCLK synchronous with external data |

| 0                      | 0                      | 1                      | DATACLK Slave      | DATACLK input, data rate clock, data recovery on        |

| 0                      | 1                      | 0                      | Low Setup/Hold     | DATACLK input, input data synchronous with DATACLK      |

| 0                      | 1                      | 1                      | Modulator Slave    | Input modulator synchronizer<br>DATACLK input           |

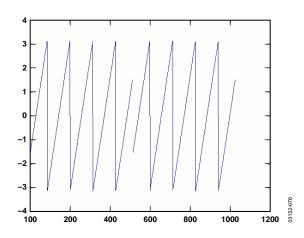

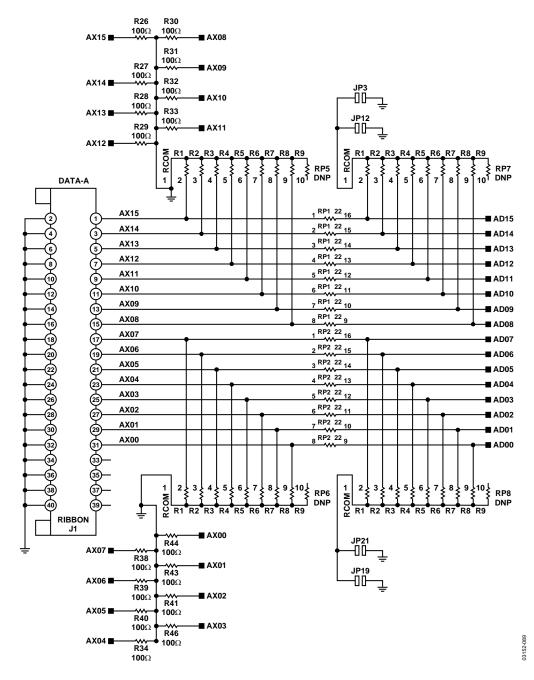

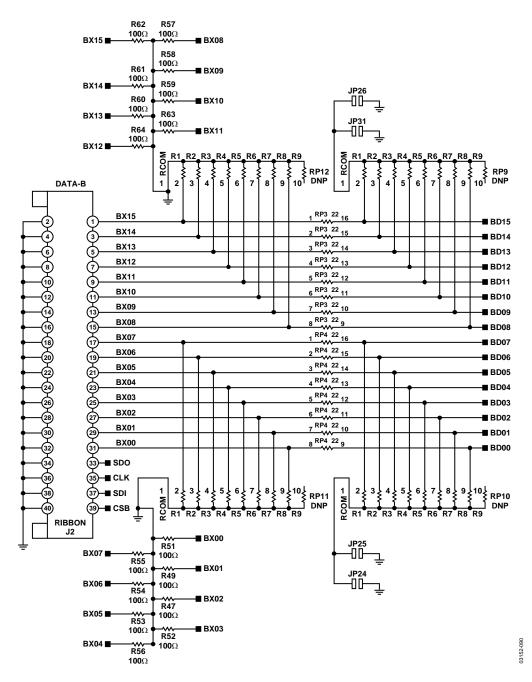

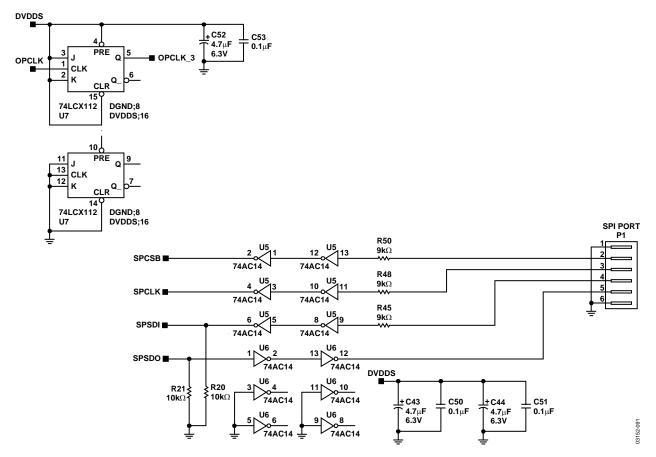

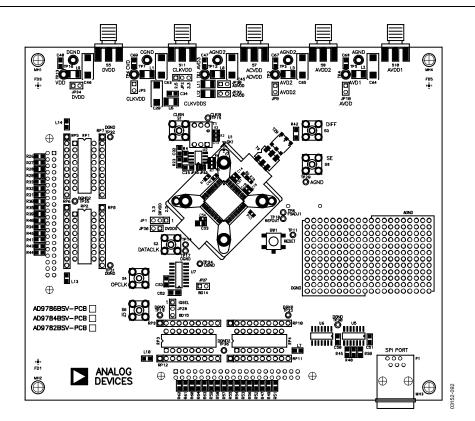

#### Two-Port Data Input Mode (DATACLK Master)

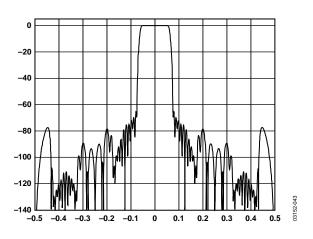

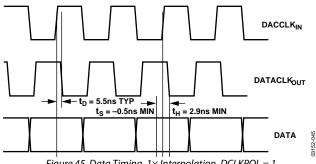

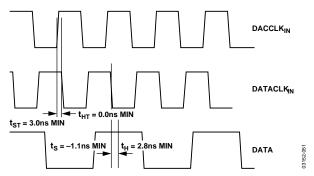

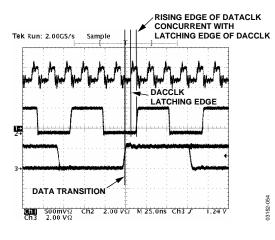

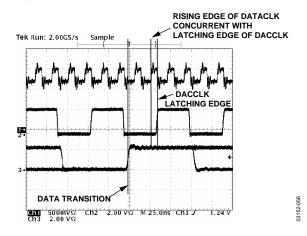

With the interpolation set to 1×, the DATACLK output is a delayed and inverted version of DACCLK at the same frequency. Note that DACCLK refers to the differential clock inputs applied at Pin 5 and Pin 6. As Figure 44 and Figure 45 show, there is a constant delay between the edges of DACCLK and DATACLK.

The DCLKPOL bit (Register 0x02, Bit 4) allows the data to be latched into the AD9786 upon either the rising or falling edge of DACCLK. With DCLKPOL = 0, the data is latched in upon the falling edge of DACCLK, as shown in Figure 44. With DCLKPOL = 1, as shown in Figure 45, data is latched in upon the rising edge of DACCLK. The setup and hold times are always with respect to the latching edge of DACCLK.

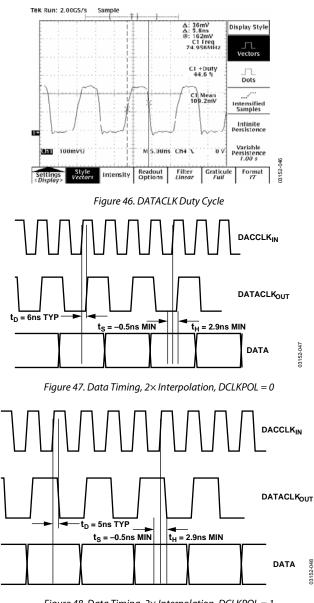

With the interpolation set to 2×, the DACCLK input runs at twice the speed of the DATACLK. Data is latched into the digital inputs of the AD9786 upon every other rising edge of DACCLK, as shown in Figure 47 and Figure 48. With DCLKPOL = 0, as shown in Figure 47, the latching edge of DACCLK is the rising edge that occurs just before the falling edge of DATACLK. With DCLKPOL = 1, as in Figure 48, the latching edge of DACCLK is the rising edge of DACCLK that occurs just before the rising edge of DATACLK. The setup and hold time values are identical to those in Figure 44 and Figure 45.

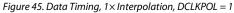

Note that there is a slight difference in the delay from the rising edge of DACCLK to the falling edge of DATACLK, and the delay from the rising edge of DACCLK to the rising edge of DATACLK. As Figure 46 shows, the DATACLK duty cycle is slightly less than 50%. This is true in all modes.

With the interpolation set to 4× or 8×, the DACCLK input runs at 4× or 8× the speed of the DATACLK output. The data is latched in upon a rising edge of DACCLK, similar to the 2× interpolation mode.

However, the latching edge is every fourth edge in 4× interpolation mode and every eighth edge in the 8× interpolation mode. Similar to operation in the 2× interpolation mode, with DCLKPOL = 0, the latching edge of DACCLK is the rising edge that occurs just before the falling edge of DATACLK. With DCLKPOL = 1, the latching edge of DACCLK is the rising edge that occurs just before the rising edge of DATACLK. The setup and hold time values are identical to those in  $1 \times$ and 2× interpolation.

Figure 48. Data Timing,  $2 \times$  Interpolation, DCLKPOL = 1

### DATACLK Slave Mode (Data Recovery On)

DATACLK (Pin 31) can be used as an input to synchronize multiple AD9786s. A clock generated by an AD9786 operating in master mode, or a clock from an external source, can be used to drive DATACLK.

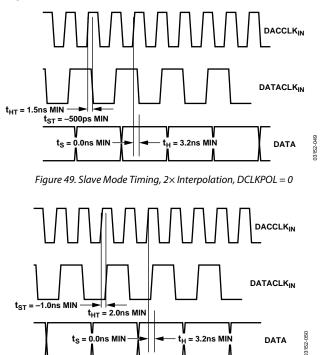

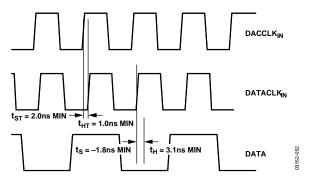

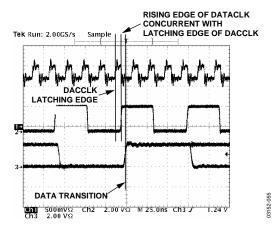

In this mode, two clocks are required to be applied to the AD9786. A clock running at the DAC sample rate, referred to as DACCLK, must be applied to the differential inputs (Pin 5 and Pin 6) of the AD9786. As described previously, a clock at the input sample rate must also be applied to Pin 31 (DATACLK). An internal DLL synchronizes the two applied clocks. The timing relationships between the input data, DATACLK, and DACCLK are given in Figure 49 and Figure 50. Note that DCLKPOL (Register 0x02, Bit 4) can be used to select the edge of DACCLK upon which the input data is latched.

There is a defined setup-and-hold window with respect to input data and the latching edge of DACCLK. There is also a required timing relationship between DATACLK and DACCLK. This is referred to in Figure 49 and Figure 50 as  $t_{ST}$  and  $t_{HT}$  (setup and hold for transition). For example, with DCLKPOL set to Logic 0, the input data latches upon the first rising edge of DACCLK that occurs more than 1.5 ns before the falling edge of DATACLK. DACCLK should not be given a rising edge in the window of 500 ps to 1.5 ns before the latching edge (falling edge when DCLKPOL = 0, rising edge when DCLKPOL = 1) of DATACLK. Failure to account for this timing relationship could result in corrupt data.

There are three status bits available for a read that allow the user to verify DLL lock. These are Bit 0, Bit 1, and Bit 2 (DCRCSTAT) in Register 0x12.

Figure 50. Slave Mode Timing,  $2 \times$  Interpolation, DCLKPOL = 1

### Low Setup/Hold Mode (DATACLK Input, Data Recovery Off)

Some applications might require that digital input data be synchronized with the DATACLK input, rather than DACCLK. For these applications, the AD9786 can be programmed for low setup/hold mode by entering the values in Table 26 into the SPI registers. With data recovery off and the MODSYNC bit set to Logic 1, the AD9786 latches data in upon the rising or falling edge of DATACLK input, depending on the state of DCLKPOL.

Figure 51. Low Setup and Hold Mode Timing,  $1 \times$  Interpolation, DCLKPOL = 0

Figure 52. Low Setup and Hold Mode Timing,  $1 \times$  Interpolation, DCLKPOL = 1

### External Sync Mode

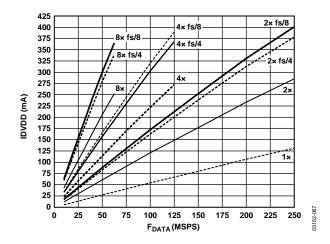

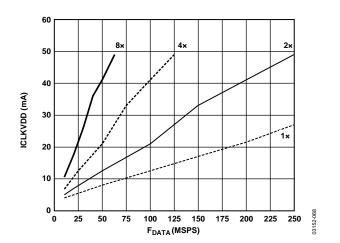

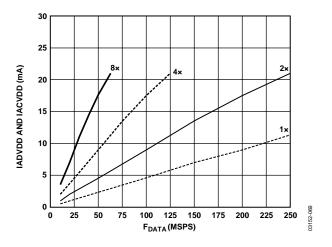

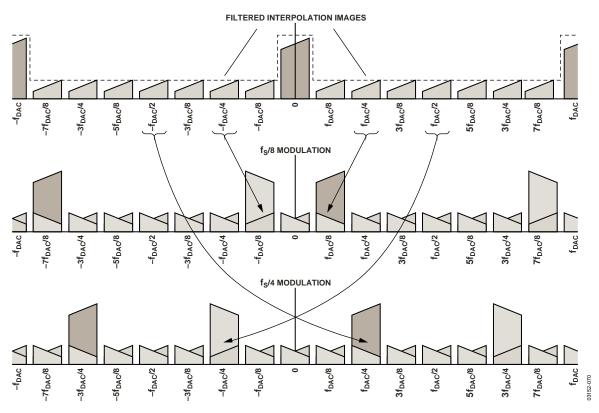

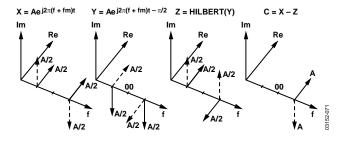

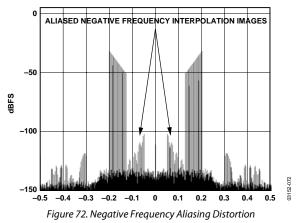

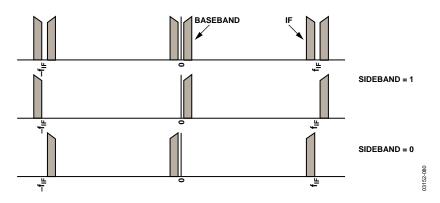

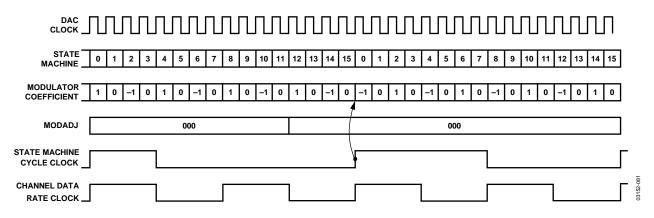

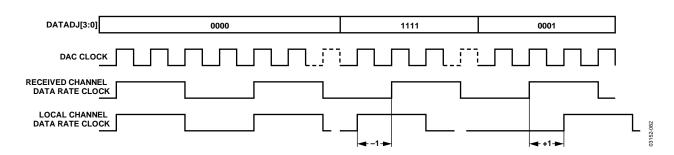

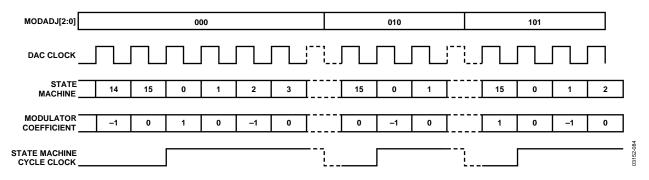

In the external sync mode, the DATACLK is programmed as an input but is not used. Applying a DATACLK input while in this mode has no effect. The digital input data is synchronized solely to the DACCLK input. With  $1\times$  interpolation, the data input is latched upon every rising edge of DACCLK. The challenge is that the user has no way of knowing exactly which edge is the latching edge when the interpolating filters are in use. In  $2\times$ ,  $4\times$ , and  $8\times$  interpolation modes, the latching edge of DACCLK is every  $2^{nd}$ ,  $4^{th}$ , or  $8^{th}$  edge, respectively.