# L4969UR-E L4969URD-E

# System voltage regulator with fault tolerant low speed CAN transceiver

#### **Features**

- Operating supply voltage 6 V to 28 V, transient up to 40 V

- Low quiescent current consumption, less than 40 µA in sleep mode

- Two very low drop voltage regulators 5 V/200 mA

- Separate voltage regulator for CAN transceiver supply with low power sleep mode

- Efficient microcontroller supervision and reset logic

- 24 bit serial interface

- An unpowered or insufficiently supplied node does not disturb the bus lines

- V<sub>S</sub> voltage sense comparator

- Supports transmission with groundshift: single wire 1.5 V - differential: 3 V

# **Description**

The L4969UR-E and L4969URD-E are integrated circuits containing 3 independent voltage regulators and a standard fault tolerant low speed CAN line interface in multipower BCD3S process.

They integrate all main local functions for automotive body electronic applications connected to a CAN bus.

Table 1. Device summary

| Package    | Order codes         |               |  |  |

|------------|---------------------|---------------|--|--|

| rackage    | Tube                | Tape and reel |  |  |

| SO-20      | L4969URD-E          | L4969URDTR-E  |  |  |

| PowerSO-20 | -20 L4969UR-E L4969 |               |  |  |

December 2011 Doc ID 022587 Rev 1 1/46

# **Contents**

| 1 | Bloc | k diagra  | am and pins description                       | 6  |

|---|------|-----------|-----------------------------------------------|----|

| 2 | Elec | trical sp | ecifications                                  | 8  |

|   | 2.1  | Absolu    | te maximum ratings                            | 8  |

|   | 2.2  | Therma    | al data                                       | 8  |

|   | 2.3  | Electric  | cal characteristics                           | 9  |

| 3 | Fund | ctional d | lescription                                   | 16 |

|   | 3.1  | Genera    | al features                                   | 16 |

|   |      | 3.1.1     | V <sub>1</sub> output voltage                 | 16 |

|   |      | 3.1.2     | V <sub>2</sub> output voltage                 | 16 |

|   |      | 3.1.3     | V <sub>3</sub> output voltage                 | 17 |

|   |      | 3.1.4     | Internal supply voltage                       | 17 |

|   | 3.2  | Power-    | up, initialization and sleep mode transitions | 17 |

|   | 3.3  | CAN tra   | ansceiver                                     | 18 |

|   |      | 3.3.1     | Negligible errors                             | 19 |

|   |      | 3.3.2     | Problematic errors                            | 20 |

|   |      | 3.3.3     | Severe errors                                 | 20 |

|   |      | 3.3.4     | Wakeup via CAN                                | 20 |

|   | 3.4  | Oscilla   | tor                                           | 21 |

|   | 3.5  | Watcho    | dog                                           | 21 |

|   | 3.6  | Reset     |                                               | 21 |

|   |      | 3.6.1     | Power-on reset                                | 21 |

|   |      | 3.6.2     | Undervoltage reset                            | 22 |

|   |      | 3.6.3     | Reset signalling during sleepmode             | 22 |

|   | 3.7  | Identifi  | er filter                                     | 23 |

|   | 3.8  | Ground    | d shift detection                             | 23 |

|   | 3.9  | Therma    | al protection                                 | 24 |

|   | 3.10 |           | nterface (SPI)                                |    |

|   |      | 3.10.1    | General dataframe format                      |    |

|   |      | 3.10.2    | Address/command field                         |    |

|   |      | 3.10.3    | Datafield #1                                  |    |

|   |      | 3.10.4    | Datafield #2/CRC                              |    |

|   |      |           |                                               |    |

|   | 3.11  | Memory map                                                            |

|---|-------|-----------------------------------------------------------------------|

| 4 | Cont  | rol and status registers                                              |

|   | 4.1   | ADR 0: VRCR voltage regulator control register                        |

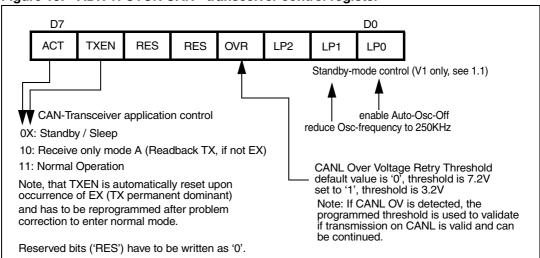

|   | 4.2   | ADR 1: CTCR CAN - transceiver control register                        |

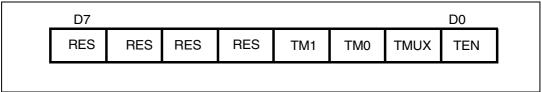

|   | 4.3   | ADR 2: GPTR global parameter and test register                        |

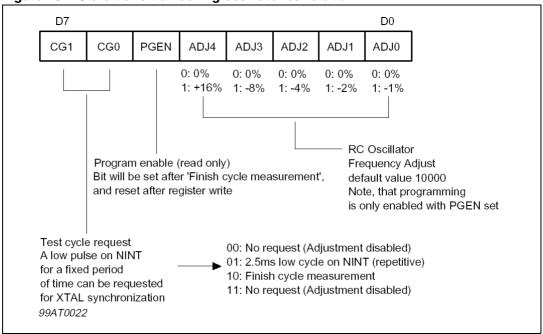

|   | 4.4   | ADR 3: RCADJ RC-oscillator adjust register                            |

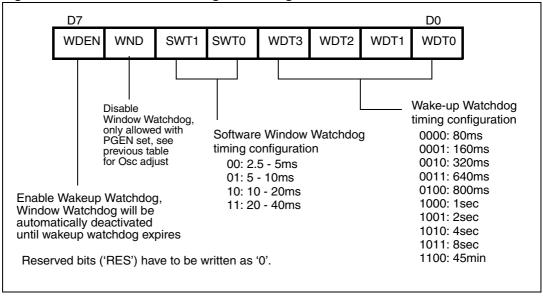

|   | 4.5   | ADR4: WDC watchdog control register                                   |

|   |       | 4.5.1 Watchdog configuration                                          |

|   |       | 4.5.2 Startup                                                         |

|   |       | 4.5.3 Window watchdog                                                 |

|   |       | 4.5.4 Wakeup watchdog                                                 |

|   | 4.6   | ADR5: GIEN global interrupt enable register                           |

|   | 4.7   | ADR6: IFR interrupt flag register                                     |

|   | 4.8   | ADR7: CTSR CAN transceiver status register                            |

|   | 4.9   | ADR 8 and 9: ID01, ID23 identifier filter sequence select register 37 |

|   | 4.10  | ADR 10: BTL identifier filter bittimelogic control register           |

|   | 4.11  | ADR 15: SYS system status register                                    |

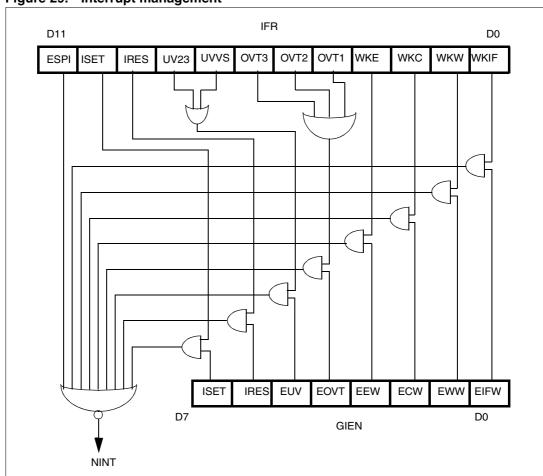

| 5 | Inter | rupt management40                                                     |

| 6 | Rema  | arks for application41                                                |

| 7 | Pack  | age information                                                       |

|   | 7.1   | ECOPACK <sup>®</sup> packages                                         |

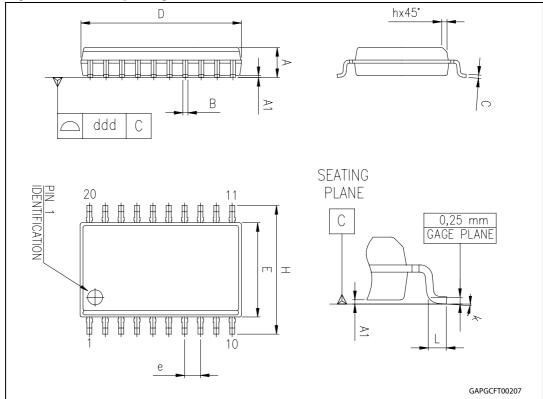

|   | 7.2   | SO-20 package information                                             |

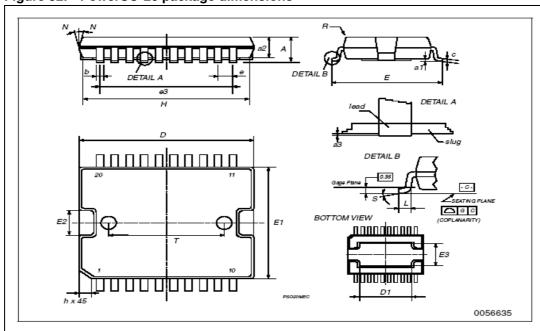

|   | 7.3   | PowerSO-20 package information                                        |

| Ω | Revie | sion history 45                                                       |

# List of tables

| Table 1.  | Device summary                            | 1  |

|-----------|-------------------------------------------|----|

| Table 2.  | Pins description                          |    |

| Table 3.  | Absolute maximum ratings                  | 8  |

| Table 4.  | Thermal data of PowerSO-20                | 8  |

| Table 5.  | Supply current                            | 9  |

| Table 6.  | Voltage regulator 1                       | 9  |

| Table 7.  | Voltage regulator 2 and 3                 | 10 |

| Table 8.  | Reset and watchdog                        | 10 |

| Table 9.  | CAN Line Interface                        | 11 |

| Table 11. | Serial data interface                     | 13 |

| Table 10. | Digital I/O                               | 13 |

| Table 12. | Diagnostic functions                      | 14 |

| Table 13. | CAN error detection                       | 14 |

| Table 14. | Wakeup                                    | 15 |

| Table 15. | Operating mode description                | 16 |

| Table 16. | Detectable physical busline failures      | 19 |

| Table 17. | L4969UR memory map                        | 27 |

| Table 18. | Operating modes of the CAN line interface | 29 |

| Table 19. | SO-20 mechanical data                     | 43 |

| Table 20. | PowerSO-20 mechanical data                | 44 |

| Table 21  | Document revision history                 | 45 |

# **List of figures**

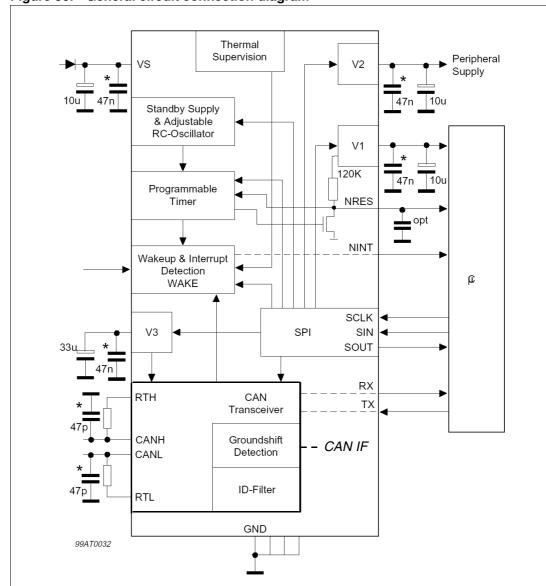

| Figure 1.  | Block diagram                                                                           | 6  |

|------------|-----------------------------------------------------------------------------------------|----|

| Figure 2.  | Pins configuration                                                                      | 7  |

| Figure 3.  | State diagram                                                                           |    |

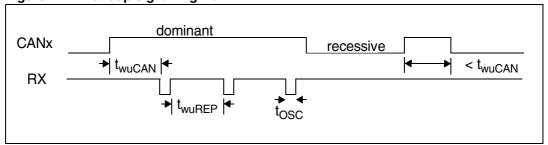

| Figure 4.  | Wakeup signalling via RX                                                                | 20 |

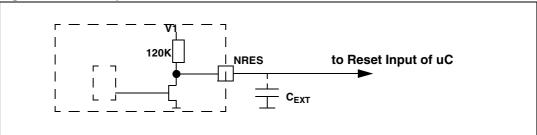

| Figure 5.  | NRES pin internal structure                                                             | 22 |

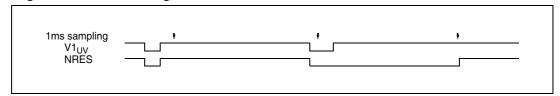

| Figure 6.  | NRES timings                                                                            |    |

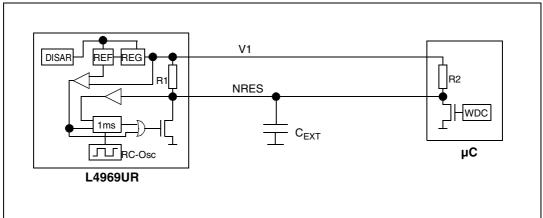

| Figure 7.  | Internal circuitry and suggested C <sub>EXT</sub> for NRES generation during sleep mode |    |

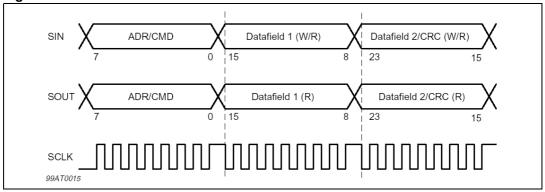

| Figure 8.  | General dataframe format                                                                | 25 |

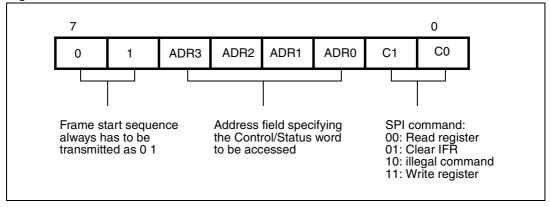

| Figure 9.  | Address / command field                                                                 | 25 |

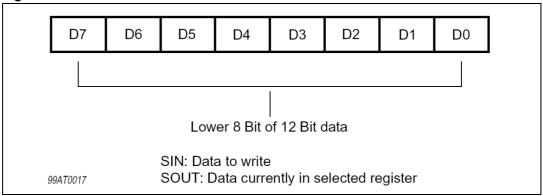

| Figure 10. | Datafield #1                                                                            |    |

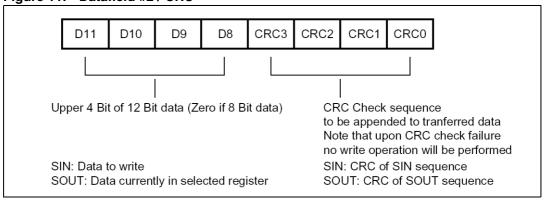

| Figure 11. | Datafield #2 / CRC                                                                      |    |

| Figure 12. | ADR 0: VRCR voltage regulator control register                                          | 28 |

| Figure 13. | ADR 1: CTCR CAN - transceiver control register                                          |    |

| Figure 14. | ADR 2: GPTR global parameter and test register                                          | 30 |

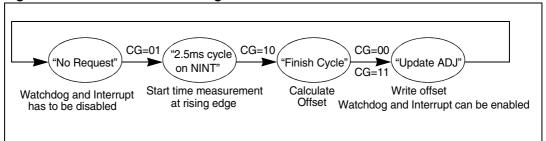

| Figure 15. | State transition during oscillator calibration                                          | 30 |

| Figure 16. | State transition during oscillator calibration                                          |    |

| Figure 17. | ADR4: WDC watchdog control register                                                     | 31 |

| Figure 18. | Watchdog configuration                                                                  | 32 |

| Figure 19. | Startup                                                                                 | 33 |

| Figure 20. | Window watchdog                                                                         | 33 |

| Figure 21. | Wakeup watchdog                                                                         |    |

| Figure 22. | Valid timing windows for WDC register rewrite                                           | 35 |

| Figure 23. | ADR5: GIEN global interrupt enable register                                             |    |

| Figure 24. | ADR6: IFR interrupt flag register                                                       |    |

| Figure 25. | ADR7: CTSR CAN transceiver status register                                              |    |

| Figure 26. | ADR 8 and 9: ID01, ID23 identifier filter sequence select register                      | 37 |

| Figure 27. | ADR 10: BTL identifier filter bittimelogic control register                             |    |

| Figure 28. | ADR 15: SYS system status register                                                      |    |

| Figure 29. | Interrupt management                                                                    |    |

| Figure 30. | General circuit connection diagram                                                      |    |

| Figure 31. | SO-20 package dimensions                                                                | 42 |

| Figure 32. | PowerSO-20 package dimensions                                                           | 43 |

# 1 Block diagram and pins description

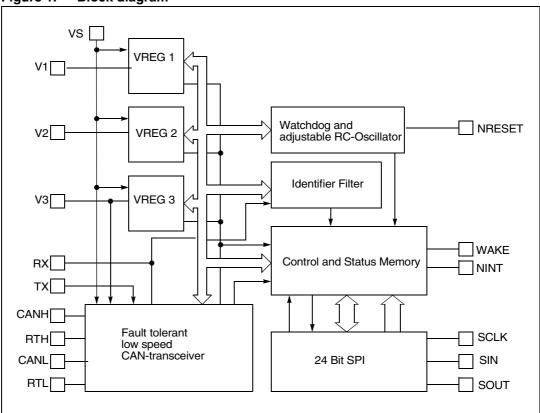

Figure 1. Block diagram

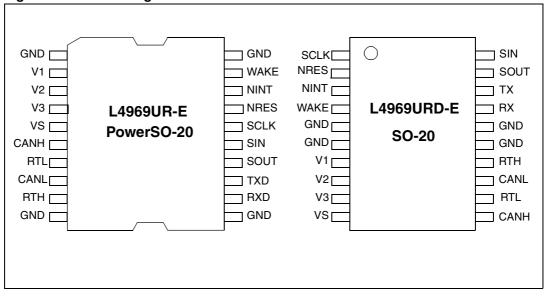

Table 2. Pins description

| Pin Nu        | mber         | Din nome | Function                                  |

|---------------|--------------|----------|-------------------------------------------|

| PowerSO-20    | SO-20        | Pin name | Function                                  |

| 1, 10, 11, 20 | 5, 6, 15, 16 | GND      | Power ground                              |

| 2             | 7            | V1       | Microcontroller supply voltage            |

| 3             | 8            | V2       | Peripheral supply voltage                 |

| 4             | 9            | V3       | Internal CAN supply                       |

| 5             | 10           | VS       | Power supply                              |

| 6             | 11           | CANH     | CANH line driver output                   |

| 7             | 12           | RTL      | CANL termination source                   |

| 8             | 13           | CANL     | CANL line driver output                   |

| 9             | 14           | RTH      | CANH termination source                   |

| 12            | 17           | RXD      | Act. Low CAN receive dominant data output |

| 13            | 18           | TXD      | Act. Low CAN transmit dominant data input |

| 14            | 19           | SOUT     | Serial data output                        |

Table 2. Pins description (continued)

| Pin Nu     | mber  | Pin name     | Function                           |  |

|------------|-------|--------------|------------------------------------|--|

| PowerSO-20 | SO-20 | Fill lialile |                                    |  |

| 15         | 20    | SIN          | Serial data input                  |  |

| 16         | 1     | SCLK         | Serial clock                       |  |

| 17         | 2     | NRES         | Act. low reset output              |  |

| 18         | 3     | NINT         | Act. low interrupt request         |  |

| 19         | 4     | WAKE         | Dual edge triggerable wakeup input |  |

Figure 2. Pins configuration

# 2 Electrical specifications

# 2.1 Absolute maximum ratings

Applying stress which exceeds the ratings listed in the *Table 3: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to the conditions in this section for extended periods may affect device reliability.

Table 3. Absolute maximum ratings<sup>(1)</sup>

| Symbol                           | Parameter                                       | Value                                            | Unit |

|----------------------------------|-------------------------------------------------|--------------------------------------------------|------|

| V <sub>VSDC</sub>                | DC operating supply voltage                     | -0.3 to 28                                       | V    |

| V <sub>VSTR</sub>                | Transient operating supply voltage (T < 400 ms) | -0.3 to 40                                       | V    |

| I <sub>VOUT13</sub>              | Output currents                                 | Internally limited                               |      |

| T <sub>STG</sub>                 | Storage temperature                             | -65 to 150                                       | °C   |

| $T_J$                            | Operating junction temperature                  | -40 to 150                                       | °C   |

| V <sub>OUT1</sub> <sup>(2)</sup> | Externally forced output voltage OUT1           | $-0.3 \text{ to V}_{S} + 0.3, \text{ max} + 6.3$ | V    |

| V <sub>OUT2</sub> <sup>(2)</sup> | Externally forced output voltage OUT2           | -0.3 to V <sub>S</sub> + 0.3                     | ٧    |

| V <sub>OUT3</sub> <sup>(2)</sup> | Externally forced output voltage OUT3           | $-0.3 \text{ to V}_{S} + 0.3, \text{ max} + 6.3$ | V    |

| V <sub>inli</sub>                | Input voltage logic inputs: SIN, SCLK, NRES     | -0.3 to 7                                        | V    |

| V <sub>inliW</sub>               | Input voltage WAKE                              | -0.3 to V <sub>S</sub> + 0.3                     | V    |

| V <sub>canh</sub>                | Voltage CANH line <sup>(3)</sup>                | -28 to 40                                        | V    |

| V <sub>canl</sub>                | Voltage CANL line                               | -28 to 40                                        | V    |

<sup>1.</sup> All pins of the IC are protected against ESD. The verification is performed according to MIL 883C, human body model with R = 1.5 k $\Omega$ , C = 100 pF and discharge voltage 2000 V, corresponding to a maximum discharge energy of 0.2 mJ.

#### 2.2 Thermal data

Table 4. Thermal data of PowerSO-20

| Symbol             | Parameter                           | Value             | Unit |

|--------------------|-------------------------------------|-------------------|------|

| R <sub>thj-a</sub> | Thermal resistance junction-ambient | 40 <sup>(1)</sup> | °C/W |

| R <sub>thj-c</sub> | Thermal resistance junction-case    | 3                 | °C/W |

<sup>1.</sup> Typical value soldered on a PC board with 8 cm<sup>2</sup> copper ground plane (35µm thick).

<sup>2.</sup> Voltage forced means voltage limited to the specified values while the current is not limited.

<sup>3.</sup> ESD pulses on CAN-pins up to 4 KV HBM vs GND with all other pins grounded.

# 2.3 Electrical characteristics

$V_{S}$  = 14 V,  $T_{j}$  = -40°C to 150°C, unless otherwise specified

Table 5. Supply current

| Symbol             | Parameter                                                               | Test conditions                                                            | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

|                    | All regulators off (CANH                                                | Timer off (sleep #1)                                                       | 20   | 40   | 60   | μΑ   |

| I <sub>SSL</sub>   | Standby                                                                 | Timer on (sleep #2)                                                        | 50   | 90   | 135  | μΑ   |

| I <sub>SSLWK</sub> | V <sub>1</sub> off, V <sub>2</sub> off, V <sub>3</sub> on (CAN RX only) | RX only                                                                    | 2    | 4    | 6    | mA   |

|                    | V <sub>1</sub> only (CAN Standby)                                       | Timer off (standby #1)                                                     | 100  | 150  | 250  | μΑ   |

| I <sub>SSB</sub>   |                                                                         | Timer on (standby #2)                                                      | 150  | 200  | 300  | μΑ   |

|                    |                                                                         | Default (standby #3)                                                       | 350  | 440  | 600  | μΑ   |

| I <sub>S</sub>     | All regulators on, (CAN active, TX high)                                | I <sub>OUT1</sub> = -100 mA;<br>I <sub>OUT2</sub> = -10 mA; no CAN<br>load | 110  | 120  | 150  | mA   |

| 1                  | Additional oscillator and charge                                        | V <sub>S</sub> = 6 V; Timer off                                            | 55   | 80   | 100  | μΑ   |

| I <sub>SCP</sub>   | pump current at low V <sub>S</sub>                                      | V <sub>S</sub> = 6 V; Timer on                                             | 10   | 30   | 50   | μΑ   |

Table 6. Voltage regulator 1

| Symbol             | Parameter                                    | Test conditions                                                          | Min. | Тур.  | Max. | Unit |

|--------------------|----------------------------------------------|--------------------------------------------------------------------------|------|-------|------|------|

| V                  | V                                            | 6 V < V <sub>S</sub> < 28 V;<br>I <sub>O</sub> > -100 mA <sup>(1)</sup>  | 4.9  | 5     | 5.1  | ٧    |

| V <sub>01</sub>    | V <sub>1</sub> output voltage                | 6 V < V <sub>S</sub> < 28 V;<br>I <sub>O</sub> > -150 mA <sup>(2)</sup>  | 4.9  | 5     | 5.1  | ٧    |

|                    |                                              | I <sub>OUT1</sub> = -10 mA                                               | 0.0  | 0.025 | 0.06 | V    |

| $V_{DP1}$          | Dropout voltage 1@<br>V <sub>S</sub> = 4.8 V | I <sub>OUT1</sub> = -100 mA <sup>(1)</sup>                               | 0.0  | 0.25  | 0.6  | V    |

|                    | 15                                           | I <sub>OUT1</sub> = -150 mA <sup>(2)</sup>                               | 0.0  | 0.4   | 0.9  | V    |

| V                  | Load regulation 1                            | $I_O = -1 \text{ mA to } -100 \text{ mA}^{(1)}$                          | 0    | 10    | 40   | mV   |

| V <sub>OL01</sub>  |                                              | I <sub>O</sub> = -1 mA to -150 mA <sup>(2)</sup>                         | 0    | 10    | 40   | mV   |

| 1                  | Current limit 1                              | 0.8 V < V <sub>Q1</sub> < 4.5 V;<br>V <sub>S</sub> = 6 V <sup>(1)</sup>  | -180 | -400  | -800 | mA   |

| I <sub>LIM1</sub>  |                                              | 0.8 V < V <sub>O1</sub> < 4.5 V;<br>V <sub>S</sub> = 14 V <sup>(2)</sup> | -180 | -400  | -800 | mA   |

| V <sub>OLI1</sub>  | Line regulation 1                            | 6 V < V <sub>S</sub> < 28 V; I <sub>O1</sub> = -1 mA                     | 0    | 5     | 30   | mV   |

| T <sub>OVT1</sub>  | Overtemp flag 1                              | 6 V < V <sub>S</sub> < 28 V                                              | 130  | 140   | 150  | °C   |

| T <sub>OTKL1</sub> | Thermal shutdown 1                           | 6 V < V <sub>S</sub> < 28 V                                              | 175  | 185   | 205  | °C   |

| V                  | Min V <sub>1</sub> reset threshold           | RTC0 = 0                                                                 | 4.15 | 4.5   | 4.7  | V    |

| V <sub>res</sub>   | voltage                                      | RTC0 = 1                                                                 | 3.7  | 4.0   | 4.2  | V    |

<sup>1.</sup> Valid for SO-20 package

<sup>2.</sup> Valid for PowerSO-20 package

Table 7. Voltage regulator 2 and 3

| Symbol            | Parameter                      | Test conditions                                                                                  | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>O</sub>    | O to the standard              | $6 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V}; \text{I}_{\text{O}} > -100 \text{ mA}^{(1)}$  | 4.8  | 5    | 5.2  | V    |

| VO                | Output voltage                 | 6 V < V <sub>S</sub> < 28 V; I <sub>O</sub> > -150 mA <sup>(2)</sup>                             | 4.8  | 5    | 5.2  | ٧    |

| V <sub>DP</sub>   | Dropout voltage                | $V_S = 4.8 \text{ V}; I_{OUT} = 100 \text{ mA}^{(1)}$                                            | 0.0  | 0.25 | 0.6  | V    |

| V DP              | Diopout voltage                | I <sub>OUT</sub> = 150 mA <sup>(2)</sup>                                                         | 0.0  | 0.4  | 0.9  | V    |

| V                 | Load regulation                | I <sub>O</sub> = -1 mA to -100 mA <sup>(1)</sup>                                                 | 0    | 10   | 40   | mV   |

| V <sub>OLO</sub>  | Load regulation                | $I_O = -1 \text{ mA to } -150 \text{ mA}^{(2)}$                                                  | 0    | 10   | 40   | mV   |

|                   | Current limit                  | $0.8 \text{ V} < \text{V}_{\text{O1}} < 4.5 \text{ V}; \text{ V}_{\text{S}} = 6 \text{ V}^{(1)}$ | -180 | -400 | -800 | mA   |

| I <sub>LIM</sub>  | Current mint                   | $0.8 \text{ V} < \text{V}_{\text{O1}} < 4.5 \text{ V}^{(2)}$                                     | -180 | -400 | -800 | mA   |

| V <sub>OLI</sub>  | Line regulation                | 6 V < V <sub>S</sub> < 28 V; I <sub>OUT</sub> = - 5 mA                                           | 0    | 5    | 30   | mV   |

| T <sub>OVT</sub>  | Overtemp flag                  | 6 V < V <sub>S</sub> < 28 V                                                                      | 130  | 140  | 150  | °C   |

| T <sub>OTKL</sub> | Thermal shutdown               | 6 V < V <sub>S</sub> < 28 V                                                                      | 150  | 165  | 180  | °C   |

| Vtrc              | V <sub>2</sub> tracking offset | 6 V < V <sub>S</sub> < 28 V; I <sub>O2</sub> = 0                                                 | -90  | 0    | +90  | mV   |

<sup>1.</sup> Valid for SO-20 package

Table 8. Reset and watchdog

| Symbol               | Parameter                                     | Test conditions                      | Min. | Min. Typ. Max.   |      |                  |  |  |

|----------------------|-----------------------------------------------|--------------------------------------|------|------------------|------|------------------|--|--|

| t <sub>OSC</sub>     | OnChip RC-timebase                            | Normal, RXonly,<br>standby3 ("1MHz") | 0.95 | μs               |      |                  |  |  |

| t <sub>OSCslow</sub> | RC-Adjustment = 0                             | Sleep2, standby2<br>("250KHz")       | 4.0  | 5.4              | 6.8  | μs               |  |  |

|                      | Wetchdog timehood (2.5 mg)                    | Normal, RXonly,<br>standby3 ("1MHz") |      | 2498             |      | tosc             |  |  |

| t <sub>WDC</sub>     | Watchdog timebase (2.5 ms)                    | Sleep2, standby2<br>("250KHz")       |      | 624              |      |                  |  |  |

| t <sub>RDnom</sub>   | Reset pulse duration (1 ms)                   |                                      |      | 1024             | tosc |                  |  |  |

| t <sub>WDstart</sub> | Reset pulse pause (320 ms) (startup watchdog) |                                      |      | 128              |      |                  |  |  |

|                      |                                               | SWT = 0 (2.5 ms)                     | 1    |                  |      | t <sub>WDC</sub> |  |  |

|                      | Watchdog window start                         | SWT = 1 (5 ms)                       | 2    |                  |      | t <sub>WDC</sub> |  |  |

| t <sub>WDswS</sub>   | (Software window watchdog)                    | SWT = 2 (10 ms)                      | 4    |                  |      | t <sub>WDC</sub> |  |  |

|                      |                                               | SWT = 3 (20 ms)                      | 8    |                  |      | t <sub>WDC</sub> |  |  |

|                      |                                               | SWT = 0 (5 ms)                       | 2    |                  |      | t <sub>WDC</sub> |  |  |

| t                    | Watchdog window end                           | SWT = 1 (10 ms)                      | 4    |                  |      | t <sub>WDC</sub> |  |  |

| <sup>t</sup> WDswE   | (Software window watchdog)                    | SWT = 2 (20 ms)                      | 8    |                  |      | t <sub>WDC</sub> |  |  |

|                      |                                               | SWT = 3 (40 ms)                      |      | t <sub>WDC</sub> |      |                  |  |  |

<sup>2.</sup> Valid for PowerSO-20 package

Table 8. Reset and watchdog (continued)

| Symbol             | Parameter                            | Test conditions                                      | Min.       | Тур. | Max. | Unit             |  |

|--------------------|--------------------------------------|------------------------------------------------------|------------|------|------|------------------|--|

|                    |                                      | WDT = 0 (80 ms)                                      |            | 32   |      |                  |  |

|                    |                                      | WDT = 1 (160 ms)                                     |            | 64   |      | t <sub>WDC</sub> |  |

| t <sub>WD1C</sub>  | System watchdog 1                    | WDT = 2 (320 ms)                                     |            | 128  |      | t <sub>WDC</sub> |  |

|                    |                                      | WDT = 3 (640 ms)                                     |            | 256  |      | t <sub>WDC</sub> |  |

|                    |                                      | WDT = 4 (800 ms)                                     |            | 320  |      |                  |  |

|                    |                                      | WDT = 8 (1 s)                                        | 400        |      |      | t <sub>WDC</sub> |  |

|                    |                                      | WDT = 9 (2 s)                                        | 784        |      |      | t <sub>WDC</sub> |  |

| t <sub>WD2C</sub>  | System watchdog 2                    | WDT = 10 (4 s)                                       | 1600       |      |      | t <sub>WDC</sub> |  |

|                    |                                      | WDT = 11 (8 s)                                       | 3200       |      |      | t <sub>WDC</sub> |  |

|                    |                                      | WDT = 12 (45 min)                                    | 1081344    |      |      | t <sub>WDC</sub> |  |

| V                  | Reset output LOW voltage             | I <sub>RES</sub> = 500 μA;<br>V <sub>1</sub> = 2.5 V | 0          | 0.3  | 0.4  | ٧                |  |

| V <sub>RESL</sub>  | Treser output LOW Voltage            | $I_{RES} = 500 \mu A;$<br>$V_1 = 1.5 V$              | 0          | 0.85 | 1.4  | V                |  |

| R <sub>PURES</sub> | Internal reset Pull-Up<br>Resistance |                                                      | 80 120 280 |      |      | ΚΩ               |  |

Table 9. CAN Line Interface

| Symbol                                 | Parameter                                                                        | Test conditions                                   | Min.                 | Тур. | Max.           | Unit     |

|----------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------|----------------------|------|----------------|----------|

| t <sub>drd</sub>                       | Propagation delay (rec to dom state)                                             | C <sub>load</sub> = 3.3 nF                        | 0.4                  | 1.0  | 1.5            | μs       |

| t <sub>ddr</sub>                       | Propagation delay (dom to rez state)                                             | $C_{load}$ = 3.3 nF;<br>$R_{TERM}$ = 100 $\Omega$ | 0.4                  | 1.0  | 2.0            | μs       |

| S <sub>RD</sub>                        | Bus output slew rate $(r \rightarrow d)$                                         | 10% 90%;<br>C <sub>Load</sub> = 3.3 nF            | 4                    | 5    | 8              | V/µs     |

| R <sub>RTH</sub> ,<br>R <sub>RTL</sub> | External termination resistance (application limit)                              |                                                   | 0.5                  |      | 16             | ΚΩ       |

| V <sub>CCFS</sub>                      | Force Standby mode (fail safe)                                                   | Min $V_S$ to turn off CAN-IF and $V_3$            | 2.20                 |      | 4.0            | <b>V</b> |

| VH <sub>RXD</sub>                      | High level output voltage on RXD                                                 |                                                   | V <sub>1</sub> - 0.9 |      | V <sub>1</sub> | <b>V</b> |

| VL <sub>RXD</sub>                      | Low level output voltage on RXD                                                  |                                                   | 0                    |      | 0.9            | ٧        |

| Vd_r                                   | Differential receiver dom to rec threshold V <sub>CANH</sub> - V <sub>CANL</sub> | No bus failures                                   | -3.85                |      | -2.50          | V        |

| Vr_d                                   | Differential receiver rez to dom threshold V <sub>CANH</sub> - V <sub>CANL</sub> | No bus failures                                   | -3.50                |      | -2.20          | V        |

| V <sub>CANHr</sub>                     | CANH recessive output voltage                                                    | $TXD = V_1; R_{RTH} < 4 K$                        |                      |      | 0.35           | V        |

Table 9. CAN Line Interface (continued)

| Symbol             | Parameter                                                                                          | Test conditions                                                                | Min.                   | Тур. | Max. | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------|------|------|------|

| V <sub>CANHd</sub> | CANH dominant output voltage                                                                       | TXD = 0;<br>I <sub>CANH</sub> = 40 mA                                          | V <sub>3</sub> - 1.4 V |      |      | ٧    |

| V <sub>CANLr</sub> | CANL recessive output voltage                                                                      | TXD = V <sub>1</sub> ; R <sub>RTL</sub> < 4 K                                  | V <sub>3</sub> - 0.2 V |      |      | ٧    |

| V <sub>CANLd</sub> | CANL dominant output voltage                                                                       | TXD = 0;<br>I <sub>CANL</sub> = -40 mA                                         |                        |      | 1.4  | ٧    |

| I <sub>CANH</sub>  | CANH dominant output current                                                                       | TXD = 0; V <sub>CANH</sub> = 0 V                                               | 70                     | 100  | 160  | mA   |

| I <sub>CANL</sub>  | CANL dominant output current                                                                       | TXD = 0; V <sub>CANL</sub> = 14 V                                              | -70                    | -100 | -160 | mA   |

| I <sub>LCANH</sub> | CANH Sleep mode leakage current                                                                    | Sleep mode.<br>$T_j = 150$ °C;<br>$V_{CANH} = 0 V$                             | -10                    | 0    | -10  | μA   |

| I <sub>LCANL</sub> | CANL Sleep mode leakage current                                                                    | Sleep mode.<br>$T_j = 150$ °C;<br>$V_{CANL} = 0 \text{ V}; V_S = 12 \text{ V}$ | -10                    | 0    | -10  | μA   |

| V <sub>WakeH</sub> | CANH wakeup voltage                                                                                | Sleep/ standby mode                                                            | 1.2                    | 1.9  | 2.7  | V    |

| V <sub>WakeL</sub> | CANL wakeup voltage                                                                                | Sleep/ standby mode                                                            | 2.4                    | 3.1  | 3.8  | V    |

| V <sub>canhs</sub> | CANH single ended receiver threshold                                                               | Normal mode.<br>-5 V < CANL < V <sub>S</sub>                                   | 1.5                    | 1.82 | 2.15 | V    |

| V <sub>canls</sub> | CANL single ended receiver threshold                                                               | Normal mode.<br>-5 V < CANH < V <sub>S</sub>                                   | 2.7                    | 3.1  | 3.4  | V    |

| V <sub>OVH</sub>   | CANH overvoltage detection threshold                                                               | Normal mode.<br>-5 V < CANL < V <sub>S</sub>                                   | 6.5                    | 7.2  | 8.0  | V    |

| V <sub>OVL</sub>   | CANL overvoltage detection threshold                                                               | Normal mode.<br>-5 V < CANH < V <sub>S</sub>                                   | 6.5                    | 7.2  | 8.0  | ٧    |

| RT <sub>RTH</sub>  | Internal RTH to GND<br>termination resistance<br>Normal mode, no failures.                         | V <sub>RTH</sub> = 1 V                                                         | 25                     | 45   | 80   | Ω    |

| IT <sub>RTHF</sub> | Internal RTH to GND<br>termination current Normal<br>mode, failure EIII                            | V <sub>RTH</sub> = V <sub>3</sub> - 1 V                                        | 55                     | 75   | 100  | μA   |

| RT <sub>RTL</sub>  | Internal RTL to V <sub>CC</sub><br>termination resistance<br>Normal mode, no failures.             | V <sub>RTL</sub> = V <sub>3</sub> - 1 V                                        | 25                     | 45   | 85   | Ω    |

| IT <sub>RTLF</sub> | Internal RTL to V <sub>CC</sub><br>termination current Normal<br>mode. (failure EIV, EVI,<br>EVII) | V <sub>RTL</sub> = V <sub>3</sub> - 1 V                                        | -6                     | -40  | -70  | μА   |

| RT <sub>RTLS</sub> | Internal RTL to V <sub>S</sub> termination resistance. No failures.                                | Standby/sleep mode.<br>V <sub>RTL</sub> = 1 V, 4 V                             | 7                      | 13   | 26   | kΩ   |

Table 10. Digital I/O

| Symbol               | Parameter                 | Test conditions         | Min.                 | Тур.  | Max.           | Unit |

|----------------------|---------------------------|-------------------------|----------------------|-------|----------------|------|

| V <sub>SINL</sub>    | Low level input voltage   |                         | 0                    |       | 0.9            | V    |

| V <sub>SINH</sub>    | High level input voltage  |                         | V <sub>1</sub> - 0.9 |       | V <sub>1</sub> | V    |

| V <sub>SCLKL</sub>   | Low level input voltage   |                         | 0                    |       | 0.9            | V    |

| V <sub>SCLKH</sub>   | High level input voltage  |                         | V <sub>1</sub> - 0.9 |       | V <sub>1</sub> | V    |

| V <sub>TXL</sub>     | Low level input voltage   |                         | 0                    |       | 0.9            | V    |

| V <sub>TXH</sub>     | High level input voltage  |                         | V <sub>1</sub> - 0.9 |       | V <sub>1</sub> | V    |

| V <sub>WakeL</sub>   | Low level input voltage   |                         | 0                    |       | 0.9            | V    |

| V <sub>WakeH</sub>   | High level input voltage  |                         | 4.1                  |       | 5.0            | V    |

| V <sub>SoutH</sub>   | High level output voltage |                         | V <sub>1</sub> - 0.9 |       | V <sub>1</sub> | V    |

| V <sub>SoutL</sub>   | Low level output voltage  |                         | 0                    |       | 0.9            | V    |

| V <sub>RXDH</sub>    | High level output voltage |                         | V <sub>1</sub> - 0.9 |       | V <sub>1</sub> | V    |

| V <sub>RXDL</sub>    | Low level output voltage  |                         | 0                    |       | 0.9            | V    |

| Ioh <sub>RXD</sub>   | High level output current | RXD = 0                 | -2.5                 | -1.8  | -0.9           | mA   |

| Iol <sub>RXD</sub>   | Low level output current  | RXD = 5 V               | 0.9                  | 1.6   | 2.5            | mA   |

| Ioh <sub>SOUT</sub>  | High level output current | SOUT = 0                | -18.0                | -14.0 | -7.0           | mA   |

| Iol <sub>SOUT</sub>  | Low level output current  | SOUT = 5 V              | 15                   | 24    | 35             | mA   |

| Ioh <sub>INT</sub>   | High level output current | INT = 0                 | -20                  | -15   | -8             | mA   |

| Iol <sub>INT</sub>   | Low level output current  | INT = 5 V               | 15                   | 24    | 35             | mA   |

| Ioh <sub>Reset</sub> | High level output current | RESET = 0               | -25.0                | -15,0 | -6.0           | μΑ   |

| Iol <sub>Reset</sub> | Low level output current  | RESET = 5 V             | 5.0                  | 7.5   | 10.0           | mA   |

| Ioh <sub>Wake</sub>  | High level output current | V <sub>Wake</sub> = 5 V | -1.5                 | 0     | 1.5            | μΑ   |

| Iol <sub>Wake</sub>  | Low level output current  | V <sub>Wake</sub> = 0 V | -4.5                 | -3.4  | -2.0           | μΑ   |

Table 11. Serial data interface

| Symbol             | Parameter                                    | Test conditions        | Min. | Тур. | Max. | Unit |

|--------------------|----------------------------------------------|------------------------|------|------|------|------|

| t <sub>Start</sub> | SIN low to SCLK low setup time (frame start) |                        | 100  |      |      | ns   |

| t <sub>Setup</sub> | SIN to SCLK setup time (write)               | Setup time (write) 100 |      |      |      |      |

| t <sub>Hold</sub>  | SIN to SCLK hold time (write)                |                        | 100  |      |      | ns   |

| t <sub>D</sub>     | SCLK to SOUT delay time (read)               |                        |      |      | 500  | ns   |

| t <sub>CKmax</sub> | SCLK maximum cycle time (timeout)            |                        | 1    | 1.5  | 3.0  | ms   |

| t <sub>GAP</sub>   | Interframe gap                               |                        | 5    |      |      | μs   |

| f <sub>SCLK</sub>  | SCLK frequency range                         |                        | 0.25 | 0.5  | 1    | MHz  |

Table 12. Diagnostic functions

| Symbol             | Parameter                            | Test conditions | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------------|-----------------|------|------|------|------|

| VS <sub>min</sub>  | Sense comparator detection threshold |                 | 6.0  | 7.2  | 8,0  | V    |

| GS <sub>CANH</sub> | CANH groundshift detection threshold |                 | -1.5 | -1   | -0.6 | V    |

Table 13. CAN error detection

| Symbol              | Parameter                                                         | Test conditions                | Min.        | Тур. | Min. Typ. Max. |       |  |

|---------------------|-------------------------------------------------------------------|--------------------------------|-------------|------|----------------|-------|--|

| N <sub>EdgeH</sub>  | Nr of dom to rec edges on<br>CANL to detect permanent<br>rez CANH | Operating mode (EI_V)          |             | 3    |                |       |  |

| N <sub>EdgeHR</sub> | Nr of dom to rec edges to detect recovery of CANH                 | Operating mode (EI_V)          |             | 3    |                | Edges |  |

| N <sub>EdgeL</sub>  | Nr of dom to rec edges on<br>CANH to detect permanent<br>rez CANL | Operating mode (EII_IX)        |             | 3    |                | Edges |  |

| N <sub>EdgeLR</sub> | Nr of dom to rec edges to detect recovery of CANL                 | Operating mode (EII_IX)        |             | 3    |                | Edges |  |

| t                   | CANH to V <sub>S</sub> short circuit                              | Operating mode (EIII)          | 1.6         | 2    | 3.6            | ms    |  |

| t <sub>EIII</sub>   | detection time                                                    | Sleep/ standby mode (EIII)     | 1.6         | 2    | 3.6            | ms    |  |

| teme                | CANH to V <sub>S</sub> short circuit                              | Operating mode (EIII)          | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EIIIR</sub>  | recovery time                                                     | Sleep/ standby mode (EIII)     | 0.4         | 0.9  | 1.6            | ms    |  |

| t                   | CANL to GND short circuit                                         | Operating mode (EIV)           | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EIV</sub>    | detection time                                                    | Sleep/ standby mode (EIV)      | 0.4         | 0.9  | 1.6            | ms    |  |

| t                   | CANL to GND short circuit                                         | Operating mode (EIV)           | 10          | 30   | 50             | μs    |  |

| t <sub>EIVR</sub>   | recovery time                                                     | Sleep/ standby mode (EIV)      | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EVI</sub>    | CANL to V <sub>S</sub> short circuit detection time               | Operating mode (EVI)           | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EVIR</sub>   | CANL to V <sub>S</sub> short circuit recovery time                | Operating mode (EVI)           | 200         | 500  | 750            | μs    |  |

| t <sub>EVII</sub>   | CANL to CANH short circuit detection time                         | Operating mode (EVII)          | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EVIIR</sub>  | CANL to CANH short circuit recovery time                          | Operating mode (EVII)          | 10          | 30   | 50             | μs    |  |

|                     | CANH to VDD short circuit                                         | Operating mode (EVIII)         | 1.6         | 1.8  | 3.6            | ms    |  |

| t <sub>EVIII</sub>  | detection time                                                    | Sleep/ standby mode<br>(EVIII) | 1.6 1.8 3.6 |      | ms             |       |  |

|                     | CANH to VDD short circuit                                         | Operating mode (EVIII)         | 0.4         | 0.9  | 1.6            | ms    |  |

| t <sub>EVIIIR</sub> | recovery time                                                     | Sleep/ standby mode<br>(EVIII) | 0.4         | 0.9  | 1.6            | ms    |  |

Table 13. CAN error detection (continued)

| Symbol               | Parameter                                        | Test conditions     | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------|---------------------|------|------|------|------|

| t <sub>FailTX</sub>  | TX permanent dominant detection time (Fail safe) | Operating mode (EX) | 0.4  | 0.9  | 1.6  | ms   |

| t <sub>FailTXR</sub> | TX permanent dominant recovery time (Fail safe)  | Operating mode (EX) | 1    | 4    | 8    | μs   |

## Table 14. Wakeup

| Symbol             | Parameter                                          | Test conditions | Min. | Тур. | Max. | Unit |

|--------------------|----------------------------------------------------|-----------------|------|------|------|------|

| t <sub>wuCAN</sub> | Minimum dominant time for wake-up via CANH or CANL | Sleep/standby   | 8    | 22   | 38   | μs   |

| t <sub>wuWK</sub>  | Minimum pulse time for wake-<br>up via WAKE        | Sleep/standby   | 8    | 22   | 38   | μs   |

# 3 Functional description

#### 3.1 General features

The L4969UR is a monolithic integrated circuit which provides all main functions for an automotive body CAN network.

It features two independent regulated voltage supplies  $V_1$  and  $V_2$ , an interrupt and reset logic with internal clock generator, Serial Interface and a low speed CAN-bus transceiver which is supplied by a separate third voltage regulator ( $V_3$ ).

The device guarantees a clearly defined behavior in case of failure, to avoid permanent CAN bus errors.

The device operates in four basic modes, with additional programming for V<sub>1</sub> Standby modes in CTCR:

Table 15. Operating mode description

| Mode                      | V1  | V2  | V3  | Timer/WDC   | CAN-IF  | I <sub>typ</sub> | LP1, LP0<br>(CTCR) | Remarks                                                                              |

|---------------------------|-----|-----|-----|-------------|---------|------------------|--------------------|--------------------------------------------------------------------------------------|

| Sleep #1                  | Off | Off | Off | Off         | Standby | 40µ              | x,x                | No Timer based wakeup                                                                |

| Sleep #2                  | Off | Off | Off | On (250Khz) | Standby | 80µ              | x,x                | Timer active based on t <sub>OSCslow</sub>                                           |

| Standby #1 <sup>(1)</sup> | On  | Off | Off | Off         | Standby | 170µ             | 1,1                | No Watchdog or Timer                                                                 |

| Standby #2 <sup>(1)</sup> | On  | Off | Off | On (250KHz) | Standby | 210μ             | 1,0                | Watchdog or timer active based on tooscolow                                          |

| Standby #3                | On  | Off | Off | On (1MHz)   | Standby | 440µ             | 0,0                | Watchdog or timer activ, POR default                                                 |

| RXOnly                    | Off | Off | On  | On (1MHz)   | RX-Only | 4mA              | x,x                | Active during Busactivity to filter ID, auto- matic fall back to Sleep when Bus idle |

| Normal                    | On  | On  | On  | On (1MHz)   | Normal  | 5mA              | x,x                | No Currents from CAN or Regulators                                                   |

Note, that in order to enter either Standby #1 or Standby #2 the Startup-Watchdog has to be acknowledged, in Standby #1, the Window Watchdog has to be disabled as described in Chapter 2.5, to allow the decativation of the internal oscillator.

## 3.1.1 V<sub>1</sub> output voltage

The  $V_1$  regulator uses a DMOS transistor as an output stage. With this structure very low dropout voltage is obtained. The dropout operation of the standby regulator is maintained down to 4 V input supply voltage. The output voltage is regulated up to the transient input supply voltage of 40 V. With this feature no functional interruption due to overvoltage pulses is generated. The output 1 regulator is switched off in sleep mode.

#### 3.1.2 V<sub>2</sub> output voltage

The  $V_2$  regulator uses the same output structure as the output 1 regulator except to being short circuit proof to  $V_S$ . The  $V_2$  output can be switched on and off through a dedicated enable bit in the control register. In addition a tracking option can be enabled to allow  $V_2$  follow  $V_1$  with constant offset. This feature allows consistent A/D conversion inside the microcontroller (supplied by  $V_1$ ) when the converted signals are referenced to  $V_2$ . The maximum voltage that can be applied to  $V_2$  is  $V_S + 0.3$  V up to a max  $V_S$  of 40 V.

## 3.1.3 V<sub>3</sub> output voltage

The third voltage regulator of the device generates the supply voltage for the internal logic and the CAN-transceiver. In operating mode it is capable of supplying up to 200 mA in order to guarantee the required short circuit current for the CAN\_H driver. The sleep and operating modes are switched through a dedicated enable bit.

#### 3.1.4 Internal supply voltage

A low power sleep mode regulator supplies the internal logic in sleep mode.

# 3.2 Power-up, initialization and sleep mode transitions

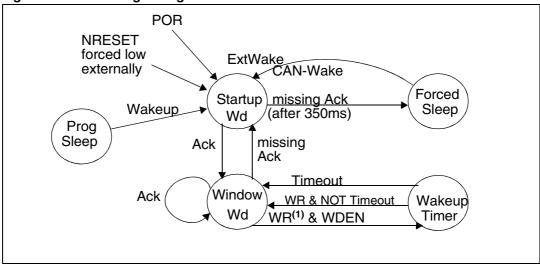

The following state-diagram illustrates the possible mode transitions inside the device.

As a prerequisite, an SPI-connection to the microcontroller with the correct CRC-algorythms is required.

During the debug phase the NRES line can be forced high externally (connect to  $V_1$ ) to deactivate the startup failure mechanism and keeping  $V_1$  alive.

The forced sleep mode is left upon wake-up through either CAN or edge on WAKE. Applying a permanent wake-up (i.e. both CAN-lines dominant) pre-After POR, V1 up or externally forced reset through low NRES, the STARTUP STATE is vents V1 from being turned off (can be used during System debugging) V1 Low Forcing NRES high externally, fail will not be incremented (Emulation) NRES Low STARTUP **STARTUP** t=320ms **FORCED SLEEP FAILURE WAKEUP** fail = 7 V1 active RESET low V1 off V2, V3, CAN off t=1ms No Reset (fail ++) If no WDC-ACK is received within A missing ACK within 320ms will **WDC-ACK** seven retrials the voltage regulator V1 will be turned off by entering the initiate a STARTUP FAILURE phase (RESET low). WDC-ACK FORCED SLEEP state **WDC-FAIL** WDEN SET Depending on the value from the last WDC-ACK, another one has to be The Window supervision can temporarily be deactivated for the time programmed during the written within the specified time frame Writing to the WDC-(SWDC[1:0]). A failure will activate the STARTUP STATE last WDC-ACK (WDT[3:0]). Upon rewriting register (WDC-ACK) the NORMAL STATE is (WDC-ACK) or expiry of the timer, the NORMAL STATE is reentered. entered. WDC-ACK **TIMER** NORMAL MODE **WINDOW** WDEN SET t=t<sub>WIN2</sub> **ACTIVE** WINDOW WDC WATCHDOG (restart by double WDC-OK **ACTIVE REFRESH** WDC-ACK & WDEN), WND SET TIMEOUT | (WDC-ACK & NOT TIMEOUT<sup>(1)</sup>) (1) Rewriting of the WDC register when the timer just expires can lead to an unwanted window watchdog failure resulting in a low pulse on RESET (see note on section 4.5.4) DISAR **SET** If during the last WDC-ACK WND has been set (after releasing write lock, see description of Watchdog Control Register) the Win-Here the timer can be used to generate time events (i.e. dow watchdog is deactivated, and no uC supervision is active wake-up uC from stop) **TIMER WDEN SET** NORMAL MODE ACTIVE WINDOW WDC (restart by double WDC-ACK & WDEN) TIMEOUT | WDC-ACK DISABLED DISAR WAKEUP SET Setting DISAR (see Voltage Regulator Control Register) Voltage regulator V1 is **Programmed** turned off, and the output voltage is decreasing depending on the external load FFP and blocking capacitor. V1 OFF Note, that during this transition no Reset will be generated (due to Debug mode). **WAKEUP** No Reset Upon wake-up however NRES will be pulled low, if V1was below the programma-&V1 UV ble reset threshold (V1\_UV). WAKEUP&V1\_UV

Figure 3. State diagram

#### 3.3 CAN transceiver

- Supports double wire unshielded busses

- Baud rate up to 125 KBaud

- Short circuit protection (battery, ground, wires shorted)

- Single wire operation possible (automatic switching to single wire upon bus failures)

- Bus not loaded in case of unpowered transceiver

The CAN transceiver stage is able to transfer serial data on two independent communication wires either deferentially (normal operation) or in case of a single wire fault on the remaining line. The physical bitcoding is done using dominant (transmitter active) and overwritable

recessive states. Too long dominant phases are detected internally and further transmission is automatically disabled (malfunction of protocol unit does not affect communication on the bus, "fail-safe" - mechanism). For low current consumption during bus inactivity a sleep mode is available. The operating mode can be entered from the sleep mode either by local wake up (microcontroller) or upon detection of a dominant bit on the CAN-bus (external wake up).

Ten different errors on the physical buslines can be distinguished:

Table 16. Detectable physical busline failures

| N    | Type of errors                                                             | Conditions                                                       |  |  |  |  |  |

|------|----------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| Erro | rs caused by damage of the datalines or isolation                          |                                                                  |  |  |  |  |  |

| I    | CANH wire interrupted (tied to Ground or termination)                      | Edgecount difference > 3                                         |  |  |  |  |  |

| II   | CANL wire interrupted (floating or tied terminationk)                      | Edgecount difference > 3                                         |  |  |  |  |  |

| Ш    | CANH short circuit to V <sub>BAT</sub> (overvoltage condition)             | V(CANH) > 7.2 V after 3.6 ms                                     |  |  |  |  |  |

| IV   | CANL short circuit to GND (permanently dominant)                           | V(CANL) < 3.1 V &<br>V(CANH)-V(CANL) > -3.25 V<br>after 1.6 ms   |  |  |  |  |  |

| ٧    | CANH short circuit to GND (permanently recessive)                          | Edgecount difference > 3                                         |  |  |  |  |  |

| VI   | CANL short circuit to V <sub>BAT</sub> (overvoltage condition)             | V(CANL) > 7.2 V after 1.6 ms                                     |  |  |  |  |  |

| VII  | CANL shorted to CANH                                                       | V(CANH) - V(CANL) < -3.25 V<br>after 1.6 ms                      |  |  |  |  |  |

| Erro | rs caused by misbehavior of transceiver stage                              |                                                                  |  |  |  |  |  |

| VIII | CANH short circuit to VDD (permanently dominant)                           | V(CANH) > 1.8 V &<br>V(CANH) - V(CANL) > -3.25 V<br>after 3.2 ms |  |  |  |  |  |

| IX   | CANL short circuit to VDD (permanently recessive) Edgecount difference > 3 |                                                                  |  |  |  |  |  |

| Erro | Errors caused by defective protocol unit                                   |                                                                  |  |  |  |  |  |

| Χ    | CANH, CANL driven dominant for more than 1.6 ms                            |                                                                  |  |  |  |  |  |

Note: Not all of the 10 different errors lead to a breakdown of the whole communication. So the errors can be categorized into 'negligible', 'problematic' and 'severe':

#### 3.3.1 Negligible errors

#### Transmitter

- Error I and II (CANH or CANL interrupted but still tied to termination)

- Error IV and VIII (CANH or CANL permanently dominant by short circuit)

In all cases above data can still be transmitted in differential mode.

#### Receiver

- Error I and II (CANH or CANL interrupted but still tied to termination).

- Error V and IX (CANH or CANL permanently recessive by short circuit).

In all cases above data can still be received in differential mode.

#### 3.3.2 Problematic errors

#### Transmitter

Error III and VI (CANH or CANL show overvoltage condition by short circuit).

Data is transmitted using the remaining dataline (single wire).

#### Receiver

Error III and VI (CANH or CANL show overvoltage condition by short circuit).

Data is received using the remaining dataline (single wire).

#### 3.3.3 Severe errors

#### Transmitter

- Error V and IX (CANH or CANL permanently recessive by short circuit).

Data is transmitted on the remaining dataline after short circuit detection.

- Error VII (CANH is shorted to CANL).

Data is transmitted on CANH or CANL after overcurrent was detected.

- Error X (attempt to transmit more than 10 successive dominant bits (at lowest bitrate specified).

Transmission is terminated (fail safe).

#### Receiver

- Error VII (CANH is shorted to CANL).

Data is received on CANH or CANL after detection of permanent dominant state.

- Error IV and VIII (CANH or CANL permanently dominant by short circuit).

Data is received on CANH or CANL after short circuit was detected.

- Error X (reception of a sequence of dominant bits, violating the protocol rules).

Data is received normally, error is detected by protocol-unit.

The error conditions is signaled issuing an error flag inside a dedicated register which is readable by the microcontroller through the serial interface. The information of the error type (I through X) is also stored into this register.

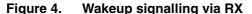

#### 3.3.4 Wakeup via CAN

When the CAN transceiver is in standby mode special low power comparators detect activity on CANH and / or CANL. This information is filtered and can be defined as a wakeup condition for the voltage regulator and the application via the 'WKC' flag in the IFR register as a maskable interrupt through NINT or via RX.

The wakeup signalling via RX is described in the following diagram:

After detecting a dominant level on either CANH or CANL for longer than the wakeup filter time ( $t_{wuCAN}$ ), RX goes low for one  $t_{OSC}$  cycle. This is repeated cyclically every  $t_{wuREP}$  until CANx returns to a recessive state or CANx is considered as shorted to a dominant value.

Note, that the duration of the extended cycle  $t_{wuREP}$  equals  $t_{wuCAN}$  when the oscillator is in 1 MHz mode (Standby3, RXOnly and Normal mode, see *Table 15*).

If the device uses the low power oscillator (250 KHz) in either Sleep2 or Standby2

$t_{\text{wuREP}} = 4.2 \text{ x } t_{\text{wuCAN}}.$

#### 3.4 Oscillator

A low power oscillator provides an internal clock, that can be calibrated in a range from -16% to +16% via the RCADJ register using the  $\mu$ C-XTAL as a reference.

In the operating modes Sleep2 and Standby2 (Watchdog / timer active) the output frequency is  $\sim$ 250 kHz (1/ $t_{OSCslow}$ ), if the Watchdog function is not requested, the internal Oscillator is switched off.

In the operating modes Normal, RXonly and Standby3 the oscillator is running at ~1 MHz (1/  $t_{OSC}$ ).

## 3.5 Watchdog

A triple function programmable watchdog is integrated to perform the following tasks:

- Wakeup watchdog:

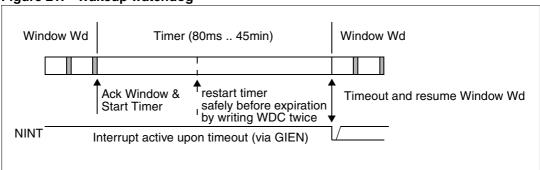

- When in sleep or standby mode the watchdog can generate a wakeup condition after a programmable period of time ranging from 80 ms up to 45 minutes

- Startup watchdog:

- Upon  $V_1$  power-up or microcontroller failure during SPI supervision a reset pulse is generated periodically every 320 ms for 2.5 ms until activity of the microcontroller is detected (SPI sequence) or no acknowledge is received within 7 cycles (2.2 sec). In this condition the device is forced into Sleep mode until a Wakeup is detected and a startup cycle is reinitialized.

- Window watchdog:

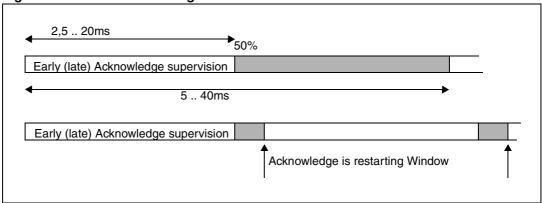

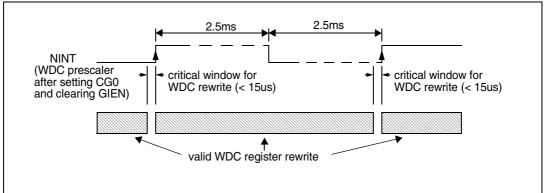

- After passing the startup sequence, this watchdog request an acknowledge by the microcontroller via the SPI within a programmable timing frame, ranging from 2.5 ... 5 ms up to 20 ... 40 ms. Upon a missing or misplaced acknowledge the Startup Watchdog is initialized.

#### 3.6 Reset

## 3.6.1 Power-on reset

Upon Power-on ( $V_S > 3.5 \text{ V}$ ), the internal reset forces the device into a predefined power-On state (see *Section 3.1: General features*):

Standby #3:  $V_1$  on  $V_2$  off  $V_3$  off, CAN-Standby mode, ID-Filter disabled, startup watchdog active.

With  $V_S$  below 5 V the regulator  $V_1$  will follow  $V_S$  with minimum drop. The microcontroller retrieves a reset if  $V_1$  is dropping below a programmable voltage level of either 4.5V (default) or 4.0 V. The programmed state of the L4969UR remains unchanged. The act. low Reset pulse duration is fixed internally by an open-drain output stage to 1 ms. However, this time can be externally extended by an additional capacitance connect between NRESET and GROUND which is then charged by the internal pull-up of typical 120 K. Depending on the Reset-Input-Threshold of the microcontroller ( $U_{TR}$ ), the required Capacitance for a typical  $t_D$  can be calculated as follows:

$$C_{EXT} = -t_D / (120E3 \ln(1-U_{TR}/V_1)).$$

To obtain a reset-pulse duration of  $t_D = 50$  ms with  $U_{TR}/V_1 = 0.5$ , a capacitance of

$C_{EXT}$ = -50E-3 / (120E3 In 0.5) = 600 nF is required

#### 3.6.2 Undervoltage reset

Upon detection of a  $V_1$  voltage level below a programmable voltage level of either 4.5 V (default) or 4.0 V, the NRES-pin is pulled low. Since this undervoltage detection is additionally sampled periodically every ms, the NRES low time will be extended by up to 1 ms if  $V_1$  was low ( $V_{1,IJV}$ ) at the sampling point (see *Figure 6*).

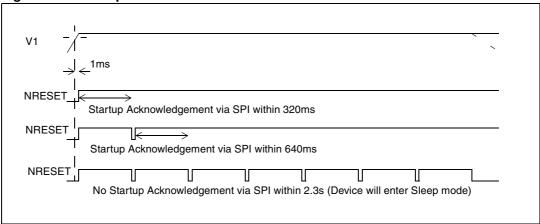

Figure 6. NRES timings

#### 3.6.3 Reset signalling during sleepmode

When entering the sleep mode by writing 1 to DISAR in the VRCR register, the Voltage regulators and their references will be deactivated to allow minimum current consumption. By removing the  $V_1$  reference, the output voltage is no longer supervised and thus NO reset will be generated.

Now two scenarios are possible (see Figure 3: State diagram):

- 1) Wakeup with  $V_1$  still above reset threshold:  $V_1$  will be reactivated and Normal mode is resumed

- 2) Wakeup with  $V_1$  below reset threshold:  $V_1$  will be activated, NRES will go low and remain low until  $V_1$  is above reset threshold and startup mode is entered.

The scenario 2 is the most critical when used with microcontroller that do not have their own POR circuitry.

In this case V<sub>1</sub> will ramp down with an unknown application state.

To guarantee a proper shut off of a microcontroller without an internal POR circuitry the following mechanism can be utilized: the L4969UR uses a bidirectional reset to detect a possible watchdog failure of the microcontroller. If this failure condition is detected, NRES will be forced low for 1 ms (with activated timer) or until a wakeup condition occurs (WDEN bit in WDC register reset, thus RC-oscillator will be switched off during sleep).

Two methods can be used to allow a proper sleep transition:

- With Timer (WDEN = 1): immediately after setting DISAR the microcontroller has to program its WDC to generate a failure causing the L4969UR to detect a low level on NRES followed by an automatic 1 ms pulse extension. If V<sub>1</sub> is ramping down slow, Cext has to be defined in a way, that NRES will stay below the input threshold of the microcontroller until V<sub>1</sub> is in a safe level.

- Without timer (WDEN = 0): same procedure as above, but microcontroller has to generate a Reset within 1 ms after WDEN has been cleared. NRES will then stay low, until a wakeup condition occurs.

Figure 7. Internal circuitry and suggested C<sub>EXT</sub> for NRES generation during sleep mode

#### 3.7 Identifier filter

A 12-Bit CAN-ID-filter is implemented allowing wakeup via specific CAN-messages thus aiding the implementation of low power partial communication networks like standby diagnostics without the need to power-up the whole network.

To guarantee the detection of the programmed Identifiers, the local RC-oscillator can be calibrated to allow the programmable Bittime logic to extract the incoming stream with a maximum of tolerance over temperature deviation.

## 3.8 Ground shift detection

In case of single wire communication via CANH the signal to noise ratio is low. Detecting the local ground shift can be used as an additional indicator on the current signal quality. The

information of the integrated ground shift detector will be refreshed upon every falling edge on TX and can be read from the CAN Transceiver Status Register (CTSR).

It will be set, if V(CANH) < -1 V, reset if V(CANH > -1 V) at the falling edge of TX.

## 3.9 Thermal protection

The device features three independent thermal warning circuits which monitor the temperature of the  $V_1$  output, the  $V_2$  output and the CAN\_H and CAN\_L drivers together with voltage regulator  $V_3$ . Each circuit sets a separate overtemperature flag in a register which is read and writable by the serial interface. The overtemperature flags cause an interrupt to the microcontroller. The microcontroller is able to switch  $V_1$ ,  $V_2$  and CAN drivers on and off through dedicated enable registers. To enhance system security the following strategy is chosen for thermal warning and shutdown:

- 3 independent warning flags are set at 140°C for V<sub>1</sub>, V<sub>2</sub> and V<sub>3</sub>/CAN-Transceiver

- at 170°C V<sub>2</sub> and V<sub>3</sub> switched off

- at 200°C V<sub>1</sub> is switched off

- V<sub>2</sub> and V<sub>3</sub> can be switched on again through the microcontroller

- V<sub>1</sub> can be switched on again at wake-up (watchdog wake-up, CAN wake-up, external wake-up)

Note, that if no wakeup source is set for V<sub>1</sub> the external WAKE pin and the CAN interface will be activated to allow a proper retry cycle.

## 3.10 Serial Interface (SPI)

A standard serial peripheral interface (SPI) is implemented to allow access to the internal registers of the L4969UR.

A total of 12 registers with different datalengths can be directly read from or written to, providing the requested address at the beginning of a dataframe. Upon every access to this interface, the content of the register currently accessed is shifted out via SOUT. All operations are performed on the rising edge of SCLK.

If a frame is not completed, the interface is automatically reset after 1.5 ms of SCLK idle time (auto timeout detection). If a message is corrupted (additional or missing SCLK pulses), the application software can detect this by evaluating the returned value of the CRC and force a communication gap of min 1.5 ms to allow communication recovery. A corruption can be caused during startup of the microcontroller and SPI initialization. The application should then wait at least 1.5 ms after SPI init prior to starting the communication.

The dataframe format used is described on Section 3.10.1: General dataframe format.

#### 3.10.1 General dataframe format

Figure 8. General dataframe format

Data is sampled on the rising edge of the clock and SOUT will change upon SCLK falling. SOUT will show a copy of SIN for the Address/Command field for initial data path checks. Independently of the command state, SOUT will show the content of the register addressed. SIN contains either data to be written or arbitrary data for all other operations. The transaction will be terminated with four bit of data followed by a 4-Bit wide CRC (Cyclic Redundancy Check) as a result of either SIN related data or calculated automatically on data returned via SOUT. Here the microcontroller has to provide the correct sequence in order to get the write command activated inside. A CRC-failure is signalled via NINT. For returned data the CRC can also be used to verify a successful transfer.

Note:

The information in data field 1 is copied from the adressed register into the SPI shift register at the last rising SCLK edge of the address/command field. A clear or write operation on the addressed register takes place after the last (24th) rising SCLK edge of the telegram if the CRC check passes.

As a consequence any Read/Clear or Write SPI command can remove the information from the addressed register that was set after the register content has been copied into the shift register for reading.

This has to be considered especially in interrupt service routines processing Wakeup Watchdog restarts that need to be synchronized with the 'WKW' flag inside the IFR register.

#### 3.10.2 Address/command field

Figure 9. Address / command field

The Address/command field starts with a 2-Bit start sequence consisting of '01'. Any other sequence will lead to a protocol error signalled via the NINT. The address field is specifying the register to be accessed. The SPI command flags allow in addition to the normal read/write operation to clear the Interrupt flag register after read.

#### 3.10.3 Datafield #1

Figure 10. Datafield #1

Datafield #1 contains either the lower 8 bits of a 12-bit frame or the complete byte of an 8-bit transfer.

Note, that SOUT is always showing the content of the register currently accessed and not a copy of SIN as during the address/command field.

#### 3.10.4 Datafield #2/CRC

Figure 11. Datafield #2 / CRC

Datafield #2 contains either the upper four bits of a 12-bit frame or zeros in case of an 8-bit transfer. This field is followed by a four bit CRC sequence that is calculated based upon the polynom 0x11h (17 decimal). This sequence is simply the remainder of a polynomial division performed on the data previously transferred. If the CRC appended to the SIN sequence fails, any writing will be disabled and an error is signalled via NINT. Another remainder is calculated on the SOUT stream and appended accordingly to allow the application software to validate the correctness of incoming data. To aid evaluation, the CRC checking can be turned off by writing arbitrary data with a valid CRC to address 15. CRC-checking will be reenabled upon another operation of this kind (Toggled information).

## 3.11 Memory map

Table 17. L4969UR memory map

| ADR | Group | MSB                       | D10      | D9     | D8   | D7                           | D6    | D5   | D4   | D3   | D2   | D1   | D0    |

|-----|-------|---------------------------|----------|--------|------|------------------------------|-------|------|------|------|------|------|-------|

| 0   | VRCR  |                           |          |        |      | EUV3                         | EUV2  | RTC0 | TRC  | RES  | ENV3 | ENV2 | DISAR |

| 1   | CTCR  |                           |          |        |      | ACT                          | TXEN  | RES  | RES  | OVR  | LP2  | LP1  | LP0   |

| 2   | GPTR  | Undefined                 |          |        | RES  | RES                          | RES   | RES  | TM1  | TM0  | TMUX | TEN  |       |

| 3   | RCADJ |                           | Register | Memory |      | CG1                          | CG0   | PGEN | SIGN | ADJ3 | ADJ2 | ADJ1 | ADJ0  |

| 4   | WDC   |                           |          |        |      | WDEN                         | WND   | SWT1 | SWT0 | WDT3 | WDT2 | WDT1 | WDT0  |

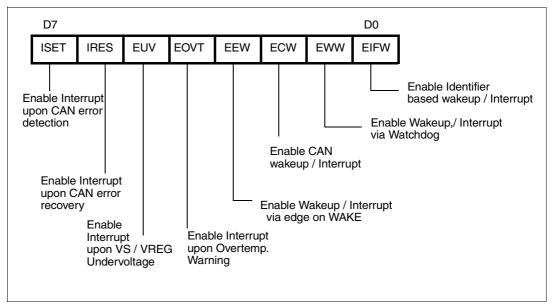

| 5   | GIEN  |                           |          |        | ISET | IRES                         | EUV   | EOVT | EEW  | ECW  | EWW  | EIFW |       |

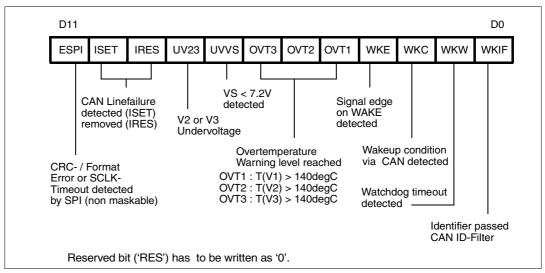

| 6   | IFR   | ESPI                      | ISET     | IRES   | UV23 | UVVS                         | OVT3  | OVT2 | OVT1 | WKE  | WKC  | WKW  | WKIF  |

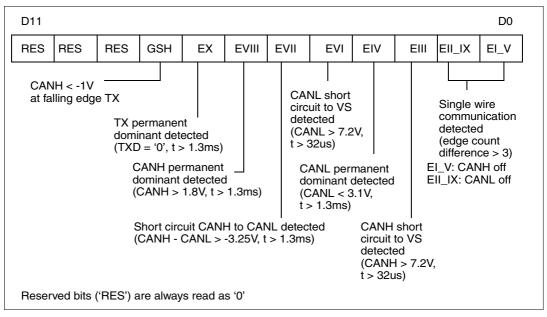

| 7   | CTSR  | RES                       | RES      | RES    | GSH  | EX                           | EVIII | EVII | EVI  | EIV  | EIII | EII  | E     |

| 8   | ID01  | A11                       | A10      | A01    | A00  | B11                          | B10   | B01  | B00  | C11  | C10  | C01  | C00   |

| 9   | ID23  | D11                       | D10      | D01    | D00  | E11                          | E10   | E01  | E00  | F11  | F10  | F01  | F00   |

| 10  | BTL   | PS23 PS22 PS21 PS20       |          |        | PS20 | PS13                         | PS12  | PS11 | PS10 | TD3  | TD2  | TD1  | TD0   |

| 11  | NAV   |                           |          |        |      |                              |       |      |      |      |      |      |       |

| 12  | NAV   |                           |          |        |      | Undefined<br>Register Memory |       |      |      |      |      |      |       |

| 13  | NAV   |                           |          |        |      |                              |       |      |      |      |      |      |       |

| 14  | TEST  | T11                       | T10      | T09    | T08  | T07                          | T06   | T05  | T04  | T03  | T02  | T01  | T00   |

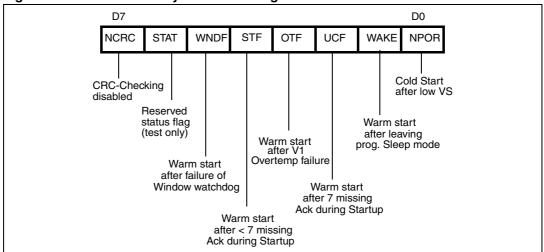

| 15  | SYS   | Undefined Register Memory |          |        |      | NCRC                         | STAT  | WNDF | STF  | OTF  | UCF  | WAKE | NPOR  |

The memory space is divided up into 16 different registers each being directly accessible using the SPI.

Each register contains specific information of a functional group.

In general all reserved bitpositions ('RES') have to be written with '0'.

Undefined bits are read as '0' and cannot be overwritten.

In addition there is one register (CTSR) being read only, thus any write attempt will leave the register content unchanged.

Certain interlock mechanisms exist to prevent unwanted overwriting of important functions i.e. voltage regulators or oscillator adjustments. These mechanisms are described with the functions of these registers.

# 4 Control and status registers

The functionality of the device can be observed and controlled through a set of registers which are read and writable by the serial interface.

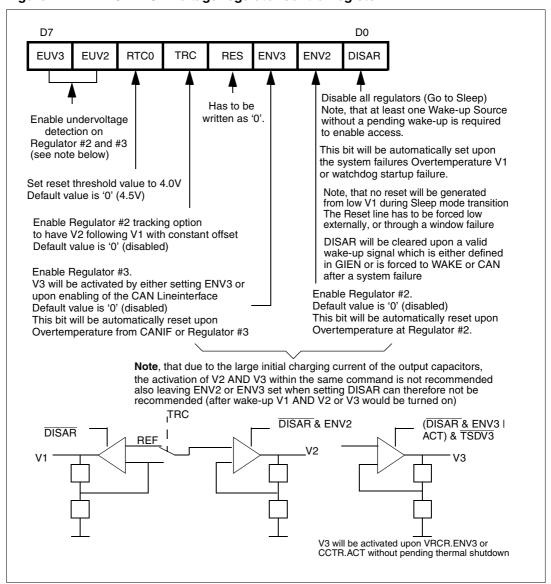

## 4.1 ADR 0: VRCR voltage regulator control register