# 128/64 SEGMENT LCD DRIVER

#### **LCD Driver**

- Controls up to 128 segments (48-pin packages) or 64 segments (32-pin package)

- Supports static, 2-mux, 3-mux, and 4-mux displays

- On-chip bias generation with internal charge pump

- · Low power blink capability

#### **GPIO Expander**

- Expands GPIO count by up to 36 pins (48-pin packages) or 20 pins (32-pin package)

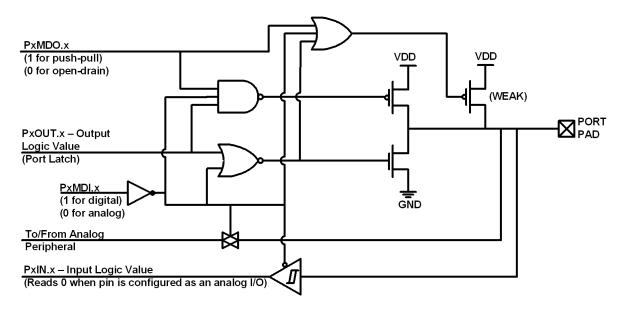

- GPIO pins may be configured to push-pull or open-drain outputs with two drive levels. GPIO may also be used as digital inputs (CP2400/1/2/3 pullups included)

- Port Match Capability can wake up host controller using interrupt pin

- 5 V Tolerant I/O

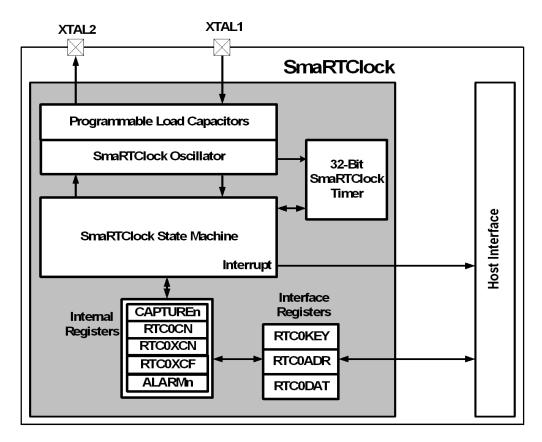

#### Real Time Clock, SmaRTClock

- Precision time keeping with 32.768 kHz watch crystal; self-oscillate mode requires no external crystal; accepts external 32 kHz CMOS clock

- 36-hour programmable counter with wake up alarm

- Can wake up the host controller using interrupt pin

- Low power (<1.5 μA)

#### 256 Bytes RAM

General purpose RAM expands the memory available to host controller.

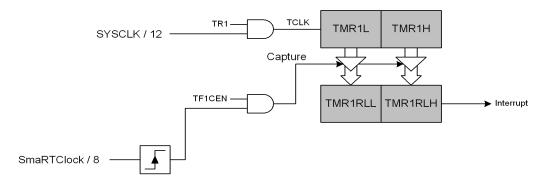

#### 16-bit Timers

• Two general purpose 16-bit timers

#### **Clock Sources**

- 20 MHz Internal oscillator

- Can be clocked from an external CMOS clock

#### **Digital Bus Interface**

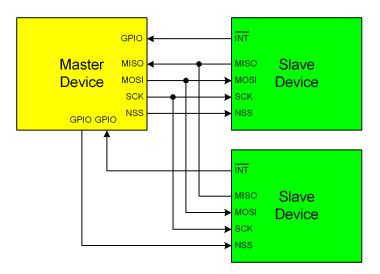

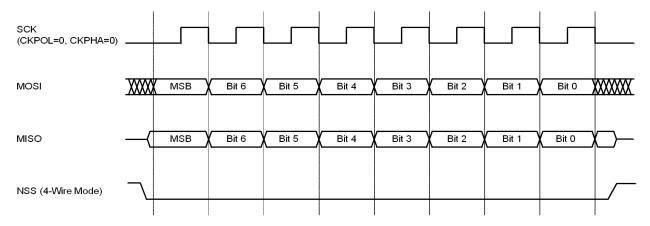

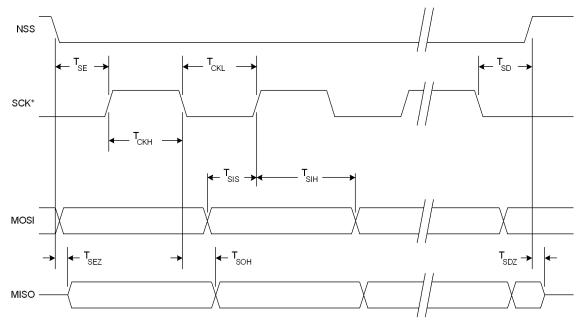

- 4-wire SPI Interface operates up to 2.5 Mbps with synchronous external clock or up to 1 Mbps with internal clock (CP2400/2 only).

- 2-wire SMBus/I<sup>2</sup>C Interface operates up to 400 kHz with internal clock (CP2401/3 only).

- Dedicated RST and INT pins.

- Optional CLK pin can be used as a CMOS clock input.

- Optional PWR pin (SMBus/I<sup>2</sup>C devices only) places the device in a low power mode. SPI devices use the NSS pin to place the device in a low power mode.

#### **Low Power**

- 1.8–3.6 V operation with integrated LDO

- Ultra Low Power Mode w/ LCD (<3 µA typical)</li>

- Shutdown current (0.05 µA typical)

#### **Example Applications**

- Handheld Equipment

- Utility Meters

- Thermostat Display

- Home Security Systems

#### **Packages**

- Pb-free 48-pin QFP (9x9 mm footprint) [-Q]

- Pb-free 48-pin QFN (7x7 mm footprint) [-M]

- Pb-free 32-pin QFN (5x5 mm footprint)

#### **Ordering Part Numbers**

- CP2400-G[M|Q] (SPI Interface)

- CP2401-G[M|Q] (SMBus/I<sup>2</sup>C Interface)

- CP2402-GM (SPI Interface)

- CP2403-GM (SMBus/I<sup>2</sup>C Interface)

### Temperature Range: -40 to +85 °C

2

# TABLE OF CONTENTS

| <u>Se</u> | <u>ection</u>                                                      | <u>Page</u> |

|-----------|--------------------------------------------------------------------|-------------|

| 1.        | System Overview                                                    |             |

|           | 1.1. Typical Connection Diagram                                    |             |

|           | Absolute Maximum Ratings                                           |             |

|           | Electrical Characteristics                                         |             |

|           | Pinout and Package Definitions                                     |             |

| 5.        | Clocking Options                                                   | 32          |

| 6.        | Internal Registers and Memory                                      |             |

|           | 6.1. Accessing Internal Registers and RAM over the SPI Interface   |             |

|           | 6.2. Accessing Internal Registers and RAM over the SMBus Interface |             |

|           | 6.3. Internal Registers                                            |             |

|           | Interrupt Sources                                                  |             |

| 8.        | Reset Sources                                                      |             |

|           | 8.1. Reset Initialization                                          |             |

|           | 8.2. Power-On Reset                                                |             |

|           | 8.3. External Pin Reset                                            |             |

| 9.        | Power Modes                                                        |             |

|           | 9.1. Normal Mode                                                   |             |

|           | 9.2. RAM Preservation Mode                                         |             |

|           | 9.3. Ultra Low Power LCD Mode                                      |             |

|           | 9.4. Ultra Low Power SmaRTClock Mode                               |             |

|           | 9.5. Shutdown Mode                                                 |             |

|           | 9.6. Determining the ULP Mode Wake-Up Source                       |             |

|           | 9.7. Port Match Functionality in the Ultra Low Power Modes         |             |

|           | 9.8. Disabling Secondary Device Functions                          |             |

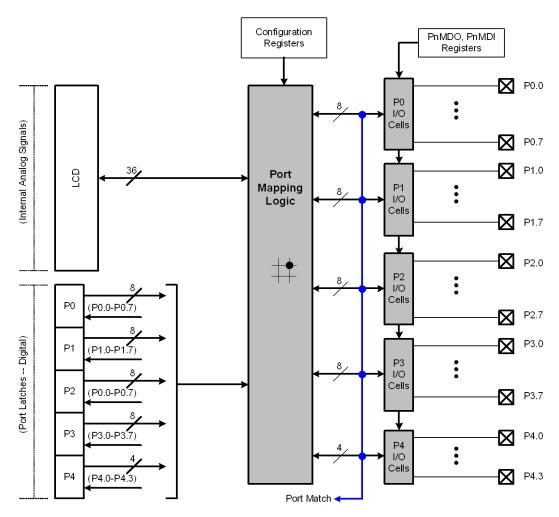

| 10        | Port Input/Output                                                  |             |

|           | 10.1.Port I/O Modes of Operation                                   |             |

|           | 10.2.Assigning Port I/O Pins to Analog and Digital Functions       |             |

|           | 10.3.Active Mode Port Match                                        |             |

|           | 10.4.Registers for Accessing and Configuring Port I/O              |             |

| 11        | .SmaRTClock (Real Time Clock)                                      |             |

|           | 11.1.SmaRTClock Interface                                          |             |

|           | 11.2.SmaRTClock Clocking Sources                                   |             |

|           | 11.3.SmaRTClock Timer and Alarm Function                           | 77          |

| 12        | LCD Segment Driver                                                 |             |

|           | 12.1.Initializing the LCD Segment Driver                           |             |

|           | 12.2.LCD Configuration                                             |             |

|           | 12.3.LCD Bias Generation and Contrast Adjustment                   |             |

|           | 12.4.LCD Timing Generation                                         |             |

|           | 12.5.Mapping ULP Memory to LCD Pins                                |             |

|           | 12.6.Blinking LCD Segments                                         |             |

| 13        | c. Timers                                                          | 92          |

# CP2400/1/2/3

| 13.1.Timer 0                          | 92  |

|---------------------------------------|-----|

| 13.2.Timer 1                          | 96  |

| 14. Serial Peripheral Interface (SPI) |     |

| 14.1.Signal Descriptions              |     |

| 14.2.Serial Clock Timing              |     |

| 15.SMBus Interface                    |     |

| 15.1.Supporting Documents             | 104 |

| 15.2.SMBus Configuration              |     |

| 15.3.SMBus Operation                  |     |

| Document Change List                  |     |

|                                       |     |

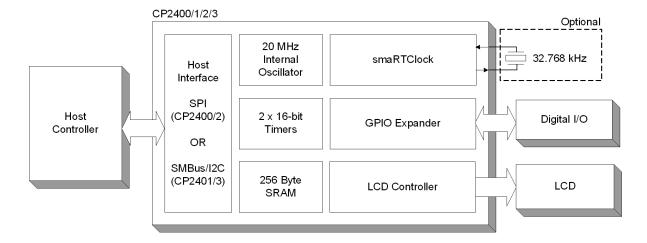

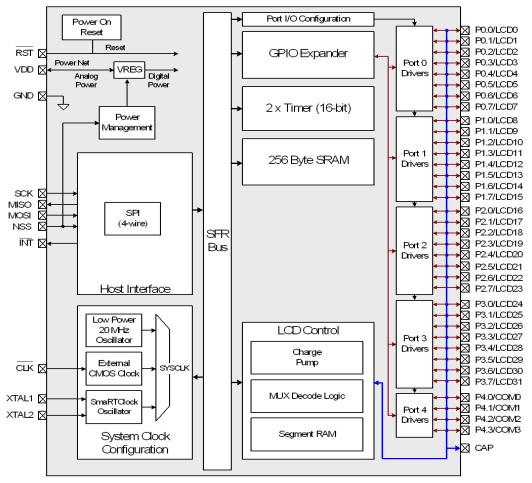

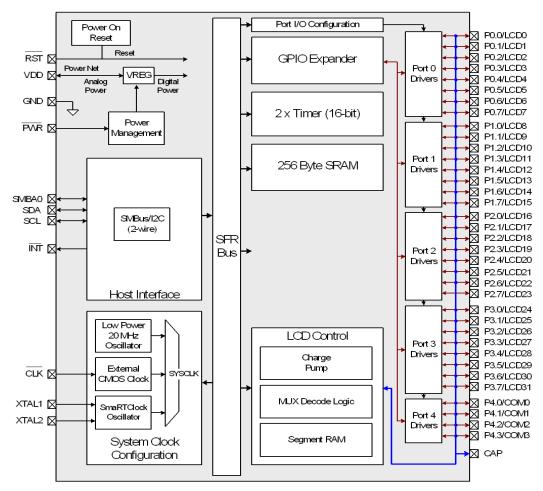

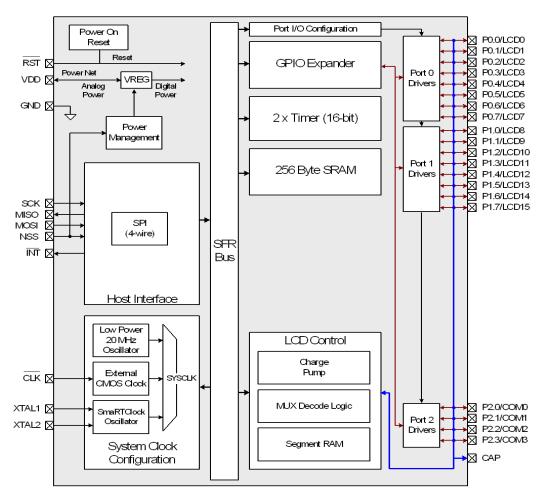

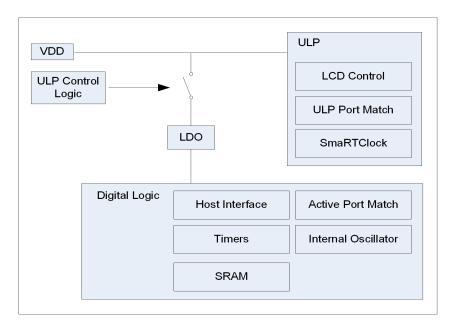

# 1. System Overview

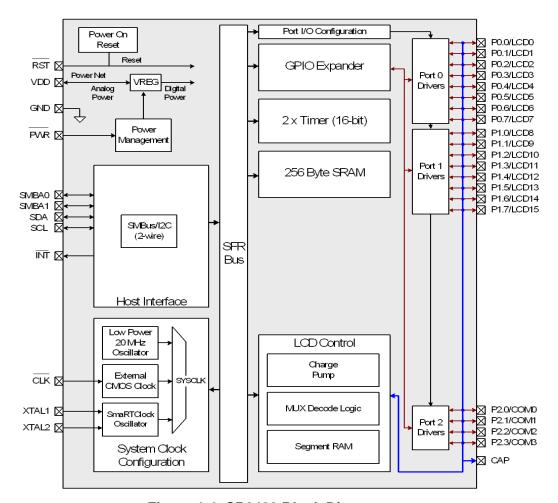

CP2400/1/2/3 devices are fixed function LCD drivers that can also be used for expanding GPIO, timekeeping, and increasing available system RAM by up to 256 bytes. The device is controlled using direct and indirect internal registers accessible through the 4-wire SPI or 2-wire SMBus interface. All digital pins on the device are 5 V tolerant.

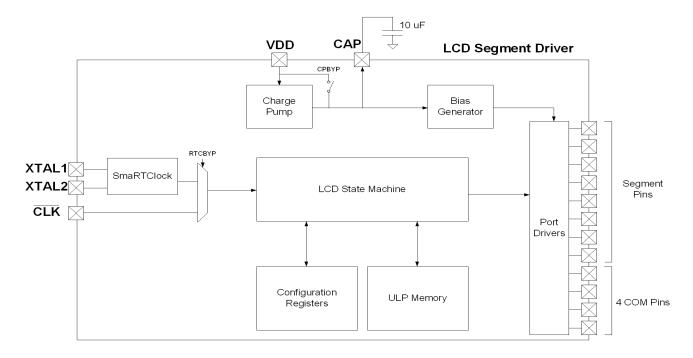

Figure 1.1. CP2400 Block Diagram

Figure 1.2. CP2401 Block Diagram

Rev. 1.0

6

Figure 1.3. CP2402 Block Diagram

Figure 1.4. CP2403 Block Diagram

Rev. 1.0

8

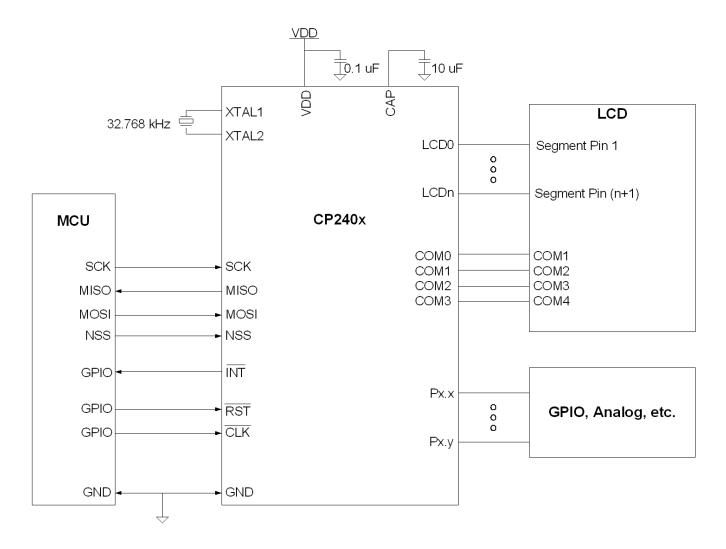

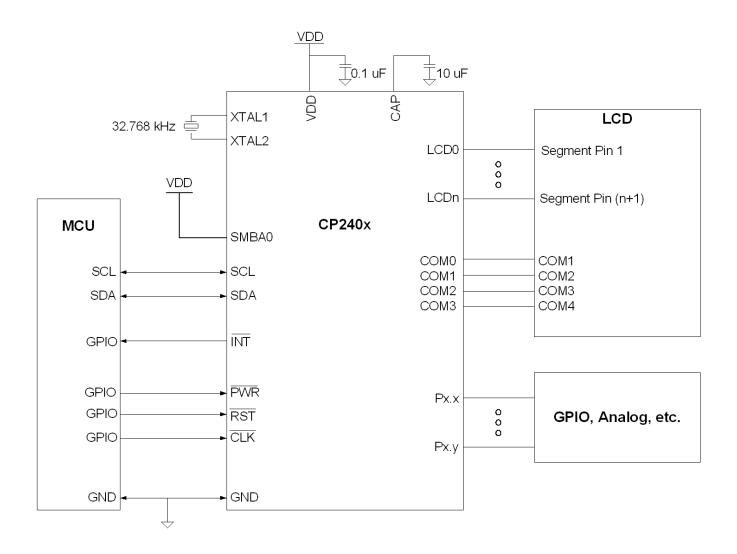

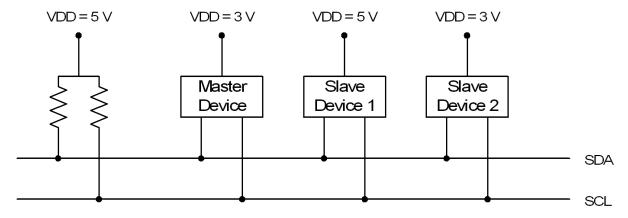

# 1.1. Typical Connection Diagram

**Figure 1.5. Typical Connection Diagram (SPI Interface)**

Figure 1.6. Typical Connection Diagram (SMBus/I<sup>2</sup>C Interface)

# 2. Absolute Maximum Ratings

**Table 2.1. Absolute Maximum Ratings**

| Parameter                                             | Conditions                                         | Min         | Тур | Max                          | Units |

|-------------------------------------------------------|----------------------------------------------------|-------------|-----|------------------------------|-------|

| Ambient temperature under bias                        |                                                    | <i>–</i> 55 | _   | 125                          | °C    |

| Storage Temperature                                   |                                                    | -65         | _   | 150                          | °C    |

| Voltage on any I/O Pin or RST with respect to GND     | V <sub>DD</sub> > 2.2 V<br>V <sub>DD</sub> < 2.2 V | -0.3        | _   | 5.8<br>V <sub>DD</sub> + 3.6 | V     |

| Voltage on V <sub>DD</sub> with respect to GND        |                                                    | -0.3        | _   | 4.2                          | V     |

| Maximum Total current through V <sub>DD</sub> and GND |                                                    | _           | _   | 500                          | mA    |

| Maximum output current sunk by RST or any I/O pin     |                                                    | _           | _   | 100                          | mA    |

**Note:** Stresses above those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the devices at or exceeding the conditions in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 3. Electrical Characteristics

**Table 3.1. Global Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85  $^{\circ}C$  unless otherwise specified.

| Parameter                                                                                                                                  | Conditions                                                                 | Min              | Тур                      | Max           | Units |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|--------------------------|---------------|-------|

| Supply Voltage                                                                                                                             |                                                                            | 1.8              | 3.3                      | 3.6           | V     |

| SYSCLK                                                                                                                                     |                                                                            | 0                | _                        | 25            | MHz   |

| T <sub>SYSH</sub> (SYSCLK High Time)                                                                                                       |                                                                            | 18               | _                        | _             | ns    |

| T <sub>SYSL</sub> (SYSCLK Low Time)                                                                                                        |                                                                            | 18               | _                        | _             | ns    |

| Specified Operating Temperature Range                                                                                                      |                                                                            | -40              | _                        | +85           | °C    |

| Normal Mode Supply Current (V <sub>DD</sub> = 3.0 V, 25                                                                                    | °C unless otherwise s                                                      | pecified)        |                          |               |       |

| 20 MHz Internal Oscillator divided by 1,<br>SYSCLK = 20 MHz, SPI data rate = 1 Mbps*                                                       | $V_{DD} = 3.6 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ $V_{DD} = 1.8 \text{ V}$ |                  | 740<br>700<br>630        | 790<br>—<br>— | μА    |

| Accessing RAM at 1 Mbps                                                                                                                    |                                                                            | _                | 740                      | _             | μA    |

| SYSCLK = 10 MHz, SPI data rate <sup>*</sup> = 500 kbps                                                                                     |                                                                            |                  | 380                      | _             | μA    |

| SYSCLK = 5 MHz, SPI data rate <sup>*</sup> = 250 kbps                                                                                      |                                                                            | _                | 230                      | _             | μA    |

| SYSCLK = 2.5 MHz, SPI data rate <sup>*</sup> = 125 kbps                                                                                    |                                                                            | _                | 150                      | _             | μA    |

| RAM Preservation Mode Supply Current (V <sub>DD</sub>                                                                                      | = 3.0 V, 25 °C unless o                                                    | therwise         | specified)               | )             |       |

| 32.768 kHz SmaRTClock Selected as the<br>System Clock, Internal Oscillator Disabled                                                        |                                                                            | _                | 20                       | _             | μΑ    |

| Ultra Low Power LCD Mode Supply Current (V                                                                                                 | / <sub>DD</sub> = 3.0 V, 25 °C unles                                       | s otherwi        | ise specif               | ied)          |       |

| LCD Enabled with Charge Pump Enabled,<br>60 Hz Refresh Rate, No Load<br>SmaRTClock with 32.768 kHz crystal                                 | 4-Mux mode<br>3-Mux mode<br>2-Mux mode<br>static mode                      | _<br>_<br>_<br>_ | 2.3<br>2.3<br>2.2<br>2.1 | _<br>_<br>_   | μΑ    |

| LCD Enabled with Charge Pump Enabled,<br>60 Hz Refresh Rate, No Load<br>SmaRTClock in Self-Oscillate Mode (AGC<br>Enabled, LOADCAP = 0x0F) | 4-Mux mode<br>3-Mux mode<br>2-Mux mode<br>static mode                      | _<br>_<br>_<br>_ | 1.7<br>1.7<br>1.7<br>1.5 | _<br>_<br>_   | μА    |

| Ultra Low Power SmaRTClock Mode Supply C                                                                                                   | urrent (V <sub>DD</sub> = 3.0 V, 25                                        | °C unles         | s otherwis               | se specific   | ed)   |

| External Crystal (RTC Timer Enabled)                                                                                                       | Fosc = 32.768 kHz                                                          | _                | 2.5                      | _             | μA    |

| CMOS Clock Input on XTAL1 and XTAL2 Pins (RTC Timer Enabled)                                                                               | Fosc = 32.768 kHz                                                          | _                | 2.3                      | _             | μA    |

| Self-Oscillate Mode (AGC enabled,<br>LOADCAP = 0x0F) (RTC Timer Enabled)                                                                   | Fosc = 14 kHz                                                              | _                | 2.0                      | _             | μA    |

| Shutdown Mode ( $V_{DD}$ = 3.0 V, 25 °C unless oth                                                                                         | erwise specified)                                                          |                  |                          |               |       |

| Shutdown (no clocks active, regulator disabled)                                                                                            | $V_{DD} = 3.6 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ $V_{DD} = 1.8 \text{ V}$ |                  | 0.030<br>0.020<br>0.015  |               | μA    |

| *Note: Indicates maximum allowed SPI data rate in th                                                                                       | is mode. Power measuren                                                    | nent taken v     | with no SPI              | traffic.      |       |

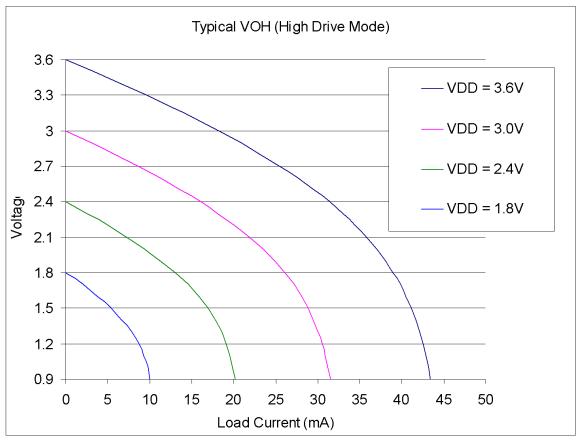

Table 3.2. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters          | Conditions                                                        | Min                   | Тур       | Max                   | Units |

|---------------------|-------------------------------------------------------------------|-----------------------|-----------|-----------------------|-------|

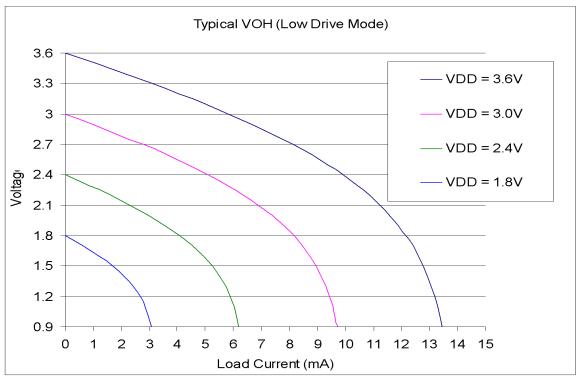

| Output High Voltage | High Drive Strength, PnDRV.n = 1                                  |                       |           |                       |       |

|                     | $I_{OH} = -3$ mA, Port I/O push-pull                              | V <sub>DD</sub> – 0.7 | _         | _                     |       |

|                     | $I_{OH} = -10 \mu A$ , Port I/O push-pull                         | V <sub>DD</sub> – 0.1 | _         | _                     |       |

|                     | $I_{OH} = -10$ mA, Port I/O push-pull                             | _                     | See Chart | _                     |       |

|                     | Low Drive Strength, PnDRV.n = 0                                   |                       |           |                       | V     |

|                     | I <sub>OH</sub> = -1 mA, Port I/O push-pull                       | V <sub>DD</sub> – 0.7 | _         | _                     |       |

|                     | $I_{OH} = -10 \mu A$ , Port I/O push-pull                         | V <sub>DD</sub> – 0.1 | _         | _                     |       |

|                     | I <sub>OH</sub> = -3 mA, Port I/O push-pull                       | _                     | See Chart | _                     |       |

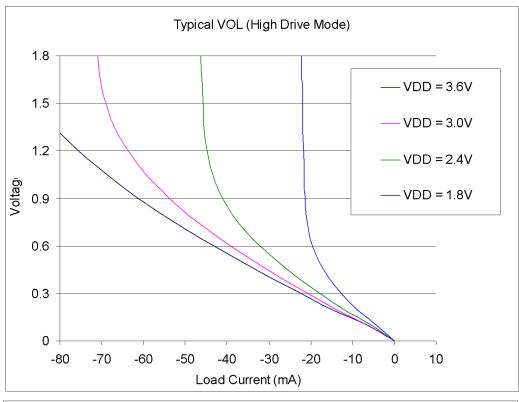

| Output Low Voltage  | High Drive Strength, PnDRV.n = 1                                  |                       |           |                       |       |

|                     | $I_{OL} = 8.5 \text{ mA}$                                         | _                     | _         | 0.6                   |       |

|                     | I <sub>OL</sub> = 10 μA                                           | _                     | _         | 0.1                   |       |

|                     | I <sub>OL</sub> = 15 mA                                           | _                     | See Chart | _                     |       |

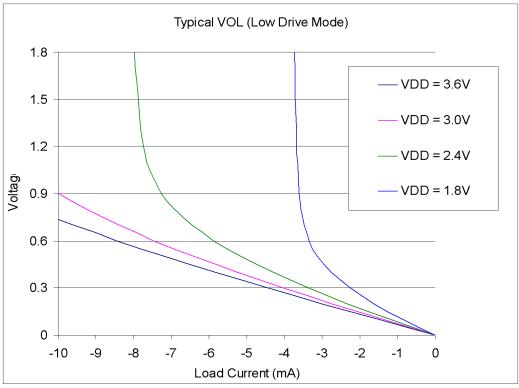

|                     | Low Drive Strength, PnDRV.n = 0                                   |                       |           |                       | V     |

|                     | $I_{OL} = 1.4 \text{ mA}$                                         | _                     | _         | 0.6                   |       |

|                     | I <sub>OL</sub> = 10 μA                                           | _                     | _         | 0.1                   |       |

|                     | I <sub>OL</sub> = 4 mA                                            | _                     | See Chart | _                     |       |

| Input High Voltage  | V <sub>DD</sub> = 2.0 to 3.6 V                                    | V <sub>DD</sub> – 0.6 | _         | _                     | V     |

|                     | V <sub>DD</sub> = 1.8 to 2.0 V                                    | 0.7 x V <sub>DD</sub> | _         | _                     | V     |

| Input Low Voltage   | V <sub>DD</sub> = 2.0 to 3.6 V                                    | _                     | _         | 0.6                   | V     |

|                     | V <sub>DD</sub> = 1.8 to 2.0 V                                    | _                     | _         | 0.3 x V <sub>DD</sub> | V     |

| Input Leakage       | Weak Pullup On, $V_{IN} = 0 \text{ V}$ , $V_{DD} = 1.8 \text{ V}$ | _                     | 4         | _                     |       |

| Current             | Weak Pullup On, Vin = 0 V, $V_{DD}$ = 3.6 V                       |                       | 20        | 30                    | μΑ    |

Figure 3.1. Typical VOH

Figure 3.2. Typical VOL

# **Table 3.3. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters                                                                                             | Conditions                                                                 | Min                   | Тур                | Max                   | UNITS |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------|--------------------|-----------------------|-------|

| RST Input High Voltage                                                                                 |                                                                            | 0.7 x V <sub>DD</sub> | _                  | _                     | V     |

| RST Input Low Voltage                                                                                  |                                                                            | _                     | _                  | 0.3 x V <sub>DD</sub> | V     |

| RST Input Pullup Current                                                                               |                                                                            |                       | 4<br>20            | <br>30                | μA    |

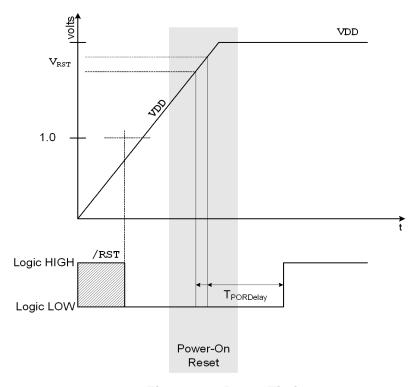

| V <sub>DD</sub> Ramp Time for Power On <sup>1</sup>                                                    | V <sub>DD</sub> Ramp from 0–1.8 V                                          | _                     | _                  | 1                     | ms    |

| Power on Reset Delay (T <sub>PORDelay</sub> ) from Start of Ramp until the Reset Complete Interrupt    | $V_{DD} = 1.8 \text{ V}$ $V_{DD} = 3.0 \text{ V}$ $V_{DD} = 3.6 \text{ V}$ |                       | 1200<br>660<br>575 | 900<br>—              | μs    |

| Required RST Low Time to guarantee a System Reset (T <sub>RST</sub> )                                  | See Note 2                                                                 | 15                    | _                  | _                     | μs    |

| Startup Delay from Reset De-<br>asserted until the Reset Complete<br>Interrupt (T <sub>STARTUP</sub> ) | Pin Reset                                                                  | _                     | 90                 | 100                   | μs    |

#### Notes:

- 1. There is no restriction on VDD ramp time if the  $\overline{RST}$  pin is toggled at the end of the ramp.

- 2. If the RST pin is held low for a shorter time period, a device reset may occur.

# **Table 3.4. Power Management Electrical Specifications**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                             | Conditions                                              | Min    | Тур | Max    | Units         |

|---------------------------------------|---------------------------------------------------------|--------|-----|--------|---------------|

| RAM Preservation Mode Wake-Up<br>Time | From the falling edge of CLK until host interface ready |        | 10  |        | ns            |

|                                       | Port Match or SmaRTClock Wakeup<br>NSS/PWR Pin Wakeup   | 3<br>7 |     | 4<br>8 | RTC<br>Cycles |

## **Table 3.5. Internal Oscillator Electrical Characteristics**

$V_{DD} = 1.8$  to 3.6 V;  $T_{\Delta} = -40$  to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                         | Conditions                                    | Min | Тур | Max | Units |

|---------------------------------------------------|-----------------------------------------------|-----|-----|-----|-------|

| Oscillator Frequency                              | –40 to +85 °C,<br>V <sub>DD</sub> = 1.8–3.6 V | 15  | 20  | 25  | MHz   |

| Oscillator Supply Current (from V <sub>DD</sub> ) | 25 °C                                         | _   | 50  | _   | μA    |

# **Table 3.6. LCD Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified.

| Parameter                        | Conditions | Min | Тур | Max | Units |

|----------------------------------|------------|-----|-----|-----|-------|

| Charge Pump Output Voltage Error |            | _   | ±30 | _   | mV    |

# 4. Pinout and Package Definitions

Table 1. CP2400/1/2/3 Pin Definitions

| Name         |     | Pin Nu           | ımbers |                  | Туре           | Description                                                                                                                                    |

|--------------|-----|------------------|--------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 48- | pin              | 32-    | pin              |                |                                                                                                                                                |

|              | SPI | I <sup>2</sup> C | SPI    | I <sup>2</sup> C |                |                                                                                                                                                |

| XTAL1        | 1   | 1                | 1      | 1                | A In           | Crystal Input. This pin is the return for the external oscillator driver. This pin can be overdriven by an external CMOS clock.                |

| XTAL2        | 2   | 2                | 2      | 2                | A Out          | Crystal Output. This pin is the excitation driver for a quartz crystal.                                                                        |

| $V_{DD}$     | 3   | 3                | 3      | 3                | Power In       | 1.8–3.6 V Power Supply Voltage Input.                                                                                                          |

| GND          | 4   | 4                | 4      | 4                |                | Ground                                                                                                                                         |

| CAP          | 48  | 48               | 32     | 32               | Power<br>Out   | LCD Power Supply Voltage Output. This pin requires a 10 μF decoupling capacitor.                                                               |

| CLK          | 47  | 47               | 31     | 31               | D In           | CMOS clock input. This pin should not be left floating.                                                                                        |

| RST          | 46  | 46               | 30     | 30               | D In           | Device Reset. An external source can initiate a system reset by driving this pin low for at least 15 µs. This pin has an internal weak pullup. |

| ĪNT          | 45  | 45               | 29     | 29               | D Out          | Interrupt Service Request. This pin provides notification to the host. This pin is a push-pull output.                                         |

| NSS          | 44  | _                | 28     | _                | D In           | Slave select signal for SPI interface. This pin should not be left floating.                                                                   |

| MOSI         | 43  | _                | 27     | _                | D In           | Master Out/Slave In data signal for SPI interface. This pin should not be left floating.                                                       |

| MISO         | 42  | _                | 26     | _                | D Out          | Master In/Slave Out data signal for SPI interface                                                                                              |

| SCK          | 41  | _                | 25     | _                | D In           | Clock signal for SPI interface. This pin should not be left floating.                                                                          |

| PWR          | _   | 44               | _      | 28               | D In           | Allows SMBus device to enter the Ultra Low Power mode. This pin should not be left floating.                                                   |

| SCL          | _   | 43               | _      | 27               | D I/O          | Clock signal for SMBus interface. This pin should not be left floating.                                                                        |

| SDA          | _   | 42               | _      | 26               | D I/O          | Data signal for SMBus interface. This pin should not be left floating.                                                                         |

| SMBA0        | _   | 41               |        | 25               | D In           | Bit 0, SMBus Slave Address. This pin should not be left floating.                                                                              |

| P0.0<br>LCD0 | 40  | 40               | 24     | 24               | D I/O<br>A Out | Bit 0, Port 0                                                                                                                                  |

| P0.1<br>LCD1 | 39  | 39               | 23     | 23               | D I/O<br>A Out | Bit 1, Port 0                                                                                                                                  |

Table 1. CP2400/1/2/3 Pin Definitions (Continued)

| Name          |     | Pin Nu           | ımbers |                  | Туре           | Description   |

|---------------|-----|------------------|--------|------------------|----------------|---------------|

|               | 48- | pin              | 32-    | pin              |                |               |

|               | SPI | I <sup>2</sup> C | SPI    | I <sup>2</sup> C |                |               |

| P0.2<br>LCD2  | 38  | 38               | 22     | 22               | D I/O<br>A Out | Bit 2, Port 0 |

| P0.3<br>LCD3  | 37  | 37               | 21     | 21               | D I/O<br>A Out | Bit 3, Port 0 |

| P0.4<br>LCD4  | 36  | 36               | 20     | 20               | D I/O<br>A Out | Bit 4, Port 0 |

| P0.5<br>LCD5  | 35  | 35               | 19     | 19               | D I/O<br>A Out | Bit 5, Port 0 |

| P0.6<br>LCD6  | 34  | 34               | 18     | 18               | D I/O<br>A Out | Bit 6, Port 0 |

| P0.7<br>LCD7  | 33  | 33               | 17     | 17               | D I/O<br>A Out | Bit 7, Port 0 |

| P1.0<br>LCD8  | 32  | 32               | 16     | 16               | D I/O<br>A Out | Bit 0, Port 1 |

| P1.1<br>LCD9  | 31  | 31               | 15     | 15               | D I/O<br>A Out | Bit 1, Port 1 |

| P1.2<br>LCD10 | 30  | 30               | 14     | 14               | D I/O<br>A Out | Bit 2, Port 1 |

| P1.3<br>LCD11 | 29  | 29               | 13     | 13               | D I/O<br>A Out | Bit 3, Port 1 |

| P1.4<br>LCD12 | 28  | 28               | 12     | 12               | D I/O<br>A Out | Bit 4, Port 1 |

| P1.5<br>LCD13 | 27  | 27               | 11     | 11               | D I/O<br>A Out | Bit 5, Port 1 |

| P1.6<br>LCD14 | 26  | 26               | 10     | 10               | D I/O<br>A Out | Bit 6, Port 1 |

| P1.7<br>LCD15 | 25  | 25               | 9      | 9                | D I/O<br>A Out | Bit 7, Port 1 |

| P2.0<br>LCD16 | 24  | 24               |        |                  | D I/O<br>A Out | Bit 0, Port 2 |

| P2.1<br>LCD17 | 23  | 23               | _      | _                | D I/O<br>A Out | Bit 1, Port 2 |

Table 1. CP2400/1/2/3 Pin Definitions (Continued)

| Name          | Pin Numbers |                  |     |                  | Туре           | Description   |

|---------------|-------------|------------------|-----|------------------|----------------|---------------|

|               | 48-         | 48-pin 32-pin    |     | pin              |                |               |

|               | SPI         | I <sup>2</sup> C | SPI | I <sup>2</sup> C |                |               |

| P2.2<br>LCD18 | 22          | 22               | _   | _                | D I/O<br>A Out | Bit 2, Port 2 |

| P2.3<br>LCD19 | 21          | 21               | _   | _                | D I/O<br>A Out | Bit 3, Port 2 |

| P2.0<br>COM0  | _           | _                | 8   | 8                | D I/O<br>A Out | Bit 0, Port 2 |

| P2.1<br>COM1  | _           | _                | 7   | 7                | D I/O<br>A Out | Bit 1, Port 2 |

| P2.2<br>COM2  | _           | _                | 6   | 6                | D I/O<br>A Out | Bit 2, Port 2 |

| P2.3<br>COM3  | _           | _                | 5   | 5                | D I/O<br>A Out | Bit 3, Port 2 |

| P2.4<br>LCD20 | 20          | 20               | _   | _                | D I/O<br>A Out | Bit 4, Port 2 |

| P2.5<br>LCD21 | 19          | 19               | _   | _                | D I/O<br>A Out | Bit 5, Port 2 |

| P2.6<br>LCD22 | 18          | 18               | _   | _                | D I/O<br>A Out | Bit 6, Port 2 |

| P2.7<br>LCD23 | 17          | 17               | _   | _                | D I/O<br>A Out | Bit 7, Port 2 |

| P3.0<br>LCD24 | 16          | 16               | _   | _                | D I/O<br>A Out | Bit 0, Port 3 |

| P3.1<br>LCD25 | 15          | 15               | _   | _                | D I/O<br>A Out | Bit 1, Port 3 |

| P3.2<br>LCD26 | 14          | 14               | _   | _                | D I/O<br>A Out | Bit 2, Port 3 |

| P3.3<br>LCD27 | 13          | 13               | _   | _                | D I/O<br>A Out | Bit 3, Port 3 |

| P3.4<br>LCD28 | 12          | 12               |     |                  | D I/O<br>A Out | Bit 4, Port 3 |

| P3.5<br>LCD29 | 11          | 11               |     |                  | D I/O<br>A Out | Bit 5, Port 3 |

Table 1. CP2400/1/2/3 Pin Definitions (Continued)

| Name          | Pin Numbers |                  |     |                  | Туре           | Description   |

|---------------|-------------|------------------|-----|------------------|----------------|---------------|

|               | 48-         | 48-pin           |     | pin              |                |               |

|               | SPI         | I <sup>2</sup> C | SPI | I <sup>2</sup> C |                |               |

| P3.6<br>LCD30 | 10          | 10               | _   | _                | D I/O<br>A Out | Bit 6, Port 3 |

| P3.7<br>LCD31 | 9           | 9                | _   | _                | D I/O<br>A Out | Bit 7, Port 3 |

| P4.0<br>COM0  | 8           | 8                | _   | _                | D I/O<br>A Out | Bit 0, Port 4 |

| P4.1<br>COM1  | 7           | 7                | _   | _                | D I/O<br>A Out | Bit 1, Port 4 |

| P4.2<br>COM2  | 6           | 6                | _   | _                | D I/O<br>A Out | Bit 2, Port 4 |

| P4.3<br>COM3  | 5           | 5                | _   | _                | D I/O<br>A Out | Bit 3, Port 4 |

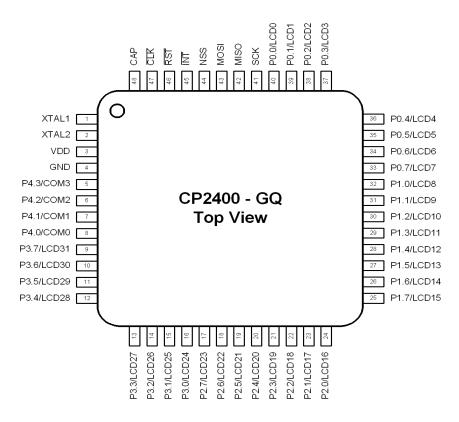

Figure 4.1. CP2400-GQ Pinout (SPI Interface)

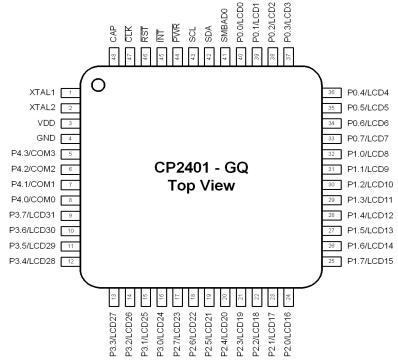

Figure 4.2. CP2401-GQ Pinout (SMBus/I<sup>2</sup>C Interface)

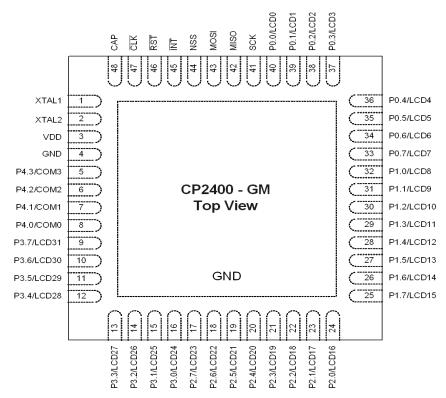

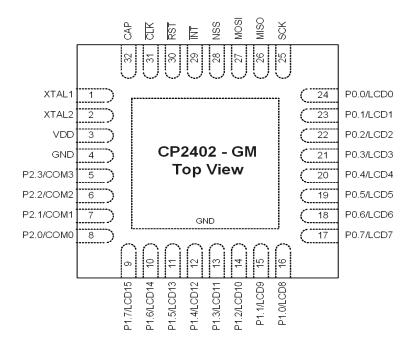

Figure 4.3. CP2400-GM Pinout (SPI Interface)

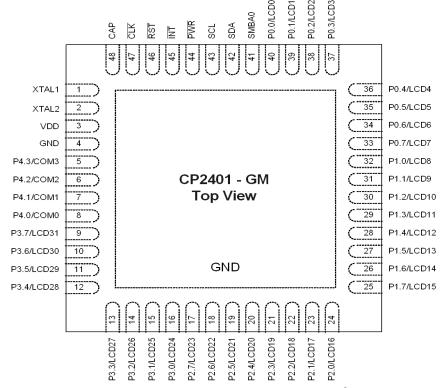

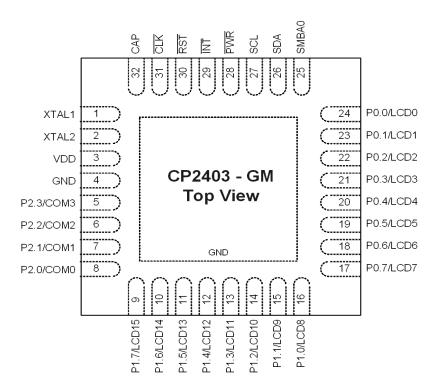

Figure 4.4. CP2401-GM Pinout (SMBus/I<sup>2</sup>C Interface)

Figure 4.5. CP2402-GM Pinout (SPI Interface)

Figure 4.6. CP2403-GM Pinout (SMBus Interface)

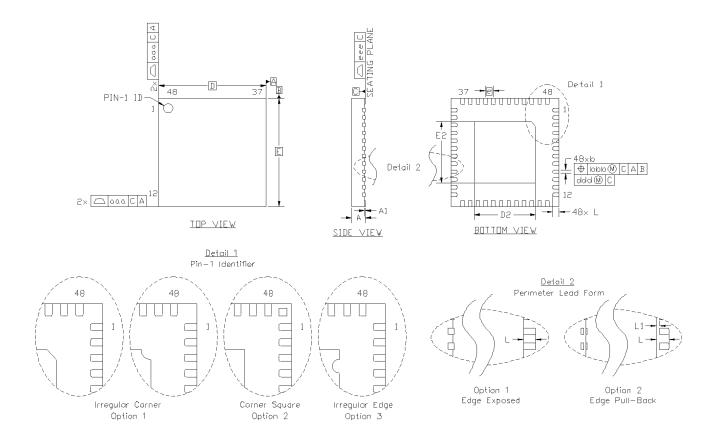

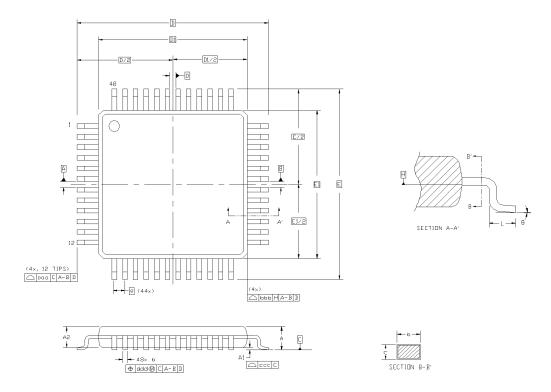

| Dimension | MIN  | NOM       | MAX  |  |

|-----------|------|-----------|------|--|

| Α         | 0.80 | 0.90      | 1.00 |  |

| A1        | 0.00 |           | 0.05 |  |

| b         | 0.18 | 0.23      | 0.30 |  |

| D         |      | 7.00 BSC. |      |  |

| D2        | 3.90 | 4.00      | 4.10 |  |

| е         |      | 0.50 BSC. |      |  |

| E         |      | 7.00 BSC. |      |  |

| E2        | 3.90 | 4.00      | 4.10 |  |

| L         | 0.30 | 0.40      | 0.50 |  |

| L1        | 0.00 |           | 0.10 |  |

| aaa       |      |           | 0.10 |  |

| bbb       |      |           | 0.10 |  |

| ddd       |      |           | 0.05 |  |

| eee       |      |           | 0.08 |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- This drawing conforms to JEDEC outline MO-220, variation VKKD-4 except for features D2 and L which are toleranced per supplier designation.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 4.7. QFN-48 Package Drawing

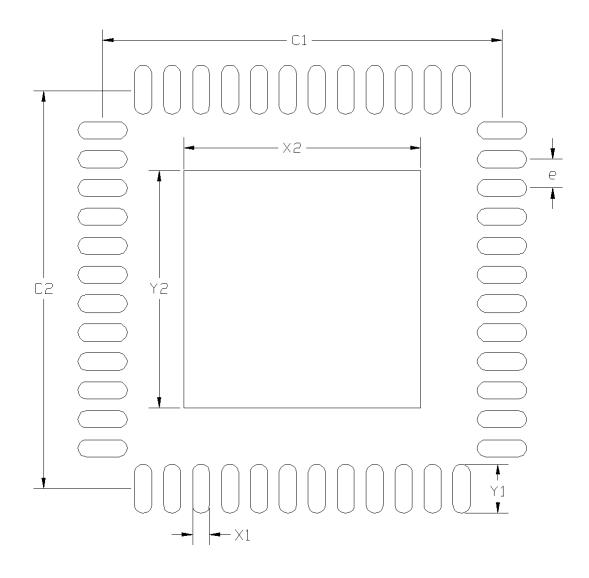

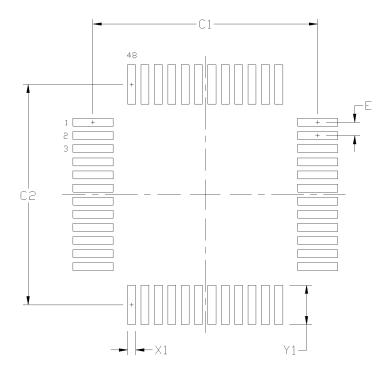

Figure 4.8. QFN-48 Landing Diagram

Table 4.1. PCB Land Pattern

| Dimension | MIN  | MAX  |

|-----------|------|------|

| C1        | 6.80 | 6.90 |

| C2        | 6.80 | 6.90 |

| е         | 0.50 | BSC  |

| X1        | 0.20 | 0.30 |

| X2        | 4.00 | 4.10 |

| Y1        | 0.75 | 0.85 |

| Y2        | 4.00 | 4.10 |

# General

- 3. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 4. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 5. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **6.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

## Stencil Design

- A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 3 x 3 array of 1.20 mm square openings on 1.40 mm pitch should be used for the center ground pad.

## **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

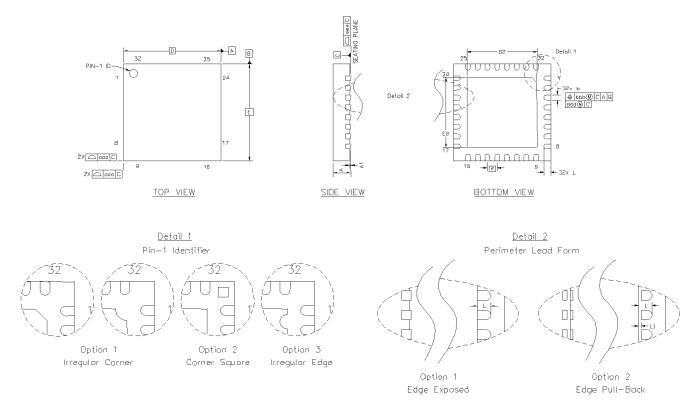

Figure 4.9. TQFP-48 Package Diagram

**Table 4.2. TQFP-48 Package Dimensions**

| Dimension | Min      | Nom      | Max  |  |  |  |

|-----------|----------|----------|------|--|--|--|

| A         | _        | _        | 1.20 |  |  |  |

| A1        | 0.05     | _        | 0.15 |  |  |  |

| A2        | 0.95     | 1.00     | 1.05 |  |  |  |

| b         | 0.17     | 0.22     | 0.27 |  |  |  |

| С         | 0.09     | _        | 0.20 |  |  |  |

| D         |          | 9.00 BSC | •    |  |  |  |

| D1        | 7.00 BSC |          |      |  |  |  |

| е         | 0.50 BSC |          |      |  |  |  |

| E         | 9.00 BSC |          |      |  |  |  |

| E1        |          | 7.00 BSC |      |  |  |  |

| L         | 0.45     | 0.60     | 0.75 |  |  |  |

| aaa       | 0.20     |          |      |  |  |  |

| bbb       | 0.20     |          |      |  |  |  |

| ccc       | 0.08     |          |      |  |  |  |

| ddd       | 0.08     |          |      |  |  |  |

| θ         | 0°       | 3.5°     | 7°   |  |  |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation ABC.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

Figure 4.10. TQFP-48 Recommended PCB Land Pattern

Table 4.3. TQFP-48 PCB Land Pattern Dimensions

| Dimension | Min       | Max  |  |

|-----------|-----------|------|--|

| C1        | 8.30      | 8.40 |  |

| C2        | 8.30 8.40 |      |  |

| E         | 0.50 BSC  |      |  |

| X1        | 0.20      | 0.30 |  |

| Y1        | 1.40      | 1.50 |  |

#### General:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

# Solder Mask Design:

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

### Stencil Design:

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

### Card Assembly:

- 7. A No-Clean, Type-3 solder paste is recommended.

- **8.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

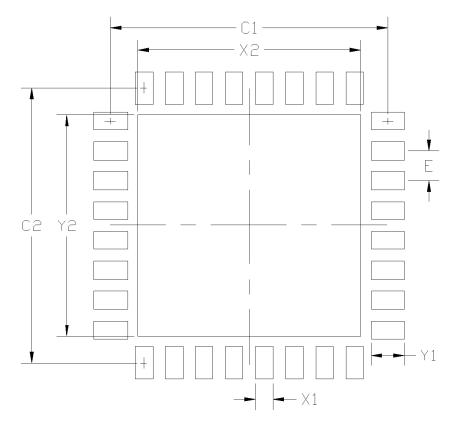

Figure 4.11. QFN-32 Package Drawing

Table 4.4. QFN-32 Package Dimensions

| Dimension | Min            | Тур  | Max  |  | Dimension | Min  | Тур  | Max  |

|-----------|----------------|------|------|--|-----------|------|------|------|

| Α         | 0.80           | 0.9  | 1.00 |  | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00           | 0.02 | 0.05 |  | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18           | 0.25 | 0.30 |  | L1        | 0.00 | _    | 0.15 |

| D         | 5.00 BSC       |      |      |  | aaa       | _    | _    | 0.15 |

| D2        | 3.20 3.30 3.40 |      |      |  | bbb       | _    | _    | 0.10 |

| е         | 0.50 BSC       |      |      |  | ddd       | _    | _    | 0.05 |

| Е         | 5.00 BSC       |      |      |  | eee       |      |      | 0.08 |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- **2.** Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 4.12. Typical QFN-32 Landing Diagram

Table 4.5. PCB Land Pattern

| Dimension | MIN      | MAX  |  |

|-----------|----------|------|--|

|           | 4.80     | 4.90 |  |

| C1        |          |      |  |

| C2        | 4.80     | 4.90 |  |

| E         | 0.50 BSC |      |  |

| X1        | 0.20     | 0.30 |  |

| X2        | 3.20     | 3.40 |  |

| Y1        | 0.75     | 0.85 |  |

| Y2        | 3.20     | 3.40 |  |

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 3 x 3 array of 1.0 mm square openings on 1.25 mm pitch should be used for the center ground pad.

## **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 5. Clocking Options

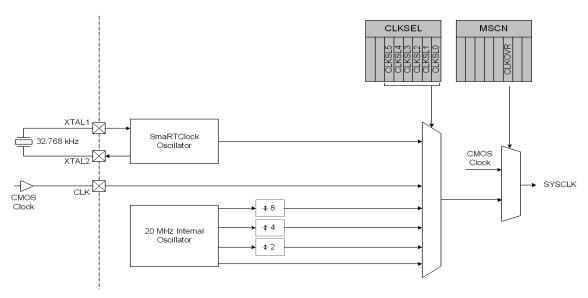

CP2400/1/2/3 devices include a 20 MHz internal oscillator that is selected as the system clock source upon reset. Additional clocking options include an external CMOS clock input, the internal oscillator divided by 2, 4, or 8, and the SmaRTClock real time clock oscillator. The system clock source is selected using the CLKSEL register. The system clock selection may always be overridden by an external CMOS clock if the CLKOVR bit (MSCN.2) is set.

Figure 5.1. Clocking Options

# SFR Definition 5.1. CLKSL: Clock Select

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1     | 0 |

|-------|-----|-----|-----|-----|-----|-----|-------|---|

| Name  |     |     |     |     |     |     | CLKSL |   |

| Туре  | R/W | R/W | R/W | R/W | R/W | R/W |       |   |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0     | 0 |

Internal Register Address = 0x32

32

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                     |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Unused | Read = 00000. Write = Don't Care.                                                                                                                                                                                                                                                                                            |

| 2:0 | CLKSL  | System Clock Select. Selects the oscillator to be used as system clock source. 000: Internal oscillator divided by 1. 001: Internal oscillator divided by 2. 010: Internal oscillator divided by 4. 011: Internal oscillator divided by 8. 100: CMOS clock (CLK pin). 101: SmaRTClock oscillator. All other values reserved. |

# SFR Definition 5.2. IOSCCN: Internal Oscillator Control

| Bit   | 7   | 6   | 5   | 4   | 3        | 2      | 1     | 0      |

|-------|-----|-----|-----|-----|----------|--------|-------|--------|

| Name  |     |     |     |     | Reserved | INTCTL | OSCEN | EXTCTL |

| Туре  | R/W | R/W | R/W | R/W | R/W      | R/W    |       |        |

| Reset | 0   | 0   | 0   | 0   | 0        | 1      | 1     | 0      |

### Internal Register Address = 0x33

| Bit | Name     | Function                                                                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused   | Read = 00000. Write = Don't Care.                                                                                                                                                                                             |

| 3   | Reserved | Read = 0. Write = Must Write 0b.                                                                                                                                                                                              |

| 2   | INTCTL   | Oscillator Internal Control Enable.  When set to 1, forces the oscillator to remain enabled. Setting this bit to 0 will gate the clock output, but will not disable the oscillator.                                           |

| 1   | OSCEN    | Internal Oscillator Enable.  When set to 0, disables power to the internal oscillator. When set to 1, allows the internal oscillator to be powered (under the control of INTCTL and EXTCTL).                                  |

| 0   | EXTCTL   | Oscillator External Control Enable.  When set to 1 and INTCTL is cleared to 0, a rising edge on CLK will cause the internal oscillator to be disabled. The internal oscillator is re-enabled by the next falling edge on CLK. |

Note: To control the internal oscillator enable from an external pin (EXTCTL = 1, INTCTL = 0), first write both bits to logic 1, then clear the INTCTL bit. See Section "9.2. RAM Preservation Mode" on page 50 for information on how to place the device in RAM Preservation Mode. When running from an external clock, the internal oscillator may be disabled by writing 0x00 to IOSCCN.

# SFR Definition 5.3. REVID: Revision Identification

| Bit   | 7          | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|------------|--------|--------|--------|--------|--------|--------|--------|--|

| Name  | REVID[7:0] |        |        |        |        |        |        |        |  |

| Туре  |            | R/W    |        |        |        |        |        |        |  |

| Reset | Varies     | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |

# Internal Register Address = 0x34

| Bit | Name       | Function                                                              |

|-----|------------|-----------------------------------------------------------------------|

| 7:0 | REVID[7:0] | Revision ID.                                                          |

|     |            | Indicates the device revision. For example 0x01 indicates Revision C. |

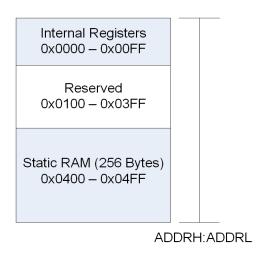

# 6. Internal Registers and Memory

The CP2400/1/2/3 is controlled by internal registers and provides the system with up to 256 bytes of additional RAM. The internal registers and memory are controlled through an indirect interface accessible through a 4-wire SPI interface (CP2400/2) or 2-wire SMBus/I<sup>2</sup>C interface (CP2401/3). A memory map of the internal registers and RAM is shown in Figure 6.1. The internal registers are listed in "6.3. Internal Registers" on page 37.

Figure 6.1. Internal Register and RAM Memory Map

# 6.1. Accessing Internal Registers and RAM over the SPI Interface

The SPI interface supports 6 commands which provide access to all internal registers and RAM. The six commands are listed in Table 6.1. Detailed information on the SPI interface including bus timing can be found in Section "14. Serial Peripheral Interface (SPI)" on page 101.

Table 6.1. SPI Command Set

| Command  | OPCODE | Description                                                                                                                       |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| REGPOLL  | 0x01   | Reads data from a single register. Used for polling a status bit.                                                                 |

| REGREAD  | 0x02   | Reads one or more bytes from registers with sequential addresses.                                                                 |

| REGSET   | 0x03   | Writes one or more bytes to a single register. Used for generating a waveform on a GPIO pin or updating the SmaRTClock registers. |

| REGWRITE | 0x04   | Writes one or more bytes to registers with sequential addresses.                                                                  |

| RAMREAD  | 0x06   | Reads one or more bytes from sequential RAM locations.                                                                            |

| RAMWRITE | 0x08   | Writes one or more bytes to sequential RAM locations.                                                                             |

Figure 6.2 shows a typical SPI transfer used to access internal registers or RAM. The first three bytes of the transfer are interpreted as COMMAND, ADDRH, and ADDRL. On a read, the fourth byte is a wait state in which the SPI shift register contents are ignored; starting with the fifth byte, data transfer begins. On a write, the fourth byte is the first data byte. The direction of data transfer depends on the specified command. The SPI transaction ends when NSS is de-asserted.

#### Write:

| COMMAND | ADDRH | ADDRL | DATA 0 | DATA 1 | 000 | DATA N |  |

|---------|-------|-------|--------|--------|-----|--------|--|

| Read:   |       |       |        |        |     |        |  |

| COMMAND | ADDRH | ADDRL | WAIT   | DATA 0 | 000 | DATA N |  |

Figure 6.2. SPI Transfer

Note: Using the RAMREAD command to read an address outside the 0x400–0x4FF range will result in a data value of 0xDE.

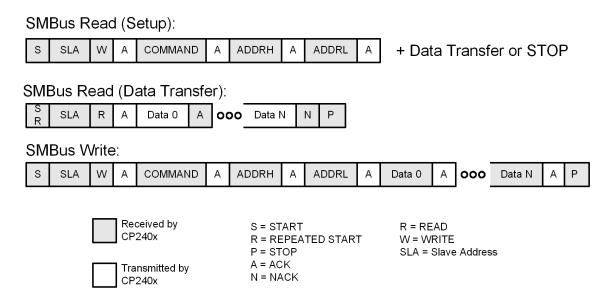

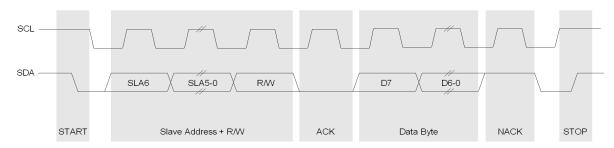

# 6.2. Accessing Internal Registers and RAM over the SMBus Interface

The SMBus interface supports 6 commands which provide access to all internal registers and RAM. The six commands are listed in Table 6.2. Detailed information on the SMBus interface including bus timing can be found in Section "15. SMBus Interface" on page 104.

Table 6.2. SMBus Command Set

| Command  | OPCODE | Description                                                                                                                       |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| REGPOLL  | 0x01   | Reads data from a single register. Used for polling a status bit.                                                                 |

| REGREAD  | 0x02   | Reads one or more bytes from registers with sequential addresses.                                                                 |

| REGSET   | 0x03   | Writes one or more bytes to a single register. Used for generating a waveform on a GPIO pin or updating the SmaRTClock registers. |

| REGWRITE | 0x04   | Writes one or more bytes to registers with sequential addresses.                                                                  |

| RAMREAD  | 0x06   | Reads one or more bytes from sequential RAM locations.                                                                            |

| RAMWRITE | 0x08   | Writes one or more bytes to sequential RAM locations.                                                                             |

Figure 6.3 shows typical SMBus read and write transfers used to access internal registers or RAM. The first three bytes of a write transfer are interpreted as COMMAND, ADDRH, and ADDRL. For the REGPOLL, REGREAD, and RAMREAD commands, a repeated start is required to begin data transfer. The host controller may also choose to end the transfer with a STOP and then start a new read transfer using the same setup information. For the WRITE and RAMWRITE command, an SMBus write transfer is required. Starting with the fourth byte following the slave address, all bytes written are interpreted as data. The SMBus transfer ends when the host sends a STOP.

Figure 6.3. SMBus Transfers

Note: Using the RAMREAD command to read an address outside the 0x400–0x4FF range will result in a data value of 0xDE.

## 6.3. Internal Registers

The CP2400/1/2/3 internal registers are grouped into categories based on function. The memory map is organized to minimize register access time, by sequentially locating registers that can be read or written with a single block read or write. Table 6.3 shows the register memory map for all registers available on the device.

**Table 6.3. Internal Register Memory Map**

| Register           | Address       | Description                                 | Preserved | Page No |

|--------------------|---------------|---------------------------------------------|-----------|---------|

| SmaRTClock Reg     | gisters       | 1                                           |           |         |

| RTCKEY             | 0x0A          | RTC0 Indirect Address                       | N         | 72      |

| RTCADR             | 0x0B          | RTC0 Indirect Data                          | N         | 73      |

| RTCDAT             | 0x0C          | RTC0 Lock and Key                           | N         | 73      |

| Interrupt Mask ar  | nd Clocking R | egisters                                    |           |         |

| INT0EN             | 0x30          | Interrupt Enable Register 0                 | N         | 43      |

| INT1EN             | 0x31          | Interrupt Enable Register 1                 | N         | 46      |

| CLKSL              | 0x32          | Clock Select                                | N         | 32      |

| IOSCCN             | 0x33          | Internal Oscillator Control                 | N         | 33      |

| REVID              | 0x34          | Revision Identifier                         | Y         | 33      |

| Interrupt Status F | Registers     |                                             |           |         |

| INT0RD             | 0x40          | Interrupt Status Register 0 (read-only)     | N         | 42      |

| INT1RD             | 0x41          | Interrupt Status Register 1 (read-only)     | N         | 45      |

| ULPST              | 0x42          | Ultra Low Power Status                      | Υ         | 55      |

| INT0               | 0x43          | Interrupt Status Register 0 (self-clearing) | N         | 41      |

| INT1               | 0x44          | Interrupt Status Register 1 (self-clearing) | N         | 44      |

| Timer 0 and Time   | r 1 Registers |                                             |           |         |

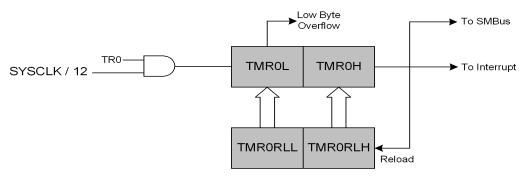

| TMR0RLL            | 0x50          | Timer 0 Reload Register Low Byte            | N         | 94      |

| TMR0RLH            | 0x51          | Timer 0 Reload Register High Byte           | N         | 94      |

| TMR0L              | 0x52          | Timer 0 Low Byte                            | N         | 95      |

| TMR0H              | 0x53          | Timer 0 High Byte                           | N         | 95      |

| TMR0CN             | 0x54          | Timer 0 Control                             | N         | 93      |

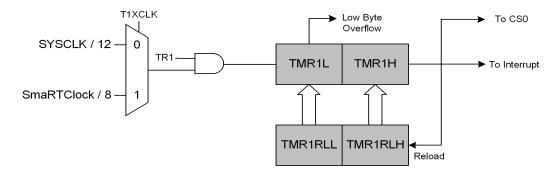

| TMR1RLL            | 0x55          | Timer 1 Reload Register Low Byte            | N         | 99      |

| TMR1RLH            | 0x56          | Timer 1 Reload Register High Byte           | N         | 99      |

| TMR1L              | 0x57          | Timer 1 Low Byte                            | N         | 100     |

| TMR1H              | 0x58          | Timer 1 High Byte                           | N         | 100     |

| TMR1CN             | 0x59          | Timer 1 Control                             | N         | 98      |

| SMBus Registers    | <b>3</b>      |                                             |           |         |

| SMBCF              | 0x68          | SMBus Configuration                         | N         | 107     |

| ULP/LCD0 Data R    | Registers     |                                             |           |         |

| LCD0BLINK          | 0x80          | LCD0 Segment Blink                          | Y         | 91      |

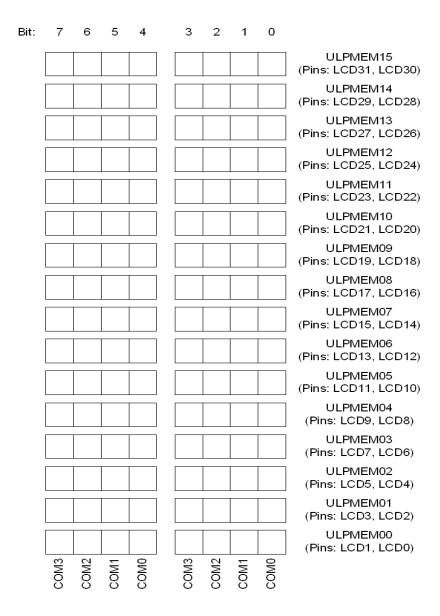

| ULPMEM00           | 0x81          | ULP Memory Byte 0                           | Y         | 57      |

| ULPMEM01           | 0x82          | ULP Memory Byte 1                           | Y         | 57      |

| ULPMEM02           | 0x83          | ULP Memory Byte 2                           | Y         | 57      |

**Table 6.3. Internal Register Memory Map (Continued)**

| Register         | Register Address Description |                              | Preserved | Page No. |

|------------------|------------------------------|------------------------------|-----------|----------|

| ULPMEM03         | 0x84                         | ULP Memory Byte 3            | Y         | 57       |

| ULPMEM04         | 0x85                         | ULP Memory Byte 4            | Y         | 57       |

| ULPMEM05         | 0x86                         | ULP Memory Byte 5            | Y         | 57       |

| ULPMEM06         | 0x87                         | ULP Memory Byte 6            | Y         | 57       |

| ULPMEM07         | 0x88                         | ULP Memory Byte 7            | Y         | 57       |

| ULPMEM08         | 0x89                         | ULP Memory Byte 8            | Y         | 57       |

| ULPMEM09         | 0x8A                         | ULP Memory Byte 9            | Y         | 57       |

| ULPMEM10         | 0x8B                         | ULP Memory Byte 10           | Y         | 57       |

| ULPMEM11         | 0x8C                         | ULP Memory Byte 11           | Y         | 57       |

| ULPMEM12         | 0x8D                         | ULP Memory Byte 12           | Y         | 57       |

| ULPMEM13         | 0x8E                         | ULP Memory Byte 13           | Y         | 57       |

| ULPMEM14         | 0x8F                         | ULP Memory Byte 14           | Y         | 57       |

| ULPMEM15         | 0x90                         | ULP Memory Byte 15           | Y         | 57       |

| LCD Control Rec  | gisters                      |                              |           |          |

| LCD0CN           | 0x95                         | LCD0 Control                 | Υ         | 84       |

| CONTRAST         | 0x96                         | LCD0 Contrast Adjustment     | Y         | 85       |

| LCD0CF           | 0x97                         | LCD0 Configuration           | Y         | 86       |

| LCD0DIVL         | 0x98                         | LCD0 Clock Divider High Byte | Y         | 87       |

| LCD0DIVH         | 0x99                         | LCD0 Clock Divider Low Byte  | Y         | 87       |

| LCD0TOGR         | 0x9A                         | LCD0 Toggle Rate             | Y         | 88       |

| LCD0PWR          | 0x9B                         | LCD0 Power Mode              | Y         | 89       |

| Ultra Low Power  | Control Regis                | sters                        |           |          |

| MSCN             | 0xA0                         | Master Control               | Y         | 58       |

| MSCF             | 0xA1                         | Master Configuration         | Y         | 59       |

| ULPCN            | 0xA2                         | Ultra Low Power Control      | Y         | 54       |

| Port I/O Configu | ration Registe               | rs                           |           |          |

| P0OUT            | 0xB0                         | Port 0 Output Data Latch     | N         | 66       |

| P1OUT            | 0xB1                         | Port 1 Output Data Latch     | N         | 66       |

| P2OUT            | 0xB2                         | Port 2 Output Data Latch     | N         | 66       |

| P3OUT            | 0xB3                         | Port 3 Output Data Latch     | N         | 66       |

| P4OUT            | 0xB4                         | Port 4 Output Data Latch     | N         | 66       |

| P0MDI            | 0xB5                         | Port 0 Input Mode            | N         | 67       |

| P1MDI            | 0xB6                         | Port 1 Input Mode            | N         | 67       |

| P2MDI            | 0xB7                         | Port 2 Input Mode            | N         | 67       |

| P3MDI            | 0xB8                         | Port 3 Input Mode            | N         | 67       |

| P4MDI            | 0xB9                         | Port 4 Input Mode            | N         | 67       |

| P0MDO            | 0xBA                         | Port 0 Output Mode           | N         | 67       |

| P1MDO            | 0xBB                         | Port 1 Output Mode           | N         | 67       |

| P2MDO            | 0xBC                         | Port 2 Output Mode           | N         | 67       |

| P3MDO            | 0xBD                         | Port 3 Output Mode           | N         | 67       |

**Table 6.3. Internal Register Memory Map (Continued)**

| Register           | egister Address Description |                       | Preserved | Page No. |

|--------------------|-----------------------------|-----------------------|-----------|----------|

| P4MDO              | 0xBE                        | Port 4 Output Mode    | N         | 67       |

| P0DRIVE            | 0xBF                        | Port 0 Drive Strength | N         | 68       |

| P1DRIVE            | 0xC0                        | Port 1 Drive Strength | N         | 68       |

| P2DRIVE            | 0xC1                        | Port 2 Drive Strength | N         | 68       |

| P3DRIVE            | 0xC2                        | Port 3 Drive Strength | N         | 68       |

| P4DRIVE            | 0xC3                        | Port 4 Drive Strength | N         | 68       |

| POMATCH            | 0xC4                        | Port 0 Match          | N         | 64       |

| P1MATCH            | 0xC5                        | Port 1 Match          | N         | 64       |

| P2MATCH            | 0xC6                        | Port 2 Match          | N         | 64       |

| P3MATCH            | 0xC7                        | Port 3 Match          | N         | 64       |

| P4MATCH            | 0xC8                        | Port 4 Match          | N         | 64       |

| P0MSK              | 0xC9                        | Port 0 Mask           | N         | 64       |

| P1MSK              | 0xCA                        | Port 1 Mask           | N         | 64       |

| P2MSK              | 0xCB                        | Port 2 Mask           | N         | 64       |

| P3MSK              | 0xCC                        | Port 3 Mask           | N         | 64       |

| P4MSK              | 0xCD                        | Port 4 Mask           | N         | 64       |

| Port I/O Input and | Status Regis                | sters                 |           |          |

| PMATCHST           | 0xD0                        | Port Match Status     | N         | 63       |

| POIN               | 0xD1                        | Port 0 Input N        |           | 66       |

| P1IN               | 0xD2                        | Port 1 Input N        |           | 66       |

| P2IN               | 0xD3                        | Port 2 Input N        |           | 66       |

| P3IN               | 0xD4                        | Port 3 Input N        |           | 66       |

| P4IN               | 0xD5                        | Port 4 Input          | N         | 66       |

## 7. Interrupt Sources

The CP2400/1/2/3 can alert the host processor when any of the interrupt source events listed in Table 7.1 triggers an interrupt. The CP2400/1/2/3 alerts the host of pending interrupt events by setting the appropriate flags in the interrupt status registers and driving the  $\overline{\text{INT}}$  pin low. The  $\overline{\text{INT}}$  pin will remain asserted until all interrupt flags for enabled interrupts have been cleared by the host. Interrupt flags are cleared by reading the self-clearing interrupt status registers, INT0 and INT1. Interrupts can be disabled by clearing the corresponding bits in INT0EN and INT1EN.

**Note:** When SmaRTClock interrupts are enabled, they are also captured in the ULPST register. If the bits in ULPST are set, then the SmaRTClock interrupt flags in the INT0 register will not clear. To clear SmaRTClock interrupt events, first clear the ULPST register then clear INT0.

If the host processor does not utilize the  $\overline{\text{INT}}$  pin, it can periodically read the interrupt status registers to determine if any interrupt-generating events have occurred. The INTORD and INT1RD read-only registers provide a method of checking for interrupts without clearing the interrupt status registers.

**Table 7.1. Interrupt Source Events**

| Event                         | Description                                                                              | Pending<br>Flag | Enable<br>Flag |

|-------------------------------|------------------------------------------------------------------------------------------|-----------------|----------------|

| SmaRTClock Alarm              | A SmaRTClock Alarm has occurred.                                                         | INT0.4          | INT0EN.4       |

| SmaRTClock Oscillator Failure | The SmaRTClock Oscillator has experienced a failure.                                     | INT0.3          | INT0EN.3       |

| Port Match                    | A Port Match event has occurred.                                                         | INT0.0          | INT0EN.0       |

| Reset Complete                | The device is now initialized and ready to communicate over the host interface.          | INT1.4          | INT1EN.4       |

| Timer 1 Overflow              | Timer 1 has overflowed from 0xFFFF to 0x0000 or a SmaRTClock capture event has occurred. | INT1.3          | INT1EN.3       |

| Timer 0 Overflow              | Timer 0 has overflowed from 0xFFFF to 0x0000.                                            | INT1.2          | INT1EN.2       |

# SFR Definition 7.1. INT0: Interrupt Status Register 0 (Self-Clearing)

| Bit   | 7 | 6 | 5        | 4    | 3       | 2 | 1 | 0     |

|-------|---|---|----------|------|---------|---|---|-------|

| Name  |   |   | Reserved | ALRM | RTCFAIL |   |   | PMINT |

| Туре  | R | R | R        | R    | R       | R | R | R     |

| Reset | 0 | 0 | 0        | 0    | 0       | 0 | 0 | 0     |

### Address = 0x43

| Bit | Name     | Function                                                                            |

|-----|----------|-------------------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 00b.                                                                         |

| 5   | Reserved | Read = 0.                                                                           |

| 4   | ALRM     | SmaRTClock Alarm Interrupt Flag.                                                    |

|     |          | 0: No SmaRTClock Alarm pending since ALRM was last cleared.                         |

|     |          | 1: SmaRTClock Alarm pending.                                                        |

| 3   | RTCFAIL  | SmaRTClock Oscillator Fail Interrupt Flag.                                          |

|     |          | 0: No SmaRTClock oscillator failure events detected since RTCFAIL was last cleared. |

|     |          | 1: SmaRTClock oscillator failure detected.                                          |

| 2:1 | Unused   | Read = 00b.                                                                         |

| 0   | PMINT    | Port Match Interrupt Flag.                                                          |

|     |          | 0: No Port Match events detected since PMINT was last cleared.                      |

|     |          | 1: Port Match event pending.                                                        |

# SFR Definition 7.2. INT0RD: Interrupt Status Register 0 (Read-Only)

| Bit   | 7 | 6 | 5        | 4     | 3        | 2 | 1 | 0      |

|-------|---|---|----------|-------|----------|---|---|--------|

| Name  |   |   | Reserved | ALRMR | RTCFAILR |   |   | PMINTR |

| Туре  | R | R | R        | R     | R        | R | R | R      |

| Reset | 0 | 0 | 0        | 0     | 0        | 0 | 0 | 0      |

### Address = 0x40

| Bit | Name     | Function                                                                            |

|-----|----------|-------------------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 00b.                                                                         |

| 5   | Reserved | Read = 0.                                                                           |

| 4   | ALRMR    | SmaRTClock Alarm Interrupt Flag.                                                    |

|     |          | 0: No SmaRTClock Alarm pending since ALRM was last cleared.                         |

|     |          | 1: SmaRTClock Alarm pending.                                                        |

| 3   | RTCFAILR | SmaRTClock Oscillator Fail Interrupt Flag.                                          |

|     |          | 0: No SmaRTClock oscillator failure events detected since RTCFAIL was last cleared. |

|     |          | 1: SmaRTClock oscillator failure detected.                                          |

| 2:1 | Unused   | Read = 00b.                                                                         |

| 0   | PMINTR   | Port Match Interrupt Flag.                                                          |

|     |          | 0: No Port Match events detected since PMINT was last cleared.                      |

|     |          | 1: Port Match event pending.                                                        |

# SFR Definition 7.3. INT0EN: Interrupt Enable Register 0

| Bit   | 7   | 6   | 5        | 4     | 3        | 2   | 1   | 0      |

|-------|-----|-----|----------|-------|----------|-----|-----|--------|

| Name  |     |     | Reserved | EALRM | ERTCFAIL |     |     | EPMINT |

| Туре  | R/W | R/W | R/W      | R/W   | R/W      | R/W | R/W | R/W    |

| Reset | 1   | 1   | 1        | 1     | 0        | 1   | 1   | 1      |

### Address = 0x30

| Bit | Name     | Function                                                                 |

|-----|----------|--------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 11b. Write = don't care.                                          |

| 5   | Reserved | Read = varies. Write = must write 0b.                                    |

| 4   | EALRM    | Enable SmaRTClock Alarm Interrupt.                                       |

|     |          | This bit sets the masking of the SmaRTClock Alarm interrupt.             |

|     |          | 0: Disable SmaRTClock Alarm interrupts.                                  |

|     |          | 1: Enable interrupt requests generated by SmaRTClock Alarm Events.       |

| 3   | ERTCFAIL | Enable SmaRTClock Fail Interrupt.                                        |

|     |          | This bit sets the masking of the SmaRTClock Oscillator Fail interrupt.   |

|     |          | 0: Disable SmaRTClock Oscillator Fail interrupt.                         |

|     |          | 1: Enable interrupt requests generated by SmaRTClock Oscillator Failure. |

| 2:1 | Unused   | Read = 11b. Write = don't care.                                          |

| 0   | EPMINT   | Enable Port Match Interrupt.                                             |

|     |          | This bit sets the masking of Port Match Interrupt.                       |

|     |          | 0: Disable Port Match Interrupt.                                         |

|     |          | 1: Enable interrupt requests generated by Port Match events.             |

# SFR Definition 7.4. INT1: Interrupt Status Register 1 (Self-Clearing)

| Bit   | 7 | 6 | 5 | 4    | 3   | 2   | 1 | 0 |

|-------|---|---|---|------|-----|-----|---|---|

| Name  |   |   |   | RSTC | T1F | T0F |   |   |

| Туре  | R | R | R | R    | R   | R   | R | R |

| Reset | 0 | 0 | 0 | 0    | 0   | 1   | 0 | 0 |

## Address = 0x44

| Bit | Name   | Function                                                                              |

|-----|--------|---------------------------------------------------------------------------------------|

| 7:5 | Unused | Read = 000b.                                                                          |

| 4   | RSTC   | Reset Complete Interrupt Flag.                                                        |