### **MIC59P50**

### 8-Bit Parallel-Input Protected Latched Driver

### **General Description**

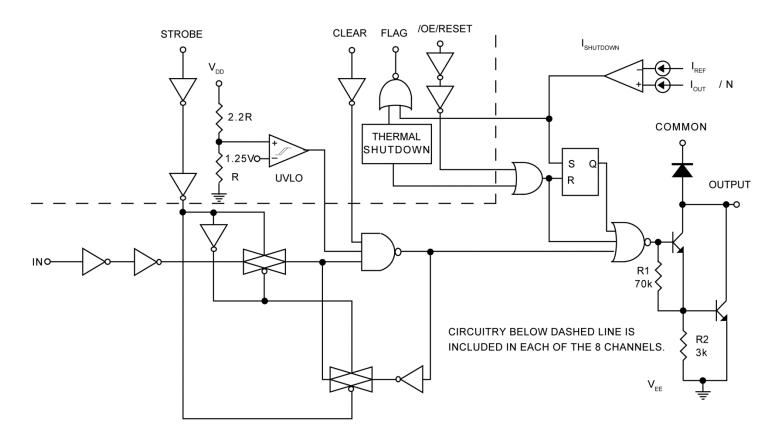

The MIC59P50 parallel-input latched driver is a high-voltage (80V), high-current (500mA) integrated circuit comprised of eight CMOS data latches, a bipolar Darlington transistor driver for each latch, and CMOS control circuitry for the common CLEAR, STROBE, and OUTPUT ENABLE functions. Similar to the MIC5801, additional protection circuitry supplied on this device includes thermal shutdown, undervoltage lockout (UVLO), and overcurrent shutdown.

The bipolar/MOS combination provides an extremely low-power latch with maximum interface flexibility. The MIC59P50 has open-collector outputs capable of sinking 500mA and integral diodes for inductive load transient suppression with a minimum output breakdown voltage rating of 80V above  $V_{\text{EE}}$  (50V sustaining). The drivers can be operated with a split supply, where the negative supply is down to -20V and may be paralleled for higher load current capability.

With a 5V logic supply, the MIC59P50 will typically operate at better than 5MHz. With a 12V logic supply, significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS, PMOS, and NMOS circuits. TTL circuits may require pull-up resistors.

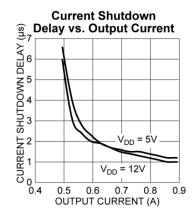

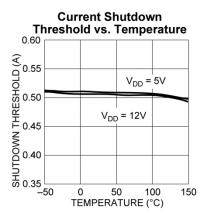

Each of these eight outputs has an independent overcurrent shutdown at 500mA. Upon current shutdown, the affected channel will turn OFF and the flag will go low until  $V_{DD}$  is cycled or the /ENABLE/RESET pin is pulsed high. Current pulses less than 2 $\mu$ s will not activate overcurrent shutdown. Temperatures above +165°C will shut down the device and activate the open-collector FLAG output at pin 1. The UVLO circuit disables the outputs at low  $V_{DD}$ ; hysteresis of 0.5V is provided.

Datasheets and support documentation are available on Micrel's website at: <a href="https://www.micrel.com">www.micrel.com</a>.

#### **Features**

- 4.4MHz minimum data input rate

- High-voltage, high-current outputs

- Per-output overcurrent shutdown (500mA typical)

- · Undervoltage lockout

- Output fault flag

- · Output transient protection diodes

- CMOS, PMOS, NMOS, and TTL-compatible inputs

- Internal pull-down resistors

- Low-power CMOS latches

- Single or split supply operation

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

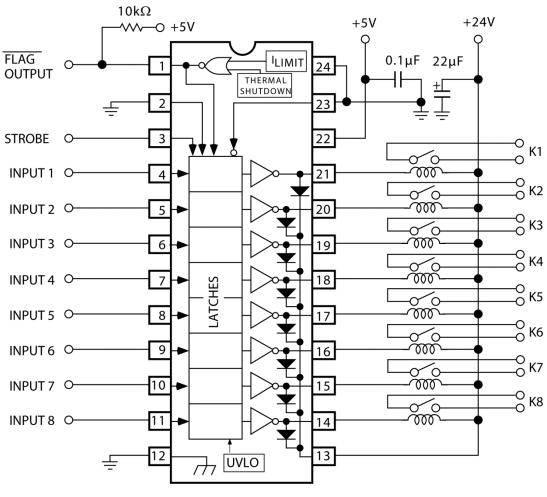

# **Functional Diagram**

## **Ordering Information**

| Part Number | Temperature Range | Package                           | Pb-Free      |

|-------------|-------------------|-----------------------------------|--------------|

| MIC59P50YN  | -40°C to +85°C    | 24-Pin Plastic DIP <sup>(1)</sup> | $\checkmark$ |

| MIC59P50YV  | -40°C to +85°C    | 28-Pin PLCC                       | $\checkmark$ |

| MIC59P50YWM | -40°C to +85°C    | 24-Pin Wide SOIC                  | $\checkmark$ |

#### Note:

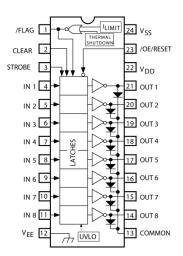

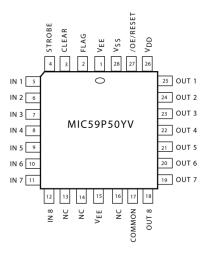

## **Pin Configuration**

24-Pin PDIP (N) 24-Pin Wide SOIC (WM) (Top View)

28-Pin PLCC (V) (Top View)

## **Pin Description**

| Pin Number<br>PDIP & SOIC | Pin Number<br>PLCC | Pin Name         | Pin Name                                                                                                                                                                                           |

|---------------------------|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | 2                  | /FLAG            | Error flag. Open-collector output is low upon overcurrent fault or overtemperature fault. /OE/RESET must be pulled high to reset the flag and fault condition.                                     |

| 2                         | 3                  | CLEAR            | Sets all latches to OFF (open).                                                                                                                                                                    |

| 3                         | 4                  | STROBE           | Input strobe pin. Loads output latches when high.                                                                                                                                                  |

| 4-11                      | 5-12               | IN <sub>n</sub>  | Parallel inputs, 1 through 8.                                                                                                                                                                      |

| 12                        | 15                 | VEE              | Output ground (substrate). Most negative voltage in the system connects here.                                                                                                                      |

| 13                        | 17                 | COMMON           | Transient suppression diodes cathode common pin.                                                                                                                                                   |

| 14-21                     | 18-25              | OUT <sub>n</sub> | Parallel outputs, 8 through 1.                                                                                                                                                                     |

| 22                        | 26                 | VDD              | Logic positive supply voltage.                                                                                                                                                                     |

| 23                        | 27                 | /OE/RESET        | Output enable reset. When low, outputs are active. When high, outputs are inactive and the flag and outputs are reset from a fault condition. An undervoltage condition emulates a high /OE input. |

| 24                        | 28                 | VSS              | Logic reference (ground) pin.                                                                                                                                                                      |

<sup>1. 300</sup>mm "Skinny DIP"

# Absolute Maximum Ratings<sup>(2)</sup>

| Input Voltage (V <sub>CE</sub> )               | +80V           |

|------------------------------------------------|----------------|

| Supply Voltage                                 |                |

| (V <sub>DD</sub> )                             | 15V            |

| $(V_{DD} - V_{EE})$                            | 25V            |

| Continuous Collector Current (I <sub>C</sub> ) |                |

| Protected Current <sup>(4)</sup>               | 1.5A           |

| Lead Temperature (soldering, 10s)              | 260°C          |

| Storage Temperature (Ts)                       | 65°C to +150°C |

| ESD Rating <sup>(5)</sup>                      | ESD Sensitive  |

|                                                |                |

# Operating Ratings<sup>(3)</sup>

| Input Voltage (V <sub>IN</sub> )        | $-0.3V$ to $V_{DD}+0.3V$ |

|-----------------------------------------|--------------------------|

| Operating Temperature (T <sub>A</sub> ) | 40°C to +85°C            |

| Junction Temperature (T <sub>J</sub> )  | +150°C                   |

| Power Dissipation (P <sub>D</sub> )     |                          |

| Plastic DIP (N)                         | 2.4W                     |

| Derate above $T_A = +25^{\circ}C$       | 24mW/°C                  |

| PLCC (V)                                | 1.6W                     |

| Derate above T <sub>A</sub> = +25°C     | 16mW/°C                  |

| Wide SOIC (WM)                          | 1.4W                     |

| Derate above T <sub>v</sub> = +25°C     |                          |

## Electrical Characteristics<sup>(6)</sup>

$V_{DD} = 5V$ ;  $T_A = 25$ °C, unless noted.

| Symbol               | Parameter              | Condition                                     | Min. | Тур. | Max. | Units |

|----------------------|------------------------|-----------------------------------------------|------|------|------|-------|

|                      | Outrot Leakana Commant | V <sub>CE</sub> = 80V, T <sub>A</sub> = +25°C |      |      | 50   | μΑ    |

| I <sub>CEX</sub>     | Output Leakage Current | V <sub>CE</sub> = 80V, T <sub>A</sub> = +70°C |      |      | 100  | μΑ    |

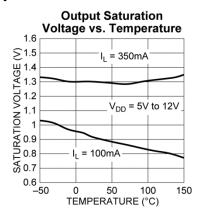

| V <sub>CE(SAT)</sub> | Collector-Emitter      | I <sub>C</sub> = 100mA                        |      | 0.9  | 1.1  | V     |

|                      | Onto mating Maltage    | I <sub>C</sub> = 200mA                        |      | 1.1  | 1.3  | V     |

|                      | Saturation Voltage     | I <sub>C</sub> = 350mA                        |      | 1.3  | 1.6  | V     |

| V <sub>IN(0)</sub>   |                        |                                               |      |      | 1.0  | V     |

|                      | Input Voltage          | V <sub>DD</sub> = 12V                         | 10.5 |      |      | V     |

| $V_{IN(1)}$          |                        | V <sub>DD</sub> = 10V                         | 8.5  |      |      | V     |

|                      |                        | V <sub>DD</sub> = 5V, Note 7                  | 3.5  |      |      | V     |

|                      |                        | V <sub>DD</sub> = 12V                         | 50   | 200  |      | kΩ    |

| R <sub>IN</sub>      | Input Resistance       | V <sub>DD</sub> = 10V                         | 50   | 300  |      | kΩ    |

|                      |                        | $V_{DD} = 5V$                                 | 50   | 600  |      | kΩ    |

| I <sub>OL</sub>      | /Flag Output Current   | V <sub>OL</sub> = 0.4V                        |      | 15   |      | mA    |

| I <sub>OH</sub>      | /Flag Output Leakage   | V <sub>OH</sub> = 12V                         |      | 50   |      | nA    |

#### Notes:

- 2. Exceeding the absolute maximum ratings may damage the device.

- 3. The device is not guaranteed to function outside its operating ratings.

- 4. Each channel VEE connection must be designed to minimize inductance and resistance.

- 5. Devices are ESD sensitive. Handling precautions are recommended. Human body model, 1.5kΩ in series with 100pF.

- 6. Specification for packaged product only.

- 7. Operation of these devices with standard TTL or DTL may require the use of appropriate pull-up resistors to ensure a minimum logic "1".

# Electrical Characteristics<sup>(6)</sup> (Continued)

$V_{DD} = 5V$ ;  $T_A = 25$ °C, unless noted.

| Symbol                  | Parameter                         | Condition                                        | Min. | Тур. | Max. | Units |

|-------------------------|-----------------------------------|--------------------------------------------------|------|------|------|-------|

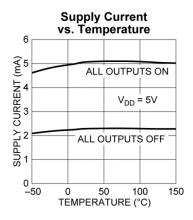

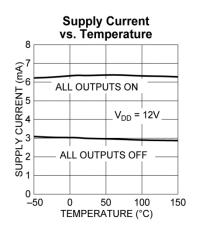

|                         |                                   | V <sub>DD</sub> = 12V, outputs open              |      | 3.3  | 4.5  | mA    |

| I <sub>DD(ON)1</sub>    | Supply Current One Output Active  | V <sub>DD</sub> = 10V, outputs open              |      | 3.1  | 4.5  | mA    |

|                         |                                   | V <sub>DD</sub> = 5V, outputs open               |      | 2.4  | 3.6  | mA    |

|                         |                                   | V <sub>DD</sub> = 12V, outputs open              |      | 6.4  | 10.0 | mA    |

| I <sub>DD(ON)</sub> All | Supply Current                    | V <sub>DD</sub> = 10V, outputs open              |      | 6.0  | 9.0  | mA    |

|                         | All Outputs Active                | V <sub>DD</sub> = 5V, outputs open               |      | 4.7  | 7.5  | mA    |

|                         | Supply Current OFF                | V <sub>DD</sub> = 12V, outputs open, inputs = 0V |      | 3.0  | 4.5  | mA    |

| I <sub>DD(OFF)</sub>    |                                   | V <sub>DD</sub> = 5V, outputs open, inputs = 0V  |      | 2.2  | 3.6  | mA    |

|                         | Claren Diada Laglaga Current      | V <sub>R</sub> = 80V, T <sub>A</sub> = +25°C     |      |      | 50   | μΑ    |

| $I_R$                   | Clamp Diode Leakage Current       | V <sub>R</sub> = 80V, T <sub>A</sub> = +70°C     |      |      | 100  | μΑ    |

| I <sub>LIM</sub>        | Overcurrent Threshold             | Each output                                      |      | 500  |      | mA    |

| V <sub>SU</sub>         | Start-up Voltage                  | Note 8                                           | 3.5  | 4.0  | 4.5  | V     |

| V <sub>DD MIN</sub>     | Minimum Operating V <sub>DD</sub> |                                                  | 3.0  | 3.5  | 4.0  | V     |

| V <sub>F</sub>          | Clamp Diode Forward Voltage       | I <sub>F</sub> = 350mA                           |      | 1.7  | 2.0  | V     |

|                         | Thermal Shutdown                  |                                                  |      | 165  |      | °C    |

|                         | Thermal Shutdown Hysteresis       |                                                  |      | 10   |      |       |

#### Notes:

### **Truth Table**

| INI             | Strobe | Clear | Output Enable | OUT <sub>n</sub> |     |  |

|-----------------|--------|-------|---------------|------------------|-----|--|

| IN <sub>n</sub> | Strobe | Clear | Output Enable | t-1              | t   |  |

| 0               | 1      | 0     | 0             | X                | OFF |  |

| 1               | 1      | 0     | 0             | X                | ON  |  |

| X               | X      | 1     | X             | X                | OFF |  |

| X               | X      | X     | 1             | X                | OFF |  |

| X               | 0      | 0     | 0             | ON               | ON  |  |

| Х               | 0      | 0     | 0             | OFF              | OFF |  |

#### Note:

X = Irrelevant

t-1 = Previous output state

t = Present output state

Information present at an input is transferred to its latch when the STROBE is high. A high CLEAR input will set all latches to the output OFF condition regardless of the data or STROBE input levels. A high OUTPUT ENABLE will set all outputs to the OFF condition, regardless of any other input conditions. When the OUTPUT ENABLE is low, the outputs depend on the state of their respective latches. If current shutdown is activated, the OUTPUT ENABLE must be pulsed high to restore operation and reset the FLAG. Overtemperature faults are not latched and require no reset pulse.

<sup>8.</sup> Undervoltage lockout is guaranteed to release device at no more than 4.5V and disable the device at no less than 3.0V input logic voltage.

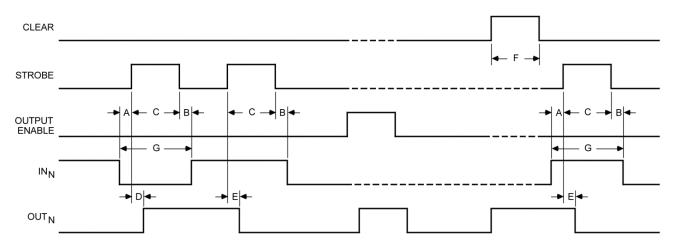

# **Timing Diagram**

### **Timing Conditions**

$T_{\text{A}}$  = +25°C; Logic levels are  $V_{\text{DD}}$  and  $V_{\text{SS}};\,V_{\text{DD}}$  = 5V.

| A. | Minimum data active time before strobe enabled (data set-up time)      | 50ns  |

|----|------------------------------------------------------------------------|-------|

| В. | Minimum data active time after strobe disabled (data hold time)        | 50ns  |

| C. | Minimum strobe pulse width                                             | 125ns |

| D. | Typical time between strobe activation and output on-to-off transition | 500ns |

| E. | Typical time between strobe activation and output off-to-on transition | 500ns |

| F. | Minimum clear pulse width                                              | 300ns |

| G. | Minimum data pulse width                                               | 225ns |

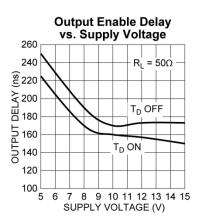

## **Typical Characteristics**

## **Typical Application**

**MIC59P50 Protected Relay Driver**

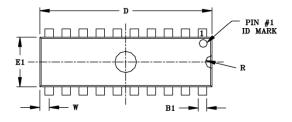

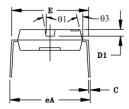

# Package Information and Recommended Land Pattern<sup>(9)</sup>

REMARKS: FOR 8L/16L(S) ALL END LEADS (4X) ARE HALF LEAD TYPES V1=0.039 (4X)

TOP VIEW

END VIEW

SIDE VIEW

#### NOTE:

- 1. SPADE WIDTH, LEAD WIDTH AND LEAD THICKNESS EXCLUSIVE OF TIN PLATING OR SOLDER PLATING/DIPPING THICKNESS.

2. PACKAGE OUTLINE EXCLUSIVE OF ANY MOLD FLASHES.

3. PACKAGE OUTLINE EXCLUSIVE OF BURR DIMENSION.

- \* REFERENCE DIMENSION.

- 5. PACKAGE AND FINISHING: TOP, BOTTOM & ALL SIDE: MATTE VDI #24~27.

| LEAD TYPE                        |    | 8LD              | 14/16LD                      | 18LD             | SOLD             | 24LD             |

|----------------------------------|----|------------------|------------------------------|------------------|------------------|------------------|

| STAND-OFF                        | A1 | 0.015 MIN        | 0.015 MIN                    | 0.015 MIN        | 0.015 MIN        | 0.015 MIN        |

| LEAD WIDTH *                     | В  | 0.018            | 0.018                        | 0.018            | 0.018            | 0.018            |

| SPADE WIDTH *                    | B1 | 0.060            | 0.060                        | 0.060            | 0.060            | 0.060            |

| LEAD THICKNESS *                 | С  | 0.010            | 0.010                        | 0.010            | 0.010            | 0.012            |

| LENGTH TOL ±0.004                | D  | 0.375            | 0.750                        | 0.890            | 1.020            | 1.250            |

| IDENT DEPTH                      | D1 | 0.030 ~<br>0.060 | 0.030 ~<br>0.060             | 0.030 ~<br>0.060 | 0.030 ~<br>0.060 | 0.030 ~<br>0.060 |

| SHOULDER WIDTH<br>OUTER TO OUTER | E  | 0.300 ~<br>0.325 | 0.300 ~<br>0.325             | 0.300 ~<br>0.325 | 0.300 ~<br>0.325 | 0.300 ~<br>0.325 |

| WIDTH TOL ±0.004                 | E1 | 0.250            | 0.250                        | 0.250            | 0.250            | 0.250            |

| LEAD SPREAD<br>OUTER TO OUTER    | еA | 0.320 ~<br>0.370 | 0.320 ~<br>0.370             | 0.320 ~<br>0.370 | 0.320 ~<br>0.370 | 0.320 ~<br>0.370 |

| LEAD PITCH *                     | e1 | 0.100            | 0.100                        | 0.100            | 0.100            | 0.100            |

| LEAD LENGTH TOL ±0.004           | L  | 0.125            | 0.125                        | 0.125            | 0.125            | 0.125            |

| IDENT RADIUS                     | R  | 0.030            | 0.030                        | 0.030            | 0.030            | 0.030            |

| TOTAL THICKNESS TOL ±0.004       | T  | 0.130            | 0.130                        | 0.130            | 0.130            | 0.130            |

| LEAD TO END PACKAGE              | w  | 0.025 REF        | 0.075REF14LD<br>0.025REF16LD | 0.045REF         | 0.060REF         | 0.075REF         |

| IDENT DRAFT TOL ±3°              | θ1 | 7°               | 7°                           | 7°               | 7°               | 7°               |

| END ANGLE (4x) TOL ±3°           | θ2 | 7°               | 7°                           | 7°               | 7°               | 7°               |

| SIDE ANGLE (4x) TOL ±3°          | θ3 | 7°               | 7°                           | 7°               | 7°               | 7°               |

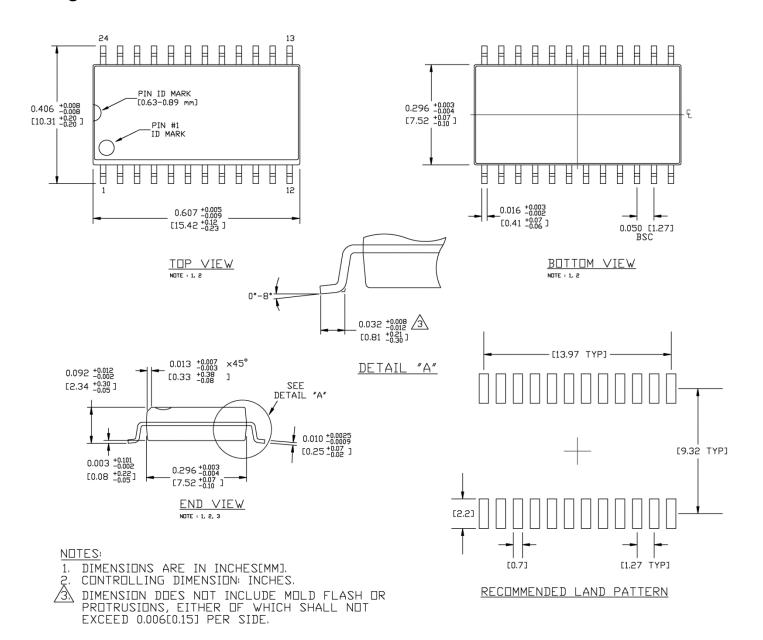

24-Pin PDIP (N)

#### Note:

9. Package information is correct as of the publication date. For updates and most current information, go to <a href="https://www.micrel.com">www.micrel.com</a>.

MIC59P50 Micrel, Inc.

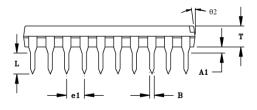

# Package Information and Recommended Land Pattern<sup>(9)</sup>

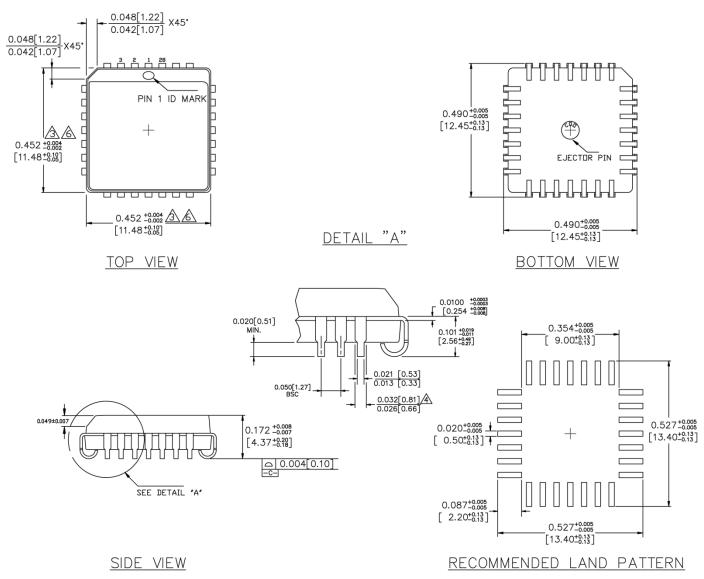

#### NOTES:

- DIMENSIONS ARE IN INCHES [MM]. CONTROLLING DIMENSION: INCHES.

- 2. CONTROLLING DIMENSION: INCHES.

DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIO

LEAD DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.008 [0.203].

- MAXIMUM AND MINIMUM SPECIFICATIONS ARE INDICATED AS FOLLOWS : MAX/MIN

- PACKAGE TOP DIMENSION MAY BE SLIGHTLY SMALLER THAN BOTTOM DIMENSION.

28-Pin PLCC (V)

# Package Information and Recommended Land Pattern<sup>(9)</sup>

24-Pin Wide SOIC (WM)

### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel, Inc. is a leading global manufacturer of IC solutions for the worldwide high performance linear and power, LAN, and timing & communications markets. The Company's products include advanced mixed-signal, analog & power semiconductors; high-performance communication, clock management, MEMs-based clock oscillators & crystal-less clock generators, Ethernet switches, and physical layer transceiver ICs. Company customers include leading manufacturers of enterprise, consumer, industrial, mobile, telecommunications, automotive, and computer products. Corporation headquarters and state-of-the-art wafer fabrication facilities are located in San Jose, CA, with regional sales and support offices and advanced technology design centers situated throughout the Americas, Europe, and Asia. Additionally, the Company maintains an extensive network of distributors and reps worldwide.

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this datasheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 1998 Micrel, Incorporated.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Microchip:

<u>MIC59P50YN MIC59P50BWM MIC59P50YV MIC59P50YWM MIC59P50YV-TR MIC59P50BWM-TR MIC59</u>