SLUSB98A - OCTOBER 2012-REVISED DECEMBER 2014

bq24196

# bg24196 I<sup>2</sup>C Controlled 2.5-A Single Cell USB/Adapter Charger with Narrow VDC Power Path Management and USB OTG

#### Features

- High Efficiency 2.5-A Switch Mode Charger

- 92% Charge Efficiency at 2 A

- Highest Battery Discharge Efficiency with 12-mΩ Battery Discharge MOSFET up to 9-A Discharge Current

- Single Input USB-compliant/Adapter Charger

- Input Voltage and Current Limit Supports USB2.0 and USB3.0

- Input Current Limit: 100 mA, 150 mA, 500 mA, 900 mA, 1.2 A, 1.5 A, 2 A and 3 A

- 3.9-V to 17-V Input Operating Voltage Range

- Support All Kinds of Adapter with Input Voltage **DPM Regulation**

- USB OTG 5 V at 1.3-A Synchronous Boost Converter Operation

- 93% 5-V Boost Efficiency at 1 A

- Narrow VDC (NVDC) Power Path Management

- Instant-on Works with No Battery or Deeply **Discharged Battery**

- Ideal Diode Operation in Battery Supplement

- 1.5-MHz Switching Frequency for Low Profile

- Autonomous Battery Charging with or without Host Management

- **Battery Charge Enable**

- **Battery Charge Preconditioning**

- Charge Termination and Recharge

- High Accuracy (0°C to 125°C)

- ±0.5% Charge Voltage Regulation

- ±7% Charge Current Regulation

- ±7.5% Input Current Regulation

- ±2% Output Regulation in Boost Mode

- **High Integration**

- Power Path Management

- Synchronous Switching MOSFETs

- Integrated Current Sensing

- **Bootstrap Diode**

- Internal Loop Compensation

- Safety

- Battery Temperature Sensing and Charging Safety Timer

- Thermal Regulation and Thermal Shutdown

- Input System Over-Voltage Protection

- **MOSFET Over-Current Protection**

- Charge Status Outputs for LED or Host Processor

- Low Battery Leakage Current and Support Shipping Mode

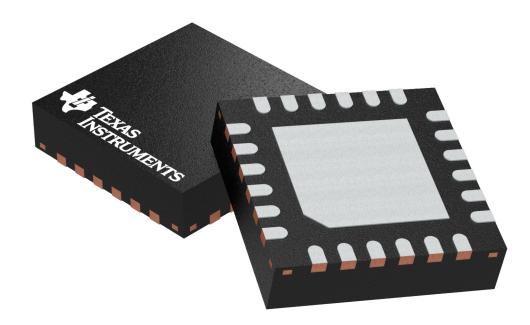

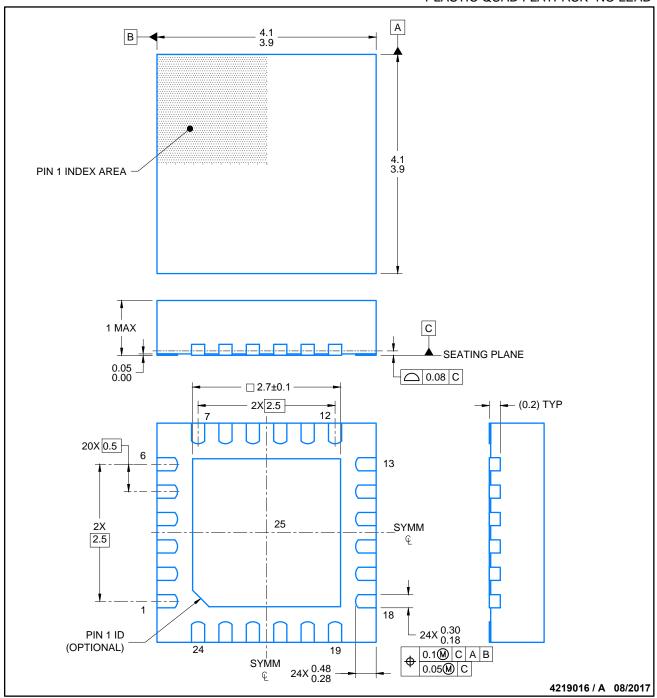

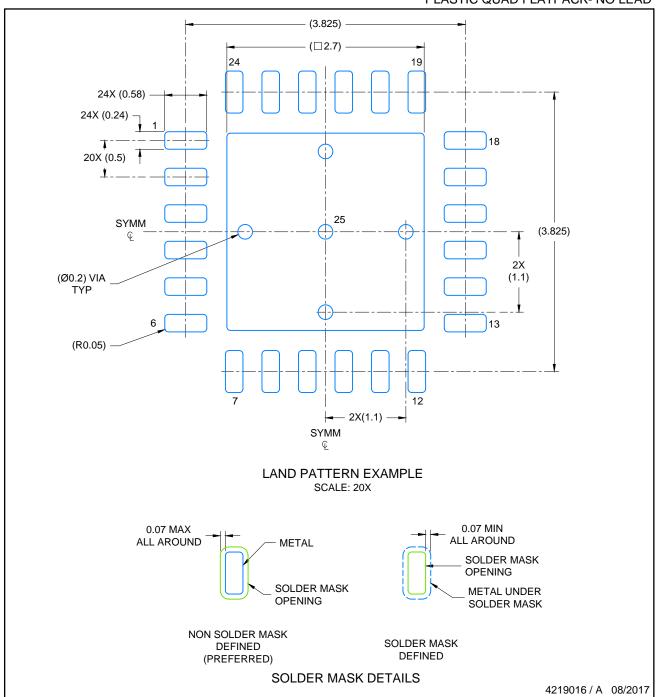

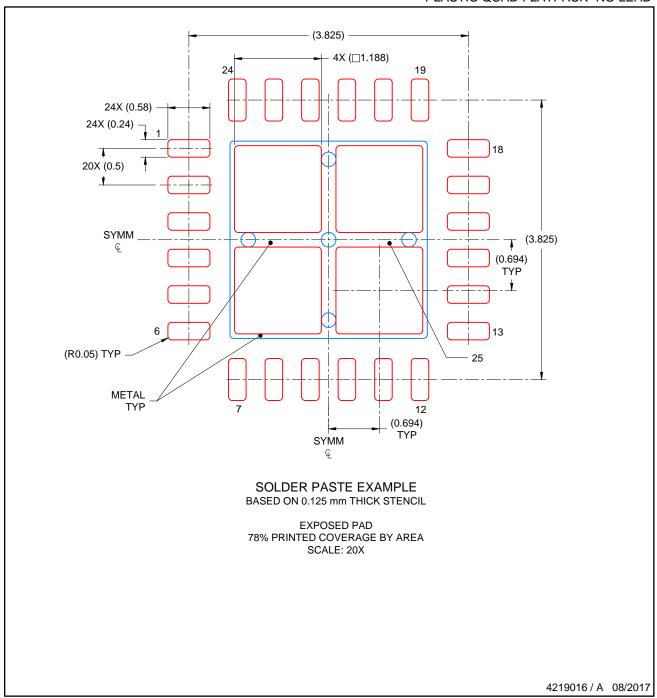

- 4.00 mm x 4.00 mm VQFN-24 Package

# **Applications**

- Tablet PC and Smart Phone

- Portable Audio Speaker

- Portable Media Players

- Internet Devices

# 3 Description

The bq24196 is highly-integrated switch-mode battery charge management and system power path management devices for single cell Li-lon and Lipolymer battery in a wide range of tablet and other portable devices.

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| bq24196     | VQFN (24) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

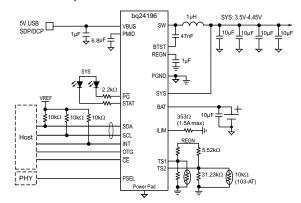

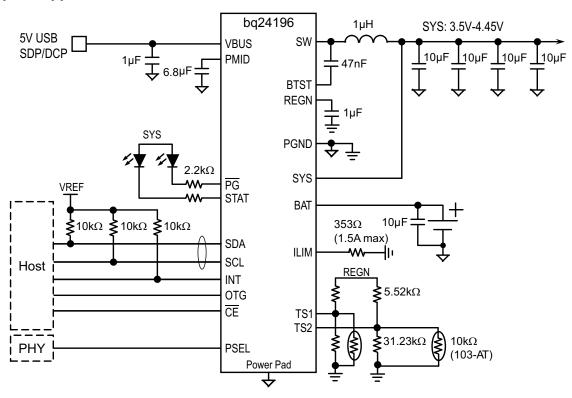

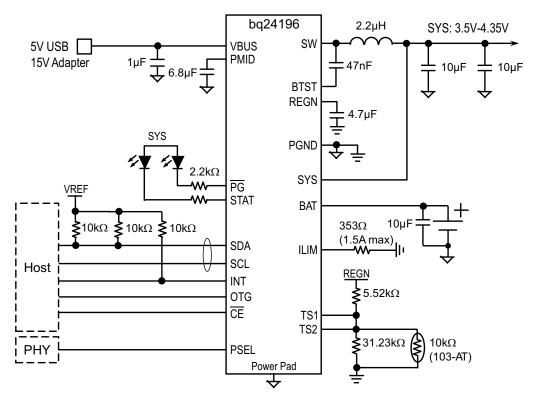

### bg24196 with PSEL from PHY, charging from SDP/DCP, and Two Thermistor Connections

# **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description                          | 13 |

|---|--------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes                      | 25 |

| 3 | Description 1                        |    | 8.5 Register Map                                 | 26 |

| 4 | Revision History2                    | 9  | Application and Implementation                   | 34 |

| 5 | Description (Continued)3             |    | 9.1 Application Information                      | 34 |

| 6 | Pin Configuration and Functions 4    |    | 9.2 Typical Application                          | 34 |

| 7 | Specifications5                      | 10 | Power Supply Recommendations                     | 39 |

| ′ | 7.1 Absolute Maximum Ratings 5       | 11 | Layout                                           | 39 |

|   | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                           |    |

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example                              | 40 |

|   | 7.4 Thermal Information              | 12 | Device and Documentation Support                 | 41 |

|   | 7.5 Electrical Characteristics 6     |    | 12.1 Documentation Support                       |    |

|   | 7.6 Typical Characteristics          |    | 12.2 Trademarks                                  | 41 |

| 8 | Detailed Description                 |    | 12.3 Electrostatic Discharge Caution             | 41 |

| 0 | 8.1 Overview                         |    | 12.4 Glossary                                    |    |

|   | 8.2 Functional Block Diagram         | 13 | Mechanical, Packaging, and Orderable Information | 42 |

# 4 Revision History

# Changes from Original (October 2012) to Revision A

Page

| • | Added Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed BOOT to BTST in Figure 36                                                                                                                                                                                                                                                        | 1    |

| • | Changed V <sub>SLEEPZ</sub> , V <sub>BAT_DPL_HY</sub> , V <sub>BATGD</sub> , I <sub>CHG_20pct</sub> , V <sub>SHORT</sub> , I <sub>ADPT_DPM</sub> , K <sub>ILIM</sub> , V <sub>BTST_REFRESH</sub> in Electrical Characteristics                                                           | 6    |

| • | Added –40°C to 85° to I <sub>BAT</sub> Test Condition                                                                                                                                                                                                                                    | 6    |

| • | Added REG00[6:3] = 0110 (4.36 V) or 1011 (4.76 V) to V <sub>INDPM_REG_ACC</sub> Test Conditions                                                                                                                                                                                          | 8    |

| • | Added a MIN value of 435 to K <sub>ILIM</sub>                                                                                                                                                                                                                                            | 8    |

| • | Deleted T <sub>Junction_REG</sub> MIN and MAX                                                                                                                                                                                                                                            | 8    |

| • | Changed V <sub>OTG_ILIM</sub> to I <sub>OTG_ILIM</sub> and V <sub>OTG_HSZCP</sub> to I <sub>OTG_HSZCP</sub>                                                                                                                                                                              |      |

| • | Deleted V <sub>REGN</sub> , V <sub>VBUS</sub> = 5 V, I <sub>REGN</sub> = 20 mA MAX value                                                                                                                                                                                                 | 9    |

| • | Changed Functional Block Diagram                                                                                                                                                                                                                                                         | . 12 |

| • | Changed REG09[5:4] to REG08[5:4] in Charging Termination section                                                                                                                                                                                                                         |      |

| • | Changed Charging Safety Timer description                                                                                                                                                                                                                                                | . 20 |

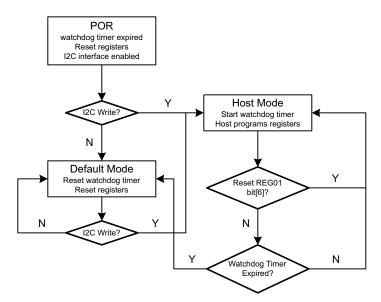

| • | Changed Host Mode and Default Mode description                                                                                                                                                                                                                                           | . 25 |

| • | Changed Charge Current Control Register REG02 Bit 0 description and note                                                                                                                                                                                                                 | . 29 |

| • | Changed Charge Voltage Limit from Default: 4.304 V (110010) to Default: 4.208 V (101100)                                                                                                                                                                                                 | . 30 |

| • | Changed BOOT to BTST in Figure 36                                                                                                                                                                                                                                                        |      |

| • | Changed BOOT to BTST in Figure 37                                                                                                                                                                                                                                                        |      |

# 5 Description (Continued)

Its low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time and extends battery life during discharging phase. The I<sup>2</sup>C serial interface with charging and system settings makes the device a truly flexible solution.

The device supports a wide range of input sources, including standard USB host port, USB charging port and high power DC adapter. The bq24196 takes the result from detection circuit in the system, such as USB PHY device. The bq24196 is compliant with USB 2.0 and USB 3.0 power spec with input current and voltage regulation. Meanwhile, the bq24196 meets USB On-the-Go operation power rating specification by supplying 5 V on VBUS with current limit up to 1.3 A.

The power path management regulates the system slightly above battery voltage but does not drop below 3.5-V minimum system voltage (programmable). With this feature, the system maintains operation even when the battery is completely depleted or removed. When the input current limit or voltage limit is reached, the power path management automatically reduces the charge current to zero. As the system load continues to increase, the power path discharges the battery until the system power requirement is met. This supplement mode operation prevents overloading the input source.

The device initiates and completes a charging cycle without software control. It automatically detects the battery voltage and charges the battery in three phases: pre-conditioning, constant current and constant voltage. At the end of the charging cycle, the charger automatically terminates when the charge current is below a preset limit in the constant voltage phase. When the full battery falls below the recharge threshold, the charger will automatically start another charging cycle.

The device provides various safety features for battery charging and system operation, including negative thermistor monitoring, charging safety timer and over-voltage/over-current protections. The thermal regulation reduces charge current when the junction temperature exceeds 120°C (programmable).

The STAT output reports the charging status and any fault conditions. The  $\overline{PG}$  output in the bq24196 indicates if a good power source is present. The INT immediately notifies the host when a fault occurs.

The bq24196 is available in a 24-pin, 4.00 x 4.00 mm<sup>2</sup> thin VQFN package.

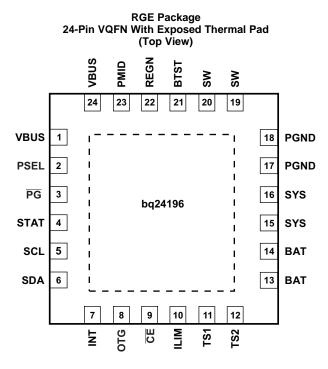

# 6 Pin Configuration and Functions

**Pin Functions**

| P    | PIN      |              |                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                           |  |

|------|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------|--|

| NAME | NUMBER   | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |  |                                                                           |  |

| VBUS | 1,24     | Р            | Charger Input Voltage. The internal n-channel reverse block MOSFET (RBFET) is connected between VBUS and PMID with VBUS on source. Place a 1-µF ceramic capacitor from VBUS to PGND and place it as close as possible to IC. (Refer to Application Information Section for details)                                                                                                     |  |                                                                           |  |

| PSEL | 2        | l<br>Digital | Power source selection input. High indicates a USB host source and Low indicates an adapter source.                                                                                                                                                                                                                                                                                     |  |                                                                           |  |

| PG   | 3        | O<br>Digital | Open drain active low power good indicator. Connect to the pull up rail via 10-k $\Omega$ resistor. LOW indicates a good input source if the input voltage is between UVLO and ACOV, above SLEEP mode threshold, and current limit is above 30 mA.                                                                                                                                      |  |                                                                           |  |

| STAT | 4        | O<br>Digital | Open drain charge status output to indicate various charger operation. Connect to the pull up rail via 10-kΩ. LOW indicates charge in progress. HIGH indicates charge complete or charge disabled. When any fault condition occurs, STAT pin blinks at 1 Hz.                                                                                                                            |  |                                                                           |  |

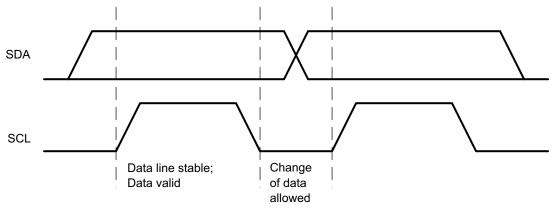

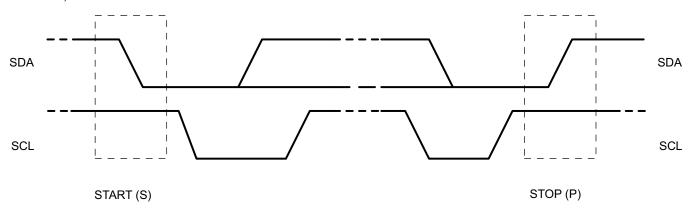

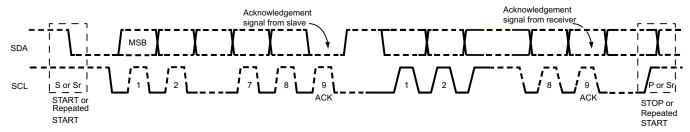

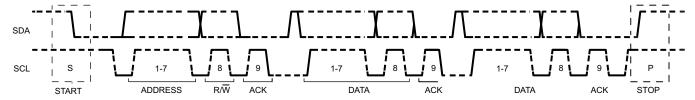

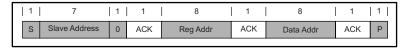

| SCL  | 5        | l<br>Digital | I <sup>2</sup> C Interface clock. Connect SCL to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                               |  |                                                                           |  |

| SDA  | SDA 6 Di |              | $I^2C$ Interface data. Connect SDA to the logic rail through a 10-k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                  |  |                                                                           |  |

| INT  | 7        | O<br>Digital | Open-drain Interrupt Output. Connect the INT to a logic rail via 10-kΩ resistor. The INT pin sends active low, 256-us pulse to host to report charger device status and fault.                                                                                                                                                                                                          |  |                                                                           |  |

|      |          |              | USB current limit selection pin during buck mode, and active high enable pin during boost mode.                                                                                                                                                                                                                                                                                         |  |                                                                           |  |

| OTG  | 8        | l<br>Digital | In buck mode with USB host (PSEL=High), when OTG = High, IIN limit = 500 mA and when OTG = Low, IIN limit = 100 mA.                                                                                                                                                                                                                                                                     |  |                                                                           |  |

|      |          |              |                                                                                                                                                                                                                                                                                                                                                                                         |  | The boost mode is activated when the REG01[5:4] = 10 and OTG pin is High. |  |

| CE   | 9        | l<br>Digital | Active low Charge Enable pin. Battery charging is enabled when REG01[5:4] = 01 and $\overline{\text{CE}}$ pin = Low. $\overline{\text{CE}}$ pin must be pulled high or low.                                                                                                                                                                                                             |  |                                                                           |  |

| ILIM | 10       | I<br>Analog  | ILIM pin sets the maximum input current limit by regulating the ILIM voltage at 1 V. A resistor is connected from ILIM pin to ground to set the maximum limit as $I_{\text{INMAX}} = (1\text{V/R}_{\text{ILIM}}) \times 530$ . The actual input current limit is the lower one set by ILIM and by $I^2\text{C}$ REG00[2:0]. The minimum input current programmed on ILIM pin is 500 mA. |  |                                                                           |  |

| TS1  | 11       | I<br>Analog  | Temperature qualification voltage input #1. Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS1 to GND. Charge suspends when either TS pin is out of range. Recommend 103AT-2 thermistor.                                                                                                                        |  |                                                                           |  |

| TS2  | 12       | I<br>Analog  | Temperature qualification voltage input #2. Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS2 to GND. Charge suspends when either TS pin is out of range. Recommend 103AT-2 thermistor. TS1 and TS2 pin can be connected together for single thermistor application.                                           |  |                                                                           |  |

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

### Pin Functions (continued)

| PI             | PIN                                                                                                            |             | DEGODINTION                                                                                                                                                                                                                                                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NUMBER                                                                                                         | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                 |

| BAT            | 13,14                                                                                                          | Р           | Battery connection point to the positive terminal of the battery pack. The internal BATFET is connected between BAT and SYS. Connect a 10 $\mu$ F closely to the BAT pin.                                                                                                                                                                   |

| SYS            | 15,16                                                                                                          | Р           | System connection point. The internal BATFET is connected between BAT and SYS. When the battery falls below the minimum system voltage, switch-mode converter keeps SYS above the minimum system voltage. (Refer to Application Information Section for inductor and capacitor selection.)                                                  |

| PGND           | GND 17,18 P channel LSFET. On PCB layout, connect directly to ground connection of input and output capacitors |             | Power ground connection for high-current power converter node. Internally, PGND is connected to the source of the n-channel LSFET. On PCB layout, connect directly to ground connection of input and output capacitors of the charger. A single point connection is recommended between power PGND and the analog GND near the IC PGND pin. |

| SW             | 19,20                                                                                                          | O<br>Analog | Switching node connecting to output inductor. Internally SW is connected to the source of the n-channel HSFET and the drain of the n-channel LSFET. Connect the 0.047-µF bootstrap capacitor from SW to BTST.                                                                                                                               |

| BTST           | 21                                                                                                             | Р           | PWM high side driver positive supply. Internally, the BTST is connected to the anode of the boost-strap diode. Connect the 0.047-µF bootstrap capacitor from SW to BTST.                                                                                                                                                                    |

| REGN           | 22                                                                                                             | Р           | PWM low side driver positive supply output. Internally, REGN is connected to the cathode of the boost-strap diode. Connect a 4.7-µF (10-V rating) ceramic capacitor from REGN to analog GND. The capacitor should be placed close to the IC. REGN also serves as bias rail of TS1 and TS2 pins.                                             |

| PMID           | 23                                                                                                             | O<br>Analog | Connected to the drain of the reverse blocking MOSFET and the drain of HSFET. Given the total input capacitance, connect a 1-µF capacitor on VBUS to PGND, and the rest all on PMID to PGND. (Refer to Application Information Section for details)                                                                                         |

| Thermal<br>Pad | -                                                                                                              | Р           | Exposed pad beneath the IC for heat dissipation. Always solder thermal pad to the board, and have vias on the thermal pad plane star-connecting to PGND and ground plane for high-current power converter.                                                                                                                                  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                       |                                                    | MIN   | MAX  | UNIT |

|---------------------------------------|----------------------------------------------------|-------|------|------|

|                                       | VBUS                                               | -2    | 22   | V    |

| Voltage range (with                   | PMID                                               | -0.3  | 22   | V    |

|                                       | STAT, PG                                           | -0.3  | 20   | V    |

|                                       | BTST                                               | -0.3  | 26   | V    |

| Voltage range (with respect to GND)   | SW                                                 | -2    | 20   | V    |

| respect to GND)                       | BAT, SYS (converter not switching)                 | -0.3  | 6    | V    |

|                                       | SDA, SCL, INT, OTG, ILIM, REGN, TS1, TS2, CE, PSEL | -0.3  | 7    | V    |

|                                       | BTST TO SW                                         | -0.3  | -7   | V    |

|                                       | PGND to GND                                        | -0.3  | -0.3 | V    |

| Output sink current                   | INT, STAT, PG                                      |       | 6    | mA   |

| Junction temperature                  |                                                    | –40°C | 150  | °C   |

| Storage temperature, T <sub>stg</sub> |                                                    | -65   | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | 1000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 250   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

|                  |                                          | MIN | MAX                                                     | UNIT |

|------------------|------------------------------------------|-----|---------------------------------------------------------|------|

| V <sub>IN</sub>  | Input voltage                            | 3.9 | 17 <sup>(1)</sup>                                       | V    |

| I <sub>IN</sub>  | Input current                            |     | 3                                                       | Α    |

| I <sub>SYS</sub> | Output current (SYS)                     |     | 2.5                                                     | Α    |

| $V_{BAT}$        | Battery voltage                          |     | 4.4                                                     | V    |

|                  | Fast charging current                    |     | 2.5                                                     | Α    |

| I <sub>BAT</sub> | Discharging current with internal MOSFET |     | 6 (continuous)<br>9 (peak)<br>(up to 1 sec<br>duration) | А    |

| T <sub>A</sub>   | Operating free-air temperature range     | -40 | 85                                                      | °C   |

<sup>(1)</sup> The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BTST or SW pins. A tight layout minimizes switching noise.

### 7.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | bq24196      | LINIT |

|--------------------|----------------------------------------------|--------------|-------|

|                    | I HERMAL METRIC                              | RGE (24 PIN) | UNIT  |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 32.2         |       |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 29.8         |       |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 9.1          | °C/W  |

| $\Psi_{JT}$        | Junction-to-top characterization parameter   | 0.3          | C/VV  |

| ΨЈВ                | Junction-to-board characterization parameter | 9.1          |       |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.2          |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 7.5 Electrical Characteristics

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to 125°C and  $T_J = 25^{\circ}C$  for typical values unless other noted.

|                         | PARAMETER                                    | TEST CONDITIONS                                                                                                     | MIN  | TYP | MAX | UNIT |

|-------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| QUIESCENT C             | CURRENTS                                     |                                                                                                                     |      |     |     |      |

|                         |                                              | $V_{VBUS}$ < $V_{UVLO}$ , VBAT = 4.2 V, leakage between BAT and VBUS                                                |      |     | 5   | μΑ   |

| I <sub>BAT</sub>        | Battery discharge current (BAT, SW, SYS)     | High-Z Mode, or no VBUS, BATFET disabled (REG07[5] = 1), -40°C to 85°C                                              |      | 12  | 20  | μΑ   |

|                         |                                              | High-Z Mode, or no VBUS, REG07[5] = 0, -40°C to 85°C                                                                |      | 32  | 55  | μΑ   |

|                         |                                              | V <sub>VBUS</sub> = 5 V, High-Z mode                                                                                |      | 15  | 30  | μΑ   |

|                         |                                              | V <sub>VBUS</sub> = 17 V, High-Z mode                                                                               |      | 30  | 50  | μΑ   |

| I <sub>VBUS</sub>       | Input supply current (VBUS)                  | $V_{VBUS} > V_{UVLO}$ , $V_{VBUS} > V_{BAT}$ , converter not switching                                              |      | 1.5 | 3   | mA   |

|                         |                                              | $V_{VBUS} > V_{UVLO}$ , $V_{VBUS} > V_{BAT}$ , converter switching, $V_{BAT} = 3.2$ V, $I_{SYS} = 0$ A              |      | 4   |     | mA   |

|                         |                                              | $V_{VBUS} > V_{UVLO}, V_{VBUS} > V_{BAT}, converter$<br>switching, $V_{BAT} = 3.8 \text{ V}, I_{SYS} = 0 \text{ A}$ |      | 15  |     | mA   |

| I <sub>OTGBOOST</sub>   | Battery discharge current in boost mode      | VBAT = 4.2 V, Boost mode, I <sub>VBUS</sub> = 0 A, converter switching                                              |      | 4   |     | mA   |

| VBUS/BAT PC             | WER UP                                       |                                                                                                                     |      |     | •   |      |

| V <sub>VBUS_OP</sub>    | VBUS operating range                         |                                                                                                                     | 3.9  |     | 17  | V    |

| V <sub>VBUS_UVLOZ</sub> | VBUS for active I <sup>2</sup> C, no battery | V <sub>VBUS</sub> rising                                                                                            | 3.6  |     |     | V    |

| V <sub>SLEEP</sub>      | Sleep mode falling threshold                 | V <sub>VBUS</sub> falling, V <sub>VBUS-VBAT</sub>                                                                   | 35   | 80  | 120 | mV   |

| V <sub>SLEEPZ</sub>     | Sleep mode rising threshold                  | V <sub>VBUS</sub> rising, V <sub>VBUS-VBAT</sub>                                                                    | 170  | 250 | 350 | mV   |

| V <sub>ACOV</sub>       | VBUS over-voltage rising threshold           | V <sub>VBUS</sub> rising                                                                                            | 17.4 | 18  |     | V    |

| V <sub>ACOV_HYST</sub>  | VBUS over-voltage falling hysteresis         | V <sub>VBUS</sub> falling                                                                                           |      | 700 |     | mV   |

| $V_{BAT\_UVLOZ}$        | Battery for active I <sup>2</sup> C, no VBUS | V <sub>BAT</sub> rising                                                                                             | 2.3  |     |     | V    |

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to 125°C and  $T_J = 25^{\circ}C$  for typical values unless other noted.

|                           | PARAMETER                                              | TEST CONDITIONS                                                                                    | MIN   | TYP  | MAX  | UNIT |

|---------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|------|------|------|

| V <sub>BAT_DPL</sub>      | Battery depletion threshold                            | V <sub>BAT</sub> falling                                                                           |       | 2.4  | 2.6  | V    |

| V <sub>BAT_DPL_HY</sub>   | Battery depletion rising hysteresis                    | V <sub>BAT</sub> rising                                                                            |       | 170  | 260  | mV   |

| V <sub>VBUSMIN</sub>      | Bad adapter detection threshold                        | V <sub>VBUS</sub> falling                                                                          |       | 3.8  |      | V    |

| I <sub>BADSRC</sub>       | Bad adapter detection current source                   |                                                                                                    |       | 30   |      | mA   |

| t <sub>BADSRC</sub>       | Bad source detection duration                          |                                                                                                    |       | 30   |      | ms   |

| POWER PATH                | MANAGEMENT                                             |                                                                                                    |       |      | ,    |      |

| V <sub>SYS_RANGE</sub>    | Typical system regulation voltage                      | Isys = 0 A, Q4 off, V <sub>BAT</sub> up to 4.2 V,<br>REG01[3:1] = 101, V <sub>SYSMIN</sub> = 3.5 V | 3.5   |      | 4.35 | V    |

| V <sub>SYS_MIN</sub>      | System voltage output                                  | REG01[3:1] = 101, V <sub>SYSMIN</sub> = 3.5 V                                                      | 3.55  | 3.65 |      | V    |

| R <sub>ON(RBFET)</sub>    | Internal top reverse blocking MOSFET on-<br>resistance | Measured between VBUS and PMID                                                                     |       | 23   | 38   | mΩ   |

| D                         | Internal top switching MOSFET on-resistance            | $T_J = -40$ °C to 85°C                                                                             |       | 30   | 38   |      |

| R <sub>ON(HSFET)</sub>    | between PMID and SW                                    | T <sub>J</sub> = -40°C to 125°C                                                                    |       | 30   | 48   | mΩ   |

| 5                         | Internal bottom switching MOSFET on-resistance         | $T_J = -40$ °C to 85°C                                                                             |       | 35   | 48   | _    |

| R <sub>ON(LSFET)</sub>    | between SW and PGND                                    | T <sub>J</sub> = -40°C to 125°C                                                                    |       | 35   | 51   | mΩ   |

| V <sub>FWD</sub>          | BATFET forward voltage in supplement mode              | BAT discharge current 10 mA                                                                        |       | 30   |      | mV   |

| V <sub>SYS BAT</sub>      | SYS/BAT Comparator                                     | V <sub>SYS</sub> falling                                                                           |       | 90   |      | mV   |

| V <sub>BATGD</sub>        | Battery good comparator rising threshold               | V <sub>BAT</sub> rising                                                                            |       | 3.55 |      | V    |

| V <sub>BATGD</sub> HYST   | Battery good comparator falling threshold              | V <sub>BAT</sub> falling                                                                           |       | 100  |      | mV   |

| BATTERY CHA               | ARGER                                                  |                                                                                                    |       |      | ,    |      |

| V <sub>BAT_REG_ACC</sub>  | Charge voltage regulation accuracy                     | V <sub>BAT</sub> = 4.208 V                                                                         | -0.5% |      | 0.5% |      |

|                           |                                                        | V <sub>BAT</sub> = 3.8 V, I <sub>CHG</sub> = 1792 mA, T <sub>J</sub> = 25°C                        | -4%   |      | 4%   |      |

| I <sub>ICHG_REG_ACC</sub> | Fast charge current regulation accuracy                | $V_{BAT} = 3.8 \text{ V}, I_{CHG} = 1792 \text{ mA}, T_{J} = -20^{\circ}\text{C to}$ 125°C         | -7%   |      | 7%   |      |

| I <sub>CHG_20pct</sub>    | Charge current with 20% option on                      | V <sub>BAT</sub> = 3.1 V, I <sub>CHG</sub> = 104 mA, REG02 = 03                                    | 75    | 100  | 150  | mA   |

| V <sub>BATLOWV</sub>      | Battery LOWV falling threshold                         | Fast charge to precharge, REG04[1] = 1                                                             | 2.6   | 2.8  | 2.9  | V    |

| V <sub>BATLOWV_HYST</sub> | Battery LOWV rising threshold                          | Precharge to fast charge, REG04[1] = 1                                                             | 2.8   | 3.0  | 3.1  | V    |

| I <sub>PRECHG_ACC</sub>   | Precharge current regulation accuracy                  | VBAT = 2.6 V, I <sub>CHG</sub> = 256 mA                                                            | -20%  |      | 20%  |      |

| I <sub>TERM_ACC</sub>     | Termination current accuracy                           | I <sub>TERM</sub> = 256 mA, I <sub>CHG</sub> = 960 mA                                              | -20%  |      | 20%  |      |

| V <sub>SHORT</sub>        | Battery Short Voltage                                  | VBAT falling                                                                                       |       | 2.0  |      | V    |

| V <sub>SHORT_HYST</sub>   | Battery Short Voltage hysteresis                       | VBAT rising                                                                                        |       | 200  |      | mV   |

| I <sub>SHORT</sub>        | Battery short current                                  | VBAT < 2.2V                                                                                        |       | 100  |      | mA   |

| V <sub>RECHG</sub>        | Recharge threshold below VBAT_REG                      | VBAT falling, REG04[0] = 0                                                                         |       | 100  |      | mV   |

| t <sub>RECHG</sub>        | Recharge deglitch time                                 | VBAT falling, REG04[0] = 0                                                                         |       | 20   |      | ms   |

| D                         | OVO DAT MODEET ' :                                     | T <sub>J</sub> = 25°C                                                                              |       | 12   | 15   | - 0  |

| R <sub>ON_BATFET</sub>    | SYS-BAT MOSFET on-resistance                           | $T_1 = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$                                        |       | 12   | 20   | mΩ   |

# **Electrical Characteristics (continued)**

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to 125°C and  $T_J = 25^{\circ}C$  for typical values unless other noted.

|                            | PARAMETER                                                              | TEST CONDITIONS                                                    | MIN   | TYP        | MAX   | UNIT        |

|----------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|-------|------------|-------|-------------|

| INPUT VOLTAG               | SE/CURRENT REGULATION                                                  |                                                                    |       |            |       |             |

| V <sub>INDPM</sub> REG ACC | Input voltage regulation accuracy                                      | REG00[6:3] = 0110 (4.36 V) or 1011 (4.76 V)                        | -2%   |            | 2%    |             |

| * INDFW_REG_ACC            |                                                                        | USB100                                                             | 85    |            | 100   | mA          |

|                            | 11001                                                                  | USB150                                                             | 125   |            | 150   | mA          |

| I <sub>USB_DPM</sub>       | USB Input current regulation limit, VBUS = 5 V, current pulled from SW |                                                                    |       |            |       |             |

|                            | ounces passed tress of                                                 | USB500                                                             | 440   |            | 500   | mA          |

|                            |                                                                        | USB900                                                             | 750   |            | 900   | mA          |

| I <sub>ADPT_DPM</sub>      | Input current regulation accuracy                                      |                                                                    | 1.35  | 1.5        | 1.65  | Α           |

| I <sub>IN_START</sub>      | Input current limit during system start up                             | VSYS < 2.2 V                                                       |       | 100        |       | mA          |

| K <sub>ILIM</sub>          | $I_{IN} = K_{ILIM}/R_{ILIM}$                                           | IINDPM = 1.5 A                                                     | 435   | 485        | 530   | ΑχΩ         |

| BAT OVER-VOI               | LTAGE PROTECTION                                                       |                                                                    |       |            |       |             |

| V <sub>BATOVP</sub>        | Battery over-voltage threshold                                         | $V_{BAT}$ rising, as percentage of $V_{BAT\_REG}$                  |       | 104%       |       |             |

| V <sub>BATOVP_HYST</sub>   | Battery over-voltage hysteresis                                        | V <sub>BAT</sub> falling, as percentage of V <sub>BAT_REG</sub>    |       | 2%         |       |             |

| t <sub>BATOVP</sub>        | Battery over-voltage deglitch time to disable charge                   |                                                                    |       | 1          |       | μs          |

| THERMAL REG                | GULATION AND THERMAL SHUTDOWN                                          |                                                                    |       |            |       |             |

| T <sub>Junction_REG</sub>  | Junction temperature regulation accuracy                               | REG06[1:0] = 11                                                    |       | 120        |       | °C          |

|                            | Thermal shutdown rising temperature                                    | Temperature increasing                                             |       | 160        |       | •C          |

| T <sub>SHUT</sub>          | 0 1                                                                    | remperature increasing                                             |       | 30         |       | °C          |

| T <sub>SHUT_HYS</sub>      | Thermal shutdown hysteresis                                            |                                                                    |       |            |       |             |

|                            | Thermal shutdown rising deglitch                                       | Temperature increasing delay                                       |       | 1          |       | ms          |

|                            | Thermal shutdown falling deglitch                                      | Temperature decreasing delay                                       |       | 1          |       | ms          |

| COLD/HOT THE               | ERMISTER COMPARATOR                                                    |                                                                    | -     |            |       |             |

| $V_{LTF}$                  | Cold temperature threshold, TS pin voltage rising threshold            | Charger suspends charge. As percentage to $V_{\text{REGN}}$        | 73%   | 73.5<br>%  | 74%   |             |

| $V_{LTF\_HYS}$             | Cold temperature hysteresis, TS pin voltage falling                    | As percentage to V <sub>REGN</sub>                                 | 0.2%  | 0.4%       | 0.6%  |             |

| V <sub>HTF</sub>           | Hot temperature TS pin voltage threshold                               | As percentage to V <sub>REGN</sub>                                 | 46.6% | 47.2<br>%  | 48.8% |             |

| V <sub>TCO</sub>           | Cut-off temperature TS pin voltage falling threshold                   | As percentage to V <sub>REGN</sub>                                 | 44.2% | 44.7<br>%  | 45.2% |             |

|                            | Deglitch time for temperature out of range detection                   | $V_{TS} > V_{LTF}$ , or $V_{TS} < V_{TCO}$ , or $V_{TS} < V_{HTF}$ |       | 10         |       | ms          |

| CHARGE OVER                | R-CURRENT COMPARATOR                                                   |                                                                    |       |            |       |             |

| I <sub>HSFET OCP</sub>     | HSFET over-current threshold                                           |                                                                    | 5.3   | 7          |       | Α           |

| I <sub>BATFET OCP</sub>    | System over load threshold                                             |                                                                    | 9     |            |       | Α           |

| =:::                       | ER-CURRENT COMPARATOR (CYCLE-BY-CYCLE)                                 |                                                                    |       |            |       |             |

| V <sub>LSFET UCP</sub>     | LSFET charge under-current falling threshold                           | From sync mode to non-sync mode                                    |       | 100        |       | mA          |

| PWM OPERATI                |                                                                        |                                                                    |       | 100        |       | 111/1       |

|                            |                                                                        |                                                                    | 1200  | 1500       | 1700  | <b>\</b> □¬ |

| F <sub>SW</sub>            | PWM Switching frequency, and digital clock                             |                                                                    | 1300  | 1500       | 1700  | kHz         |

| D <sub>MAX</sub>           | Maximum PWM duty cycle                                                 | VBTST-VSW when LSFET refresh pulse is                              |       | 97%<br>3.6 |       |             |

| $V_{BTST\_REFRESH}$        | Bootstrap refresh comparator threshold                                 | requested, VBUS = 5 V  VBTST-VSW when LSFET refresh pulse is       |       | 4.5        |       | V           |

|                            |                                                                        | requested, VBUS > 6 V                                              |       |            |       |             |

| BOOST MODE                 |                                                                        |                                                                    |       |            | 1     |             |

| $V_{OTG\_REG}$             | OTG output voltage                                                     | I(VBUS) = 0                                                        |       | 5.00       |       | V           |

| V <sub>OTG_REG_ACC</sub>   | OTG output voltage accuracy                                            | I(VBUS) = 0                                                        | -2%   |            | 2%    |             |

| I <sub>OTG</sub>           | OTG mode output current                                                | REG01[0] = 0<br>REG01[0] = 1                                       | 0.5   |            |       | A<br>A      |

| V                          | OTG over veltage threshold                                             | REGUI[0] = 1                                                       | 1.3   | F 2        | E F   |             |

| V <sub>OTG_OVP</sub>       | OTG over-voltage threshold                                             |                                                                    | 2.5   | 5.3        | 5.5   | V           |

| I <sub>OTG_ILIM</sub>      | LSFET cycle-by-cycle current limit                                     |                                                                    | 3.2   | 4.6        |       | Α           |

| I <sub>OTG_HSZCP</sub>     | HSFET under current falling threshold                                  |                                                                    |       | 100        |       | mΑ          |

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

$V_{VBUS\_UVLOZ} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to 125°C and  $T_J = 25^{\circ}C$  for typical values unless other noted.

| 1.8  | Α   |

|------|-----|

|      | A   |

|      |     |

|      |     |

| 6.4  | V   |

|      | V   |

|      | mA  |

|      |     |

| 0.4  | V   |

|      | V   |

| 0.4  | V   |

| 1    | μΑ  |

|      |     |

|      | V   |

| 0.4  | V   |

| 0.4  | V   |

| 1    | μA  |

| 400  | kHz |

|      |     |

| 50   | kHz |

| 1700 | kHz |

|      | sec |

|      | 50  |

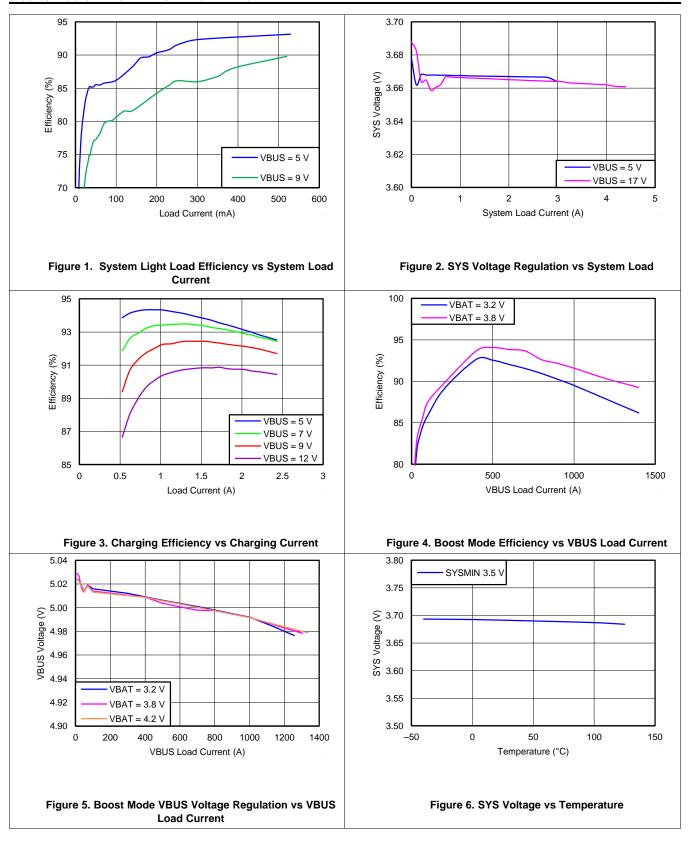

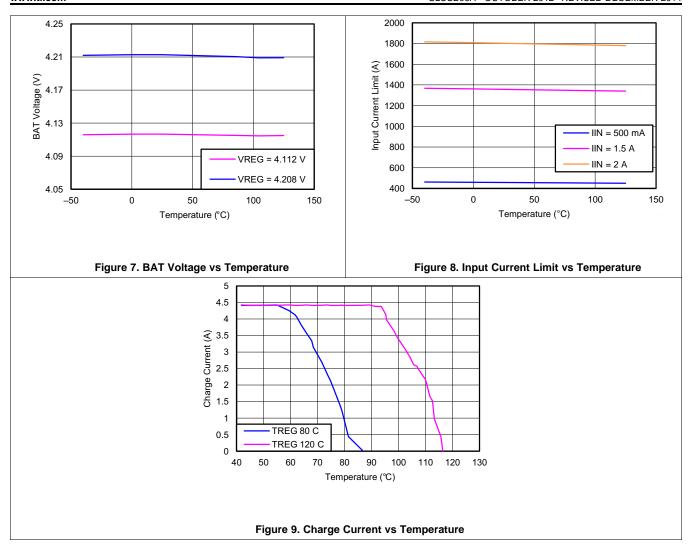

# 7.6 Typical Characteristics

Table 1. Table of Figures

|                                                         | FIGURE NO. |

|---------------------------------------------------------|------------|

| System Light Load Efficiency vs System Load Current     | Figure 1   |

| SYS Voltage Regulation vs System Load                   | Figure 2   |

| Charging Efficiency vs Charging Current                 | Figure 3   |

| Boost Mode Efficiency vs VBUS Load Current              | Figure 4   |

| Boost Mode VBUS Voltage Regulation vs VBUS Load Current | Figure 5   |

| SYS Voltage vs Temperature                              | Figure 6   |

| BAT Voltage vs Temperature                              | Figure 7   |

| Input Current Limit vs Temperature                      | Figure 8   |

| Charge Current vs Temperature                           | Figure 9   |

# 8 Detailed Description

#### 8.1 Overview

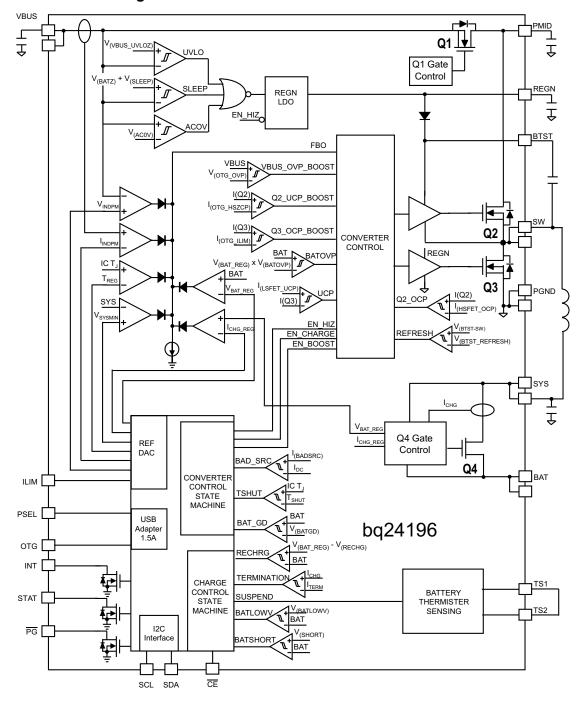

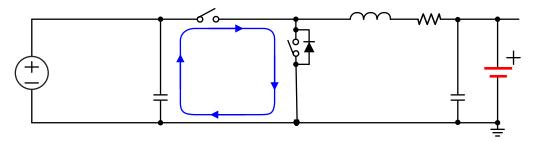

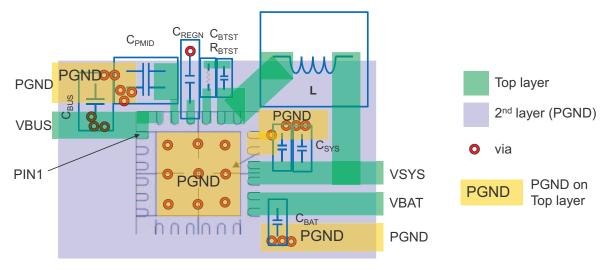

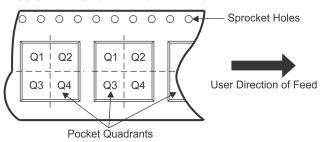

The bq24196 is an  $I^2C$  controlled power path management device and a single cell Li-lon battery charger. It integrates the input reverse-blocking FET (RBFET, Q1), high-side switching FET (HSFET, Q2), low-side switching FET (LSFET, Q3), and BATFET (Q4) between system and battery. The device also integrates the bootstrap diode for the high-side gate drive.

# 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Device Power Up

### 8.3.1.1 Power-On-Reset (POR)

The internal bias circuits are powered from the higher voltage of VBUS and BAT. When VBUS or VBAT rises above UVLOZ, the sleep comparator, battery depletion comparator and BATFET driver are active. I<sup>2</sup>C interface is ready for communication and all the registers are reset to default value. The host can access all the registers after POR.

#### 8.3.1.2 Power Up from Battery without DC Source

If only battery is present and the voltage is above depletion threshold (V<sub>BAT\_DEPL</sub>), the BATFET turns on and connects battery to system. The REGN LDO stays off to minimize the quiescent current. The low R<sub>DSON</sub> in BATFET and the low quiescent current on BAT minimize the conduction loss and maximize the battery run time. The device always monitors the discharge current through BATFET. When the system is overloaded or shorted, the device will immediately turn off BATFET and keep BATFET off until the input source plugs in again.

#### 8.3.1.2.1 BATFET Turn Off

The BATFET can be forced off by the host through I<sup>2</sup>C REG07[5]. This bit allows the user to independently turn off the BATFET when the battery condition becomes abnormal during charging. When BATFET is off, there is no path to charge or discharge the battery.

When battery is not attached, the BATFET should be turned off by setting REG07[5] to 1 to disable charging and supplement mode.

#### 8.3.1.2.2 Shipping Mode

When end equipment is assembled, the system is connected to battery through BATFET. There will be a small leakage current to discharge the battery even when the system is powered off. In order to extend the battery life during shipping and storage, the device can turn off BATFET so that the system voltage is zero to minimize the leakage.

In order to keep BATFET off during shipping mode, the host has to disable the watchdog timer (REG05[5:4] = 00) and disable BATFET (REG07[5] = 1) at the same time.

Once the BATFET is disabled, the BATFET can be turned on by plugging in adapter.

### 8.3.1.3 Power Up from DC Source

When the DC source plugs in, the bq24196 checks the input source voltage to turn on REGN LDO and all the bias circuits. It also checks the input current limit before starts the buck converter.

#### 8.3.1.3.1 REGN LDO

The REGN LDO supplies internal bias circuits as well as the HSFET and LSFET gate drive. The LDO also provides bias rail to TS1/TS2 external resistors. The pull-up rail of STAT and  $\overline{PG}$  can be connected to REGN as well.

The REGN is enabled when all the conditions are valid.

- 1. VBUS above UVLOZ

- 2. VBUS above battery + V<sub>SLEEPZ</sub> in buck mode or VBUS below battery + V<sub>SLEEPZ</sub> in boost mode

- 3. After typical 220ms delay (100ms minimum) is complete

If one of the above conditions is not valid, the device is in high impedance mode (HIZ) with REGN LDO off. The device draws less than 50  $\mu$ A from VBUS during HIZ state. The battery powers up the system when the device is in HIZ.

#### 8.3.1.3.2 Input Source Qualification

After REGN LDO powers up, the bq24196 checks the current capability of the input source. The input source has to meet the following requirements to start the buck converter.

### **Feature Description (continued)**

- 1. VBUS voltage below 18 V (not in ACOV)

- 2. VBUS voltage above 3.8 V when pulling 30 mA (poor source detection)

Once the input source passes all the conditions above, the status register REG08[2] goes high and the  $\overline{PG}$  pin goes low. An INT is asserted to the host.

If the device fails the poor source detection, it will repeat the detection every 2 seconds.

#### 8.3.1.3.3 Input Current Limit Detection

The USB ports on personal computers are convenient charging source for portable devices (PDs). If the portable device is attached to a USB host, the USB specification requires the portable device to draw limited current (100 mA/500 mA in USB 2.0, and 150 mA/900 mA in USB 3.0). If the portable device is attached to a charging port, it is allowed to draw up to 1.5 A.

After the PG is LOW or REG08[2] goes HIGH, the charger device always runs input current limit detection when a DC source plugs in unless the charger is in HIZ during host mode.

The bg24196 sets input current limit through PSEL and OTG pins.

After the input current limit detection is done, the host can write to REG00[2:0] to change the input current limit.

#### 8.3.1.3.4 PSEL/OTG Pins Set Input Current Limit

The bq24196 has PSEL. It directly takes the USB PHY device output to decide whether the input is USB host or charging port.

| PSEL | OTG  | INPUT CURRENT LIMIT | REG08[7:6] |  |  |  |  |  |

|------|------|---------------------|------------|--|--|--|--|--|

| HIGH | LOW  | 100 mA              | 01         |  |  |  |  |  |

| HIGH | HIGH | 500 mA              | 01         |  |  |  |  |  |

| LOW  | _    | 3 A                 | 10         |  |  |  |  |  |

Table 2. bq24196 Input Current Limit Detection

#### 8.3.1.3.5 HIZ State wth 100mA USB Host

In battery charging spec, the good battery threshold is the minimum charge level of a battery to power up the portable device successfully. When the input source is 100-mA USB host, and the battery is above bat-good threshold ( $V_{BATGD}$ ), the device follows battery charging spec and enters high impedance state (HIZ). In HIZ state, the device is in the lowest quiescent state with REGN LDO and the bias circuits off. The charger device sets REG00[7] to 1, and the VBUS current during HIZ state will be less than 30  $\mu$ A. The system is supplied by the battery.

Once the charger device enters HIZ state in host mode, it stays in HIZ until the host writes REG00[7] = 0. When the processor host wakes up, it is recommended to first check if the charger is in HIZ state.

In default mode, the charger IC will reset REG00[7] back to 0 when input source is removed. When another source plugs in, the charger IC will run detection again, and update the input current limit.

# 8.3.1.3.6 Force Input Current Limit Detection

The host can force the charger device to run input current limit detection by setting REG07[7] = 1. After the detection is complete, REG07[7] will return to 0 by itself.

### 8.3.1.4 Converter Power-Up

After the input current limit is set, the converter is enabled and the HSFET and LSFET start switching. If battery charging is disabled, BATFET turns off. Otherwise, BATFET stays on to charge the battery.

The bq24196 provides soft-start when ramp up the system rail. When the system rail is below 2.2 V, the input current limit is forced to 100 mA. After the system rises above 2.2 V, the charger device sets the input current limit set by the lower value between register and ILIM pin.

As a battery charger, the bq24196 deploys a 1.5-MHz step-down switching regulator. The fixed frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current and temperature, simplifying output filter design.

A type III compensation network allows using ceramic capacitors at the output of the converter. An internal saw-tooth ramp is compared to the internal error control signal to vary the duty cycle of the converter. The ramp height is proportional to the PMID voltage to cancel out any loop gain variation due to a change in input voltage.

In order to improve light-load efficiency, the device switches to PFM control at light load when battery is below minimum system voltage setting or charging is disabled. During the PFM operation, the switching duty cycle is set by the ratio of SYS and VBUS.

### 8.3.1.5 Boost Mode Operation from Battery

The bq24196 supports boost converter operation to deliver power from the battery to other portable devices through USB port. The boost mode output current rating meets the USB On-The-Go 500-mA output requirement. The maximum output current is 1.3 A. The boost operation can be enabled if the following conditions are valid:

- 1. BAT above BATLOWV threshold (V<sub>BATLOWV</sub> set by REG04[1])

- 2. VBUS less than BAT+V<sub>SLEEP</sub> (in sleep mode)

- 3. Boost mode operation is enabled (OTG pin HIGH and REG01[5:4] = 10)

- 4. After 220-ms delay from boost mode enable

In boost mode, the bq24196 employs a 1.5-MHz step-up switching regulator. Similar to buck operation, the device switches from PWM operation to PFM operation at light load to improve efficiency.

During boost mode, the status register REG08[7:6] is set to 11, the VBUS output is 5 V and the output current can reach up to 500 mA or 1.3 A, selected via I<sup>2</sup>C (REG01[0]).

Any fault during boost operation, including VBUS over-voltage or over-current, sets the fault register REG09[6] to 1 and an INT is asserted.

#### 8.3.2 Power Path Management

The bq24196 accommodates a wide range of input sources from USB, wall adapter, to car battery. The device provides automatic power path selection to supply the system (SYS) from input source (VBUS), battery (BAT), or both.

#### 8.3.2.1 Narrow VDC Architecture

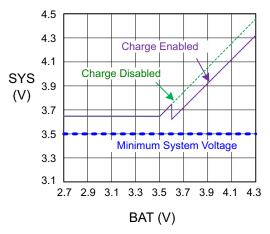

The device deploys Narrow VDC architecture (NVDC) with BATFET separating system from battery. The minimum system voltage is set by REG01[3:1]. Even with a fully depleted battery, the system is regulated above the minimum system voltage (default 3.5 V).

When the battery is below minimum system voltage setting, the BATFET operates in linear mode (LDO mode), and the system is 150 mV above the minimum system voltage setting. As the battery voltage rises above the minimum system voltage, BATFET is fully on and the voltage difference between the system and battery is the  $V_{DS}$  of BATFET.

When the battery charging is disabled or terminated, the system is always regulated at 150 mV above the minimum system voltage setting. The status register REG08[0] goes high when the system is in minimum system voltage regulation.

Figure 10. V(SYS) vs V(BAT)

### 8.3.2.2 Dynamic Power Management

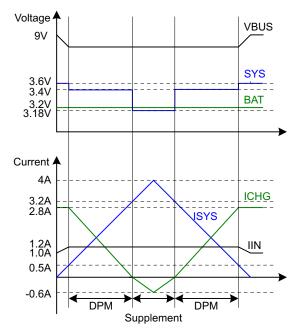

To meet maximum current limit in USB spec and avoid over loading the adapter, the bq24196 features Dynamic Power Management (DPM), which continuously monitors the input current and input voltage.

When input source is over-loaded, either the current exceeds the input current limit (REG00[2:0]) or the voltage falls below the input voltage limit (REG00[6:3]). The device then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit.

When the charge current is reduced to zero, but the input source is still overloaded, the system voltage starts to drop. Once the system voltage falls below the battery voltage, the device automatically enters the supplement mode where the BATFET turns on and battery starts discharging so that the system is supported from both the input source and battery.

During DPM mode (either VINDPM or IINDPM), the status register REG08[3] will go high.

Figure 11 shows the DPM response with 9-V/1.2-A adapter, 3.2-V battery, 2.8-A charge current and 3.4-V minimum system voltage setting.

Figure 11. DPM Response

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

#### 8.3.2.3 Supplement Mode

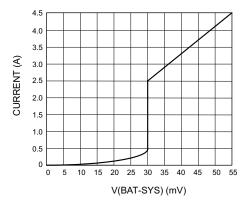

When the system voltage falls below the battery voltage, the BATFET turns on and the BATFET gate is regulated the gate drive of BATFET so that the minimum BATFET  $V_{DS}$  stays at 30 mV when the current is low. This prevents oscillation from entering and exiting the supplement mode. As the discharge current increases, the BATFET gate is regulated with a higher voltage to reduce  $R_{DSON}$  until the BATFET is in full conduction. At this point onwards, the BATFET  $V_{DS}$  linearly increases with discharge current. Figure 12 shows the V-I curve of the BATFET gate regulation operation. BATFET turns off to exit supplement mode when the battery is below battery depletion threshold.

Figure 12. BATFET V-I Curve

#### 8.3.3 Battery Charging Management

The bq24196 charges 1-cell Li-Ion battery with up to 2.5A charge current for high capacity tablet battery. The 12- $m\Omega$  BATFET improves charging efficiency and minimizes the voltage drop during discharging.

#### 8.3.3.1 Autonomous Charging Cycle

With battery charging enabled at POR (REG01[5:4] = 01), the bq24196 can complete a charging cycle without host involvement. The device default charging parameters are listed in .

| DEFAULT MODE        | bq24196  |

|---------------------|----------|

| Charging voltage    | 4.208 V  |

| Charging current    | 2.048 A  |

| Pre-charge current  | 256 mA   |

| Termination current | 256 mA   |

| Temperature profile | Hot/Cold |

| Safety timer        | 8 hours  |

**Table 3. Charging Parameter Default Setting**

A new charge cycle starts when the following conditions are valid:

- Converter starts

- Battery charging is enabled by I<sup>2</sup>C register bit (REG01[5:4]) = 01 and CE is low

- No thermistor fault on TS1 and TS2

- · No safety timer fault

- BATFET is not forced to turn off (REG07[5])

The charger device automatically terminates the charging cycle when the charging current is below termination threshold and charge voltage is above recharge threshold. When a full battery voltage is discharged below recharge threshold (REG04[0]), the bq24196 automatically starts another charging cycle.

The STAT output indicates the charging status of charging (LOW), charging complete or charge disable (HIGH) or charging fault (Blinking). The status register REG08[5:4] indicates the different charging phases: 00-charging disable, 01-precharge, 10-fast charge (constant current) and constant voltage mode, 11-charging done. Once a charging cycle is complete, an INT is asserted to notify the host.

Copyright © 2012–2014, Texas Instruments Incorporated

The host can always control the charging operation and optimize the charging parameters by writing to the registers through I<sup>2</sup>C.

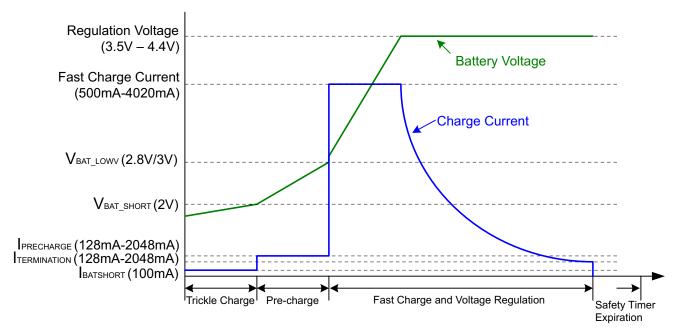

# 8.3.3.2 Battery Charging Profile

The device charges the battery in three phases: preconditioning, constant current and constant voltage. At the beginning of a charging cycle, the device checks the battery voltage and applies current.

**Table 4. Charging Current Setting**

| VBAT      | CHARGING CURRENT | REG DEFAULT SETTING | REG08[5:4] |

|-----------|------------------|---------------------|------------|

| < 2 V     | 100 mA           | -                   | 01         |

| 2 V - 3 V | REG03[7:4]       | 256 mA              | 01         |

| > 3 V     | REG02[7:2]       | 2048 mA             | 10         |

If the charger device is in DPM regulation or thermal regulation during charging, the actual charging current will be less than the programmed value. In this case, termination is temporarily disabled and the charging safety timer is counted at half the clock rate.

Figure 13. Battery Charging Profile

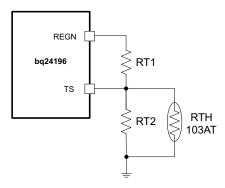

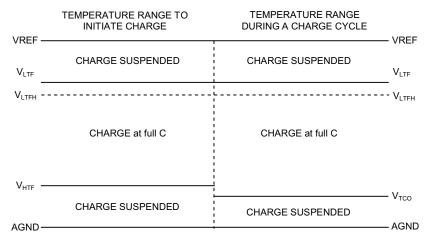

#### 8.3.3.3 Thermistor Cold/Hot Temperature Window

The bq24196 continuously monitors battery temperature by measuring the voltage between the TS pins and ground, typically determined by a negative temperature coefficient thermistor and an external voltage divider. The device compares this voltage against its internal thresholds to determine if charging is allowed. To initiate a charge cycle, the battery temperature must be within the  $V_{LTF}$  to  $V_{HTF}$  thresholds. During the charge cycle the battery temperature must be within the  $V_{LTF}$  to  $V_{HTF}$  to vertice suspends charging and waits until the battery temperature is within the  $V_{LTF}$  to  $V_{HTF}$  range.

Figure 14. TS Resistor Network

When the TS fault occurs, the fault register REG09[2:0] indicates the actual condition on each TS pin and an INT is asserted to the host. The STAT pin indicates the fault when charging is suspended.

Figure 15. TS Pin Thermistor Sense Thresholds

Assuming a 103AT NTC thermistor is used on the battery pack, the value RT1 and RT2 can be determined by using the following equations:

$$RT2 = \frac{V_{VREF} \times RTH_{COLD} \times RTH_{HOT} \times \left(\frac{1}{V_{LTF}} - \frac{1}{V_{TCO}}\right)}{RTH_{HOT} \times \left(\frac{V_{VREF}}{V_{TCO}} - 1\right) - RTH_{COLD} \times \left(\frac{V_{VREF}}{V_{LTF}} - 1\right)}$$

$$RT1 = \frac{\frac{V_{VREF}}{V_{LTF}} - 1}{\frac{1}{RT2} + \frac{1}{RTH_{COLD}}}$$

(1)

Select 0°C to 45°C range for Li-ion or Li-polymer battery,

$RTH_{COLD} = 27.28 \text{ k}\Omega$

$RTH_{HOT} = 4.911 \text{ k}\Omega$

RT1 =  $5.52 \text{ k}\Omega$

$RT2 = 31.23 \text{ k}\Omega$

Copyright © 2012-2014, Texas Instruments Incorporated

#### 8.3.3.4 Charging Termination

The bq24196 terminates a charge cycle when the battery voltage is above recharge threshold, and the current is below termination current. After the charging cycle is complete, the BATFET turns off. The converter keeps running to power the system, and BATFET can turn back on to engage supplement mode.

When termination occurs, the status register REG08[5:4] is 11, and an INT is asserted to the host. Termination is temporarily disabled if the charger device is in input current/voltage regulation or thermal regulation. Termination can be disabled by writing 0 to REG05[7].

#### 8.3.3.4.1 Termination when REG02[0] = 1

When REG02[0] is HIGH to reduce the charging current by 80%, the charging current could be less than the termination current. The charger device termination function should be disabled. When the battery is charged to fully capacity, the host disables charging through  $\overline{CE}$  pin or REG01[5:4].

#### 8.3.3.4.2 Termination when REG05[6] = 1

Usually the STAT bit indicates charging complete when the charging current falls below termination threshold. Write REG05[6] = 1 to enable an early "charge done" indication on STAT pin. The STAT pin goes high when the charge current reduces below 800 mA. The charging cycle is still on-going until the current falls below the termination threshold.

### 8.3.3.5 Charging Safety Timer

The bg24196 has safety timer to prevent extended charging cycle due to abnormal battery conditions.

In default mode, the device keeps charging the battery with 5-hour fast charging safety timer regardless of REG05[2:1] default value. At the end of the 5 hours, the EN\_HIZ (REG00[7]) is set to signal the buck converter stops and the system load is supplied by the battery. The EN\_HIZ bit can be cleared to restart the buck converter.

In host mode, the device keeps charging the battery until the fast charging safety timer expired. The duration of safety timer can be set by the REG05[2:1] bits (default = 8 hours). At the end of safety timer, the EN\_HIZ (REG00[7]) is cleared to signal the buck converter continues to operation to supply system load.

The safety timer is 1 hour when the battery is below BATLOWV threshold. The user can program fast charge safety timer through I<sup>2</sup>C (REG05[2:1]). When safety timer expires, the fault register REG09[5:4] goes 11 and an INT is asserted to the host. The safety timer feature can be disabled via I2C (REG05[3]).

The following actions restart the safety timer:

- · At the beginning of a new charging cycle

- Toggle the CE pin HIGH to LOW to HIGH (charge enable)

- Write REG01[5:4] from 00 to 01 (charge enable)

- Write REG05[3] from 0 to 1 (safety timer enable)

During input voltage/current regulation or thermal regulation, or when FORCE\_20PCT (REG02[0]) bit is set, the safety timer counts at half clock rate since the actual charge current is likely to be below the register setting. For example, if the charger is in input current regulation (IINDPM) throughout the whole charging cycle, and the safety time is set to 5 hours, the safety timer will expire in 10 hours. This feature can be disabled by writing 0 to REG07[6].

It is recommended to disable safety timer first by clearing REG05[3] bit before safety timer configuration is changed. The safety timer should be re-enabled by setting REG05[3] bit.

#### 8.3.3.6 USB Timer when Charging from USB100mA Source

The total charging time in default mode from USB100-mA source is limited by a 45-min max timer. At the end of the timer, the device stops the converter and goes to HIZ.

### 8.3.4 Status Outputs (PG, STAT, and INT)

### 8.3.4.1 Power Good Indicator (PG)

In bg24196, PG goes LOW to indicate a good input source when:

- 1. VBUS above UVLO

- 2. VBUS above battery (not in sleep)

- 3. VBUS below ACOV threshold

- 4. VBUS above 3.8 V when 30-mA current is applied (not a poor source)

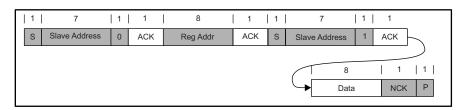

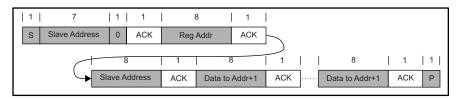

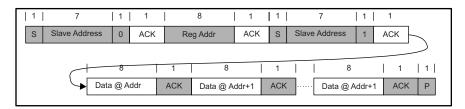

### 8.3.4.2 Charging Status Indicator (STAT)