# 315MHz/390MHz Dual-Frequency ASK Transmitter

#### **General Description**

The MAX7058 UHF transmitter alternately transmits ASK/OOK data at 315MHz or 390MHz using a single crystal. The MAX7058 has internal tuning capacitors at the output of the power amplifier that can be programmed for matching to the antenna or load. The MAX7058 can transmit at a data rate up to 100kbps NRZ (50kbps Manchester coded). Typical transmitted power into a  $50\Omega$  load is +10dBm. The MAX7058 operates from +2.1V to +3.6V and draws under 8.0mA of current. The standby current is less than 1µA at room temperature. A 15MHz crystal is used as the reference for 315MHz and 390MHz operation by selecting synthesizer-divide ratios of 21 and 26, respectively.

The MAX7058 is available in a 4mm x 4mm, 24-pin thin QFN package and is specified to operate in the -40°C to +125°C automotive temperature range.

### **Applications**

- Garage Door Openers

- RF Remote Controls

- Home Automation

- Wireless Sensors

- Security Systems

#### **Features**

- Switched 315MHz/390MHz Carrier Frequency Using One Crystal

- +2.1V to +3.6V Single-Supply Operation

- ASK/OOK Modulation

- Internal Switched Capacitors for Optimum Dual-Frequency Operation

- 8.0mA DC Current Drain (50% Duty Cycle OOK)

- 0.8µA Standby Current

- Small 4mm x 4mm, 24-Pin Thin QFN Package

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE                    |

|-------------|-----------------|--------------------------------|

| MAX7058ATG+ | -40°C to +125°C | 24 Thin QFN-EP*<br>(4mm x 4mm) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

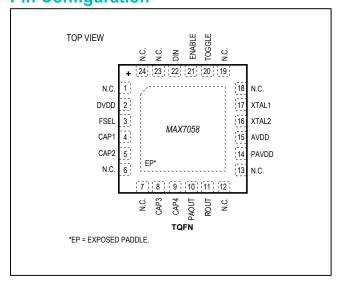

# **Pin Configuration**

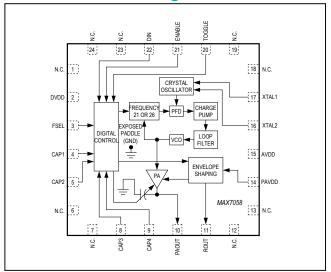

#### **Functional Block Diagram**

#### MAX7058

# 315MHz/390MHz Dual-Frequency ASK Transmitter

## **Absolute Maximum Ratings**

| Supply Voltage, AVDD, DVDD, PAVDD to GND (Exposed               | Operating Temperature40°C to +125°C     |

|-----------------------------------------------------------------|-----------------------------------------|

| Paddle)0.3V to +4V                                              | Storage Temperature65°C to +150°C       |

| All Other PinsExposed Paddle - 0.3V to (V <sub>DD</sub> + 0.3V) | Lead Temperature (soldering, 10s)+300°C |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)           |                                         |

| 24-Pin TQFN (derate 20.8mW/°C above +70°C)1666.7mW              |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

(*Typical Operating Circuit*,  $50\Omega$  system impedance,  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.1V$  to +3.6V,  $f_{RF} = 315MHz$  or 390MHz,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.7V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted. All min and max values are 100% tested at  $T_A = +125^{\circ}C$ , and guaranteed by design and characterization over temperature, unless otherwise noted.)

| PARAMETER                | SYMBOL             | CONDITIONS                                                       |                          | MIN              | TYP  | MAX                       | UNITS |

|--------------------------|--------------------|------------------------------------------------------------------|--------------------------|------------------|------|---------------------------|-------|

| Supply Voltage           | V <sub>DD</sub>    | PAVDD, AVDD, and DVDD connected to power supply, V <sub>DD</sub> |                          | 2.1              | 2.7  | 3.6                       | V     |

|                          |                    | PA off, V <sub>DIN</sub> at 0% duty                              | f <sub>RF</sub> = 315MHz |                  | 3.4  | 5.4                       |       |

|                          |                    | cycle                                                            | f <sub>RF</sub> = 390MHz |                  | 3.8  | 6.3                       |       |

| Supply Current           | I                  | V <sub>DIN</sub> at 50%, duty cycle                              | f <sub>RF</sub> = 315MHz |                  | 8.0  | 13.7                      | ]     |

| Supply Current           | l <sub>DD</sub>    | (Notes 1, 2, 3)                                                  | f <sub>RF</sub> = 390MHz |                  | 8.3  | 14.2                      | mA    |

|                          |                    | f <sub>RF</sub> = 315MHz                                         |                          | 12.6             | 21.9 | 1                         |       |

|                          |                    | (Note 1)                                                         | f <sub>RF</sub> = 390MHz |                  | 12.9 | 22.1                      | 1     |

|                          | I <sub>STDBY</sub> | V <sub>ENABLE</sub> < V <sub>IL</sub>                            | T <sub>A</sub> = +25°C   |                  | 0.8  |                           |       |

| Standby Current          |                    | (Note 3)                                                         | T <sub>A</sub> < +85°C   |                  | 1.0  | 4.0                       | μA    |

|                          |                    |                                                                  | T <sub>A</sub> < +125°C  |                  | 6.2  | 16.1                      |       |

| DIGITAL I/O              |                    |                                                                  | •                        |                  |      |                           |       |

| Input High Threshold     | V <sub>IH</sub>    |                                                                  |                          | 0.9 x            |      |                           | V     |

| input riigii rriiesiloid | VIH                |                                                                  |                          | DV <sub>DD</sub> |      | -                         | V     |

| Input Low Threshold      | V <sub>IL</sub>    |                                                                  |                          |                  |      | 0.1 x<br>DV <sub>DD</sub> | V     |

| Pulldown Sink Current    |                    |                                                                  |                          |                  | 13   |                           | μΑ    |

#### **AC Electrical Characteristics**

(*Typical Operating Circuit*,  $50\Omega$  system impedance,  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.1V$  to +3.6V,  $f_{RF} = 315MHz$  or 390MHz,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.7V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted. All min and max values are 100% tested at  $T_A = +125^{\circ}C$ , and guaranteed by design and characterization over temperature, unless otherwise noted.)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                                                                         |                                                                                         | MIN | TYP     | MAX    | UNITS      |  |

|--------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|---------|--------|------------|--|

| GENERAL CHARACTERISTICS              |                   | •                                                                                                                  |                                                                                         |     |         |        |            |  |

| Frequency Range                      |                   |                                                                                                                    |                                                                                         | 300 | 315/390 | 450    | MHz        |  |

| Power-On Time                        | _                 |                                                                                                                    | ENABLE transition low-to-high, frequency settled to within 50kHz of the desired carrier |     | 110     |        | 116        |  |

|                                      | ton               |                                                                                                                    | n low-to-high, frequency<br>Hz of the desired carrier                                   |     | 250     |        | μs         |  |

| Maximum Data Data                    |                   | Manchester encod                                                                                                   | led                                                                                     |     | 50      |        | lchno      |  |

| Maximum Data Rate                    |                   | Nonreturn to zero                                                                                                  | (NRZ)                                                                                   |     | 100     |        | kbps       |  |

| Frequency Switching Time             |                   | Time from low-to-high or high-to-low transition of FSEL to frequency settled to within 5kHz of the desired carrier |                                                                                         | 30  |         | μs     |            |  |

| PHASE-LOCKED LOOP (PLL)              |                   |                                                                                                                    |                                                                                         | •   |         |        |            |  |

| VCO Gain                             | KVCO              |                                                                                                                    |                                                                                         |     | 320     |        | MHz/V      |  |

|                                      |                   | f = 215MUz                                                                                                         | 10kHz offset                                                                            |     | -87     |        |            |  |

| PLL Phase Noise                      |                   | f <sub>RF</sub> = 315MHz                                                                                           | 1MHz offset                                                                             |     | -98     |        | dDa/L'-    |  |

| FIL Fliase Noise                     |                   | f = 200MH=                                                                                                         | 10kHz offset                                                                            |     | -84     | dBc/Hz |            |  |

|                                      |                   | f <sub>RF</sub> = 390MHz                                                                                           | 1MHz offset                                                                             |     | -98     |        |            |  |

| Loop Bandwidth                       |                   |                                                                                                                    |                                                                                         |     | 600     |        | kHz        |  |

| Reference Frequency Input Level      |                   |                                                                                                                    |                                                                                         |     | 500     |        | $mV_{P-P}$ |  |

| Frequency-Divider Range              |                   |                                                                                                                    |                                                                                         | 21  |         | 26     |            |  |

| CRYSTAL OSCILLATOR                   |                   |                                                                                                                    |                                                                                         |     |         |        |            |  |

| Crystal Frequency                    | f <sub>XTAL</sub> |                                                                                                                    |                                                                                         |     | 15      |        | MHz        |  |

| Frequency Pulling by V <sub>DD</sub> |                   |                                                                                                                    |                                                                                         |     | 4       |        | ppm/V      |  |

| Crystal Load Capacitance             |                   | (Note 4)                                                                                                           |                                                                                         |     | 10      |        | pF         |  |

#### **AC Electrical Characteristics (continued)**

(Typical Operating Circuit,  $50\Omega$  system impedance,  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.1V$  to +3.6V,  $f_{RF} = 315MHz$  or 390MHz,  $T_A = -40$ °C to +125°C, unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PAVDD} = +2.7$ V,  $T_A = +25$ °C, unless otherwise noted. All min and max values are 100% tested at  $T_A$  = +125°C, and guaranteed by design and characterization over temperature, unless otherwise noted.)

| PARAMETER                 | SYMBOL           | CONDITIONS                                                                                          |                          | MIN | TYP  | MAX  | UNITS |  |

|---------------------------|------------------|-----------------------------------------------------------------------------------------------------|--------------------------|-----|------|------|-------|--|

| POWER AMPLIFIER           |                  |                                                                                                     |                          |     |      |      |       |  |

| Output Power (Note 1)     |                  | T <sub>A</sub> = +25°C (Note 3)                                                                     |                          | 4.2 | 10   | 15.5 | dBm   |  |

|                           | P <sub>OUT</sub> | $T_A = +125$ °C, $V_{PAVDD} = V_{AVDD} = V_{DVDD} = +2.1$ V                                         |                          | 3.0 | 5.9  |      |       |  |

|                           |                  | T <sub>A</sub> = -40°C, V <sub>PAVDD</sub> = V <sub>AVDD</sub> = V <sub>DVDD</sub> = +3.6V (Note 3) |                          |     | 13.3 | 16.4 |       |  |

| Modulation Depth          |                  |                                                                                                     |                          |     | 80   |      | dB    |  |

| Maximum Carrier Harmonics |                  | With output matching                                                                                | f <sub>RF</sub> = 315MHz |     | -28  |      | dBc   |  |

|                           |                  | network $f_{RF} = 390MHz$                                                                           |                          |     | -32  |      | ubc   |  |

| Reference Spur            |                  |                                                                                                     |                          |     | -48  |      | dBc   |  |

Note 1: Supply current and output power are greatly dependent on board layout and PAOUT match.

Note 2: 50% duty cycle at 10kHz ASK data (Manchester coded).

Note 3: Guaranteed by design and characterization, not production tested.

Note 4: Dependent on PCB trace capacitance.

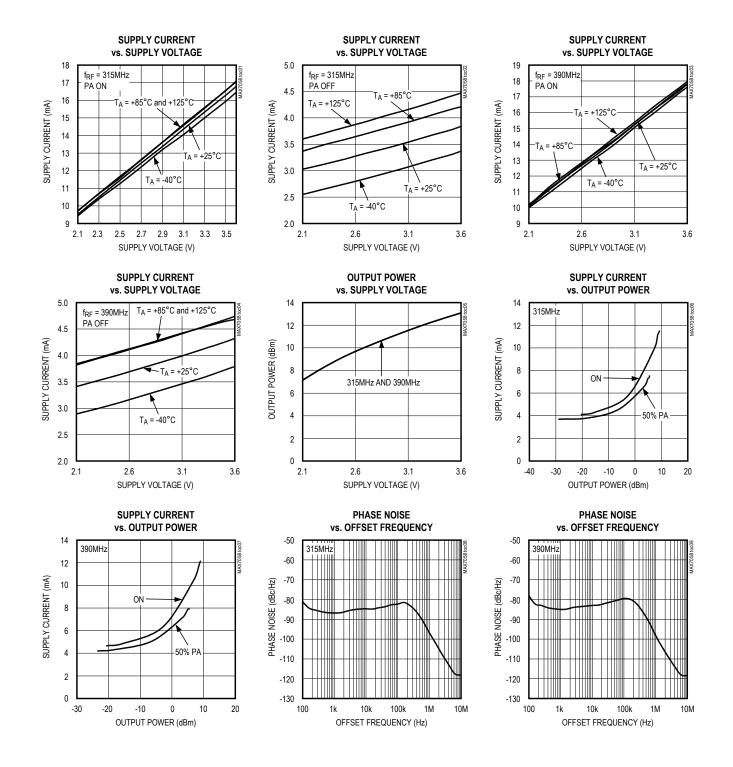

# **Typical Operating Characteristics**

(TA = +25°C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

(TA = +25°C, unless otherwise noted.)

# 315MHz/390MHz Dual-Frequency ASK Transmitter

# **Pin Description**

| PIN                               | NAME     | FUNCTION                                                                                                                                                                                                                                                          |

|-----------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 7, 12,<br>13, 18, 19,<br>24 | N.C.     | No Connection. Internally not connected.                                                                                                                                                                                                                          |

| 2                                 | DVDD     | Digital Positive Supply Voltage. Bypass to GND with $0.1\mu F$ and $0.01\mu F$ capacitors placed as close to the pin as possible.                                                                                                                                 |

| 3                                 | FSEL     | Frequency Select. Internally pulled down to GND when the part is not in standby mode. Set FSEL = 0/ TOGGLE = 0 to select continuous 390MHz, and FSEL = 1/TOGGLE = 0 to select continuous 315MHz. See Table 1 for detailed mode description.                       |

| 4                                 | CAP1     | Output Capacitance Adjustment 1. Logic pin to control the capacitance on PAOUT (see Table 2). Set CAP1 = 1 to add 0.5pF shunt capacitance at PAOUT when at 315MHz. Internally pulled down to GND when the part is not in standby mode.                            |

| 5                                 | CAP2     | Output Capacitance Adjustment 2. Logic pin to control the capacitance on PAOUT (see Table 2). Set CAP2 = 1 to add 1pF shunt capacitance at PAOUT when at 315MHz. Internally pulled down to GND when the part is not in standby mode.                              |

| 8                                 | CAP3     | Output Capacitance Adjustment 3. Logic pin to control the capacitance on PAOUT (see Table 2). Set CAP3 = 1 to add 2pF shunt capacitance at PAOUT when at 315MHz. Internally pulled down to GND when the part is not in standby mode.                              |

| 9                                 | CAP4     | Output Capacitance Adjustment 4. Logic pin to control the capacitance on PAOUT (see Table 2). Set CAP4 = 1 to add 4pF shunt capacitance at PAOUT when at 315MHz. Internally pulled down to GND when the part is not in standby mode.                              |

| 10                                | PAOUT    | Power Amplifier Output. Requires a pullup inductor to the supply voltage or ROUT. The pullup inductor can be part of the output-matching network.                                                                                                                 |

| 11                                | ROUT     | Envelope-Shaping Output. ROUT controls the power amplifier envelope's rise and fall times. Connect ROUT to PA pullup inductor or optional power-adjust resistor. Bypass the inductor to GND as close to the inductor as possible with 680pF and 220pF capacitors. |

| 14                                | PAVDD    | Power Amplifier Supply Voltage. Bypass to GND with 0.01µF and 220pF capacitors placed as close to the pin as possible.                                                                                                                                            |

| 15                                | AVDD     | Analog Positive Supply Voltage. Bypass AVDD to GND with 0.1µF and 0.01µF capacitors placed as close to the pin as possible.                                                                                                                                       |

| 16                                | XTAL2    | Crystal Input 2. XTAL2 can be driven from an AC-coupled external reference.                                                                                                                                                                                       |

| 17                                | XTAL1    | Crystal Input 1. Bypass to GND if XTAL2 is driven from an AC-coupled external reference.                                                                                                                                                                          |

| 20                                | TOGGLE   | Toggle Pin. Set TOGGLE = 1 to enable toggle operation (see the <i>Detailed Description</i> section and Table 1 for operating mode). Internally pulled down to GND when the part is not in standby mode.                                                           |

| 21                                | ENABLE   | Enable Pin. Drive high for normal operation, and drive low or leave unconnected to put the device in standby mode. Internally pulled down to GND.                                                                                                                 |

| 22                                | DIN      | ASK Data Input. Internally pulled down to GND. Auto power-up occurs upon activity (see the <i>Detailed Description</i> section).                                                                                                                                  |

| 23                                | N.C.     | No connection. Must remain unconnected.                                                                                                                                                                                                                           |

| _                                 | EP (GND) | Exposed Paddle. Internally connected to ground (the only ground for the MAX7058.) Requires low-inductance path (e.g., one or more vias) to solid ground plane. Solder evenly to the board's ground plane for proper operation.                                    |

#### **Detailed Description**

The MAX7058 alternately transmits OOK/ASK data at 315MHz or 390MHz using a single crystal. The device has integrated tuning capacitors at the output of the power amplifier to ensure high efficiency at each frequency.

The crystal-based architecture of the MAX7058 eliminates many of the common problems with surface acoustic wave (SAW) transmitters, by providing greater modulation depth, faster frequency settling, tighter transmit frequency tolerance, and reduced temperature dependence. In particular, the tighter transmit frequency tolerance means that a super-heterodyne receiver with a narrower IF bandwidth (therefore lower noise bandwidth) can be used. The payoff is improved overall receiver performance when using a super-heterodyne receiver such as the MAX1471, MAX1473, MAX7033, MAX7034, or MAX7042.

#### **Dual Frequency**

The MAX7058 is a crystal-referenced PLL VHF/UHF transmitter that transmits OOK/ASK data at 315MHz or 390MHz. Two fixed synthesizer-divide ratios of 21 and 26 can be selected, and a 15MHz crystal is used as the reference for 315MHz/390MHz operation. The FSEL pin is used to select the divide ratio. The MAX7058 can operate over a 300MHz to 450MHz range by using different crystal frequencies. The two operating frequencies are always related by a 26:21 ratio.

An internal variable shunt capacitor is connected at the PA output. This capacitor is controlled by four external logic bits (CAP1–CAP4) to maintain highly efficient transmission at either 315MHz or 390MHz. This means that it is possible to change the frequency and retune the antenna to the new frequency in a very short time. The combination of rapid-antenna tuning ability with rapid-synthesizer tuning makes the MAX7058 a true frequency-agile transmitter. The tuning capacitor has a

resolution of 0.5pF. When the MAX7058 operates at 315MHz, the capacitance added at PAOUT corresponds to the setting at CAP1–CAP4, as seen in Table 2. When the MAX7058 operates at 390MHz, the MAX7058 does not add any internal shunt capacitance at PAOUT.

The MAX7058 supports ASK data rates up to 100kbps NRZ and features adjustable output power through an external resistor to more than +10dBm into a  $50\Omega$  load.

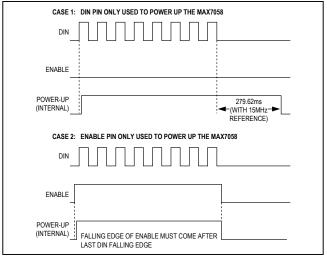

#### **Power-Up and Standby Modes**

The MAX7058 can be placed in either an enabled state (all circuit blocks necessary for transmission powered up) or a disabled state (low-current standby). The state selection can be controlled either by ENABLE (ENABLE method) or by activity on DIN (auto-power-up method). In either method, the MAX7058 can begin transmission within 250µs after being enabled. Either method can be used with any TOGGLE/FSEL operating mode.

In the ENABLE method, setting ENABLE to a logic-high state enables the MAX7058 and setting it to a logic-low state disables the MAX7058. To avoid conflict with the auto-power-up method, DIN must be set to a logic-low state before ENABLE is set to a logic-low state, and remains low until after ENABLE is set to a logic-high state.

In the auto-power-up method, ENABLE can be hard-wired to a logic-low state and a rising edge on DIN will enable the MAX7058. The MAX7058 will remain enabled until DIN is placed in a steady logic-low state for 2<sup>22</sup> cycles of the reference clock (279.62ms with a 15MHz crystal), at which time the MAX7058 will be disabled.

When the MAX7058 is enabled, the active pulldowns at CAP1–CAP4, FSEL, and TOGGLE will be turned on. When the MAX7058 is disabled, these active pulldowns will be turned off. The active pulldowns at ENABLE and DIN are always turned on.

#### **Operating Mode**

TOGGLE and FSEL are two pins available for controlling the state of the toggle mode and the operating frequency. The following truth table defines the pin logic for the four possible operating states.

**Table 1. Toggle Pin Operation for MAX7058**

| TOGGLE<br>PIN | FSEL<br>PIN | OPERATING STATE                                         |

|---------------|-------------|---------------------------------------------------------|

| 0             | 0           | Continuous fixed-frequency operation at 390MHz          |

| 0             | 1           | Continuous fixed-frequency operation at 315MHz          |

| 1             | 0           | Five packets toggle operation between 315MHz and 390MHz |

| 1             | 1           | 100 packets toggle operation between 315MHz and 390MHz  |

The internal variable shunt capacitor control pins (CAP1–CAP4) are used whenever the frequency setting is 315MHz, in either continuous (TOGGLE = 0, FSEL = 1) or toggle (TOGGLE = 1) mode.

#### **Toggle Definition**

With TOGGLE/FSEL set to state 10, the MAX7058 is in 5-packet toggle mode; with TOGGLE/FSEL set to state 11, the MAX7058 is in 100-packet toggle mode. Upon power-up, the MAX7058 begins transmission at 315MHz within 250µs. Packet termination is defined as the time duration of greater than 218 crystal oscillator reference clock cycles (17.49ms) with DIN continuously at logic 0. The frequency of operation toggles every five or 100 packets based on the logic level of FSEL.

#### Power Amplifier (PA)

The power amplifier (PA) of the MAX7058 is a high-efficiency, open-drain, switching-mode amplifier. In a switching-mode amplifier, the gate of the final-stage FET is driven with a very sharp 25% duty-cycle square wave at the transmit frequency. This square wave is derived from the synthesizer circuit. When the matching network is tuned correctly, the output FET resonates the attached tank circuit with a minimum amount of power dissipated in the FET. With a proper output-matching network, the PA can drive a wide range of antenna impedances, which include a small-loop PCB trace and a  $50\Omega$  antenna. The output-matching network suppresses the carrier harmonics and transforms the

Figure 1. Power-Up Waveform with DIN/ENABLE for MAX7058

antenna impedance to optimal impedance at PAOUT, which is from  $125\Omega$  to  $250\Omega$ .

When the output-matching network is properly tuned, the PA transmits +10dBm (typ), with a high overall efficiency. The efficiency of the PA itself is more than 40%. The output power can be adjusted by changing the impedance seen by the PA or by adjusting the value of an external resistor at PAOUT.

#### **Envelope Shaping**

The MAX7058 features an internal envelope-shaping resistor, which connects between PAVDD and ROUT. When connected to the PA pullup inductor, the envelope-shaping resistor slows the turn-on/turn-off time of the PA and results in a smaller spectral width of the modulated PA output signal.

#### **Variable Capacitor**

The MAX7058 has a set of selectable internal shunt capacitors that can be switched in and out to present different capacitor values at the PA output. The capacitors are connected from the PA output to ground. This allows changing the tuning network, along with the synthesizer-divide ratio each time the transmitted frequency changes, making it possible to maintain maximum transmitter power while moving rapidly from one frequency to another.

When the particular capacitance control input pin is high, then the corresponding amount of capacitance is added at PAOUT; this capacitance tuning works only at 315MHz. The 16 capacitor values are selected by setting CAP1–CAP4; the capacitance resolution is 0.5pF. The total capacitance varies from 0 to 7.5pF. For example, if CAP1 and CAP3 are high and CAP4 and CAP2 are low when operating at 315MHz, then this circuit will add 2.5pF at PAOUT.

**Table 2. Variable Capacitor Values and Control Input Pins**

| CAPACITOR ADDED SHUNT CAPACITANG |              |              |  |  |  |

|----------------------------------|--------------|--------------|--|--|--|

| CONTROL PIN STATE                | IN pF        |              |  |  |  |

| (CAP4-CAP1)                      | 315MHz (÷21) | 390MHz (÷26) |  |  |  |

| 0000                             | 0            |              |  |  |  |

| 0001                             | 0.5          |              |  |  |  |

| 0010                             | 1.0          |              |  |  |  |

| 0011                             | 1.5          |              |  |  |  |

| 0100                             | 2.0          |              |  |  |  |

| 0101                             | 2.5          |              |  |  |  |

| 0110                             | 3.0          |              |  |  |  |

| 0111                             | 3.5          | 0            |  |  |  |

| 1000                             | 4.0          |              |  |  |  |

| 1001                             | 4.5          |              |  |  |  |

| 1010                             | 5.0          |              |  |  |  |

| 1011                             | 5.5          |              |  |  |  |

| 1100                             | 6.0          |              |  |  |  |

| 1101                             | 6.5          |              |  |  |  |

| 1110                             | 7.0          |              |  |  |  |

| 1111                             | 7.5          |              |  |  |  |

#### **Phase-Locked Loop**

The MAX7058 utilizes a fully integrated, programmable PLL for its frequency synthesizer. All PLL components including the loop filter are included on-chip. The divide ratio is set at one of two fixed values: 21 (FSEL is set to high) or 26 (FSEL is set to low).

#### Crystal (XTAL) Oscillator

The crystal (XTAL) oscillator in the MAX7058 is designed to present a capacitance of approximately 6pF between XTAL1 and XTAL2. In most cases, this corresponds to an 8pF load capacitance applied to the external crystal when typical PCB parasitics are added. The MAX7058 is designed to operate with a typical 10pF load capacitance crystal. It is very important to use a crystal with a load capacitance equal to the capacitance of the MAX7058 crystal oscillator plus PCB parasitics. If a crystal designed to oscillate with a different load capacitance is used, the crystal is pulled away from its stated operating frequency, introducing an error in the reference frequency. A crystal designed to operate at a higher load capacitance than the value specified for the oscillator will always be pulled higher in frequency. Adding capacitance to increase the load capacitance on the crystal will increase the startup time and may prevent oscillation altogether.

In actuality, the oscillator pulls every crystal. The crystal's natural frequency is really below its specified frequency, but when loaded with the specified load capacitance, the crystal is pulled and oscillates at its specified frequency. This pulling is already accounted for in the specification of the load capacitance.

Additional pulling can be calculated if the electrical parameters of the crystal are known. The frequency pulling is given by:

$$\ddot{\psi} \ddot{s} \ddot{u} \frac{C_m}{2} \left( \frac{1}{C_{case} + C_{load}} - \frac{1}{C_{case} + C_{spec}} \right) \times 6$$

where:

fp is the amount the crystal frequency is pulled in ppm

C<sub>m</sub> is the motional capacitance of the crystal

C<sub>case</sub> is the case capacitance

Cload is the actual load capacitance

C<sub>spec</sub> is the specified load capacitance

When the crystal is loaded as specified (i.e.,  $C_{load} = C_{spec}$ ), the frequency pulling equals zero.

# Applications Information Output Matching to $50\Omega$

When matched to a  $50\Omega$  system, the MAX7058's PA is capable of delivering +10dBm of output power at  $V_{DD}$  = +2.7V. The output of the PA is an open-drain transistor, which has internal selectable shunt tuning capacitors for impedance matching (see the Variable Capacitor section). It is connected to  $V_{DD}$  through a pullup inductor for proper biasing. The internal selectable shunt capacitors make it easy for tuning when changing the output frequency. The pullup inductance from the PAOUT to  $V_{DD}$  or ROUT serves three main purposes: resonating the capacitive PA output, providing biasing for the PA, and acting as a high-frequency choke to prevent RF energy from coupling into  $V_{DD}$ . The pi network between the PA output and the antenna also forms a lowpass filter that provides attenuation for the higher-order harmonics.

#### **Output Matching to PCB Loop Antenna**

In many applications, the MAX7058 must be impedance-matched to a small loop antenna. The antenna is usually fabricated out of a copper trace on a PCB in a rectangular, circular, or square pattern. The antenna has impedance that consists of a lossy component and a radiative component. To achieve high radiating efficiency, the radiative component should be as high as possible, while minimizing the lossy component. In addition, the loop antenna has an inherent loop inductance associated with it (assuming the antenna is terminated to ground). In a typical application,

the inductance of the loop antenna is approximately 50nH to 100nH. The radiative and lossy impedances may be anywhere from a few tenths of an ohm to  $5\Omega$  or  $10\Omega$ .

#### **Layout Considerations**

A properly designed PCB is an essential part of any RF/microwave circuit. At high-frequency inputs and outputs, use controlled-impedance lines and keep them as short as possible to minimize losses and radiation. At high frequencies, trace lengths that are on the order of  $\lambda/10$  or longer act as antennas, where  $\lambda$  is the wavelength.

Keeping the traces short also reduces parasitic inductance. Generally, one inch of PCB trace adds about 20nH of parasitic inductance. The parasitic inductance can have a dramatic effect on the effective inductance of a passive component. For example, a 0.5in trace connecting to a 100nH inductor adds an extra 10nH of inductance, or 10%.

To reduce parasitic inductance, use wider traces and a solid ground or power plane below the signal traces. Using a solid ground plane can reduce the parasitic inductance from approximately 20nH/in to 7nH/in. Also, use low-inductance connections to the ground plane and place decoupling capacitors as close as possible to all VDD pins.

#### **Chip Information**

PROCESS: CMOS

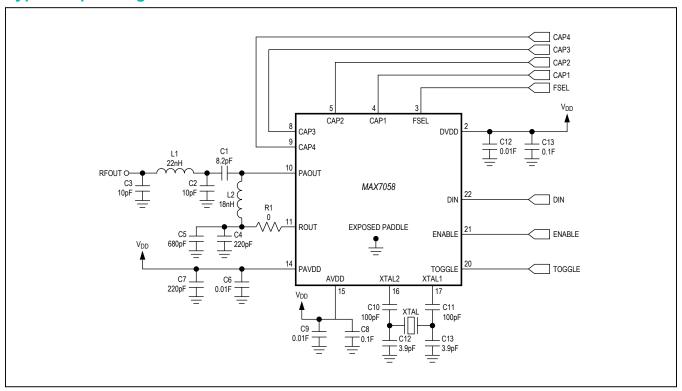

# **Typical Operating Circuit**

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | DOCUMENT | LAND        |

|------------|---------|----------|-------------|

| TYPE       | CODE    | NO.      | PATTERN NO. |

| 24 TQFN-EP | T2444+3 | 21-0139  | 90-0021     |

## MAX7058

# 315MHz/390MHz Dual-Frequency ASK Transmitter

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                  | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------|------------------|

| 0                  | 1/08             | Initial Release                              | _                |

| 1                  | 7/14             | Removed automotive reference from data sheet | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX7058ATG+ MAX7058ATG+T