# Dual Mode DisplayPort to HDMI Level shifter and Re-driver

#### **Features**

- Re-drives HDMI1.4a signal across long PCB trace

- Converts low-swing AC coupled differential input to HDMI<sup>TM</sup> rev 1.4a compliant open-drain current steering Rx terminated differential output

- HDMI level shifting operation up to 2.97Gbps per lane (297MHz pixel clock) for stereo video

- Integrated 50-ohm termination resistors for AC-coupled differential inputs.

- Enable/Disable feature to turn off TMDS outputs to enter low-power state.

- 3.3 Power supply required.

- Integrated ESD protection to 8kV contact on all high speed

I/O pins (IN\_x and OUT\_x) per IEC61000-4-2 test spec, level 4

- DDC level shifters from 5V from sink side down to 3.3V on source side

- · Level shifter for HPD signal from HDMI/DVI connector

- Integrated pull-down on HPD\_sink input guarantees "input low" when no display is plugged in

- Packaging (Pb-Free & Green)

- 48 TQFN, 7mm x 7mm (ZBE)

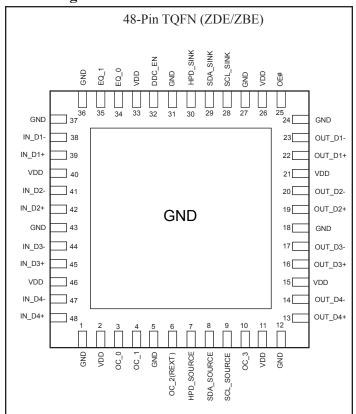

### **Pin Configuration**

#### **Description**

Pericom Semiconductor's PI3VDP1430 provides the ability to use a Dual-mode DP transmitter in HDMI™ mode. This flexibility provides the user a choice of how to connect to their favorite display. All signal paths accept AC coupled video signals. The PI3VDP1430 converts this AC coupled signal into an HDMI rev 1.4a compliant signal with proper signal swing. This conversion is automatic and transparent to the user.

The PI3VDP1430 supports up to 2.97Gbps, which provides stereo video functionality as described in the HDMI 1.4a specifrication.

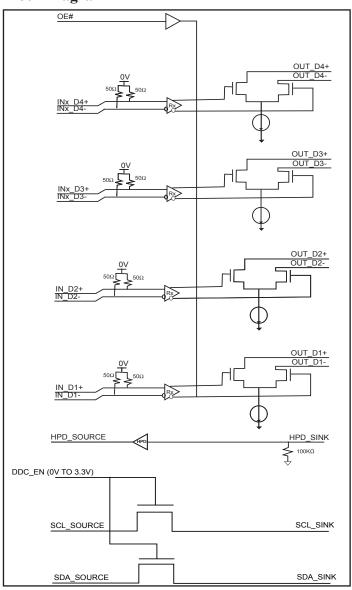

#### **Block Diagram**

1

# **Pin Assignment**

| Pin Name | Type | Description                                                                |                   |        |  |  |  |  |  |

|----------|------|----------------------------------------------------------------------------|-------------------|--------|--|--|--|--|--|

|          |      | 5.5V tolerant low-voltage single-ended input Enable for level shifter path |                   |        |  |  |  |  |  |

| OE#      | I    | OE#                                                                        | IN_D Termination  |        |  |  |  |  |  |

|          | _    | 1                                                                          | >100KΩ            | High-Z |  |  |  |  |  |

|          |      | 0                                                                          | 50Ω               | Active |  |  |  |  |  |

| IN_D4+   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D4-   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D3+   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D3-   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D2+   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D2-   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D1+   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| IN_D1-   | I    | Differentia                                                                | al input          |        |  |  |  |  |  |

| OUT_D4+  | О    | TMDS Di                                                                    | fferential output |        |  |  |  |  |  |

| OUT_D4-  | О    | TMDS Di                                                                    | fferential output |        |  |  |  |  |  |

| OUT_D3+  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

| OUT_D3-  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

| OUT_D2+  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

| OUT_D2-  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

| OUT_D1+  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

| OUT_D1-  | О    | TMDS Differential output                                                   |                   |        |  |  |  |  |  |

(Continued)

| Pin Name                     | Туре                                              | Description                                                                                                                                                                                                                                |                                                                                                                   |  |  |

|------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| HPD_SINK                     | 5V tolerance single-ended input                   | Low Frequency, 0V to 5V (nominal) input signal. This signal comes from the HDMI connector. Voltage High indicates "plugged" state; voltage low indicated "unplugged". HPD_SINK is pulled down by an integrated 100K ohm put-down resistor. |                                                                                                                   |  |  |

| HPD_SOURCE                   | 3.3V single-ended output                          | HPD_SOURCE: 0V to 3.3 This is level-shifted version                                                                                                                                                                                        | V (nominal) output signal.<br>n of the HPD_SINK signal.                                                           |  |  |

| SCL_SOURCE                   | Single-ended 3.3V open-drain DDC I/O              | 3.3V DDC Data I/O. Pulled tion to 3.3V. Connected to age-limiting integrated NM.                                                                                                                                                           | SCL_SINK through volt-                                                                                            |  |  |

| SDA_SOURCE                   | Single-ended 3.3V open-drain DDC I/O              | 3.3V DDC Data I/O. Pulled to 3.3V. Connected to SDA limiting integrated NMOS                                                                                                                                                               |                                                                                                                   |  |  |

| SCL_SINK                     | Single-ended 5V open-drain DDC I/O                | 5V DDC Clock I/O. Pulled up by external termination to 5V. Connected to SCL_SOURCE through voltage-limiting integrated NMOS passgate.                                                                                                      |                                                                                                                   |  |  |

| SDA_SINK                     | Single-ended 5V open-drain DDC I/O                | 5V DDC Data I/O. Pulled up by external termination to 5V. Connected to SDA_SOURCE through voltage limiting integrated NMOS passgate.                                                                                                       |                                                                                                                   |  |  |

|                              |                                                   | Enables bias voltage to the DDC passgate level shifter gates. (May be implemented as a bias voltage connection to the DDC pass gates themselves.)                                                                                          |                                                                                                                   |  |  |

| DDC_EN                       | 5.0V tolerant Single-ended input                  | DDC_EN                                                                                                                                                                                                                                     | Passgate                                                                                                          |  |  |

|                              |                                                   | 0V                                                                                                                                                                                                                                         | Disabled                                                                                                          |  |  |

|                              |                                                   | 3.3V                                                                                                                                                                                                                                       | Enabled                                                                                                           |  |  |

| VDD                          | 3.3V DC Supply                                    | $3.3V \pm 10\%$                                                                                                                                                                                                                            |                                                                                                                   |  |  |

| OC_2<br>(REXT)               | OC_2  3 3V single-ended control input             |                                                                                                                                                                                                                                            | Acceptable connections to OC_1 (REXT) pin are: Resistor to GND; Resistor to 3.3V; NC. (Resistor should be 0-ohm). |  |  |

| OC_3                         | Analog connection to external component or supply | Acceptable connections to OC_3 pin are: short to 3.3V or to GND; NC.                                                                                                                                                                       |                                                                                                                   |  |  |

| OC_0<br>OC_1<br>EQ_0<br>EQ_1 | Output and Input jitter elimination control       | Control pins are to enable Jitter elimination features. For normal operation these pins are tied GND or to VDD. Please see the truth tables for more information.                                                                          |                                                                                                                   |  |  |

**Table 1: Truth Table**

| OC_3 <sup>(1)</sup> | OC_2 <sup>(1)</sup> | OC_1 <sup>(1)</sup> | OC_0 <sup>(1)</sup> | Vswing (mV) | Pre/De-emphasis |

|---------------------|---------------------|---------------------|---------------------|-------------|-----------------|

| 0                   | 0                   | 0                   | 0                   | 500         | 0               |

| 0                   | 0                   | 0                   | 1                   | 600         | 0               |

| 0                   | 0                   | 1                   | 0                   | 750         | 0               |

| 0                   | 0                   | 1                   | 1                   | 1000        | 0               |

| 0                   | 1                   | 0                   | 0                   | 500         | 0               |

| 0                   | 1                   | 0                   | 1                   | 500         | 1.5dB           |

| 0                   | 1                   | 1                   | 0                   | 500         | 3.5dB           |

| 0                   | 1                   | 1                   | 1                   | 500         | 6dB             |

| 1                   | 0                   | 0                   | 0                   | 400         | 0               |

| 1                   | 0                   | 0                   | 1                   | 400         | 3.5dB           |

| 1                   | 0                   | 1                   | 0                   | 400         | 6dB             |

| 1                   | 0                   | 1                   | 1                   | 400         | 9dB             |

| 1                   | 1                   | 0                   | 0                   | 1000        | 0               |

| 1                   | 1                   | 0                   | 1                   | 1000        | -3.5dB          |

| 1                   | 1                   | 1                   | 0                   | 1000        | -6dB            |

| 1                   | 1                   | 1                   | 1                   | 1000        | -9dB            |

**Table 2: Truth Table**

| EQ_1 <sup>(1)</sup> | EQ_0 <sup>(1)</sup> | Equalization @ 1.25GHz (dB) |

|---------------------|---------------------|-----------------------------|

| 0                   | 0                   | 3                           |

| 0                   | 1                   | 6                           |

| 1                   | 0                   | 9                           |

| 1                   | 1                   | 12                          |

#### **Notes:**

1) These signals have internal 100kohm pull-ups.

### **Absolute Maximum Ratings** (Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                                  | 65°C to +150°C |

|------------------------------------------------------|----------------|

| Supply Voltage to Ground Potential  DC Input Voltage |                |

| DC Output Current                                    |                |

| Power Dissipation                                    | 1.0W           |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Thermal Characteristics**

| Symbol         | Parameter                               | Rating | Unit |

|----------------|-----------------------------------------|--------|------|

| $T_{Jmax}$     | Junction Temperature                    | 125    | °C   |

| $R_{	heta JC}$ | Thermal Resistance, Junction to Case    | 23.65  |      |

| $R_{	heta JA}$ | Thermal Resistance, Junction to Ambient | 9.1    | °C/W |

### **Electrical Characteristics**

# **Table 3: Power Supplies and Temperature Range**

| Symbol | Parameter                                       | Min  | Nom | Max | Units   | Comments                                                                        |

|--------|-------------------------------------------------|------|-----|-----|---------|---------------------------------------------------------------------------------|

| VDD    | Power Supply                                    | 2.89 | 3.3 | 3.6 | V       |                                                                                 |

| ICC    | Max Current                                     |      |     | 100 | mA      | Total current from VDD 3.3V supply when de-emphasis/pre-emphasis is set to 0dB. |

| ICCQ   | Standby Current Consumption                     |      |     | 2   | mA      | OE# = HIGH                                                                      |

| TCASE  | Case temperature range for operation with spec. | -40  |     | 85  | Celcius |                                                                                 |

**Table 4: OE# Description**

| OE#                       | Device State                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                       |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Asserted (low voltage)    | Differential input buffers and output buffers enabled. Input impedance = $50\Omega$                                                                                                                                  | Normal functioning state for IN_D to OUT_D level shifting function.                                                                                                                                                                                                            |  |

| Unasserted (high voltage) | Low-power state.  Differential input buffers and termination are disabled. Differential inputs are in a high-impedance state.  OUT_D level-shifting outputs are disabled.  OUT_D level-shifting outputs are in high- | Intended for lowest power condition when:  • No display is plugged in or  • The level shifted data path is disabled  HPD_SINK input and HPD_SOURCE output are not affected by OE# SCL_SOURCE,  SCL_SINK, SDA_SOURCE and SDA_SINK signals and functions are not affected by OE# |  |

|                           | impedence state. Internal bias currents are turned off.                                                                                                                                                              | signals and functions are not affected by OF                                                                                                                                                                                                                                   |  |

Table 5: Differential Input Characteristics for IN\_D and RX\_IN signals

| Symbol                  | Parameter                               | Min   | Nom | Max | Units | Comments                                                                                                                                                   |

|-------------------------|-----------------------------------------|-------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tbit                    | Unit Interval                           | 360   |     |     | ps    | Tbit is determined by the display mode.<br>Nominal bit rate ranges from 250Mbps<br>to 2.5Gbps per lane. Nominal Tbit at 2.5<br>Gbps=400ps. 360ps=400ps-10% |

| V <sub>RX-DIFFp-p</sub> | Differential Input Peak to Peak Voltage | 0.175 |     | 1.2 | V     | VRX-DIFFp-p=2' VRX-D+ x VRX-D-  Applies to IN_D and RX_IN signals                                                                                          |

| T <sub>RX-EYE</sub>     | Minimum Eye Width at IN_D input pair    | 0.8   |     |     | Tbit  | The level shifter may add a maximum of 0.02UI jitter                                                                                                       |

| V <sub>CM-AC-pp</sub>   | AC Peak<br>Common Mode Input<br>Voltage |       |     | 100 | mV    | VCM-AC-pp =  VRX-D+ + VRX-D- /2 - VRX-CM-DC.<br>VRX-CM-DC = DC(avg) of  VRX-D+ + VRX-D- /2<br>VCM-AC-pp includes all frequencies above 30 kHz.             |

| Z <sub>RX-DC</sub>      |                                         | 40    | 50  | 60  | Ω     | Required IN_D+ as well as IN_D- DC impedance ( $50\Omega \pm 20\%$ tolerance).                                                                             |

| V <sub>RX-Bias</sub>    |                                         | 0     |     | 2.0 | V     | Intended to limit power-up stress on chipset's PCIE output buffers.                                                                                        |

| Z <sub>RX-HIGH-Z</sub>  |                                         | 100   |     |     | kΩ    | Differential inputs must be in a high impedance state when OE# is HIGH.                                                                                    |

# **TMDS Outputs**

The level shifter's TMDS outputs are required to meet HDMI 1.4a specifications.

The HDMI 1.4a Specification is assumed to be the correct reference in instances where this document conflicts with the HDMI 1.4 specification.

Table 6: Differential Output Characteristics for TMDS\_OUT signals

| Symbol                       | Parameter                                      | Min       | Nom       | Max       | Units | Comments                                                                                                                                                                |

|------------------------------|------------------------------------------------|-----------|-----------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>H</sub>               | Single-ended<br>high level out-<br>put voltage | VDD-10mV  | VDD       | VDD+10mV  | V     | VDD is the DC termination voltage in the HDMI or DVI Sink. VDD is nominally 3.3V                                                                                        |

| $V_{ m L}$                   | Single-ended low level output voltage          | VDD-600mV | VDD-500mV | VDD-400mV | V     | The open-drain output pulls down from VDD.                                                                                                                              |

| V <sub>SWING</sub>           | Single-ended output swing voltage              | 450mV     | 500mV     | 600mV     | V     | Swing down from TMDS termination voltage (3.3V ± 10%)                                                                                                                   |

| I <sub>OFF</sub>             | Single-ended current in high-Z state           |           |           | 50        | μA    | Measured with TMDS outputs pulled up to VDD Max _(3.6V) through 50Ω resistors.                                                                                          |

| $T_{R}$                      | Rise time                                      | 125ps     |           | 0.4Tbit   | ps    | Max Rise/Fall time @2.7Gbps = 148ps. 125ps = 148-15%                                                                                                                    |

| $T_{ m F}$                   | Fall time                                      | 125ps     |           | 0.4Tbit   | ps    | Max Rise/Fall time @2.7Gbps = 148ps. 125ps = 148-15%                                                                                                                    |

| T <sub>SKEW</sub> -<br>INTRA | Intra-pair<br>differential<br>skew             |           |           | 30        | ps    | This differential skew budget is in addition to the skew presented between D+ and D- paired input pins. HDMI revision 1.3 source allowable intra-pair skew is 0.15Tbit. |

| T <sub>SKEW</sub> - INTER    | Inter-pair lane-<br>to-lane output<br>skew     |           |           | 100       | ps    | This lane-to-lane skew budget is in addition to skew between differential input pairs                                                                                   |

| $T_{ m JIT}$                 | Jitter added to TMDS signals                   |           |           | 25        | ps    | Jitter budget for TMDS signals as they pass through the level shifter. 25ps = 0.056 Tbit at 2.25 Gb/s                                                                   |

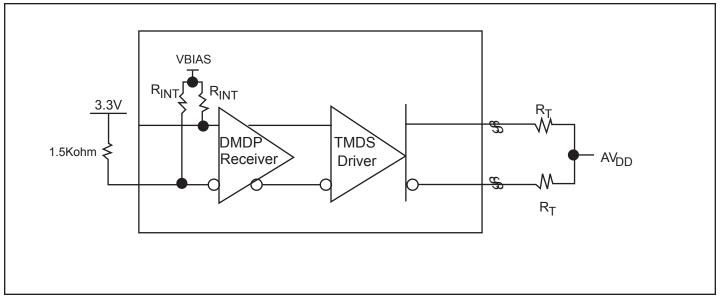

# **TMDS Output Oscillation Elimination**

The inputs do not incorporate a squelch circuit. Therefore, we recommend the input to be externally biased to prevent output oscillation. Pericom recommends to add a 1.5Kohm pull-up to the Clock input.

**TMDS Input Fail-Safe Recommendation**

**Table 8: HPD Input Characteristics**

| Symbol               | Parameter                                | Min | Nom | Max             | Units | Comments                                                                                               |

|----------------------|------------------------------------------|-----|-----|-----------------|-------|--------------------------------------------------------------------------------------------------------|

| V <sub>IH-HPD</sub>  | Input High Level                         | 2.0 | 5.0 | 5.3             | V     | Low-speed input changes state on cable plug/unplug                                                     |

| V <sub>IL-HPD</sub>  | HPD_sink Input<br>Low Level              | 0   |     | 0.8             | V     |                                                                                                        |

| I <sub>IN-HPD</sub>  | HPD_sink Input<br>Leakage Current        |     |     | 70              | μΑ    | Measured with HPD_sink at V <sub>IH-HPD</sub> max and V <sub>IL-HPD</sub> min                          |

| V <sub>OH-HPDB</sub> | HPD_sink Output<br>High-Level            | 2.5 |     | V <sub>DD</sub> | V     | $V_{\rm DD} = 3.3 V \pm 10\%$                                                                          |

| V <sub>OL-HPDB</sub> | HPD_sink Output<br>Low-Level             | 0   |     | 0.02            | V     |                                                                                                        |

| $T_{ m HPD}$         | HPD_sink to HPD_source propagation delay |     |     | 200             | ns    | Time from HPD_sink changing state to HPD_source changing state. Includes HPD_source rise/fall time     |

| T <sub>RF-HPDB</sub> | HPD_source rise/<br>fall time            | 1   |     | 20              | ns    | Time required to transition from $V_{OH-HPDB}$ to $V_{OL-HPDB}$ or from $V_{OL-HPDB}$ to $V_{OH-HPDB}$ |

# Table 9: OE# Input and DDC\_EN

| Symbol            | Parameter             | Min | Nom | Max | Units | Comments                                                                 |

|-------------------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------------|

| $V_{\mathrm{IH}}$ | Input High Level      | 2.0 |     | VDD | V     | TMDS enable input changes state on cable plug/unplug                     |

| $V_{\mathrm{IL}}$ | Input Low Level       | 0   |     | 0.8 | V     |                                                                          |

| I <sub>IN</sub>   | Input Leakage Current |     |     | 10  | μΑ    | Measured with input at V <sub>IH-EN</sub> max and V <sub>IL-EN</sub> min |

# **Table 10: Termination Resistors**

| Symbol           | Parameter                          | Min | Nom  | Max  | Units | Comments                                                  |

|------------------|------------------------------------|-----|------|------|-------|-----------------------------------------------------------|

| R <sub>HPD</sub> | HPD_sink input pull-down resistor. | 80K | 100k | 120K | Ω     | Guarantees HPD_sink is LOW when no display is plugged in. |

9

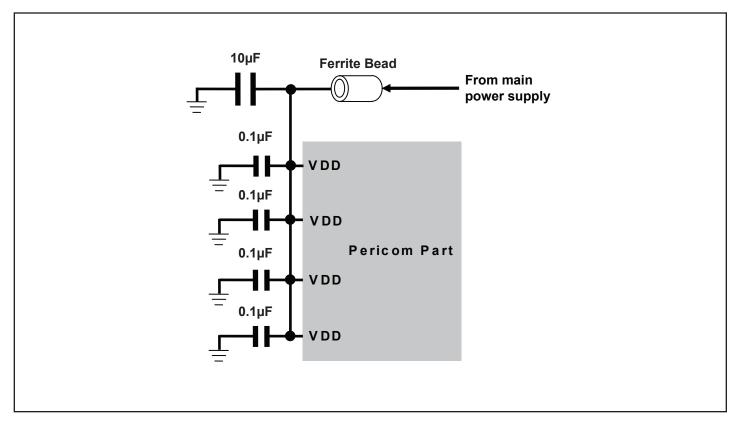

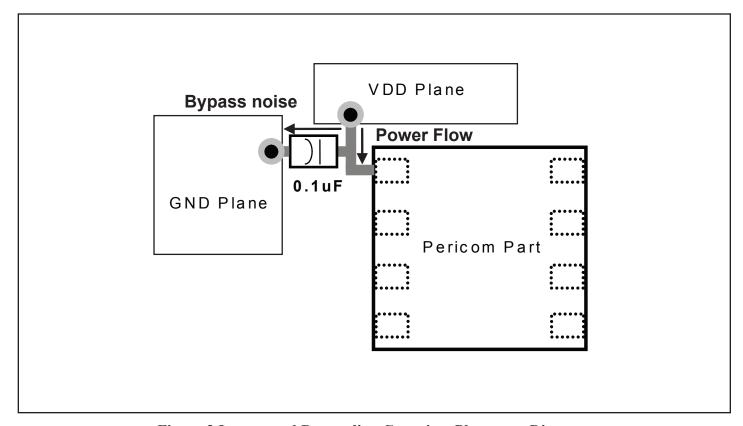

## **Recommended Power Supply Decoupling Circuit**

Figure 1 is the recommended power supply decoupling circuit configuration. It is recommended to put  $0.1\mu F$  decoupling capacitors on each  $V_{DD}$  pins of our part, there are four  $0.1\mu F$  decoupling capacitors are put in Figure 1 with an assumption of only four  $V_{DD}$  pins on our part, if there is more or less  $V_{DD}$  pins on our Pericom parts, the number of  $0.1\mu F$  decoupling capacitors should be adjusted according to the actual number of  $V_{DD}$  pins. On top of  $0.1\mu F$  decoupling capacitors on each  $V_{DD}$  pins, it is recommended to put a  $10\mu F$  decoupling capacitor near our part's  $V_{DD}$ , it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Figure 1 Recommended Power Supply Decoupling Circuit Diagram

### Requirements on the Decoupling Capacitors

There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

## **Layout and Decoupling Capacitor Placement Consideration**

- i. Each 0.1µF decoupling capacitor should be placed as close as possible to each V<sub>DD</sub> pin.

- ii. V<sub>DD</sub> and GND planes should be used to provide a low impedance path for power and ground.

- iii. Via holes should be placed to connect to V<sub>DD</sub> and GND planes directly.

- iv. Trace should be as wide as possible

- v. Trace should be as short as possible.

- vi. The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- vii.  $10\mu F$  capacitor should also be placed closed to our part and should be placed in the middle location of  $0.1\mu F$  capacitors.

- viii. Avoid the large current circuit placed close to our part; especially when it is shared the same  $V_{DD}$  and GND planes. Since large current flowing on our  $V_{DD}$  or GND planes will generate a potential variation on the  $V_{DD}$  or GND of our part.

Figure 2 Layout and Decoupling Capacitor Placement Diagram

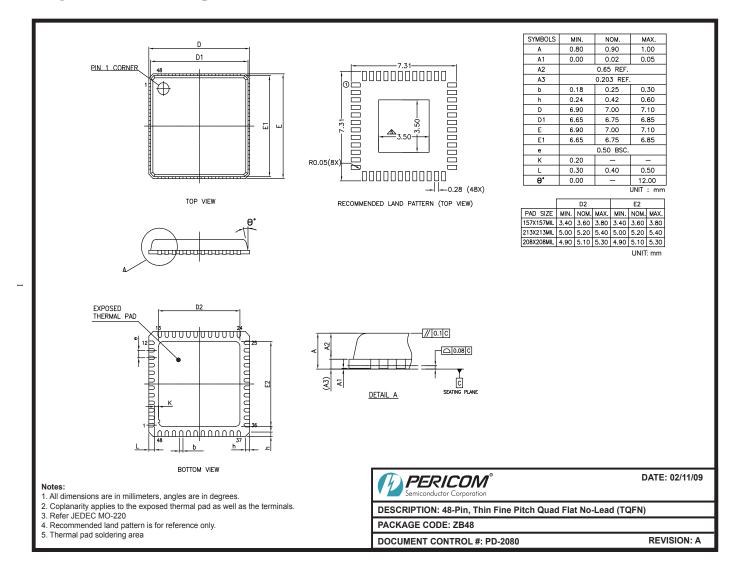

# Package Mechanical: 48-pin TQFN

#### Note:

- For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

- The epad size is 5.1 x 5.1 mm

### **Ordering Information**

| Ordering Code | Package Code | Package Description          |

|---------------|--------------|------------------------------|

| PI3VDP1430ZBE | ZBE          | 48-pin Pb-free & Green, TQFN |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X Suffix = Tape/Reel

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**Diodes Incorporated:**

PI3VDP1430ZBE PI3VDP1430ZBEX