The bg2406x series are highly integrated Li-lon and

Li-Pol linear chargers, targeted at space-limited

portable applications. The bq2406x series offers a variety of safety features and functional options,

while still implementing a complete charging system

in a small package. The battery is charged in three

phases: conditioning, constant or thermally regulated

current, and constant voltage. Charge is terminated

programmable charge timer provides a backup

safety feature for charge termination and is

dynamically adjusted during the thermal regulation

phase. The bq2406x automatically re-starts the charge if the battery voltage falls below an internal

threshold; sleep mode is set when the external input

supply is removed. Multiple versions of this device

family enable easy design of the bg2406x in cradle

chargers or in the end equipment, while using low

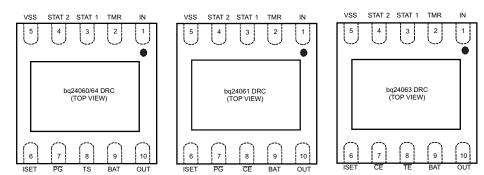

Pin Out

(Top View)

bq24061

10

9

8

7

6

OUT

BAT

CE

PG

ISET

current.

An

internal

minimum

## 1A SINGLE-CHIP Li-Ion/Li-Pol CHARGE MANAGEMENT IC WITH THERMAL REGULATION

DESCRIPTION

on

cost or high-end AC adapters.

IN

2

3

4

5

TMR

STAT1

STAT2

$V_{SS}$

based

#### FEATURES

- Ideal for Low-Dropout Designs for Single-Cell Li-Ion or Li-Pol Packs in Space Limited Applications

- Integrated Power FET and Current Sensor for up to 1-A Charge Applications

- Reverse Leakage Protection Prevents Battery

Drainage

- ±0.5% Voltage Regulation Accuracy

- Thermal Regulation Maximizes Charge Rate

- Charge Termination by Minimum Current and Time

- Precharge Conditioning With Safety Timer

- Status Outputs for LED or System Interface Indicate Charge, Fault, and Power Good Outputs

- Short-Circuit and Thermal Protection

- Automatic Sleep Mode for Low Power Consumption

- Small 3×3 mm MLP Package

- Selectable Battery Insertion and Battery Absent Detection

- Input Overvoltage Protection

6.5 V and 10.5 V Options

#### APPLICATIONS

A

- PDA, MP3 Players, Digital Cameras

- Internet Appliances and Handheld Devices

#### Li-lon or Li-Pol bq24061 **Battery Pack** Input Power Pack+ 10 1 IN ουτ R<sub>TMR</sub> 2 ÷ **≒ 4.7** μF 9 TMR BAT **49.9 k**Ω Pack 4.7 μF 1.5 kΩ 1.5 kΩ 3 STAT1 CE 4 PG STAT2 5 6 V<sub>SS</sub> ISET R<sub>SET</sub> **1.13 k**Ω Typical Application for Charging Between 350 mA and 1 A. Charge Enable and Input Power Status

#### **TYPICAL APPLICATION CIRCUIT**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

| Charge<br>Voltage | Input Over<br>Voltage | Termination<br>Enable | Safety<br>Timer<br>Enable | Power<br>Good<br>Status | IC<br>Enable | Pack<br>Temp | Pack Voltage<br>Detection<br>(Absent) | Devices <sup>(1)(2)(3)</sup> | Marking |

|-------------------|-----------------------|-----------------------|---------------------------|-------------------------|--------------|--------------|---------------------------------------|------------------------------|---------|

| 4.2 V             | 6.5 V                 | TMR pin               | TMR pin                   | PG pin                  | No           | TS pin       | With timer<br>enabled                 | bq24060                      | BPG     |

| 4.2 V             | 6.5 V                 | TMR pin               | TMR pin                   | PG pin                  | CE pin       | No           | With timer<br>enabled                 | bq24061                      | BPH     |

| 4.2 V             | 6.5 V                 | TE pin                | TMR pin                   | No                      | CE pin       | No           | With termination enabled              | bq24063                      | Preview |

| 4.2 V             | 10.5 V                | TMR pin               | TMR pin                   | PG pin                  | No           | TS pin       | With timer<br>enabled                 | bq24064                      | BSA     |

#### AVAILABLE OPTIONS

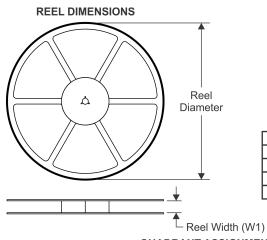

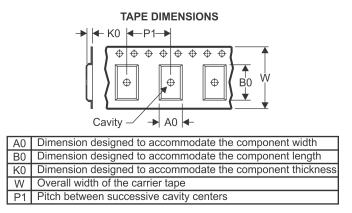

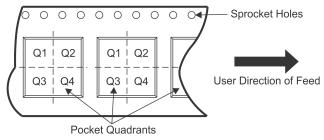

(1) The bq2406x are only available taped and reeled. Add suffix R to the part number for quantities of 3,000 devices per reel (e.g.,

bq24060BPGR). Add suffix T to the part number for quantities of 250 devices per reel (e.g., bq24060DRCT).

(2) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

(3) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

|                  |                                                                           | bq2406x                       |  |  |

|------------------|---------------------------------------------------------------------------|-------------------------------|--|--|

|                  | Supply voltage (IN with respect to Vss)                                   | -0.3 V to 18 V <sup>(2)</sup> |  |  |

|                  | Input voltage on IN, STATx, PG, TS, CE, TE, TMR (all with respect to Vss) | -0.3 V to V(IN)               |  |  |

|                  | Input voltage on OUT, BAT, ISET (all with respect to Vss)                 | –0.3 V to 7 V                 |  |  |

|                  | Output sink current (STATx) + PG 15 mA                                    |                               |  |  |

|                  | Output current (OUT pin)                                                  | 1.5 A                         |  |  |

| T <sub>A</sub>   | Operating free-air temperature range                                      | -40°C to 155°C                |  |  |

| T <sub>stg</sub> | Storage temperature range                                                 | –65°C to 150°C                |  |  |

| TJ               | Junction temperature range                                                | -40°C to 150°C                |  |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

(2) The bq2406x device can withstand up to 26 V for a maximum of 87 hours.

#### **RECOMMENDED OPERATING CONDITIONS**

|                   |                            |                                         | MIN  | ΤΥΡ Ι | MAX  | UNIT |

|-------------------|----------------------------|-----------------------------------------|------|-------|------|------|

| V <sub>(IN)</sub> | Supply voltage range       | Battery absent detection not functional | 3.5  |       | 4.35 | V    |

| V <sub>(IN)</sub> | Supply voltage range       | Battery absent detection functional     | 4.35 |       | 16.5 | V    |

| TJ                | Junction temperature       |                                         | 0    |       | 125  | °C   |

| R <sub>TMR</sub>  | $33K \le R_{TMR} \le 100K$ |                                         |      |       |      |      |

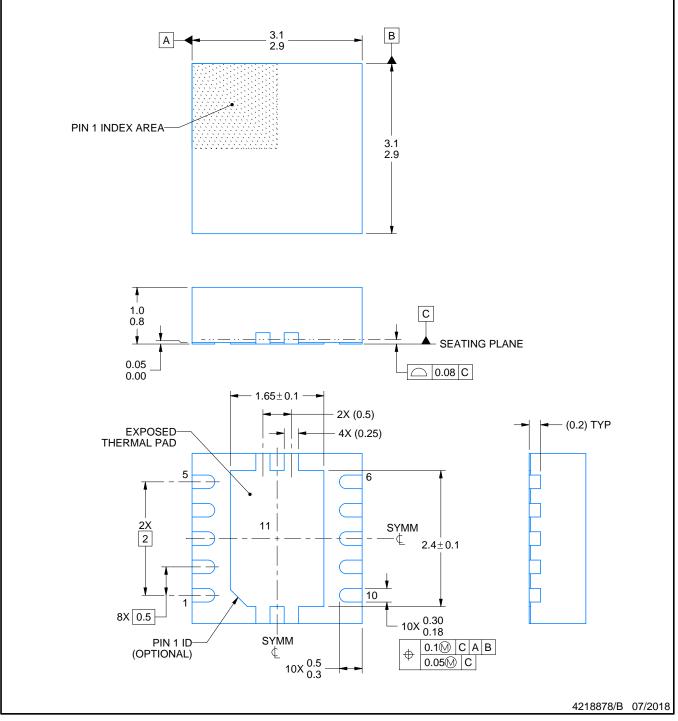

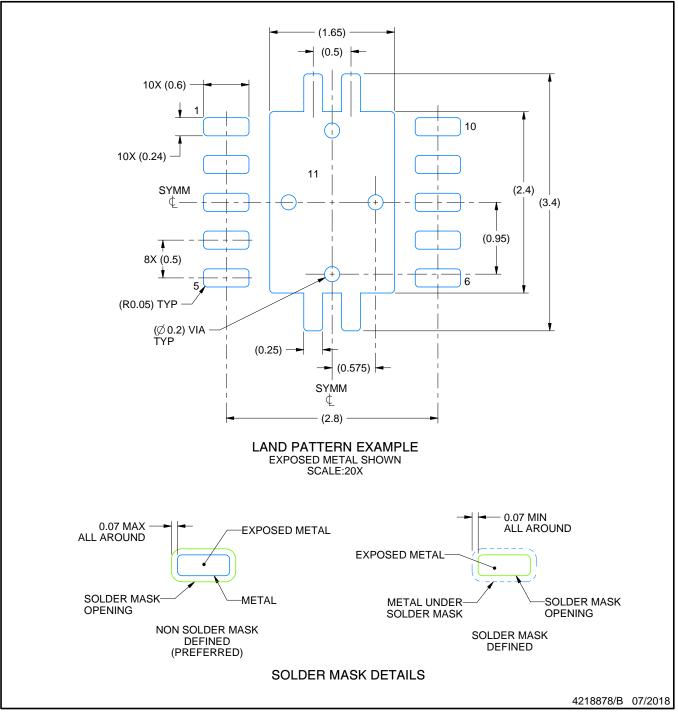

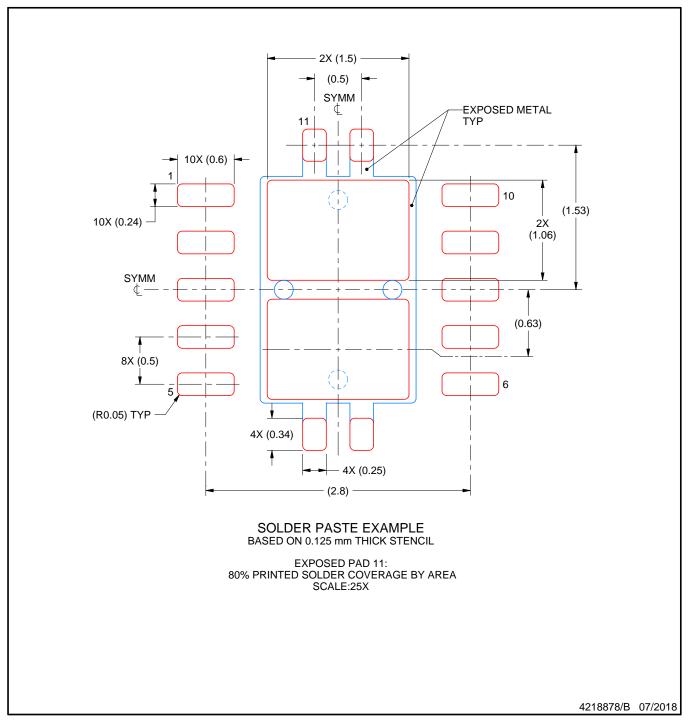

#### **DISSIPATION RATINGS**<sup>(1)</sup>

| PACKAGE    | θ <sub>JC</sub> (°C/W) | θ <sub>JA</sub> (°C/W) |

|------------|------------------------|------------------------|

| 10-pin DRC | 3.21                   | 46.87                  |

(1) This data is based on using the JEDEC High-K board and the exposed die pad is connected to a Cu pad on the board. This is connected to the ground plane by a 2x3 via matrix.

#### ELECTRICAL CHARACTERISTICS

over recommended operating,  $T_J = 0 - 125^{\circ}C$  range, See the Application Circuits section, typical values at  $T_J = 25^{\circ}C$  (unless otherwise noted)

|                                         | PARAMETER                                                            | TEST CONDITIONS                                                                                                                                                                                       |                                             |      | TYP  | MAX  | UNIT   |

|-----------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|------|------|--------|

| POWER DOWN THRESHOLD – UNDERVOLTAGE LOC |                                                                      | СКОИТ                                                                                                                                                                                                 |                                             |      |      |      |        |

| V <sub>(UVLO)</sub>                     | Power down threshold                                                 | $ \begin{array}{l} V(IN) = 0 \text{ V, increase V(OUT): } 0 \rightarrow 3 \text{ V OR} \\ V(OUT) = 0 \text{ V, increase V(IN): } 0 \rightarrow 3 \text{ V,} \\ \overline{CE} = LO^{(1)} \end{array} $ |                                             | 1.5  |      | 3.0  | V      |

| INPUT POWE                              | ER DETECTION, $\overline{CE}$ = HI or LOW, V(IN) >                   | 3.5 V                                                                                                                                                                                                 |                                             | 1    |      |      |        |

| V <sub>IN(DT)</sub>                     | Input power detection threshold                                      | V <sub>(IN)</sub> detected at [V(IN) – V(0                                                                                                                                                            | $DUT)] > V_{IN(DT)}$                        |      |      | 130  | mV     |

| V <sub>HYS(INDT)</sub>                  | Input power detection hysteresis                                     | Input power not detected at $[V_{(IN)} - V_{(OUT)}] < [V_{IN(DT)} - V_{HY}]$                                                                                                                          | (INDT)]                                     | 30   |      |      | mV     |

| T <sub>DGL(INDT1)</sub>                 | Deglitch time, input power detected status                           | $\label{eq:result} \hline \hline{PG}{:}HI \rightarrow LO, \mbox{ Thermal regula} \\ R_{TMR} = 50 \mbox{ K}\Omega \mbox{ or } V_{(TMR)} = 0 \\ \hline$                                                 |                                             | 1.5  |      | 3.5  | ms     |

| T <sub>DGL(NOIN)</sub>                  | Delay time, input power not detected status                          | $\overline{PG}$ : LO $\rightarrow$ HI after T <sub>DGL(NOIN</sub>                                                                                                                                     | )                                           |      |      | 10   | μs     |

| T <sub>DLY(CHGOFF)</sub>                | Charger off delay                                                    | Charger turned off after T <sub>DLY</sub> from PG: LO $\rightarrow$ HI; Timer re T <sub>DLY(CHGOFF)</sub>                                                                                             | <sub>(CHGOFF)</sub> , Measured<br>set after | 28   |      | 32   | ms     |

| INPUT OVER                              | VOLTAGE PROTECTION                                                   |                                                                                                                                                                                                       |                                             |      |      |      |        |

| M                                       | Insuit overveltage detection threshold                               |                                                                                                                                                                                                       | bq24060/61/63                               | 6.2  | 6.5  | 7.0  | V      |

| V <sub>(OVP)</sub>                      | Input overvoltage detection threshold                                | V(IN) increasing                                                                                                                                                                                      | bq24064                                     | 10.2 | 10.5 | 11.7 | v      |

| V                                       | Input overvoltage hysteresis                                         | V(IN) decreasing                                                                                                                                                                                      | bq24060/61/63                               | 0.1  |      | 0.2  | V      |

| V <sub>HYS(OVP)</sub>                   | input overvoltage hysteresis                                         |                                                                                                                                                                                                       | bq24064                                     | 0.3  |      | 0.5  | v      |

| T <sub>DGL(OVDET)</sub>                 | Input overvoltage detection delay                                    | $\overline{CE}$ = HI or LO, Measured from V(IN) > V <sub>(OVP)</sub> to PG: LO $\rightarrow$ HI; VIN increasing                                                                                       |                                             | 10   |      | 100  | μs     |

| T <sub>DGL(OVNDET)</sub>                | Input overvoltage not detected delay                                 | $\overline{CE}$ = HI or LO, Measured from V(IN) < V <sub>(OVP)</sub> to $\overline{PG}$ : HI $\rightarrow$ LO; V(IN) decreasing                                                                       |                                             | 10   |      | 100  | μs     |

| QUIESCENT                               | CURRENT                                                              |                                                                                                                                                                                                       |                                             |      |      |      |        |

| 1                                       | IN pin quiescent current, charger off                                | Input power detected, $\overline{CE}$ =                                                                                                                                                               | V <sub>(IN)</sub> = 6 V                     |      | 100  | 200  | μA     |

| I <sub>CC(CHGOFF)</sub>                 | na più quescent current, charger on                                  | HI                                                                                                                                                                                                    | V <sub>(IN)</sub> = 16.5 V                  |      | 300  |      | μΑ     |

| I <sub>CC(CHGON)</sub>                  | IN pin quiescent current, charger on                                 | Input power detected, $\overline{CE}$ =                                                                                                                                                               | LO, V <sub>BAT</sub> = 4.5 V                |      | 4    | 6    | mA     |

| I <sub>BAT(DONE)</sub>                  | Battery leakage current after termination into IC                    | Input power detected, charge $\overline{CE} = LO$                                                                                                                                                     | e terminated,                               |      | 1    | 5    | μA     |

| I <sub>BAT(CHGOFF)</sub>                | Battery leakage current into IC, charger off                         | Input power detected, $\overline{CE} =$<br>input power not detected, $\overline{CE}$                                                                                                                  |                                             |      | 1    | 5    | μA     |

| TS PIN COM                              | PARATOR                                                              |                                                                                                                                                                                                       |                                             |      |      |      |        |

| V <sub>(TS1)</sub>                      | Lower voltage temperature threshold                                  | Hot detected at $V(TS) < V_{(TS)}$                                                                                                                                                                    | (31); NTC thermistor                        | 29   | 30   | 31   | %V(IN) |

| V <sub>(TS2)</sub>                      | Upper voltage temperature threshold                                  | Cold detected at V(TS) > V(T                                                                                                                                                                          | (S2); NTC thermistor                        | 60   | 61   | 62   | %V(IN) |

| V <sub>HYS(TS)</sub>                    | Hysteresis                                                           | Temp OK at V(TS) > [ $V_{(TS1)} + V_{HYS(TS)}$ ] OR<br>V <sub>(TS)</sub> < [ $V_{(TS2)} - V_{HYS(TS)}$ ]                                                                                              |                                             |      | 2    |      | %V(IN) |

| CE INPUT                                |                                                                      | , /                                                                                                                                                                                                   |                                             |      |      |      |        |

| V <sub>IL</sub>                         | Input (low) voltage                                                  | V(CE) increasing                                                                                                                                                                                      |                                             | 0    |      | 1    | V      |

| V <sub>IH</sub>                         | Input (high) voltage                                                 | V(CE) decreasing                                                                                                                                                                                      |                                             | 2.0  |      |      | V      |

| STAT1, STAT                             | T2 AND $\overline{PG}$ OUTPUTS , V(IN) $\ge$ V <sub>O(REG)</sub> + V | (DO-MAX)                                                                                                                                                                                              |                                             |      |      |      |        |

| V <sub>OL</sub>                         | Output (low) saturation voltage                                      | loutput = 5 mA (sink)                                                                                                                                                                                 |                                             |      |      | 0.5  | V      |

| THERMAL SH                              | HUTDOWN                                                              |                                                                                                                                                                                                       |                                             |      |      |      |        |

| T <sub>(SHUT)</sub>                     | Temperature trip                                                     | Junction temperature, temp                                                                                                                                                                            | rising                                      |      | 155  |      | °C     |

| T <sub>(SHUTHYS)</sub>                  | Thermal hysteresis                                                   | Junction temperature                                                                                                                                                                                  |                                             |      | 20   |      | °C     |

(1) Specified by design, not production tested.

#### **ELECTRICAL CHARACTERISTICS (Continued)**

over recommended operating,  $T_J = 0-125^{\circ}C$  range, See the Application Circuits section, typical values at  $T_J = 25^{\circ}C$  (unless otherwise noted)

|                            | PARAMETER                                                                                           | TEST CONDITIONS                                                                                                                                                                    |                                                                  |          | TYP     | MAX     | UNIT |

|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------|---------|---------|------|

| VOLTAGE RE                 | EGULATION, V(IN) $\ge$ V <sub>O(REG)</sub> + V <sub>(DO</sub> .                                     | <sub>MAX)</sub> , I <sub>(TERM)</sub> < I <sub>(OUT)</sub> < I <sub>O(OUT)</sub> , C                                                                                               | HARGER ENABLE                                                    | D, NO FA | ULT CO  | NDITIO  | NS   |

| V <sub>O(REG)</sub>        | Output voltage                                                                                      | bq24060/61/63/64                                                                                                                                                                   |                                                                  |          | 4.20    |         | V    |

|                            |                                                                                                     | $T_A = 25^{\circ}C$                                                                                                                                                                |                                                                  | -0.5%    |         | 0.5%    |      |

| V <sub>O(TOL)</sub>        | Voltage regulation accuracy                                                                         |                                                                                                                                                                                    |                                                                  | -1%      |         | 1%      |      |

| V <sub>(DO)</sub>          | Dropout voltage, V(IN) – V(OUT)                                                                     | $I_{(OUT)} = 1 \text{ A}$                                                                                                                                                          |                                                                  |          |         | 750     | mV   |

|                            | EGULATION , V(IN) > V(OUT) > V                                                                      | (==)                                                                                                                                                                               | O FAULT CONDITI                                                  | ONS DET  | ECTED   |         |      |

| I <sub>O(OUT)</sub>        | Output current range                                                                                | $V_{(BAT)} > V_{(LOWV)}, I_{O(OUT)} = I_{(OUT)}$<br>$V_{(SET)}/R_{SET}$                                                                                                            |                                                                  | 100      |         | 1000    | mA   |

| V <sub>(SET)</sub>         | Output current set voltage                                                                          | $V(ISET) = V_{(SET)}, V_{(LOWV)} < V(ISET)$                                                                                                                                        | BAT) ≤ V <sub>O(REG)</sub>                                       | 2.45     | 2.50    | 2.55    | V    |

|                            |                                                                                                     | $100 \text{ mA} \le I_{O(OUT)} \le 1000 \text{ mA}$                                                                                                                                | $mA \times k\Omega$                                              | 315      | 335     | 355     |      |

| K <sub>(SET)</sub>         | Output current set factor                                                                           | $10 \text{ mA} \le I_{O(OUT)} < 100 \text{ mA}$                                                                                                                                    | Volts                                                            | 315      | 372     | 430     |      |

| R <sub>ISET</sub>          | External resistor range                                                                             | Resistor connected to ISET pir                                                                                                                                                     | <u>ו</u>                                                         | 0.7      |         | 10      | kΩ   |

| VOLTAGE AN                 | ND CURRENT REGULATION TIMIN<br>R <sub>TMR</sub> = 50K or V(TMR) = OPEN; The                         |                                                                                                                                                                                    |                                                                  | D, NO FA | AULT CO | ONDITIC | ONS  |

| T <sub>PWRUP(CHG)</sub>    | Input power detection to full<br>charge current time delay                                          | $ \begin{array}{l} \mbox{Measured from $\overline{PG}$:HI $\rightarrow$ LO to} \\ \hline \mbox{CE} = LO,  I_{O(OUT)} = 1  A,  V(BAT) \end{array} $                                 |                                                                  |          | 25      | 35      | ms   |

| T <sub>PWRUP(EN)</sub>     | Charge enable to full charge current delay                                                          | Measured from $\overline{CE}$ :HI $\rightarrow$ LO to $I_{O(OUT)}$ = 1A, $V_{(BAT)}$ = 3.5 V, $V_{(II)}$ power detected                                                            |                                                                  | 25       | 35      | ms      |      |

| T <sub>PWRUP(LDO)</sub>    | Input power detection to voltage<br>regulation delay, LDO mode set,<br>no battery or load connected | Measured from $\overrightarrow{PG}$ :HI $\rightarrow$ LO to<br>charge voltage regulation;<br>V <sub>(TMR)</sub> = OPEN, LDO mode se<br>load at OUT pin, $\overrightarrow{CE}$ = LO | . ,                                                              |          | 25      | 35      | ms   |

|                            | E AND OUTPUT SHORT-CIRCUIT C<br>O FAULT CONDITIONS DETECTED                                         |                                                                                                                                                                                    |                                                                  |          |         |         | ER   |

| V <sub>(LOWV)</sub>        | Precharge to fast-charge transition threshold                                                       | V <sub>(BAT)</sub> increasing                                                                                                                                                      | , <b>.</b>                                                       | 2.8      | 2.95    | 3.15    | V    |

| V <sub>(SC)</sub>          | Precharge to short-circuit transition threshold                                                     | V <sub>(BAT)</sub> decreasing                                                                                                                                                      |                                                                  | 1.2      | 1.4     | 1.6     | V    |

| V <sub>(SCIND)</sub>       | Short-circuit indication                                                                            | V <sub>(BAT)</sub> decreasing                                                                                                                                                      |                                                                  | 1.6      | 1.8     | 2.0     |      |

| I <sub>O(PRECHG)</sub>     | Precharge current range                                                                             | $V_{(SC)} < V_{I(BAT)} < V_{(LOWV)}, t < T_{(IO(PRECHG)} = K_{(SET)} \times V_{(PRECHG)}$                                                                                          | PRECHG)<br>/R <sub>(ISET)</sub>                                  | 10       |         | 100     | mA   |

| V <sub>(PRECHG)</sub>      | Precharge set voltage                                                                               | $V_{(ISET)} = V_{(PRECHG)}, V_{(SC)} < V_{I(t)}$<br>t < T <sub>(PRECHG)</sub>                                                                                                      | $V_{(ISET)} = V_{(PRECHG)}, V_{(SC)} < V_{I(BAT)} < V_{(LOWV)},$ |          | 250     | 280     | mV   |

|                            | Output shorted regulation current                                                                   | $V_{SS} \leq V_{(BAT)} \leq V_{(SCI)},$                                                                                                                                            | $V_{POR} < V_{IN} < 6.0$<br>V                                    | 15       | 22      | 30      | mA   |

| IO(SHORT)                  |                                                                                                     |                                                                                                                                                                                    |                                                                  |          | 25      |         |      |

| TEMPERATU                  | RE REGULATION (Thermal regulat                                                                      | ion™), CHARGER ENABLED,                                                                                                                                                            | NO FAULT CONDIT                                                  | IONS DE  | TECTE   | )       |      |

| T <sub>J(REG)</sub>        | Temperature regulation limit                                                                        | V(IN) = 5.5 V, V(BAT) = 3.2 V,<br>current set to 1A                                                                                                                                | Fast charge                                                      | 101      | 112     | 125     | °C   |

| I <sub>(MIN_TJ(REG))</sub> | Minimum current in thermal regulation                                                               | V(LOWV) < V(BAT) < VO(REG<br>< 3.5kΩ                                                                                                                                               | 6), 0.7kΩ < RISET                                                |          | 200     | 250     | mA   |

#### ELECTRICAL CHARACTERISTICS (Continued)

over recommended operating,  $T_J = 0-125^{\circ}C$  range, See the Application Circuits section, typical values at  $T_J = 25^{\circ}C$  (unless otherwise noted)

|                        | PARAMETER                                                                          | TEST CONDIT                                                                                                      | TEST CONDITIONS        |                |          | MAX                                      | UNIT  |

|------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------|----------------|----------|------------------------------------------|-------|

| CHARGE T<br>regulation | ERMINATION DETECTION, V <sub>O(RI</sub><br>LOOP NOT ACTIVE, R <sub>TMR</sub> = 50K | <sub>EG)</sub> = 4.2 V, CHARGER ENABLI<br>or TMR pin OPEN                                                        | ED, NO FAULT CON       | DITIONS        | DETECTED | Therma                                   | I     |

| I <sub>(TERM)</sub>    | Termination detection current range                                                | $V_{(BAT)} > V_{(RCH)}, I_{(TERM)} = K_{(SET)}$                                                                  | 10                     |                | 100      | mA                                       |       |

| V <sub>(TERM)</sub>    | Charge termination detection set voltage <sup>(1)</sup>                            | $V_{(BAT)} > V_{(RCH)}$                                                                                          |                        | 225            | 250      | 275                                      | mV    |

| T <sub>DGL(TERM)</sub> | Deglitch time, termination detected                                                | V <sub>(ISET)</sub> decreasing                                                                                   |                        | 15             | 25       | 35                                       | ms    |

| BATTERY I              | RECHARGE THRESHOLD                                                                 |                                                                                                                  |                        | r.             |          |                                          |       |

| V <sub>(RCH)</sub>     | Recharge threshold detection                                                       | $[V_{O(REG)}-V(BAT)] > V_{(RCH)}$                                                                                |                        | 75             | 100      | 135                                      | mV    |

| T <sub>DGL(RCH)</sub>  | Deglitch time, recharge detection                                                  | V <sub>(BAT)</sub> decreasing                                                                                    |                        | 15             | 25       | 35                                       | ms    |

| TIMERS, C              | E = LO, CHARGER ENABLED, N                                                         | O FAULT CONDITIONS DETEC                                                                                         | CTED, V(TMR) < 3 V,    | TIMERS E       | ENABLED  | L. L |       |

| T <sub>(CHG)</sub>     | Charge safety timer range                                                          | $T_{(CHG)} = K_{(CHG)} \times R_{TMR}$ ; therma                                                                  | 3                      |                | 10       | hours                                    |       |

| K <sub>(CHG)</sub>     | Charge safety timer constant                                                       | $V_{(BAT)} > V_{(LOWV)}$                                                                                         |                        | 0.08           | 0.1      | 0.12                                     | hr/kΩ |

| T <sub>(PCHG)</sub>    | Pre-charge safety timer range                                                      | $T_{(PCHG)} = K_{(PCHG)} \times T_{(CHG)}$ ; The loop not active                                                 | 1080                   |                | 3600     | sec                                      |       |

| K <sub>(PCHG)</sub>    | Pre-charge safety timer<br>constant                                                | V <sub>(BAT)</sub> < V <sub>(LOWV)</sub>                                                                         | 0.08                   | 0.1            | 0.12     |                                          |       |

| V <sub>TMR(OFF)</sub>  | Charge timer and termination enable threshold                                      | [Charge timer AND<br>termination disabled] at V <sub>(TMR)</sub><br>> V <sub>TMR(OFF)</sub>                      | bq24060/61/64          | 2.5            | 3.0      | 3.5                                      | V     |

|                        | Charge timer enable threshold                                                      | [Charge timer disabled] at $V_{(TMR)} > V_{TMR(OFF)}$                                                            | bq24063                |                |          |                                          |       |

| I <sub>TMR</sub>       | TMR pin source current                                                             | V <sub>(TMR)</sub> = 3.5 V, V <sub>(IN)</sub> = 4.5 V                                                            |                        | 1              |          | 6                                        | μA    |

| BATTERY I              | DETECTION THRESHOLDS                                                               |                                                                                                                  |                        | r.             |          |                                          |       |

| IDET(DOWN)             | Battery detection current (sink)                                                   | $2 V < V_{(BAT)} < V_{O(REG)}$                                                                                   |                        | 1              | 2        | 3.2                                      | mA    |

| I <sub>DET(UP)</sub>   | Battery detection current (source)                                                 | $2 V < V_{(BAT)} < V_{O(REG)}$                                                                                   |                        | ۱ <sub>С</sub> | (PRECHG) |                                          |       |

| T <sub>(DETECT)</sub>  | Battery detection time                                                             | 2 V < V <sub>(BAT)</sub> < V <sub>O(REG)</sub> , Therma active; $R_{TMR} = 50 \text{ k}\Omega$ , $I_{DET(down})$ | al regulation loop not | 85             | 120      | 150                                      | ms    |

| TIMER FAU              | ILT RECOVERY                                                                       |                                                                                                                  | · · · ·                | r.             |          |                                          |       |

| I <sub>(FAULT)</sub>   | Fault Current (source)                                                             | V <sub>(OUT)</sub> < V <sub>(RCH)</sub>                                                                          | -12                    | -10            | -8       | mA                                       |       |

| CHARGE O               | VERCURRENT DETECTION, V(I                                                          | N) ≥ 4.5 V, CHARGER ENABLE                                                                                       | D                      |                |          |                                          |       |

| I <sub>CH(OI)</sub>    | Charge overcurrent detection threshold                                             | V <sub>(ISET)</sub> = VSS                                                                                        |                        | 2              |          | А                                        |       |

| T <sub>DGL(OI)</sub>   | Overcurrent detection delay time                                                   | Measured from $V_{(ISET)} = VSS t$                                                                               | to $I_{O(OUT)} = 0$    |                | 100      |                                          | μs    |

|                        |                                                                                    | 1                                                                                                                |                        | 1              |          |                                          |       |

(1) The voltage on the ISET pin is compared to the  $V_{(TERM)}$  voltage to determine when the termination should occur.

#### **DEVICE INFORMATION**

#### **PIN ASSIGNMENT**

#### **TERMINAL FUNCTIONS, REQUIRED COMPONENTS**

| TERMINAL NO.              |            | TERMINAL NO. |         |     |                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|------------|--------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                      | bq24060/64 | bq24061      | bq24063 | I/O | DESCRIPTION AND REQUIRED COMPONENTS                                                                                                                                                                                                                                                                                                             |

| IN                        | 1          | 1            | 1       | I   | Charge Input Voltage and internal supply. Connect a 1- $\mu F$ (minimum) capacitor from IN to VSS. $C_{IN}{\geq}C_{OUT}$                                                                                                                                                                                                                        |

| TMR                       | 2          | 2            | 2       | I   | Safety Timer Program Input, timer disabled if floating. Connect a resistor to VSS pin to program safety timer timeout value                                                                                                                                                                                                                     |

| STAT1                     | 3          | 3            | 3       | 0   | Charge Status Output 1 (open-collector, seeTable 3)                                                                                                                                                                                                                                                                                             |

| STAT2                     | 4          | 4            | 4       | 0   | Charge Status Output 2 (open-collector, see Table 3)                                                                                                                                                                                                                                                                                            |

| VSS                       | 5          | 5            | 5       | I   | Ground                                                                                                                                                                                                                                                                                                                                          |

| ISET                      | 6          | 6            | 6       | 0   | Charge current set point, resistor connected from ISET to VSS sets charge current value. Connect a 0.47- $\mu$ F capaciator from BAT to ISET.                                                                                                                                                                                                   |

| PG                        | 7          | 7            | _       | 0   | Power Good status output (open-collector), active low                                                                                                                                                                                                                                                                                           |

| CE                        | _          | 8            | 7       | I   | Charge enable Input. $\overline{CE}$ = LO enables charger. $\overline{CE}$ = HI disables charger.                                                                                                                                                                                                                                               |

| TE                        | _          | _            | 8       | I   | Termination enable Input. $\overline{TE}$ = LO enables termination detection and battery absent detection. $\overline{TE}$ = HI disables termination detection and battery absent detection.                                                                                                                                                    |

| TS                        | 8          | _            | _       | I   | Temperature Sense Input, connect to battery pack thermistor. Connect an external resistive divider to program temperature thresholds.                                                                                                                                                                                                           |

| BAT                       | 9          | 9            | 9       | I   | Battery Voltage Sense Input. Connect to the battery positive terminal. Connect a 200- $\Omega$ resistor from BAT to OUT.                                                                                                                                                                                                                        |

| OUT                       | 10         | 10           | 10      | 0   | Charge current output. Connect to the battery positive terminal. Connect a 1- $\mu F$ (minimum) capacitor from OUT to VSS.                                                                                                                                                                                                                      |

| Exposed<br>Thermal<br>Pad | Pad        | Pad          | Pad     |     | There is an internal electrical connection between the exposed thermal pad<br>and Vss pin of the IC. The exposed thermal pad must be connected to the<br>same potential as the VSS pin on the printed circuit board. Do not use the<br>thermal pad as the primary ground input for the IC. VSS pin must be<br>connected to ground at all times. |

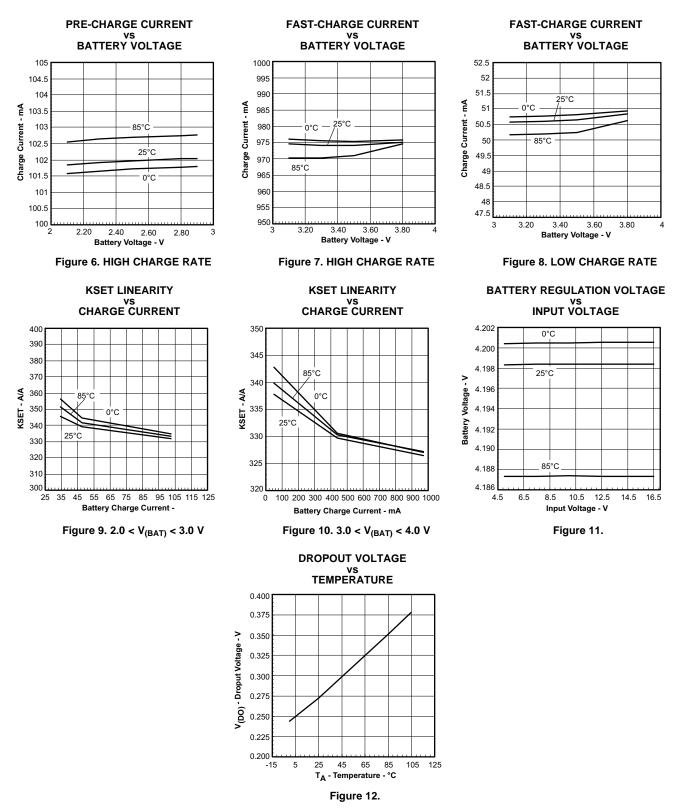

#### **TYPICAL OPERATING CHARACTERISTICS**

Measured using the typical application circuit shown previously.

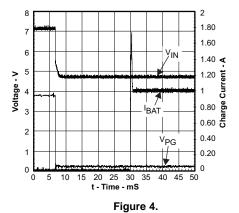

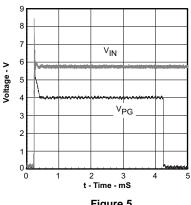

INPUT OVP RECOVERY TRANSIENTS

#### **TYPICAL OPERATING CHARACTERISTICS (continued)**

Measured using the typical application circuit shown previously.

#### FUNCTIONAL DESCRIPTION

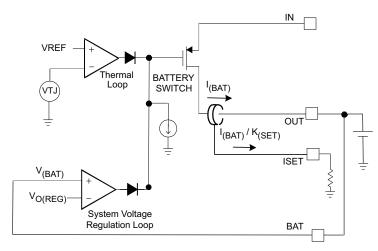

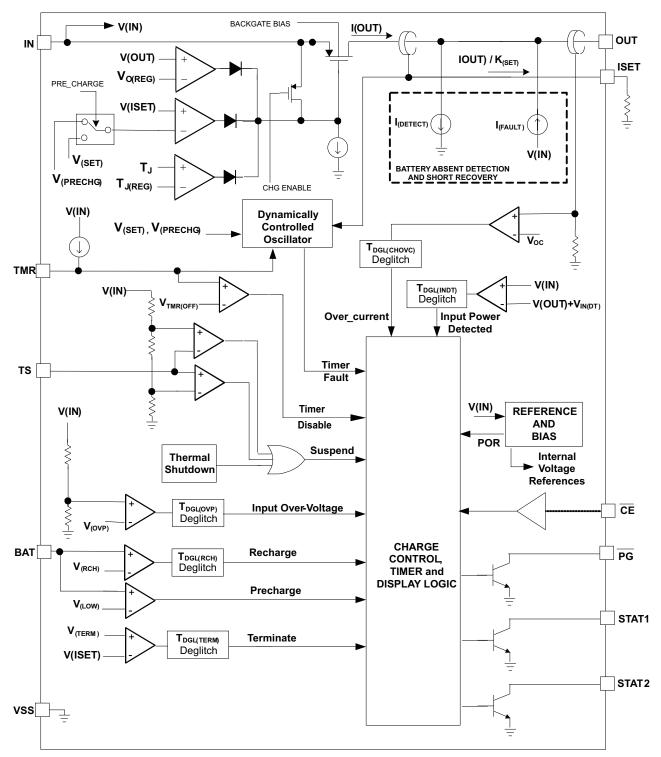

The charge current is programmable using external components ( $R_{ISET}$  resistor). The charge process starts when an external input power is connected to the system, the charger is enabled by  $\overline{CE} = LO$  and the battery voltage is below the recharge threshold, V(BAT) < V<sub>(RCH)</sub>. When the charge cycle starts a safety timer is activated, if the safety timer function is enabled. The safety timer timeout value is set by an external resistor connected to TMR pin.

When the charger is enabled two control loops modulate the battery switch drain to source impedance to limit the BAT pin current to the programmed charge current value (charge current loop) or to regulate the BAT pin voltage to the programmed charge voltage value (charge voltage loop). If V(BAT) < V(LOWV) (3 V typical) the BAT pin current is internally set to 10% of the programmed charge current value.

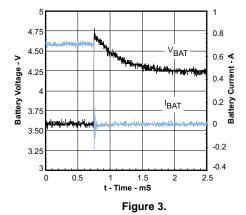

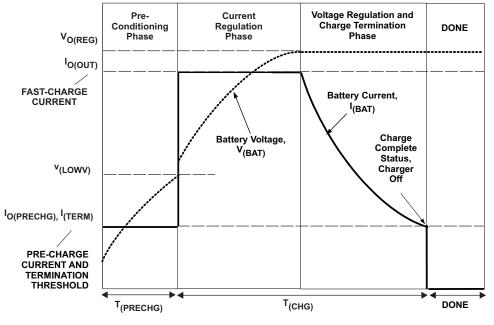

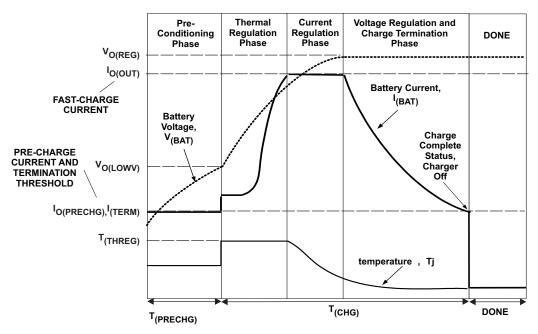

A typical charge profile is shown below, for an operation condition that does not cause the IC junction temperature to exceed  $T_{J(REG)}$ , (112°C typical).

Figure 13. Charging Profile With T<sub>J(REG)</sub>

If the operating conditions cause the IC junction temperature to exceed  $T_{J(REG)}$ , the charge cycle is modified, with the activation of the integrated thermal control loop. The thermal control loop is activated when an internal voltage reference, which is inversely proportional to the IC junction temperature, is lower than a fixed, temperature stable internal voltage. The thermal loop overrides the other charger control loops and reduces the charge current until the IC junction temperature returns to  $T_{J(REG)}$ , effectively regulating the IC junction temperature.

Figure 14. Thermal Regulation Circuit

A modified charge cycle, with the thermal loop active, is shown in Figure 15.

Figure 15. Charge Profile, Thermal Loop Active

#### FUNCTIONAL BLOCK DIAGRAM

#### **APPLICATION CIRCUITS**

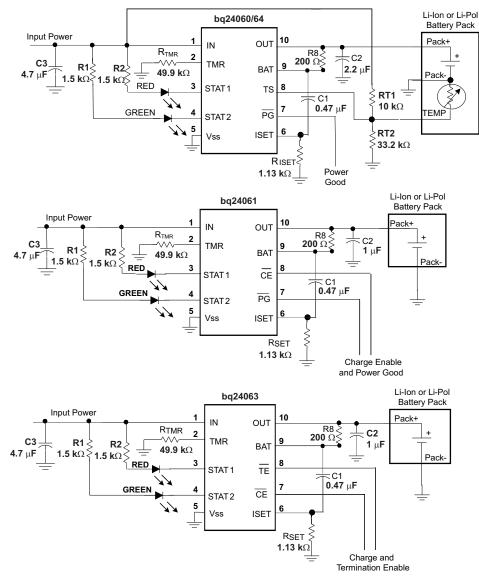

The typical application diagrams shown here are configured for 750 mA fast charge current, 75 mA pre-charge current, 5 hour safety timer and 30 min pre-charge timer.

NOTE: Temp window set between 0°C and 45°C for application w/TS pin.

Figure 16. Application Circuits

#### **OPERATING MODES**

#### **Power Down**

The bq2406x family is in a power-down mode when the input power voltage (IN) is below the power-down threshold  $V_{(PDWN)}$ . During the power down mode all IC functions are off, and the host commands at the control pins are not interpreted. The integrated power mosfet connected between IN and OUT pins is off, the status output pins STAT1 and STAT2 are set to high impedance mode and  $\overline{PG}$  output is set to the high impedance state.

#### Sleep Mode

The bq2406x enters the sleep mode when the input power voltage (IN) is above the power down threshold V(PDWN) but still lower than the input power detection threshold,  $V(IN) < V(OUT) + V_{IN(DT)}$ .

During the sleep mode the charger is off, and the host commands at the control pins are not interpreted. The integrated power mosfet connected between IN and OUT pins is off, the status output pins STAT1 and STAT2 are set to the high impedance state and the  $\overline{PG}$  output indicates input power not detected.

The sleep mode is entered from any other state, if the input power (IN) is not detected.

#### Overvoltage Lockout

The input power is detected when the input voltage  $V(IN) > V(OUT) + V_{IN(DT)}$ . When the input power is detected the bq2460x transitions from the sleep mode to the power-on-reset mode. In this mode of operation an internal timer  $T_{(POR)}$  is started and internal blocks are reset (power-on-reset). Until the timer expires the STAT1 and STAT2 outputs indicate charger OFF, and the  $\overline{PG}$  output indicates the input power status as not detected.

At the end of the power-on-reset delay the internal comparators are enabled, and the STAT1, STAT2 and  $\overline{PG}$  pins are active.

#### Stand-By Mode

In the bq24061/63 the stand-by mode is started at the end of the power-on-reset phase, if the input power is detected and  $\overline{CE}$  = HI. In the stand-by mode selected blocks in the IC are operational, and the control logic monitors system status and control pins to define if the charger will set to on or off mode. The quiescent current required in stand-by mode is 100 µA typical.

If the CE pin is not available the bq2406x enters the begin charge mode at the end of the power-on-reset phase.

#### Begin Charge Mode

All blocks in the IC are powered up, and the bq2406x is ready to start charging the battery pack. A new charge cycle is started when the control logic decides that all conditions required to enable a new charge cycle are met. During the begin charge phase all timers are reset, after that the IC enters the charging mode.

#### Charging Mode

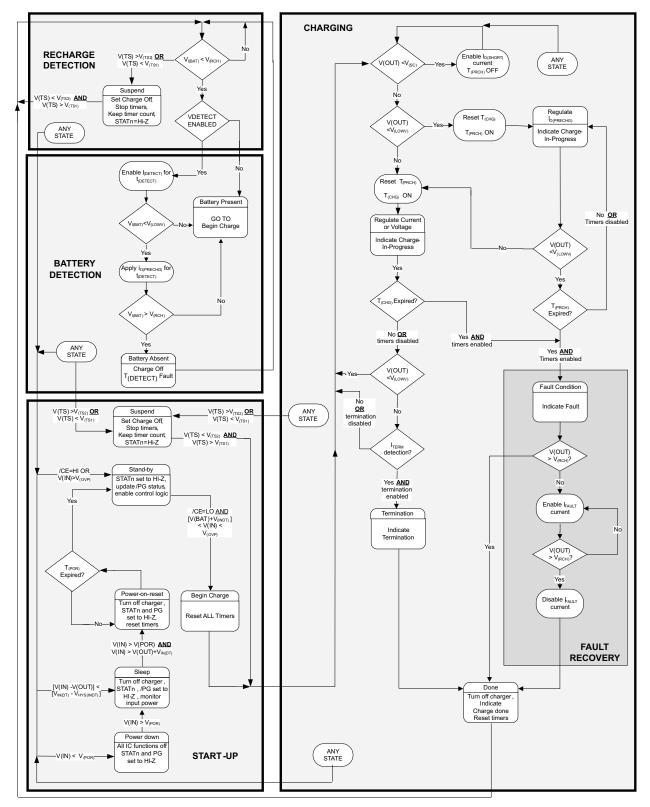

When the charging mode is active the bq2406x executes the charging algorithm, as described in the operational flow chart, Figure 17.

#### Suspend Mode

The suspend mode is entered when the pack temperature is not within the valid temperature range. During the suspend mode the charger is set to off, but the timers are not reset.

The normal charging mode resumes when the pack temperature is within range.

#### LDO Mode Operation

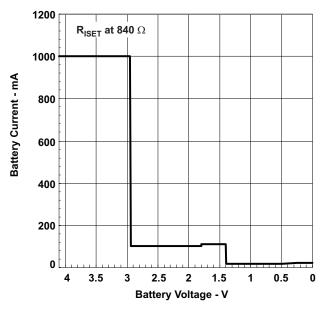

The *LDO Mode* (TMR pin open circuit) disables the charging termination circuit, disables the battery detect routine and holds the safety timer clock in reset. This is often used for operation without a battery or in production testing. This mode is different than a typical LDO since it has different modes of operation, and delivers less current at lower output voltages. See Figure 24 for the output current versus the output voltage. Note that a load on the output prior to powering the device may keep the part in short-circuit mode. Also, during normal operation, exceeding the programmed fast charge level causes the output to drop, further restricting the output power, and soon ends up in short-circuit mode. Operation with a battery or keeping the average load current below the programmed current level prevents this type of latch up. The out pin current can be monitored via the ISET pin. If in LDO mode without a battery present, It is recommended that a 200- $\Omega$  feedback resistor, R8, be used, see Figure 16.

#### STATE MACHINE DIAGRAM

Figure 17. Operational Flow Chart

#### CONTROL LOGIC OVERVIEW

An external host can enable or disable the charging process using a dedicated control pin,  $\overline{CE}$ . A low-level signal on this pin enables the charge, and a high-level signal disables the charge. The bq2460x is in stand-by mode with  $\overline{CE} = HI$ . When the charger function is enabled ( $\overline{CE} = LO$ ) a new charge is initiated.

Table 1 describes the charger control logic operation, in bq2460x versions without the TS pin the pack temp status is internally set to OK.

|                              |    |                 |                             |                            | •                        | -              |                                    |               |                           |

|------------------------------|----|-----------------|-----------------------------|----------------------------|--------------------------|----------------|------------------------------------|---------------|---------------------------|

| bq2460X<br>OPERATION<br>MODE | CE | INPUT<br>POWER  | TIMER<br>FAULT<br>(latched) | OUTPUT<br>SHORT<br>CIRCUIT | TERMINATION<br>(latched) | PACK<br>TEMP   | THERMAL<br>SHUTDOWN                | POWER<br>DOWN | CHARGER<br>POWER<br>STAGE |

| POWER<br>DOWN                | LO | Low             | Х                           | Х                          | Х                        | Х              | Х                                  | Yes           | OFF                       |

| SLEEP                        | Х  | Not<br>Detected | Х                           | Х                          | Х                        | Х              | Х                                  | No            | OFF                       |

| STANDBY                      | Н  | Detected        | Х                           | Х                          | Х                        | Х              | Х                                  | No            | OFF                       |

| SEE STATE                    | LO | Detected        | Х                           | Yes                        | Х                        | Х              | Х                                  | No            |                           |

| DIAGRAM                      | LO | Detected        | No                          | No                         | Yes                      | Х              | Х                                  | No            | OFF                       |

|                              | LO | Detected        | Yes                         | No                         | No                       | Х              | Х                                  | No            | IFAULT                    |

|                              | LO | Detected        | No                          | No                         | Yes                      | Absent         | T <sub>J</sub> < T <sub>SHUT</sub> | No            | IDETECT                   |

|                              | LO | Detected        | No                          | No                         | No                       | Hot or<br>Cold | $T_J < T_{SHUT}$                   | No            | OFF                       |

|                              | LO | Detected        | No                          | No                         | No                       | Ok             | T <sub>J</sub> < T <sub>SHUT</sub> | No            | OFF                       |

|                              | LO | Over<br>Voltage | No                          | No                         | No                       | Ok             | T <sub>J</sub> < T <sub>SHUT</sub> | No            | OFF                       |

| CHARGING                     | LO | Detected        | No                          | No                         | No                       | Ok             | T <sub>J</sub> < T <sub>SHUT</sub> | No            | ON                        |

Table 1. Control Logic Functionality

In both STANDBY and SUSPEND modes the charge process is disabled. In the STANDBY mode all timers are reset; in SUSPEND mode the timers are held at the count stored when the suspend mode was set.

The timer fault, termination and output short circuit variables shown in the control logic table are latched in the detection circuits, outside the control logic. Refer to the timers, termination and short circuit protection sections for additional details on how those latched variables are reset.

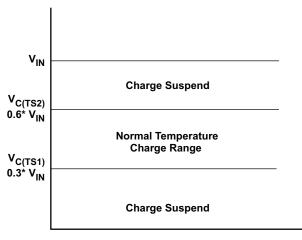

#### TEMPERATURE QUALIFICATION (Applies only to versions with TS pin option)

The bq2406x devices continuously monitor the battery temperature by measuring the voltage between the TS and VSS pins. The IC compares the voltage on the TS pin against the internal  $V_{(TS1)}$  and  $V_{(TS2)}$  thresholds to determine if charging is allowed. Once a temperature outside the  $V_{(TS1)}$  and  $V_{(TS2)}$  thresholds is detected the IC immediately suspends the charge. The IC suspends charge by turning off the power FET and holding the timer value (i.e., timers are NOT reset). Charge is resumed when the temperature returns to the normal range.

#### Figure 18. Battery Temperature Qualification With NTC Thermistor

The external resistors  $R_{T1}$  and  $R_{T2}$  (see application diagram) enable selecting a temperature window. If  $R_{TC}$  and  $R_{TH}$  are the thermistor impedances for the Cold and Hot thresholds the values for  $R_{T1}$  and  $R_{T2}$  can be calculated as follows, for a NTC (negative temperature coefficient) thermistor. Solve for  $R_{T2}$  first and substitute into  $R_{T1}$  equation.

$$R_{T2} = \frac{2.5 R_{TC} R_{TH}}{R_{TC} - 3.5 R_{TH}}$$

(1)

$$R_{T1} = \frac{7 R_{TH} R_{T2}}{3 \left[ R_{TH} + R_{T2} \right]}$$

(2)

Applying a fixed voltage, 1/2 Vin (50% resistor divider from Vin to ground), to the TS pin to disable the temperature sensing feature.

#### INPUT OVERVOLTAGE DETECTION, POWER GOOD STATUS OUTPUT

The input power detection status for pin IN is shown at the open collector output pin PG.

| INPUT POWER DETECTION (IN) | PG STATE       |

|----------------------------|----------------|

| NOT DETECTED               | High impedance |

| DETECTED, NO OVERVOLTAGE   | LO             |

| DETECTED, OVERVOLTAGE      | High impedance |

#### **Table 2. Input Power Detection Status**

The bq2406x detects an input overvoltage when  $V(IN) > V_{(OVP)}$ . When an overvoltage protection is detected the charger function is turned off and the bq2460x is set to standby mode of operation. The OVP detection is not latched, and the IC returns to normal operation when the fault condition is removed.

#### **CHARGE STATUS OUTPUTS**

The open-collector STAT1 and STAT2 outputs indicate various charger operations as shown in Table 3. These status pins can be used to drive LEDs or communicate to the host processor. Note that OFF indicates the open-collector transistor is turned off. When termination is disabled (TMR pin floating or  $\overline{TE}$  = Hi, bq24063) the Done state is not available; the status LEDs indicate fast charge if  $V_{BAT} > V_{LOWV}$  and precharge if  $V_{BAT} < V_{LOWV}$ . The available output current is a function of the OUT pin voltage, See Figure 24.

#### Table 3. Charge Status<sup>(1)</sup>

| Charge State                              | STAT1 | STAT2 |

|-------------------------------------------|-------|-------|

| Precharge in progress                     | ON    | ON    |

| Fast charge in progress                   | ON    | OFF   |

| Done (termination enabled only)           | OFF   | ON    |

| Charge Suspend (temperature)              |       |       |

| Timer Fault                               |       |       |

| Charger off                               |       |       |

| Selected Input power overvoltage detected | OFF   | OFF   |

| Battery absent                            |       |       |

| Batteryshort                              |       |       |

(1) Pulse loading on the OUT pin may cause the IC to cycle between Done and charging states (LEDs *Flashing*)

#### BATTERY CHARGING: CONSTANT CURRENT PHASE

The bq2406x family offers on-chip current regulation. The current regulation is defined by the value of the resistor connected to ISET pin.

During a charge cycle the fast charge current  $I_{O(OUT)}$  is applied to the battery if the battery voltage is above the  $V_{(LOWV)}$  threshold (2.95 V typical):

$$I(OUT) = I_{O(OUT)} = \frac{V_{(SET)} \times K_{SET}}{R_{ISET}}$$

(3)

Where  $K_{(SET)}$  is the output current set factor and  $V_{(SET)}$  is the output current set voltage.

During a charge cycle if the battery voltage is below the  $V_{(LOWV)}$  threshold a pre-charge current  $I_{(PRECHG)}$  is applied to the battery. This feature revives deeply discharged cells.

$$I(OUT) = I_{(PRECHG)} = \frac{V_{(PRECHG)} \times K_{SET}}{R_{ISET}} \sim \frac{I_{O(OUT)}}{10}$$

(4)

Where  $K_{(SET)}$  is the output current set factor and  $V_{(PRECHG)}$  is the precharge set voltage.

At low constant current charge currents, less than 350 mA, it is recommended that a  $0.47-\mu$ F capacitor be placed between the ISET and BAT pins to insure stability, see Figure 16.

#### CHARGE CURRENT TRANSLATOR

When the charge function is enabled internal circuits generate a current proportional to the charge current at the ISET pin. This current, when applied to the external charge current programming resistor  $R_{ISET}$  generates an analog voltage that can be monitored by an external host to calculate the current sourced from the OUT pin.

$$V(ISET) = I(OUT) \times \frac{R_{ISET}}{K_{(SET)}}$$

(5)

#### **BATTERY VOLTAGE REGULATION**

The battery pack voltage is sensed through the BAT pin, which is tied directly to the positive side of the battery pack. The bq2406x monitors the battery pack voltage between the BAT and VSS pins. When the battery voltage rises to  $V_{O(REG)}$  threshold the voltage regulation phase begins and the charging current begins to taper down. The voltage regulation threshold  $V_{O(REG)}$  is fixed by an internal IC voltage reference.

#### PRE-CHARGE TIMER

The bq2406x family activates an internal safety timer during the battery pre-conditioning phase. The charge safety timer time-out value is set by the external resistor connected to TMR pin,  $R_{TMR}$  and the timeout constants  $K_{(PCHG)}$  and  $T_{(CHG)}$ :

$\mathsf{T}_{(\mathsf{PCHG})} = \mathsf{K}_{(\mathsf{PCHG})} \times \mathsf{T}_{(\mathsf{CHG})}$

The pre-charge timer operation is detailed in Table 4.

| bq2460X MODE                     | $V(OUT) > V_{(LOWV)}$ | PRE-CHARGE TIMER MODE              |

|----------------------------------|-----------------------|------------------------------------|

| STANDBY ( $\overline{CE} = Hi$ ) | Х                     | RESET                              |

| CHARGING                         | Yes                   | RESET                              |

| SUSPEND (TS out of range)        | Yes                   | RESET                              |

| SUSPEND (TS out of range)        | No                    | Hold                               |

| CHARGING, TMR PIN NOT OPEN       | No                    | COUNTING, EXTERNAL PROGRAMMED RATE |

| CHARGING, TMR PIN OPEN           | Х                     | RESET                              |

#### Table 4. Pre-Charge Timer Operational Modes

In SUSPEND mode the pre-charge timer is put on hold (i.e., pre-charge timer is not reset), normal operation resumes when the timer returns to the normal operating mode (COUNTING). If V(BAT) does not reach the internal voltage threshold  $V_{(LOWV)}$  within the pre-charge timer period a fault condition is detected, the charger is turned off and the pre-charge safety timer fault condition is latched.

When the pre-charge timer fault latch is set the charger is turned off. Under those conditions a small current  $I_{FAULT}$  is applied to the OUT pin, as long as input power (IN) is detected **AND** V(OUT) <  $V_{(LOWV)}$ , as part of a timer fault recovery protocol. This current allows the output voltage to rise above the pre-charge threshold  $V_{(LOWV)}$ , resetting the pre-charge timer fault latch when the pack is removed. Table 5 further details the pre-charge timer fault latch operation.

#### Table 5. Pre-Charge Timer Latch Functionality

| PRE-CHARGE TIMER FAULT ENTERED WHEN                        | PRE-CHARGE TIMER FAULT LATCH RESET AT |  |  |  |

|------------------------------------------------------------|---------------------------------------|--|--|--|

|                                                            | CE rising edge or OVP detected        |  |  |  |

| Pre-charge timer timeout <b>AND</b> V(OUT) > $V_{(LOW V)}$ | Input power removed (not detected)    |  |  |  |

|                                                            | Timer function disabled               |  |  |  |

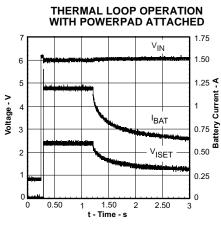

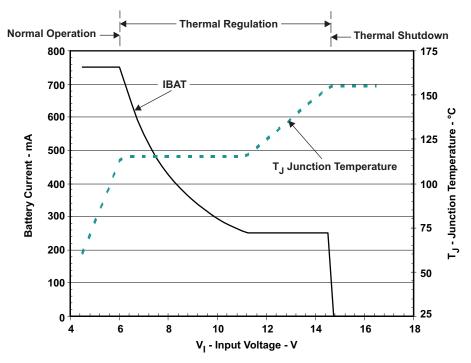

#### THERMAL PROTECTION LOOP

An internal control loop monitors the bq2406x junction termperature (T<sub>J</sub>) to ensure safe operation during high power dissipations and or increased ambient temperatures. This loop monitors the bq2406x junction temperature and reduces the charge current as necessary to keep the junction temperature from exceeding,  $T_{J(REG)}$ , (112°C, typical).

The bq2406x's thermal loop control can reduce the charging current down to ~200mA if needed. If the junction temperature continues to rise, the IC will enter thermal shutdown.

#### THERMAL SHUTDOWN AND PROTECTION

Internal circuits monitor the junction temperature, T<sub>J</sub>, of the die and suspends charging if T<sub>J</sub> exceeds an internal threshold T<sub>(SHUT)</sub> (155°C typical). Charging resumes when T<sub>J</sub> falls below the internal threshold T<sub>(SHUT)</sub> by approximately 20°C.

Figure 19. Thermal Regulation Loop Performance and Thermal Shutdown

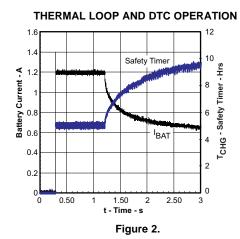

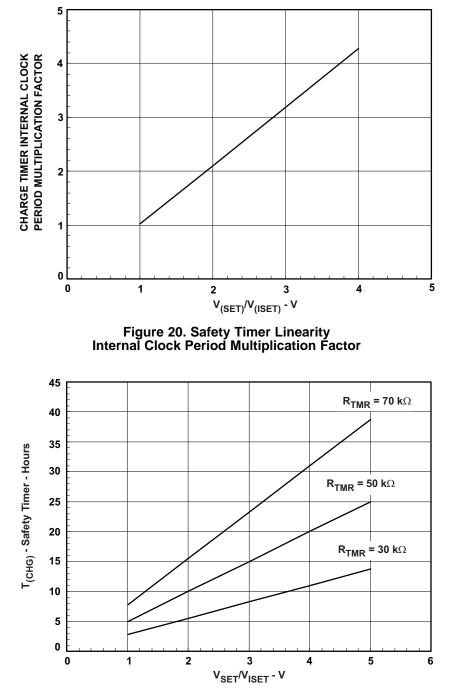

#### DYNAMIC TIMER FUNCTION

The charge and pre-charge safety timers are programmed by the user to detect a fault condition if the charge cycle duration exceeds the total time expected under normal conditions. The expected charge time is usually calculated based on the fast charge current rate.

When the thermal loop is activated the charge current is reduced, and bq2406x activates the dynamic timer control, an internal circuit that slows down the safety timer's clock frequency. The dynamic timer control circuit effectively extends the safety time duration for either the precharge or fast charge timer modes. This minimizes the chance of a safety timer fault due to thermal regulation.

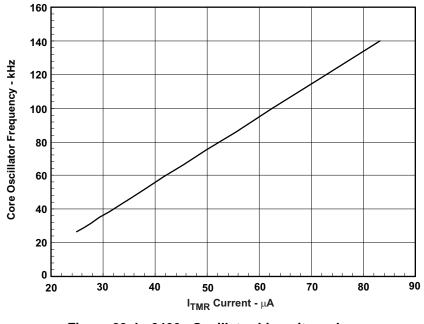

The bq2406x dynamic timer control (DTC) monitors the voltage at pin ISET during pre-charge and fast charge, and if in thermal regulation slows the clock frequency proportionately to the change in charge current. The time duration is based on a  $2^{24}$  ripple counter, so slowing the clock frequency is a real time correction. The DTC circuit changes the safety timers clock period based on the  $V_{(SET)}/V_{(ISET)}$  ratio (fast charge) or  $V_{(PRECHG)}/V_{(SET)}$  ratio (pre-charge). Typical safety timer multiplier values relative to the  $V_{(SET)}/V_{(ISET)}$  ratio is shown in Figure 20 and Figure 21.

Figure 21. bq2406x Safety Timer Linearity for  $R_{\text{TMR}}$  Values

Figure 22. bq2406x Oscillator Linearity vs I<sub>TMR</sub> R<sub>TMR</sub> 30 K $\Omega$  – 100 K $\Omega$

#### CHARGE TERMINATION DETECTION AND RECHARGE

The charging current is monitored the during the voltage regulation phase. Charge termination is indicated at the STATx pins (STAT1 = Hi-Z; STAT2 = Low) once the charge current falls below the termination current threshold  $I_{(TERM)}$ . A deglitch period  $T_{DGL(TERM)}$  is added to avoid false termination indication during transient events.

Charge termination is not detected if the charge current falls below the termination threshold as a result of the thermal loop activation. Termination is also not detected when charger enters the suspend mode, due to detection of invalid pack temperature or internal thermal shutdown.

Table 6 describes the termination latch functionality.

#### Table 6. Termination Latch Functionality

| TERMINATION DETECTED LATCHED WHEN                                      | TERMINATION LATCH RESET AT                    |  |  |

|------------------------------------------------------------------------|-----------------------------------------------|--|--|

| $I(OUT) < I_{(TERM)}$ AND t > $T_{DGL(TERM)}$ AND $V(OUT) > V_{(RCH)}$ | CE rising edge or OVP detected                |  |  |

|                                                                        | New charging cycle started; see state diagram |  |  |

|                                                                        | Termination disabled                          |  |  |

#### The termination function is DISABLED:

- 1. In bq24060/61/64 the termination is disabled when the TMR pin is left open (floating).

- 2. In bq24063 leaving TMR pin open (floating) does NOT disable the termination. The only way to disable termination in the bq24063 is to set TE = HIGH.

#### **BATTERY ABSENT DETECTION – VOLTAGE MODE ALGORITHM**

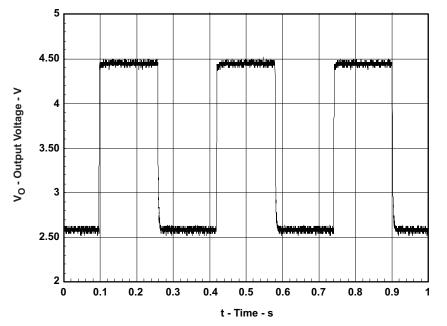

The bq2406x provides a battery absent detection scheme to reliably detect insertion and/or removal of battery packs. The detection circuit applies an internal current to the battery terminal, and detects battery presence based on the terminal voltage behavior. Figure 23 has a typical waveform of the output voltage when the battery absent detection is enabled and no battery is connected:

Figure 23. Battery-Absent Detection Waveforms

The battery absent detection function is disabled if the voltage at the BAT pin is held above the battery recharge threshold,  $V_{(RCH)}$ , after termination detection. When the voltage at the BAT pin falls to the recharge threshold, either by connection of a load to the battery or due to battery removal, the bq2406x begins a battery absent detection test. This test involves enabling a detection current,  $I_{DET(DOWN)}$ , for a period of  $T_{(DETECT)}$  and checking to see if the battery voltage is below the pre-charge threshold,  $V_{(LOWV)}$ . Following this, the precharge current,  $I_{DET(UP)}$  is applied for a period of  $T_{(DETECT)}$  and the battery voltage checked again to be above the recharge threshold.

Passing both of the discharge and charging tests (battery terminal voltage being below the pre-charge and above the recharge thresholds on the battery detection test) indicates a battery absent fault at the STAT1 and STAT2 pins. Failure of either test starts a new charge cycle. For the absent battery condition the voltage on the BAT pin rises and falls between the  $V_{(LOWV)}$  and  $V_{O(REG)}$  thresholds indefinitely. See the operation flowchart for more details on this algorithm. If it is desired to power a system load without a battery, it is recommended to float the TMR pin which puts the charger in *LDD mode* (disables termination).

The battery absent detection function is disabled when the termination is disabled.

The bq2406x provides a small battery leakage current, IBAT(DONE) (1  $\mu$ A typical), after termination to pull down the BAT pin voltage in the event of battery removal. If the leakage on the OUT pin is higher than this pulldown current, then the voltage at the pin remains above termination and a battery-absent state will not be detected. This problem is fixed with the addition of a pulldown resistor of 2 M $\Omega$  to 4 M $\Omega$  from the OUT pin to VSS. A resistor too large (< 2 M $\Omega$ ) can cause the OUT pin voltage to drop below the V(LOWV) threshold before the recharge deglitch (typical 25 ms) expires, causing a fault condition. In this case the bq2406x provides a fault current (typical 750  $\mu$ A) to pull the pin above the termination threshold.

#### CHARGE SAFETY TIMER

As a safety mechanism the bq2406x has a user-programmable timer that monitors the total fast charge time. This timer (charge safety timer) is started at the beginning of the fast charge period. The safety charge timeout value is set by the value of an external resistor connected to the TMR pin ( $R_{TMR}$ ); if pin TMR is left open (floating) the charge safety timer is disabled.

The charge safety timer time-out value is calculated as follows:

$T_{(CHG)} = [K_{(CHG)} \times R_{(TMR)}]$

The safety timer operation modes are shown in Table 7

#### Table 7. Charge Safety Timer Operational Modes

| bq2460X                    | V(OUT) > V <sub>(LOWV)</sub> | CHARGE SAFETY TIMER MODE |

|----------------------------|------------------------------|--------------------------|

| STANDBY                    | Х                            | RESET                    |

| CHARGING                   | No                           | RESET                    |

| SUSPEND                    | No                           | RESET                    |

| SUSPEND                    | Yes                          | SUSPEND                  |

| CHARGING, TMR PIN NOT OPEN | Yes                          | COUNTING                 |

| CHARGING, TMR PIN OPEN     | X                            | RESET                    |