SLOS829A - FEBRUARY 2013-REVISED JULY 2015

# THS4532 Ultra Low Power, Rail-to-Rail Output, Fully-Differential Amplifier

Technical

Documents

Sample &

Buy

### 1 Features

- Ultra Low Power:

- Voltage: 2.5 V to 5.5 V

- Current: 250 µA

- Power-Down Mode: 0.5 µA (typ)

- Fully-Differential Architecture

- Bandwidth: 36 MHz

- Slew Rate: 200 V/µs

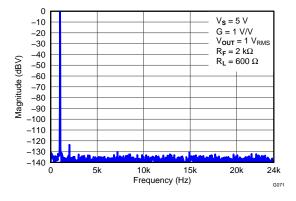

- THD: –120 dBc at 1 kHz (1 V<sub>RMS</sub>, R<sub>L</sub>= 2 kΩ)

- Input Voltage Noise: 10 nV/ $\sqrt{Hz}$  (f = 1 kHz)

- High DC Accuracy:

- V<sub>OS</sub>: ±100 μV

- V<sub>OS</sub> Drift: ±3 μV/°C (-40°C to +125°C)

- A<sub>OL</sub>: 114 dB

- Rail-to-Rail Output (RRO)

- Negative Rail Input (NRI)

- Output Common-Mode Control

### 2 Applications

- Low-Power SAR, ΔΣ ADC Driver

- Low Power, High Performance:

- Differential to Differential Amplifier

- Single-Ended to Differential Amplifier

- Low-Power, Wide-Bandwidth Differential Driver

- Low-Power, Wide-Bandwidth Differential Signal Conditioning

- · High Channel Count and Power Dense Systems

## 3 Description

Tools &

Software

The THS4532 is a low-power, fully-differential amplifier with input common-mode range below the negative rail and rail-to-rail output. The device is designed for low-power data acquisition systems and high density applications where power consumption and dissipation is critical.

Support &

Community

20

The device features accurate output common-mode control that allows for dc coupling when driving analog-to-digital converters (ADCs). This control, coupled with the input common-mode range below the negative rail and rail-to-rail output, allows for easy interface from single-ended ground-referenced signal sources to successive-approximation registers (SARs), and delta-sigma ( $\Delta\Sigma$ ) ADCs using only single-supply 2.5-V to 5-V power. The THS4532 is also a valuable tool for general-purpose, low-power differential signal conditioning applications.

The device is characterized for operation over the extended industrial temperature range from -40°C to 125°C. The following package options are available:

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| THS4532     | TSSOP   | 5.00 mm x 4.40 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

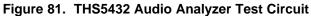

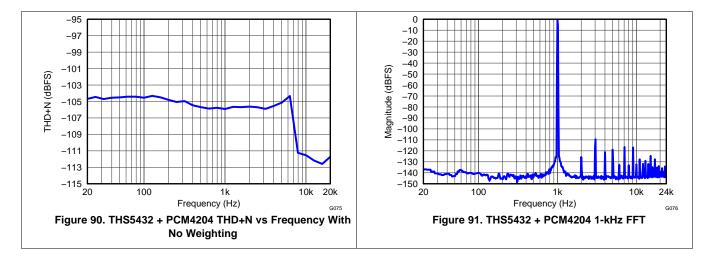

### 1-kHz FFT Plot on Audio Analyzer

2

# **Table of Contents**

| 1 | Feat | tures 1                                              |

|---|------|------------------------------------------------------|

| 2 | Арр  | lications 1                                          |

| 3 | Des  | cription1                                            |

| 4 | Rev  | ision History 2                                      |

| 5 | Rela | ated Products 3                                      |

| 6 | Pin  | Configuration and Functions 4                        |

| 7 | Spe  | cifications5                                         |

|   | 7.1  | Absolute Maximum Ratings 5                           |

|   | 7.2  | ESD Ratings5                                         |

|   | 7.3  | Recommended Operating Conditions5                    |

|   | 7.4  | Thermal Information 5                                |

|   | 7.5  | Electrical Characteristics: V <sub>S</sub> = 2.7 V 6 |

|   | 7.6  | Electrical Characteristics: V <sub>S</sub> = 5 V 9   |

|   | 7.7  | Typical Characteristics 12                           |

| 8 | Deta | ailed Description 25                                 |

|   | 8.1  | Overview 25                                          |

|   | 8.2  | Functional Block Diagram 25                          |

|   |      |                                                      |

|    | 8.3  | Feature Description               | 25 |

|----|------|-----------------------------------|----|

|    | 8.4  | Device Functional Modes           | 28 |

| 9  | Арр  | lication and Implementation       | 29 |

|    | 9.1  | Application Information           | 29 |

|    | 9.2  | Typical Applications              | 37 |

|    | 9.3  | Systems Examples                  | 41 |

| 10 | Pow  | ver Supply Recommendations        | 47 |

| 11 | Lay  | out                               | 48 |

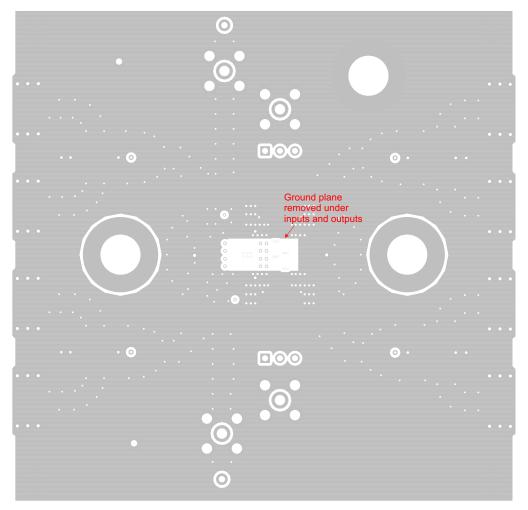

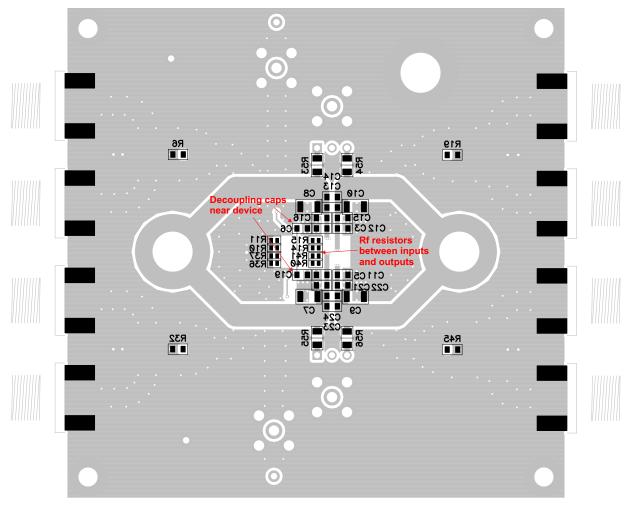

|    | 11.1 | Layout Guidelines                 | 48 |

|    | 11.2 | Layout Example                    | 49 |

| 12 | Dev  | ice and Documentation Support     | 53 |

|    | 12.1 | Documentation Support             | 53 |

|    | 12.2 | Community Resources               | 53 |

|    | 12.3 | Trademarks                        | 53 |

|    | 12.4 | Electrostatic Discharge Caution   | 53 |

|    | 12.5 | Glossary                          | 53 |

| 13 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 53 |

|    |      |                                   |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes f | from Ori | ginal (Fe  | ebruary  | 2013) | to R | evision | Δ |

|-----------|----------|------------|----------|-------|------|---------|---|

| onanges i |          | ginai (i v | con uary | 2013) |      | CVISION | ~ |

| Cł | nanges from Original (February 2013) to Revision A                                                                                                                                                                                                                                                                                                                   | Page           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | Added the ESD Ratings table, Recommended Operating Conditions, Detailed Description section, Feature<br>Description section, Device Functional Modes section, Application and Implementation section. Power Supply<br>Recommendations section, Layout section, Device and Documentation Support section, Mechanical, Packaging,<br>and Orderable Information section | 1              |

| •  | Changed $V_{OCM}$ = open To: $V_{OCM}$ = + $V_S$ /2 in the test conditions of <i>Electrical Characteristics:</i> $V_S$ = 2.7 V                                                                                                                                                                                                                                       | <mark>6</mark> |

| •  | Added Note 3 to the <i>Electrical Characteristics:</i> $V_{\rm S} = 2.7 V$ table.                                                                                                                                                                                                                                                                                    | 7              |

| •  | Changed $V_{OCM}$ = open To: $V_{OCM}$ = + $V_S/2$ in the test conditions of <i>Electrical Characteristics:</i> $V_S$ = 5 V                                                                                                                                                                                                                                          | 9              |

| •  | Changed Typical Characteristics: V <sub>S</sub> = 2.7 V Conditions deleted text "Channel 1"                                                                                                                                                                                                                                                                          | 13             |

| •  | Changed Typical Characteristics: $V_{s} = 5 V$ Conditions deleted text "Channel 1"                                                                                                                                                                                                                                                                                   | 19             |

www.ti.com

# **5** Related Products

|         |          |                     |                         | •                       |                  |                      |

|---------|----------|---------------------|-------------------------|-------------------------|------------------|----------------------|

| DEVICE  | BW (MHz) | l <sub>Q</sub> (mA) | THD (dBc) at<br>100 kHz | V <sub>N</sub> (nV/√Hz) | RAIL-TO-RAIL     | DUAL PART<br>NUMBERS |

| THS4531 | 36       | 0.25                | -104                    | 10                      | Negative In, Out | THS4532              |

| THS4121 | 100      | 16                  | -79                     | 5.4                     | Out              |                      |

| THS4521 | 145      | 1.14                | -120                    | 4.6                     | Negative In, Out | THS4522              |

| THS4131 | 150      | 16                  | -107                    | 1.3                     | No               |                      |

| THS4520 | 620      | 14.2                | -107                    | 2                       | Out              |                      |

| THS4541 | 850      | 10.1                | -137                    | 2.2                     | Negative In, Out |                      |

### Table 1. Related Amplifiers

### **Table 2. Related Precision ADCs**

| DEVICE   | BITS | MAX DATA RATE<br>(kSPS) | NOMINAL SUPPLY<br>(V) | NOMINAL I <sub>CC</sub> (mA)<br>MAX CLK RATE | TYPICAL POWER (mW)<br>MAX CLK RATE |

|----------|------|-------------------------|-----------------------|----------------------------------------------|------------------------------------|

| ADS8881  | 18   | 1000                    | 5                     | 1.1                                          | 5.5                                |

| ADS8861  | 16   | 1000                    | 3.3                   | 1.67                                         | 5.3                                |

| ADS8321E | 16   | 100                     | 5                     | 0.9                                          | 4.5                                |

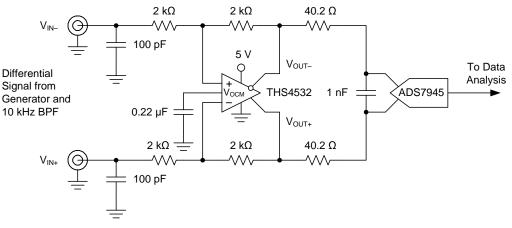

| ADS7945  | 14   | 2000                    | 5                     | 2.32                                         | 5.8/ch (dual)                      |

| ADS7044  | 12   | 1000                    | 3                     | 0.3                                          | 0.9                                |

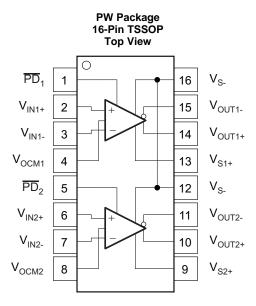

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN                |        | I/O | DESCRIPTION                                                                                                                                |  |  |

|--------------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME               | NO.    | 1/0 | DESCRIPTION                                                                                                                                |  |  |

| PD 1               | 1      | —   | Power-down 1, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation (PIN MUST BE DRIVEN)           |  |  |

| PD 2               | 5      | —   | Amplifier 2 Power-down, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation (PIN MUST BE DRIVEN) |  |  |

| V <sub>IN1+</sub>  | 2      | I   | Noninverting amplifier 1 input                                                                                                             |  |  |

| V <sub>IN1-</sub>  | 3      | I   | Inverting amplifier 1 input                                                                                                                |  |  |

| V <sub>IN2+</sub>  | 6      | I   | Noninverting amplifier 2 input                                                                                                             |  |  |

| V <sub>IN2-</sub>  | 7      | I   | Inverting amplifier 2 input                                                                                                                |  |  |

| V <sub>OCM1</sub>  | 4      | I   | Common-mode voltage input 1                                                                                                                |  |  |

| V <sub>OCM2</sub>  | 8      | I   | Common-mode voltage input 2                                                                                                                |  |  |

| V <sub>OUT1+</sub> | 14     | 0   | Noninverting amplifier 1 output                                                                                                            |  |  |

| V <sub>OUT1-</sub> | 15     | 0   | Inverting amplifier 1 output                                                                                                               |  |  |

| V <sub>OUT2+</sub> | 10     | 0   | Noninverting amplifier 2 output                                                                                                            |  |  |

| V <sub>OUT2-</sub> | 11     | 0   | Inverting amplifier 2 output                                                                                                               |  |  |

| V <sub>S-</sub>    | 12, 16 | I   | Negative power-supply input. Note $V_{S-}$ tied together on multichannel devices                                                           |  |  |

| V <sub>S1+</sub>   | 13     | I   | Amplifier 1 positive power-supply input                                                                                                    |  |  |

| V <sub>S2+</sub>   | 9      | Ι   | Amplifier 2 positive power-supply input                                                                                                    |  |  |

### 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                                                       | MIN                      | MAX              | UNIT |

|-----------------------------------------------------------------------|--------------------------|------------------|------|

| Supply voltage, $V_{S-}$ to $V_{S+}$                                  |                          | 5.5              | V    |

| Input/output voltage, $V_{IN\pm}$ , $V_{OUT\pm}$ , and $V_{OCM}$ pins | (V <sub>S-</sub> ) – 0.7 | $(V_{S+}) + 0.7$ | V    |

| Differential input voltage, VID                                       |                          | 1                | V    |

| Continuous output current, I <sub>O</sub>                             |                          | 50               | mA   |

| Continuous input current, I <sub>i</sub>                              |                          | 0.75             | mA   |

| Continuous power dissipation                                          | See Therma               | al Information   |      |

| Maximum junction temperature, T <sub>J</sub>                          |                          | 150              | °C   |

| Operating junction temperature, T <sub>J</sub>                        | -40                      | 125              | °C   |

| Storage temperature, T <sub>stg</sub>                                 | -65                      | 150              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                                            |                                                                                       | VALUE | UNIT |

|--------------------|--------------------------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                                            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2500 |      |

| V <sub>(ESD)</sub> | V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                       | MIN | NOM | MAX | UNIT |

|-----------------|-----------------------|-----|-----|-----|------|

| V <sub>S+</sub> | Single-supply voltage | 2.7 | 5   | 5.4 | V    |

| T <sub>A</sub>  | Ambient temperature   | -40 | 25  | 125 | °C   |

### 7.4 Thermal Information

|                       |                                              | THS4532    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | TSSOP (PW) | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 122.4      |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 61.2       |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 66.7       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 14.4       | C/VV |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 66.2       |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

TEXAS INSTRUMENTS

www.ti.com

# 7.5 Electrical Characteristics: V<sub>s</sub> = 2.7 V

Test conditions at  $T_A = 25^{\circ}$ C,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | TEST CONDITIONS                                  | MIN TYP | МАХ | UNIT    | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------------------|--------------------------------------------------|---------|-----|---------|------------------------------|

| AC PERFORMANCE                       |                                                  |         |     |         |                              |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 1  | 34      |     |         |                              |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 2  | 16      |     | N 41 1- |                              |

| Small-signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 5  | 6       |     | MHz     |                              |

|                                      | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 2.7     |     |         |                              |

| Gain-bandwidth product               | V <sub>OUT</sub> = 100 mV <sub>PP</sub> , G = 10 | 27      |     | MHz     |                              |

| Large-signal bandwidth               | $V_{OUT} = 2 V_{PP}, G = 1$                      | 34      |     | MHz     |                              |

| Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1     | 12      |     | MHz     |                              |

| Slew rate, rise/fall, 25% to 75%     |                                                  | 190/320 |     | V/µs    |                              |

| Rise/fall time, 10% to 90%           |                                                  | 5.2/6.1 |     | ns      |                              |

| Settling time to 1%, rise/fall       |                                                  | 25/20   |     |         |                              |

| Settling time to 0.1%, rise/fall     | V <sub>OUT</sub> = 2-V step                      | 60/60   | -   |         |                              |

| Settling time to 0.01%, rise/fall    |                                                  | 150/110 |     |         |                              |

| Overshoot/undershoot, rise/fall      |                                                  | 1/1%    |     |         |                              |

|                                      | f = 1 kHz, V <sub>OUT</sub> = 1 V <sub>RMS</sub> | -122    |     | dBc     | с                            |

| 2nd-order harmonic distortion        | f = 10 kHz                                       | -127    |     |         |                              |

|                                      | f = 1 MHz                                        | -59     |     |         |                              |

|                                      | $f = 1 \text{ kHz}, V_{OUT} = 1 V_{RMS}$         | -130    |     |         |                              |

| 3rd-order harmonic distortion        | f = 10 kHz                                       | -135    |     | dBc     |                              |

|                                      | f = 1 MHz                                        | -70     |     |         |                              |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing,                 | -83     |     | dDo     |                              |

| 3rd-order intermodulation distortion | $V_{OUT}$ envelope = 2 $V_{PP}$                  | -81     |     | dBc     |                              |

| Input voltage noise                  | f = 1 kHz                                        | 10      | r   | nV/√Hz  |                              |

| Voltage noise 1/f corner frequency   |                                                  | 45      |     | Hz      |                              |

| Input current noise                  | f = 100 kHz                                      | 0.25    | F   | oA/√Hz  |                              |

| Current noise 1/f corner frequency   |                                                  | 6.5     |     | kHz     |                              |

| Overdrive recovery time              | Overdrive = 0.5 V                                | 65      |     | ns      |                              |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz             | -65     |     | dB      |                              |

| Closed-loop output impedance         | f = 1 MHz (differential)                         | 2.5     |     | Ω       |                              |

| Channel-to-channel crosstalk         | f = 10 kHz, measured differentially              | -133    |     | dB      |                              |

Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

# Electrical Characteristics: V<sub>s</sub> = 2.7 V (continued)

Test conditions at  $T_A = 25^{\circ}$ C,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                             | MIN                   | ТҮР                       | МАХ                      | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|---------------------------------------------|-----------------------|---------------------------|--------------------------|----------|------------------------------|

| DC PERFORMANCE                            |                                             |                       |                           |                          |          |                              |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                             | 100                   | 113                       |                          | dB       | А                            |

|                                           | $T_A = 25^{\circ}C$                         |                       | ±80                       | ±400                     |          | А                            |

| have a farmer of a ffar to the            | $T_A = 0^{\circ}C$ to $70^{\circ}C$         |                       |                           | ±715                     | μV       |                              |

| Input-referred offset voltage             | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       |                           | ±855                     | μv       | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       |                           | ±1300                    |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$         |                       | ±2                        | ±7                       |          |                              |

| Input offset voltage drift <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       | <u>+2</u>                 | ±7                       | µV/°C    | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       | ±3                        | ±9                       |          |                              |

|                                           | $T_A = 25^{\circ}C$                         |                       | 200                       | 250                      |          | А                            |

| Input biog ourrant                        | $T_A = 0^{\circ}C$ to $70^{\circ}C$         |                       |                           | 275                      | nA       |                              |

| Input bias current                        | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       |                           | 286                      | ΠA       | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       |                           | 305                      |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$         |                       | 0.45                      | 0.55                     |          |                              |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       | 0.45                      | 0.55                     | -        | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       | 0.45                      | 0.55                     |          |                              |

|                                           | $T_A = 25^{\circ}C$                         |                       | ±5                        | ±50                      | nA       | А                            |

| Input offect ourrent                      | $T_A = 0^{\circ}C$ to 70°C                  |                       |                           | ±55                      |          |                              |

| Input offset current                      | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       |                           | ±57                      |          | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       |                           | ±60                      |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$         |                       | ±0.03                     | ±0.1                     | nA/°C    |                              |

| Input offset current drift <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $85^{\circ}C$       |                       | ±0.03                     | ±0.1                     |          | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       | ±0.03                     | ±0.1                     |          |                              |

| INPUT                                     |                                             |                       |                           |                          |          |                              |

| Common mode input low                     | $T_A = 25^{\circ}C$ , CMRR > 87 dB          |                       | $V_{S-} - 0.2$            | V <sub>S-</sub>          | V        | А                            |

| Common-mode input low                     | $T_A = -40^{\circ}C$ to 125°C, CMRR > 87 dB |                       | $V_{S-} - 0.2$            | V <sub>S-</sub>          | v        | В                            |

| Common-mode input high                    | $T_A = 25^{\circ}C$ , CMRR > 87 dB          | V <sub>S+</sub> – 1.2 | V <sub>S+</sub> – 1.1     |                          | v        | А                            |

| Common-mode input high                    | $T_A = -40^{\circ}C$ to 125°C, CMRR > 87 dB | V <sub>S+</sub> – 1.2 | V <sub>S+</sub> – 1.1     |                          | v        | В                            |

| Common-mode rejection ratio               |                                             | 90                    | 116                       |                          | dB       | А                            |

| Input impedance common-mode               |                                             |                       | 200    1.2                |                          | kΩ    pF | С                            |

| Input impedance differential mode         |                                             |                       | 200    1                  |                          | ки прг   | С                            |

| OUTPUT                                    |                                             |                       |                           |                          |          |                              |

|                                           | $T_A = 25^{\circ}C$                         |                       | V <sub>S-</sub> +<br>0.06 | V <sub>S-</sub> +<br>0.2 | V        | А                            |

| Single-ended output voltage: low          | $T_A = -40^{\circ}C$ to $125^{\circ}C$      |                       | V <sub>S</sub> _+<br>0.06 | V <sub>S-</sub> +<br>0.2 |          | В                            |

|                                           | T <sub>A</sub> = 25°C                       | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> –<br>0.11 |                          | - V      | А                            |

| Single-ended output voltage: high         | $T_A = -40^{\circ}C$ to $125^{\circ}C$      | V <sub>S+</sub> - 0.2 | V <sub>S+</sub> –<br>0.11 |                          |          | В                            |

| Output saturation voltage: high/low       |                                             |                       | 110/60                    |                          | mV       | С                            |

|                                           | T <sub>A</sub> = 25°C                       | ±15                   | ±22                       |                          |          | А                            |

| Linear output current drive               | $T_A = -40^{\circ}C$ to 125°C               | ±15                   |                           |                          | mA       | В                            |

(2) Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

# Electrical Characteristics: V<sub>s</sub> = 2.7 V (continued)

Test conditions at  $T_A = 25^{\circ}$ C,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2$ ,  $V_{OUT} = 2$   $V_{PP}$ ,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                         | TEST CONDITIONS                                                                                     | MIN  | ТҮР            | МАХ  | UNIT  | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|----------------|------|-------|------------------------------|

| POWER SUPPLY                                      |                                                                                                     |      |                |      |       |                              |

| Specified operating voltage                       |                                                                                                     | 2.5  |                | 5.5  | V     | В                            |

|                                                   | $T_A = 25^{\circ}C, \overline{PD} = V_{S+}$                                                         |      | 230            | 330  |       | А                            |

| Quiescent operating current/ch                    | $T_A = -40^{\circ}C$ to 125°C, $\overline{PD} = V_{S+}$                                             |      | 270            | 370  | μA    | В                            |

| Power-supply rejection (PSRR)                     |                                                                                                     | 87   | 108            |      | dB    | Α                            |

| POWER DOWN                                        |                                                                                                     |      |                |      |       |                              |

| Enable voltage threshold                          | Specified on above 2.1 V                                                                            |      |                | 2.1  | V     | А                            |

| Disable voltage threshold                         | Specified off below 0.7 V                                                                           | 0.7  |                |      | V     | А                            |

| Disable pin bias current                          | $\overline{PD} = V_{S-} + 0.5 V$                                                                    |      | 50             | 500  | nA    | А                            |

| Power-down quiescent current                      | $\overline{PD} = V_{S-} + 0.5 V$                                                                    |      | 0.5            | 2    | μA    | А                            |

| Turn-on time delay                                | Time from $\overline{PD}$ = high to V <sub>OUT</sub> = 90% of final value, R <sub>L</sub> = 200 Ω   |      | 650            |      | ns    | С                            |

| Turn-off time delay                               | Time from $\overline{PD}$ = low to V <sub>OUT</sub> = 10% of original value, R <sub>L</sub> = 200 Ω |      | 20             |      | ns    | С                            |

| OUTPUT COMMON-MODE VOLT                           | AGE CONTROL (V <sub>OCM</sub> )                                                                     |      |                |      |       |                              |

| Small-signal bandwidth                            | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                                       |      | 23             |      | MHz   | С                            |

| Slew rate                                         | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                                        |      | 14             |      | V/µs  | С                            |

| Gain                                              |                                                                                                     | 0.99 | 0.996          | 1.01 | V/V   | А                            |

| Common-mode offset voltage                        | Offset = output common-mode voltage - V <sub>OCM</sub> input voltage                                |      | ±1             | ±5   | mV    | А                            |

| V <sub>OCM</sub> input bias current               | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                                     |      | ±20            | ±100 | nA    | А                            |

| $V_{\rm OCM}$ input voltage range                 |                                                                                                     | 0.8  | 0.75 to<br>1.9 | 1.75 | V     | A                            |

| V <sub>OCM</sub> input impedance                  |                                                                                                     |      | 100    1.6     |      | kΩ∥pF | С                            |

| Default voltage offset from $(V_{S+} - V_{S-})/2$ | Offset = output common-mode voltage – $(V_{S+} - V_{S-})/2$                                         |      | ±3             | ±10  | mV    | A                            |

### 7.6 Electrical Characteristics: $V_s = 5 V$

Test conditions at  $T_A = +25^{\circ}C$ ,  $V_{S+} = 5 V$ ,  $V_{S-} = 0 V$ ,  $V_{OCM} = open$ ,  $V_{OUT} = 2 V_{PP}$ ,  $R_F = 2 k\Omega$ ,  $R_L = 2 k\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | TEST CONDITIONS                                          | MIN TYP | МАХ | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------------------|----------------------------------------------------------|---------|-----|--------------------|------------------------------|

| AC PERFORMANCE                       |                                                          |         |     |                    |                              |

|                                      | $V_{OUT} = 100 \text{ mV}_{PP}, \text{ G} = 1$           | 36      |     |                    |                              |

| Small signal bandwidth               | $V_{OUT} = 100 \text{ mV}_{PP}, \text{ G} = 2$           | 17      |     | N 41 1-            |                              |

| Small-signal bandwidth               | $V_{OUT} = 100 \text{ mV}_{PP}, \text{ G} = 5$           | 6       |     | MHz                |                              |

|                                      | $V_{OUT} = 100 \text{ mV}_{PP}, \text{ G} = 10$          | 2.7     |     |                    |                              |

| Gain-bandwidth product               | $V_{OUT} = 100 \text{ mV}_{PP}, \text{ G} = 10$          | 27      |     | MHz                |                              |

| Large-signal bandwidth               | $V_{OUT} = 2 V_{PP}, G = 1$                              | 36      |     | MHz                |                              |

| Bandwidth for 0.1-dB flatness        | $V_{OUT} = 2 V_{PP}, G = 1$                              | 15      |     | MHz                |                              |

| Slew rate, rise/fall, 25% to 75%     |                                                          | 220/390 |     | V/µs               |                              |

| Rise/fall time, 10% to 90%           |                                                          | 4.6/5.6 |     | ns                 |                              |

| Settling time to 1%, rise/fall       |                                                          | 25/20   |     | ns                 |                              |

| Settling time to 0.1%, rise/fall     | V <sub>OUT</sub> = 2 V <sub>Step</sub>                   | 60/60   |     | ns                 |                              |

| Settling time to 0.01%, rise/fall    |                                                          | 150/110 |     | ns                 |                              |

| Overshoot/undershoot, rise/fall      |                                                          | 1/1%    |     |                    | С                            |

|                                      | $f = 1 \text{ kHz}, \text{ V}_{OUT} = 1 \text{ V}_{RMS}$ | -122    |     | dBc                |                              |

| 2nd-order harmonic distortion        | f = 10 kHz                                               | -128    |     |                    |                              |

|                                      | f = 1 MHz                                                | -60     |     |                    |                              |

|                                      | $f = 1 \text{ kHz}, \text{ V}_{OUT} = 1 \text{ V}_{RMS}$ | -130    |     |                    |                              |

| 3rd-order harmonic distortion        | f = 10 kHz                                               | –137    |     | dBc                |                              |

|                                      | f = 1 MHz                                                | -71     |     |                    |                              |

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing,                         | -85     |     | dBc                |                              |

| 3rd-order intermodulation distortion | $V_{OUT}$ envelope = 2 $V_{PP}$                          | -83     |     | dBc                |                              |

| Input voltage noise                  | f = 1 kHz                                                | 10      | ı   | nV/√ <del>Hz</del> |                              |

| Voltage noise 1/f corner frequency   |                                                          | 45      |     | Hz                 |                              |

| Input current noise                  | f = 100 kHz                                              | 0.25    | F   | pA/√Hz             |                              |

| Current noise 1/f corner frequency   |                                                          | 6.5     |     | kHz                |                              |

| Overdrive recovery time              | Overdrive = 0.5 V                                        | 65      |     | ns                 |                              |

| Output balance error                 | V <sub>OUT</sub> = 100 mV, f = 1 MHz                     | -67     |     | dB                 |                              |

| Closed-loop output impedance         | f = 1 MHz (differential)                                 | 2.5     |     | Ω                  |                              |

| Channel-to-channel crosstalk         | f = 10 kHz, measured differentially                      | -133    |     | dB                 |                              |

Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

# Electrical Characteristics: V<sub>s</sub> = 5 V (continued)

Test conditions at  $T_A = +25^{\circ}C$ ,  $V_{S+} = 5 \text{ V}$ ,  $V_{S-} = 0 \text{ V}$ ,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ ,  $R_F = 2 \text{ k}\Omega$ ,  $R_L = 2 \text{ k}\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                              | MIN                    | ТҮР                    | МАХ                   | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------|----------------------------------------------|------------------------|------------------------|-----------------------|----------|------------------------------|

| DC PERFORMANCE                            |                                              |                        |                        |                       |          |                              |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                              | 100                    | 114                    |                       | dB       | А                            |

| Input-referred offset voltage             | $T_A = 25^{\circ}C$                          |                        | ±80                    | ±400                  |          | А                            |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        |                        | ±715                  |          |                              |

|                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        |                        | ±855                  | μV       | В                            |

|                                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$       |                        |                        | ±1300                 |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        | ±2                     | ±7                    |          |                              |

| Input offset voltage drift <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        | ±2                     | ±7                    | µV/°C    | В                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C                |                        | ±3                     | ±9                    |          |                              |

|                                           | $T_A = 25^{\circ}C$                          |                        | 200                    | 250                   |          | А                            |

| lanut hing avanat                         | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        |                        | 279                   | nA       | В                            |

| Input bias current                        | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        |                        | 292                   |          |                              |

|                                           | $T_A = -40^{\circ}C$ to 125°C                |                        |                        | 315                   |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        | 0.5                    | 0.65                  |          |                              |

| Input bias current drift <sup>(2)</sup>   | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        | 0.5                    | 0.65                  | nA/°C    | В                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C                |                        | 0.5                    | 0.65                  |          |                              |

|                                           | $T_A = 25^{\circ}C$                          |                        | ±5                     | ±50                   | nA       | А                            |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        |                        | ±55                   |          |                              |

| Input offset current                      | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        |                        | ±57                   |          | В                            |

|                                           | $T_A = -40^{\circ}C$ to 125°C                |                        |                        | ±60                   |          |                              |

|                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$          |                        | ±0.03                  | ±0.1                  | nA/°C    | В                            |

| Input offset current drift <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $85^{\circ}C$        |                        | ±0.03                  | ±0.1                  |          |                              |

|                                           | $T_A = -40^{\circ}C$ to 125°C                |                        | ±0.03                  | ±0.1                  | 1        |                              |

| INPUT                                     |                                              | U                      |                        |                       | 1        |                              |

| <b>2</b>                                  | T <sub>A</sub> = 25°C, CMRR > 87 dB          |                        | V <sub>S-</sub> – 0.2  | V <sub>S-</sub>       |          | А                            |

| Common-mode input: low                    | $T_A = -40^{\circ}$ C to 125°C, CMRR > 87 dB |                        | V <sub>S-</sub> – 0.2  | V <sub>S-</sub>       | V        | В                            |

|                                           | T <sub>A</sub> = 25°C, CMRR > 87 dB          | V <sub>S+</sub> – 1.2  | V <sub>S+</sub> –1.1   |                       |          | А                            |

| Common-mode input: high                   | $T_A = -40^{\circ}$ C to 125°C, CMRR > 87 dB | V <sub>S+</sub> – 1.2  | V <sub>S+</sub> –1.1   |                       | V        | В                            |

| Common-mode rejection ratio               |                                              | 90                     | 116                    |                       | dB       | А                            |

| Input impedance common-mode               |                                              |                        | 200    1.2             |                       |          | С                            |

| Input impedance differential mode         |                                              |                        | 200    1               |                       | kΩ    pF | С                            |

| OUTPUT                                    |                                              | +                      |                        |                       |          |                              |

|                                           | $T_A = 25^{\circ}C$                          |                        | V <sub>S-</sub> + 0.1  | V <sub>S-</sub> + 0.2 | V        | А                            |

| Linear output voltage: low                | $T_A = -40^{\circ}C$ to $125^{\circ}C$       |                        | V <sub>S-</sub> + 0.1  | V <sub>S-</sub> + 0.2 | V        | В                            |

| l in an antiput colta an la bh            | $T_A = 25^{\circ}C$                          | V <sub>S+</sub> – 0.25 | V <sub>S+</sub> - 0.12 |                       | V        | А                            |

| Linear output voltage: high               | $T_A = -40^{\circ}C$ to 125°C                | V <sub>S+</sub> – 0.25 | V <sub>S+</sub> – 0.12 |                       | V        | В                            |

| Output saturation voltage: high/low       |                                              |                        | 120/100                |                       | mV       | С                            |

|                                           | $T_A = 25^{\circ}C$                          | ±15                    | ±25                    |                       | mA       | А                            |

| Linear output current drive               | $T_A = -40^{\circ}C$ to 125°C                | ±15                    |                        |                       |          | В                            |

(2) Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

# Electrical Characteristics: V<sub>s</sub> = 5 V (continued)

Test conditions at  $T_A = +25^{\circ}C$ ,  $V_{S+} = 5 V$ ,  $V_{S-} = 0 V$ ,  $V_{OCM} = open$ ,  $V_{OUT} = 2 V_{PP}$ ,  $R_F = 2 k\Omega$ ,  $R_L = 2 k\Omega$  differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                         | TEST CONDITIONS                                                                                            | MIN  | ТҮР             | МАХ  | UNIT  | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|-----------------|------|-------|------------------------------|

| POWER SUPPLY                                      |                                                                                                            |      |                 |      |       |                              |

| Specified operating voltage                       |                                                                                                            | 2.5  |                 | 5.5  | V     | В                            |

|                                                   | $T_A = 25^{\circ}C, \overline{PD} = V_{S+}$                                                                |      | 250             | 350  |       | А                            |

| Quiescent operating current/ch                    | $T_A = -40^{\circ}C$ to 125°C, $\overline{PD} = V_{S+}$                                                    |      | 290             | 390  | μA    | В                            |

| Power-supply rejection (PSRR)                     |                                                                                                            | 87   | 108             |      | dB    | А                            |

| POWER DOWN                                        |                                                                                                            |      |                 |      |       |                              |

| Enable voltage threshold                          | Specified on above 2.1 V                                                                                   |      |                 | 2.1  | V     | А                            |

| Disable voltage threshold                         | Specified off below 0.7 V                                                                                  | 0.7  |                 |      | V     | А                            |

| Disable pin bias current                          | $\overline{PD} = V_{S-} + 0.5 V$                                                                           |      | 50              | 500  | nA    | А                            |

| Power-down quiescent current                      | $\overline{PD} = V_{S-} + 0.5 V$                                                                           |      | 0.5             | 2    | μA    | А                            |

| Turn-on time delay                                | Time from $\overline{PD}$ = high to V <sub>OUT</sub> = 90% of final value, R <sub>L</sub> = 200 $\Omega$   |      | 600             |      | ns    | С                            |

| Turn-off time delay                               | Time from $\overline{PD}$ = low to V <sub>OUT</sub> = 10% of original value, R <sub>L</sub> = 200 $\Omega$ |      | 15              |      | ns    | С                            |

| OUTPUT COMMON-MODE VOLT                           | AGE CONTROL (V <sub>OCM</sub> )                                                                            |      |                 |      |       |                              |

| Small-signal bandwidth                            | V <sub>OCM</sub> input = 100 mV <sub>PP</sub>                                                              |      | 24              |      | MHz   | С                            |

| Slew rate                                         | V <sub>OCM</sub> input = 1 V <sub>STEP</sub>                                                               |      | 15              |      | V/µs  | С                            |

| Gain                                              |                                                                                                            | 0.99 | 0.996           | 1.01 | V/V   | А                            |

| Common-mode offset voltage                        | Offset = output common-mode voltage - V <sub>OCM</sub> input voltage                                       |      | ±1              | ±5   | mV    | A                            |

| V <sub>OCM</sub> input bias current               | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                                            |      | ±20             | ±120 | nA    | А                            |

| V <sub>OCM</sub> input voltage range              |                                                                                                            | 0.95 | 0.75 to<br>4.15 | 4.0  | V     | A                            |

| V <sub>OCM</sub> input impedance                  |                                                                                                            |      | 65    0.86      |      | kΩ∥pF | С                            |

| Default voltage offset from $(V_{S+} - V_{S-})/2$ | Offset = output common-mode voltage – $(V_{S+} - V_{S-})/2$                                                |      | ±3              | ±10  | mV    | А                            |

TEXAS INSTRUMENTS

www.ti.com

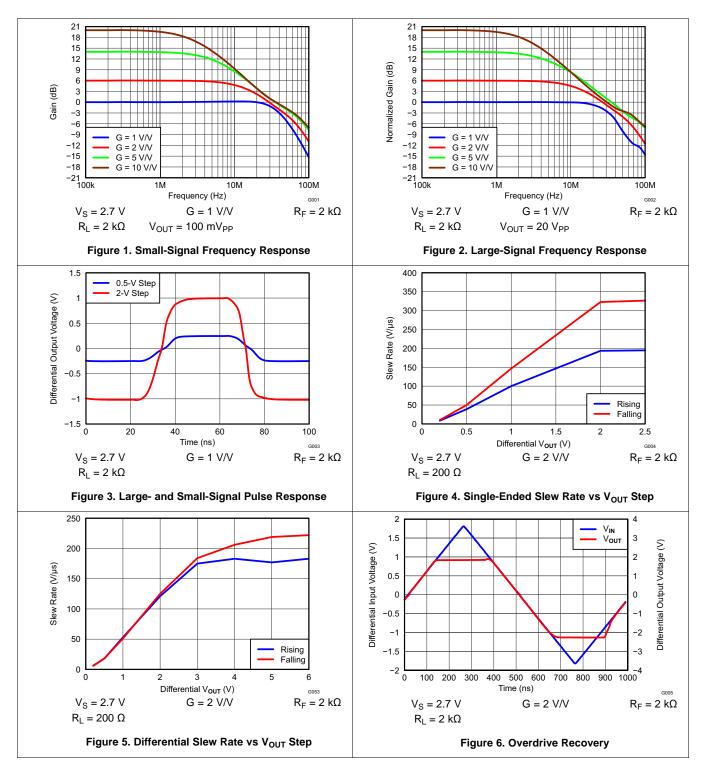

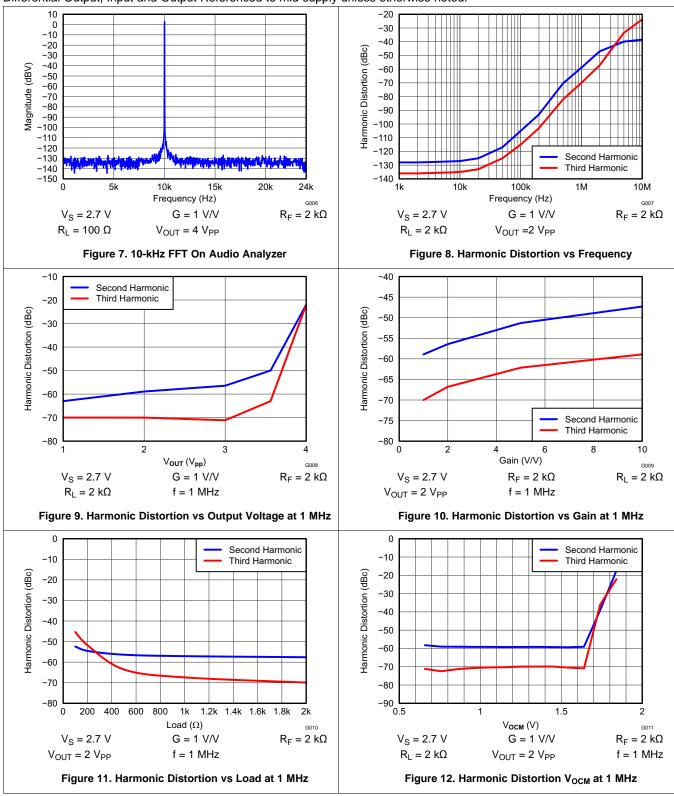

# 7.7 Typical Characteristics

### Table 3. Table of Graphs

| DESCRIPTION                                                         | V <sub>S</sub> = 2.7 V | V <sub>S</sub> = 5 V |

|---------------------------------------------------------------------|------------------------|----------------------|

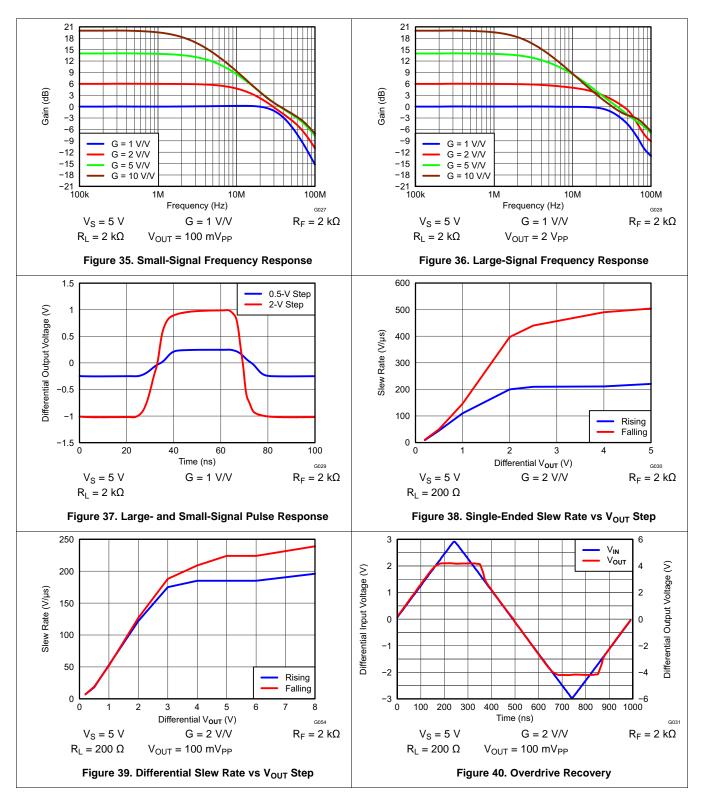

| Small-signal frequency response                                     | Figure 1               | Figure 35            |

| Large-signal frequency response                                     | Figure 2               | Figure 36            |

| Large- and small- signal pulse response                             | Figure 3               | Figure 37            |

| Single-ended slew rate vs V <sub>OUT</sub> step                     | Figure 4               | Figure 38            |

| Differential slew rate vs V <sub>OUT</sub> step                     | Figure 5               | Figure 39            |

| Overdrive recovery                                                  | Figure 6               | Figure 40            |

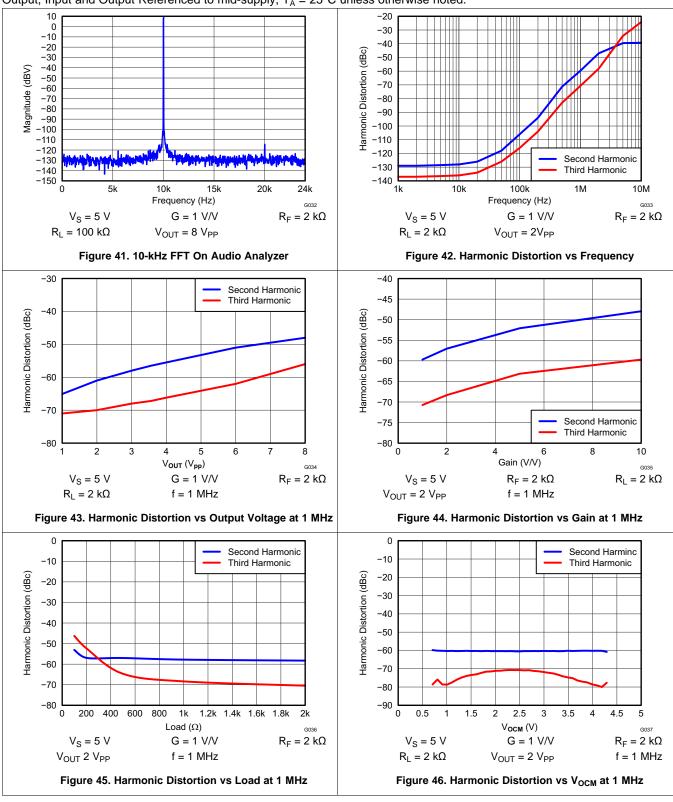

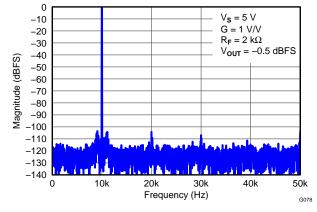

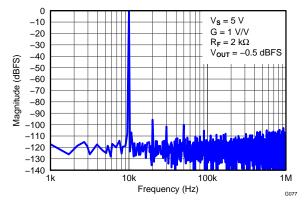

| 10-kHz FFT on audio analyzer                                        | Figure 7               | Figure 41            |

| Harmonic distortion vs Frequency                                    | Figure 8               | Figure 42            |

| Harmonic distortion vs Output voltage at 1 MHz                      | Figure 9               | Figure 43            |

| Harmonic distortion vs Gain at 1 MHz                                | Figure 10              | Figure 44            |

| Harmonic distortion vs Load at 1 MHz                                | Figure 11              | Figure 45            |

| Harmonic distortion vs V <sub>OCM</sub> at 1 MHz                    | Figure 12              | Figure 46            |

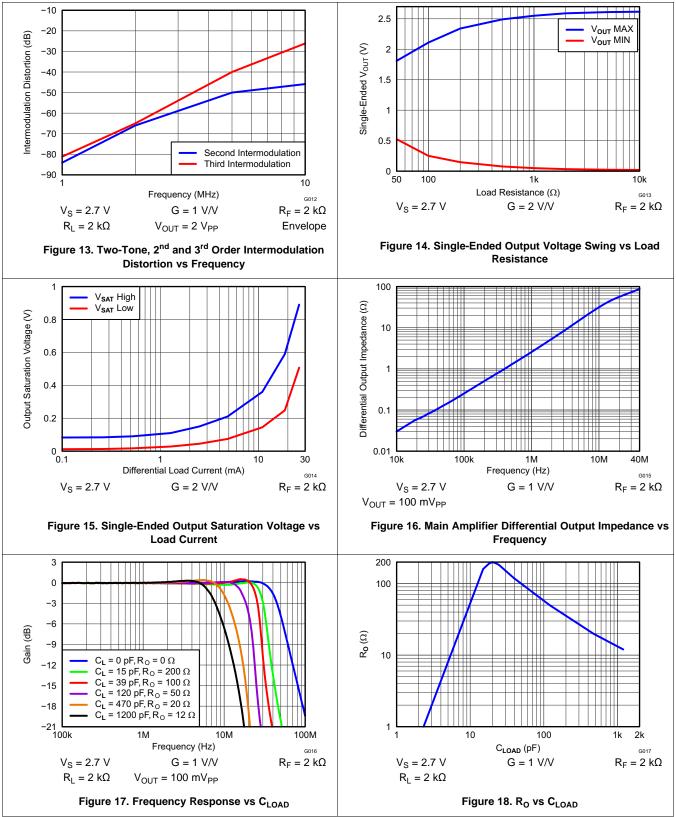

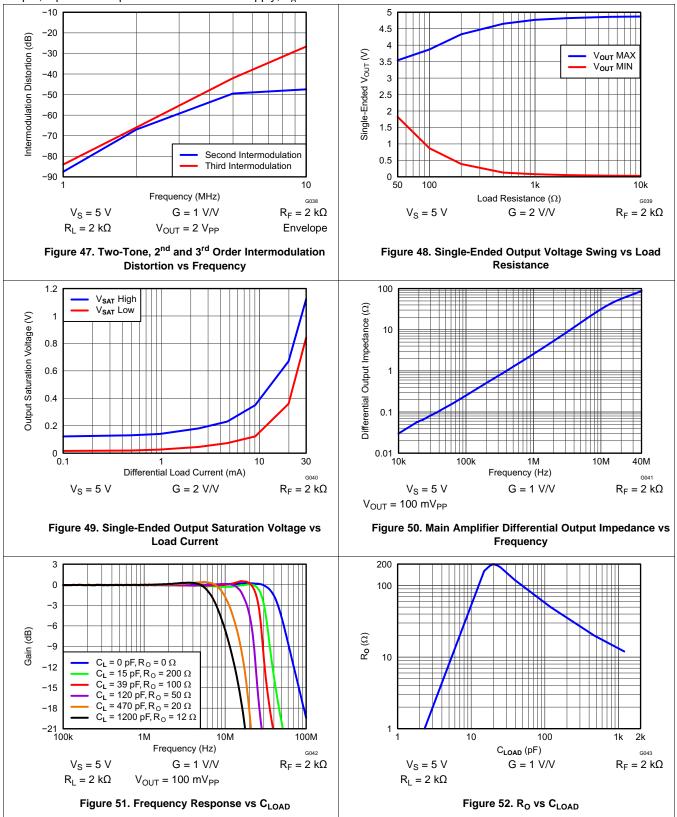

| Two-tone, 2nd and 3rd order intermodulation distortion vs Frequency | Figure 13              | Figure 47            |

| Single-ended output voltage swing vs Load resistance                | Figure 14              | Figure 48            |

| Single-ended output saturation voltage vs Load current              | Figure 15              | Figure 49            |

| Main amplifier differential output impedance vs Frequency           | Figure 16              | Figure 50            |

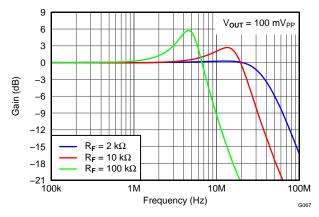

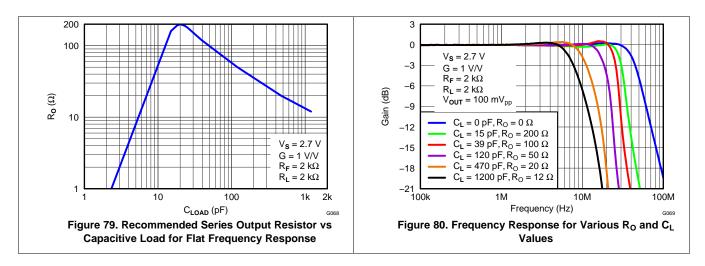

| Frequency response vs C <sub>LOAD</sub>                             | Figure 17              | Figure 51            |

| R <sub>O</sub> vs C <sub>LOAD</sub>                                 | Figure 18              | Figure 52            |

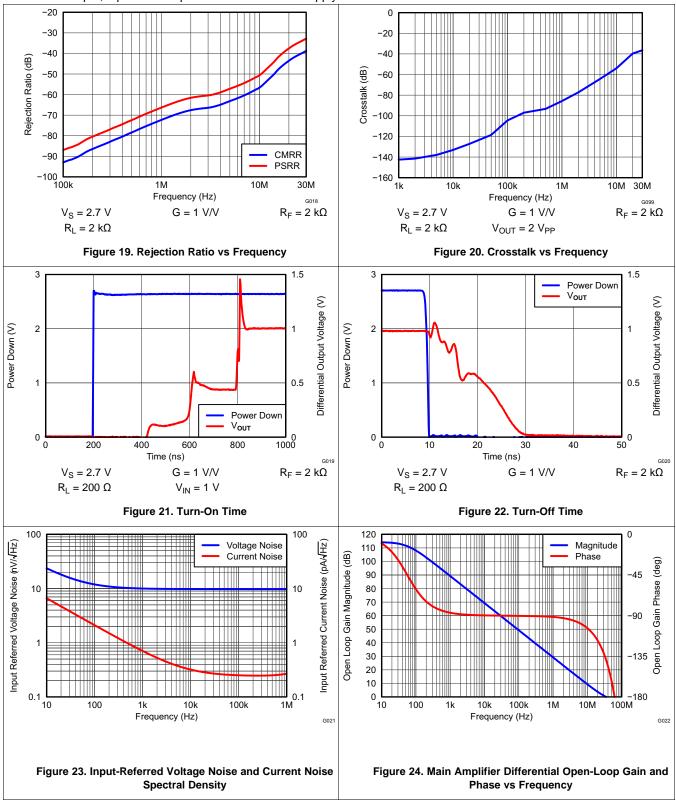

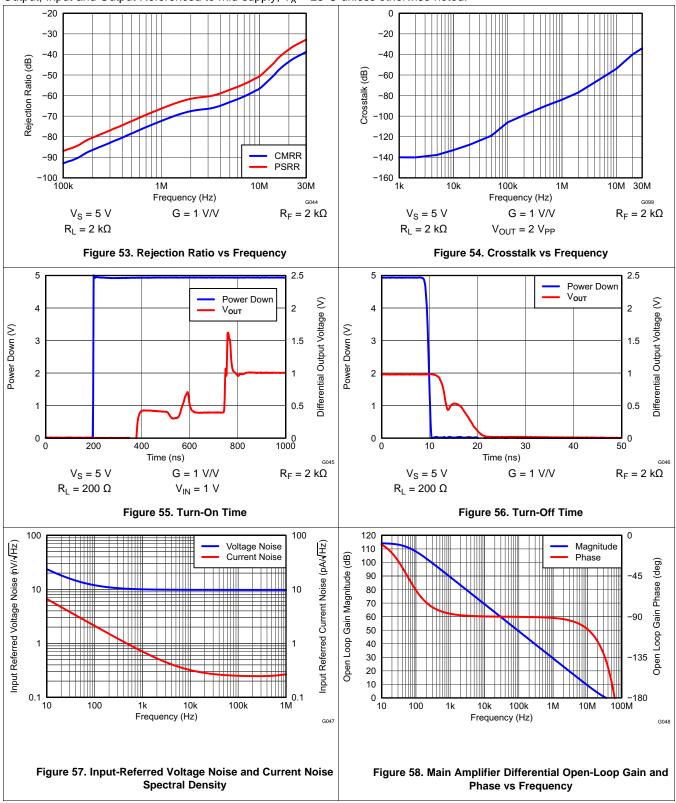

| Rejection ratio vs Frequency                                        | Figure 19              | Figure 53            |

| Crosstalk vs Frequency                                              | Figure 20              | Figure 54            |

| Turn-on time                                                        | Figure 21              | Figure 55            |

| Turn-off time                                                       | Figure 22              | Figure 56            |

| Input-referred voltage noise and current noise spectral density     | Figure 23              | Figure 57            |

| Main amplifier differential open-loop gain and phase vs Frequency   | Figure 24              | Figure 58            |

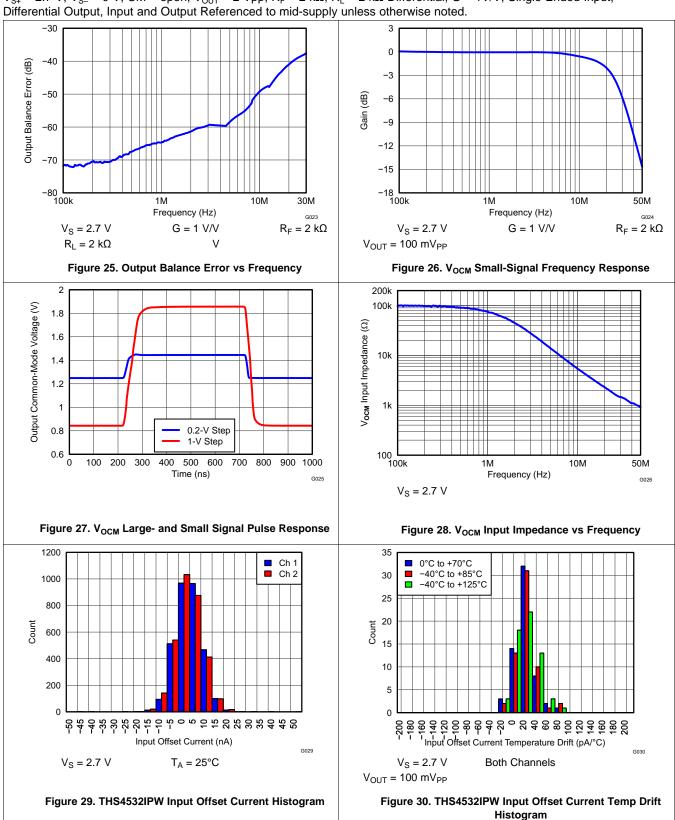

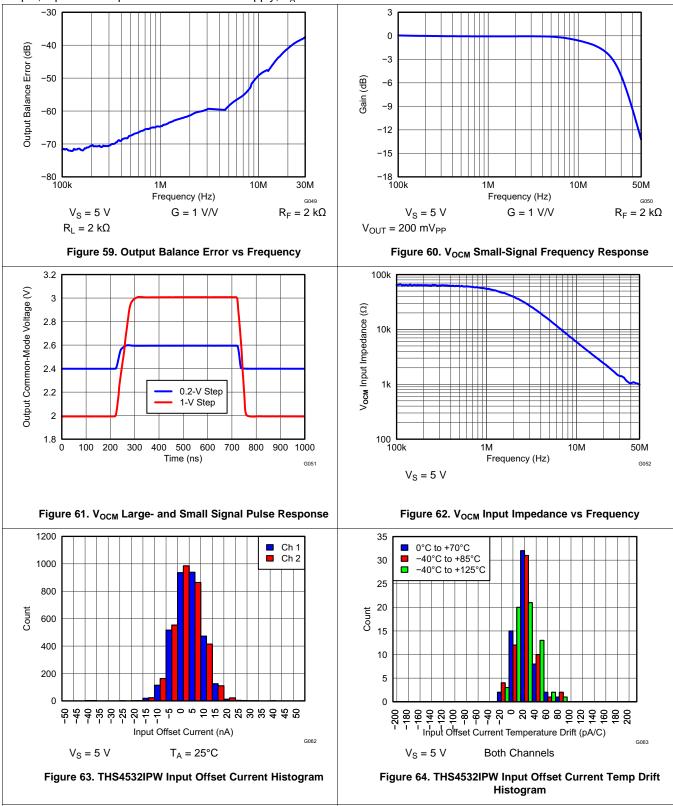

| Output balance error vs Frequency                                   | Figure 25              | Figure 59            |

| V <sub>OCM</sub> small signal frequency response                    | Figure 26              | Figure 60            |

| V <sub>OCM</sub> large and small signal pulse response              | Figure 27              | Figure 61            |

| V <sub>OCM</sub> input impedance vs frequency                       | Figure 28              | Figure 62            |

| Count vs input offset current                                       | Figure 29              | Figure 63            |

| Count vs input offset current temperature drift                     | Figure 30              | Figure 64            |

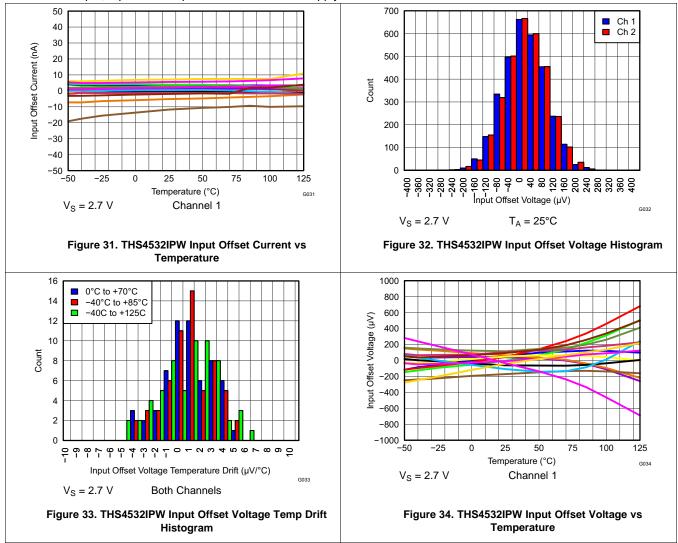

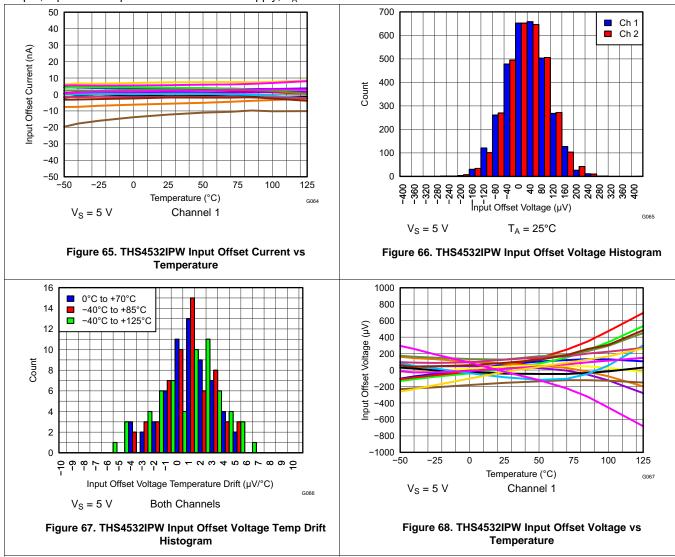

| Input offset current vs temperature                                 | Figure 31              | Figure 65            |

| Count vs input offset voltage                                       | Figure 32              | Figure 66            |

| Count vs input offset voltage temperature drift                     | Figure 33              | Figure 67            |

| Input offset voltage vs temperature                                 | Figure 34              | Figure 68            |

### 7.7.1 Typical Characteristics: V<sub>S</sub> = 2.7 V

# Typical Characteristics: V<sub>s</sub> = 2.7 V (continued)

### Typical Characteristics: V<sub>s</sub> = 2.7 V (continued)

$V_{S+} = 2.7 \text{ V}, V_{S-} = 0 \text{ V}, \text{CM} = \text{open}, V_{OUT} = 2 \text{ Vpp}, R_F = 2 \text{ k}\Omega, R_L = 2 \text{ k}\Omega$  Differential, G = 1V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

Copyright © 2013–2015, Texas Instruments Incorporated

# Typical Characteristics: V<sub>s</sub> = 2.7 V (continued)

### Typical Characteristics: V<sub>s</sub> = 2.7 V (continued)

# Typical Characteristics: V<sub>s</sub> = 2.7 V (continued)

### 7.7.2 Typical Characteristics: V<sub>S</sub> = 5 V

# Typical Characteristics: V<sub>s</sub> = 5 V (continued)

### Typical Characteristics: V<sub>s</sub> = 5 V (continued)

$V_{S+} = 5 V$ ,  $V_{S-} = 0 V$ ,  $V_{OCM} = open$ ,  $V_{OUT} = 2 Vpp$ ,  $R_F = 2 k\Omega$ ,  $R_L = 2 k\Omega$  Differential, G = 1V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^{\circ}C$  unless otherwise noted.

Copyright © 2013–2015, Texas Instruments Incorporated

# Typical Characteristics: V<sub>s</sub> = 5 V (continued)

### Typical Characteristics: V<sub>s</sub> = 5 V (continued)

# Typical Characteristics: V<sub>s</sub> = 5 V (continued)

8

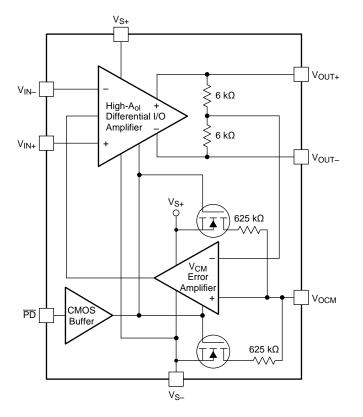

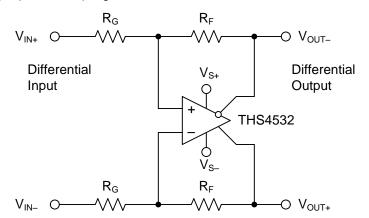

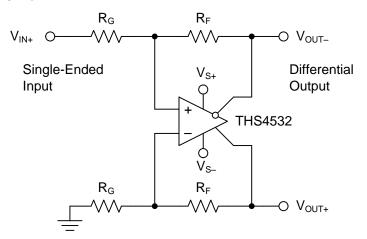

As shown in the Functional Block Diagram, the THS4532 device is comprised of three functional blocks: a fully-

differential amplifier with high open-loop gain of 114 dB, a servo amplifier to set the common-mode voltage of the output equal to the V<sub>OCM</sub> input, and a power-down circuit to greatly reduce the power consumption when the device is idle.

The common-mode voltage servo has impressive performance specifications of ±1% maximum gain error, ±5-mV maximum voltage offset, and 24-MHz bandwidth.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Input Common-Mode Voltage Range

The input common-mode voltage of a fully-differential amplifier is the voltage at the positive and negative (+ and -) input pins of the amplifier.

Do not violate the input common-mode voltage range (V<sub>ICR</sub>) of the amplifier. Assuming the amplifier is in linear operation, the voltage across the input pins is only a few millivolts at most. Therefore, finding the voltage at one input pin determines the input common-mode voltage of the amplifier.

Use Equation 1 to calculate the voltage with the negative input as a summing node.

$$\left(V_{OUT+} \times \frac{R_G}{R_G + R_F}\right) + \left(V_{IN-} \times \frac{R_F}{R_G + R_F}\right)$$

To determine the  $V_{ICR}$  of the amplifier, the voltage at the negative input is evaluated at the extremes of  $V_{OUT+}$ .

As the gain of the amplifier increases, the input common-mode voltage becomes closer and closer to the input common-mode voltage of the source.

(1)

26

### Feature Description (continued)

### 8.3.1.1 Setting the Output Common-Mode Voltage

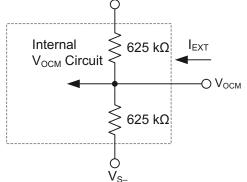

The output common-model voltage is set by the voltage at the V<sub>OCM</sub> pin and the internal circuit works to maintain the output common-mode voltage as close as possible to this voltage. If left unconnected, the output commonmode is set to mid-supply by internal circuitry, which may be over-driven from an external source. Figure 69 is representative of the V<sub>OCM</sub> input. The internal V<sub>OCM</sub> circuit has about 24-MHz of -3-dB bandwidth, which is required for best performance, but it is intended to be a DC bias input pin. Bypass capacitors are recommended on this pin to reduce noise. Use Equation 2 to calculate the external current required to overdrive the internal resistor divider.

$$I_{EXT} = \frac{2V_{OCM} - \left(V_{S^{+}} + V_{S^{-}}\right)}{625 \text{ k}\Omega}$$

where

$V_{OCM}$  is the voltage applied to the  $V_{OCM}$  pin.

Figure 69. Simplified V<sub>OCM</sub> Input Circuit

$V_{S+}$

(2)

### Feature Description (continued)

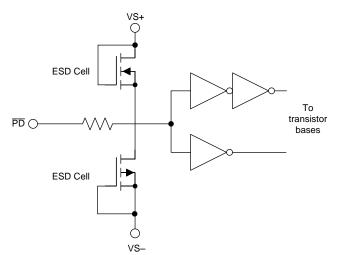

### 8.3.2 Power Down

The power down pin is internally connected to a CMOS stage which must be driven to a minimum of 2.1 V to ensure proper high logic.

Figure 70. Simplified Power-Down Internal Circuit

If 1.8-V logic is used to drive the pin, a shoot through current of up to 100  $\mu$ A may develop in the digital logic causing the overall quiescent current to exceed the 2  $\mu$ A of maximum disabled quiescent current specified in the *Electrical Characteristics:* V<sub>S</sub> = 2.7 V.

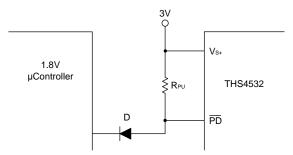

To properly interface to 1.8-V logic with minimal increase in additional current draw, a logic-level translator like the SN74AVC1T45 device can be used.

Alternatively, the same function can be achieved using a diode and pullup resistor as shown in Figure 71.

Figure 71. THS5432 Power Down Interface to 1.8-V Logic Microcontroller

The voltage at the power down pin will be a function of the supply voltage, input logic level, and diode drop. As long as the diode is forward biased, the power down voltage is calculated using Equation 3.

$V_{PD} = V_L + V_f$

where

- $V_{L}$  is the logic level voltage.

- V<sub>f</sub> is the forward voltage drop across the diode.

(3)

This means for 1.8-V logic, the forward voltage of the diode should be greater than 0.3 V but less than 0.7 V to keep the power down logic level above 2.1 V and less than 0.7 V respectively.

For example, if 1N914 is selected as the diode with a forward voltage of approximately 0.4 V, the translated logic voltages will be 0.4 V for disabled operation and 2.2 V for enabled operation.

### Feature Description (continued)

Use Equation 4 to calculate the additional current draw.

$$i_{PD} = \frac{V_{CC} - (V_L + V_f)}{R_{PU}}$$

(4)

Equation 2 shows that larger values of RPU result in a smaller additional current. A reasonable value of RPU is 500 k $\Omega$  where an additional current draw of 5.2  $\mu$ A is expected while the device is in operation and 1.6  $\mu$ A when disabled.

### 8.4 Device Functional Modes

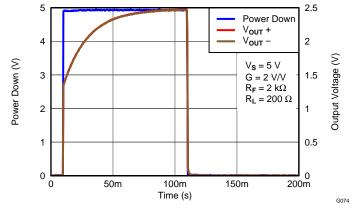

The THS4532 has two functional modes: full-power mode and power-down mode. The power-down mode reduces the quiescent current of the device to 500 nA from a typical value of 290 µA with a 5-V supply.

With a turnon time of only 600 ns and a turnoff time of 15 ns, the power-down mode can be used to greatly reduce the average power consumption of the device without sacrificing system performance.

### 9 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

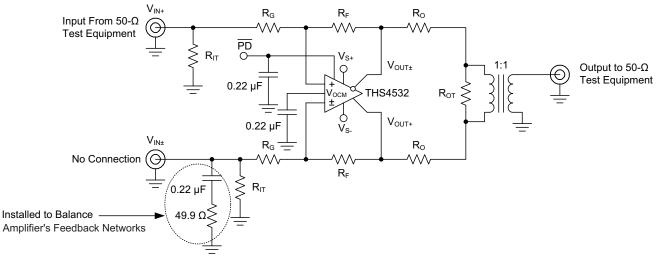

### 9.1 Application Information

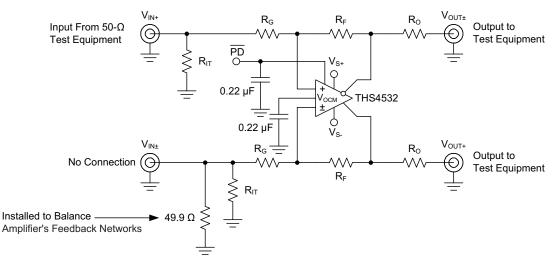

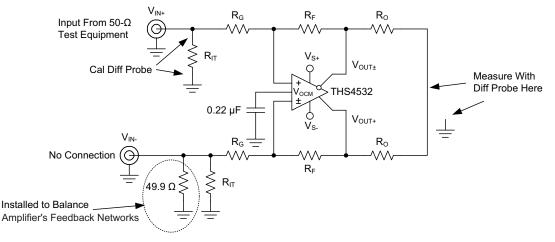

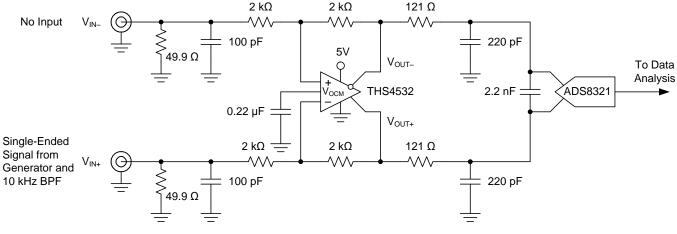

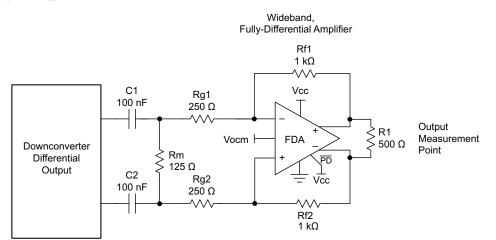

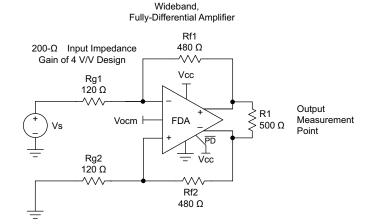

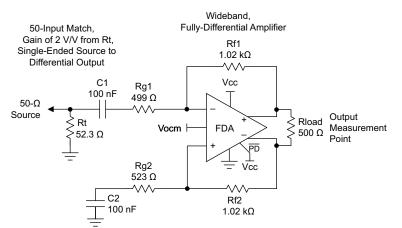

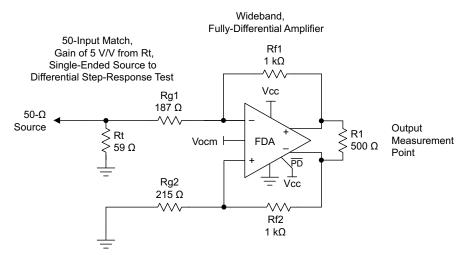

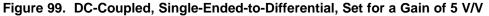

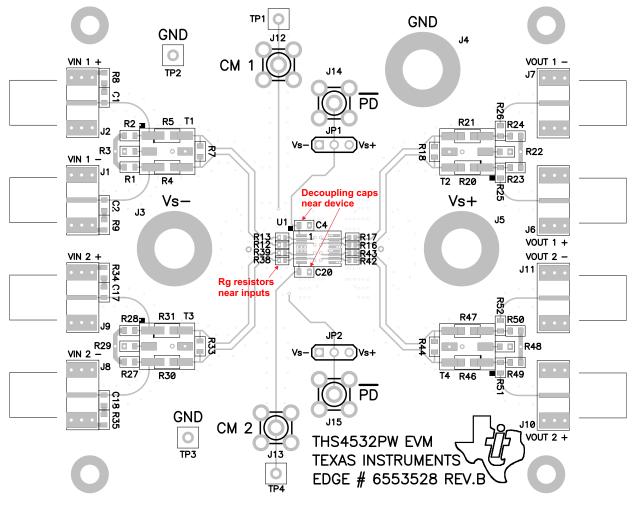

Figure 72 shows the general test circuit built on the EVM that was used for testing the THS5432. For simplicity, power supply decoupling is not shown – see *Layout* for recommendations. Depending on the test conditions, component values are changed per Table 4 and Table 5, or as otherwise noted. Some of the signal generators used are AC-coupled 50- $\Omega$  sources and a 0.22- $\mu$ F capacitor and 49.9- $\Omega$  resistor to ground are inserted across R<sub>IT</sub> on the un-driven or alternate input as shown to balance the circuit. A split-power supply is used to ease the interface to common lab test equipment, but if properly biased, the amplifier can be operated single-supply as described in the applications section with no impact on performance. For most of the tests, the devices are tested with single ended input and a transformer on the output to convert the differential output to single ended because common lab test equipment have single ended inputs and outputs. Performance is the same or better with differential input and differential output.

### Figure 72. General Test Circuit

|        | -              |                |                 |

|--------|----------------|----------------|-----------------|

| GAIN   | R <sub>F</sub> | R <sub>G</sub> | R <sub>IT</sub> |

| 1 V/V  | 2 kΩ           | 2 kΩ           | 51.1 Ω          |

| 2 V/V  | 2 kΩ           | 1 kΩ           | 52.3 Ω          |

| 5 V/V  | 2 kΩ           | 392 Ω          | 53.6 Ω          |

| 10 V/V | 2 kΩ           | 187 Ω          | 57.6 Ω          |

(1) Components are chosen to achieve gain and 50-Ω input termination. Resistor values shown are closest standard values so gains are approximate.

|       | •              | 5               |            |

|-------|----------------|-----------------|------------|

| RL    | R <sub>o</sub> | R <sub>ot</sub> | ATTEN (dB) |

| 100 Ω | 25 Ω           | open            | 6          |

| 200 Ω | 84.5 Ω         | 71.5 Ω          | 16.7       |

| 500 Ω | 237 Ω          | 56.2 Ω          | 25.6       |

| 1 kΩ  | 487 Ω          | 52.3 Ω          | 31.8       |

| 2 kΩ  | 976 Ω          | 51.1 Ω          | 38         |

### Table 5. Load Component Values For 1:1 Differential to Single-Ended Output Transformer<sup>(1)</sup>

(1) The total load includes  $50-\Omega$  termination by the test equipment. Components are chosen to achieve load and  $50-\Omega$  line termination through a 1:1 transformer. Resistor values shown are closest standard values so loads are approximate.

Because of the voltage divider on the output formed by the load component values, the output of the amplifier is attenuated. The column *ATTEN* in Table 5 shows the attenuation expected from the resistor divider. When using a transformer at the output as shown in Figure 72, the signal has slightly more loss because of transformer insertion loss, and these numbers are approximate. The standard output load used for most tests is 2 k $\Omega$  with associated 38 dB of loss.

### 9.1.1 Frequency Response and Output Impedance

The circuit shown in Figure 72 is used to measure the frequency response of the amplifier.

A network analyzer is used as the signal source and the measurement device. The output impedance of the network analyzer is 50  $\Omega$  and is AC coupled. R<sub>IT</sub> and R<sub>G</sub> are selected to impedance match to 50  $\Omega$  and maintain the proper gain. To balance the amplifier, a 49.9- $\Omega$  resistor and blocking capacitor to ground is inserted across R<sub>IT</sub> on the alternate input.

The output is routed to the input of the network analyzer through 50- $\Omega$  coax. For a 2k load, 38 dB is added to the measurement to refer back to the output of the amplifier according to Table 5.

For output impedance, the signal is injected at  $V_{OUT}$  with  $V_{IN}$  left open. The voltage drop across the 2x  $R_O$  resistors is measured with a high impedance differential probe and used to calculate the impedance into the output of the amplifier.

### 9.1.2 Distortion

At 1 MHz and above, the circuit shown in Figure 72 is used to measure harmonic, intermodulation distortion, and output impedance of the amplifier.

A signal generator is used as the signal source and the output is measured with a spectrum analyzer. The output impedance of the signal generator is 50  $\Omega$  and is AC coupled. R<sub>IT</sub> and R<sub>G</sub> are chosen to impedance match to 50  $\Omega$  and maintain the proper gain. To balance the amplifier, a 0.22-µF capacitor and 49.9- $\Omega$  resistor to ground is inserted across R<sub>IT</sub> on the alternate input. A low-pass filter is inserted in series with the input to reduce harmonics generated by the signal source. The level of the fundamental is measured and then a high-pass filter is inserted at the output to reduce the fundamental so it does not generate distortion in the input of the spectrum analyzer.

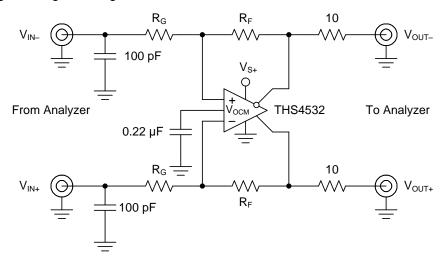

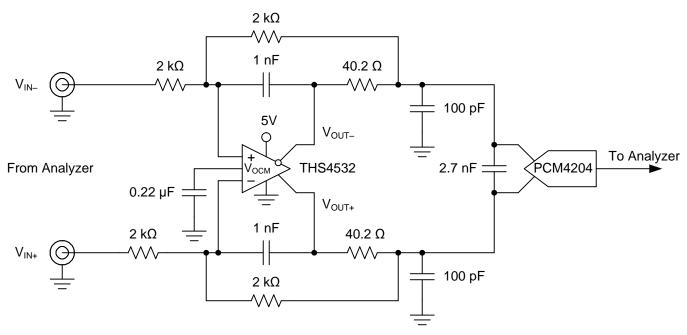

Distortion in the audio band is measured using an audio analyzer. Refer to the *Audio Performance* section for details.

# 9.1.3 Slew Rate, Transient Response, Settling Time, Overdrive, Output Voltage, and Turnon and Turnoff Time

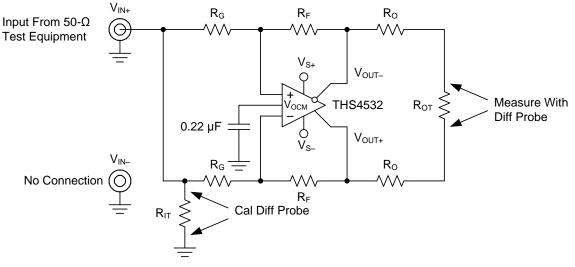

The circuit shown in Figure 73 is used to measure slew rate, transient response, settling time, overdrive recovery, and output voltage swing. Turnon and turnoff times are measured with  $50-\Omega$  input termination on the PD input, by replacing the 0.22-µF capacitor with 49.9- $\Omega$  resistor.

Figure 73. Slew Rate, Transient Response, Settling Time, Z<sub>0</sub>, Overdrive Recovery, V<sub>OUT</sub> Swing, and Turn-On and Turn-Off Test Circuit

### 9.1.4 Common-Mode and Power Supply Rejection

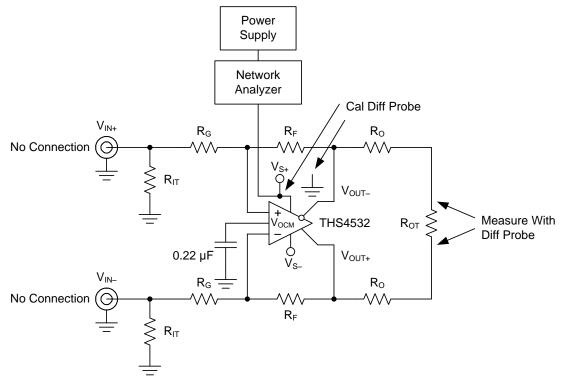

The circuit shown in Figure 74 is used to measure the CMRR. The signal from the network analyzer is applied common-mode to the input.

Figure 74. CMRR Test Circuit

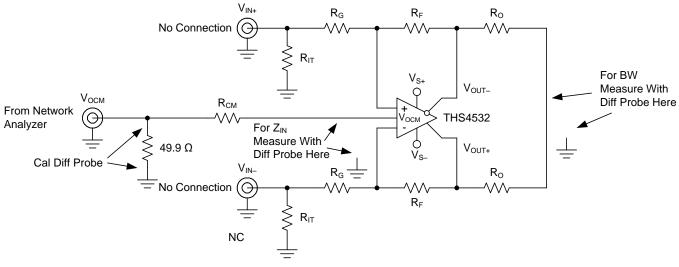

Figure 75 is used to measure the PSRR of  $V_{S+}$  and  $V_{S-}$ . The power supply is applied to the network DC offset input of the analyzer. For both CMRR and PSRR, the output is probed using a high impedance differential probe across  $R_{OT}$ . The calculated CMRR and PSRR are referred to the input of the device.

TEXAS INSTRUMENTS

www.ti.com