# 500 mA, Ultra-Low Quiescent Current, I<sub>Q</sub> 13 μA, **Ultra-Low Noise, LDO Voltage Regulator**

Noise sensitive RF applications such as Power Amplifiers in satellite radios, infotainment equipment, and precision instrumentation require very clean power supplies. The NCP705 is 500 mA LDO that provides the engineer with a very stable, accurate voltage with ultra low noise and very high Power Supply Rejection Ratio (PSRR) suitable for RF applications. The device doesn't require any additional noise bypass capacitor to achieve ultra-low noise performance. In order to optimize performance for battery operated portable applications, the NCP705 employs dynamic Iq management for ultra-low quiescent current consumption at light-load conditions and great dynamic performance.

## **Features**

- Operating Input Voltage Range: 2.5 V to 5.5 V

- Available Fixed Voltage Option: 0.8 V to 3.5 V

- Adjustable Voltage Option: 0.8 V to 5.5 V-V<sub>DROP</sub>

- Reference Voltage 0.8 V

- Ultra-Low Quiescent Current of Typ. 13 μA

- Ultra–Low Noise: 12 μV<sub>RMS</sub> from 100 Hz to 100 kHz

- Very Low Dropout: 230 mV Typical at 500 mA

- ±2% Accuracy Over Load/Line/Temperature

- High PSRR: 71 dB at 1 kHz

- Internal Soft-Start to Limit the Turn-On Inrush Current

- Thermal Shutdown and Current Limit Protections

- Stable with a 1 µF Ceramic Output Capacitor

- Active Output Discharge for Fast Turn-Off

- These are Pb-Free Devices

## **Typical Applications**

- PDAs, Mobile Phones, GPS, Smartphones

- Wireless Handsets, Wireless LAN, Bluetooth®, ZigBee®

- Portable Medical Equipment

- Other Battery Powered Applications

# ON Semiconductor®

www.onsemi.com

# **MARKING DIAGRAM**

WDFN6 CASE 511BR

XX = Specific Device Code = Date Code

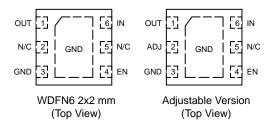

# **PIN CONNECTIONS**

# ORDERING INFORMATION

See detailed ordering, marking and shipping information on page 19 of this data sheet.

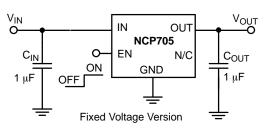

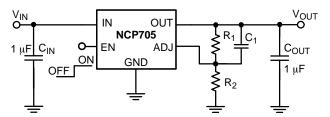

Figure 1. Typical Application Schematics

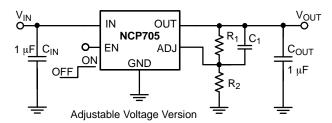

Figure 2. Simplified Schematic Block Diagrams

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name –<br>Fixed | Pin Name –<br>Adjustable | Description                                                                                                                         |

|---------|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OUT                 | OUT                      | Regulated output voltage pin. A small 1 $\mu\text{F}$ ceramic capacitor is needed from this pin to ground to assure stability.      |

| 2       | N/C                 | ADJ                      | Feedback pin for set-up output voltage. Use resistor divider for voltage selection.                                                 |

| 3       | GND                 | GND                      | Power supply ground. Expose pad must be tied with GND pin. Soldered to the copper plane allows for effective heat dissipation.      |

| 4       | EN                  | EN                       | Enable pin. Driving EN over $0.9~\rm V$ turns on the regulator. Driving EN below $0.4~\rm V$ puts the regulator into shutdown mode. |

| 5       | N/C                 | N/C                      | Not connected. This pin can be tied to ground to improve thermal dissipation.                                                       |

| 6       | IN                  | IN                       | Input pin. A small capacitor is needed from this pin to ground to assure stability.                                                 |

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                    | Symbol             | Value                             | Unit |

|-------------------------------------------|--------------------|-----------------------------------|------|

| Input Voltage (Note 1)                    | V <sub>IN</sub>    | –0.3 V to 6 V                     | V    |

| Output Voltage                            | V <sub>OUT</sub>   | –0.3 V to V <sub>IN</sub> + 0.3 V | V    |

| Enable Input                              | V <sub>EN</sub>    | –0.3 V to V <sub>IN</sub> + 0.3 V | V    |

| Adjustable Input                          | $V_{ADJ}$          | –0.3 V to V <sub>IN</sub> + 0.3 V | V    |

| Output Short Circuit Duration             | t <sub>SC</sub>    | Indefinite                        | S    |

| Maximum Junction Temperature              | $T_{J(MAX)}$       | 150                               | °C   |

| Storage Temperature                       | T <sub>STG</sub>   | -55 to 150                        | °C   |

| ESD Capability, Human Body Model (Note 2) | ESD <sub>HBM</sub> | 2000                              | V    |

| ESD Capability, Machine Model (Note 2)    | ESD <sub>MM</sub>  | 200                               | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

# Table 3. THERMAL CHARACTERISTICS (Note 3)

| Rating                                                                                                                    | Symbol                        | Value       | Unit |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|------|

| Thermal Characteristics, WDFN6 2x2 mm Thermal Resistance, Junction–to–Air Thermal Resistance Parameter, Junction–to–Board | $^{	heta_{\sf JA}}_{\sf VJB}$ | 116.5<br>30 | °C/W |

3. Single component mounted on 1 oz, FR 4 PCB with 645 mm<sup>2</sup> Cu area.

# **Table 4. ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \leq T_{J} \leq 125^{\circ}C; \ V_{IN} = V_{OUT(NOM)} + 0.5 \ V \ or \ 2.5 \ V, \ whichever is greater; \ V_{EN} = 0.9 \ V, \ I_{OUT} = 10 \ mA, \ C_{IN} = C_{OUT} = 1 \ \mu F \ unless \ otherwise noted. Typical values are at T_{J} = +25^{\circ}C. \ (Note 4)$

| Parameter                                                   | Test Conditions                                                                                                                |                                                                                    | Symbol                                   | Min | Тур            | Max                     | Unit              |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|-----|----------------|-------------------------|-------------------|

| Operating Input Voltage                                     |                                                                                                                                |                                                                                    | V <sub>IN</sub>                          | 2.5 |                | 5.5                     | V                 |

| Output Voltage Range (Adjustable)                           |                                                                                                                                |                                                                                    | V <sub>OUT</sub>                         | 0.8 |                | 5.5-<br>V <sub>DO</sub> | V                 |

| Undervoltage Lock-out                                       | V <sub>IN</sub> rising                                                                                                         |                                                                                    | UVLO                                     | 1.2 | 1.6            | 1.9                     | V                 |

| Output Voltage Accuracy (Fixed)                             | $V_{OUT} + 0.5 V \le V_{IN} \le 5.5 V$ ,                                                                                       | $I_{OUT} = 0 - 500 \text{ mA}$                                                     | V <sub>OUT</sub>                         | -2  |                | +2                      | %                 |

| Reference Voltage                                           |                                                                                                                                |                                                                                    | $V_{REF}$                                |     | 0.8            |                         | V                 |

| Reference Voltage Accuracy                                  | I <sub>OUT</sub> = 10 mA                                                                                                       |                                                                                    | $V_{REF}$                                | -2  |                | +2                      | %                 |

| Line Regulation                                             | $ \begin{aligned} &V_{OUT} + 0.5 \ V \leq V_{IN} \leq 4.5 \ V, \\ &V_{OUT} + 0.5 \ V \leq V_{IN} \leq 5.5 \ V, \end{aligned} $ | I <sub>OUT</sub> = 10 mA<br>I <sub>OUT</sub> = 10 mA                               | Reg <sub>LINE</sub>                      |     | 550<br>750     |                         | μV/V              |

| Load Regulation                                             | I <sub>OUT</sub> = 0 mA to 500 mA                                                                                              |                                                                                    | Reg <sub>LOAD</sub>                      |     | 12             |                         | μV/mA             |

| Load Transient                                              | $I_{OUT}$ = 1 mA to 500 mA or 5 1 μs, $C_{OUT}$ = 1 μF                                                                         | 00 mA to 1 mA in                                                                   | Tran <sub>LOAD</sub>                     |     | ±120           |                         | mV                |

| Dropout Voltage (Note 5)                                    | I <sub>OUT</sub> = 500 mA, V <sub>OUT(nom)</sub> =                                                                             | = 2.8 V                                                                            | $V_{DO}$                                 |     | 230            | 350                     | mV                |

| Output Current Limit                                        | V <sub>OUT</sub> = 90% V <sub>OUT(nom)</sub>                                                                                   | NCP705                                                                             | I <sub>CL</sub>                          | 510 | 750            | 950                     | mA                |

|                                                             |                                                                                                                                | $\begin{array}{l} NCP705E \\ (0^{\circ}C \leq T_{J} \leq 70^{\circ}C) \end{array}$ |                                          | 600 | 750            | 950                     |                   |

| Quiescent Current                                           | I <sub>OUT</sub> = 0 mA                                                                                                        |                                                                                    | IQ                                       |     | 13             | 25                      | μΑ                |

| Ground Current                                              | I <sub>OUT</sub> = 500 mA                                                                                                      |                                                                                    | I <sub>GND</sub>                         |     | 260            |                         | μΑ                |

| Shutdown Current                                            | $V_{EN} \le 0.4 \text{ V}, T_J = +25^{\circ}\text{C}$                                                                          |                                                                                    | I <sub>DIS</sub>                         |     | 0.12           |                         | μΑ                |

|                                                             | $V_{EN} \le 0 \text{ V}, V_{IN} = 2.0 \text{ to } 4.5 \text{ V}, T_J = -40 \text{ to } +85^{\circ}\text{C}$                    |                                                                                    | I <sub>DIS</sub>                         |     | 0.55           | 2                       | μΑ                |

| EN Pin Threshold Voltage<br>High Threshold<br>Low Threshold | V <sub>EN</sub> Voltage increasing<br>V <sub>EN</sub> Voltage decreasing                                                       |                                                                                    | V <sub>EN_HI</sub><br>V <sub>EN_LO</sub> | 0.9 |                | 0.4                     | V                 |

| EN Pin Input Current                                        | V <sub>EN</sub> = 5.5 V                                                                                                        |                                                                                    | I <sub>EN</sub>                          |     | 100            | 500                     | nA                |

| ADJ Pin Current                                             | V <sub>ADJ</sub> = 0.8 V                                                                                                       |                                                                                    |                                          |     | 1              |                         | nA                |

| Turn-On Time                                                | C <sub>OUT</sub> = 1.0 μF, from assertion EN pin to 98% V <sub>OUT</sub> (nom)                                                 |                                                                                    | t <sub>ON</sub>                          |     | 150            |                         | μs                |

| Power Supply Rejection Ratio                                | $V_{IN} = 3.8 \text{ V}, V_{OUT} = 2.8 \text{ V}$ (Fixed), $I_{OUT} = 500 \text{ mA}$ f = 100 Hz f = 1 kHz f = 10 kHz          |                                                                                    | PSRR                                     |     | 73<br>71<br>56 |                         | dB                |

| Output Noise Voltage                                        | $V_{OUT}$ = 2.5 V (Fixed), $V_{IN}$ = 3.5 V, $I_{OUT}$ = 500 mA f = 100 Hz to 100 kHz                                          |                                                                                    | V <sub>N</sub>                           |     | 12             |                         | μV <sub>rms</sub> |

| Thermal Shutdown Temperature                                | Temperature increasing from T <sub>J</sub> = +25°C                                                                             |                                                                                    | T <sub>SD</sub>                          |     | 160            |                         | °C                |

| Thermal Shutdown Hysteresis                                 | Temperature falling from T <sub>S</sub>                                                                                        | D                                                                                  | T <sub>SDH</sub>                         | _   | 20             | -                       | °C                |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>4.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

5. Characterized when V<sub>OUT</sub> falls 100 mV below the regulated voltage at V<sub>IN</sub> = V<sub>OUT(NOM)</sub> + 0.5 V.

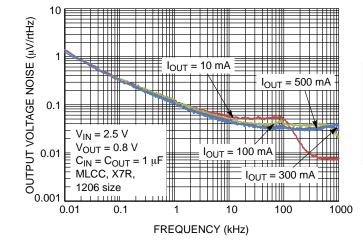

|        | RMS Output Noise (μV) |                  |  |

|--------|-----------------------|------------------|--|

| IOUT   | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| 10 mA  | 19.06                 | 18.21            |  |

| 100 mA | 15.99                 | 15.04            |  |

| 300 mA | 14.42                 | 13.39            |  |

| 500 mA | 13.70                 | 12.60            |  |

Figure 3. Output Voltage Noise Spectral Density for  $V_{OUT}$  = 0.8 V,  $C_{OUT}$  = 1  $\mu F$

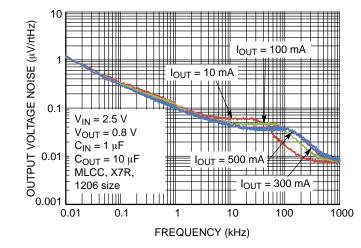

|                  | RMS Output Noise (μV) |                  |  |

|------------------|-----------------------|------------------|--|

| I <sub>OUT</sub> | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| 10 mA            | 16.17                 | 15.28            |  |

| 100 mA           | 16.41                 | 15.65            |  |

| 300 mA           | 14.94                 | 14.10            |  |

| 500 mA           | 14.08                 | 13.11            |  |

Figure 4. Output Voltage Noise Spectral Density for  $V_{OUT}$  = 0.8 V,  $C_{OUT}$  = 10  $\mu F$

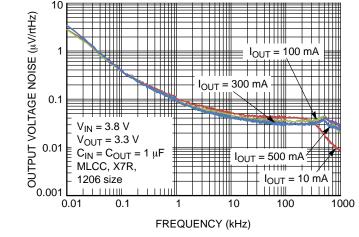

|        | RMS Output Noise (μV) |                  |  |

|--------|-----------------------|------------------|--|

| IOUT   | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| 10 mA  | 18.12                 | 15.39            |  |

| 100 mA | 16.42                 | 13.50            |  |

| 300 mA | 16.35                 | 12.47            |  |

| 500 mA | 16.00                 | 12.10            |  |

Figure 5. Output Voltage Noise Spectral Density for  $V_{OUT}$  = 3.3 V,  $C_{OUT}$  = 1  $\mu F$

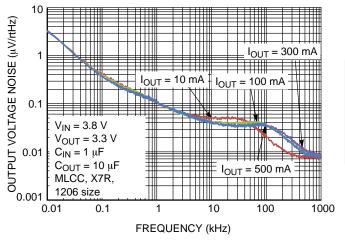

|        | RMS Output Noise (μV) |                  |  |

|--------|-----------------------|------------------|--|

| lоит   | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| 1 mA   | 17.35                 | 14.07            |  |

| 100 mA | 17.43                 | 14.29            |  |

| 300 mA | 16.55                 | 13.33            |  |

| 500 mA | 16.48                 | 13.20            |  |

Figure 6. Output Voltage Noise Spectral Density for  $V_{OUT}$  = 3.3 V,  $C_{OUT}$  = 10  $\mu F$

| .,               | RMS Output Noise (μV) |                  |  |

|------------------|-----------------------|------------------|--|

| V <sub>OUT</sub> | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| 1.5 V            | 31.40                 | 30.33            |  |

| 3.3 V            | 49.14                 | 44.30            |  |

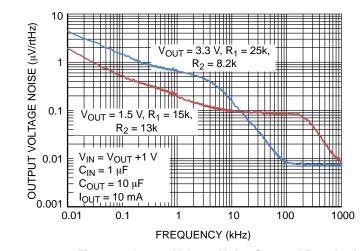

Figure 7. Output Voltage Noise Spectral Density for Adjustable Version – Different Output Voltage

|                  | RMS Output Noise (μV) |                  |  |

|------------------|-----------------------|------------------|--|

| I <sub>OUT</sub> | 10 Hz – 100 kHz       | 100 Hz – 100 kHz |  |

| none             | 50.17                 | 43.85            |  |

| 100 pF           | 46.90                 | 40.39            |  |

| 1 nF             | 36.92                 | 27.99            |  |

| 10 nF            | 27.02                 | 18.31            |  |

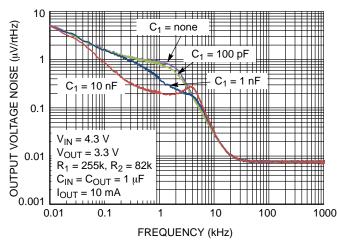

Figure 8. Output Voltage Noise Spectral Density for Adjustable Version for Various C1

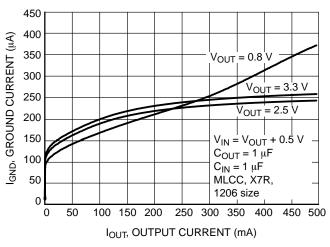

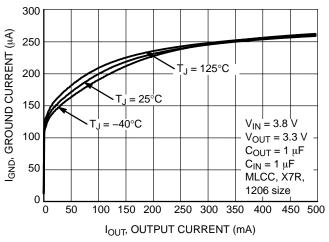

Figure 9. Ground Current vs. Output Current

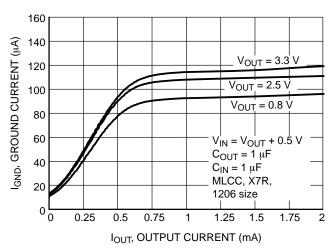

Figure 10. Ground Current vs. Output Current from 0 mA to 2 mA

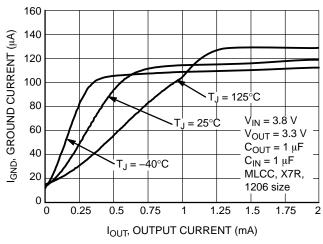

Figure 11. Ground Current vs. Output Current at Temperatures

Figure 12. Ground Current vs. Output Current 0 mA to 2 mA at Temperature

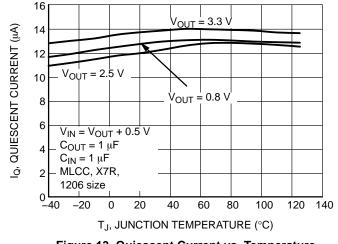

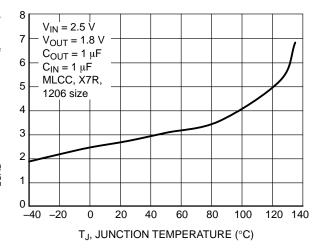

Figure 13. Quiescent Current vs. Temperature

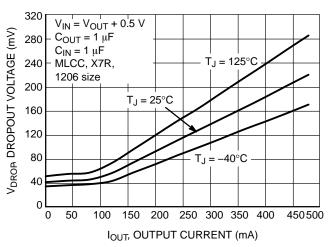

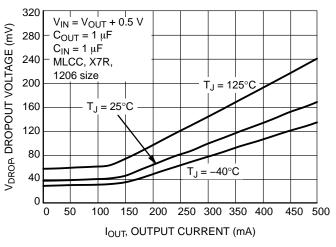

Figure 14. Dropout Voltage vs. Output Current at Temperature (2.5 V)

Figure 15. Dropout Voltage vs. Output Current at Temperatures (3.3 V)

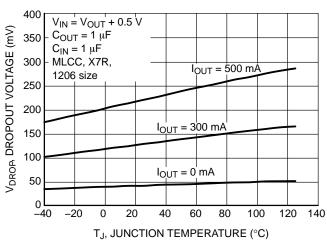

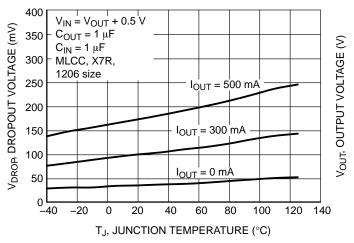

Figure 16. Dropout Voltage vs. Temperature (2.5 V)

Figure 17. Dropout Voltage vs. Temperature, (3.3 V)

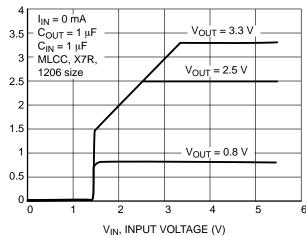

Figure 18. Input Voltage vs. Output Voltage

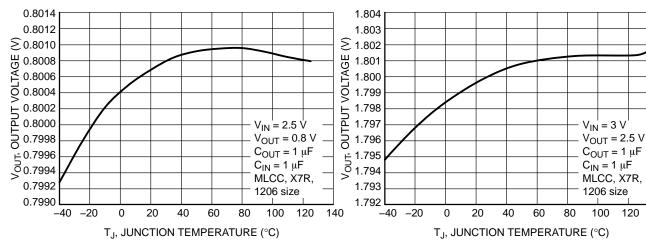

Figure 19. Output Voltage vs. Temperature, (0.8 V)

Figure 20. Output Voltage vs. Temperature, (2.5 V)

# TYPICAL CHARACTERISTICS

700

REGLINE, LINE REGULATION (µV/V) 680 660 640 620 600  $V_{IN} = 2.5 \text{ V}$ 580  $V_{OUT} = 1.8 V$ 560  $C_{OUT} = 1 \mu F$ 540  $C_{IN} = 1 \, \mu F$ MLCC, X7R, 520 1206 size 500 -40 -20 40 60 80 100 120 140 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

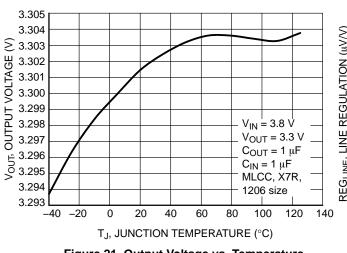

Figure 21. Output Voltage vs. Temperature, (3.3 V)

Figure 22. Line Regulation vs. Temperature, (1.8 V)

Figure 23. Line Regulation vs. Temperature, (3.3 V)

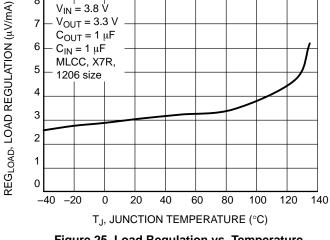

Figure 24. Load Regulation vs. Temperature, (1.8 V)

Figure 25. Load Regulation vs. Temperature, (3.3 V)

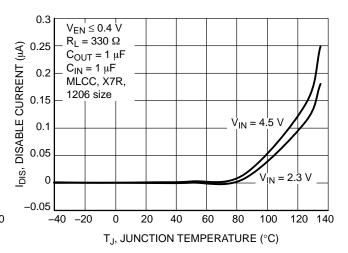

Figure 26. Disable Current vs. Temperature

750 735 720 **CURRENT LIMIT (mA)** 705 /<sub>OUT</sub> = 1.8 690 675 660 VouŢ  $V_{IN} = V_{OUT} + 0.5 V$ 645  $C_{OUT} = 1 \mu F$ ŗ, 630  $C_{IN} = 1 \mu F$ MLCC, X7R, 615 1206 size 600 -40 -20 20 40 60 80 100 120 140 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

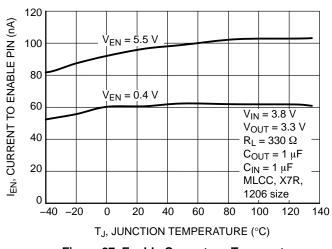

Figure 27. Enable Current vs. Temperature

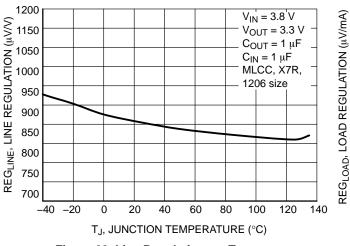

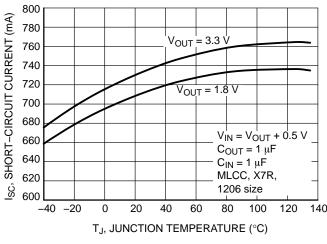

Figure 28. Current Limit vs. Temperature

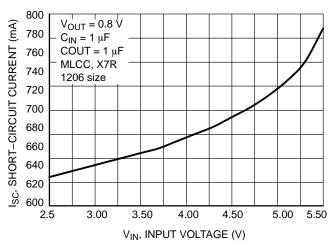

Figure 29. Short-Circuit vs. Temperature

Figure 30. Short-Circuit Current vs.

Temperature

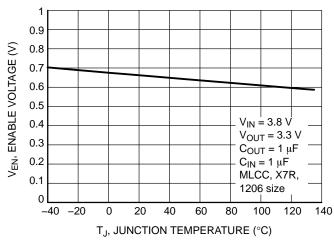

Figure 31. Enable Threshold (High)

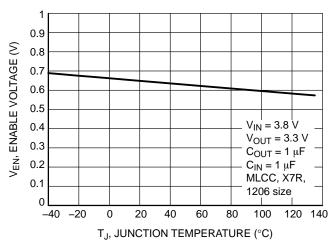

Figure 32. Enable Threshold (Low)

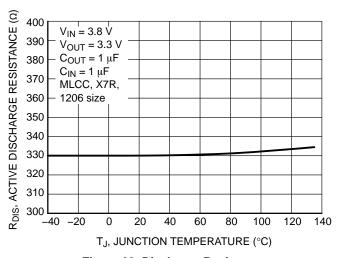

Figure 33. Discharge Resistance vs. Temperature

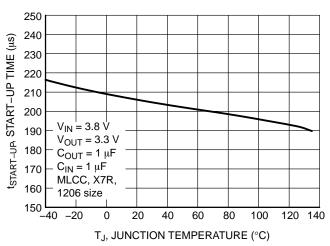

Figure 34. Start-up Time vs. Temperature

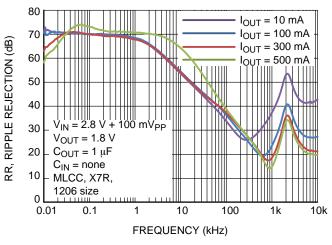

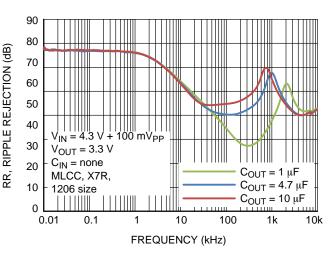

Figure 35. Power Supply Rejection Ratio, V<sub>OUT</sub> = 1.8 V

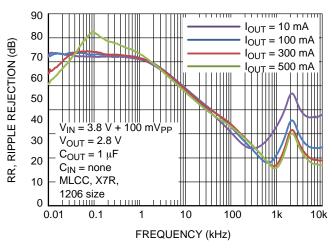

Figure 36. Power Supply Rejection Ratio, V<sub>OUT</sub> = 2.8 V

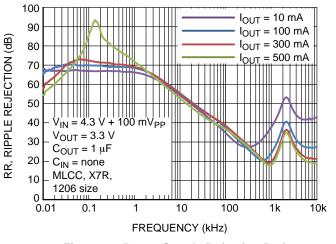

Figure 37. Power Supply Rejection Ratio, V<sub>OUT</sub> = 3.3 V

Figure 38. Power Supply Rejection Ratio, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 10 mA - Different C<sub>OUT</sub>

# **TYPICAL CHARACTERISTICS**

70

60

50

40

30 V<sub>IN</sub> = 4.3 V + 100 mV<sub>PP</sub> V<sub>OUT</sub> = 3.3 V V<sub>IN</sub> = 225k, R<sub>2</sub> = 82k I<sub>LOAD</sub> = 10 mA C<sub>OUT</sub> = 1 μF MLCC, X7R, 1206 size 0.01 0.1 1 10 100 FREQUENCY (kHz)

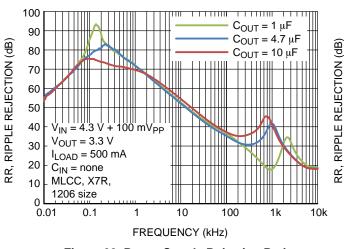

Figure 39. Power Supply Rejection Ratio,  $V_{OUT} = 3.3 \text{ V}$ ,  $I_{OUT} = 500 \text{ mA} - \text{Different C}_{OUT}$

Figure 40. Power Supply Rejection Ratio, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 10 mA – Different C1

$C_1 = none$

$C_1 = 1 \text{ nF}$

$C_1 = 10 \text{ nF}$

$C_1 = 100 \text{ nF}$

1k

10k

$C_1 = 100 pF$

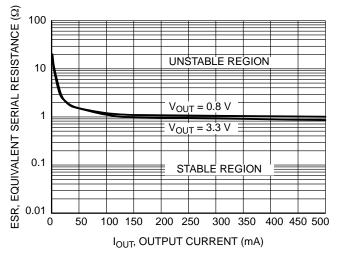

Figure 41. Output Capacitor ESR vs. Output Current

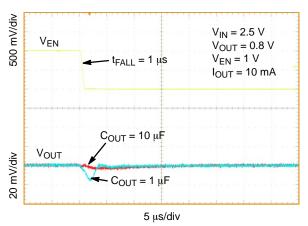

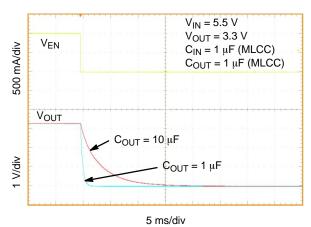

Figure 42. Enable Turn-on Response,  $C_{OUT} = 1 \; \mu F, \; I_{OUT} = 10 \; mA$

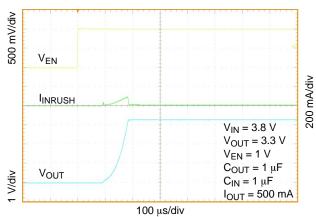

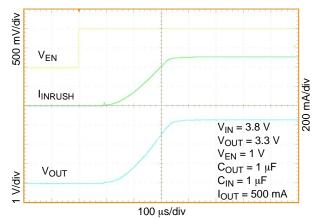

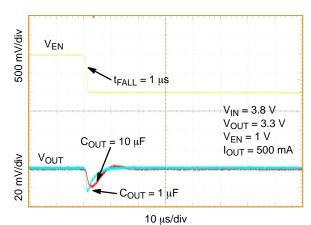

Figure 43. Enable Turn-on Response,  $C_{OUT} = 1 \mu F$ ,  $I_{OUT} = 500 \text{ mA}$

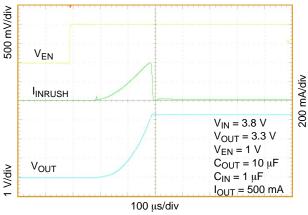

Figure 44. Enable Turn-on Response,  $C_{OUT}$  = 10  $\mu$ F,  $I_{OUT}$  = 10 mA

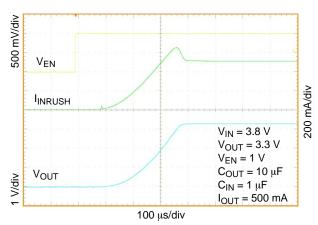

Figure 45. Enable Turn-on Response,  $C_{OUT} = 10 \ \mu F, I_{OUT} = 500 \ mA$

Figure 46. Line Transient Response – Rising Edge, V<sub>OUT</sub> = 0.8 V, I<sub>OUT</sub> = 10 mA

Figure 47. Line Transient Response – Falling Edge, V<sub>OUT</sub> = 0.8 V, I<sub>OUT</sub> = 10 mA

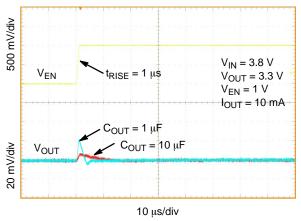

Figure 48. Line Transient Response – Rising Edge, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 10 mA

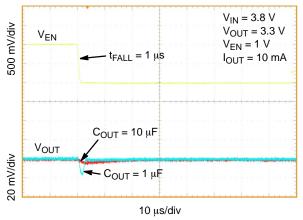

Figure 49. Line Transient Response – Falling Edge, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 10 mA

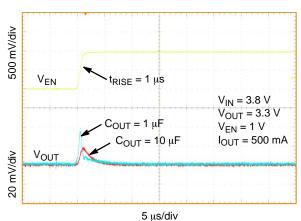

Figure 50. Line Transient Response – Rising Edge, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 500 mA

Figure 51. Line Transient Response – Falling Edge, V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 500 mA

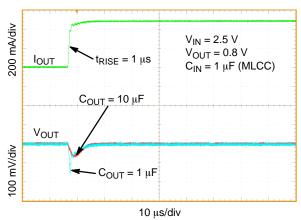

Figure 52. Load Transient Response – Rising Edge,  $V_{OUT}$  = 0.8 V,  $I_{OUT}$  = 1 mA to 500 mA,  $C_{OUT}$  = 1  $\mu$ F, 10  $\mu$ F

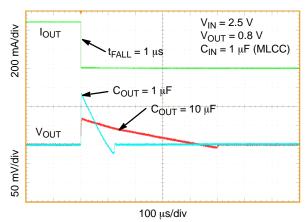

Figure 53. Load Transient Response – Falling Edge,  $V_{OUT}$  = 0.8 V,  $I_{OUT}$  = 1 mA to 500 mA,  $C_{OUT}$  = 1  $\mu$ F, 10  $\mu$ F

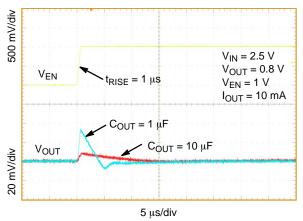

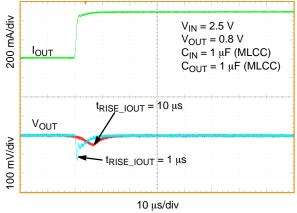

Figure 54. Load Transient Response – Rising Edge,  $V_{OUT}$  = 0.8 V,  $I_{OUT}$  = 1 mA to 500 mA,  $t_{RISE\ IOUT}$  = 1  $\mu$ s, 10  $\mu$ s

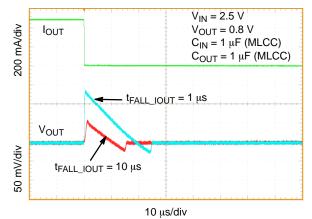

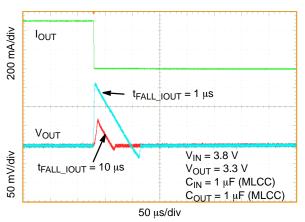

Figure 55. Load Transient Response – Falling Edge,  $V_{OUT}$  = 0.8 V,  $I_{OUT}$  = 1 mA to 500 mA,  $t_{FALL\ IOUT}$  = 1  $\mu$ s, 10  $\mu$ s

Figure 56. Load Transient Response – Rising Edge,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 1 mA to 500 mA,  $C_{OUT}$  = 1  $\mu$ F, 10  $\mu$ F

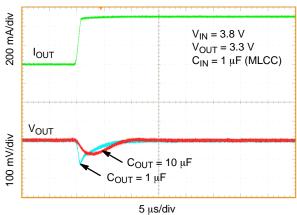

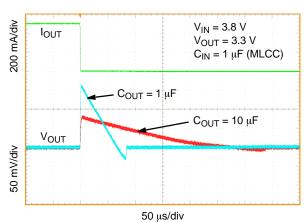

Figure 57. Load Transient Response – Falling Edge,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 1 mA to 500 mA,  $C_{OUT}$  = 1  $\mu$ F, 10  $\mu$ F

Figure 58. Load Transient Response – Rising Edge,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 1 mA to 500 mA,  $t_{RISE\ IOUT}$  = 1  $\mu$ s, 10  $\mu$ s

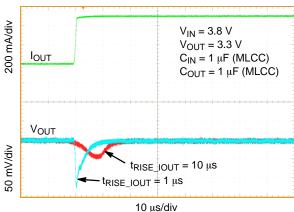

Figure 59. Load Transient Response – Falling Edge,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 1 mA to 500 mA,  $t_{FALL\ IOUT}$  = 1  $\mu$ s, 10  $\mu$ s

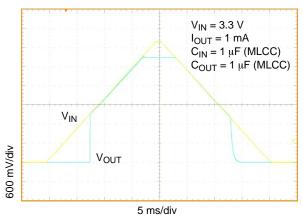

Figure 60. Turn-on/off, Slow Rising VIN

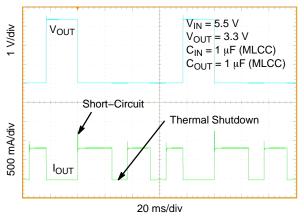

Figure 61. Short-Circuit and Thermal Shutdown

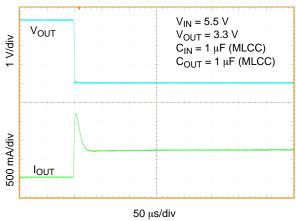

Figure 62. Short-Circuit Current Peak

Figure 63. Enable Turn-off

# **APPLICATIONS INFORMATION**

## General

The NCP705 is a high performance 500 mA Low Dropout Linear Regulator. This device delivers excellent noise and dynamic performance. Thanks to its adaptive ground current feature the device consumes only 13 µA of quiescent current at no-load condition. The regulator features ultra-low noise of 12 µVRMS, PSRR of 71 dB at 1 kHz and very good load/line transient performance. Such excellent dynamic parameters and small package size make the device an ideal choice for powering the precision analog and noise sensitive circuitry in portable applications. The LDO achieves this ultra low noise level output without the need for a noise bypass capacitor. A logic EN input provides ON/OFF control of the output voltage. When the EN is low the device consumes as low as typ. 10 nA from the IN pin. The device is fully protected in case of output overload, output short circuit condition and overheating, assuring a very robust design.

## Input Capacitor Selection (CIN)

It is recommended to connect a minimum of 1  $\mu F$  Ceramic X5R or X7R capacitor close to the IN pin of the device. This capacitor will provide a low impedance path for unwanted AC signals or noise modulated onto constant input voltage. There is no requirement for the min./max. ESR of the input capacitor but it is recommended to use ceramic capacitors for their low ESR and ESL. A good input capacitor will limit the influence of input trace inductance and source resistance during sudden load current changes. Larger input capacitor may be necessary if fast and large load transients are encountered in the application.

# **Output Decoupling (COUT)**

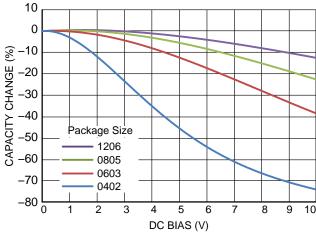

The NCP705 requires an output capacitor connected as close as possible to the output pin of the regulator. The minimal capacitor value is 1  $\mu F$  and X7R or X5R dielectric due to its low capacitance variations over the specified temperature range. The NCP705 is designed to remain stable with minimum effective capacitance of 1  $\mu F$  to account for changes with temperature, DC bias and package size. Especially for small package size capacitors such as 0402 the effective capacitance drops rapidly with the applied DC bias. Refer to the Figure 64, for the capacitance vs. package size and DC bias voltage dependence.

There is no requirement for the minimum value of Equivalent Series Resistance (ESR) for the  $C_{OUT}$  but the maximum value of ESR should be less than 900 m $\Omega$ . Larger output capacitors and lower ESR could improve the load transient response or high frequency PSRR as shown in typical characteristics. It is not recommended to use tantalum capacitors on the output due to their large ESR. The equivalent series resistance of tantalum capacitors is also strongly dependent on the temperature, increasing at low

temperature. The tantalum capacitors are generally more costly than ceramic capacitors.

Figure 64. Capacitance Change vs. DC Bias

# No-load Operation

The regulator remains stable and regulates the output voltage properly within the  $\pm 2\%$  tolerance limits even with no external load applied to the output.

# **Adjustable Operation**

The output voltage range can be set from 0.8 V to  $5.5~V-V_{DO}$  by resistor divider network. Use Equations 1 and 2 to calculate appropriate values of resistors and output voltage. Typical current to ADJ pin is 1 nA. For output voltage 0.8 V ADJ pin can be tied directly to Vout pin.

$$V_{OUT} = 0.8 \cdot \left(1 + \frac{R_1}{R_2}\right) + R_1 \cdot I_{ADJ}$$

(eq. 1)

$$R_2 \cong R_1 \cdot \frac{1}{\frac{V_{OUT}}{0.8} - 1}$$

(eq. 2)

The resistor divider should be designed carefully to achieve the best performance. Recommended current through divider is 10  $\mu A$  and more. Too high values of resistors  $(M\Omega)$  cause increasing noise and longer start–up time. The suggested values of the resistors are in Table 5. To improve dynamic performance capacitor C1 should be at least 1 nF. Recommended range of capacity is between 10 nF and 100 nF. Higher value of capacitor C1 increasing start–up time.

Table 5. Proposal Resistor Values for Variuos Vout

| V <sub>OUT</sub> | R1   | R2   |

|------------------|------|------|

| 1.5 V            | 130k | 150k |

| 3.3 V            | 256k | 82k  |

| 5.0 V            | 430k | 82k  |

Figure 65. NCP705 Adjustable with Noise Improvement Capacitor

# **Enable Operation**

The NCP705 uses the EN pin to enable/disable its device and to deactivate/activate the active discharge function.

If the EN pin voltage >0.9 V the device is guaranteed to be enabled. The NCP705 regulates the output voltage and the active discharge transistor is turned—off.

The EN pin has internal pull-down current source with typ. value of 110 nA which assures that the device is turned-off when the EN pin is not connected. Build in 2 mV hysteresis into the EN prevents from periodic on/off oscillations that can occur due to noise.

In the case where the EN function isn't required the EN should be tied directly to IN.

## **Undervoltage Lockout**

The internal UVLO circuitry assures that the device becomes disabled when the  $V_{IN}$  falls below typ. 1.5 V. When the  $V_{IN}$  voltage ramps—up the NCP705 becomes enabled, if  $V_{IN}$  rises above typ. 1.6 V. The 100 mV hysteresis prevents from on/off oscillations that can occur due to noise on  $V_{IN}$  line.

## **Output Current Limit**

Output Current is internally limited within the IC to a typical 750 mA. The NCP705 will source this amount of current measured with a voltage drops on the 90% of the nominal  $V_{OUT}$ . If the Output Voltage is directly shorted to ground ( $V_{OUT}=0$  V), the short circuit protection will limit the output current to 800 mA (typ). The current limit and short circuit protection will work properly up to

$V_{\rm IN} = 5.5$  V at  $T_{\rm A} = 125^{\circ}{\rm C}$ . There is no limitation for the short circuit duration.

## Internal Soft-Start Circuit

NCP705 contains an internal soft-start circuitry to protect against large inrush currents which could otherwise flow during the start-up of the regulator. Soft-start feature protects against power bus disturbances and assures a controlled and monotonic rise of the output voltage.

## Thermal Shutdown

When the die temperature exceeds the Thermal Shutdown threshold ( $T_{SD}-160^{\circ}\text{C}$  typical), Thermal Shutdown event is detected and the device is disabled. The IC will remain in this state until the die temperature decreases below the Thermal Shutdown Reset threshold ( $T_{SDU}-140^{\circ}\text{C}$  typical). Once the IC temperature falls below the  $140^{\circ}\text{C}$  the LDO is enabled again. The thermal shutdown feature provides the protection from a catastrophic device failure due to accidental overheating. This protection is not intended to be used as a substitute for proper heat sinking. For reliable operation junction temperature should be limited to  $+125^{\circ}\text{C}$  maximum.

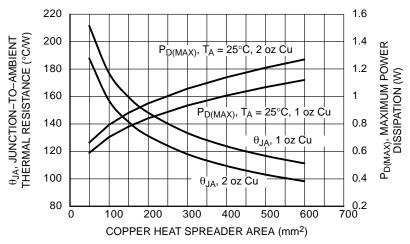

## **Power Dissipation**

As power dissipated in the NCP705 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part.

The maximum power dissipation the NCP705 can handle is given by:

$$P_{D(MAX)} = \frac{\left[ + 125^{\circ}C - T_{A} \right]}{\theta_{JA}}$$

(eq. 3)

The power dissipated by the NCP705 for given application conditions can be calculated from the following equations:

$$P_{D} \approx V_{IN} (I_{GND}@I_{OUT}) + I_{OUT} (V_{IN} - V_{OUT})$$

(eq. 4)

Figure 66.  $\theta_{JA}$  and  $P_{D(MAX)}$  vs. Copper Area (WDFN6)

## **Reverse Current**

The PMOS pass transistor has an inherent body diode which will be forward biased in the case that  $V_{OUT} > V_{IN}$ . Due to this fact in cases, where the extended reverse current condition can be anticipated the device may require additional external protection.

## **Load Regulation**

The NCP705 features very good load regulation of maximum 2 mV in 0 mA to 500 mA range. In order to achieve this very good load regulation a special attention to PCB design is necessary. The trace resistance from the OUT pin to the point of load can easily approach 100 m $\Omega$  which will cause 50 mV voltage drop at full load current, deteriorating the excellent load regulation.

# Line Regulation

The IC features very good line regulation of 0.75 mV/V measured from  $V_{IN} = V_{OUT} + 0.5$  V to 5.5 V. For battery operated applications it may be important that the line regulation from  $V_{IN} = V_{OUT} + 0.5$  V up to 4.5 V is only 0.55 mV/V.

# **Power Supply Rejection Ratio**

The NCP705 features very good Power Supply Rejection ratio. If desired the PSRR at higher frequencies in the range

100 kHz - 10 MHz can be tuned by the selection of  $C_{OUT}$  capacitor and proper PCB layout.

## **Output Noise**

The IC is designed for ultra-low noise output voltage without external noise filter capacitor ( $C_{nr}$ ). Figures 3-6 shows NCP705 noise performance. Generally the noise performance in the indicated frequency range improves with increasing output current.

## Turn-On Time

The turn—on time is defined as the time period from EN assertion to the point in which  $V_{OUT}$  will reach 98% of its nominal value. This time is dependent on various application conditions such as  $V_{OUT(NOM)}$ ,  $C_{OUT}$ ,  $T_A$ .

## **PCB Layout Recommendations**

To obtain good transient performance and good regulation characteristics place  $C_{IN}$  and  $C_{OUT}$  capacitors close to the device pins and make the PCB traces wide. In order to minimize the solution size, use 0402 capacitors. Larger copper area connected to the pins will also improve the device thermal resistance. The actual power dissipation can be calculated from the equation above (Equation 4).

# **ORDERING INFORMATION**

| Device         | Voltage Option | Marking | Package            | Shipping <sup>†</sup> |  |

|----------------|----------------|---------|--------------------|-----------------------|--|

| NCP705MT09TCG  | 0.9 V          | 5G      |                    |                       |  |

| NCP705MT18TCG  | 1.8 V          | 5A      |                    |                       |  |

| NCP705MT28TCG  | 2.8 V          | 5C      |                    | 3000 / Tape & Reel    |  |

| NCP705MT30TCG  | 3.0 V          | 5D      | WDFN6<br>(Pb-Free) |                       |  |

| NCP705MT33TCG  | 3.3 V          | 5E      | ( ' ,              |                       |  |

| NCP705EMT33TCG | 3.3 V          | 3A      |                    |                       |  |

| NCP705MTADJTCG | Adjustable     | 5J      |                    |                       |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

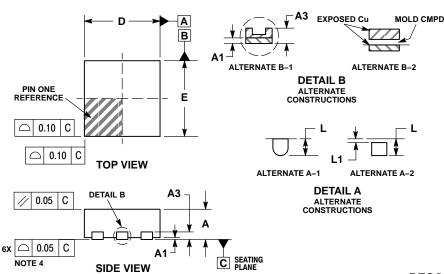

# PACKAGE DIMENSIONS

## WDFN6 2x2, 0.65P

CASE 511BR **ISSUE B**

0.10 M C A

0.05 M C NOTE 3

#### NOTES

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25 mm FROM THE TERMINAL TIP.

- THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

FOR DEVICES CONTAINING WETTABLE FLANK OPTION, DETAIL A ALTERNATE CONSTRUCTION A-2 AND DETAIL B ALTERNATE CONSTRUCTION

A-2 AND DETAIL B ALTERNATE CONSTRUCTION B-2 ARE NOT APPLICABLE.

|     | MILLIMETERS |      |

|-----|-------------|------|

| DIM | MIN         | MAX  |

| Α   | 0.70        | 0.80 |

| A1  | 0.00        | 0.05 |

| A3  | 0.20 REF    |      |

| b   | 0.25        | 0.35 |

| D   | 2.00 BSC    |      |

| D2  | 1.50        | 1.70 |

| E   | 2.00 BSC    |      |

| E2  | 0.90        | 1.10 |

| е   | 0.65 BSC    |      |

| L   | 0.20        | 0.40 |

| L1  |             | 0.15 |

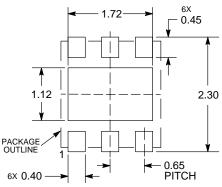

# RECOMMENDED **MOUNTING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Bluetooth is a registered trademark fo Bluetooth SIG. ZigBee is a registered trademark of ZigBee Alliance.

D2

**BOTTOM VIEW**

DETAIL A

е

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

# LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

NCP705MT33TCG NCP705MTADJTCG