**Programmers and Debuggers**

# Atmel

### SAM-ICE

#### **USER GUIDE**

### Introduction

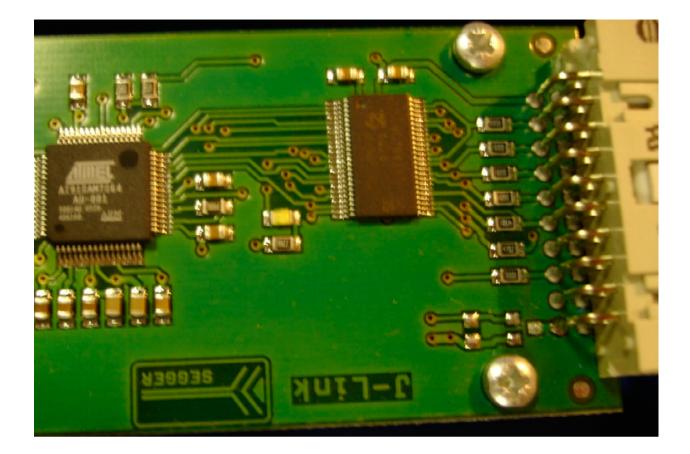

SAM-ICE is a JTAG emulator designed for Atmel<sup>®</sup> AT91 ARM<sup>®</sup> cores. It connects via USB to a PC running Microsoft<sup>®</sup> Windows<sup>®</sup> 2000 or higher. SAM-ICE<sup>™</sup> has a built-in 20-pin JTAG connector, which is compatible with the standard 20-pin connector defined by ARM.

### **Table of Contents**

| Int | roduc         | tion                                                                                   | .1  |  |  |

|-----|---------------|----------------------------------------------------------------------------------------|-----|--|--|

| 1.  | Ove           | rview                                                                                  | .4  |  |  |

|     | 1.1.          | Features of SAM-ICE                                                                    | . 4 |  |  |

|     | 1.2.          | Specification                                                                          | .4  |  |  |

|     | 1.3.          | Requirements                                                                           |     |  |  |

|     |               | 1.3.1. Host System                                                                     | . 5 |  |  |

|     |               | 1.3.2. Target System                                                                   | .5  |  |  |

| 2.  | Harc          | lware                                                                                  | 6   |  |  |

| ۷.  | 2.1.          | JTAG Interface                                                                         |     |  |  |

|     | 2.1.          |                                                                                        |     |  |  |

|     |               | <ul><li>2.1.1. JTAG Pinout</li><li>2.1.2. Multiple Devices in the Scan Chain</li></ul> |     |  |  |

|     | 2.2           | SWD Interface                                                                          |     |  |  |

|     | 2.2.          | 2.2.1. SWD Pinout                                                                      |     |  |  |

|     |               | 2.2.1. SWD + mout                                                                      |     |  |  |

|     |               |                                                                                        |     |  |  |

| 3.  | Mult          | i-core Debugging                                                                       | 11  |  |  |

|     | 3.1.          | How Multi-core Debugging Works                                                         | 11  |  |  |

| 4.  | Setu          | ıp 1                                                                                   | 4   |  |  |

|     | 4.1.          | Installing the USB Driver                                                              | 14  |  |  |

|     |               | 4.1.1. Verifying Correct Driver Installation                                           |     |  |  |

|     | 4.2.          | Debug Installation                                                                     |     |  |  |

|     | 4.3.          | Connecting the Target System                                                           | 18  |  |  |

|     |               | 4.3.1. Power-on Sequence                                                               | 18  |  |  |

|     |               | 4.3.2. Verifying Target Device Connection                                              | 18  |  |  |

|     |               | 4.3.3. Problems                                                                        | 18  |  |  |

| 5.  | SAM           | I-ICE Related Software1                                                                | 9   |  |  |

|     | 5.1.          | Overview                                                                               | 19  |  |  |

|     | 5.2.          | Free Software                                                                          |     |  |  |

|     | 0             | 5.2.1. JLink.exe (Command Line Tool)                                                   |     |  |  |

|     |               | 5.2.2. SAM-ICE TCP/IP Server (Remote SAM-ICE Use)                                      |     |  |  |

|     |               | 5.2.3. J-Mem Memory Viewer                                                             |     |  |  |

| 6.  | Freq          | uently Asked Questions                                                                 | 21  |  |  |

|     |               |                                                                                        |     |  |  |

| 1.  |               | port                                                                                   |     |  |  |

|     | 7.1.          | Troubleshooting                                                                        |     |  |  |

|     |               | 7.1.1. General Procedure                                                               |     |  |  |

|     | 7.0           | 7.1.2. Typical Problem Scenarios                                                       |     |  |  |

|     | 7.2.          | Contacting Support                                                                     | 23  |  |  |

| 8.  | 3. Glossary24 |                                                                                        |     |  |  |

|     | 8.1.  | Terminology                       | . 24 |

|-----|-------|-----------------------------------|------|

| 9.  | Errat | a                                 | 27   |

|     | 9.1.  | Reset Problem on the SAM-ICE V5.1 | . 27 |

| 10. | Revi  | sion History                      | .29  |

### 1. Overview

#### 1.1. Features of SAM-ICE

- Any Atmel AT91 core supported, including ARM<sup>®</sup> Thumb<sup>®</sup> mode

- Seamless integration into IAR Embedded Workbench<sup>®</sup>

- No power supply required, powered through USB

- Maximum JTAG speed 12MHz

- Auto speed recognition

- All JTAG signals can be monitored

- Support for multiple devices

- Fully plug and play compatible

- Standard 20-pin JTAG connector

- Wide target voltage range: 1.2V to 3.3V

- USB and 20-pin ribbon cable included

- Memory viewer (J-Mem) included

- SAM-ICE TCP/IP server included, can use SAM-ICE via TCP/IP networks

- RDI server available, can use SAM-ICE with RDI compliant software

- Support for adaptive clocking

#### 1.2. Specification

#### Table 1-1. SAM-ICE Specification

| Parameter                                       | Value                            |

|-------------------------------------------------|----------------------------------|

| Power supply                                    | USB powered <50mA                |

| USB Interface                                   | USB 2.0, full speed              |

| Target interface                                | JTAG 20-pin                      |

| Serial transfer rate between SAM-ICE and target | Up to 12MHz                      |

| Supported Target Voltage                        | 1.2V to 3.3V                     |

| Operating Temperature                           | +5°C to +60°C                    |

| Storage Temperature                             | -20°C to +65°C                   |

| Relative Humidity (non-condensing)              | <90% rH                          |

| Size (without cables)                           | 100mm x 53mm x 27mm              |

| Weight (without cables)                         | 70g                              |

| Electromagnetic Compatibility (EMC)             | EN 55022, EN 55024               |

| Supported OS                                    | Microsoft Windows 2000 and newer |

### 1.3. Requirements

#### 1.3.1. Host System

In order to use SAM-ICE, a host system running Windows 2000 or newer with the SAM-ICE custom USB driver is required.

#### 1.3.2. Target System

An Atmel AT91 target system is required.

### 2. Hardware

#### 2.1. JTAG Interface

By default, only one device is assumed to be in the JTAG scan chain. If you have multiple devices in the scan chain, you must properly configure it. To do so, you have to specify the exact position of the CPU that should be addressed. Configuration of the scan is done by the target application. A target application can be a debugger such as Atmel Studio, the IAR<sup>™</sup> C-SPY<sup>®</sup> debugger, ARM's AXD using RDI, a flash programming application such as SEGGER's J-Flash, or any other application using J-Link/J-Trace. It is the application's responsibility to supply a way to configure the scan chain. Most applications offer a dialog box for this purpose.

#### 2.1.1. JTAG Pinout

SAM-ICE has a JTAG connector compatible to ARM's Multi-ICE. The JTAG connector is a 20-way Insulation Displacement Connector (IDC) keyed box header (2.54mm male) that mates with IDC sockets mounted on a ribbon cable.

#### Figure 2-1. JTAG Pinout

| VTref     | 1   | •     | 2    | NC   |

|-----------|-----|-------|------|------|

| nTRST     | 3   | ullet | • 4  | GND  |

| TDI       | 5   | ullet | 6    | GND  |

| TMS       | 7   | •     | 8    | GND  |

| тск 🗌     | 9   | ٠     | 10   | GND  |

| RTCK      | _11 | ullet | 12   | GND  |

| TDO       | 13  | •     | • 14 | GND* |

| RESET     | 15  | •     | 16   | GND* |

| DBGRQ     | 17  | •     | 18   | GND* |

| 5V-Supply | 19  | •     | 20   | GND* |

|           |     |       |      |      |

The table below lists the SAM-ICE JTAG pinouts.

#### Table 2-1. JTAG Pinout

| Pin | Signal  | Туре  | Description                                                                                                                                                                                                                                                        |

|-----|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VTref   | Input | This is the target reference voltage.                                                                                                                                                                                                                              |

|     |         |       | It is used to check if the target has power, to create the logic-<br>level reference for the input comparators and controls the output<br>logic levels to the target. It is normally fed from $V_{DD}$ on the target<br>board and must not have a series resistor. |

| 2   | Vsupply | NC    | This pin is not connected in SAM-ICE. It is reserved for compatibility with other equipment. Connect to $V_{DD}$ or leave open in target system.                                                                                                                   |

# Atmel

| Pin | Signal | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | nTRST  | Output | JTAG Reset. Output from SAM-ICE to the Reset signal on the target JTAG port. Typically connected to nTRST on the target CPU. This pin is normally pulled HIGH on the target to avoid unintentional resets when there is no connection.                                                                                                                                                                                        |

| 4   | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | TDI    | Output | JTAG data input of the target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TDI on target CPU.                                                                                                                                                                                                                                                                |

| 6   | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7   | TMS    | Output | JTAG mode set input of target CPU. This pin should be pulled<br>up on the target. Typically connected to TMS on target CPU.                                                                                                                                                                                                                                                                                                   |

| 8   | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | ТСК    | Output | JTAG clock signal to target CPU. It is recommended that this pin<br>is pulled to a defined state on the target board. Typically<br>connected to TCK on target CPU.                                                                                                                                                                                                                                                            |

| 10  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11  | RTCK   | NC     | Input Return test clock signal from the target. Some targets must<br>synchronize the JTAG inputs to internal clocks. To assist in<br>meeting this requirement, a returned and re-timed TCK can be<br>used to dynamically control the TCK rate. SAM-ICE supports<br>adaptive clocking, which waits for TCK changes to be echoed<br>correctly before making further changes. Connect to RTCK if<br>available, otherwise to GND. |

| 12  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13  | TDO    | Input  | JTAG data output from target CPU. Typically connected to TDO on target CPU.                                                                                                                                                                                                                                                                                                                                                   |

| 14  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15  | RESET  | I/O    | Target CPU reset signal                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17  | -      | NC     | This pin is not connected in SAM-ICE                                                                                                                                                                                                                                                                                                                                                                                          |

| 18  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19  | -      | NC     | This pin is not connected in SAM-ICE                                                                                                                                                                                                                                                                                                                                                                                          |

| 20  | GND    | -      | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 2.1.2. Multiple Devices in the Scan Chain

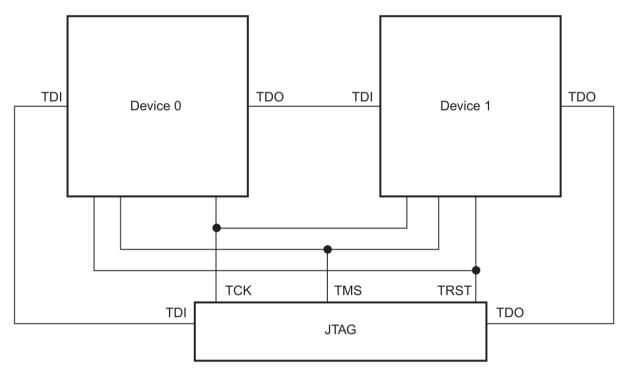

SAM-ICE can handle multiple devices in the scan chain. This applies to hardware where multiple chips are connected to the same JTAG connector. As can be seen in the following figure, the TCK and TMS lines of all JTAG device are connected, while the TDI and TDO lines form a bus.

Currently, up to eight devices in the scan chain are supported. One or more of these devices can be CPU cores; the other devices can be of any other type, but need to comply with the JTAG standard.

#### 2.2. SWD Interface

The SAM-ICE support ARM's Serial Wire Debug (SWD). SWD replaces the 5-pin JTAG port with a clock (SWDCLK) and a single bi-directional data pin (SWDIO), providing all the normal JTAG debug and test functionality. SWDIO and SWCLK are overlaid on the TMS and TCK pins. In order to communicate with a SWD device, J-Link sends out data on SWDIO, synchronous to the SWCLK. With every rising edge of SWCLK, one bit of data is transmitted or received on the SWDIO.

#### 2.2.1. SWD Pinout

The SAM-ICE JTAG connector is also compatible to ARM's Serial Wire Debug (SWD).

Figure 2-2. SWD Pinout

|           |       |      | 1            |

|-----------|-------|------|--------------|

| VTref     | 1 •   | • 2  | NC           |

| Not used  | 3 •   | • 4  | GND          |

| Not used  | 5 •   | • 6  | GND          |

| SWDIO     | 7 •   | • 8  | GND          |

| SWCLK     | _ 9 ● | • 10 | GND          |

| Not used  | _11 ● | • 12 | GND          |

| SWO       | 13 •  | • 14 | GND*         |

| RESET     | 15 •  | • 16 | <b>GND</b> * |

| Not used  | 17 •  | • 18 | <b>GND</b> * |

| 5V-Supply | 19 •  | • 20 | <b>GND</b> * |

|           | 1     |      |              |

The table below lists the SAM-ICE SWD pinout.

#### Table 2-2. SWD Pinout

| Pin | Signal | Туре             | Description                                                                                                                                                                                                                                                        |

|-----|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VTref  | Input            | This is the target reference voltage.                                                                                                                                                                                                                              |

|     |        |                  | It is used to check if the target has power, to create the logic-<br>level reference for the input comparators and controls the output<br>logic levels to the target. It is normally fed from $V_{DD}$ on the target<br>board and must not have a series resistor. |

| 2   |        | NC               | This pin is not connected                                                                                                                                                                                                                                          |

| 3   |        | NC               | This pin is not used. If the device may also be accessed via JTAG, this pin may be connected to nTRST, otherwise leave open.                                                                                                                                       |

| 4   | GND    |                  | Common ground                                                                                                                                                                                                                                                      |

| 5   |        | NC               | This pin is not used. If the device may also be accessed via JTAG, this pin may be connected to TDI, otherwise leave open.                                                                                                                                         |

| 6   | GND    |                  | Common ground                                                                                                                                                                                                                                                      |

| 7   | SWDIO  | Input/<br>Output | Single bi-directional data pin. A pull-up resistor is required. ARM recommends $100k\Omega$ .                                                                                                                                                                      |

| 8   | GND    |                  | Common ground                                                                                                                                                                                                                                                      |

| 9   | SWCLK  | Output           | Clock signal to target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TCK of target CPU.                                                                                                            |

**Atmel**

| Pin | Signal | Туре             | Description                                                                                                                                                           |

|-----|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | GND    |                  | Common ground                                                                                                                                                         |

| 11  |        | NC               | This pin is not used by the SAM-ICE when operating in SWD mode. If the device may also be accessed via JTAG, this pin may be connected to RTCK, otherwise leave open. |

| 12  | GND    |                  | Common ground                                                                                                                                                         |

| 13  | SWO    | Input            | Serial Wire Output trace port. (Optional, not required for SWD communication.)                                                                                        |

| 14  | GND    |                  | Common ground                                                                                                                                                         |

| 15  | RESET  | Input/<br>Output | Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called "nRST", "nRESET", or "RESET".                              |

| 16  | GND    |                  | Common ground                                                                                                                                                         |

| 17  |        | NC               | This pin is not connected in SAM-ICE                                                                                                                                  |

| 18  | GND    |                  | Common ground                                                                                                                                                         |

| 19  |        | NC               | This pin is not connected in SAM-ICE                                                                                                                                  |

| 20  | GND    |                  | Common ground                                                                                                                                                         |

#### 2.2.2. SWO

Serial Wire Output (SWO) support means support for a single pin output signal from the core. The Instrumentation Trace Macrocell (ITM) and Serial Wire Output (SWO) can be used to form a Serial Wire Viewer (SWV). The Serial Wire Viewer provides a low-cost method of obtaining information from inside the MCU.

Usually it should not be necessary to configure the SWO speed because this is usually done by the debugger.

### 3. Multi-core Debugging

SAM-ICE is able to debug multiple cores on one target system connected to the same scan chain.

#### 3.1. How Multi-core Debugging Works

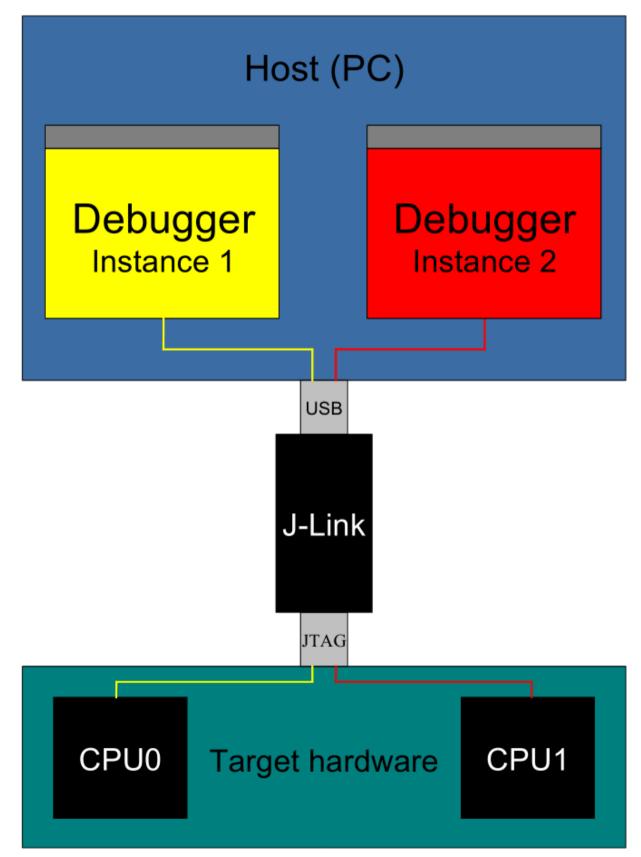

Multi-core debugging requires multiple debuggers or multiple instances of the same debugger. Two or more debuggers can use the same SAM-ICE simultaneously. Configuring a debugger to work with a core in a multi-core environment does not require special settings. All that is required is proper setup of the scan chain for each debugger. This enables SAM-ICE to debug more than one core on a target at the same time.

The following figure shows a host, debugging two CPU cores with two instances of the same debugger.

Both debuggers share the same physical connection. The core to debug is selected through the JTAG settings as described below.

### 4. Setup

#### 4.1. Installing the USB Driver

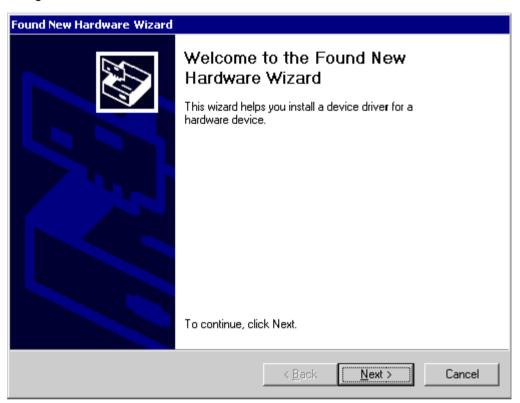

When your SAM-ICE is plugged into the computer's USB port, or when the computer is first powered on after connecting SAM-ICE, Windows<sup>®</sup> detects the new hardware.

The wizard starts the installation of the driver. First, select the "Search for a suitable driver for my device (recommended)" option, then click on the "Next >" button.

| Found New Hardware Wizard                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Install Hardware Device Drivers<br>A device driver is a software program that enables a hardware device to work with<br>an operating system.                                                    |  |  |  |  |  |

| This wizard will complete the installation for this device:                                                                                                                                     |  |  |  |  |  |

|                                                                                                                                                                                                 |  |  |  |  |  |

| A device driver is a software program that makes a hardware device work. Windows<br>needs driver files for your new device. To locate driver files and complete the<br>installation click Next. |  |  |  |  |  |

| What do you want the wizard to do?                                                                                                                                                              |  |  |  |  |  |

| Search for a suitable driver for my device (recommended)                                                                                                                                        |  |  |  |  |  |

| Display a list of the known drivers for this device so that I can choose a specific driver                                                                                                      |  |  |  |  |  |

|                                                                                                                                                                                                 |  |  |  |  |  |

| < <u>B</u> ack <u>N</u> ext > Cancel                                                                                                                                                            |  |  |  |  |  |

In the next step, you need to select the "Specify a location" option, and click on the "Next >" button.

| Found New Hardware Wizard                                                                         |                                      |

|---------------------------------------------------------------------------------------------------|--------------------------------------|

| Locate Driver Files<br>Where do you want Windows to search for o                                  | driver files?                        |

| Search for driver files for the following hardw.                                                  | are device:                          |

| The wizard searches for suitable drivers in its<br>any of the following optional search locations |                                      |

| To start the search, click Next. If you are sea<br>insert the floppy disk or CD before clicking N |                                      |

| Optional search locations:<br>Floppy <u>disk</u> drives                                           |                                      |

| ☐ <u>C</u> D-ROM drives ✓ <u>Specify a location</u>                                               |                                      |

| Microsoft Windows Update                                                                          |                                      |

|                                                                                                   | < <u>B</u> ack <u>N</u> ext > Cancel |

Copy the driver available on the DVD-ROM to your location.

The wizard asks you to specify the location of the correct driver files for the new device. Use the directory navigator to select D:\tools\driver\usb\jlinkarm (or your chosen location) and confirm with a click on the "Next >" button.

| Files Needed |                                                                |                |  |  |  |

|--------------|----------------------------------------------------------------|----------------|--|--|--|

|              | The file 'ilink.sys' on J-Link Installation Disk is needed.    | ОК             |  |  |  |

| _            |                                                                | Cancel         |  |  |  |

|              | Type the path where the file is located, and then click<br>OK. |                |  |  |  |

|              | Copy files from:                                               |                |  |  |  |

|              | ver\usb\jlinkarm\jlinkarm.sys 💌                                | <u>B</u> rowse |  |  |  |

The wizard confirms your choice and starts to copy, when you click on the "OK" button.

At this point, the installation is complete. Click on the "Finish" button to dismiss the installation.

#### 4.1.1. Verifying Correct Driver Installation

To verify the correct installation of the driver, disconnect and reconnect SAM-ICE to the USB port. During the enumeration process, which takes about 2 seconds, the LED on SAM-ICE is flashing. After successful enumeration, the LED stays on permanently.

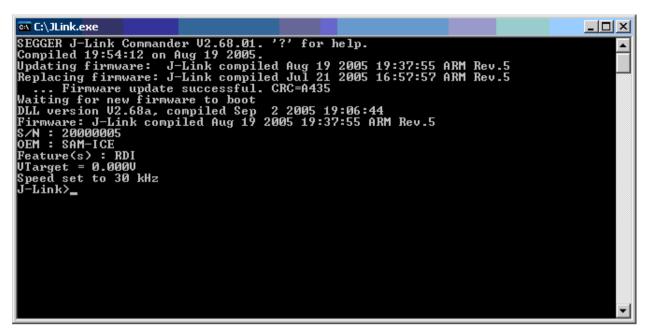

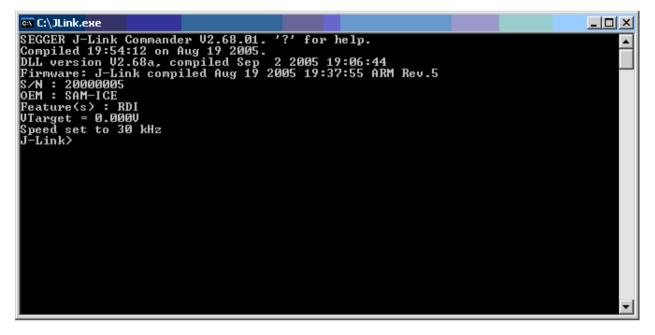

Start the provided sample application JLink.exe. JLink.exe should display the build date of the SAM-ICE firmware, the serial number, a target voltage of 0.000V if a target is not connected to SAM-ICE, and the speed selection. See the screen-shot below.

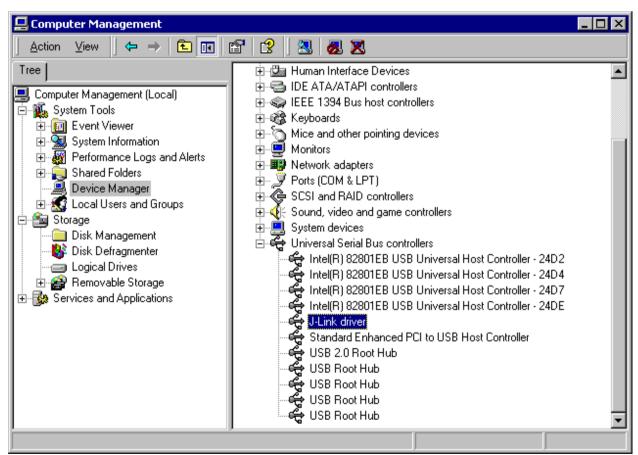

In addition to this you may verify the driver installation by consulting the Windows device manager. If the driver is installed and your SAM-ICE is connected to your computer, the device manager should list the J-Link driver as a node below "Universal Serial Bus controllers", as shown in the following screen-shot:

A right-click on the driver opens a context menu, which contains the item "Properties". If you select this item, a new dialog is opened and should report: "This device is working properly".

#### 4.2. Debug Installation

The SAM-ICE RDI software is an RDI interface for SAM-ICE. It makes it possible to use SAM-ICE with any RDI compliant debugger.

The main part of the software is an RDI compliant DLL, which needs to be selected in the debugger.

Supported configurations are described on the AT91 DVD-ROM. For additional information on debug, refer to the SAM-ICE "Getting started" bar menu.

#### 4.3. Connecting the Target System

#### 4.3.1. Power-on Sequence

SAM-ICE must be powered on before connecting it to the target device. First, connect SAM-ICE to the host system via the USB and then connect SAM-ICE to the target device via JTAG. Power-on the device after you have connected SAM-ICE to it.

#### 4.3.2. Verifying Target Device Connection

If the USB driver is working properly and your SAM-ICE is connected to the host system, you may connect SAM-ICE to your target hardware. Then start JLink.exe again; it should now display the same SAM-ICE related information as above. In addition, it should report that it found a JTAG target and the target core ID. The screen-shot below shows the output of JLink.exe. As can be seen, it reports a SAMICE with one JTAG device connected.

#### 4.3.3. Problems

For help with any of the steps described above, refer to Troubleshooting for troubleshooting tips.

### 5. SAM-ICE Related Software

#### 5.1. Overview

Table 5-1. Available Software Packages

| Software              | Description                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| JLink.exe             | Free Command line tool with basic functionality for target analysis.                                    |

| SAM-ICE TCP/IP Server | Free utility which provides the possibility to use SAM-ICE remotely via TCP/IP.                         |

| J-Mem memory viewer   | Free target memory viewer. Shows the memory content of a running target and allows editing as well.     |

| SAM-ICE ARM Flash DLL | An enhanced version of the JLinkARM.DLL, which contains additional API functions for Flash programming. |

| RDI support           | Provides Remote Debug Interface (RDI) support.                                                          |

#### 5.2. Free Software

Free software related to SAM-ICE ships with SAM-ICE and may also be downloaded from the web site: http://www.segger.com.

No additional license is required to use this software.

#### 5.2.1. JLink.exe (Command Line Tool)

JLink.exe is a tool, that can be used to verify proper installation of the USB driver and to verify the connection to the ARM chip, as well as for simple analysis of the target system. It permits some simple commands, such as memory dump, halt, step, go, and ID-check, as well as some more in-depths analysis of the state of the ARM core and the ICE breaker module.

#### 5.2.2. SAM-ICE TCP/IP Server (Remote SAM-ICE Use)

The SAM-ICE TCP/IP server allows using SAM-ICE remotely via TCP/IP. This enables you to connect to and fully use a SAM-ICE from another computer. Performance is just slightly (about 10%) lower than with direct USB connection.

| IPStat          | Not co | nnected          | 1 |      |    |

|-----------------|--------|------------------|---|------|----|

|                 | R      |                  | W | V    | VR |

| This connection |        |                  | 0 |      | 0  |

| Total           |        |                  | 0 |      | 0  |

| USBStat         | Not co | nnected          | 1 |      |    |

|                 | 🗖 Stay | y on <u>t</u> op |   | Abou | ut |

| Status          |        |                  |   |      |    |

#### 5.2.3. J-Mem Memory Viewer

J-Mem displays memory contents of ARM systems and allows modifications of RAM and SFRs (Special Function Registers) while the target is running. This makes it possible to look into the memory of an ARM chip at run-time; RAM can be modified and SFRs can be written. The type of access for both read and write access can be selected to be 8/16/32 bits. This is an efficient means for modifying SFRs, in particular because it writes the SFR only after the complete value has been entered.

| <u>File Target</u> | Optic | ons        | Help |           |            |            |        |            |    |    |    |    |    |    |    |    |               |

|--------------------|-------|------------|------|-----------|------------|------------|--------|------------|----|----|----|----|----|----|----|----|---------------|

| Address: 0x0       |       |            | ×1   | <u>×2</u> | × <u>4</u> | B          | efresk |            |    |    |    |    |    |    |    |    |               |

| Address            | 0     | 1          | 2    | 3         | 4          | 5          | 6      | 7          | 8  | 9  | A  | B  | С  | D  | E  | F  | ASCII         |

| 00000000           | 06    | 00         | 00   | EA        | FE         | FF         | FF     | EA         | FE | FF | FF | EA | FE | FF | FF | EA |               |

| 00000010           | FE    | FF         | FF   | EA        | FE         | FF         | FF     | EA         | 5C | 07 | 00 | EA | 7C | 07 | 00 | EA |               |

| 00000020           | 50    | DØ         | 9F   | E5        | 50         | 00         | 9F     | E5         | ØF | EØ | AØ | E1 | 10 | FF | 2F | E1 | PP/.          |

| 00000030           | 40    | 00         | 9F   | E5        | D1         | FØ         | 21     | E3         | 40 | 80 | 9F | E5 | D2 | FØ | 21 | E3 | et.et.        |

| 00000040           | 00    | DØ         | AØ   | E1        | 60         | 00         | 40     | E2         | 13 | FØ | 21 | E3 | 00 | DØ | AØ | E1 | `.et          |

| 00000050           | 2C    | 00         | 9F   | E5        | ØF         | EØ         | AØ     | E1         | 10 | FF | 2F | E1 | 24 | EØ | 9F | E5 |               |

| 00000060           | 24    | 00         | 9F   | E5        | 10         | FF         | 2F     | E1         | FE | FF | FF | EA | FE | FF | FF | EA | \$/           |

| 00000070           | FE    | FF         | FF   | EA        | FE         | FF         | FF     | EA         | 00 | 00 | 21 | 00 | 91 | 00 | 00 | 00 |               |

| 00000080           | 00    | FØ         | FF   | FF        | 25         | 01         | 00     | 00         | 68 | 00 | 00 | 00 | DD | 12 | 00 | 00 | ×h            |

| 00000090           | 00    | <b>B</b> 5 | 1A   | 48        | 9F         | 21         | C9     | 43         | 19 | 40 | ØA | 60 | 19 | 49 | 80 | 22 | H.t.C.J.`.I." |

| 000000A0           | 12    | 02         | ØA   | 60        | 18         | 49         | 01     | 62         | 81 | 6E | C9 | 07 | FC | D5 | 17 | 49 | `.I.b.nI      |

| 000000B0           | C1    | 62         | 81   | 6E        | 49         | 07         | FC     | D5         | 81 | 6E | 09 | 07 | FC | D5 | 04 | 21 | .b.nI!        |

| 00000000           | 01    | 63         | 81   | 6E        | 09         | 07         | FC     | D5         | 01 | 6B | 03 | 22 | ØA | 43 | 02 | 63 | .c.nk.".C.c   |

| 000000D0           | 81    | 6E         | 09   | 07        | FC         | D5         | ØE     | 48         | ØE | 49 | 01 | 60 | 01 | 20 | 05 | EØ | .nH.I.`       |

| 000000E0           | 04    | 21         | 41   | 43        | ØA         | <b>4</b> A | ØC     | <b>4</b> B | 53 | 50 | 40 | 10 | 1F | 28 | F7 | DB | .tAC.J.KSP@   |

| 000000F0           | ØA    | 48         | ØB   | 49        | 01         | 60         | 01     | BC         | 00 | 47 | CØ | 46 | 00 | FC | FF | FF | .H.I.`G.F     |

| 00000100           | 00    | 01         | 30   | 00        | 44         | FD         | FF     | FF         | 01 | 06 | 00 | 00 | 05 | 10 | 19 | 10 | 0.D           |

| 00000110           | 80    | FØ         | FF   | FF        | 6C         | 00         | 00     | 00         | 70 | 00 | 00 | 00 | 34 | F1 | FF | FF | 1p4           |

| 00000120           | 74    | 00         | 00   | 00        | 12         | <b>4</b> A | 13     | 48         | 70 | B4 | 81 | BØ | 11 | 10 | 12 | 1D | tJ.Hp         |

| 00000130           | ØA    | EØ         | ØB   | 68        | 54         | 68         | 15     | 68         | 00 | 2B | 03 | DØ | 5B | 1E | E6 | 5C | hTh.h.+[\     |

| 00000140           | EE    | 54         | FB   | D1        | ØC         | 31         | ØC     | 32         | 81 | 42 | ØC | D2 | 53 | 68 | 14 | 68 | .T1.2.BSh.h   |

### 6. Frequently Asked Questions

| Which CPUs are supported?                               | SAM-ICE supports all ARM based Atmel microcontrollers.                                                                                                                          |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What is the maximum JTAG speed<br>supported by SAM-ICE? | The maximum supported JTAG speed is 8MHz.                                                                                                                                       |

| Can I access individual ICE<br>registers via SAM-ICE?   | Yes, you can access all individual ICE registers via SAM-ICE.                                                                                                                   |

| Can SAM-ICE read back the status of the JTAG pins?      | Yes, the status of all pins can be read. This includes the outputs of SAM-ICE as well as the supply voltage and can be useful to detect hardware problems on the target system. |

| Does SAM-ICE support the embedded trace macro (ETM)?    | No. ETM requires another connection to the ARM chip and a CPU with built-in ETM.                                                                                                |

### 7. Support

#### 7.1. Troubleshooting

#### 7.1.1. General Procedure

If you experience problems with a SAM-ICE, follow the steps below to solve these problems:

- 1. Close all running applications on your host system.

- 2. Disconnect the SAM-ICE device from USB.

- 3. Power-off target.

- 4. Re-connect SAM-ICE to host system (attach USB cable).

- 5. Power-on target.

- 6. Try your target application again. If the problem disappears, you are done; otherwise, continue.

- 7. Close all applications running on your host system again.

- 8. Disconnect the SAM-ICE device from USB.

- 9. Power-off target.

- 10. Re-connect SAM-ICE to host system (attach USB cable).

- 11. Power-on target.

- 12. Start JLink.exe.

- 13. If JLink.exe reports the SAM-ICE serial number and the target processor's core ID, the SAM-ICE is working properly and cannot be the cause of your problem.

- 14. If JLink.exe is unable to read the target processor's core ID, you should analyze the communication between your target and SAM-ICE with a logic analyzer or oscilloscope.

- 15. If your problem persists and you own an original SAM-ICE (not an OEM version), see section Typical Problem Scenarios.

#### 7.1.2. Typical Problem Scenarios

#### 7.1.2.1. SAM-ICE LED is OFF

Meaning: The USB connection does not work.

CorrectiveCheck the USB connection. Try to re-initialize SAM-ICE by disconnecting andaction:reconnecting it. Make sure that the connectors are firmly attached. Check the cable<br/>connections on your SAM-ICE and the computer. If this does not solve the problem,<br/>check if your cable is defective. If the USB cable is OK, try a different PC.

#### 7.1.2.2. SAM-ICE LED is Flashing at a High Frequency

Meaning:

SAM-ICE cannot be enumerated by the USB controller.

Most likely

• Another program is already using SAM-ICE

- causes: The SAM-ICE USB driver does not work correctly

- **Corrective** Close all running applications and try to reinitialize SAM-ICE by disconnecting and reconnecting it

- If the LED blinks permanently, check the correct installation of the SAM-ICE USB driver. Deinstall and reinstall the driver as shown in chapter Setup.

#### 7.1.2.3. SAM-ICE does not get any Connection to the Target

Most likely causes:

- The JTAG cable is defective

- The target hardware is defective

Corrective action:

Follow the steps described in section General Procedure.

#### 7.2. Contacting Support

Before contacting support, assure that you have tried to solve your problem by following the steps outlined in section General Procedure. You may also try your SAM-ICE with another PC and, if possible, with another target system to see if it works there. If the device functions correctly, the USB setup on the original machine or your target hardware is the source of the problem, not SAM-ICE.

Make sure that you have the following information available for the support team:

- A detailed description of the problem

- SAM-ICE serial number

- Output of JLink.exe if available

- Your findings on the signal analysis

- Information about your target hardware (processor, board etc.)

## 8. Glossary

### 8.1. Terminology

| Adaptive clocking                | A technique in which a clock signal is sent out by Multi-ICE and waits for the returned clock before generating the next clock pulse. The technique allows the Multi-ICE interface unit to adapt to differing signal drive capabilities and differing cable lengths.                                                                        |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application Program<br>Interface | A specification of a set of procedures, functions, data structures, and constants that are used to interface two or more software components together.                                                                                                                                                                                      |

| Big-endian                       | Memory organization where the least significant byte of a word is at a higher address than the most significant byte. See Little-endian.                                                                                                                                                                                                    |

| Cache cleaning                   | The process of writing dirty data in a cache to main memory.                                                                                                                                                                                                                                                                                |

| Coprocessor                      | An additional processor that is used for certain operations, for example, for floating-point math calculations, signal processing, or memory management.                                                                                                                                                                                    |

| Dirty data                       | When referring to a processor data cache, data that has been written to the cache but has not been written to main memory. Only write-back caches can have dirty data, because a write-through cache writes data to the cache and to main memory simultaneously. The process of writing dirty data to main memory is called cache cleaning. |

| Dynamic Linked<br>Library (DLL)  | A collection of programs, any of which can be called when needed by an executing program. A small program that helps a larger program communicate with a device such as a printer or keyboard is often packaged as a DLL.                                                                                                                   |

| EmbeddedICE <sup>™</sup>         | The additional hardware provided by debug-able ARM processors to aid debugging.                                                                                                                                                                                                                                                             |

| Halfword                         | A 16-bit unit of information. Contents are taken as being an unsigned integer, unless otherwise stated.                                                                                                                                                                                                                                     |

| Host                             | A computer which provides data and other services to another computer.<br>Especially, a computer providing debugging services to a target being<br>debugged.                                                                                                                                                                                |

| lCache                           | Instruction cache.                                                                                                                                                                                                                                                                                                                          |

| ICE Extension Unit               | A hardware extension to the EmbeddedICE logic that provides more breakpoint units.                                                                                                                                                                                                                                                          |

| ID                               | Identifier.                                                                                                                                                                                                                                                                                                                                 |

| IEEE <sup>®</sup> 1149.1         | The IEEE Standard, which defines TAP. Commonly (but incorrectly) referred to as JTAG.                                                                                                                                                                                                                                                       |

| Image                            | An executable file that has been loaded onto a processor for execution.                                                                                                                                                                                                                                                                     |

| In-Circuit Emulator<br>(ICE)      | A device enabling access to and modification of the signals of a circuit while that circuit is operating.                                                                                                                                              |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Register              | When referring to a TAP controller, a register that controls the operation of the TAP.                                                                                                                                                                 |

| IR                                | See Instruction Register.                                                                                                                                                                                                                              |

| Joint Test Action<br>Group (JTAG) | The name of the standards group which created the IEEE 1149.1 specification.                                                                                                                                                                           |

| Little-endian                     | Memory organization where the least significant byte of a word is at a lower address than the most significant byte. See also Big-endian.                                                                                                              |

| Memory Management<br>Unit (MMU)   | Hardware that controls caches and access permissions to blocks of memory, and translates virtual to physical addresses.                                                                                                                                |

| Multi-ICE                         | Multi-processor EmbeddedICE interface.                                                                                                                                                                                                                 |

| nSRST                             | Abbreviation of System Reset. The electronic signal which causes the target system other than the TAP controller to be reset. This signal is known as nSYSRST in some other manuals. See also nTRST.                                                   |

| nTRST                             | Abbreviation of TAP Reset. The electronic signal that causes the target system TAP controller to be reset. This signal is known as nICERST in some other manuals. See also nSRST.                                                                      |

| Open collector                    | A signal that may be actively driven LOW by one or more drivers, and is otherwise passively pulled HIGH. Also known as a "wired-AND" signal.                                                                                                           |

| Processor Core                    | The part of a microprocessor that reads instructions from memory and executes them, including the instruction fetch unit, arithmetic and logic unit, and the register bank. It excludes optional coprocessors, caches, and the memory management unit. |

| Program Status<br>Register (PSR)  | Contains some information about the current program and some information about the current processor. Often, therefore, also referred to as Processor Status Register.                                                                                 |

|                                   | Is also referred to as Current PSR (CPSR), to emphasize the distinction between it and the Saved PSR (SPSR). The SPSR holds the value the PSR had when the current function was called, and which will be restored when control is returned.           |

| Remapping                         | Changing the address of physical memory or devices after the application has started executing. This is typically done to allow RAM to replace ROM once the initialization has been done.                                                              |

| Remote Debug<br>Interface (RDI)   | RDI is an open ARM standard procedural interface between a debugger and the debug agent. The widest possible adoption of this standard is encouraged.                                                                                                  |

| RTCK                              | Returned TCK. The signal which enables Adaptive Clocking.                                                                                                                                                                                              |

| RTOS                              | Real Time Operating System.                                                                                                                                                                                                                            |

| Scan Chain                           | A group of one or more registers from one or more TAP controllers connected between TDI and TDO, through which test data is shifted.                                                           |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Semihosting                          | A mechanism whereby the target communicates I/O requests made in the application code to the host system, rather than attempting to support the I/O itself.                                    |

| SWI                                  | Software Interrupt. An instruction that causes the processor to call a programer-specified subroutine. Used by ARM to handle semihosting.                                                      |

| TAP Controller                       | Logic on a device, which allows access to some or all of that device for test purposes. The circuit functionality is defined in IEEE1149.1.                                                    |

| Target                               | The actual processor (real silicon or simulated) on which the application program is running.                                                                                                  |

| тск                                  | The electronic clock signal, which times data on the TAP data lines TMS, TDI, and TDO.                                                                                                         |

| TDI                                  | The electronic signal input to a TAP controller from the data source (upstream). Usually this is seen connecting the Multi-ICE Interface Unit to the first TAP controller.                     |

| TDO                                  | The electronic signal output from a TAP controller to the data sink (downstream). Usually this is seen connecting the last TAP controller to the Multi-ICE Interface Unit.                     |

| Test Access Port<br>(TAP)            | The port used to access a device's TAP Controller. Comprises TCK, TMS, TDI, TDO, and nTRST (optional).                                                                                         |

| Transistor-Transistor<br>Logic (TTL) | A type of logic design in which two bipolar transistors drive the logic output to one or zero. LSI and VLSI logic often used TTL with HIGH logic level approaching +5V and LOW approaching 0V. |

| Watchpoint                           | A location within the image that will be monitored and cause execution to stop when it changes.                                                                                                |

| Word                                 | A 32-bit unit of information. Contents are taken as being an unsigned integer, unless otherwise stated.                                                                                        |

### 9. Errata

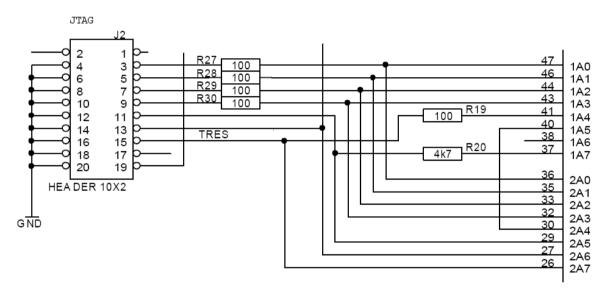

#### 9.1. Reset Problem on the SAM-ICE V5.1

In certain cases, the reset signal generated by the AT91 target may be inoperative due to the fact that the SAM-ICE reset output (JTAG connector pin 15) is a push-pull stage with a  $100\Omega$  serial resistor.

#### Workaround

- Replace R19 by a Schottky diode with the same resistor footprint (e.g. BAT54J)

- Remove the resistor

This problem has been resolved in SAM-ICE V5.2.

### 10. Revision History

| Doc. rev. | Date    | Comment                                                                                                                                                                                |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6206E     | 09/2016 | <ul> <li>Change FAQ entry 1: The SAM-ICE supports all ARM based Atmel<br/>microcrontrollers.</li> </ul>                                                                                |

| 6206D     | 09/2016 | <ul> <li>Overview, Windows 7 removed. Need only list Windows 2000 and newer.</li> <li>SWD Interface, added chapters on SWD.</li> <li>Change structure of hardware chapters.</li> </ul> |

| 6206C     | 04/2013 | <ul> <li>Overview, Windows 7 added.</li> <li>Features of SAM-ICE, Cortex-M3/Cortex-M4 added; JTAG speed 12MHz<br/>Back page updated. Removed ARM7/9 references.</li> </ul>             |

| 6206B     |         | <ul> <li>Features of SAM-ICE, Support for adaptive clocking added</li> <li>Table 2-1 pin 11, RTCK, Description rewritten.</li> </ul>                                                   |

| 6206A     |         | Initial document release.                                                                                                                                                              |

www.atmel.com

# Atmel Enabling Unlimited Possibilities®

Atmel Corporation

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

f 🔰 in 8 🖸 W

© 2016 Atmel Corporation. / Rev.: Atmel-6206E-SAM-ICE User Guide-09/2016

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM<sup>®</sup>, ARM Connected<sup>®</sup> logo and others are the registered trademarks or trademarks of ARM Ltd. Windows<sup>®</sup> is a registered trademark of Microsoft Corporation in U.S. and or other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as military-grade.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip: AT91SAM-ICE