# **Synchronous PWM Controller**

The NCP3011 is a PWM device designed to operate from a wide input range and is capable of producing an output voltage as low as 0.8 V. The NCP3011 provides integrated gate drivers and an internally set 400 kHz oscillator. The NCP3011 has an externally compensated transconductance error amplifier with an internally fixed soft–start. The NCP3011 incorporates output voltage monitoring with a Power Good pin to indicate that the system is in regulation. The dual function SYNC pin synchronizes the device to a higher frequency (Slave Mode) or outputs a 180° out–of–phase clock signal to drive another NCP3011 (Master Mode). Protection features include lossless current limit and short circuit protection, output overvoltage and undervoltage protection, and input undervoltage lockout. The NCP3011 is available in a 14–pin TSSOP package.

#### **Features**

- Input Voltage Range from 4.7 V to 28 V

- 400 kHz Operation

- 0.8 V ± 1.0% Reference Voltage

- Buffered External +1.25 V Reference

- Current Limit and Short Circuit Protection

- Power Good

- Enable/Disable Pin

- Input Undervoltage Lockout

- External Synchronization

- Output Overvoltage and Undervoltage Protection

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Controls

- This is a Pb-Free Device

### **Typical Applications**

- Set Top Box

- Power Modules

- ASIC / DSP Power Supply

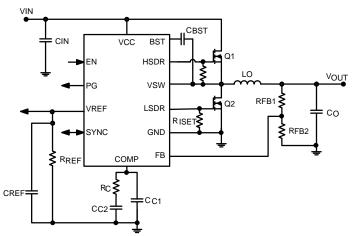

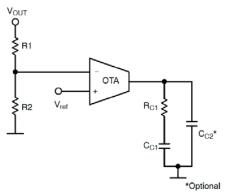

**Figure 1. Typical Application Circuit**

## ON Semiconductor®

## www.onsemi.com

TSSOP-14 DT SUFFIX CASE 948G

#### **MARKING DIAGRAM**

3011 = Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb–Free Package

(Note: Microdot may be in either location)

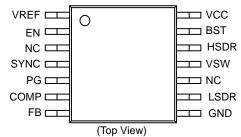

## PIN CONNECTIONS

### **ORDERING INFORMATION**

| Device        | Package               | Shipping <sup>†</sup> |

|---------------|-----------------------|-----------------------|

| NCP3011DTBR2G | TSSOP-14<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCV3011DTBR2G | TSSOP-14<br>(Pb-Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

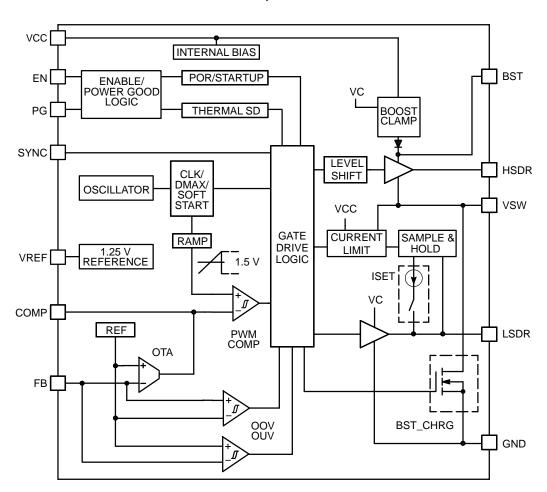

Figure 2. NCP3011 Block Diagram

## PIN FUNCTION DESCRIPTION

| Pin | Pin Name        | Description                                                                                                                                                                                                                                                                                     |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VREF            | The VREF pin is the output for a 1.25 V reference (1 mA max). A 100 k $\Omega$ resistor in parallel with a 1 $\mu$ F ceramic capacitor must be connected from this pin to GND to ensure external reference stability.                                                                           |

| 2   | EN              | The EN pin is the enable/disable input. A logic high on this pin enables the device. This pin has also an internal current source pull up. A 10 k $\Omega$ resistor should be connected in series with this pin if $V_{EN}$ is externally biased from a separate supply.                        |

| 3   | NC              | Not Connected                                                                                                                                                                                                                                                                                   |

| 4   | SYNC            | The dual function SYNC pin synchronizes the device to a higher frequency (Slave Mode). Alternately, it outputs a 456 kHz clock signal with 180° of phase shift (Master Mode). Connect a 100 k $\Omega$ resistor from SYNC to GND to enable Master Mode. No resistor is required for Slave Mode. |

| 5   | PG              | The Power Good pin is an open drain output that is low when the regulated output voltage is beyond the "Power Good" upper and lower thresholds. Otherwise, it is a high impedance pin.                                                                                                          |

|     |                 | The COMP pin connects to the output of the Operational Transconductance Amplifier (OTA) and the positive terminal of the PWM comparator. This pin is used in conjunction with the FB pin to compensate the voltage mode control feedback loop.                                                  |

| 7   | FB              | The FB pin is connected to the inverting input of the OTA. This pin is used in conjunction with the COMP pin to compensate the voltage mode control feedback loop.                                                                                                                              |

| 8   | GND             | Ground Pin                                                                                                                                                                                                                                                                                      |

| 9   | LSDR            | The LSDR pin is connected to the output of the low side driver which connects to the gate of the low side N–FET. It is also used to set the threshold of the current limit circuit (I <sub>SET</sub> ) by connecting a resistor from LSDR to GND.                                               |

| 10  | NC              | Not Connected                                                                                                                                                                                                                                                                                   |

| 11  | VSW             | The VSW pin is the return path for the high side driver. It is also used in conjunction with the V <sub>CC</sub> pin to sense current in the high side MOSFET.                                                                                                                                  |

| 12  | HSDR            | The HSDR pin is connected to the output of the high side driver which connects to the gate of the high side N-FET.                                                                                                                                                                              |

| 13  | BST             | The BST pin is the supply rail for the gate drivers. A capacitor must be connected between this pin and the VSW pin.                                                                                                                                                                            |

| 14  | V <sub>CC</sub> | The $V_{CC}$ pin is the main voltage supply input. It is also used in conjunction with the VSW pin to sense current in the high side MOSFET.                                                                                                                                                    |

## ABSOLUTE MAXIMUM RATINGS (measured vs. GND pin 8, unless otherwise noted)

| Rating                                                                                            | Symbol              | V <sub>MAX</sub>             | V <sub>MIN</sub> | Unit |

|---------------------------------------------------------------------------------------------------|---------------------|------------------------------|------------------|------|

| High Side Drive Boost Pin                                                                         | BST                 | 45                           | -0.3             | V    |

| Boost to V <sub>SW</sub> differential voltage                                                     | BST-V <sub>SW</sub> | 13.2                         | -0.3             | V    |

| COMP                                                                                              | COMP                | 5.5                          | -0.3             | V    |

| Enable                                                                                            | EN                  | 5.5                          | -0.3             | V    |

| Feedback                                                                                          | FB                  | 5.5                          | -0.3             | V    |

| High-Side Driver Output                                                                           | HSDR                | 40                           | -0.3             | V    |

| Low-Side Driver Output                                                                            | LSDR                | 13.2                         | -0.3             | V    |

| Power Good                                                                                        | PG                  | 5.5                          | -0.3             | V    |

| Synchronization                                                                                   | SYNC                | 5.5                          | -0.3             | V    |

| Main Supply Voltage Input                                                                         | V <sub>CC</sub>     | 40                           | -0.3             | V    |

| External Reference                                                                                | VREF                | 5.5                          | -0.3             | V    |

| Switch Node Voltage                                                                               | $V_{\sf SW}$        | 40                           | -0.6             | V    |

| Maximum Average Current V <sub>CC</sub> , BST, HSDRV, LSDRV, V <sub>SW</sub> , GND REF EN SYNC PG | I <sub>max</sub>    | 130<br>7.1<br>2.5<br>11<br>4 |                  | mA   |

| Operating Junction Temperature Range (Note 1)                                                     | TJ                  | -40 t                        | o +140           | °C   |

| Maximum Junction Temperature                                                                      | $T_{J(MAX)}$        | +150                         |                  | °C   |

| Storage Temperature Range                                                                         | T <sub>stg</sub>    | -55 to +150                  |                  | °C   |

| Thermal Characteristics (Note 2) TSSOP–14 Plastic Package Thermal Resistance Junction–to–Air      | $R_{	hetaJA}$       | 1                            | 90               | °C/W |

| Lead Temperature Soldering (10 sec): Reflow (SMD styles only) Pb–Free (Note 3)                    | R <sub>F</sub>      | 260                          | Peak             | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The maximum package power dissipation limit must not be exceeded.

$$\mathsf{P}_\mathsf{D} = \frac{\mathsf{T}_\mathsf{J(max)} - \mathsf{T}_\mathsf{A}}{\mathsf{R}_{\theta \mathsf{JA}}}$$

- 2. When mounted on minimum recommended FR-4 or G-10 board

- 3. 60-180 seconds minimum above 237°C.

## $\textbf{ELECTRICAL CHARACTERISTICS} \ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < +125^{\circ}\text{C}, \ \text{V}_{\text{CC}} = 12 \ \text{V}, \ \text{for min/max values unless otherwise noted})$

| Characteristic                 | Conditions                                                                                             | Min  | Тур  | Max  | Unit |

|--------------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage Range            | -                                                                                                      | 4.7  |      | 28   | V    |

| SUPPLY CURRENT                 |                                                                                                        |      |      |      |      |

| Quiescent Supply Current       | EN = 0 V <sub>CC</sub> = 12 V                                                                          | -    | 2.5  | 4.0  | mA   |

| V <sub>CC</sub> Supply Current | $V_{FB}$ = 0.75 V, Switching, $V_{CC}$ = 4.7 V                                                         | _    | 5.8  | 8.0  | mA   |

| V <sub>CC</sub> Supply Current | $V_{FB} = 0.75 \text{ V}$ , Switching, $V_{CC} = 28 \text{ V}$                                         | _    | 6.0  | 12   | mA   |

| UNDER VOLTAGE LOCKOUT          |                                                                                                        |      |      |      |      |

| UVLO Rising Threshold          | V <sub>CC</sub> Rising Edge                                                                            | 3.8  | 4.3  | 4.7  | V    |

| UVLO Falling Threshold         | V <sub>CC</sub> Falling Edge                                                                           | 3.6  | 4.0  | 4.3  | V    |

| OSCILLATOR                     | •                                                                                                      | •    | •    | •    | •    |

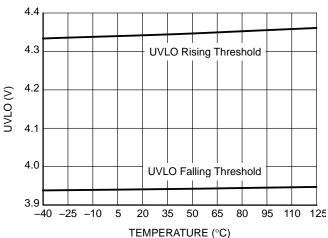

| Oscillator Frequency           | $T_J = +25^{\circ}C, 4.7 \text{ V} \le V_{CC} \le 28 \text{ V}$                                        | 350  | 400  | 450  | kHz  |

|                                | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}, 4.7 \text{ V} \le \text{V}_{CC} \le 28 \text{ V}$ | 330  | 400  | 470  | kHz  |

| Ramp-Amplitude Voltage         | V <sub>peak</sub> – V <sub>alley</sub>                                                                 | _    | 1.5  | _    | V    |

| Ramp Valley Voltage            |                                                                                                        | 0.44 | 0.7  | 0.96 | V    |

| PWM                            | •                                                                                                      |      |      |      |      |

| Minimum Duty Cycle             |                                                                                                        | _    | 7    | _    | %    |

| Maximum Duty Cycle             |                                                                                                        | 80   | 83   | _    | %    |

| Soft Start Ramp Time           | $V_{FB} = V_{COMP}$                                                                                    | _    | 5.2  | _    | ms   |

| EXTERNAL VOLTAGE REFERENC      | E                                                                                                      | 1    | 1    | 1    |      |

| VREF Voltage                   | I <sub>REF</sub> = 1 mA                                                                                | 1.14 | 1.25 | 1.35 | V    |

| VREF Line Regulation           | V <sub>CC</sub> = 4.7 V - 28 V                                                                         | -1   | _    | +1   | %    |

| VREF Load Regulation           | I <sub>REF</sub> = 0 mA to 1.5 mA                                                                      | -2   | -0.2 | +2   | %    |

| Short Circuit Output Current   | V <sub>REF</sub> = 0 V                                                                                 | 4.5  | 5.7  | 7.0  | mA   |

| ENABLE                         | •                                                                                                      | •    | •    | •    | •    |

| Enable Threshold High          |                                                                                                        | _    | _    | 3.4  | V    |

| Enable Threshold Low           |                                                                                                        | 1.0  | _    | _    | V    |

| Enable Source Current          |                                                                                                        | 20   | 50   | 90   | μΑ   |

| POWER GOOD                     | •                                                                                                      | •    | •    | •    | •    |

| Power Good High Threshold      | V <sub>CC</sub> = 12 V                                                                                 | 0.72 | 0.89 | 1.06 | V    |

| Power Good Low Threshold       | V <sub>CC</sub> = 12 V                                                                                 | 0.65 | 0.71 | 0.75 | V    |

| Power Good Low Voltage         | V <sub>CC</sub> = 12 V, I <sub>PG</sub> = 4 mA                                                         | 0.13 | 0.22 | 0.35 | V    |

| SYNC                           | •                                                                                                      |      |      |      |      |

| SYNC Input High Threshold      |                                                                                                        | -    | -    | 2.0  | V    |

| SYNC Output High               | 10 μA load                                                                                             | _    | 5.0  | _    | V    |

| SYNC Output Low                |                                                                                                        | _    | 90   | -    | mV   |

| Phase Delay                    | (Note 4)                                                                                               | _    | 200  | -    | 0    |

| SYNC Drive Current (Sourcing)  |                                                                                                        | _    | 1.6  | -    | mA   |

| Master Threshold Current       |                                                                                                        | 5.0  | 14.4 | 25   | μΑ   |

| Master Frequency               |                                                                                                        | 390  | 466  | 550  | kHz  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 4. Guaranteed by design.

5. The voltage sensed across the high side MOSFET during conduction.

6. This assumes 100 pF capacitance to ground on the COMP Pin and a typical internal  $R_0$  of > 10 M $\Omega$ .

7. This is not a protection feature.

## **ELECTRICAL CHARACTERISTICS** ( $-40^{\circ}$ C < T<sub>J</sub> < +125°C, V<sub>CC</sub> = 12 V, for min/max values unless otherwise noted)

| Characteristic                               | Conditions                                                                             | Min      | Тур      | Max        | Unit                     |

|----------------------------------------------|----------------------------------------------------------------------------------------|----------|----------|------------|--------------------------|

| ERROR AMPLIFIER (GM)                         |                                                                                        | •        | •        |            |                          |

| Transconductance                             |                                                                                        | 0.9      | 1.33     | 1.9        | mS                       |

| Open Loop dc Gain                            | (Notes 4 and 6)                                                                        | -        | 70       | _          | dB                       |

| Output Source Current<br>Output Sink Current |                                                                                        | 45<br>45 | 70<br>70 | 100<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| FB Input Bias Current                        |                                                                                        | _        | 0.5      | 500        | nA                       |

| Feedback Voltage                             | T <sub>J</sub> = 25 C                                                                  | 0.792    | 0.8      | 0.808      | V                        |

|                                              | $-40^{\circ}$ C < T <sub>J</sub> < $+125^{\circ}$ C,<br>4.7 V < V <sub>IN</sub> < 28 V | 0.788    | 0.8      | 0.812      | V                        |

| COMP High Voltage                            | V <sub>FB</sub> = 0.75 V                                                               | 4.0      | 4.4      | 5.0        | V                        |

| COMP Low Voltage                             | V <sub>FB</sub> = 0.85 V                                                               | -        | 60       | _          | mV                       |

| OUTPUT VOLTAGE FAULTS                        |                                                                                        | •        |          |            |                          |

| Feedback OOV Threshold                       |                                                                                        | 0.9      | 1.0      | 1.1        | V                        |

| Feedback OUV Threshold                       |                                                                                        | 0.55     | 0.59     | 0.65       | V                        |

| OVER CURRENT                                 |                                                                                        | <b>-</b> |          |            |                          |

| ISET Source Current                          |                                                                                        | 7.0      | 14       | 18         | μΑ                       |

| Current Limit Set Voltage (Note 5)           | $R_{SET} = 22.2 \text{ k}\Omega$                                                       | 140      | 240      | 360        | mV                       |

| GATE DRIVERS AND BOOST CLAMP                 |                                                                                        | •        |          |            |                          |

| HSDRV Pullup Resistance                      | $V_{CC}$ = 8 V and $V_{BST}$ = 7.5 V $V_{SW}$ = GND 100 mA out of HSDR pin             | 4.0      | 10.5     | 20         | Ω                        |

| HSDRV Pulldown Resistance                    | $V_{CC}$ = 8 V and $V_{BST}$ = 7.5 V $V_{SW}$ = GND 100 mA into HSDR pin               | 2.5      | 5.0      | 11.5       | Ω                        |

| LSDRV Pullup Resistance                      | $V_{CC}$ = 8 V and $V_{BST}$ = 7.5 V $V_{SW}$ = GND 100 mA out of LSDR pin             | 3.0      | 8.9      | 16         | Ω                        |

| LSDRV Pulldown Resistance                    | $V_{CC}$ = 8 V and $V_{BST}$ = 7.5 V $V_{SW}$ = GND 100 mA into LSDR pin               | 1.0      | 2.8      | 6.0        | Ω                        |

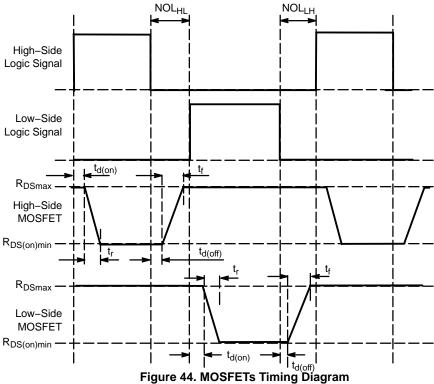

| HSDRV falling to LSDRV Rising Delay          | $V_{CC}$ and $V_{BST} = 8 V$                                                           | 50       | 85       | 110        | ns                       |

| LSDRV Falling to HSDRV Rising De-<br>lay     | $V_{CC}$ and $V_{BST} = 8 \text{ V}$                                                   | 60       | 85       | 120        | ns                       |

| Boost Clamp Voltage                          | $V_{IN}$ = 12 V, $V_{SW}$ = GND, $V_{COMP}$ = 1.3 V                                    | 5.5      | 7.5      | 9.6        | V                        |

| THERMAL SHUTDOWN                             |                                                                                        |          |          |            |                          |

| Thermal Shutdown                             | (Notes 4 and 7)                                                                        | _        | 150      | _          | °C                       |

| Hysteresis                                   | (Notes 4 and 7)                                                                        | -        | 15       | _          | °C                       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Guaranteed by design.

<sup>5.</sup> The voltage sensed across the high side MOSFET during conduction.

6. This assumes 100 pF capacitance to ground on the COMP Pin and a typical internal R<sub>0</sub> of > 10 MΩ.

7. This is not a protection feature.

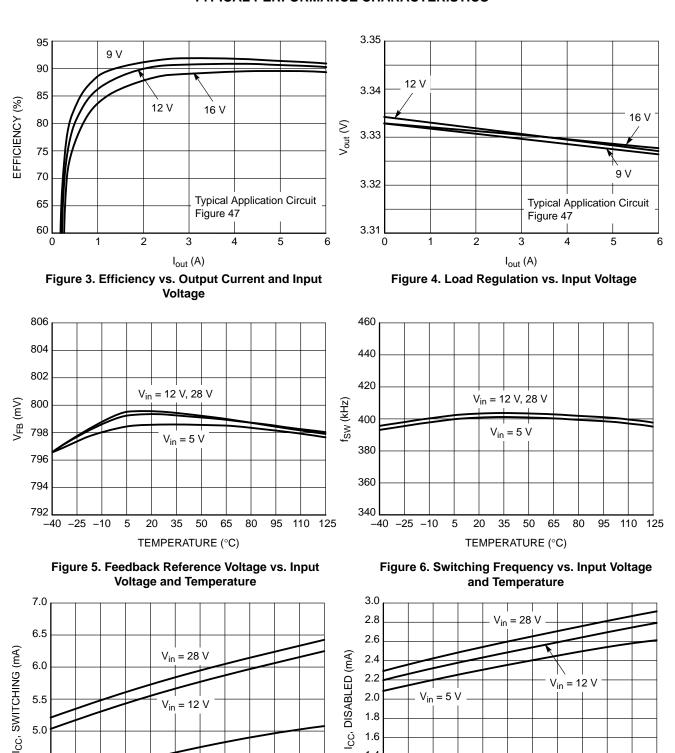

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 7. Supply Current vs. Input Voltage and **Temperature**

$V_{in} = 5 V$

TEMPERATURE (°C)

50

65 80 95

35

5.0

4.5

-25 -10 5 20

Figure 8. Supply Current (Disabled) vs. Input **Voltage and Temperature**

35 50

TEMPERATURE (°C)

65

80

95 110 125

110 125

1.6 1.4

1.2 1.0

-25 -10

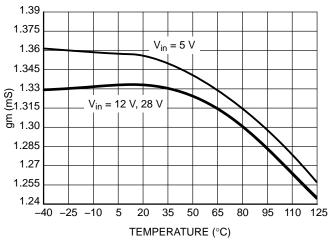

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 9. Transconductance vs. Input Voltage and Temperature

Figure 10. Input Undervoltage Lockout vs. Temperature

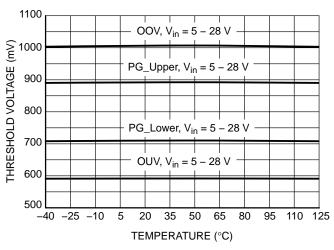

Figure 11. Output Voltage Thresholds vs. Input Voltage and Temperature

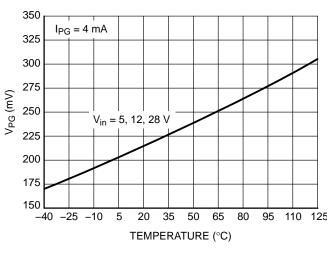

Figure 12. Power Good Output Low Voltage vs. Input Voltage and Temperature

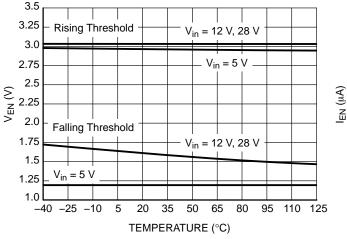

Figure 13. Enable Thresold vs. Input Voltage and Temperature

Figure 14. Enable Pullup Current vs. Input Voltage and Temperature

### TYPICAL PERFORMANCE CHARACTERISTICS

1000 950 900 VALLEY VOLTAGE (mV) 850 800  $V_{in} = 5 - 28 \text{ V}$ 750 700 650 600 550 500 450 400 -40 -25 -10 35 50 65 110 125 20 80 TEMPERATURE (°C)

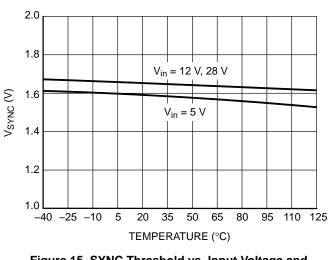

Figure 15. SYNC Threshold vs. Input Voltage and Temperature

1.26

1.255

1.25

1.24

1.235

1.23

-40 -25 -10

(2) H1.245  $V_{in} = 5 V$

$V_{in} = 12 \text{ V}, 28 \text{ V}$

5 20

Figure 16. Valley Voltage vs. Input Voltage and Temperature

Figure 17. External Reference Voltage vs. Input Voltage and Temperature

TEMPERATURE (°C)

35 50 65 80

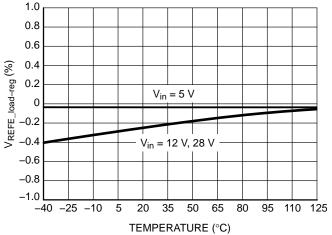

Figure 18. External Reference Voltage vs. Input

Voltage and Temperature

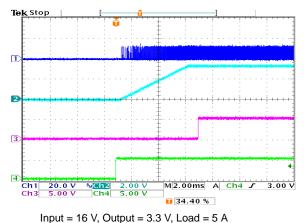

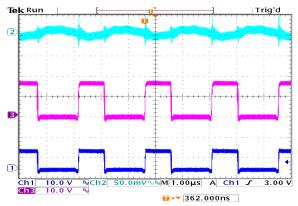

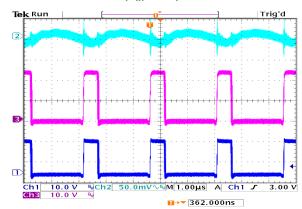

C1 (Blue) = VSW, C2 (Light Blue) = V<sub>OUT</sub>

C3 (Magenta) = Power Good, C4 (Green) = Enable

Figure 19. Soft-Start Waveforms

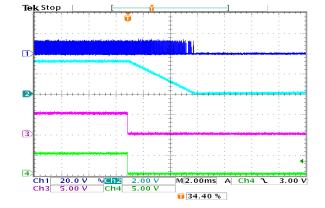

Input = 16 V, Output = 3.3 V, Load = 5 A C1 (Blue) = VSW, C2 (Light Blue) = V<sub>OUT</sub> C3 (Magenta) = Power Good, C4 (Green) = Enable

Figure 20. Soft-Stop Waveforms

### TYPICAL PERFORMANCE CHARACTERISTICS

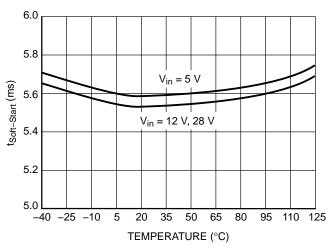

Figure 21. Soft-Start Time vs. Input Voltage and Temperature

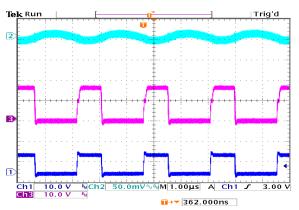

Input = 9 V, Output = 3.3 V, Load = 0 A C1 (Blue) = VSW, C2 (Light Blue) = V<sub>OUT</sub> C3 (Magenta) = HSDR

Figure 23. No Load Switching Waveforms  $(V_{in} = 9 V)$

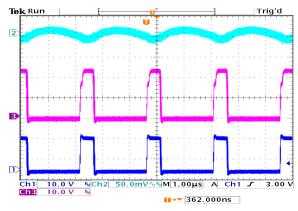

Input = 16 V, Output = 3.3 V, Load = 0 A C1 (Blue) = VSW, C2 (Light Blue) =  $V_{OUT}$  C3 (Magenta) = HSDR

Figure 25. No Load Switching Waveforms  $(V_{in} = 16 \text{ V})$

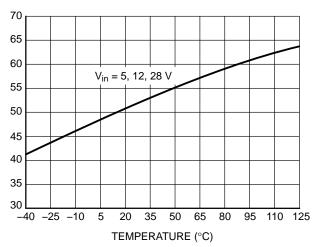

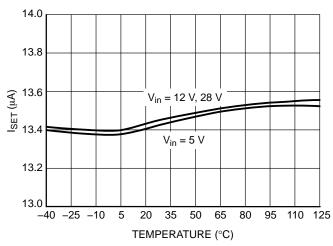

Figure 22. Current Limit Set Current vs.

Temperature

Input = 9 V, Output = 3.3 V, Load = 5 A C1 (Blue) = VSW, C2 (Light Blue) = V<sub>OUT</sub> C3 (Magenta) = HSDR

Figure 24. CCM Switching Waveforms  $(V_{in} = 9 V)$

Input = 16 V, Output = 3.3 V, Load = 5 A C1 (Blue) = VSW, C2 (Light Blue) =  $V_{OUT}$  C3 (Magenta) = HSDR

Figure 26. CCM Switching Waveforms (V<sub>in</sub> = 16 V)

#### **DETAILED DESCRIPTION**

### **OVERVIEW**

The NCP3011 operates as a 400 kHz, voltage–mode, pulse–width–modulated, (PWM) synchronous buck converter. It drives high–side and low–side N–channel power MOSFETs. The NCP3011 incorporates an internal boost circuit consisting of a boost Clamp and boost diode to provide supply voltage for the high side MOSFET Gate driver. The NCP3011 also integrates several protection features including input undervoltage lockout (UVLO), output undervoltage (OUV), output overvoltage (OOV), adjustable high–side current limit (I<sub>SET</sub> and I<sub>LIM</sub>), and thermal shutdown (TSD). The NCP3011 includes a Power Good (PG) open drain output which flags out of regulation conditions.

The operational transconductance amplifier (OTA) provides a high gain error signal which is compared to the internal ramp signal using the PWM comparator. This results in a voltage mode PWM feedback stage. The PWM signal is sent to the internal gate drivers to modulate MOSFET on and off times. The gate driver stage incorporates symmetrical fixed non–overlap time between the high–side and low–side MOSFET gate drives.

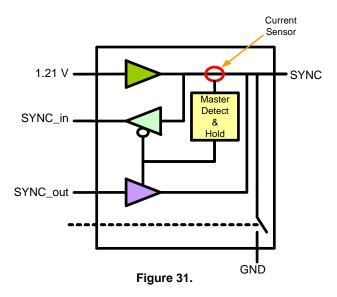

The NCP3011 has a dual function Master/Slave SYNC pin In Slave mode, the NCP3011 synchronizes to an external clock signal. In Master mode, the NCP3011 can output a phase shifted clock signal to drive another master slave equipped power stage to provide a 180° switching relationship between the power stages. This can help to reduce the required input filter capacitance in multi–stage power converters.

The external 1.25 V reference voltage (VREF) is provided for system level use. It remains active even when the NCP3011 is disabled.

#### **POR and UVLO**

The device contains an internal Power On Reset (POR) and input Undervoltage Lockout (UVLO) that inhibits the internal logic and the output stage from operating until  $V_{CC}$  reaches their respective predefined voltage levels. The internal logic takes approximately 50  $\mu$ s to check the SYNC pin and determine if the device is in Master mode or Slave mode once the voltage at  $V_{CC}$  exceeds the rising UVLO

threshold. The device remains in Standby if enable is not asserted following the 50 µs time period.

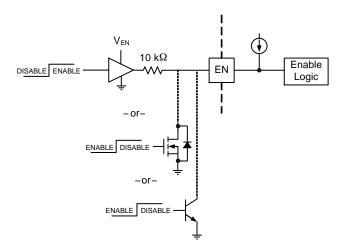

### Enable/Disable

The device has an enable pin (EN) with internal 50  $\mu$ A pullup current. This gives the user the option of driving EN with a push–pull or open–drain/collector enable signal. When driving EN with an external logic supply a 10 k $\Omega$  series current limiting resistor must be placed in series with EN. See Figure 27. The maximum enable threshold is 3.4 V. If no external drive voltage is available, the internal pullup can be used to enable the device, and an open drain/collector input, such as a MOSFET or BJT can be used to disable the device. A capacitor connected between EN and ground can be used with the internal pullup current source to provide a fixed delay to turn–on and turn off. See Equation 1.

Figure 27. Enable Circuits: Push-Pull, Open-Drain, or Open-Collector

$$C_{EN\_DLY} = \frac{I_{PU} \times T_{EN\_DLY}}{V_{EN\_TH}}$$

(eq. 1)

$C_{EN\ DLY} = Delay Capacitance (F)$

$I_{PU} = Pullup Current$

$V_{EN\_TH}$  = Enable Input High Threshold Voltage

T<sub>EN DLY</sub> = Desired Delay Time

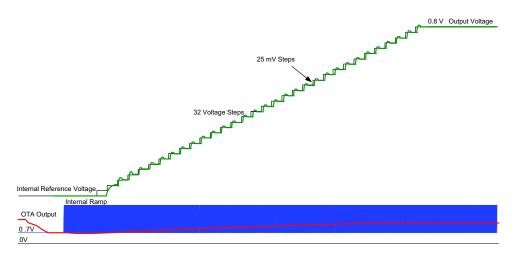

### Startup and Shutdown

Once enable is asserted the device begins its startup process. Closed–loop soft–start begins after a 400 µs delay wherein the boost capacitor is charged, and the current limit threshold is set. During the 400 µs delay the OTA output is set to just below the valley voltage of the internal ramp. This is done to reduce delays and to ensure a consistent pre soft–start condition. The device increases the internal reference from 0 V to 0.8 V in 32 discrete steps while maintaining closed loop regulation at each step. Some overshoot may be evident at the start of each step depending on the voltage loop phase margin and bandwidth. See Figure 28. The total soft–start time is 5.12 ms.

The soft–stop process begins once the EN pin voltage goes below the input low threshold. Soft–stop decreases the internal reference from 0.8~V-0~V in 32 steps as with Soft–Start. Soft–Stop finishes with one "last" high side gate pulse at half the period of the prior pulse. This helps ensure positive inductor current following turn off at light loads, which prevents negative output voltage.

Enable low during Soft-Start will result in Soft-Stop down counting from that step. Likewise, Enable high during Soft-Stop will result in Soft-Start up counting from that step.

Figure 28. Soft-Start Details

### Master/Slave Synchronization

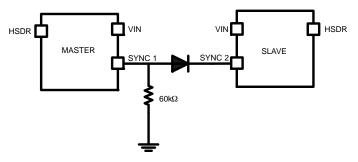

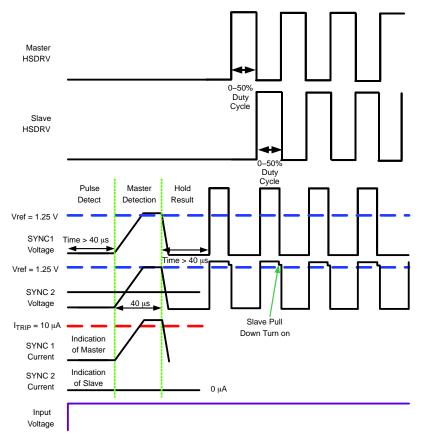

The SYNC pin performs two functions. The first function is to identify if the device is a master or a slave. The second function is to either synchronize to an external clock (Slave Mode) or provide an external clock that is shifted by 180° from the high side switch (Master Mode). The typical application circuit for this is shown in Figure 29.

Figure 29. Master Slave Typical Application

Upon initial power up, the device determines if it is a Master or Slave by applying 1.25 V to the SYNC pin and determining whether the current draw from the pin is greater than the Master Threshold Current (ISYNC<sub>TRIP</sub>). If ISYNC<sub>TRIP</sub> is exceeded then the device enters master mode. If the current is less than ISYNC<sub>TRIP</sub> the device enters slave mode. Once identified as a Master, the device switching frequency is increased by 15%. See Equation 2.

$$R_{Master} = \frac{SYNC_{ref}}{ISYNC_{TRIP}}$$

(eq. 2)

$$\begin{split} R_{Master} &= Master \ Select \ Resistor \ (\Omega) \\ SYNC_{ref} &= Sync \ Reference \ Voltage \ (V) \\ ISYNC_{TRIP} &= Master \ Threshold \ Current \ (A) \end{split}$$

Figure 30. Master Slave Typical Waveforms

The master slave identification begins when input voltage is applied prior to POR. Upon application of input voltage, the device waits for input pulses for a minimum of 40 µs as shown in Figure 30. During the pulse detection period if concurrent edges occur on the SYNC pin from an external source, the device enters slave mode and skips the master detection sequence. The device will remain in the detected state until power is cycled.

### **External Synchronization**

The device can sync to frequencies that are 15% to 60% higher than the nominal switching frequency. If an external sync pulse is present at the SYNC pin prior to input voltage application to the device, then no additional external components are needed. If the external clock is not present following power on reset of the device, the voltage on the SYNC pin will determine whether the device is a master or a slave. If the external clock source is meant to start after device operation, its off state should be high or tristate. It is also important to note that the slope of the internal ramp is fixed and synchronizing to a faster clock which will truncate

the ramp signal. The equation for calculating the remaining ramp height is shown below:

$$V_{RAMP} = VRAMP_{typ} * \frac{F_{nom}}{F_{SYNC}} \rightarrow 1 V * \frac{400 \text{ kHz}}{570 \text{ kHz}} \approx 0.70 \text{ V}$$

(eq. 3)

### OOV, OUV, and Power Good

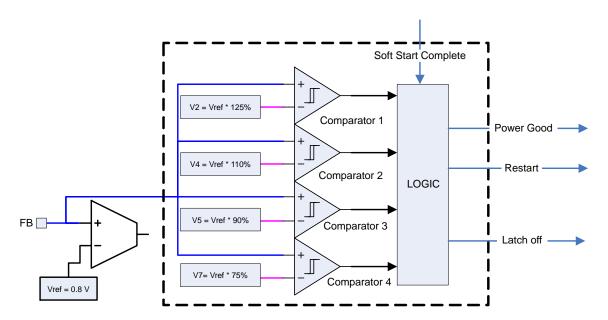

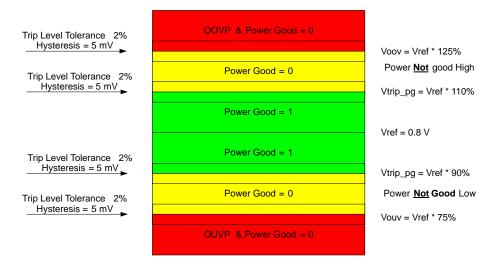

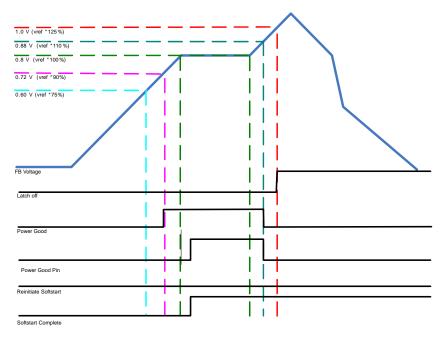

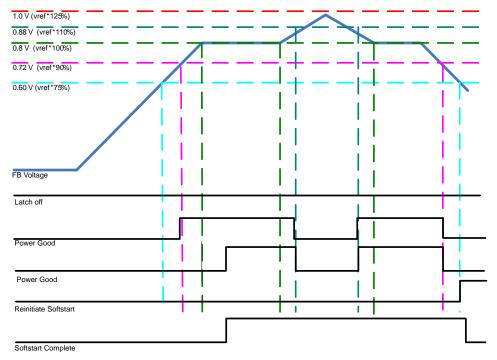

The output voltage of the buck converter is monitored at the Feedback pin of the output power stage. Four comparators are placed on the feedback node of the OTA to monitor the operating window of the feedback voltage as shown in Figures 32 and 33. All comparator outputs are ignored during the soft-start sequence as soft-start is regulated by the OTA and false trips would be generated. Further, the Power Good pin is held low until the comparators are evaluated. After the soft-start period has ended, if the feedback is below the reference voltage of comparator 4 (0.6 < V<sub>FB</sub>), the output is considered "undervoltage," the device will initiate a restart, and the Power Good pin remains low with a 55  $\Omega$  pulldown resistance. If the voltage at the Feedback pin is between the reference voltages of comparator 4 and comparator 3 (0.60 < V<sub>FB</sub> < 0.72), then the output voltage is considered "power not good low" and the Power Good pin remains low. When the Feedback pin voltage rises between the reference voltages of comparator 3 and comparator 2 (0.72 < V<sub>FB</sub> <0.88), then the output voltage is considered "Power Good" and the Power Good pin is released. If the voltage at the Feedback pin is between the reference voltages of comparator 2 and comparator 1 (0.88 <  $V_{FB}$  < 1.00), the output voltage is considered "power not good high" and the power good pin is pulled low with a 55  $\Omega$  pulldown resistance. Finally, if the feedback voltage is greater than comparator 1 (1.0 <  $V_{FB}$ ), the output voltage is considered "overvoltage," the Power Good pin will remain low, and the device will latch off. To clear a latch fault, input voltage must be recycled. Graphical representation of the OOV, OUV, and Power Good pin functionality is shown in Figures 34 and 35.

Figure 32. OOV, OUV, and Power Good Circuit Diagram

Figure 33. OOV, OUV, and Power Good Window Diagram

Figure 34. Powerup Sequence and Overvoltage Latch

Figure 35. Powerup Sequence and Undervoltage Soft-Start

#### **CURRENT LIMIT AND CURRENT LIMIT SET**

#### Overview

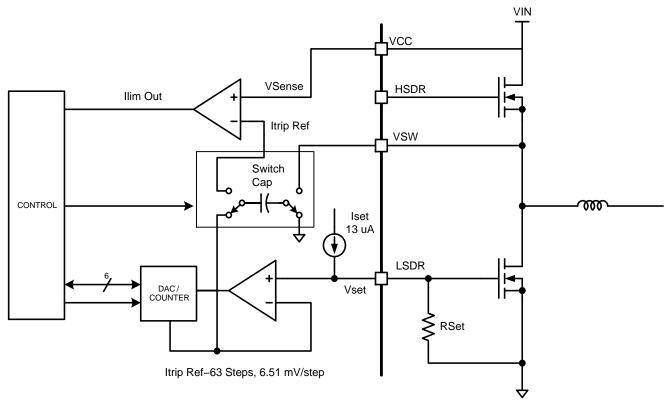

The NCP3011 uses the voltage drop across the High Side MOSFET during the on time to sense inductor current. The

$I_{Limit}$  block consists of a voltage comparator circuit which compares the differential voltage across the  $V_{CC}$  Pin and the  $V_{SW}$  Pin with a resistor settable voltage reference. The sense portion of the circuit is only active while the HS MOSFET is turned ON.

Figure 36. I<sub>set</sub> / I<sub>Limit</sub> Block Diagram

### **Current Limit Set**

The  $I_{Limit}$  comparator reference is set during the startup sequence by forcing a typically 13  $\mu A$  current through the low side gate drive resistor. The gate drive output will rise to a voltage level shown in the equation below:

$$V_{set} = I_{set} * R_{set}$$

(eq. 4)

Where  $I_{SET}$  is 13  $\mu A$  and  $R_{SET}$  is the gate to source resistor on the low side MOSFET.

This resistor is normally installed to prevent MOSFET leakage from causing unwanted turn on of the low side MOSFET. In this case, the resistor is also used to set the  $I_{Limit}$  trip level reference through the  $I_{Limit}$  DAC. The  $I_{set}$  process takes approximately 350  $\mu$ s to complete prior to Soft–Start stepping. The scaled voltage level across the  $I_{SET}$  resistor is converted to a 6 bit digital value and stored as the trip value. The binary  $I_{Limit}$  value is scaled and converted to the analog  $I_{Limit}$  reference voltage through a DAC counter. The DAC has 63 steps in 6.51 mV increments equating to a maximum sense voltage of 403 mV. During the  $I_{set}$  period

prior to Soft–Start, the DAC counter increments the reference on the  $I_{SET}$  comparator until it crosses the  $V_{SET}$  voltage and holds the DAC reference output to that count value. This voltage is translated to the  $I_{Limit}$  comparator during the  $I_{Sense}$  portion of the switching cycle through the switch cap circuit. See Figure 36. Exceeding the maximum sense voltage results in no current limit. Steps 0 to 10 result in an effective current limit of 0 mV.

### **Current Sense Cycle**

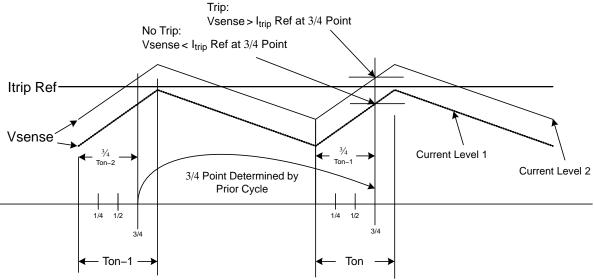

Figure 37 shows how the current is sampled as it relates to the switching cycle. Current level 1 in Figure 37 represents a condition that will not cause a fault. Current level 2 represents a condition that will cause a fault. The sense circuit is allowed to operate below the 3/4 point of a given switching cycle. A given switching cycle's 3/4 Ton time is defined by the prior cycle's Ton and is quantized in 10 ns steps. A fault occurs if the sensed MOSFET voltage exceeds the DAC reference within the 3/4 time window of the switching cycle.

Each switching cycle's Ton is counted in 10 nS time steps. The 3/4 sample time value is held and used for the following cycle's limit sample time

Figure 37. I<sub>Limit</sub> Trip Point Description

### Soft-Start Current limit

During soft–start the  $I_{SET}$  value is doubled to allow for inrush current to charge the output capacitance. The DAC reference is set back to its normal value after soft–start has completed.

### V<sub>SW</sub> Ringing

The  $I_{Limit}$  block can lose accuracy if there is excessive  $V_{SW}$  voltage ringing that extends beyond the 1/2 point of the high-side transistor on-time. Proper snubber design and keeping the ratio of ripple current and load current in the 10-30% range can help alleviate this as well.

### **Current Limit**

A current limit trip results in completion of one switching cycle and subsequently half of another cycle T<sub>on</sub> to account for negative inductor current that might have caused negative potentials on the output. Subsequently the power MOSFETs are both turned off and a 4 soft—start time period wait passes before another soft—start cycle is attempted.

## Iave vs Trip Point

The average load trip current versus  $R_{\text{SET}}$  value is shown the equation below:

$$I_{AveTRIP} = \frac{I_{set} \times R_{set}}{R_{DS(on)}} - \frac{1}{4} \left[ \frac{V_{IN} - V_{OUT}}{L} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{F_{SW}} \right]$$

(eq. 5)

Where:

L = Inductance (H)

$I_{SET} = 13 \mu A$

$R_{SET}$  = Gate to Source Resistance ( $\Omega$ )

$R_{DS(on)} = On Resistance of the HS MOSFET (\Omega)$

$V_{IN} = Input Voltage (V)$

$V_{OUT} = Output \ Voltage \ (V)$

$F_{SW} = Switching Frequency (Hz)$

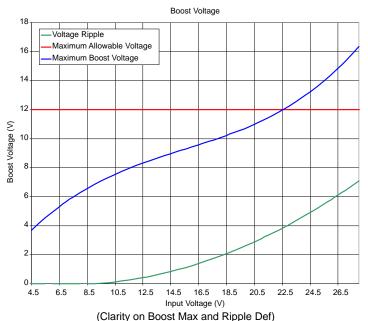

## **Boost Clamp Functionality**

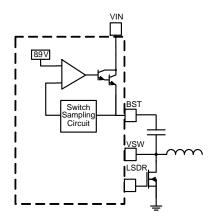

The boost circuit requires an external capacitor connected between the BST and  $V_{SW}$  pins to store charge for supplying the high and low–side gate driver voltage. This clamp circuit limits the driver voltage to typically 7.5 V when  $V_{IN}>9$  V, otherwise this internal regulator is in dropout and typically  $V_{IN}-1.25$  V.

The boost circuit regulates the gate driver output voltage and acts as a switching diode. A simplified diagram of the boost circuit is shown in Figure 38. While the switch node is grounded, the sampling circuit samples the voltage at the boost pin, and regulates the boost capacitor voltage. The sampling circuit stores the boost voltage while the  $V_{\rm SW}$  is high and the linear regulator output transistor is reversed biased.

Figure 38. Boost Circuit

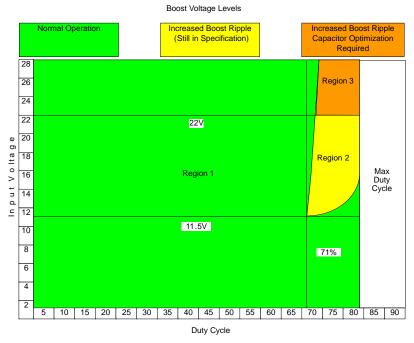

Reduced sampling time occurs at high duty cycles where the low side MOSFET is off for the majority of the switching period. Reduced sampling time causes errors in the regulated voltage on the boost pin. High duty cycle / input voltage induced sampling errors can result in increased boost ripple voltage or higher than desired DC boost voltage. Figure 39 outlines all operating regions.

The recommended operating conditions are shown in Region 1 (Green) where a 0.1  $\mu$ F, 25 V ceramic capacitor can be placed on the boost pin without causing damage to the device or MOSFETS. Larger boost ripple voltage occurring over several switching cycles is shown in Region 2 (Yellow).

The boost ripple frequency is dependent on the output capacitance selected. The ripple voltage will not damage the device or  $\pm 12$  V gate rated MOSFETs.

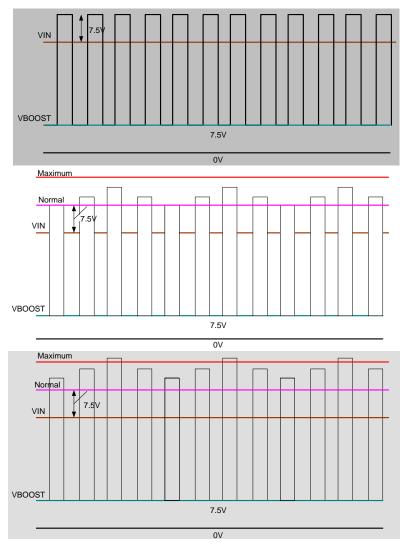

Conditions where maximum boost ripple voltage could damage the device or  $\pm$  12 V gate rated MOSFETs can be seen in Region 3 (Orange). Placing a boost capacitor that is no greater than 10X the input capacitance of the high side MOSFET on the boost pin limits the maximum boost voltage < 12 V. The typical drive waveforms for Regions 1, 2 and 3 (green, yellow, and orange) regions of Figure 39 are shown in Figure 40.

Figure 39. Safe Operating Area for Boost Voltage with a 0.1 μF Capacitor

Figure 40. Typical Waveforms for Region 1 (top), Region 2 (middle), and Region 3 (bottom)

To illustrate, a 0.1  $\mu$ F boost capacitor operating at > 80% duty cycle and > 22.5 V input voltage will exceed the specifications for the driver supply voltage. See Figure 41.

Figure 41. Boost Voltage at 80% Duty Cycle

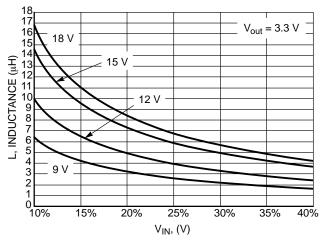

### **Inductor Selection**

When selecting the inductor, it is important to know the input and output requirements. Some example conditions are listed below to assist in the process.

**Table 1. DESIGN PARAMETERS**

| Design Para           | Example Value             |             |

|-----------------------|---------------------------|-------------|

| Input Voltage         | (V <sub>IN</sub> )        | 9 V to 18 V |

| Nominal Input Voltage | (V <sub>IN</sub> )        | 12 V        |

| Output Voltage        | (V <sub>OUT</sub> )       | 3.3 V       |

| Input ripple voltage  | (VIN <sub>RIPPLE</sub> )  | 300 mV      |

| Output ripple voltage | (VOUT <sub>RIPPLE</sub> ) | 50 mV       |

| Output current rating | (I <sub>OUT</sub> )       | 8 A         |

| Operating frequency   | (Fsw)                     | 400 kHz     |

A buck converter produces input voltage ( $V_{IN}$ ) pulses that are LC filtered to produce a lower dc output voltage ( $V_{OUT}$ ). The output voltage can be changed by modifying the on time relative to the switching period (T) or switching frequency. The ratio of high side switch on time to the switching period is called duty cycle (D). Duty cycle can also be calculated using  $V_{OUT}$ ,  $V_{IN}$ , the low side switch voltage drop  $V_{LSD}$ , and the High side switch voltage drop  $V_{HSD}$ .

$$F = \frac{1}{T}$$

(eq. 6)

$$D = \frac{T_{ON}}{T}(-D) = \frac{T_{OFF}}{T}$$

(eq. 7)

$$D = \frac{V_{OUT} + V_{LSD}}{V_{IN} - V_{HSD} + V_{LSD}} \approx D = \frac{V_{OUT}}{V_{IN}}$$

$$\Rightarrow 27.5\% = \frac{3.3 \text{ V}}{12 \text{ V}}$$

(eq. 8)

The ratio of ripple current to maximum output current simplifies the equations used for inductor selection. The formula for this is given in Equation 9.

$$ra = \frac{\Delta I}{I_{OUT}}$$

(eq. 9)

The designer should employ a rule of thumb where the percentage of ripple current in the inductor lies between 10% and 40%. When using ceramic output capacitors the ripple current can be greater thus a user might select a higher ripple current, but when using electrolytic capacitors a lower ripple current will result in lower output ripple. Now, acceptable values of inductance for a design can be calculated using Equation 10.

$$\begin{split} L &= \frac{V_{OUT}}{I_{OUT} \cdot ra \cdot F_{SW}} \cdot (1 - D) \rightarrow 3.3 \, \mu H \\ &= \frac{3.3 \, V}{8 \, A \cdot 23\% \cdot 400 \, kHz} \cdot (1 - 27.5\%) \end{split}$$

(eq. 10)

The relationship between ra and L for this design example is shown in Figure 42.

Figure 42. Ripple Current Ratio vs. Inductance

To keep within the bounds of the parts maximum rating, calculate the RMS current and peak current.

$$I_{RMS} = I_{OUT} \cdot \sqrt{1 + \frac{ra^2}{12}} \rightarrow 8.02 \text{ A}$$

$$= 8 \text{ A} \cdot \sqrt{1 + \frac{(0.23)^2}{12}}$$

(eq. 11)

$$I_{PK} = I_{OUT} \cdot \left(1 + \frac{ra}{2}\right) \rightarrow 8.92 \text{ A} = 8 \text{ A} \cdot \left(1 + \frac{(0.23)}{2}\right)$$

(eq. 12)

An inductor for this example would be around 3.3  $\mu$ H and should support an rms current of 8.02 A and a peak current of 8.92 A.

The final selection of an output inductor has both mechanical and electrical considerations. From a mechanical perspective, smaller inductor values generally correspond to smaller physical size. Since the inductor is often one of the largest components in the regulation system, a minimum inductor value is particularly important in space—constrained applications. From an electrical perspective, the maximum current slew rate through the output inductor for a buck regulator is given by Equation 13.

$$\mathsf{SlewRate}_{\mathsf{LOUT}} = \frac{\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}}{\mathsf{L}_{\mathsf{OUT}}} \rightarrow 2.6 \frac{\mathsf{A}}{\mu \mathsf{s}} = \frac{12 \; \mathsf{V} - 3.3 \; \mathsf{V}}{3.3 \; \mu \mathsf{H}} \tag{eq. 13}$$

This equation implies that larger inductor values limit the regulator's ability to slew current through the output inductor in response to output load transients. Consequently, output capacitors must supply the load current until the inductor current reaches the output load current level. This results in larger values of output capacitance to maintain tight output voltage regulation. In contrast, smaller values of inductance increase the regulator's maximum achievable slew rate and decrease the necessary capacitance, at the expense of higher ripple current. The peak—to—peak ripple current for the NCP3011 is given by the following equation:

$$I_{PP} = \frac{V_{OUT}(1 - D)}{L_{OUT} \cdot F_{SW}}$$

(eq. 14)

Ipp is the peak to peak current of the inductor. From this equation it is clear that the ripple current increases as L<sub>OUT</sub> decreases, emphasizing the trade-off between dynamic response and ripple current.

The power dissipation of an inductor consists of both copper and core losses. The copper losses can be further categorized into dc losses and ac losses. A good first order approximation of the inductor losses can be made using the DC resistance as they usually contribute to 90% of the losses of the inductor shown below:

$$LP_{CLI} = I_{RMS}^{2} \cdot DCR$$

(eq. 15)

The core losses and ac copper losses will depend on the geometry of the selected core, core material, and wire used. Most vendors will provide the appropriate information to make accurate calculations of the power dissipation then the total inductor losses can be capture buy the equation below:

$$LP_{tot} = LP_{CU DC} + LP_{CU AC} + LP_{Core}$$

(eq. 16)

## **Input Capacitor Selection**

The input capacitor has to sustain the ripple current produced during the on time of the upper MOSFET, so it must have a low ESR to minimize the losses. The RMS value of this ripple is:

$$lin_{RMS} = I_{OUT} \cdot \sqrt{D \cdot (1 - D)}$$

(eq. 17)

D is the duty cycle,  $Iin_{RMS}$  is the input RMS current, and  $I_{OUT}$  is the load current.

The equation reaches its maximum value with D=0.5. Loss in the input capacitors can be calculated with the following equation:

$$P_{CIN} = ESR_{CIN} \cdot \left(I_{IN-RMS}\right)^{2}$$

(eq. 18)

$P_{CIN}$  is the power loss in the input capacitors and  $ESR_{CIN}$  is the effective series resistance of the input capacitance. Due to large dI/dt through the input capacitors, electrolytic or ceramics should be used. If a tantalum must be used, it must by surge protected. Otherwise, capacitor failure could occur.

#### Input Start-up Current

To calculate the input startup current, the following equation can be used.

$$I_{\text{INRUSH}} = \frac{C_{\text{OUT}} \cdot V_{\text{OUT}}}{t_{\text{SS}}}$$

(eq. 19)

$I_{inrush}$  is the input current during startup,  $C_{OUT}$  is the total output capacitance,  $V_{OUT}$  is the desired output voltage, and  $t_{SS}$  is the soft start interval. If the inrush current is higher than the steady state input current during max load, then the input fuse should be rated accordingly, if one is used.

### **Output Capacitor Selection**

The important factors to consider when selecting an output capacitor is dc voltage rating, ripple current rating, output ripple voltage requirements, and transient response requirements.

The output capacitor must be rated to handle the ripple current at full load with proper derating. The RMS ratings given in datasheets are generally for lower switching frequency than used in switch mode power supplies but a multiplier is usually given for higher frequency operation. The RMS current for the output capacitor can be calculated below:

$$Co_{RMS} = I_O \cdot \frac{ra}{\sqrt{12}}$$

(eq. 20)

The maximum allowable output voltage ripple is a combination of the ripple current selected, the output capacitance selected, the equivalent series inductance (ESL) and ESR.

The main component of the ripple voltage is usually due to the ESR of the output capacitor and the capacitance selected.

$$V_{ESR\_C} = I_O \cdot ra \cdot \left(ESR_{Co} + \frac{1}{8 \cdot F_{SW} \cdot Co}\right)$$

(eq. 21)

The ESL of capacitors depends on the technology chosen but tends to range from 1 nH to 20 nH where ceramic capacitors have the lowest inductance and electrolytic capacitors then to have the highest. The calculated contributing voltage ripple from ESL is shown for the switch on and switch off below:

$$V_{ESLON} = \frac{ESL \cdot I_{PP} \cdot F_{SW}}{D}$$

(eq. 22)

$$V_{ESLOFF} = \frac{ESL \cdot I_{PP} \cdot F_{SW}}{(1 - D)}$$

(eq. 23)

The output capacitor is a basic component for the fast response of the power supply. In fact, during load transient, for the first few microseconds it supplies the current to the load. The controller immediately recognizes the load transient and sets the duty cycle to maximum, but the current slope is limited by the inductor value.

During a load step transient the output voltage initially drops due to the current variation inside the capacitor and the ESR (neglecting the effect of the effective series inductance (ESL)).

$$\Delta V_{OUT-ESR} = \Delta I_{TRAN} \cdot ESR_{Co}$$

(eq. 24)

A minimum capacitor value is required to sustain the current during the load transient without discharging it. The voltage drop due to output capacitor discharge is approximated by the following equation:

$$\Delta V_{OUT-DISCHG} = \frac{\left(I_{TRAN}\right)^2 \cdot L_{OUT}}{C_{OUT} \cdot \left(V_{IN} - V_{OUT}\right)} \quad (eq. 25)$$

In a typical converter design, the ESR of the output capacitor bank dominates the transient response. It should be noted that  $\Delta$ VOUT-DISCHARGE and  $\Delta$ VOUT-ESR are out of phase with each other, and the larger of these two voltages will determine the maximum deviation of the output voltage (neglecting the effect of the ESL).

Conversely during a load release, the output voltage can increase as the energy stored in the inductor dumps into the output capacitor. The ESR contribution from Equation 21 still applies in addition to the output capacitor charge which is approximated by the following equation:

$$\Delta V_{OUT-CHG} = \frac{\left(I_{TRAN}\right)^2 \cdot L_{OUT}}{C_{OUT} \cdot V_{OUT}}$$

(eq. 26)

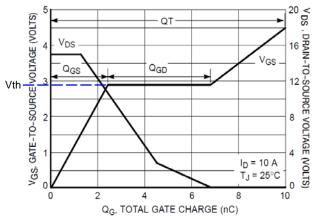

### **Power MOSFET Selection**

Power dissipation, package size, and the thermal environment drive MOSFET selection. To adequately select the correct MOSFETs, the design must first predict its power dissipation. Once the dissipation is known, the thermal impedance can be calculated to prevent the specified maximum junction temperatures from being exceeded at the highest ambient temperature.

Power dissipation has two primary contributors: conduction losses and switching losses. The control or high-side MOSFET will display both switching and conduction losses. The synchronous or low-side MOSFET will exhibit only conduction losses because it switches into nearly zero voltage. However, the body diode in the synchronous MOSFET will suffer diode losses during the non-overlap time of the gate drivers.

Starting with the high-side or control MOSFET, the power dissipation can be approximated from:

$$P_{D \text{ CONTROL}} = P_{COND} + P_{SW \text{ TOT}}$$

(eq. 27)

The first term is the conduction loss of the high-side MOSFET while it is on.

$$P_{COND} = (I_{RMS\ CONTROL})^2 \cdot R_{DS(on)\ CONTROL}$$

(eq. 28)

Using the ra term from Equation 9, I<sub>RMS</sub> becomes:

$$I_{RMS\_CONTROL} = I_{OUT} \cdot \sqrt{D \cdot \left(1 + \left(\frac{ra^2}{12}\right)\right)}$$

(eq. 29)

The second term from Equation 27 is the total switching loss and can be approximated from the following equations.

$$P_{SW TOT} = P_{SW} + P_{DS} + P_{RR}$$

(eq. 30)

The first term for total switching losses from Equation 30 includes the losses associated with turning the control MOSFET on and off and the corresponding overlap in drain voltage and current.

$$\begin{split} \mathbf{P}_{\text{SW}} &= \mathbf{P}_{\text{TON}} + \mathbf{P}_{\text{TOFF}} \\ &= \frac{1}{2} \cdot \left( \mathbf{I}_{\text{OUT}} \cdot \mathbf{V}_{\text{IN}} \cdot f_{\text{SW}} \right) \cdot \left( \mathbf{t}_{\text{ON}} + \mathbf{t}_{\text{OFF}} \right) \end{split} \tag{eq. 31}$$

where:

$$t_{ON} = \frac{Q_{GD}}{I_{G1}} = \frac{Q_{GD}}{\left(V_{BST} - V_{TH}\right) / \left(R_{HSPU} + R_{G}\right)} \quad \text{(eq. 32)}$$

and:

$$t_{OFF} = \frac{Q_{GD}}{I_{G2}} = \frac{Q_{GD}}{(V_{BST} - V_{TH})/(R_{HSPD} + R_G)}$$

(eq. 33)

Next, the MOSFET output capacitance losses are caused by both the control and synchronous MOSFET but are dissipated only in the control MOSFET.

$$P_{DS} = \frac{1}{2} \cdot Q_{OSS} \cdot V_{IN} \cdot f_{SW}$$

(eq. 34)

Finally the loss due to the reverse recovery time of the body diode in the *synchronous* MOSFET is shown as follows:

$$P_{RR} = Q_{RR} \cdot V_{IN} \cdot f_{SW} \qquad (eq. 35)$$

The low-side or synchronous MOSFET turns on into zero volts so switching losses are negligible. Its power dissipation only consists of conduction loss due to  $R_{DS(on)}$  and body diode loss during the non-overlap periods.

$$P_{D \text{ SYNC}} = P_{COND} + P_{BODY}$$

(eq. 36)

Conduction loss in the low-side or synchronous MOSFET is described as follows:

$$P_{COND} = (I_{RMS\_SYNC})^2 \cdot R_{DS(on)\_SYNC} \quad (eq. 37)$$

where:

$$I_{RMS\_SYNC} = I_{OUT} \cdot \sqrt{(1 - D) \cdot \left(1 + \left(\frac{ra^2}{12}\right)\right)}$$

(eq. 38)

The body diode losses can be approximated as:

$$P_{BODY} = V_{FD} \cdot I_{OUT} \cdot f_{SW} \cdot (NOL_{LH} + NOL_{HL}) \text{ (eq. 39)}$$

Figure 43. MOSFET Switching Characteristics

$I_{G1}$ : output current from the high-side gate drive (HSDR)  $I_{G2}$ : output current from the low-side gate drive (LSDR)  $f_{SW}$ : switching frequency of the converter.

$V_{BST}$ : gate drive voltage for the high-side drive, typically 7.5 V.

Q<sub>GD</sub>: gate charge plateau region, commonly specified in the MOSFET datasheet

$V_{TH}$ : gate-to-source voltage at the gate charge plateau region

QOSS: MOSFET output gate charge specified in the data sheet

Q<sub>RR</sub>: reverse recovery charge of the low-side or synchronous MOSFET, specified in the datasheet

$R_{DS(on)\_CONTROL}$ : on resistance of the high–side, or control, MOSFET

$R_{DS(on)\_SYNC}$ : on resistance of the low–side, or synchronous, MOSFET

$NOL_{LH}$ : dead time between the LSDR turning off and the HSDR turning on, typically 85 ns

NOL<sub>HL</sub>: dead time between the HSDR turning off and the LSDR turning on, typically 75 ns

Once the MOSFET power dissipations are determined, the designer can calculate the required thermal impedance for each device to maintain a specified junction temperature at the worst case ambient temperature. The formula for calculating the junction temperature with the package in free air is:

$$T_{J} = T_A + P_D \cdot R_{\theta,JA}$$

T<sub>J</sub>: Junction Temperature

T<sub>A</sub>: Ambient Temperature

P<sub>D</sub>: Power Dissipation of the MOSFET under analysis

$R_{\theta JA} :$  Thermal Resistance Junction–to–Ambient of the MOSFET's package

As with any power design, proper laboratory testing should be performed to insure the design will dissipate the required power under worst case operating conditions. Variables considered during testing should include maximum ambient temperature, minimum airflow, maximum input voltage, maximum loading, and component variations (i.e. worst case MOSFET R<sub>DS(on)</sub>).

Another consideration during MOSFET selection is their delay times. Turn-on and turn-off times must be short enough to prevent cross conduction. If not, there will be conduction from the input through both MOSFETs to ground. Therefore, the following conditions must be met.

$$\label{eq:td(ON)_CONTROL} t_{\rm d(OFF)_SYNC} + t_{\rm f_SYNC}$$

and (eq. 40)

$$t_{(ON)\_SYNC} + NOL_{HL} > t_{d(OFF)\_CONTROL} + t_{f\_CONTROL}$$

The MOSFET parameters,  $t_{d(ON)}$ ,  $t_r$ ,  $t_{d(OFF)}$  and  $t_f$  are can be found in their appropriate datasheets for specific conditions. NOLLH and NOLHL are the dead times which were described earlier and are 85 ns and 75 ns, respectively.

### **Feedback and Compensation**

The NCP3011 is a voltage mode buck convertor with a transconductance error amplifier compensated by an external compensation network. Compensation is needed to achieve accurate output voltage regulation and fast transient

response. The goal of the compensation circuit is to provide a loop gain function with the highest crossing frequency and adequate phase margin (minimally 45°). The transfer function of the power stage (the output LC filter) is a double pole system. The resonance frequency of this filter is expressed as follows:

$$f_{PO} = \frac{1}{2 \cdot \pi \cdot \sqrt{L \cdot C_{OUT}}}$$

(eq. 41)

Parasitic Equivalent Series Resistance (ESR) of the output filter capacitor introduces a high frequency zero to the filter network. Its value can be calculated by using the following equation:

$$f_{\rm Z0} = \frac{1}{2 \cdot \pi \cdot {\rm C_{OUT} \cdot ESR}}$$

(eq. 42)

The main loop zero crossover frequency fo can be chosen to be 1/10 - 1/5 of the switching frequency. Table 2 shows the three methods of compensation.

**Table 2. COMPENSATION TYPES**

| Zero Crossover Frequency Condition | Compensation Type                                                                                  | Typical Output Capacitor Type |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------|--|--|

| $f_{P0} < f_{Z0} < f_0 < f_S/2$    | $f_{P0} < f_{Z0} < f_0 < f_S/2$ Type II Elec $f_{P0} < f_0 < f_{Z0} < f_S/2$ Type III Method I Tar |                               |  |  |

| $f_{P0} < f_0 < f_{Z0} < f_S/2$    |                                                                                                    |                               |  |  |

| $f_{P0} < f_0 < f_{S/2} < f_{Z0}$  | Type III Method II                                                                                 | Ceramic                       |  |  |

### Compensation Type II

This compensation is suitable for electrolytic capacitors. Components of the Type II compensation (Figure 45) network can be specified by the following equations:

Figure 45. Type II Compensation

$$\mathsf{R}_{\mathsf{C1}} = \frac{2 \cdot \pi \cdot f_0 \cdot \mathsf{L} \cdot \mathsf{V}_{\mathsf{RAMP}} \cdot \mathsf{V}_{\mathsf{OUT}}}{\mathsf{ESR} \cdot \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{V}_{\mathsf{ref}} \cdot \mathsf{gm}} \quad \text{ (eq. 43)}$$

$$C_{C1} = \frac{1}{0.75 \cdot 2 \cdot \pi \cdot f_{P0} \cdot R_{C1}}$$

(eq. 44)

$$C_{C2} = \frac{1}{\pi \cdot R_{C1} \cdot f_S}$$

(eq. 45)

$$R1 = \frac{V_{OUT} - V_{ref}}{V_{ref}} \cdot R2$$

(eq. 46)

$V_{RAMP}$  is the peak-to-peak voltage of the oscillator ramp and gm is the transconductance error amplifier gain. Capacitor CC2 is optional.

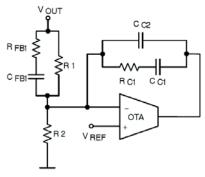

### **Compensation Type III**

Tantalum and ceramics capacitors have lower ESR than electrolytic, so the zero of the output LC filter goes to a higher frequency above the zero crossover frequency. This requires a Type III compensation network as shown in Figure 46.

There are two methods to select the zeros and poles of this compensation network. Method I is ideal for tantalum output capacitors, which have a higher ESR than ceramic:

Figure 46. Type III Compensation

$$f_{71} = 0.75 \cdot f_{P0}$$

(eq. 47)

$$f_{Z2} = f_{P0}$$

(eq. 48)

$$f_{P2} = f_{Z0}$$

(eq. 49)

$$f_{P3} = \frac{f_{S}}{2}$$

(eq. 50)

Method II is better suited for ceramic capacitors that typically have the lowest ESR available:

$$f_{Z2} = f_0 \cdot \sqrt{\frac{1 - \sin\theta \max}{1 + \sin\theta \max}}$$

(eq. 51)

$$f_{P2} = f_0 \cdot \sqrt{\frac{1 + \sin \theta \max}{1 - \sin \theta \max}}$$

(eq. 52)

$$f_{Z1} = 0.5 \cdot f_{Z2}$$

(eq. 53)

$$f_{P3} = 0.5 \cdot f_{S}$$

(eq. 54)

$\theta$ max is the desired maximum phase margin at the zero crossover frequency,  $f_0$ . It should be  $45^{\circ} - 75^{\circ}$ . Convert degrees to radians by the formula:

$$\theta \max = \theta \max_{\text{degress}} \cdot \left(\frac{2 \cdot \pi}{360}\right)$$

: Units = radians (eq. 55)

The remaining calculations are the same for both methods.

$$R_{C1} > \frac{2}{gm}$$

(eq. 56)

$$C_{C1} = \frac{1}{2 \cdot \pi \cdot f_{71} \cdot R_{C1}}$$

(eq. 57)

$$C_{C2} = \frac{1}{2 \cdot \pi \cdot f_{P3} \cdot R_{C1}}$$

(eq. 58)

$$C_{\text{FB1}} = \frac{2 \cdot \pi \cdot f_0 \cdot L \cdot V_{\text{RAMP}} \cdot C_{\text{OUT}}}{V_{\text{IN}} \cdot R_{\text{C1}}} \qquad \text{(eq. 59)}$$

$$R_{FB1} = \frac{1}{2\pi \cdot C_{FB1} \cdot f_{P2}}$$

(eq. 60)

$$R1 = \frac{1}{2 \cdot \pi \cdot C_{FB1} \cdot f_{Z2}} - R_{FB1}$$

(eq. 61)

$$R2 = \frac{V_{ref}}{V_{OUT} - V_{ref}} \cdot R1$$

(eq. 62)

If the equation in Equation 63 is not true, then a higher value of  $R_{C1}$  must be selected.

$$\frac{\text{R1} \cdot \text{R2} \cdot \text{R}_{\text{FB1}}}{\text{R1} \cdot \text{R}_{\text{FB1}} + \text{R2} \cdot \text{R}_{\text{FB1}} + \text{R1} \cdot \text{R2}} > \frac{1}{\text{gm}} (\text{eq. 63})$$

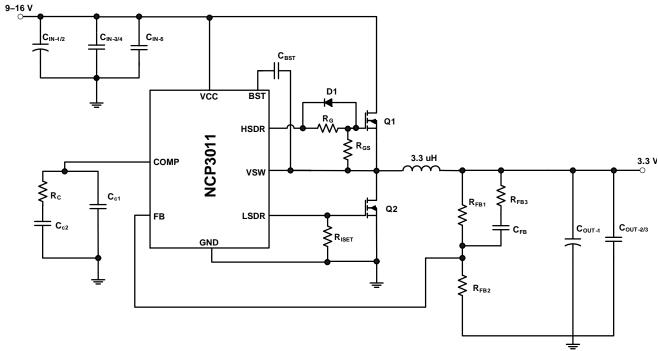

### **TYPICAL APPLICATION CIRCUIT**

Figure 47. Typical Application,  $V_{IN} = 9 - 16 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $I_{OUT} = 6 \text{ A}$

| Reference Designator | Value     |

|----------------------|-----------|

| CIN-1                | 470 μF    |

| CIN-2                | 470 μF    |

| CIN-3                | 22 μF     |

| CIN-4                | 22 μF     |

| CIN-5                | 1 μF      |

| CC1                  | 56 pF     |

| CC2                  | 12 nF     |

| CFB                  | 1.0 nF    |

| COUT1                | 470 μF    |

| COUT2                | 22 μF     |

| COUT3                | 22 μF     |

| CBST                 | 0.1 μF    |

| RC                   | 4.81 kΩ   |

| RG                   | 0 Ω       |

| RGS                  | 1.0 kΩ    |

| RISET                | 22.1 kΩ   |

| RFB1                 | 3.16 kΩ   |

| RFB2                 | 1.0 kΩ    |

| RFB3                 | 1.0 kΩ    |

| Q1                   | NTMS4816N |

| Q2                   | NTMS4816N |

| D1                   | BAT54     |

## **Special Note**

The NCP3011/NCV3011 are dedicated for current sensing across high–side MOSFET via VCC pin and VSW pin, as shown in Figure 36. Therefore, the VCC pin must connect to the VIN voltage, i.e., the drain of high–side MOSFET as shown in Figure 47 above. In other words, the NCP3011/NCV3011 does not support separated VCC voltage and VIN voltage, regardless any current limit setting in LSDR pin. Using a lower VCC voltage than the VIN voltage, such as VCC=12V and VIN=20V, may damage the NCP3011/NCV3011. Disconnecting the VCC pin supply, while VIN is still presented and EN is asserted, risks the NCP3011/NCV3011 of being damaged as well.

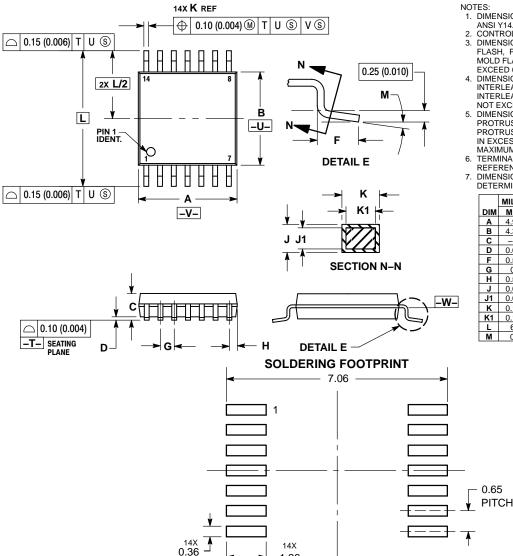

### PACKAGE DIMENSIONS

### TSSOP-14 CASE 948G **ISSUE C**

- DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER

- DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

- DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION, ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.90        | 5.10 | 0.193     | 0.200 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.20 |           | 0.047 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.75 | 0.020     | 0.030 |

| O   | 0.65 BSC    |      | 0.026 BSC |       |

| Ξ   | 0.50        | 0.60 | 0.020     | 0.024 |

| _   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| Κ   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| Г   | 6.40 BSC    |      | 0.252     | BSC   |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

1.26

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

**DIMENSIONS: MILLIMETERS**

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

NCP3011DTBR2G NCV3011DTBR2G