# Single Supply 16-Bit, 100ksps, Sampling ADCs

#### **FEATURES**

Sample Rate: 100ksps

Complete 16-Bit Solution on a Single 5V Supply

Unipolar Input Range: 0V to 4V (LTC1605-1)

Bipolar Input Range: ±4V (LTC1605-2)

Power Dissipation: 55mW Typ

Signal-to-Noise Ratio: 86dB Typ

Operates with Internal or External Reference

Internal Synchronized Clock

28-Pin SSOP Package

#### **APPLICATIONS**

- Industrial Process Control

- Multiplexed Data Acquisition Systems

- High Speed Data Acquisition for PCs

- Digital Signal Processing

#### DESCRIPTION

The LTC®1605-1/LTC1605-2 are 100ksps, sampling 16-bit A/D converters that draw only 55mW (typical) from a single 5V supply. These easy-to-use devices include a sample-and-hold, precision reference, switched capacitor successive approximation A/D and trimmed internal clock.

The LTC1605-1's input range is 0V to 4V while the LTC1605-2's input range is ±4V. An external reference can be used if greater accuracy over temperature is needed.

The ADC has a microprocessor compatible, 16-bit or two byte parallel output port. A convert start input and a data ready signal (BUSY) ease connections to FIFOs, DSPs and microprocessors.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

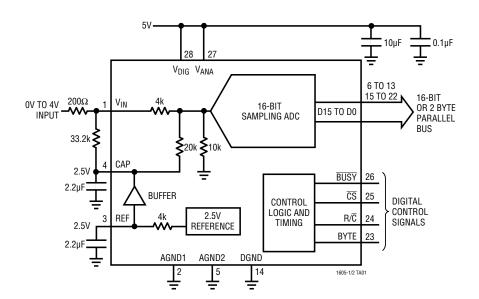

## TYPICAL APPLICATION

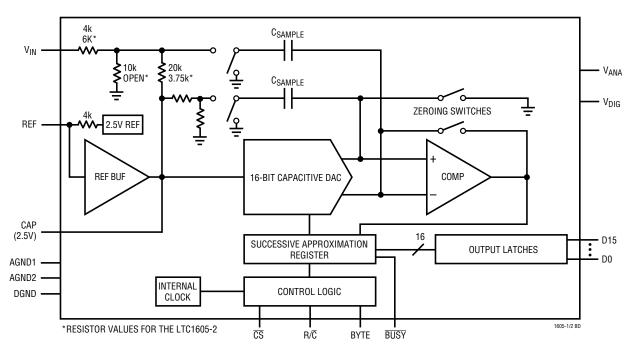

#### LTC1605-1 Low Power, 100kHz, 16-Bit Sampling ADC on 5V Supply

# **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| V <sub>ΔNI</sub> Δ        | 7V                               |

|---------------------------|----------------------------------|

|                           | 0.3V                             |

| V <sub>DIG</sub>          | 7V                               |

| Ground Voltage Difference | }                                |

| DGND, AGND1 and AGN       | JD2±0.3V                         |

| Analog Inputs (Note 3)    |                                  |

| V <sub>IN</sub>           | ±25V                             |

| CAP                       | $V_{ANA}$ + 0.3V to AGND2 – 0.3V |

|                           | Indefinite Short to AGND2        |

|                           | Momentary Short to VANA          |

| Digital Input Voltage (Note 4) V<br>Digital Output Voltage V <sub>DGND</sub> – |              |

|--------------------------------------------------------------------------------|--------------|

| Power Dissipation                                                              |              |

| Operating Ambient Temperature Rang                                             | ge           |

| LTC1605-1C/LTC1605-2C                                                          | 0°C to 70°C  |

| LTC1605-1I/LTC1605-2I                                                          | 40°C to 85°C |

| Storage Temperature Range                                                      |              |

| Lead Temperature (Soldering, 10 sec)                                           | )300°C       |

|                                                                                |              |

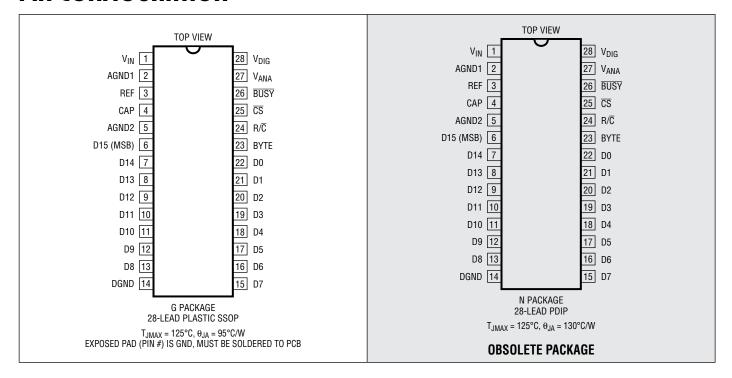

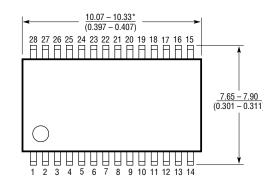

# PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|------------------|-------------------|--------------|----------------------|-------------------|

| LTC1605-1CG#PBF  | LTC1605-1CG#TRPBF | LTC1605-1CG  | 28-Lead Plastic SSOP | 0°C to 70°C       |

| LTC1605-1IG#PBF  | LTC1605-1IG#TRPBF | LTC1605-1IG  | 28-Lead Plastic SSOP | -40°C to 85°C     |

| LTC1605-2CG#PBF  | LTC1605-2CG#TRPBF | LTC1605-2CG  | 28-Lead Plastic SSOP | 0°C to 70°C       |

| LTC1605-2IG#PBF  | LTC1605-2IG#TRPBF | LTC1605-2IG  | 28-Lead Plastic SSOP | -40°C to 85°C     |

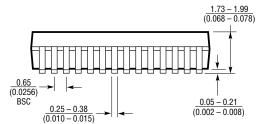

|                  |                   | OBSOLETE F   | PACKAGE              | ·                 |

| LTC1605-1CN#PBF  | LTC1605-1CN#TRPBF | LTC1605-1CN  | 28-Lead PDIP         | 0°C to 70°C       |

| LTC1605-1IN#PBF  | LTC1605-1IN#TRPBF | LTC1605-1IN  | 28-Lead PDIP         | -40°C to 85°C     |

| LTC1605-2CN#PBF  | LTC1605-2CN#TRPBF | LTC1605-2CN  | 28-Lead PDIP         | 0°C to 70°C       |

| LTC1605-2IN#PBF  | LTC1605-2IN#TRPBF | LTC1605-2IN  | 28-Lead PDIP         | -40°C to 85°C     |

Consult factory for Military grade parts.

Consult LTC Marketing for parts specified with wider operating temperature ranges.

Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part markings, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

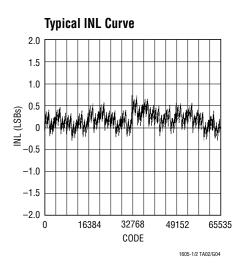

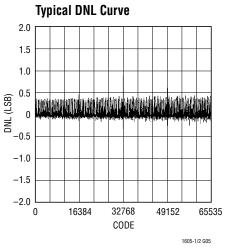

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . With external reference (Notes 5, 6).

| PARAMETER                                                                         | CONDITIONS                           |   | MIN | TYP | MAX   | UNITS              |

|-----------------------------------------------------------------------------------|--------------------------------------|---|-----|-----|-------|--------------------|

| Resolution                                                                        |                                      | • | 16  |     |       | Bits               |

| No Missing Codes                                                                  |                                      | • | 15  |     |       | Bits               |

| Transition Noise                                                                  |                                      |   |     | 1   |       | LSB <sub>RMS</sub> |

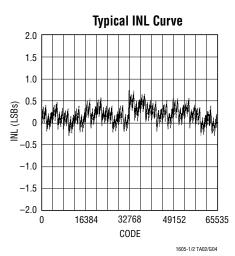

| Integral Linearity Error                                                          | (Note 7)                             | • |     |     | ±3    | LSB                |

| Zero Error                                                                        | Ext. Reference = 2.5V (Note 8)       | • |     |     | ±10   | mV                 |

| Zero Error Drift                                                                  |                                      |   |     | ±2  |       | ppm/°C             |

| Full-Scale Error Drift                                                            |                                      |   |     | ±7  |       | ppm/°C             |

| Full-Scale Error                                                                  | Ext. Reference = 2.5V (Notes 12, 13) | • |     |     | ±0.50 | %                  |

| Full-Scale Error Drift                                                            | Ext. Reference = 2.5V                |   |     | ±2  |       | ppm/°C             |

| Power Supply Sensitivity<br>V <sub>ANA</sub> = V <sub>DIG</sub> = V <sub>DD</sub> | V <sub>DD</sub> = 5V ±5% (Note 9)    |   |     |     | ±8    | LSB                |

# **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL          | PARAMETER                   | CONDITIONS                                                                                                                              |   | MIN | TYP          | MAX | UNITS |

|-----------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------|-----|-------|

| V <sub>IN</sub> | Analog Input Range (Note 9) | $ \begin{array}{l} 4.75V \leq V_{ANA} \leq 5.25V, \ 4.75V \leq V_{DIG} \leq 5.25V \\ \text{LTC1605-1} \\ \text{LTC1605-2} \end{array} $ | • |     | 0 to 4<br>±4 |     | V     |

| C <sub>IN</sub> | Analog Input Capacitance    |                                                                                                                                         |   |     | 10           |     | pF    |

| R <sub>IN</sub> | Analog Input Impedance      |                                                                                                                                         |   |     | 10           |     | kΩ    |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Notes 5, 14)

| SYMBOL    | PARAMETER                            | CONDITIONS                                                                     | MIN TYP MAX                 | UNITS          |

|-----------|--------------------------------------|--------------------------------------------------------------------------------|-----------------------------|----------------|

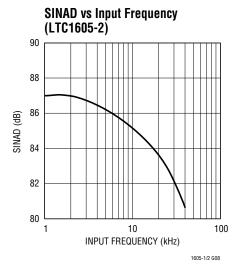

| S/(N + D) | Signal-to-(Noise + Distortion) Ratio | 1kHz Input Signal (Note 14)<br>10kHz Input Signal<br>20kHz, –60dB Input Signal | 87<br>85<br>30              | dB<br>dB<br>dB |

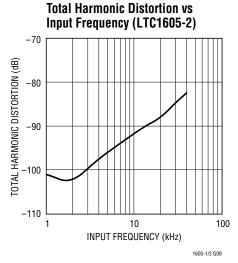

| THD       | Total Harmonic Distortion            | 1kHz Input Signal, First 5 Harmonics<br>10kHz Input Signal, First 5 Harmonics  | -101<br>-92                 | dB<br>dB       |

|           | Peak Harmonic or Spurious Noise      | 1kHz Input Signal<br>10kHz Input Signal                                        | -101<br>-92                 | dB<br>dB       |

|           | Full-Power Bandwidth                 | (Note 15)                                                                      | 275                         | kHz            |

|           | Aperture Delay                       |                                                                                | 40                          | ns             |

|           | Aperture Jitter                      |                                                                                | Sufficient to Meet AC Specs |                |

|           | Transient Response                   | Full-Scale Step (Note 9)                                                       | 2                           | μs             |

|           | Overvoltage Recovery                 | (Note 16)                                                                      | 150                         | ns             |

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| PARAMETER                                          | CONDITIONS                     |   | MIN   | TYP   | MAX   | UNITS  |

|----------------------------------------------------|--------------------------------|---|-------|-------|-------|--------|

| V <sub>REF</sub> Output Voltage                    | I <sub>OUT</sub> = 0           | • | 2.470 | 2.500 | 2.520 | V      |

| V <sub>REF</sub> Output Tempco                     | I <sub>OUT</sub> = 0           |   |       | ±5    |       | ppm/°C |

| Internal Reference Source Current                  |                                |   |       | 1     |       | μA     |

| External Reference Voltage for Specified Linearity | (Notes 9, 10)                  |   | 2.30  | 2.50  | 2.70  | V      |

| External Reference Current Drain                   | Ext. Reference = 2.5V (Note 9) | • |       |       | 100   | μА     |

| CAP Output Voltage                                 | I <sub>OUT</sub> = 0           |   |       | 2.50  |       | V      |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL              | PARAMETER                         | CONDITIONS                        |                        |   | MIN | TYP  | MAX | UNITS |

|---------------------|-----------------------------------|-----------------------------------|------------------------|---|-----|------|-----|-------|

| $\overline{V_{IH}}$ | High Level Input Voltage          | VDD = 5.25V                       |                        | • | 2.4 |      |     | V     |

| $V_{IL}$            | Low Level Input Voltage           | $V_{DD} = 4.75V$                  |                        | • |     |      | 0.8 | V     |

| I <sub>IN</sub>     | Digital Input Current             | $V_{IN} = 0V \text{ to } V_{DD}$  |                        | • |     |      | ±10 | μА    |

| C <sub>IN</sub>     | Digital Input Capacitance         |                                   |                        |   |     | 5    |     | pF    |

| $V_{OH}$            | High Level Output Voltage         | V <sub>DD</sub> = 4.75V           | $I_0 = -10\mu A$       |   |     | 4.5  |     | V     |

|                     |                                   |                                   | $I_0 = -200 \mu A$     | • | 4.0 |      |     | V     |

| $V_{OL}$            | Low Level Output Voltage          | V <sub>DD</sub> = 4.75V           | I <sub>0</sub> = 160μA |   |     | 0.05 |     | V     |

|                     |                                   |                                   | I <sub>0</sub> = 1.6mA | • |     | 0.10 | 0.4 | V     |

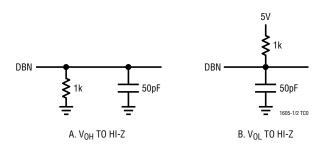

| I <sub>OZ</sub>     | Hi-Z Output Leakage D15 to D0     | $V_{OUT} = 0V \text{ to } V_{DD}$ | , CS High              | • |     |      | ±10 | μА    |

| $C_{OZ}$            | Hi-Z Output Capacitance D15 to D0 | CS High (Note 9)                  |                        | • |     |      | 15  | pF    |

| I <sub>SOURCE</sub> | Output Source Current             | V <sub>OUT</sub> = 0V             |                        |   |     | -10  |     | mA    |

| I <sub>SINK</sub>   | Output Sink Current               | $V_{OUT} = V_{DD}$                |                        |   |     | 10   |     | mA    |

LINEAR

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 5)

| SYMBOL                   | PARAMETER                          | CONDITIONS            |   | MIN | TYP | MAX | UNITS |

|--------------------------|------------------------------------|-----------------------|---|-----|-----|-----|-------|

| f <sub>SAMPLE(MAX)</sub> | Maximum Sampling Frequency         |                       | • | 100 |     |     | kHz   |

| t <sub>CONV</sub>        | Conversion Time                    |                       | • |     |     | 8   | μs    |

| t <sub>ACQ</sub>         | Acquisition Time                   |                       | • |     |     | 2   | μs    |

| $\overline{t_1}$         | Convert Pulse Width                | (Note 11)             | • | 40  |     |     | ns    |

| $\overline{t_2}$         | Data Valid Delay After R/C↓        | (Note 9)              | • |     |     | 8   | μs    |

| t <sub>3</sub>           | BUSY Delay from R/C↓               | C <sub>L</sub> = 50pF | • |     |     | 65  | ns    |

| $\overline{t_4}$         | BUSY Low                           |                       |   |     |     | 8   | μs    |

| t <sub>5</sub>           | BUSY Delay After End of Conversion |                       |   |     | 220 |     | ns    |

| $\overline{t_6}$         | Aperture Delay                     |                       |   |     | 40  |     | ns    |

| $\overline{t_7}$         | Bus Relinquish Time                |                       | • | 10  | 35  | 83  | ns    |

| t <sub>8</sub>           | BUSY Delay After Data Valid        |                       | • | 50  | 200 |     | ns    |

| t <sub>9</sub>           | Previous Data Valid After R/C↓     |                       |   |     | 7.4 |     | μs    |

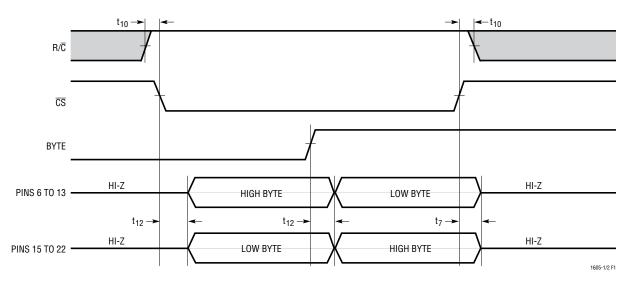

| t10                      | R/C to CS Setup Time               | (Notes 9, 10)         |   | 10  |     |     | ns    |

| t11                      | Time Between Conversions           |                       |   | 10  |     |     | μs    |

| t12                      | Bus Access and Byte Delay          | (Notes 9, 10)         |   | 10  |     | 83  | ns    |

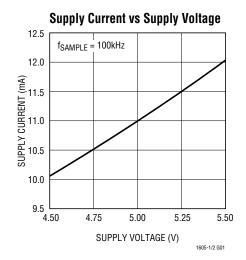

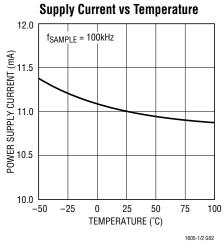

# **POWER REQUIREMENTS**The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL              | PARAMETER               | CONDITIONS    |   | MIN  | TYP | MAX  | UNITS |

|---------------------|-------------------------|---------------|---|------|-----|------|-------|

| $\overline{V_{DD}}$ | Positive Supply Voltage | (Notes 9, 10) |   | 4.75 |     | 5.25 | V     |

| $I_{DD}$            | Positive Supply Current |               | • |      | 11  | 16   | mA    |

| P <sub>DIS</sub>    | Power Dissipation       |               |   |      | 55  | 80   | mW    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All voltage values are with respect to ground with DGND, AGND1 and AGND2 wired together (unless otherwise noted).

**Note 3:** When these pin voltages are taken below ground or above  $V_{ANA} = V_{DIG} = V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents of greater than 100mA below ground or above  $V_{DD}$  without latch-up.

**Note 4:** When these pin voltages are taken below ground, they will be clamped by internal diodes. This product can handle input currents of 90mA below ground without latchup. These pins are not clamped to  $V_{DD}$ .

**Note 5:**  $V_{DD}$  = 5V,  $f_{SAMPLE}$  = 100kHz,  $t_r$  =  $t_f$  = 5ns unless otherwise specified.

Note 6: Linearity, offset and full-scale specifications apply for a  $V_{\text{IN}}$  input with respect to ground.

**Note 7:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual end points of the transfer curve. The deviation is measured from the center of the quantization band.

**Note 8:** Zero error for the LTC1605-1 is the voltage measured from 0.5LSB when the output code flickers between 0000 0000 0000 0000

and 0000 0000 0000 0001. Zero error for the LTC1605-2 is the voltage measured from -0.5LSB when the output code flickers between 0000 0000 0000 0000 and 1111 1111 1111 1111.

Note 9: Guaranteed by design, not subject to test.

Note 10: Recommended operating conditions.

**Note 11:** With  $\overline{CS}$  low the falling R/ $\overline{C}$  edge starts a conversion. If R/ $\overline{C}$  returns high at a critical point during the conversion it can create small errors. For best results ensure that R/ $\overline{C}$  returns high within 3 $\mu$ s after the start of the conversion.

**Note 12:** As measured with fixed resistors shown in Figure 4. Adjustable to zero with external potentiometer.

**Note 13:** Full-scale error is the untrimmed deviation from ideal last code transition, divided by the full-scale range and includes the effect of offset error.

**Note 14:** All specifications in dB are referred to a full-scale 4V input for the LTC1605-1 and to  $\pm$ 4V input for the LTC1605-2.

**Note 15:** Full-power bandwidth is defined as full-scale input frequency at which a signal-to-(noise + distortion) degrades to 60dB or 10 bits of accuracy.

**Note 16:** Recovers to specified performance after (±20V) input overvoltage for the LTC1605-1 and ±15V for the LTC1605-2.

## TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

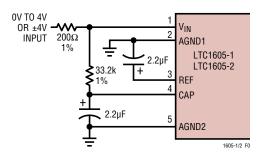

**VIN (Pin 1):** Analog Input. Connect through a  $200\Omega$  resistor to the analog input. Full-scale input range is 0V to 4V for the LTC1605-1 and  $\pm$ 4V for the LTC1605-2.

**AGND1 (Pin 2):** Analog Ground. Tie to analog ground plane.

**REF (Pin 3):** 2.5V Reference Output. Bypass with 2.2µF tantalum capacitor. Can be driven with an external reference.

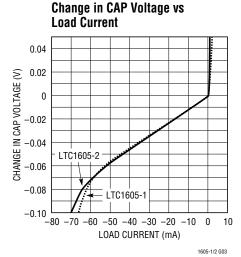

**CAP (Pin 4):** Reference Buffer Output. Bypass with 2.2µF tantalum capacitor.

**AGND2 (Pin 5):** Analog Ground. Tie to analog ground plane.

**D15 to D8 (Pins 6 to 13):** Three-State Data Outputs. Hi-Z state when  $\overline{CS}$  is high or when R/ $\overline{C}$  is low.

**DGND (Pin 14):** Digital Ground.

**D7 to D0 (Pins 15 to 22):** Three-State Data Outputs. Hi-Z state when  $\overline{CS}$  is high or when R/ $\overline{C}$  is low.

BYTE (Pin 23): Byte Select. With BYTE low, data will be output with Pin 6 (D15) being the MSB and Pin 22 (D0)

being the LSB. With BYTE high the upper eight bits and the lower eight bits will be switched. The MSB is output on Pin 15 and bit 8 is output on Pin 22. Bit 7 is output on Pin 6 and the LSB is output on Pin 13.

**R/C** (**Pin 24**): Read/ $\overline{\text{Convert}}$  Input. With  $\overline{\text{CS}}$  low, a falling edge on R/ $\overline{\text{C}}$  puts the internal sample-and-hold into the hold state and starts a conversion. With  $\overline{\text{CS}}$  low, a rising edge on R/ $\overline{\text{C}}$  enables the output data bits.

$\overline{\text{CS}}$  (Pin 25):  $\overline{\text{Chip Select}}$ . Internally OR'd with R/ $\overline{\text{C}}$ . With R/ $\overline{\text{C}}$  low, a falling edge on  $\overline{\text{CS}}$  will initiate a conversion. With R/ $\overline{\text{C}}$  high, a falling edge on  $\overline{\text{CS}}$  will enable the output data.

**BUSY** (**Pin 26**): Output Shows Converter Status. It is low when a conversion is in progress. Data valid on the rising edge of BUSY. CS or R/C must be high when BUSY rises or another conversion will start without time for signal acquisition.

$V_{ANA}$  (Pin 27): 5V Analog Supply. Bypass to ground with a 0.1µF ceramic and a 10µF tantalum capacitor.

$V_{DIG}$  (Pin 28): 5V Digital Supply. Connect directly to Pin 27.

# **FUNCTIONAL BLOCK DIAGRAM**

#### **TEST CIRCUITS**

#### **Load Circuit for Access Timing**

# DBN $\longrightarrow$ 1k $\longrightarrow$ 1k $\longrightarrow$ CL $\longrightarrow$ CL $\longrightarrow$ 1605-1/2 TC0 A. HI-Z TO V<sub>OH</sub> AND V<sub>OL</sub> TO V<sub>OH</sub> $\longrightarrow$ B. HI-Z TO V<sub>OL</sub> AND V<sub>OH</sub> TO V<sub>OH</sub>

#### **Load Circuit for Output Float Delay**

## APPLICATIONS INFORMATION

#### **Conversion Details**

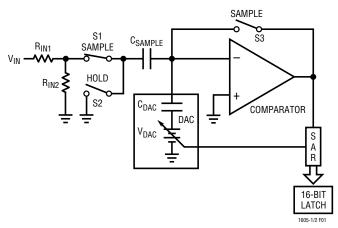

The LTC1605-1/LTC1605-2 use a successive approximation algorithm and an internal sample-and-hold circuit to convert an analog signal to a 16-bit or two byte parallel output. The ADC is complete with a precision reference and an internal clock. The control logic provides easy interface to microprocessors and DSPs. (Please refer to the Digital Interface section for the data format.)

Conversion start is controlled by the  $\overline{CS}$  and R/ $\overline{C}$  inputs. At the start of conversion, the successive approximation register (SAR) is reset. Once a conversion cycle has begun, it cannot be restarted.

During the conversion, the internal 16-bit capacitive DAC output is sequenced by the SAR from the most significant bit (MSB) to the least significant bit (LSB). Referring to Figure 1,  $V_{IN}$  is connected through the resistor divider and S1 to the sample-and-hold capacitor during the acquire phase and the comparator offset is nulled by the

Figure 1. LTC1605-1/LTC1605-2 Simplified Equivalent Circuit

autozero switch, S3. In this acquire phase, a minimum delay of  $2\mu s$  will provide enough time for the sample-and-hold capacitor to acquire the analog signal. During the convert phase, S3 opens, putting the comparator into the compare mode. The input switch S2 switches  $C_{SAMPLE}$  to ground, injecting the analog input charge onto the summing junction. This input charge is successively compared with the binary-weighted charges supplied by the capacitive DAC. Bit decisions are made by the high speed comparator. At the end of a conversion, the DAC output balances the  $V_{IN}$  input charge. The SAR contents (a 16-bit data word) that represents the  $V_{IN}$  are loaded into the 16-bit output latches.

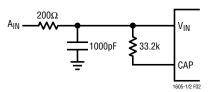

#### **Driving the Analog Inputs**

The nominal input range for the LTC1605-1 is 0V to 4V or (1.6V<sub>RFF</sub>) and for the LTC1605-2 the input range is ±4V or (±1.6V<sub>RFF</sub>). The inputs are overvoltage protected to  $\pm 25$ V. The input impedance is typically  $10k\Omega$ ; therefore, it should be driven by a low impedance source. Wideband noise coupling into the input can be minimized by placing a 1000pF capacitor at the input as shown in Figure 2. An NPO-type capacitor gives the lowest distortion. Place the capacitor as close to the device input pin as possible. If an amplifier is to be used to drive the input, care should be taken to select an amplifier with adequate accuracy, linearity and noise for the application. The following list is a summary of the op amps that are suitable for driving the LTC1605-1/LTC1605-2. More detailed information is available in the Linear Technology data books and LinearView™ CD-ROM.

LinearView is a trademark of Linear Technology Corporation

LT®1007 - Low noise precision amplifier. 2.7mA supply current ±5V to ±15V supplies. Gain bandwidth product 8MHz. DC applications.

LT1097 - Low cost, low power precision amplifier. 300µA supply current. ±5V to ±15V supplies. Gain bandwidth product 0.7MHz. DC applications.

LT1227 - 140MHz video current feedback amplifier. 10mA supply current. ±5V to ±15V supplies. Low noise and low distortion.

LT1360 - 37MHz voltage feedback amplifier. 3.8mA supply current. ±5V to ±15V supplies. Good AC/DC specs.

LT1363 - 50MHz voltage feedback amplifier. 6.3mA supply current. Good AC/DC specs.

LT1364/LT1365 - Dual and quad 50MHz voltage feedback amplifiers. 6.3mA supply current per amplifier. Good AC/DC specs.

LT1468 - 90MHz, 22V/µs 16-Bit Accurate Amplifier

Figure 2. Analog Input Filtering

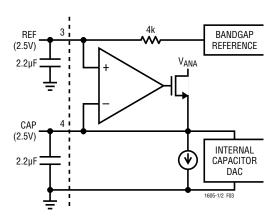

#### Internal Voltage Reference

The LTC1605-1/LTC1605-2 has an on-chip, temperature compensated, curvature corrected, bandgap reference, which is factory trimmed to 2.50V. The full-scale range of the ADC is equal to (1.6V<sub>REF</sub>) or nominally 0V to 4V for the LTC1605-1 and (±1.6V<sub>REF</sub>) or nominally ±4V for the LTC1605-2. The output of the reference is connected to the input of a unity-gain buffer through a 4k resistor (see Figure 3). The input to the buffer or the output of the reference is available at REF (Pin 3). The internal reference can be overdriven with an external reference if more accuracy is needed. The buffer output drives the internal DAC and is available at CAP (Pin 4). The CAP pin can be used to drive a steady DC load of less than 2mA. Driving an AC load is not recommended because it can cause the performance of the converter to degrade.

For minimum code transition noise the REF pin and the CAP pin should each be decoupled with a capacitor to filter wideband noise from the reference and the buffer (2.2µF tantalum).

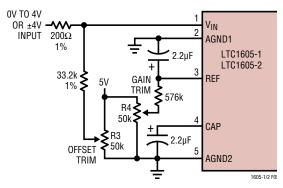

#### Offset and Gain Adjustments

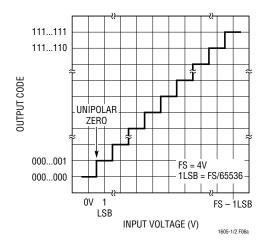

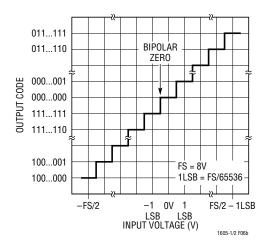

The LTC1605-1/LTC1605-2 offset and full-scale errors have been trimmed at the factory with the external resistors shown in Figure 4. This allows for external adjustment of offset and full scale in applications where absolute accuracy is important. See Figure 5 for the offset and gain trim circuit for the LTC1605-1/LTC1605-2. First adjust the offset to zero by adjusting resistor R3. Apply an input voltage of  $30.5\mu V$  (0.5LSB) and adjust R3 so the code is changing between 0000 0000 0000 0001 and 0000 0000 0000 0000. The gain error is trimmed by adjusting resistor R4. An input voltage of 3.999908V (FS - 1.5LSB) is applied to  $V_{IN}$  and R4 is adjusted until the output code is changing between 1111 1111 1111 1110 and 1111 1111 1111 1111. Figure 6a shows the unipolar transfer characteristic of the LTC1605-1.

For the LTC1605-2, first adjust the offset to zero by adjusting resistor R3. Apply an input voltage of  $-61\mu V$  (-0.5LSB) and adjust R3 so the code is changing between 1111 1111 1111 1111 and 0000 0000 0000 0000. The gain error is trimmed by adjusting resistor R4. An input voltage of 3.999817V (+FS - 1.5LSB) is applied to  $V_{IN}$  and R4 is adjusted until the output code is changing between 0111 1111 1111 1110 and 0111 1111 1111. Figure 6b shows the bipolar transfer characteristics of the LTC1605-2.

#### **DC** Performance

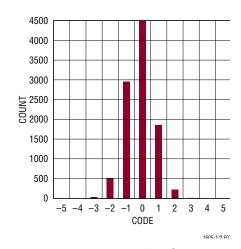

One way of measuring the transition noise associated with a high resolution ADC is to use a technique where a DC signal is applied to the input of the ADC and the resulting output codes are collected over a large number of conversions. For example, in Figure 7 the distribution of output code is shown for a DC input that has been digitized 10000 times. The distribution is Gaussian and the RMS code transition is about 1LSB.

Figure 3. Internal or External Reference Source

Figure 4. OV to 4V Input for the LTC1605-1 and ±4V for the LTC1605-2 Without Trim

Figure 5. OV to 4V Input for the LTC1605-1 and ±4V for the LTC1605-2 with Offset and Gain Trim

Figure 6a. LTC1605-1 Unipolar Transfer Characteristics

Figure 6B. LTC1605-2 Bipolar Transfer Characteristics

Figure 7. Histogram for 10000 Conversions

#### **DIGITAL INTERFACE**

#### **Internal Clock**

The ADC has an internal clock that is trimmed to achieve a typical conversion time of  $7\mu s$ . No external adjustments are required and, with the typical acquisition time of  $1\mu s$ , throughput performance of 100ksps is assured.

#### **Timing and Control**

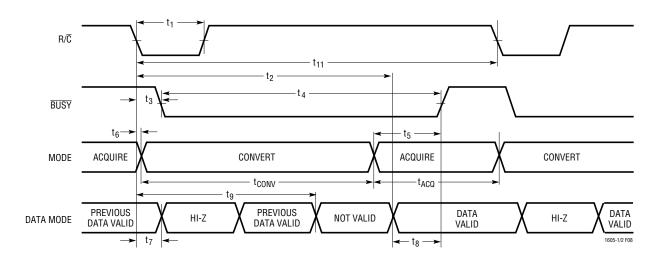

Conversion start and data read are controlled by two digital inputs:  $\overline{CS}$  and  $R/\overline{C}$ . To start a conversion and put the sample-and-hold into the hold mode, bring  $\overline{CS}$  and  $R/\overline{C}$  low for no less than 40ns. Once initiated, it cannot be restarted until the conversion is complete. Converter status is indicated by the  $\overline{BUSY}$  output and this is low while the conversion is in progress.

There are two modes of operation. The first mode is shown in Figure 8. The digital input  $R/\overline{C}$  is used to control the start of conversion.  $\overline{CS}$  is tied low. When  $R/\overline{C}$  goes low, the sample-and-hold goes into the hold mode and a conversion is started.  $\overline{BUSY}$  goes low and stays low during the conversion and will go back high after the conversion has been completed and the internal output shift registers have been updated.  $R/\overline{C}$  should remain low for no less than 40ns. During the time  $R/\overline{C}$  is low, the digital outputs are in

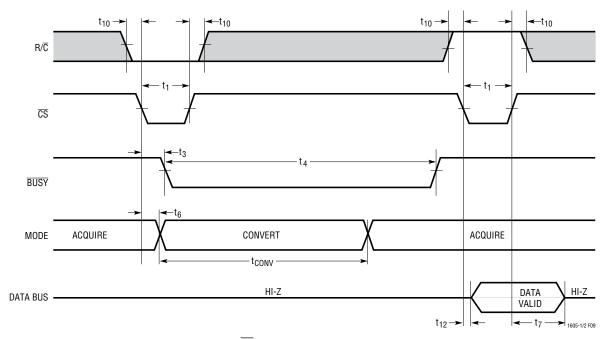

a Hi-Z state. R/ $\overline{C}$  should be brought back high within 3µs after the start of the conversion to ensure that no errors occur in the digitized result. The second mode, shown in Figure 9, uses the  $\overline{CS}$  signal to control the start of a conversion and the reading of the digital output. In this mode, the R/ $\overline{C}$  input signal should be brought low no less than 10ns before the falling edge of  $\overline{CS}$ . The minimum pulse width for  $\overline{CS}$  is 40ns. When  $\overline{CS}$  falls,  $\overline{BUSY}$  goes low and will stay low until the end of the conversion.  $\overline{BUSY}$  will go high after the conversion has been completed. The new data is valid when  $\overline{CS}$  is brought back low again to initiate a read. Again, it is recommended that both R/ $\overline{C}$  and  $\overline{CS}$  return high within 3µs after the start of the conversion.

#### **Output Data**

The output data can be read as a 16-bit word or it can be read as two 8-bit bytes. The format of the output data is straight binary for the LTC1605-1 and two's complement for the LTC1605-2. The digital input pin BYTE is used to control the two byte read. With the BYTE pin low, the first eight MSBs are output on the D15 to D8 pins and the eight LSBs are output on the D7 to D0 pins. When the BYTE pin is taken high, the eight LSBs replace the eight MSBs (Figure 10).

Figure 8. Conversion Timing with Outputs Enabled After Conversion (CS Tied Low)

Figure 9. Using  $\overline{\text{CS}}$  to Control Conversion and Read Timing

Figure 10. Using  $\overline{\text{CS}}$  and BYTE to Control Data Bus Read Timing

#### **Dynamic Performance**

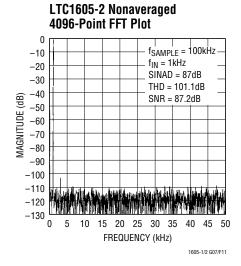

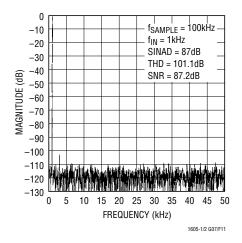

FFT (Fast Fourier Transform) test techniques are used to test the ADC's frequency response, distortion and noise at the rated throughput. By applying a low distortion sine wave and analyzing the digital output using an FFT algorithm, the ADC's spectral content can be examined for frequencies outside the fundamental. Figure 11 shows a typical LTC1605-2 FFT plot which yields a SINAD of 87dB and THD of –101.1dB.

#### Signal-to-Noise Ratio

The Signal-to-Noise and Distortion Ratio (SINAD) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other frequency components at the A/D output. The output is band limited to frequencies from above DC and below half the sampling frequency. Figure 11 shows a typical SINAD of 87dB with a 100kHz sampling rate and a 1kHz input.

Figure 11. LTC1605-2 Nonaveraged 4096-Point FFT Plot

#### **Total Harmonic Distortion**

Total Harmonic Distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half the sampling frequency. THD is expressed as:

THD =

$$20\log \frac{\sqrt{V2^2 + V3^2 + V4^2 ... + V_N^2}}{V1}$$

where V1 is the RMS amplitude of the fundamental frequency and V2 through  $V_N$  are the amplitudes of the second through Nth harmonics.

#### **Board Layout, Power Supplies and Decoupling**

Wire wrap boards are not recommended for high resolution or high speed A/D converters. To obtain the best performance from the LTC1605-1/LTC1605-2, a printed circuit board is required. Layout for the printed circuit board should ensure the digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track or underneath the ADC. The analog input should be screened by AGND.

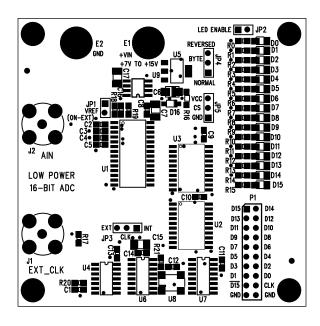

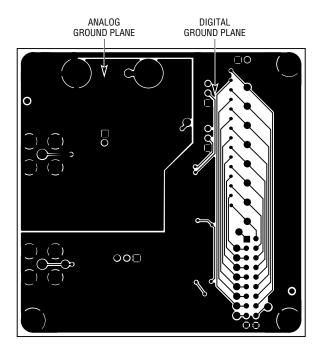

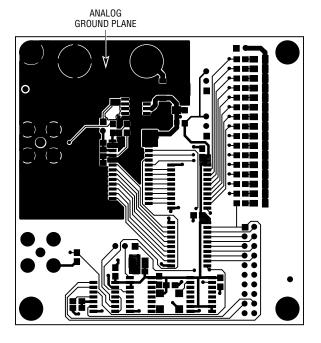

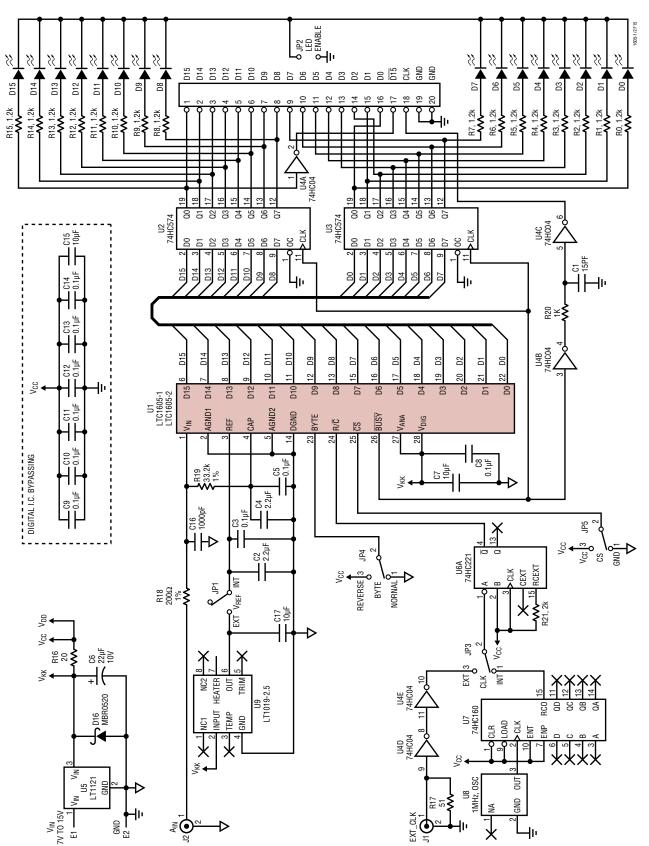

Figures 12 through 15 show a layout for a suggested evaluation circuit which will help obtain the best performance from the 16-bit ADC. Additional information regarding the evaluation circuit and Gerber files for the PC board layout are available from Linear Technology or your local sales office. Pay particular attention to the design of the analog and digital ground planes. The DGND pin of the LTC1605-1/ LTC1605-2 can be tied to the analog ground plane. Placing the bypass capacitor as close as possible to the power supply, the reference and reference buffer output is very important. Low impedance common returns for these bypass capacitors are essential to low noise operation of the ADC, and the PC track width for these lines should be as wide as possible. Also, since any potential difference in grounds between the signal source and ADC appears as an error voltage in series with the input signal, attention should be paid to reducing the ground circuit impedance as much as possible. The digital output latches and the onboard sampling clock have been placed on the digital ground plane. The two ground planes are tied together at the power supply ground connection.

Figure 12. Component Side Silkscreen for the Suggested LTC1605-1/LTC1605-2 Evaluation Circuit

Figure 13. Bottom Side Showing Analog Ground Plane

Figure 14. Component Side Showing Separate Analog and Digital Ground Plane

LINEAR

Figure 15. LTC1605-1 Suggested Evaluation Circuit Schematic

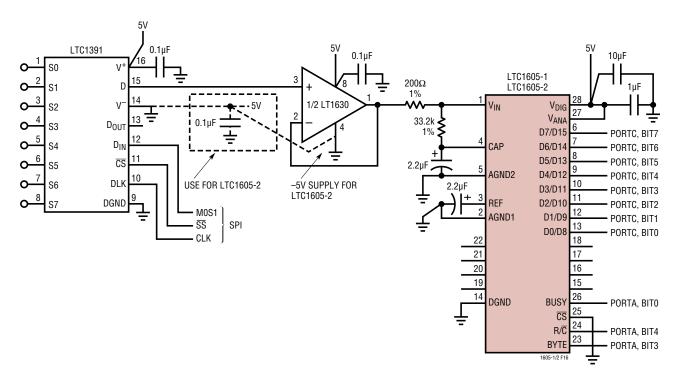

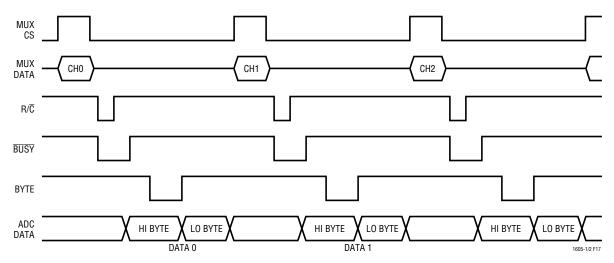

The circuit in Figure 16 is an example showing the LTC1605 16-bit A/D converter and LTC1391 8-channel MUX connected to a 68HC11 controller. The LTC1605's 16-bit data output is read in two 8-bit bytes using Pins 6 (MSB, Bit7) through 13 (Bit8, Bit0), connected to the HC11's PORTC. The MUX's 4-bit serial address data is sent using the controller's SPI.

The process to convert a channel's input signal is shown in sample listing A. It begins with shifting in the MUX's channel data while the  $\overline{SS}$  signal is a logic high. The MUX channel address is latched on the falling edge of  $\overline{SS}$  and

the chosen channel's input is applied at the LTC1605's input, Pin 1. Through the processor's PORTA, a low-going pulse is applied to the LTC1605's R/ $\overline{C}$  pin, initiating a conversion. The processor then monitors the  $\overline{BUSY}$  output. When this signal becomes a logic high, signaling the end of conversion, the processor reads the high byte of the conversion through PORTC. The low byte is read through PORTC when the processor changes the BYTE signal to a logic high. The timing relationship of the control signals and data are shown in Figure 17.

#### Sample Listing A

```

* This example program selects the an LTC1391 MUX channel, initiates a*

* conversion, and retrieves conversion data. It stores the 16-bit data*

* in two consecutive memory locations. The program is designed for use*

* with the LTC1605's /CS tied to ground (see timing diagram in

Figure 17).

*******************

************

* 68HC11 register definitions

$1000 Parallel port A

PORTA EQU

Use Bit0 as an input for the LTC1605's /BUSY signal

Use Bit3 as an output driving the LTC1605's BYTE

input

$1002 Parallel I/O control register

PIOC

EOU

"STAF, STAI, CWOM, HNDS, OIN, PLS, EGA, INVB"

PORTC

EQU

$1003 Port C data register

"Bit7, Bit6, Bit5, Bit4, Bit3, Bit2, Bit1, Bit0"

DDRC

$1007 Port D data direction register

"Bit7, Bit6, Bit5, Bit4, Bit3, Bit2, Bit1, Bit0"

1 = \text{output}, 0 = \text{input}

$1008 Port D data register

PORTD EOU

" - , - , SS* , CSK ; MOSI, MISO, TxD , RxD "

$1009 Port D data direction register

DDRD

EOU

$1028 SPI control register

SPCR

EQU

"SPIE, SPE , DWOM, MSTR; SPOL, CPHA, SPR1, SPR0"

SPSR

EQU

$1029 SPI status register

"SPIF, WCOL, - , MODF; - , - , - "

SPDR

EOU

$102A SPI data register; Read-Buffer; Write-Shifter

* RAM variables to hold the LTC1605's 14 conversion result

DIN1

EQU

$00

This memory location holds the LTC1605's bits 15 - 08

$01

This memory location holds the LTC1605's bits 07 - 00

DTN2

EQU

$02

MIIX

EQU

This memory location holds the MUX address data

```

LINEAR TECHNOLOGY

```

* Start GETDATA Routine

Program start location

ORG

$C000

INIT1 LDAA

#$03

0,0,0,0,0,0,1,1

"STAF=0,STAI=0,CWOM=0,HNDS=0, OIN=0, PLS=0, EGA=1,INVB=1"

STAA

PIOC

Ensures that the PIOC register's status is the same

as after a reset, necessary of simple Port D manipulation

LDAA

#$00

0,0,0,0,0,0,0,0

"Bits 7 - 0 are used as inputs for the LTC1605's data

STAA

DDRC

Direction of PortD's bit are now set as inputs

#$2F

LDAA

-,-,1,0;1,1,1,1

-, -, SS*-Hi, SCK-Lo, MOSI-Hi, MISO-Hi, X, X

STAA

PORTD

Keeps SS* a logic high when DDRD, Bit5 is set

LDAA

#$38

-,-,1,1;1,0,0,0

SS* , SCK, MOSI are configured as Outputs

STAA

DDRD

MISO, TxD, RxD are configured as Inputs

DDRD's Bit5 is a 1 so that port D's SS* pin is a general output

#$50

LDAA

STAA

SPCR

The SPI is configured as Master, CPHA = 0, CPOL = 0

and the clock rate is E/2

(This assumes an E-Clock frequency of 4MHz. For higher

E-Clock frequencies, change the above value of $50 to a

value that ensures the SCK frequency is 2MHz or less.)

GETDATAPSHX

PSHY

PSHA

***********

* Setup indices

**********

LDX

The X register is used as a pointer to the memory

locations that hold the conversion data

#$1000

LDY

**********

* Ensure that a logic high is applied

to the LTC1391's /CS and the

LTC1605's R/C pins

BSET

PORTD, Y %00100000

This sets the SS* output bit to a logic

high, ensuring that the LTC1391's CS*

input is a logic high while clocking

MUX address data into the LTC1391

BSET

PORTA,Y %00010000

This sets the R/C* output bit to a logic

high, ensuring that the LTC1605's R/C*

input is a logic high before initiating

a conversion

```

```

* Retrieve the MUX address from memory

* and send it to the LTC1391

**********

Retrieve the MUX address from memory

LDAA

ORAA

#$08 Enable the selected MUX address

SPDR Select the MUX channel

STAA

WAIT1 LDAA SPSR This loop waits for the SPI to complete a serial

transfer/exchange by reading the SPI Status Register

BPL

WAIT1 The SPIF (SPI transfer complete flaq) bit is the SPSR's

MSB and is set to one at the end of an SPI transfer. The

branch will occur while SPIF is a zero.

PORTD,Y %00100000

BCLR

This forces a logic low on PORTD's SS*,

latching the MUXes data

************

* Initiate a LTC1605 conversion

BCLR

PORTA,Y %00010000

Initiate a conversion

BSET

PORTA,Y %00010000

This sets the LTC1605's R/C* to a logic

**********

* Set the LTC1605's BYTE input low to

* ensure that the high byte is present

* during the first read

Get the contents of Port A

LDAA PORTA

ANDA #%11110111

Set Bit3 low

STAA

PORTA

Set the LTC1605's BYTE input low

***********

* The next short loop ensures that the *

* LTC1605's conversion is finished *

* before starting the data transfer*

**********

CONVENDLDAA

PORTA

Retrieve the contents of port A

#%0000001

ANDA

Look at Bit0

Bit0 = Lo; the LTC1605's conversion is not

Bit0 = Hi; the LTC1605's conversion is complete

BEQ

CONVEND

Branch to the loop's beginning while Bit7

remains low

```

```

This routine retrieves the LTC1605's 16-bit data using two 8-bit

reads. The BYTE input is manipulated through Port A's Bit3. During

the first read when BYTE is low, the upper byte is read and stored in*

DIN1. During the second read when BYTE is high, the lower byte is

read and stored in DIN2.

********

PORTC Retrieve the LTC1605's high byte

LDAA

STAA

DIN1

Store the high byte

PORTA Get the contents of Port A

LDAA

#%00001000

ORAA

Set Bit3 high

STAA

PORTA Set the LTC1605's BYTE input high

LDAA

PORTC Retrieve the LTC1605's low byte

STAA

Store the high byte

DIN2

PULA

Restore the A register

PULY

Restore the Y register

PULX

Restore the X register

RTS

```

Figure 16. 8-Channel, 16-Bit Data Acquisition System with Interface to the 68HC11

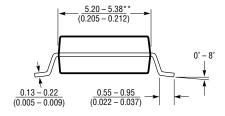

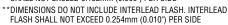

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### G Package 28-Lead Plastic SSOP (0.209)

(LTC DWG # 05-08-1640)

NOTE: DIMENSIONS ARE IN MILLIMETERS

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.152mm (0.006") PER SIDE

G28 SSOP 1098

LINEAL

# **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                    | PAGE NUMBER |

|-----|-------|--------------------------------|-------------|

| Α   | 07/15 | Obsoleted 28-Lead PDIP Package | 2, 20       |

Figure 17. This Is the Timing Relationship Between the Selected MUX Channel, Its Conversion Data and the ADC and MUX Control Signals When Using the Sample Program In Listing 1. The Conversion Process Is Latency Free: the Data Is Always Generated Based On the Currently Selected MUX Input

# **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                           | COMMENTS                                               |

|-----------------|---------------------------------------|--------------------------------------------------------|

| LT®1019-2.5     | Precision Bandgap Reference           | 0.05% Max, 5ppm/°C Max                                 |

| LTC1274/LTC1277 | Low Power 12-Bit, 100ksps ADCs        | 10mW Power Dissipation, Parallel/Byte Interface        |

| LTC1415         | Single 5V, 12-Bit, 1.25Msps ADC       | 55mW Power Dissipation, 72dB SINAD                     |

| LTC1419         | Low Power 14-Bit, 800ksps ADC         | True 14-Bit Linearity, 81.5dB SINAD, 150mW Dissipation |

| LT1460-2.5      | Micropower Precision Series Reference | 0.075% Max, 10ppm/°C Max, Only 130μA Supply Current    |

| LTC1594/LTC1598 | Micropower 4-/8-Channel 12-Bit ADCs   | Serial I/O, 3V and 5V Versions                         |

| LTC1604         | 16-Bit, 333ksps Sampling ADC          | ±2.5V Input, 90dB SINAD, 100dB THD                     |

| LTC1605         | Low Power 100ksps 16-Bit ADC          | Single 5V, ±10V Inputs                                 |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **Analog Devices Inc.:**

<u>LTC1605-2IG#PBF</u> <u>LTC1605-1IG#TRPBF</u> <u>LTC1605-1CG#TR</u> <u>LTC1605-1CG</u> <u>LTC1605-2CG#PBF</u> <u>LTC1605-1CG#TRPBF</u> <u>LTC1605-2CG#TRPBF</u> <u>LTC1605-2IG#TRPBF</u> <u>LTC1605-2IG#TRPBF</u>