A Product Line of Diodes Incorporated

## DDR BUS TERMINATION REGULATOR

# Description

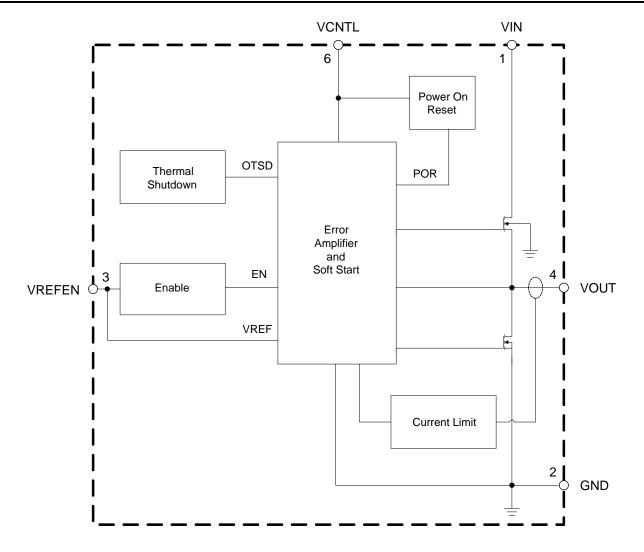

The AP2303 is a low dropout linear regulator to generate termination voltage of DDR-SDRAM system. The regulator can source or sink up to 1.75A current continuously. The output voltage is regulated to track tightly with the reference voltage ( $1/2V_{DDQ}$ ) within ±10mV.

The AP2303 supports soft start-up when used to turn on the VCNTL and VREFEN. It integrates a shutdown circuit that will be triggered once the voltage of VIN, VCNTL or VREFEN falls below a certain value.

AP2303 features over temperature protection and current limit protection for both source and sink.

AP2303 is available in packages of SOIC-8 and PSOP-8.

### Features

- Support DDR-II (V<sub>TT</sub>=0.9V), DDR-III (V<sub>TT</sub>=0.75V), DDR-IIIL (V<sub>TT</sub>=0.675V), DDR-IV (V<sub>TT</sub>=0.6V) Application

- Source and Sink up to 1.75A Current

- Output Voltage Accuracy Over Full Load: ±2% (Max.)

- Soft Start-up and Shutdown along with V<sub>IN</sub>, V<sub>CNTL</sub> and V<sub>REFEN</sub> Rising and Shutdown along with V<sub>IN</sub>, V<sub>CNTL</sub> and V<sub>REFEN</sub> Dropping

- Flexible Output by 2 External Resistors

- Requires Minimum 10µF Output Ceramic Capacitor for Application

- Current Limit Protection for Both Source and Sink

- OTSD Protection

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

Pad

PSOP-8

6

5

VCNTL

NC

VREFEN

VOUT

3

4

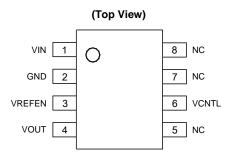

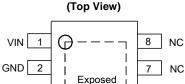

**Pin Assignments**

## Applications

- DDR-II/DDR-III/DDR-IIIL/DDR-IV Memory System

- Desktop PC, Notebook Mother Board

- Graphic Card

- STB, LCD-TV, Web-TV

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

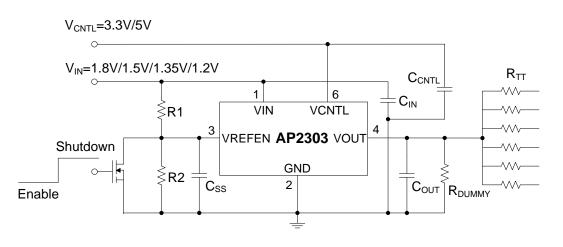

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number | Pin Name    | Function                                                                                                                                                                            |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VIN         | Unregulated input supply. A small 10µF MLCC should be connected from this pin to GND.                                                                                               |

| 2          | GND         | Ground                                                                                                                                                                              |

| 3          | VREFEN      | Reference voltage input and active low shutdown control pin. Pulling the pin to ground turns off device by BJT or FET. When it is released, a soft-start will take for about 0.1ms. |

| 4          | VOUT        | Regulated voltage output. A minimum of 10µF ceramic capacitor to ground is required to assure stability.                                                                            |

| 5, 7, 8    | NC          | No Connection                                                                                                                                                                       |

| 6          | VCNTL       | VCNTL supplies the internal control circuitry and provides the drive voltage.                                                                                                       |

| _          | Exposed Pad | The exposed pad should be connected to ground copper for better heat dissipation performance.                                                                                       |

# **Functional Block Diagram**

# Absolute Maximum Ratings (Note 4)

| Symbol            | Parameter                                         | Ra                          | Rating    |      |  |

|-------------------|---------------------------------------------------|-----------------------------|-----------|------|--|

| V <sub>IN</sub>   | Power Input Voltage                               | -0.3                        | -0.3 to 6 |      |  |

| V <sub>CNTL</sub> | Control Input Voltage                             | -0.3                        | -0.3 to 6 |      |  |

| Vrefen            | Reference Input Voltage                           | -0.3                        | -0.3 to 6 |      |  |

| T <sub>STG</sub>  | Storage Temperature                               | +150                        |           |      |  |

| TJ                | Junction Temperature +150                         |                             | °C        |      |  |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10sec)               | +2                          | +260      |      |  |

|                   |                                                   | PSOP-8                      | 80        |      |  |

| $\theta_{JA}$     | Thermal Resistance (Junction to Ambient) (Note 5) | SOIC-8                      | 110       | °C/W |  |

| _                 |                                                   | PSOP-8                      | 38        |      |  |

| θ <sub>JC</sub>   | Thermal Resistance (Junction to Case)             | SOIC-8                      | 50        | °C/W |  |

| ESD               | ESD (Human Body Model)                            | ESD (Human Body Model) 2000 |           | V    |  |

| ESD               | ESD (Machine Model)                               | 2                           | 200       |      |  |

Notes: 4. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

5.  $\theta_{JA}$  is measured with the component mounted on a 2-Layer FR-4 board with 2.54cm\*2.54cm thermal sink pad in free air.

# **Recommended Operating Conditions**

| Symbol             | Parameter                            | Min | Мах                    | Unit |

|--------------------|--------------------------------------|-----|------------------------|------|

| V <sub>CNTL</sub>  | Control Input Voltage (Note 6)       | 3.0 | 5.5                    | V    |

| V <sub>IN</sub>    | Power Input Voltage                  | 1.2 | 5.5                    | V    |

| V <sub>REFEN</sub> | Reference Input Voltage              | 0.6 | V <sub>CNTL</sub> -2.2 | V    |

| TJ                 | Operating Junction Temperature Range | -40 | +125                   | °C   |

| T <sub>A</sub>     | Operating Ambient Temperature Range  | -40 | +85                    | °C   |

Note 6: Keep  $V_{CNTL} \ge V_{IN}$  in operation power on and power off sequences.

**Electrical Characteristics** (@T<sub>A</sub> = +25°C, V<sub>IN</sub> = 1.8V/1.5V/1.35V/1.2V, V<sub>CNTL</sub> = 3.3V, V<sub>REFEN</sub> = 0.9V/0.75V/0.675V/0.6V, C<sub>IN</sub> = 10 $\mu$ F (Ceramic), C<sub>OUT</sub> = 10 $\mu$ F (Ceramic), unless otherwise specified.)

| Symbol                | Parameter                            | Conditions                                         | Min                                     | Тур  | Max   | Unit |  |

|-----------------------|--------------------------------------|----------------------------------------------------|-----------------------------------------|------|-------|------|--|

| Input                 |                                      |                                                    |                                         | -71  |       |      |  |

| IVCNTL                | VCNTL Operating Current              | No Load                                            | _                                       | 0.5  | 1.5   | mA   |  |

| I <sub>SD-VCNTL</sub> | VCNTL Input Current in Shutdown Mode | V <sub>REFEN</sub> < 0.15V                         | _                                       | 30   | 50    | μA   |  |

| I <sub>SD-VIN</sub>   | VIN Input Current in Shutdown Mode   | V <sub>REFEN</sub> < 0.15V                         | -1                                      | _    | 1     | μA   |  |

| IVREFEN               | VREFEN Leakage Current               | $V_{REFEN} = 0.75V$                                | -1                                      | -    | 1     | μA   |  |

| Output                |                                      |                                                    |                                         |      |       |      |  |

| V <sub>OS</sub>       | Output Offset Voltage (Note 7)       | No Load                                            | -10                                     | 0    | 10    | mV   |  |

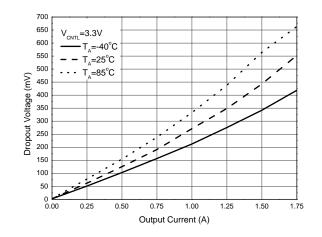

|                       |                                      | V <sub>CNTL</sub> = 3.3V, I <sub>OUT</sub> = 1A    | -                                       | 220  | -     |      |  |

| V <sub>DROPOUT</sub>  | Dropout Voltage                      | V <sub>CNTL</sub> = 3.3V, I <sub>OUT</sub> = 1.5A  | -                                       | 400  | -     | mV   |  |

|                       |                                      | V <sub>CNTL</sub> = 3.3V, I <sub>OUT</sub> = 1.75A | -                                       | 520  | -     | 1    |  |

|                       |                                      | I <sub>OUT</sub> = 0A to 1.75A                     | -20                                     | -    | 20    |      |  |

| V <sub>LOAD</sub>     | Load Regulation                      | I <sub>OUT</sub> = 0A to -1.75A -20 -              |                                         | 20   | mV    |      |  |

| Protection            |                                      |                                                    |                                         |      |       |      |  |

|                       |                                      | Source                                             | 1.75                                    | -    | -     |      |  |

| ILIMIT                | Current Limit                        | Sink                                               | -                                       | -    | -1.75 | A    |  |

|                       |                                      | V <sub>OUT</sub> = 0V                              | -                                       | 2    | -     |      |  |

| Ishort                | Short Current                        | V <sub>OUT</sub> = V <sub>IN</sub>                 | ν <sub>OUT</sub> = V <sub>IN</sub> – -2 |      | -     | A    |  |

| T <sub>SHDN</sub>     | Thermal Shutdown Temperature         | $3.3V \le V_{CNTL} \le 5V$                         | _                                       | +160 | _     | °C   |  |

| _                     | Thermal Shutdown Hysteresis          | -                                                  | -                                       | +30  | _     | °C   |  |

| Start-up & Shutdown   | Function                             |                                                    |                                         |      |       |      |  |

| VIH                   |                                      | Output = High                                      | 0.4                                     | -    | -     |      |  |

| VIL                   | VREFEN Shutdown Threshold Voltage    | Output = Low                                       | -                                       | -    | 0.15  | V    |  |

| V <sub>CNTL-ON</sub>  |                                      | Output = High                                      | 2.9                                     | _    | _     |      |  |

| V <sub>CNTL-OFF</sub> | VCNTL Shutdown Threshold Voltage     | Output = Low                                       | -                                       | -    | 2.2   | V    |  |

| V <sub>IN-ON</sub>    |                                      | Output = High                                      | 1.1                                     | -    | _     |      |  |

| V <sub>IN-OFF</sub>   | VIN Shutdown Threshold Voltage       | Output = Low                                       | _                                       | _    | 0.4   | V    |  |

Note 7:  $V_{OS}$  is the voltage measurement defined as  $V_{OUT}$  subtracted from  $V_{REFEN}$ .

## **Performance Characteristics**

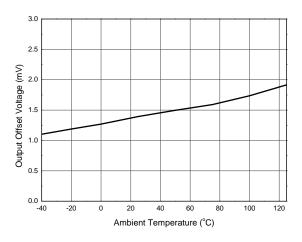

### **Output Offset Voltage vs. Ambient Temperature**

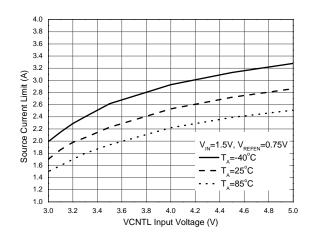

#### Source Current Limit vs. VCNTL Input Voltage

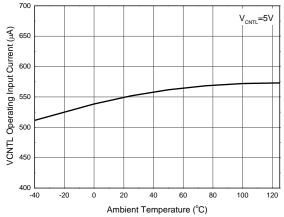

VCNTL Operating Input Current vs. Ambient Temperature

**Dropout Voltage vs. Output Current**

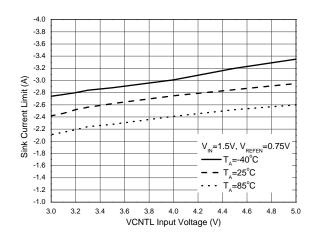

Sink Current Limit vs. VCNTL Input Voltage

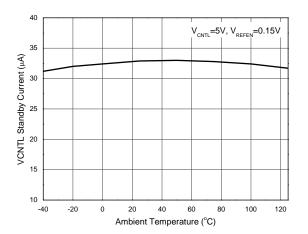

VCNTL Standby Current vs. Ambient Temperature

### Performance Characteristics (Cont.)

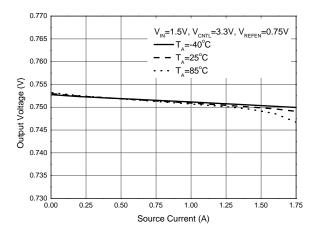

### Output Voltage vs. Source Current (DDR-III)

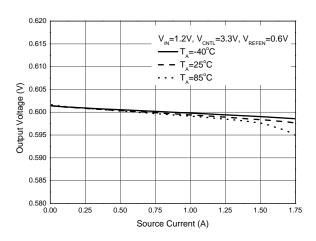

#### Output Voltage vs. Source Current (DDR-IV)

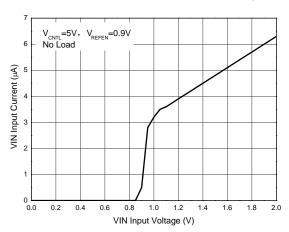

#### VIN Input Current vs. VIN Input Voltage

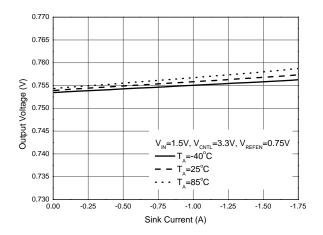

Output Voltage vs. Sink Current (DDR-III)

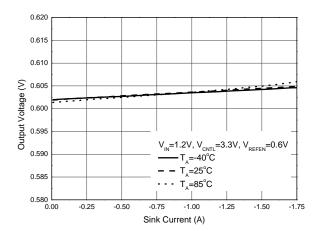

#### **Output Voltage vs. Sink Current (DDR-IV)**

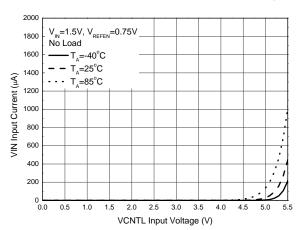

#### VIN Input Current vs. VCNTL Input Voltage

# Performance Characteristics (Cont.)

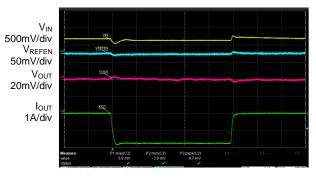

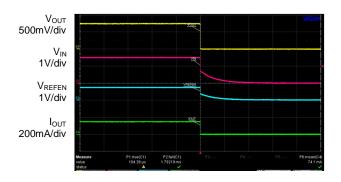

Time 100 µs/div

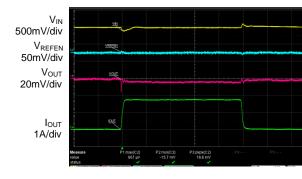

Source Load Transient (DDR-III)

(CIN=COUT=10µF, IOUT=0A to 1.75A,

V<sub>IN</sub>=1.5V, V<sub>REFEN</sub>=0.75V, V<sub>CNTL</sub>=3.3V)

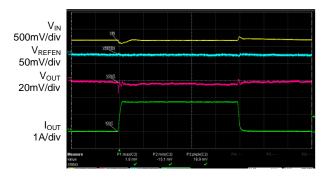

### Source Load Transient (DDR-IV) ( $C_{IN}=C_{OUT}=10\mu$ F, $I_{OUT}=0A$ to 1.75A, $V_{IN}=1.2V$ , $V_{REFEN}=0.6V$ , $V_{CNTL}=3.3V$ )

Time 100 µs/div

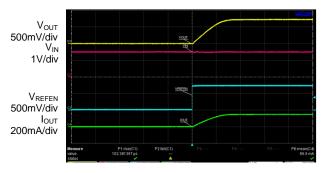

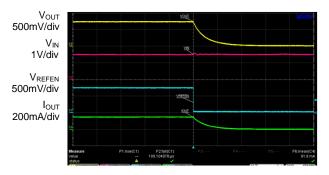

# $\label{eq:VREFEN} \begin{array}{l} \text{VREFEN Power On} \\ \text{(C}_{\text{IN}} = C_{\text{OUT}} = 10 \mu\text{F}, \ R_{\text{LOAD}} = 5 \Omega, \ V_{\text{CNTL}} = 5 \text{V}) \end{array}$

Time 100 µs/div

Sink Load Transient (DDR-III) ( $C_{IN}=C_{OUT}=10\mu$ F,  $I_{OUT}=0A$  to -1.75A,  $V_{IN}=1.5V$ ,  $V_{REFEN}=0.75V$ ,  $V_{CNTL}=3.3V$ )

Time 100 µs/div

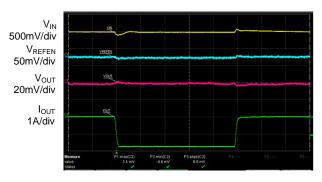

Sink Load Transient (DDR-IV) ( $C_{IN}=C_{OUT}=10\mu F$ ,  $I_{OUT}=0A$  to -1.75A,  $V_{IN}=1.2V$ ,  $V_{REFEN}=0.6V$ ,  $V_{CNTL}=3.3V$ )

Time 100 µs/div

$\label{eq:VREFEN} \begin{array}{l} \text{VREFEN Power Off} \\ \text{(C_{IN}=C_{OUT}=10 \mu F, R_{LOAD}=5 \Omega, V_{CNTL}=5 V)} \end{array}$

Time 100 µs/div

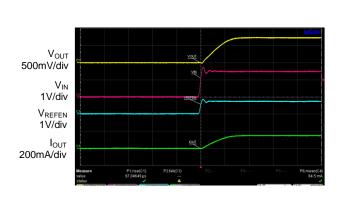

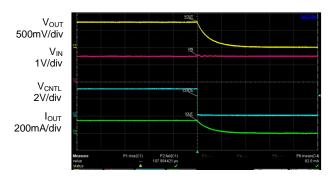

# Performance Characteristics (Cont.)

Time 100 µs/div

$\label{eq:VIN Power On} $$ VIN Power On$$ (C_{IN}=C_{OUT}=10 \mu F, R_{LOAD}=5\Omega, V_{CNTL}=5V)$ }$

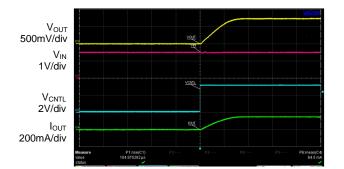

### VCNTL Power On ( $C_{IN}=C_{OUT}=10\mu F$ , $R_{LOAD}=5\Omega$ )

Time 100 µs/div

$\label{eq:VIN Power Off} VIN \ Power \ Off \\ (C_{IN}=C_{OUT}=10 \mu F, \ R_{LOAD}=5\Omega, \ V_{CNTL}=5V) \\$

Time 500ms/div

$\label{eq:VCNTL Power Off} \begin{array}{l} \text{(C}_{\text{IN}} = C_{\text{OUT}} = 10 \mu F, \ R_{\text{LOAD}} = 5 \Omega \end{array} \right)$

Time 100 µs/div

# **Application Information**

#### 1. Input Capacitor

The input capacitor of VIN should be placed to VIN pin as close as possible. Use a low ESR, 10µF or larger MLCC capacitor to provide surge current during load transient.

The input capacitor for VCNTL is recommended to be 0.47µF or larger to decouple the supply voltage of AP2303's control circuitry.

#### 2. Output Capacitor

The output capacitor is recommended with a  $10\mu$ F or higher MLCC capacitor which will be sufficient at full temperature range. An aluminum electrolytic capacitor with low ESR also should be larger than  $10\mu$ F. The output capacitor should be placed to VOUT pin as close as possible.

#### 3. Reference Voltage

A reference voltage is applied to the VREFEN pin by a resistor divider between VIN and GND pins. And a 0.1µF to 1µF bypass capacitor is preferred to form a low-pass filter to reduce the noise from VIN. More capacitance and large resistance will increase the start-up time after VIN power-up.

#### 4. Thermal Consideration

There's an internal thermal protection circuitry of AP2303 to protect device during overload conditions. For continuous operation, make sure not to exceed the operating junction temperature range of +125°C. The power dissipation definition in device is:

$P_{D}=(V_{IN} - V_{OUT})xI_{OUT}+V_{IN}xI_{Q}$

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout and the surrounding airflow. The maximum power dissipation can also be calculated as:

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})}\text{-}\mathsf{T}_{\mathsf{A}})/\theta_{\mathsf{J}\mathsf{A}}$

The maximum power dissipation for PSOP-8 package at  $T_A = +25^{\circ}C$  can be calculated as:

$P_{D(MAX)} = (125^{\circ}C-25^{\circ}C) / (80^{\circ}C/W) = 1.25W$

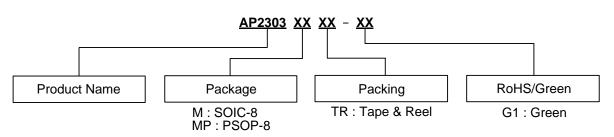

# **Ordering Information**

| Package | Temperature Range | Part Number   | Marking ID | Packing          |  |

|---------|-------------------|---------------|------------|------------------|--|

| SOIC-8  |                   | AP2303MTR-G1  | 2303M-G1   | 4000/Tape & Reel |  |

| PSOP-8  | -40 to +85°C      | AP2303MPTR-G1 | 2303MP-G1  | 4000/Tape & Reel |  |

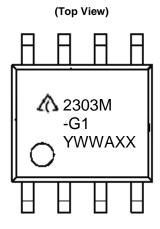

# **Marking Information**

## (1) SOIC-8

First and Second Lines: Logo and Marking ID Third Line: Date Code Y: Year WW: Work Week of Molding A: Assembly House Code XX: 7<sup>th</sup> and8<sup>th</sup> Digits of Batch No.

(2) PSOP-8

First and Second Lines: Logo and Marking ID Third Line: Date Code Y: Year WW: Work Week of Molding A: Assembly House Code XX: 7<sup>th</sup> and 8<sup>th</sup> Digits of Batch No.

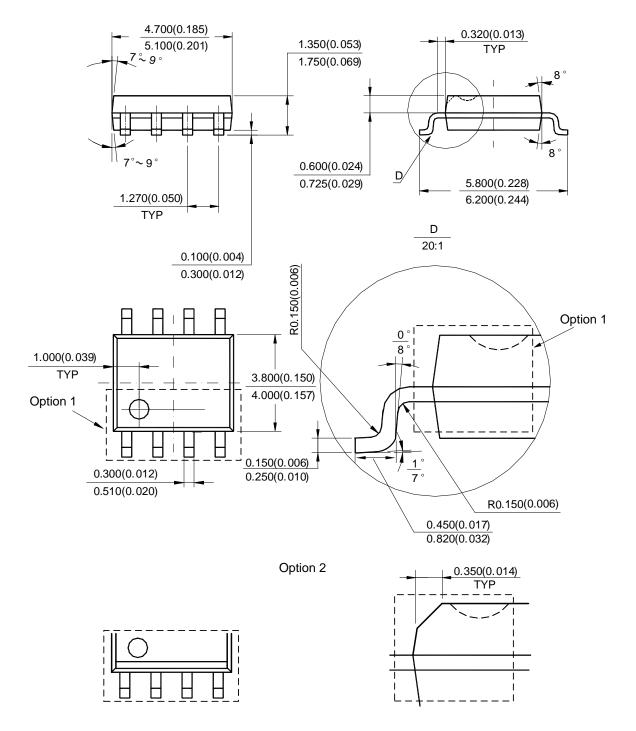

## Package Outline Dimensions (All dimensions in mm(inch).)

### (1) Package Type: SOIC-8

Note: Eject hole, oriented hole and mold mark is optional.

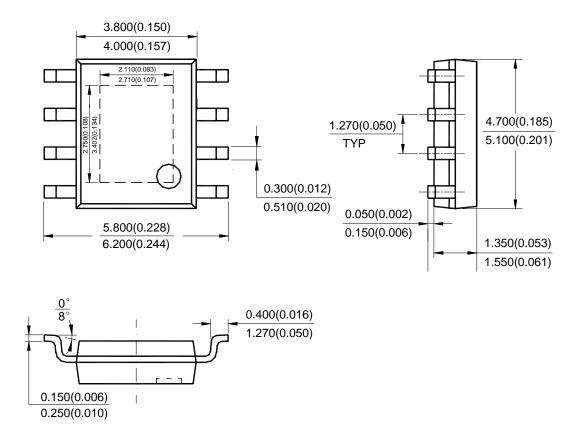

# Package Outline Dimensions (Cont. All dimensions in mm(inch).)

#### (2) Package Type: PSOP-8

Note: Eject hole, oriented hole and mold mark is optional.

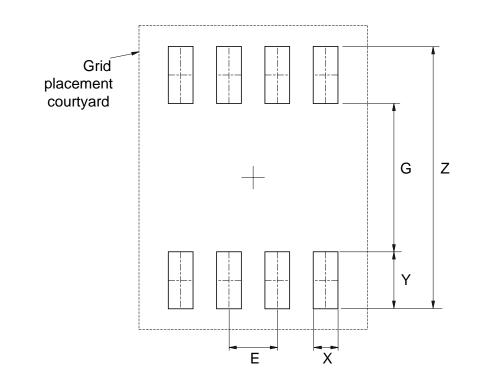

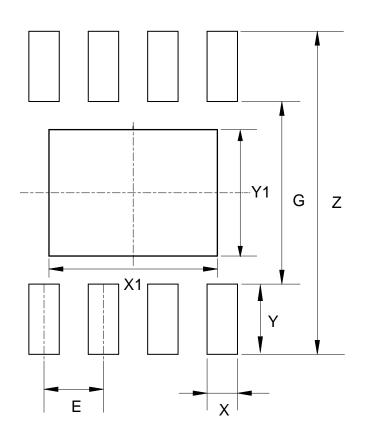

# **Suggested Pad Layout**

### (1) Package Type: SOIC-8

| Dimensions | Z           | G           | X           | Y           | E           |

|------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) |

| Value      | 6.900/0.272 | 3.900/0.154 | 0.650/0.026 | 1.500/0.059 | 1.270/0.050 |

# Suggested Pad Layout (Cont.)

### (2) Package Type: PSOP-8

| Dimensions | Z           | G           | Х           | Y           | X1          | Y1          | E           |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) |

| Value      | 6.900/0.272 | 3.900/0.154 | 0.650/0.026 | 1.500/0.059 | 3.600/0.142 | 2.700/0.106 | 1.270/0.050 |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2014, Diodes Incorporated

www.diodes.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Diodes Incorporated: AP2303MTR-G1 AP2303MPTR-G1