**DAC3484**

SLAS749E - MARCH 2011 - REVISED NOVEMBER 2015

# DAC3484 Quad-Channel, 16-Bit, 1.25 GSPS Digital-to-Analog Converter (DAC)

#### **Features**

- Very Low Power: 1.27 W at 1.25 GSPS, Full **Operating Conditions**

- Multi-DAC Synchronization

- Selectable 2x, 4x, 8x, 16x Interpolation Filter

- Stop-Band Attenuation > 90 dBc

- Flexible On-chip Complex Mixing

- Two Independent Fine Mixers with 32-Bit **NCOs**

- Power Saving Coarse Mixers: ± nxFs/8

- High Performance, Low Jitter Clock Multiplying

- Digital I and Q Correction

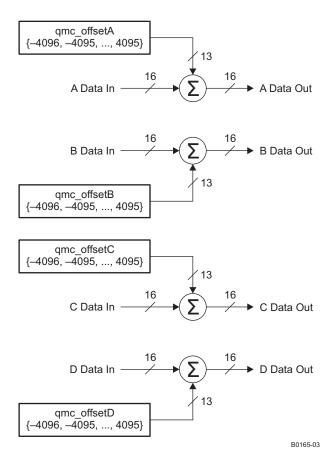

- Gain, Phase, Offset, and Group Delay Correction

- Digital Inverse Sinc Filter

- Flexible 16-Bit LVDS Input Data Bus

- 8 Sample Input FIFO

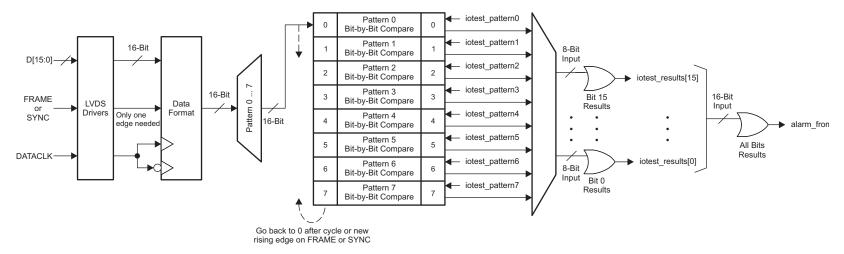

- Data Pattern Checker

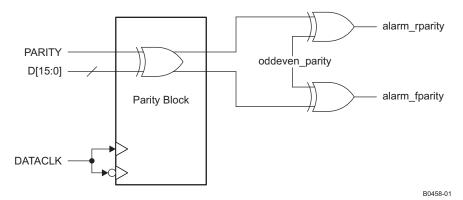

- Parity Check

- GC5330 Compatible

- Temperature Sensor

- Differential Scalable Output: 10 mA to 30 mA

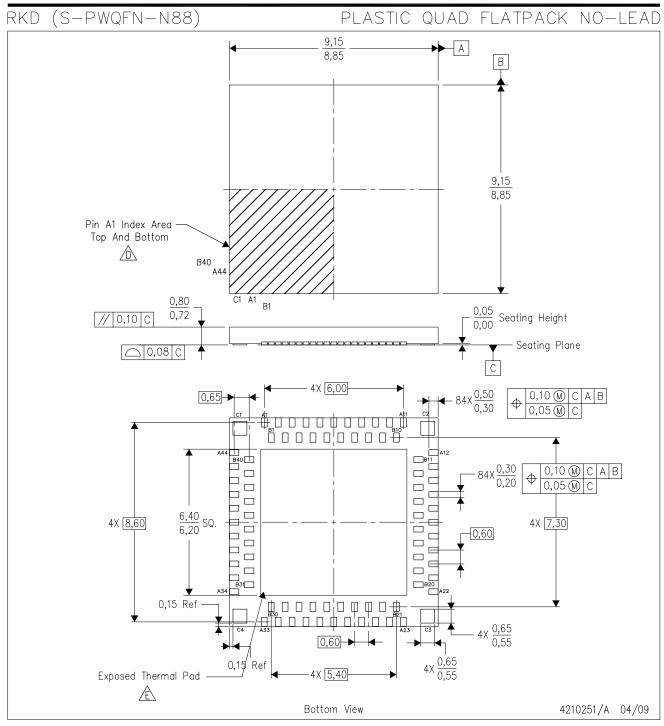

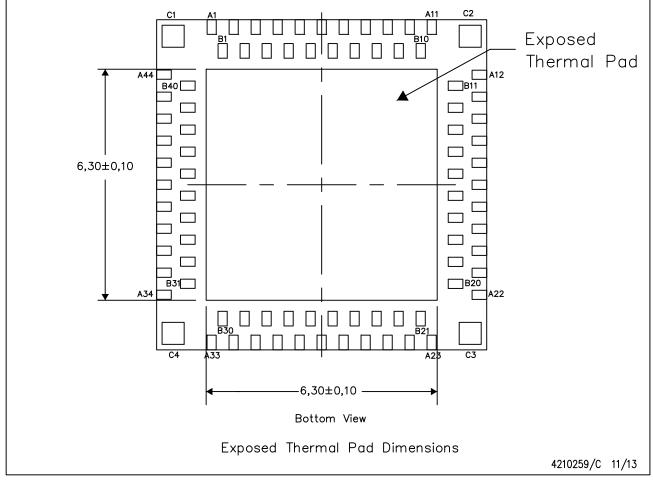

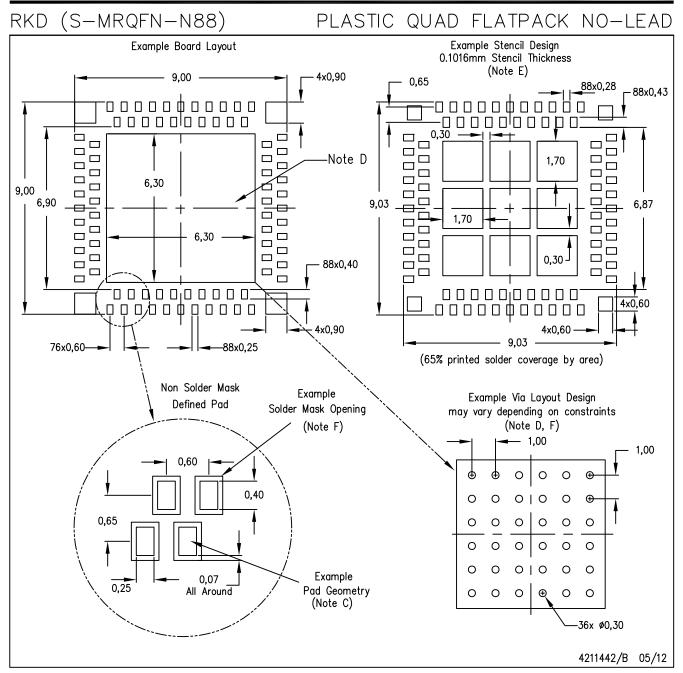

- Multiple Package Options: 88-Pin 9x9mm WQFN and 196-Ball 12mmx12mm NFBGA (GREEN / Pb-Free)

## **Applications**

- Cellular Base Stations

- **Diversity Transmit**

- Wideband Communications

## 3 Description

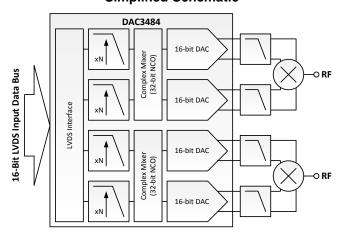

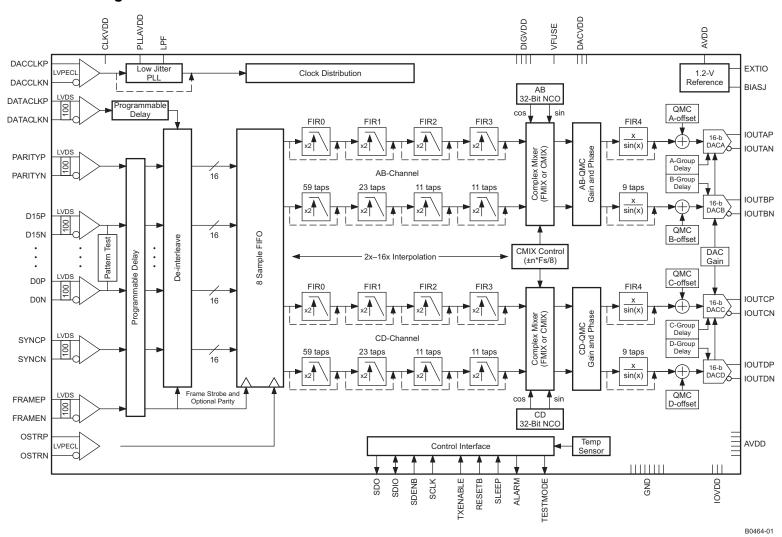

The DAC3484 is a very low power, high dynamic quad-channel, 16-bit digital-to-analog converter (DAC) with a sample rate as high as 1.25 GSPS.

The device includes features that simplify the design of complex transmit architectures: 2x to 16x digital interpolation filters with over 90dB of stop-band interface simplify attenuation the data reconstruction filters. Independent complex mixers allow flexible carrier placement. A high-performance low jitter clock multiplier simplifies clocking of the device without significant impact on the dynamic range. The digital Quadrature Modulator Correction (QMC) enables complete IQ compensation for gain, offset, phase and group delay between channels in direct up-conversion applications.

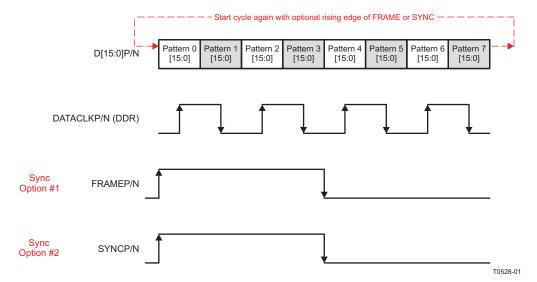

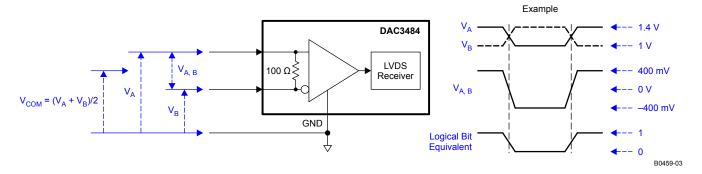

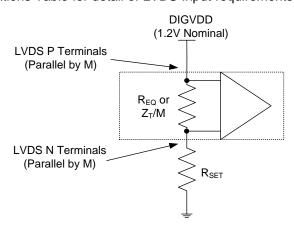

Digital data is input to the device through a 16-bit LVDS data bus with on-chip termination. The device includes a FIFO, data pattern checker and parity test to ease the input interface. The interface also allows full synchronization of multiple devices.

The device is characterized for operation over the entire industrial temperature range of -40°C to 85°C and is available in a very-small 88-pin 9x9mm WQFN package or 196-ball 12x12mm NFBGA package.

Very low power, small size, superior crosstalk, high dynamic range and features of the DAC3484 are an ideal fit for systems with multiple transmit channels.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |  |  |

|-------------|-------------|---------------------|--|--|

| DAC2494     | WQFN (88)   | 9.00 mm x 9.00 mm   |  |  |

| DAC3484     | NFBGA (196) | 12.00 mm x 12.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

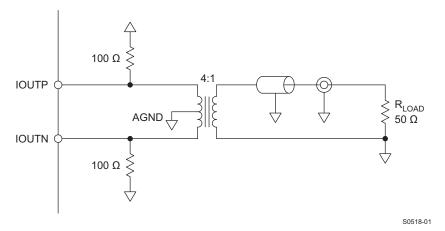

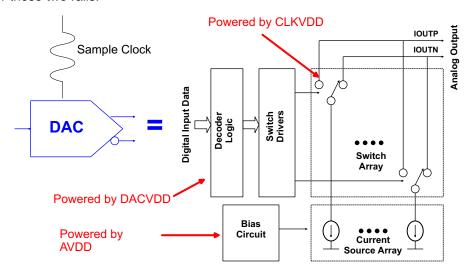

#### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                                 |    | 7.3 Feature Description                          | 29 |

|---|------------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                             |    | 7.4 Device Functional Modes                      | 58 |

| 3 | Description 1                                              |    | 7.5 Programming                                  | 62 |

| 4 | Revision History2                                          |    | 7.6 Register Map                                 | 66 |

| 5 | Pin Configuration and Functions 5                          | 8  | Application and Implementation                   | 83 |

| 6 | Specifications                                             |    | 8.1 Application Information                      | 83 |

| • | 6.1 Absolute Maximum Ratings                               |    | 8.2 Typical Applications                         | 84 |

|   | 6.2 ESD Ratings                                            | 9  | Power Supply Recommendations                     | 90 |

|   | 6.3 Recommended Operating Conditions                       | 10 | Layout                                           | 91 |

|   | 6.4 Thermal Information                                    |    | 10.1 Layout Guidelines                           |    |

|   | 6.5 Electrical Characteristics – DC Specifications 12      |    | 10.2 Layout Examples                             | 92 |

|   | 6.6 Electrical Characteristics – Digital Specifications 14 | 11 | Device and Documentation Support                 |    |

|   | 6.7 Electrical Characteristics – AC Specifications 15      |    | 11.1 Device Support                              | 95 |

|   | 6.8 Timing Requirements – Digital Specifications 15        |    | 11.2 Documentation Support                       | 96 |

|   | 6.9 Switching Characteristics – AC Specifications 17       |    | 11.3 Community Resources                         | 96 |

|   | 6.10 Typical Characteristics                               |    | 11.4 Trademarks                                  | 96 |

| 7 | Detailed Description                                       |    | 11.5 Electrostatic Discharge Caution             | 96 |

| • | 7.1 Overview                                               |    | 11.6 Glossary                                    | 96 |

|   | 7.2 Functional Block Diagram                               | 12 | Mechanical, Packaging, and Orderable Information | 96 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision D (September 2015) to Revision E                                  |    |  |  |  |  |  |

|---|----------------------------------------------------------------------------------------|----|--|--|--|--|--|

| • | Changed I <sub>(CLKVDD)</sub> Clock supply current Mode 1 max value from 95mA to 100mA | 13 |  |  |  |  |  |

#### Changes from Revision C (August 2012) to Revision D

Page

|   | ····g··· · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                               | 9-       |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| • | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1        |

| • | Added 196-ball 12x12mm BGA package to Description                                                                                                                                                                                                                                    | 1        |

| • | Added additional operation requirement for SLEEP pin if SLEEP pin is set to logic HIGH before and during device power up and initialization.                                                                                                                                         | <b>7</b> |

| • | Added additional circuit configuration for unused terminals - IOUTAP/N, IOUTBP/N, IOUTCP/N, IOUTDP/N                                                                                                                                                                                 | 9        |

| • | Added additional operation requirement for SLEEP pin if SLEEP pin is set to logic HIGH before and during device power up and initialization.                                                                                                                                         | 10       |

| • | Changed DACCLKP/N Differential voltage TYP value from 1.0 V to 0.8 V                                                                                                                                                                                                                 | 14       |

| • | Changed the parameter name Single-Ended Swing Level to Single-Ended Input Level to better reflect the specification for minimum recommended single-ended voltage level.                                                                                                              | 14       |

| • | Changed OSTRP/N Differential voltage TYP value from 1.0 V to 0.8 V                                                                                                                                                                                                                   | 14       |

| • | Changed the parameter name Single-Ended Swing Level to Single-Ended Input Level to better reflect the specification for minimum recommended single-ended voltage level.                                                                                                              | 14       |

| • | Changed Standard high swing note for <i>Electrical Characteristics – Digital Specifications</i>                                                                                                                                                                                      | 14       |

| • | Added Minimum voltage note for Electrical Characteristics – Digital Specifications                                                                                                                                                                                                   | 14       |

| • | Added LMK0480x family to note for <i>Timing Requirements – Digital Specifications</i>                                                                                                                                                                                                | 16       |

| • | Added text to Input FIFO section                                                                                                                                                                                                                                                     | 32       |

| • | Changed syncsel_fifoout(3:0) description in Input FIFO section to clarify the FIFO read pointer reset capture method                                                                                                                                                                 | 22       |

Submit Documentation Feedback

Copyright © 2011–2015, Texas Instruments Incorporated

| •  | Added Note to Input FIFO section                                                                                                                       | 33                 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| •  | Added LMK0480x family to Input FIFO section                                                                                                            | 33                 |

| •  | Changed text in Single Sync Source Mode to clarify the latency limitation of Single Sync Source Mode                                                   | 35                 |

| •  | Added the effect of bypassing the FIFO in the Bypass Mode section to clarify the operation of the FIFO, LVDS FRAME, and LVDS SYNC in FIFO Bypass Mode. | 35                 |

| •  | Added package information for LPF pin in PLL Mode section                                                                                              | 37                 |

| •  | Changed table reference in FIR Filters section                                                                                                         | 38                 |

| •  | Added text to Data Pattern Checker section with additional operating recommendations.                                                                  | 49                 |

| •  | Added reference to application report in DAC3484 Alarm Monitoring section                                                                              | 53                 |

| •  | Added note to Figure 80                                                                                                                                | 54                 |

| •  | Added Unused LVDS Port Termination section                                                                                                             | 55                 |

| •  | Changed information to Multi-Device Operation: Single Sync Source mode section to clarify the latency limitation of Single Sync Source Mode.           | 61                 |

| •  | Changed Figure 90 to clarify the latency limitation of Single Sync Source Mode.                                                                        | 62                 |

| •  | Changed the NCO setting description in the Example Start-up Sequence Section to reflect the example register writes                                    | s. <mark>64</mark> |

| •  | Added A32 to A32 for DAC3484IRKD and N9 for DAC3484IZAY in register config3 bit 0 description                                                          | 70                 |

| •  | Changed alarm_lparity to alarm_fparity in register config7                                                                                             | 72                 |

| •  | Changed QMC offset registers to QMC correction registers in register config16                                                                          | 74                 |

| •  | Added SLEEP pin information to register config27 bit 11                                                                                                | 77                 |

| •  | Changed 1.2VDIG to DIGVDD in register config27 bits 5:0                                                                                                | 77                 |

| •  | Changed 1.2VCLK to CLKVDD in register config27 bits 5:0                                                                                                |                    |

| •  | Added pin description for both packages in register config35                                                                                           | 80                 |

| •  | Added reference to Digital Input Timing Specifications Table in register config36                                                                      | 80                 |

| •  | Added text to register config45 bit 0 description                                                                                                      | 81                 |

| CI | hanges from Revision B (February) to Revision C  Deleted T <sub>J</sub> row from top of thermal table                                                  | Page               |

| •  | Added thermal information to the Absolute Maximum Ratings table                                                                                        |                    |

| •  | Added Recommended Operating Conditions table                                                                                                           |                    |

|    | Deleted T <sub>J</sub> row from top of thermal table                                                                                                   |                    |

| •  | Deleted OPERATING RANGE section from bottom of Electrical Characteristics – DC Specifications table                                                    |                    |

| _  | Deleted OF ENATING NAMES Section from bottom of Electrical Characteristics – DC Specifications table                                                   | 10                 |

| CI | hanges from Revision A (July 2011) to Revision B                                                                                                       | Page               |

| •  | Changed the revision from A, July 2011 to B, June 2012                                                                                                 | 1                  |

| •  | Changed Package options in FEATURES                                                                                                                    | 1                  |

| •  | Added ZAY package information to Thermal Information                                                                                                   | 2                  |

| •  | Added ZAY package                                                                                                                                      | 8                  |

| •  | Added ZAY pin functions                                                                                                                                | 9                  |

| •  | Added ZAY package information to Thermal Information                                                                                                   | 12                 |

| •  | Added Input Common Mode max value of 1.6V                                                                                                              | 14                 |

| •  | Added information to CLOCK INPUT (DACCLKP/N) in Electrical Characteristics – Digital Specifications                                                    | 14                 |

| •  | Added information to OUTPUT STROBE (OSTRP/N) in Electrical Characteristics – Digital Specifications                                                    | 14                 |

| •  |                                                                                                                                                        |                    |

|    | Changed Electrical Characteristics – AC Specifications AC Performance information                                                                      | 15                 |

| •  | Changed Electrical Characteristics – AC Specifications AC Performance information                                                                      |                    |

| •  |                                                                                                                                                        | 20                 |

#### **DAC3484**

| SLA | AS749E - MARCH 2011-REVISED NOVEMBER 2015                                                                                 | www.ti.com |

|-----|---------------------------------------------------------------------------------------------------------------------------|------------|

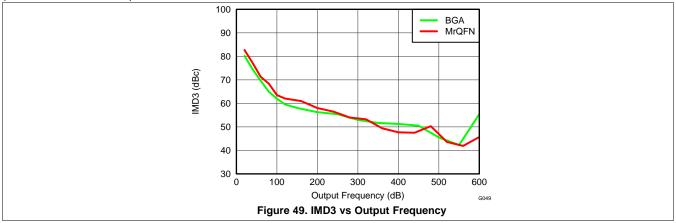

| •   | Added Figure 48                                                                                                           | 24         |

| •   | Added Figure 49                                                                                                           | 25         |

| •   | Changed config 3 to config9 in Input FIFO section                                                                         | 32         |

| •   | Added information for double-charge-pump current to PLL MODE section                                                      | 37         |

| •   | Changed Figure 71                                                                                                         | 43         |

| •   | Changed +3.75 to -3.75 degrees in 1024 steps to +26.5 to -26.5 degrees in 4096 steps in GAIN AND PHASE CORRECTION section |            |

| •   | Added dual channel mode enable information to POWER-UP SEQUENCE step 6                                                    | 62         |

| •   | Changed config1, bit 8 in Table 11                                                                                        | 66         |

| •   | Changed config16, bits 13:12 in Table 11                                                                                  | 66         |

| •   | Changed register config1, bit8 from Reserved to quad_ena                                                                  | 69         |

| •   | Changed register config16, bits 13:12 from reserved to dual_ena (1:0)                                                     |            |

| Ch  | nanges from Original (March 2011) to Revision A                                                                           | Page       |

| •   | Changed from PRODUCT PREVIEW to PRODUCTION DATA                                                                           | 1          |

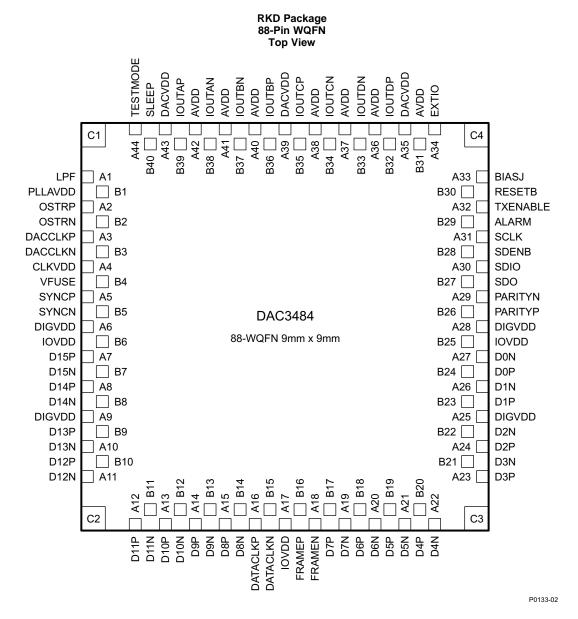

# 5 Pin Configuration and Functions

#### **Pin Functions - WQFN**

| PIN    |                                            | 1/0 | DESCRIPTION                                                                                                                                                                                                                     |  |  |  |

|--------|--------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME   | NO.                                        | 1/0 | DESCRIPTION                                                                                                                                                                                                                     |  |  |  |

| AVDD   | A36, A37,<br>A38, A40,<br>A41, A42,<br>B31 | 1   | Analog supply voltage. (3.3 V)                                                                                                                                                                                                  |  |  |  |

| ALARM  | B29                                        | 0   | CMOS output for ALARM condition. The ALARM output functionality is defined through the <i>config7</i> register. Default polarity is active high, but can be changed to active low via <i>config0</i> alarm_out_pol control bit. |  |  |  |

| BIASJ  | A33                                        | 0   | Full-scale output current bias. For 30-mA full-scale output current, connect 1.28 k $\Omega$ to ground. Change the full-scale output current through $coarse\_dac(3:0)$ in $config3$ , $bit<15:12>$                             |  |  |  |

| CLKVDD | A4                                         | I   | Internal clock buffer supply voltage. (1.2 V) It is recommended to isolate this supply from DIGVDD and DACVDD.                                                                                                                  |  |  |  |

# Pin Functions - WQFN (continued)

| PIN      |                                                                                                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME NO. |                                                                                                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

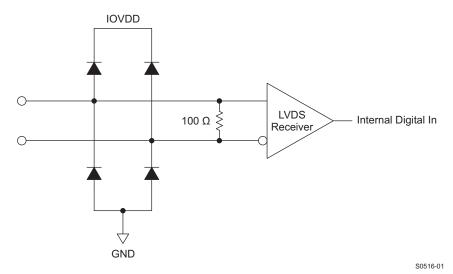

|          | A7, A8, B9,<br>B10, A12,                                                                          |     | LVDS positive input data bits 0 through 15. Internal 100-Ω termination resistor. Data format relative to DATACLKP/N clock is Double Data Rate (DDR).                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| D[150]P  | A13, A14,<br>A15, B17,<br>B18, B19,                                                               | ı   | D15P is most significant data bit (MSB) D0P is least significant data bit (LSB)                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|          | B20, A23,<br>A24, B23,<br>B24                                                                     |     | The order of the bus can be reversed via config2 revbus bit.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| D[150]N  | B7, B8, A10,<br>A11, B11,<br>B12, B13,<br>B14, A19,<br>A20, A21,<br>A22, B21,<br>B22, A26,<br>A27 | I   | LVDS negative input data bits 0 through 15. (See D[15:0]P description above)                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

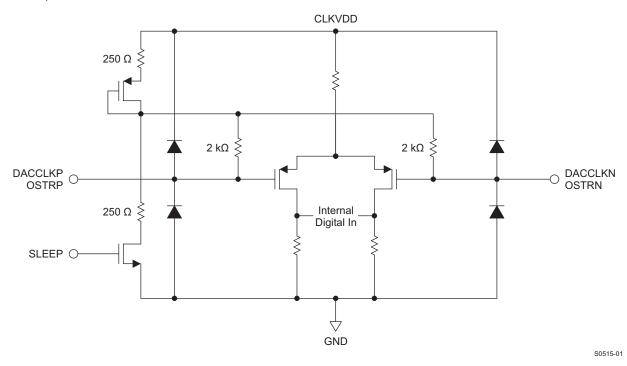

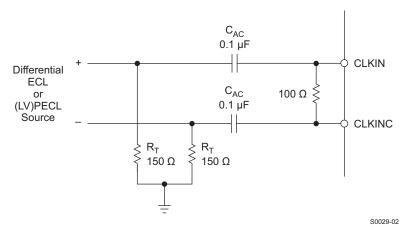

| DACCLKP  | А3                                                                                                | I   | Positive external LVPECL clock input for DAC core with a self-bias.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| DACCLKN  | В3                                                                                                | I   | Complementary external LVPECL clock input for DAC core. (see the DACCLKP description)                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| DACVDD   | A35, A39,<br>A43                                                                                  | I   | DAC core supply voltage. (1.2 V). It is recommended to isolate this supply from CLKVDD and DIGVDD.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| DATACLKP | A16                                                                                               | I   | LVDS positive input data clock. Internal 100 $\Omega$ termination resistor. Input data D[15:0]P/N is latched on both edges of DATACLKP/N (Double Data Rate).                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| DATACLKN | B15                                                                                               | I   | LVDS negative input data clock. (See DATACLKP description)                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| DIGVDD   | A6, A9, A25,<br>A28                                                                               | I   | Digital supply voltage. (1.2 V). It is recommended to isolate this supply from CLKVDD and DACVDD.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| EXTIO    | A34                                                                                               | I/O | Used as external reference input when internal reference is disabled through <i>config27 extref_ena</i> 1b. Used as internal reference output when <i>config27 extref_ena</i> = 0b (default). Requires a 0.1-µF decoupling capacitor to AGND when used as reference output.                                                                                                                                                                                            |  |  |  |  |  |

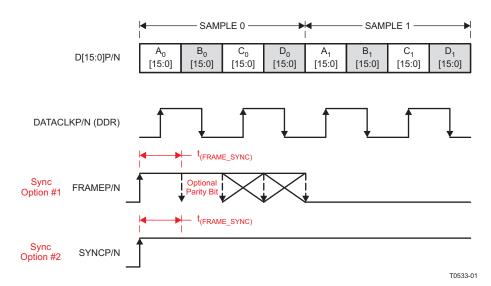

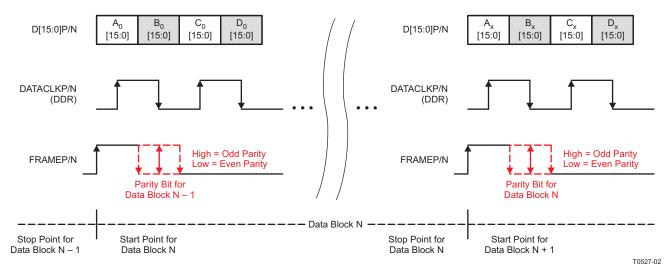

| FRAMEP   | B16                                                                                               | I   | LVDS frame indicator positive input. Internal 100-Ω termination resistor. The main functions of this input are to reset the FIFO pointer or to be used as a syncing source. These two functions are captured with the rising edge of DATACLKP/N. The signal captured by the falling edge of DATACLKP/N can be used as a block parity bit. The FRAMEP/N signal should be edge-aligned with D[15:0]P/N.  Additionally it is used to indicate the beginning of the frame. |  |  |  |  |  |

| FRAMEN   | A18                                                                                               | ı   | LVDS frame indicator negative input. (See the FRAMEP description)                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GND      | C1, C2, C3,<br>C4, Thermal<br>Pad                                                                 | I   | These pins are ground for all supplies.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

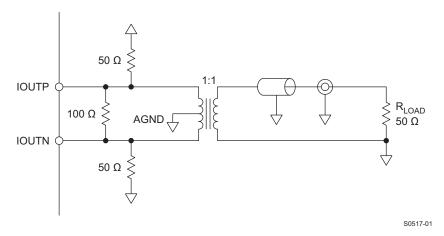

| IOUTAP   | B39                                                                                               | 0   | A-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| IOUTAN   | B38                                                                                               | 0   | A-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IOUTBP   | B36                                                                                               | 0   | B-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| IOUTBN   | B37                                                                                               | 0   | B-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IOUTCP   | B35                                                                                               | 0   | C-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| IOUTCN   | B34                                                                                               | 0   | C-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IOUTDP   | B32                                                                                               | 0   | D-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| IOUTDN   | B33                                                                                               | 0   | D-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IOVDD    | B6, A17, B25                                                                                      | I   | Supply voltage for all digital I/O. (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| LPF      | A1<br>A2                                                                                          | I/O | PLL loop filter connection. If not using the clock multiplying PLL, the LPF pin can be left unconnected.  LVPECL output strobe positive input. This positive/negative pair is captured with the rising edge of                                                                                                                                                                                                                                                         |  |  |  |  |  |

|          |                                                                                                   |     | DACCLKP/N. It is used for multiple DAC synchronization. If unused it can be left unconnected.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| OSTRN    | B2                                                                                                | I   | LVPECL output strobe negative input. (See the OSTRP description)                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| PARITYP  | B26                                                                                               | l   | Optional LVDS positive input parity bit. The PARITYP/N LVDS pair has an internal 100 $\Omega$ termination resistor. If unused it can be left unconnected.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PARITYN  | A29                                                                                               | 1   | Optional LVDS negative input parity bit.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PLLAVDD  | B1                                                                                                | I   | PLL analog supply voltage. (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

# Pin Functions - WQFN (continued)

| PIN      |     | 1/0 | D                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

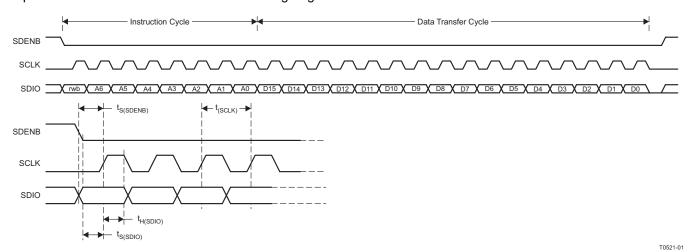

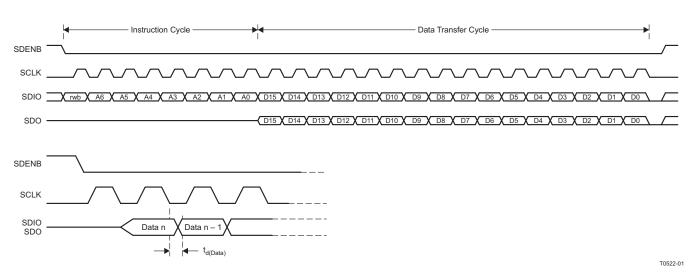

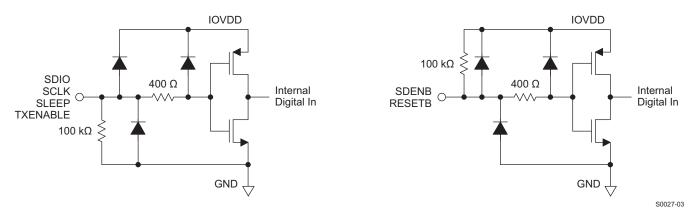

| SCLK     | A31 | I   | Serial interface clock. Internal pull-down.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| SDENB    | B28 | I   | Active low serial data enable, always an input to the DAC3484. Internal pull-up.                                                                                                                                                                                                                                                               |  |  |  |  |

| SDIO     | A30 | I/O | Serial interface data. Bi-directional in 3-pin mode (default) and uni-directional 4-pin mode. Internal pull-down.                                                                                                                                                                                                                              |  |  |  |  |

| SDO      | B27 | 0   | Uni-directional serial interface data in 4-pin mode. The SDO pin is tri-stated in 3-pin interface mode (default).                                                                                                                                                                                                                              |  |  |  |  |

| SLEEP    | B40 | 1   | Active high asynchronous hardware power-down input. Internal pull-down. If SLEEP pin is set to logic HIGH before and during device power-up and initialization, the fuse_sleep bit in register 0x1B, bit 11 must be written after register 0x23 during device initialization register setup.                                                   |  |  |  |  |

| SYNCP    | A5  | 1   | Optional LVDS SYNC positive input. The SYNCP/N LVDS pair has an internal 100-Ω termination resistor. If unused it can be left unconnected.                                                                                                                                                                                                     |  |  |  |  |

| SYNCN    | B5  | ı   | Optional LVDS SYNC negative input.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RESETB   | B30 | I   | Active low input for chip RESET, which resets all the programming registers to their default state. Internal pull-up.                                                                                                                                                                                                                          |  |  |  |  |

| TXENABLE | A32 | ı   | Transmit enable active high input. Internal pull-down.  To enable analog output data transmission, set <i>sif_txenable</i> in register <i>config3</i> to 1b <b>or</b> pull CMOS TXENABLE pin to high.  To disable analog output, set <i>sif_txenable</i> to 0b <b>and</b> pull CMOS TXENABLE pin to low. The DAC output is forced to midscale. |  |  |  |  |

| TESTMODE | A44 | I   | This pin is used for factory testing. Internal pull-down. Leave unconnected for normal operation.                                                                                                                                                                                                                                              |  |  |  |  |

| VFUSE    | B4  | 1   | Digital supply voltage. This supply pin is also used for factory fuse programming. Connect to DACVDD for normal operation.                                                                                                                                                                                                                     |  |  |  |  |

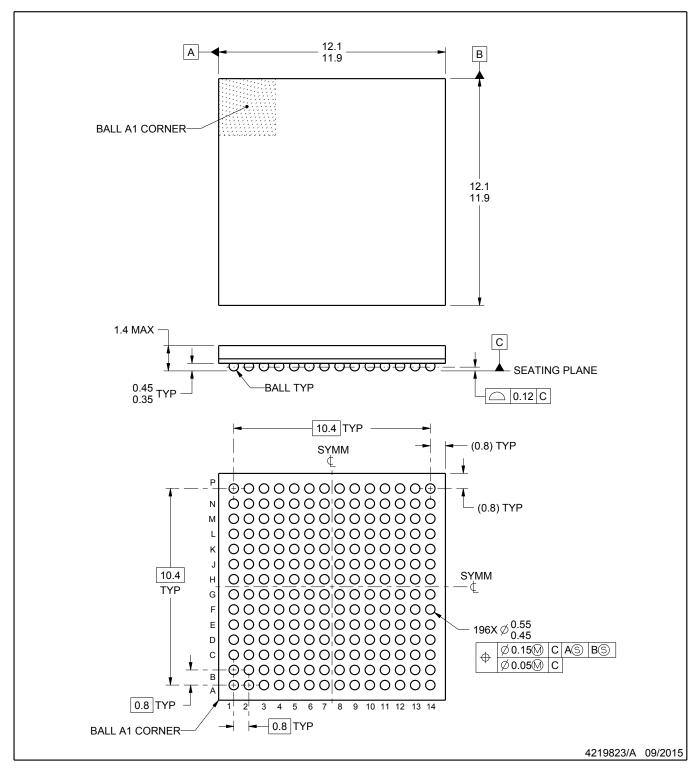

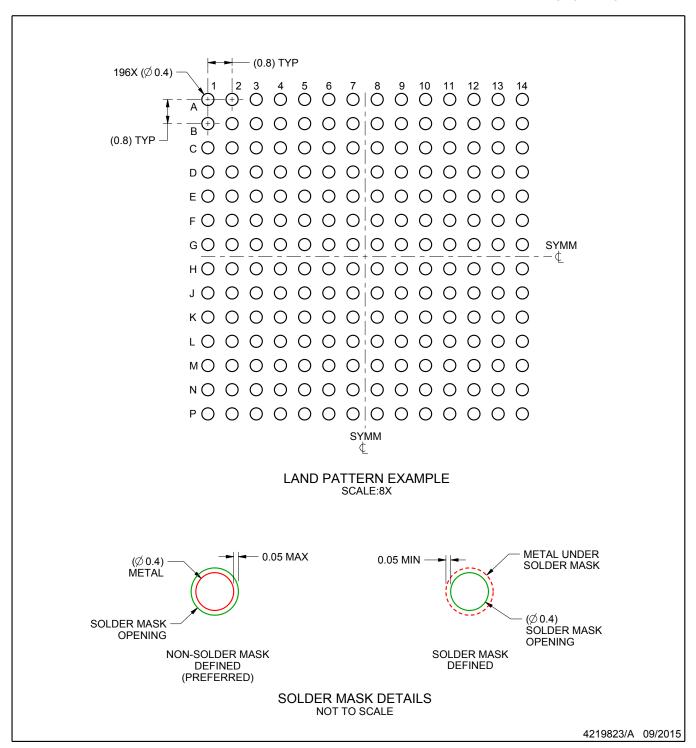

## ZAY Package 196-Pin NFBGA Top View

|    |              |            |             |             |            |            | TOP V        | IEW        |            |            |            |            |              |             |

|----|--------------|------------|-------------|-------------|------------|------------|--------------|------------|------------|------------|------------|------------|--------------|-------------|

|    | Α            | В          | С           | D           | E          | F          | G            | Н          | J          | K          | L          | М          | N            | Р           |

| 14 | GND          | IOUT<br>AP | IOUT<br>AN  | GND         | IOUT<br>BN | IOUT<br>BP | GND          | GND        | IOUT<br>CP | IOUT<br>CN | GND        | IOUT<br>DN | IOUT<br>DP   | GND         |

| 13 | GND          | GND        | GND         | GND         | GND        | GND        | GND          | GND        | GND        | GND        | GND        | GND        | GND          | GND         |

| 12 | DAC<br>CLKP  | GND        | CLK<br>VDD  | LPF         | GND        | GND        | EXTIO        | BIASJ      | GND        | N/C        | N/C        | GND        | ALARM        | SDO         |

| 11 | DAC<br>CLKN  | GND        | PLL<br>AVDD | PLL<br>AVDD | AVDD       | AVDD       | AVDD         | AVDD       | AVDD       | AVDD       | N/C        | GND        | N/C          | SDIO        |

| 10 | GND          | GND        | GND         | AVDD        | DAC<br>VDD | DAC<br>VDD | DAC<br>VDD   | DAC<br>VDD | DAC<br>VDD | DAC<br>VDD | AVDD       | GND        | RESET<br>B   | SDENB       |

| 9  | OS<br>TRP    | OS<br>TRN  | GND         | DAC<br>VDD  | DAC<br>VDD | GND        | GND          | GND        | GND        | DAC<br>VDD | DAC<br>VDD | GND        | TX<br>ENABLE | SCLK        |

| 8  | TEST<br>MODE | SLEEP      | GND         | GND         | GND        | GND        | GND          | GND        | GND        | GND        | GND        | GND        | N/C          | N/C         |

| 7  | N/C          | N/C        | GND         | VFUSE       | DIG<br>VDD | GND        | GND          | GND        | GND        | DIG<br>VDD | N/C        | GND        | N/C          | N/C         |

| 6  | N/C          | N/C        | GND         | IO<br>VDD   | DIG<br>VDD | GND        | GND          | GND        | GND        | DIG<br>VDD | IO<br>VDD  | GND        | N/C          | N/C         |

| 5  | SYNCP        | SYNCN      | GND         | IO<br>VDD   | DIG<br>VDD | DIG<br>VDD | IO<br>VDD    | IO<br>VDD  | DIG<br>VDD | DIG<br>VDD | IO<br>VDD  | GND        | PARITY<br>P  | PARITY<br>N |

| 4  | D15P         | D15N       | N/C         | N/C         | N/C        | N/C        | N/C          | N/C        | N/C        | N/C        | N/C        | N/C        | D0P          | D0N         |

| 3  | D14P         | D14N       | N/C         | N/C         | N/C        | N/C        | N/C          | N/C        | N/C        | N/C        | N/C        | N/C        | D1P          | D1N         |

| 2  | D13P         | D13N       | D11P        | D10P        | D9P        | D8P        | DATA<br>CLKP | FRAME<br>P | D7P        | D6P        | D5P        | D4P        | D2P          | D2N         |

| 1  | D12P         | D12N       | D11N        | D10N        | D9N        | D8N        | DATA<br>CLKN | FRAME<br>N | D7N        | D6N        | D5N        | D4N        | D3P          | D3N         |

|    |              |            |             |             |            |            |              |            |            |            |            |            |              |             |

Product Folder Links: DAC3484

P0134-02

#### **Pin Functions - NFBGA**

| PIN      |                                                                                                                                                                                                                                                                                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.                                                                                                                                                                                                                                                                               | Ņ   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AVDD     | D10, E11, F11, G11,<br>H11, J11, K11, L10                                                                                                                                                                                                                                         | I   | Analog supply voltage. (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| ALARM    | N12                                                                                                                                                                                                                                                                               | 0   | CMOS output for ALARM condition. The ALARM output functionality is defined through the config7 register. Default polarity is active low, but can be changed to active high via config0 alarm_out_pol control bit.                                                                                                                                                                                                                                                            |  |  |  |

| BIASJ    | H12                                                                                                                                                                                                                                                                               | 0   | Full-scale output current bias. For 30-mA full-scale output current, connect 1.28 k $\Omega$ to ground. Change the full-scale output current through $coarse\_dac(3:0)$ in $config3$ , $bit<15:12>$                                                                                                                                                                                                                                                                          |  |  |  |

| CLKVDD   | C12                                                                                                                                                                                                                                                                               | I   | Internal clock buffer supply voltage. (1.2 V) It is recommended to isolate this supply from DIGVDD and DACVDD.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| D[150]P  | N4, N3, N2, N1, M2, L2,<br>K2, J2, F2, E2, D2, C2,                                                                                                                                                                                                                                | I   | LVDS positive input data bits 0 through 15. Internal 100-Ω termination resistor. Data format relative to DATACLKP/N clock is Double Data Rate (DDR).  D15P is most significant data bit (MSB)                                                                                                                                                                                                                                                                                |  |  |  |

|          | A1, A2, A3, A4                                                                                                                                                                                                                                                                    |     | D0P is least significant data bit (LSB)  The order of the bus can be reversed via <i>config2 revbus</i> bit.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D[150]N  | P4, P3, P2, P1, M1, L1,<br>K1, J1, F1, E1, D1, C1,<br>B1, B2, B3, B4                                                                                                                                                                                                              | I   | LVDS negative input data bits 0 through 15. (See D[15:0]P description above)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DACCLKP  | A12                                                                                                                                                                                                                                                                               | I   | Positive external LVPECL clock input for DAC core with a self-bias.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACCLKN  | A11                                                                                                                                                                                                                                                                               | I   | Complementary external LVPECL clock input for DAC core. (see the DACCLKP description)                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| DACVDD   | D9, E9, E10, F10, G10,<br>H10, J10, K9, K10, L9                                                                                                                                                                                                                                   | I   | DAC core supply voltage. (1.2 V). It is recommended to isolate this supply from CLKVDD and DIGVDD.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| DATACLKP | G2                                                                                                                                                                                                                                                                                | _   | LVDS positive input data clock. Internal 100- $\Omega$ termination resistor. Input data D[15:0]P/N is latched on both edges of DATACLKP/N (Double Data Rate).                                                                                                                                                                                                                                                                                                                |  |  |  |

| DATACLKN | G1                                                                                                                                                                                                                                                                                | Ι   | LVDS negative input data clock. (See DATACLKP description)                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| DIGVDD   | E5, E6, E7, F5, J5, K5,<br>K6, K7                                                                                                                                                                                                                                                 | I   | Digital supply voltage. (1.2 V). It is recommended to isolate this supply from CLKVDD and DACVDD.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| EXTIO    | G12                                                                                                                                                                                                                                                                               | I/O | Used as external reference input when internal reference is disabled through <i>config27</i> extref_ena = 1b. Used as internal reference output when <i>config27</i> extref_ena = 0b (default). Requires a 0.1-µF decoupling capacitor to AGND when used as reference output.                                                                                                                                                                                                |  |  |  |

| FRAMEP   | H2                                                                                                                                                                                                                                                                                | I   | LVDS frame indicator positive input. Internal $100-\Omega$ termination resistor. The main functions of this input are to reset the FIFO pointer or to be used as a syncing source. These two functions are captured with the rising edge of DATACLKP/N. The signal captured by the falling edge of DATACLKP/N can be used as a block parity bit. The FRAMEP/N signal should be edge-aligned with D[15:0]P/N. Additionally it is used to indicate the beginning of the frame. |  |  |  |

| FRAMEN   | H1                                                                                                                                                                                                                                                                                | I   | LVDS frame indicator negative input. (See the FRAMEP description)                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| GND      | A10, A13, A14, B10, B11, B12, B13, C5, C6, C7, C8, C9, C10, C13, D8, D13, D14, E8, E12, E13, F6, F7, F8, F9, F12, F13, G6, G7, G8, G9, G13, G14, H6, H7, H8, H9, H13, H14, J6, J7, J8, J9, J12, J13, K8, K13, L8, L13, L14, M5, M6, M7, M8, M9, M10, M11, M12, M13, N13, P13, P14 | I   | These pins are ground for all supplies.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| IOUTAP   | B14                                                                                                                                                                                                                                                                               | 0   | A-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| IOUTAN   | C14                                                                                                                                                                                                                                                                               | 0   | A-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| IOUTBP   | F14                                                                                                                                                                                                                                                                               | 0   | B-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| IOUTBN   | E14                                                                                                                                                                                                                                                                               | 0   | B-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| IOUTCP   | J14                                                                                                                                                                                                                                                                               | 0   | C-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

# Pin Functions - NFBGA (continued)

| PIN      |                        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NAME NO.               |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IOUTCN   | K14                    | 0   | C-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                              |  |  |  |

| IOUTDP   | N14                    | 0   | D-Channel DAC current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                                            |  |  |  |

| IOUTDN   | M14                    | 0   | D-Channel DAC complementary current output. Connect directly to ground if unused.                                                                                                                                                                                                                                                              |  |  |  |

| IOVDD    | D5, D6, G5, H5, L5, L6 | Ι   | Supply voltage for all digital I/O. (3.3 V)                                                                                                                                                                                                                                                                                                    |  |  |  |

| LPF      | D12                    | I   | PLL loop filter connection. If not using the clock multiplying PLL, the LPF pin can be left unconnected.                                                                                                                                                                                                                                       |  |  |  |

| OSTRP    | A9                     | I   | LVPECL output strobe positive input. This positive/negative pair is captured with the risin edge of DACCLKP/N. It is used for multiple DAC synchronization. If unused it can be left unconnected.                                                                                                                                              |  |  |  |

| OSTRN    | B9                     | Ι   | LVPECL output strobe negative input. (See the OSTRP description)                                                                                                                                                                                                                                                                               |  |  |  |

| PARITYP  | N5                     | -   | Optional LVDS positive input parity bit. The PARITYP/N LVDS pair has an internal $100-\Omega$ termination resistor. If unused it can be left unconnected.                                                                                                                                                                                      |  |  |  |

| PARITYN  | P5                     | Ι   | Optional LVDS negative input parity bit.                                                                                                                                                                                                                                                                                                       |  |  |  |

| PLLAVDD  | C11, D11               | I   | PLL analog supply voltage. (3.3 V)                                                                                                                                                                                                                                                                                                             |  |  |  |

| SCLK     | P9                     | Ι   | Serial interface clock. Internal pull-down.                                                                                                                                                                                                                                                                                                    |  |  |  |

| SDENB    | P10                    | Ι   | Active low serial data enable, always an input to the DAC3484. Internal pull-up.                                                                                                                                                                                                                                                               |  |  |  |

| SDIO     | P11                    | I/O | Serial interface data. Bi-directional in 3-pin mode (default) and 4-pin mode. Internal pull-down.                                                                                                                                                                                                                                              |  |  |  |

| SDO      | P12                    | 0   | Uni-directional serial interface data in 4-pin mode. The SDO pin is three-stated in 3-pin interface mode (default).                                                                                                                                                                                                                            |  |  |  |

| SLEEP    | B8                     | I   | Active high asynchronous hardware power-down input. Internal pull-down. If SLEEP pin is set to logic HIGH before and during device power-up and initialization, the fuse_sleep bit in register 0x1B, bit 11 must be written after register 0x23 during device initialization register setup.                                                   |  |  |  |

| SYNCP    | A5                     | I   | Optional LVDS SYNC positive input. The SYNCP/N LVDS pair has an internal $100-\Omega$ termination resistor. If unused it can be left unconnected.                                                                                                                                                                                              |  |  |  |

| SYNCN    | B5                     | Ι   | LVDS SYNC negative input.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RESETB   | N10                    | ı   | Active low input for chip RESET, which resets all the programming registers to their default state. Internal pull-up.                                                                                                                                                                                                                          |  |  |  |

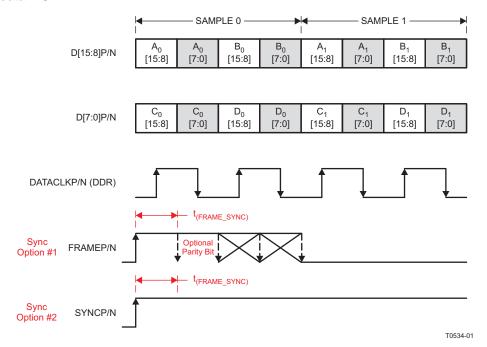

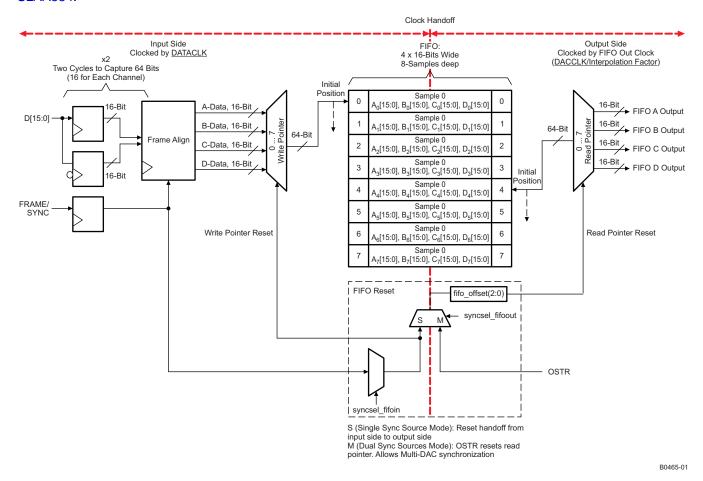

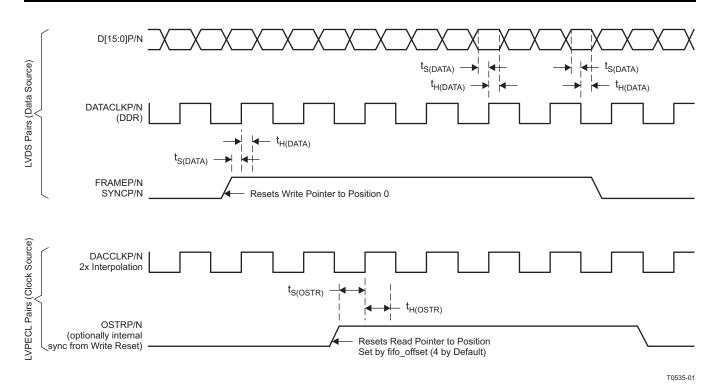

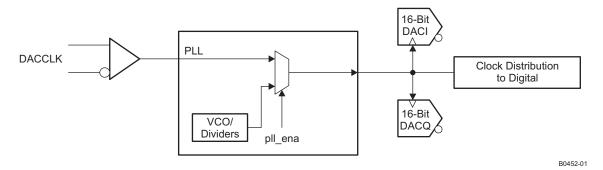

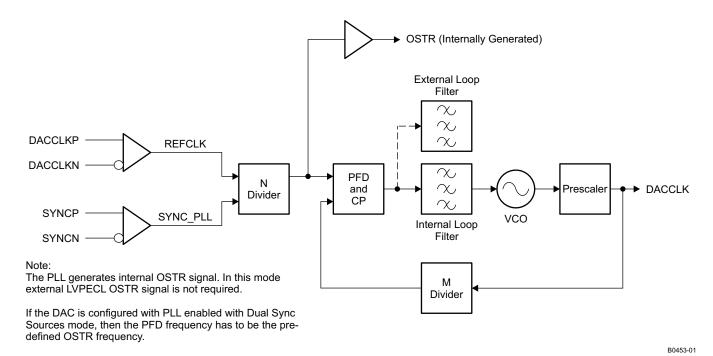

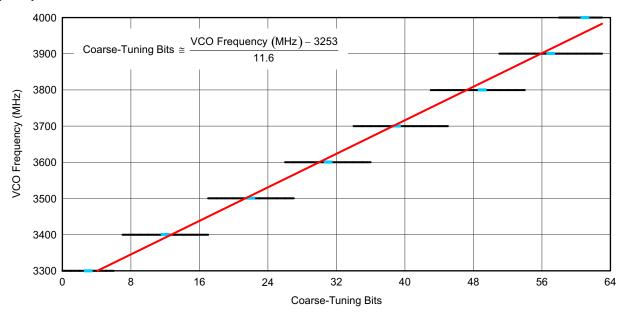

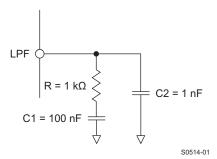

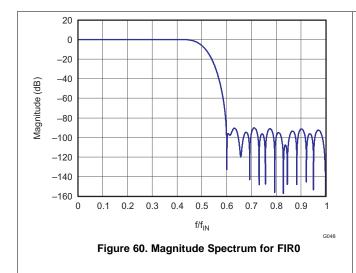

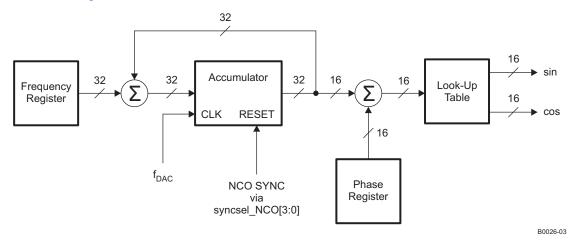

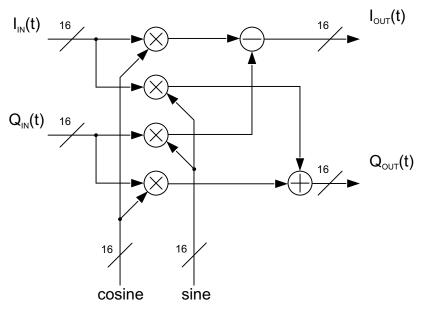

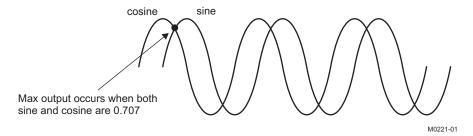

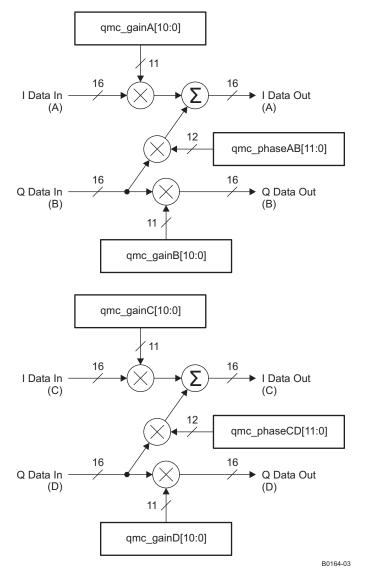

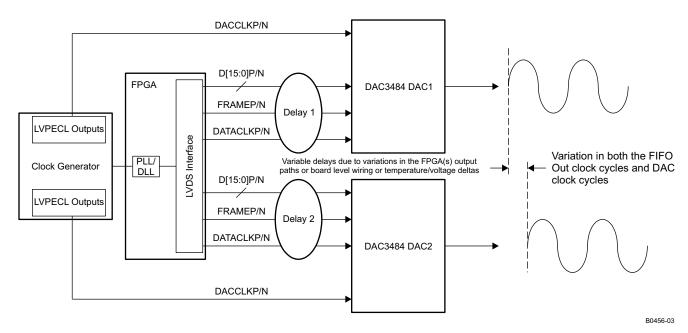

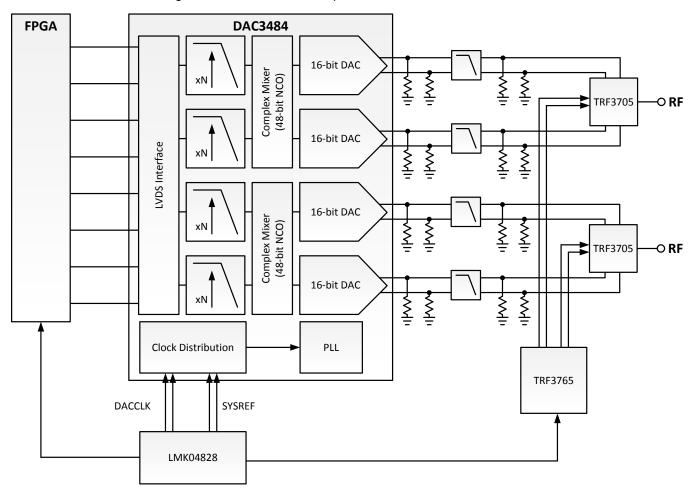

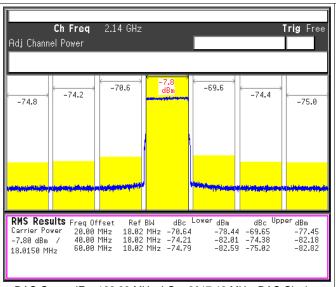

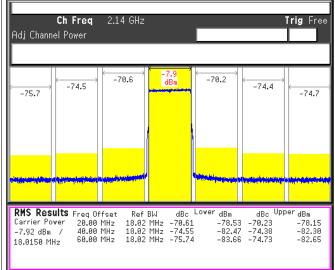

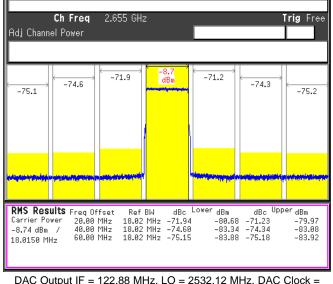

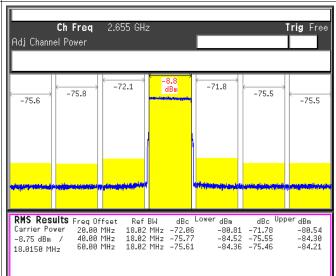

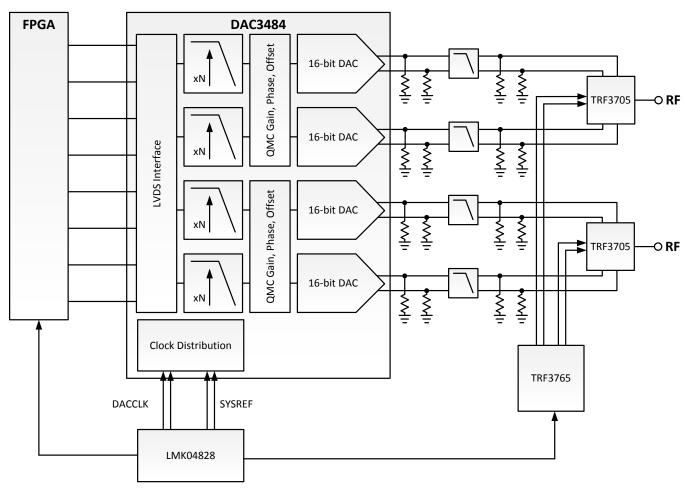

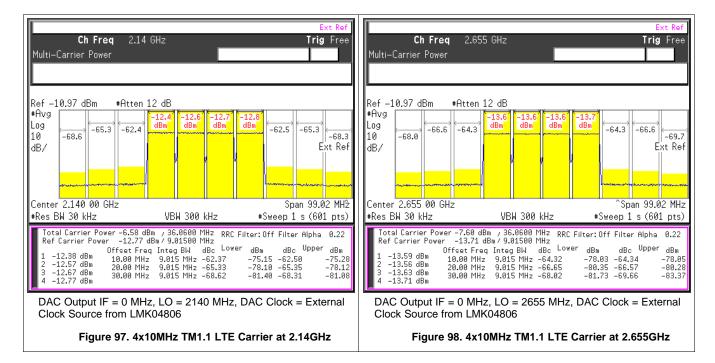

| TXENABLE | N9                     | I   | Transmit enable active high input. Internal pull-down.  To enable analog output data transmission, set <i>sif_txenable</i> in register <i>config3</i> to 1b <b>or</b> pull CMOS TXENABLE pin to high.  To disable analog output, set <i>sif_txenable</i> to 0b <b>and</b> pull CMOS TXENABLE pin to low. The DAC output is forced to midscale. |  |  |  |