## Features

- Integrated high-voltage start-up

- 4 drivers for PFC, half-bridge & pre-heating MOSFETs

- Fully integrated power management for all operating modes

- 5V microcontroller compatible

- Internal two point  $V_{CC}$  regulator

- Over-current protection with digital output signal

- Cross-conduction protection (interlocking)

- Under voltage lock-out

- Integrated bootstrap diode

## Applications

- Dimmable / non-dimmable ballast

## Description

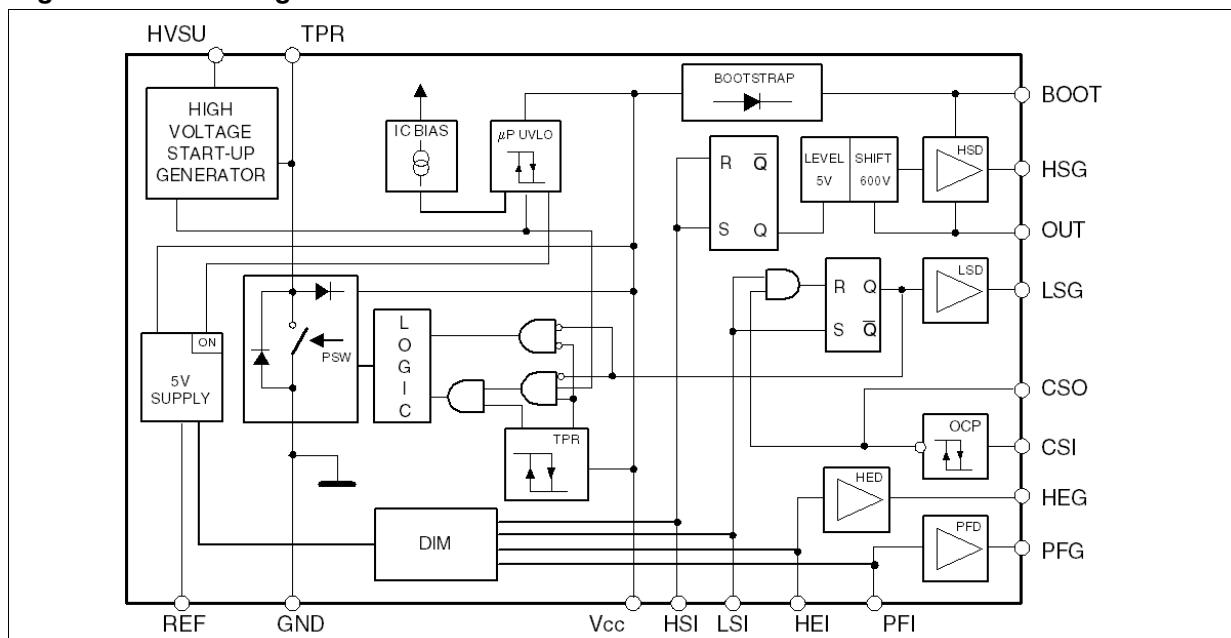

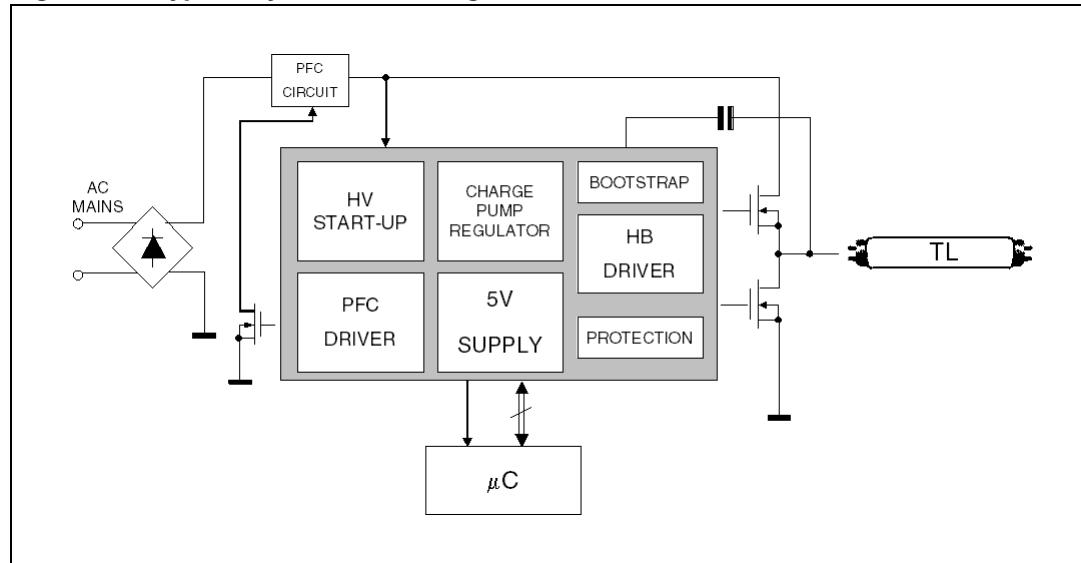

The L6382D5 is suitable for microcontrolled electronic ballasts embedding a PFC stage and a half-bridge stage. The L6382D5 includes 4 MOSFET driving stages (for the PFC, for the half bridge, for the preheating MOSFET) plus a power management unit (PMU) featuring also a reference able to supply the microcontroller in any condition.

Besides increasing the application efficiency, the L6382D5 reduces the bill of materials because different tasks (regarding drivers and power management) are performed by a single IC, which improves the application reliability.

**Figure 1. Block diagram**

## Contents

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Device description</b>                                               | <b>3</b>  |

| <b>2</b> | <b>Pin settings</b>                                                     | <b>4</b>  |

| 2.1      | Pin connection                                                          | 4         |

| 2.2      | Pin description                                                         | 4         |

| <b>3</b> | <b>Maximum ratings</b>                                                  | <b>6</b>  |

| 3.1      | Absolute maximum ratings                                                | 6         |

| 3.2      | Thermal data                                                            | 6         |

| <b>4</b> | <b>Electrical characteristics</b>                                       | <b>7</b>  |

| <b>5</b> | <b>Application information</b>                                          | <b>11</b> |

| 5.1      | Power management                                                        | 11        |

| 5.2      | START-UP mode                                                           | 11        |

| 5.2.1    | SAVE Mode                                                               | 12        |

| 5.2.2    | OPERATING Mode                                                          | 12        |

| 5.2.3    | Shut Down                                                               | 12        |

| <b>6</b> | <b>Block description</b>                                                | <b>15</b> |

| 6.1      | Supply section                                                          | 15        |

| 6.2      | 5V reference voltage                                                    | 15        |

| 6.3      | Drivers                                                                 | 16        |

| 6.4      | Internal logic, over current protection (OCP) and interlocking function | 16        |

| <b>7</b> | <b>Package mechanical data</b>                                          | <b>17</b> |

| <b>8</b> | <b>Order codes</b>                                                      | <b>19</b> |

| <b>9</b> | <b>Revision history</b>                                                 | <b>20</b> |

## 1 Device description

Designed in High-voltage BCD Off-line technology, the L6382D5 is provided with 4 inputs pin and a high voltage start-up generator conceived for applications managed by a microcontroller. It allows the designer to use the same ballast circuit for different lamp wattage/type by simply changing the  $\mu$ C software.

The digital input pins - able to receive signals up to 400KHz - are connected to level shifters that provide the control signals to their relevant drivers; in particular the L6382D5 embeds one driver for the PFC pre-regulator stage, two drivers for the ballast half-bridge stage (High Voltage, including also the bootstrap function) and the last one to provide supplementary features like preheating of filaments supplied through isolated filaments in dimmable applications.

A precise reference voltage ( $+5V \pm 2\%$ ) able to provide up to 30mA is available to supply the  $\mu$ C in *operating* mode. Instead, during *start-up* and *save* mode the current available at  $V_{REF}$  is up to 10mA and it is provided by the internal high voltage start-up generator.

The chip has been conceived with advanced power management logic to minimize power losses and increase the application reliability.

In the half-bridge section, a patented integrated bootstrap section replaces the external bootstrap diode.

The L6382D5 integrates also a function that regulates the IC supply voltage (without the need of any external charge pump) and optimizes the current consumption.

**Figure 2. Typical system block diagram**

## 2 Pin settings

### 2.1 Pin connection

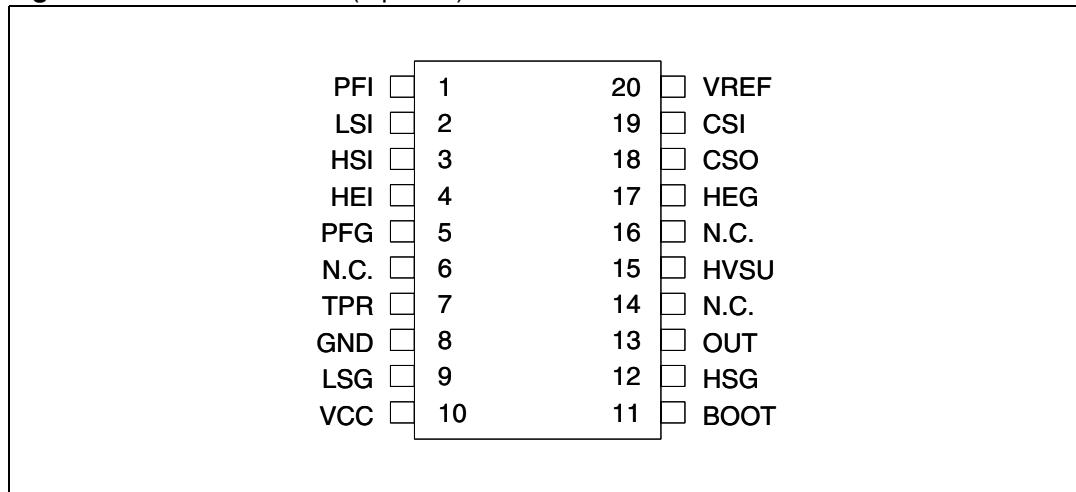

Figure 3. Pin connection (top view)

### 2.2 Pin description

Table 1. Pin description

| Name | Pin N° | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PFI    | Digital input signal to control the PFC gate driver. This pin has to be connected to a 5V CMOS compatible signal.                                                                                                                                                                                                                                                                       |

| 2    | LSI    | Digital input signal to control the half-bridge low side driver. This pin has to be connected to a 5V CMOS compatible signal.                                                                                                                                                                                                                                                           |

| 3    | HSI    | Digital input signal to control the half-bridge high side driver. This pin has to be connected to a 5V CMOS compatible signal.                                                                                                                                                                                                                                                          |

| 4    | HEI    | Digital input signal to control the HEG output. This pin has to be connected to a 5V CMOS compatible signal.                                                                                                                                                                                                                                                                            |

| 5    | PFG    | PFC Driver Output. This pin must be connected to the PFC power MOSFET gate. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current. An internal 10KΩ resistor toward ground avoids spurious and undesired MOSFET turn-on<br>The totem pole output stage is able to drive the power MOS with a peak current of 120mA source and 250mA sink. |

| 6    | N.C.   | Not connected                                                                                                                                                                                                                                                                                                                                                                           |

| 7    | TPR    | Input for two point regulator; by coupling the pin with a capacitor to a switching circuit, it is possible to implement a charge circuit for the Vcc.                                                                                                                                                                                                                                   |

| 8    | GND    | Chip ground. Current return for both the low-side gate-drive currents and the bias current of the IC. All of the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                                                                                                                                |

**Table 1. Pin description** (continued)

| Name | Pin N° | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9    | LSG    | Low Side Driver Output. This pin must be connected to the gate of the half-bridge low side power MOSFET. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.<br>An internal 20KΩ resistor toward ground avoids spurious and undesired MOSFET turn-on.<br>The totem pole output stage is able to drive power with a peak current of 120mA source and 120mA sink.                                                                                                                                                     |

| 10   | Vcc    | Supply Voltage for the signal part of the IC and for the drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11   | BOOT   | High-side gate-drive floating supply Voltage. The bootstrap capacitor connected between this pin and pin 13 (OUT) is fed by an internal synchronous bootstrap diode driven in phase with the low-side gate-drive. This patented structure normally replaces the external diode.                                                                                                                                                                                                                                                                                      |

| 12   | HSG    | High Side Driver Output. This pin must be connected to the gate of the half bridge high side power MOSFET . A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.<br>An internal 20KΩ resistor toward OUT pin avoids spurious and undesired MOSFET turn-on<br>The totem pole output stage is able to drive the power MOS with a peak current of 120mA source and 120mA sink.                                                                                                                                          |

| 13   | OUT    | High-side gate-drive floating ground. Current return for the high-side gate-drive current. Layout carefully the connection of this pin to avoid too large spikes below ground.                                                                                                                                                                                                                                                                                                                                                                                       |

| 14   | N.C.   | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15   | HVSU   | High-voltage start-up. The current flowing into this pin charges the capacitor connected between pin Vcc and GND to start up the IC. Whilst the chip is in <u>save</u> mode, the generator is cycled on-off between turn-on and <u>save</u> mode voltages. When the chip works in <u>operating</u> mode the generator is shut down and it is re-enabled when the Vcc voltage falls below the UVLO threshold. According to the required V <sub>REF</sub> pin current, this pin can be connected to the rectified mains voltage either directly or through a resistor. |

| 16   | N.C.   | High-voltage spacer. The pin is not connected internally to isolate the high-voltage pin and comply with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17   | HEG    | Output for the HEI block; this driver can be used to drive the MOS employed in isolated filaments preheating. An internal 20KΩ resistor toward ground avoids spurious and undesired MOSFET turn-on.                                                                                                                                                                                                                                                                                                                                                                  |

| 18   | CSO    | Output of current sense comparator, compatible with 5V CMOS logic; during <u>operating</u> mode, the pin is forced low whereas whenever the OC comparator is triggered (CSI> 0.55 typ.) the pin latches high.                                                                                                                                                                                                                                                                                                                                                        |

| 19   | CSI    | Input of current sense comparator, it is enabled only during <u>operating</u> mode; when the pin voltage exceeds the internal threshold, the CSO pin is forced high and the half bridge drivers are disabled. It exits from this condition by either cycling the Vcc below the UVLO or with LGI=HGI=low simultaneously.                                                                                                                                                                                                                                              |

| 20   | VREF   | Voltage reference. During <u>operating</u> mode an internal generator provides an accurate voltage reference that can be used to supply up to 30mA to an external circuit. A small film capacitor (0.22μF min.), connected between this pin and GND is recommended to ensure the stability of the generator and to prevent noise from affecting the reference.                                                                                                                                                                                                       |

## 3 Maximum ratings

### 3.1 Absolute maximum ratings

**Table 2. Absolute maximum ratings**

| Symbol                | Pin           | Parameter                                     | Value                   | Unit |

|-----------------------|---------------|-----------------------------------------------|-------------------------|------|

| $V_{CC}$              | 10            | IC supply voltage ( $ICC = 20\text{mA}$ )     | Self-limited            |      |

| $V_{HVSU}$            | 15            | High voltage start-up generator voltage range | -0.3 to 600             | V    |

| $V_{BOOT}$            | 11            | Floating supply voltage                       | -1 to $V_{HVSU}+V_{CC}$ | V    |

| $V_{OUT}$             | 13            | Floating ground voltage                       | -1 to 600               | V    |

| $I_{TPR(\text{RMS})}$ | 7             | Maximum TPR RMS current                       | $\pm 200$               | mA   |

| $I_{TPR(\text{PK})}$  | 7             | Maximum TPR peak current                      | $\pm 600$               | mA   |

| $V_{TPR}$             | 7             | Maximum TPR voltage <sup>(1)</sup>            | 14                      | V    |

|                       | 19            | CSI input voltage                             | -0.3 to 7               | V    |

|                       | 1, 2,<br>3, 4 | Logic input voltage                           | -0.3 to 7               | V    |

|                       | 9, 12,<br>17  | Operating frequency                           | 15 to 400               | KHz  |

|                       | 5             | Operating frequency                           | 15 to 600               | KHz  |

| $T_{\text{stg}}$      |               | Storage Temperature                           | -40 to +150             | °C   |

| $T_j$                 |               | Ambient Temperature operating range           | -40 to +125             | °C   |

1. Excluding *operating* mode

### 3.2 Thermal data

**Table 3. Thermal data**

| Symbol            | Parameter                                   | Value | Unit |

|-------------------|---------------------------------------------|-------|------|

| $R_{\text{thJA}}$ | Maximum thermal resistance junction-ambient | 120   | °C/W |

## 4 Electrical characteristics

**Table 4. Electrical characteristics** ( $T_J = 25^\circ\text{C}$ ,  $V_{CC} = 13\text{V}$ ,  $C_{DRIVER} = 1\text{nF}$  unless otherwise specified)

| Symbol                                      | Pin | Parameter                                  | Test condition                                                                 | Min   | Typ   | Max   | Unit          |

|---------------------------------------------|-----|--------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|---------------|

| <b>Supply voltage</b>                       |     |                                            |                                                                                |       |       |       |               |

| $V_{ccON}$                                  | 10  | Turn-on voltage                            |                                                                                | 13    | 14    | 15    | V             |

| $V_{ccOFF}$                                 | 10  | Turn-off voltage                           |                                                                                | 8.5   | 9     | 9.5   | V             |

| $V_{ccSM}$                                  | 10  | Save mode voltage                          |                                                                                | 12.75 | 13.8  | 14.85 | V             |

| $V_{SMhys}$                                 | 10  | Save mode hysteresys                       |                                                                                | 0.12  | 0.16  | 0.2   | V             |

| $V_{REF(OFF)}$                              | 10  | Reference turn-off                         |                                                                                | 6     | 6.4   | 6.8   | V             |

| $I_{vccON}$                                 | 10  | Start-up current                           |                                                                                |       |       | 160   | $\mu\text{A}$ |

| $I_{vccSM}$                                 | 10  | Save Mode current consumption              |                                                                                |       |       | 220   | $\mu\text{A}$ |

|                                             |     |                                            | (1)                                                                            |       | 190   | 250   | $\mu\text{A}$ |

| $I_{vcc}$                                   | 10  | Quiescent current in <i>operating mode</i> | $V_{CC}=13\text{V}$ ;<br>$LGI = HGI = \text{high}$ ;<br>no load on $V_{REF}$ . |       |       | 2.1   | mA            |

| $V_z$                                       | 10  | Internal Zener                             |                                                                                | 16.5  | 17    | 18    | V             |

| <b>High voltage start-up</b>                |     |                                            |                                                                                |       |       |       |               |

| IMSS                                        | 15  | Maximum current                            | $V_{HVSU} > 50\text{V}$                                                        | 20    |       |       | mA            |

| ILSS                                        | 15  | Leakage current off state                  | $V_{HVSU} = 600\text{V}$                                                       |       |       | 40    | $\mu\text{A}$ |

| <b>Two point regulator (TPR) protection</b> |     |                                            |                                                                                |       |       |       |               |

| $TPR_{st}$                                  | 10  | Vcc Protection level                       | <i>Operating mode</i>                                                          | 14.0  | 14.5  | 15.0  | V             |

| $TPR_{(ON)}$                                | 10  | Vcc Turn-on level                          | <i>Operating mode; after the first falling edge on LSG</i>                     | 12.5  | 13    | 13.5  | V             |

| $TPR_{(OFF)}$                               | 10  | Vcc Turn-off level                         | <i>Operating mode; after the first falling edge on LSG</i>                     | 12.45 | 12.95 | 13.48 | V             |

|                                             | 7   | Output voltage on state                    | $I_{TPR} = 200\text{mA}$                                                       |       |       | 2     | V             |

|                                             | 7   | Forward voltage drop Diode                 | @ 600mA forward current.                                                       |       |       | 2.3   | V             |

|                                             | 7   | Leakage current off state                  | $V_{TPR} = 13\text{V}$                                                         |       |       | 5     | $\mu\text{A}$ |

**Table 4. Electrical characteristics** ( $T_J = 25^\circ\text{C}$ ,  $V_{CC} = 13\text{V}$ ,  $C_{DRIVER} = 1\text{nF}$  unless otherwise specified) (continued)

| Symbol                                       | Pin  | Parameter                           | Test condition                   | Min  | Typ  | Max | Unit             |

|----------------------------------------------|------|-------------------------------------|----------------------------------|------|------|-----|------------------|

| <b>LSG, HEG &amp; PFG drivers</b>            |      |                                     |                                  |      |      |     |                  |

| $V_{OH(LS)}$                                 | 5, 9 | HIGH Output Voltage                 | ILSG = IPFG = 10mA               | 12.5 | 12.5 |     | V                |

|                                              | 17   |                                     | IHEG = 2.5mA                     |      |      |     |                  |

| $V_{OL(LS)}$                                 | 5, 9 | LOW Output Voltage                  | ILSG = IPFG = 10mA               | 0.5  | 0.5  |     | V                |

|                                              | 17   |                                     | IHEG = 2.5mA                     |      |      |     |                  |

|                                              |      | Source Current Capability           | LSG and PFG                      | 120  |      |     | mA               |

|                                              |      |                                     | HEG                              | 50   |      |     | mA               |

|                                              |      | Sink Current Capability             | LSG                              | 120  |      |     | mA               |

|                                              |      |                                     | HEG                              | 70   |      |     |                  |

|                                              |      |                                     | PFG                              | 250  |      |     |                  |

| $T_{RISE}$                                   | 5    | Rise time                           | Cload = 1nF                      | 80   | 300  | 60  | ns               |

|                                              | 9    |                                     |                                  |      |      |     |                  |

|                                              | 17   |                                     |                                  |      |      |     |                  |

| $T_{FALL}$                                   | 5,   | Fall time                           | Cload = 1nF                      | 60   | 110  | 40  | ns               |

|                                              | 9    |                                     |                                  |      |      |     |                  |

|                                              | 17   |                                     |                                  |      |      |     |                  |

| $T_{DELAY}$                                  |      | Propagation delay (input to output) | LSG; high to low and low to high |      |      | 300 | ns               |

|                                              |      |                                     | HEG; high to low and low to high |      |      | 200 | ns               |

|                                              |      |                                     | PFG; high to low                 |      |      | 250 | ns               |

|                                              |      |                                     | PFG; low to high                 |      |      | 200 | ns               |

| $R_B$                                        |      | Pull down Resistor                  | LSG                              |      | 20   |     | $\text{K}\Omega$ |

|                                              |      |                                     | HEG                              |      | 50   |     | $\text{K}\Omega$ |

|                                              |      |                                     | PFG                              |      | 10   |     | $\text{K}\Omega$ |

| <b>HSG driver (voltages referred to OUT)</b> |      |                                     |                                  |      |      |     |                  |

| $V_{OH(HS)}$                                 | 12   | HIGH Output Voltage                 | IHSG = 10 mA                     |      | 12.5 |     | V                |

| $V_{OL(HS)}$                                 | 12   | LOW Output Voltage                  | IHSG = 10 mA                     |      | 0.5  |     | V                |

|                                              | 12   | Sink Current Capability             |                                  | 120  |      |     | mA               |

|                                              | 12   | Source Current Capability           |                                  | 120  |      |     | mA               |

| $T_{RISE}$                                   | 12   | Rise time                           | Cload = 1nF                      |      | 115  |     | ns               |

**Table 4. Electrical characteristics** ( $T_J = 25^\circ\text{C}$ ,  $V_{CC} = 13\text{V}$ ,  $C_{DRIVER} = 1\text{nF}$  unless otherwise specified) (continued)

| Symbol                                       | Pin | Parameter                                 | Test condition                                                                                                           | Min  | Typ  | Max  | Unit             |

|----------------------------------------------|-----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------------------|

| $T_{FALL}$                                   | 12  | Fall time                                 | $C_{load} = 1\text{nF}$                                                                                                  |      | 75   |      | ns               |

| $T_{DELAY}$                                  | 12  | Propagation delay (LGI to LSG)            | high to low and low to high                                                                                              |      |      | 300  | ns               |

| $R_B$                                        | 12  | Pull down Resistor                        | to OUT                                                                                                                   |      | 20   |      | $\text{k}\Omega$ |

| <b>High-side floating gate-driver supply</b> |     |                                           |                                                                                                                          |      |      |      |                  |

| $I_{LKBOOT}$                                 | 11  | $V_{BOOT}$ pin leakage current            | $V_{BOOT} = 580\text{V}$                                                                                                 |      |      | 5    | $\mu\text{A}$    |

| $I_{LKOUT}$                                  | 13  | OUT pin leakage current                   | $V_{OUT} = 562\text{V}$                                                                                                  |      |      | 5    | $\mu\text{A}$    |

| $R_{DS(on)}$                                 |     | Synchronous bootstrap diode on-resistance | $V_{LVG} = \text{HIGH}$                                                                                                  |      | 150  |      | $\Omega$         |

|                                              |     | Forward Voltage Drop                      | at 10 mA forward current                                                                                                 |      | 2.4  |      | V                |

|                                              |     | Forward Current                           | at 5V forward voltage drop                                                                                               | 20   |      |      | mA               |

| <b><math>V_{REF}</math></b>                  |     |                                           |                                                                                                                          |      |      |      |                  |

| $V_{REF}$                                    | 20  | Reference voltage                         | 15mA load.                                                                                                               | 4.9  | 5    | 5.1  | V                |

|                                              | 20  | Load regulation                           | $ I_{Ref}  = -3 \text{ to } +30 \text{ mA}$                                                                              | -20  |      | 2    | mV               |

|                                              | 20  | Voltage change                            | 15mA load; $V_{CC} = 9\text{V}$ to 15V                                                                                   |      |      | 15   | mV               |

|                                              | 20  | $V_{REF}$ latched protection              |                                                                                                                          |      |      | 3.2  | V                |

|                                              | 20  | $V_{REF}$ Clamp @3mA                      | $V_{CC}$ from 0 to $V_{CCON}$ during start-up; $V_{CC}$ from $V_{REF(OFF)}$ to 0 during shut-down; $V_{REF} < 2\text{V}$ |      | 1.2  | 1.8  | V                |

| $I_{REF}$                                    | 20  | Current Drive Capability                  |                                                                                                                          | -3   |      | +30  | mA               |

|                                              |     |                                           | Save mode                                                                                                                | -3   |      | +10  | mA               |

| <b>Overcurrent buffer stage</b>              |     |                                           |                                                                                                                          |      |      |      |                  |

| $V_{CSI}$                                    | 19  | Comparator Level                          |                                                                                                                          | 0.52 | 0.54 | 0.56 | V                |

| $I_{CSI}$                                    | 19  | Input Bias Current                        |                                                                                                                          |      |      | 500  | nA               |

|                                              |     | Propagation delay                         | CSO turn off to LSG low                                                                                                  |      |      | 200  | ns               |

**Table 4. Electrical characteristics** ( $T_J = 25^\circ\text{C}$ ,  $V_{CC} = 13\text{V}$ ,  $C_{DRIVER} = 1\text{nF}$  unless otherwise specified) (continued)

| Symbol             | Pin    | Parameter                      | Test condition              | Min                     | Typ | Max | Unit             |

|--------------------|--------|--------------------------------|-----------------------------|-------------------------|-----|-----|------------------|

|                    | 18     | High output voltage            | $I_{CSO} = 200\mu\text{A}$  | $V_{REF} = 0.5\text{V}$ |     |     |                  |

|                    | 18     | Low output voltage             | $I_{CSO} = -150\mu\text{A}$ |                         |     | 0.5 | V                |

| <b>DIM</b>         |        |                                |                             |                         |     |     |                  |

|                    |        | Normal Mode Time Out           |                             | 65                      | 100 | 135 | $\mu\text{s}$    |

|                    |        | Vref enabling drivers          |                             |                         | 4.6 |     | V                |

| $T_{ED}$           |        | Time enabling drivers          |                             |                         | 10  |     | $\mu\text{s}$    |

| <b>Logic input</b> |        |                                |                             |                         |     |     |                  |

|                    | 1 to 4 | Low Level Logic Input Voltage  |                             |                         |     | 1.3 | V                |

|                    | 1 to 4 | High Level Logic Input Voltage |                             | 3.7                     |     |     | V                |

|                    | LGI    | Pull down resistor             |                             |                         | 100 |     | $\text{K}\Omega$ |

1. Specification over the  $-40^\circ\text{C}$  to  $+125^\circ\text{C}$  junction temperature range are ensured by design, characterization and statistical correlation.

## 5 Application information

### 5.1 Power management

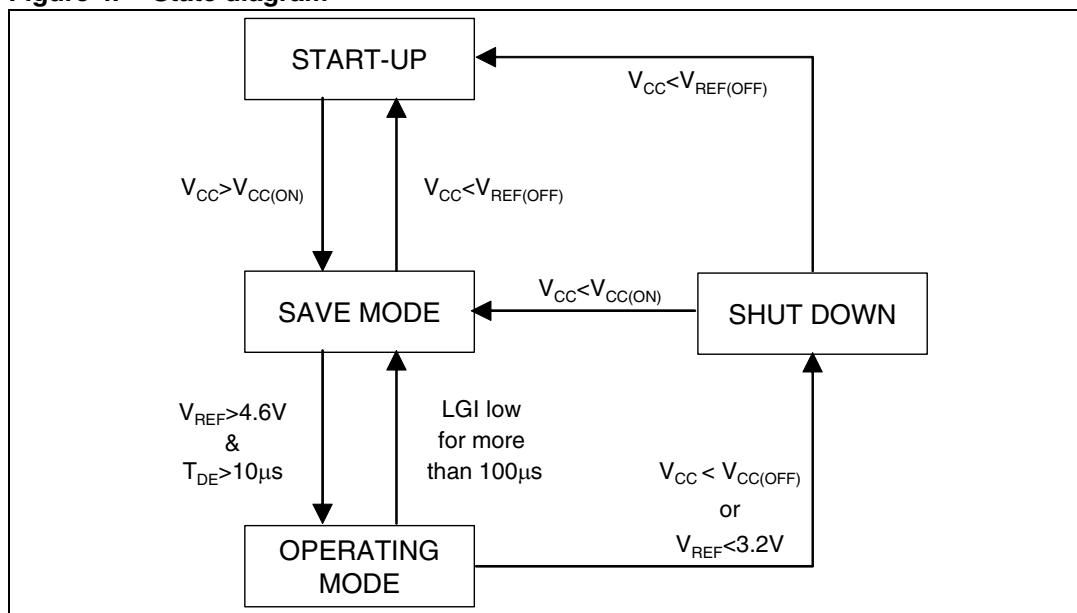

The L6382D5 has two stable states (*save mode* and *operating mode*) and two additional states that manage the Start-up and fault conditions: the Over Current Protection is a parallel asynchronous process enabled when in *operating mode* [Figure 4](#).

Following paragraphs will describe each mode and the condition necessary to shift between them.

**Figure 4. State diagram**

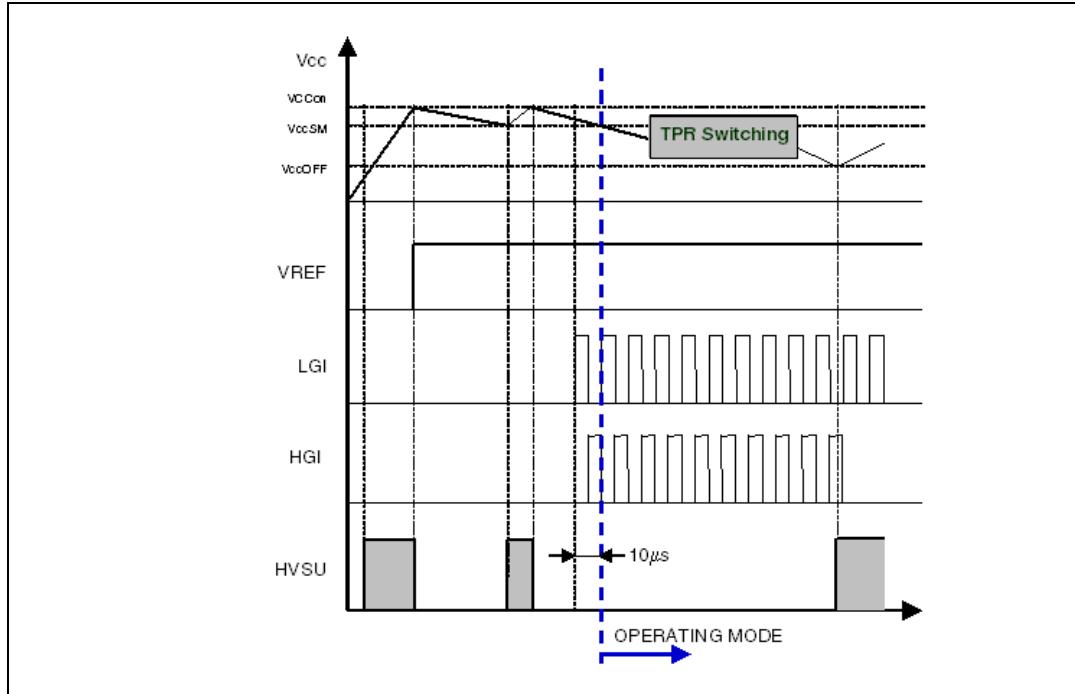

### 5.2 START-UP mode

With reference to the timing diagram of figure 6, when power is first applied to the converter, the voltage on the bulk capacitor ( $V_{in}$ ) builds up and the HV generator is enabled to operate drawing about 10mA. This current, diminished by the IC consumption (less than 150 $\mu$ A), charges the bypass capacitor connected between pin  $V_{cc}$  and ground and makes its voltage rise almost linear.

During this phase, all IC's functions are disabled except for:

- the current sinking circuit on  $V_{REF}$  pin that maintains low the voltage by keeping disabled the microcontroller connected to this pin;

- the High-Voltage Start-Up (HVSU) that is ON (conductive) to charge the external capacitor on pin  $V_{cc}$ .

As the  $V_{cc}$  voltage reaches the start-up threshold (14V typ.) the chip starts operating and the HV generator is switched off.

Summarizing:

- The high-voltage start-up generator is active;

- $V_{REF}$  is disabled with additional sinking circuit on pin  $V_{REF}$  enabled;

- TPR is disabled;

- OCP is disabled;

- The drivers are disabled.

### 5.2.1 SAVE Mode

This mode is entered after the  $V_{CC}$  voltage reaches the turn-on threshold; the  $V_{REF}$  is enabled in low current source mode to supply the  $\mu$ C connected to it, whose wake-up required current must be less than 10mA: if no switching activity is detected at LGI input, the high voltage start-up generator cycles ON-OFF keeping the  $V_{cc}$  voltage between  $V_{ccON}$  and  $V_{ccSM}$ .

Summarizing:

- The high-voltage start-up generator is cycling;

- $V_{REF}$  is enabled in low source current capability ( $I_{REF} \leq 10\text{mA}$ );

- TPR circuit is disabled;

- OCP is disabled;

- The drivers are disabled.

If the  $V_{CC}$  voltage falls below the  $V_{REF(OFF)}$  threshold, the device enters the *start-up* mode.

### 5.2.2 OPERATING Mode

After 10 $\mu$ s in *save* mode and only if the voltage at  $V_{REF}$  is higher than 4.6V, on the falling edge on the HGI input, the driver are enabled as well as all the IC's functions; this is the mode correspondent to the proper lamp behaviour.

Summarizing:

- HVSU is OFF

- $V_{REF}$  is enabled in high source current mode ( $I_{REF} < 30\text{mA}$ )

- TPR circuit is enabled

- OCP is enabled

- The drivers are enabled

If there is no switching activity on LGI for more than 100 $\mu$ s, the IC returns in *save* mode.

### 5.2.3 Shut Down

This state permits to manage the fault conditions in *operating* mode and it is entered by the occurrence on one of the following conditions:

1.  $V_{CC} < V_{ccOff}$  (Under Voltage fault on Supply),

2.  $V_{REF} < 3.2\text{V}$  (Under Voltage fault on  $V_{REF}$ )

In this state the functions are:

- The HVSU generator is ON

- $V_{REF}$  is enabled in low source current mode ( $I_{REF} < 10mA$ )

- TPR is disabled

- OCP is disabled

- The drivers are disabled

In this state if  $V_{CC}$  reaches  $V_{CCOn}$ , the device enters the save mode otherwise, if  $V_{CC} < V_{REF(OFF)}$ , also the  $\mu$ C is turned off and the device will be ready to execute the Start-up sequence.

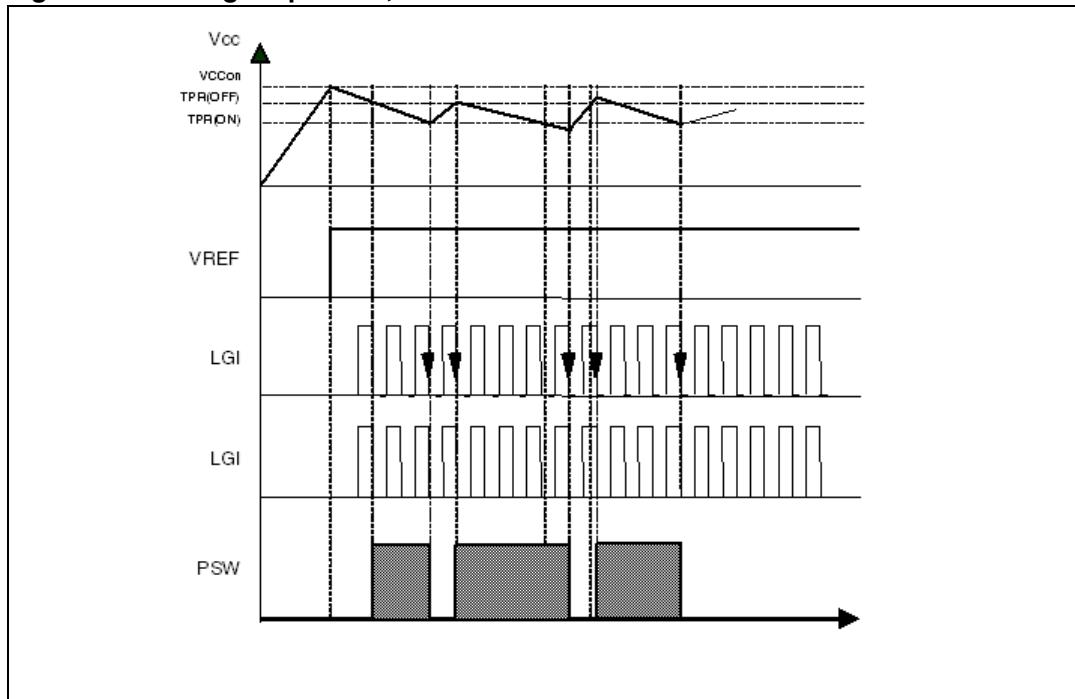

**Figure 5. Timing Sequences, TPR behavior**

Figure 6. Timing Sequences, save mode and operating mode

## 6 Block description

### 6.1 Supply section

- **μPUVLO ( Power Under Voltage Lock Out):** This block controls the power management of the L6382D5 ensuring the right current consumption in each operating state, the correct  $V_{REF}$  current capability, the driver enabling and the high-voltage start-up generator switching.

During Start-up the device sinks the current necessary to charge the external capacitor on pin  $V_{CC}$  from the high voltage bus; in this state the other IC's functions are disabled and the current consumption of the whole IC is less than  $150\mu A$ .

When the voltage on  $V_{CC}$  pin reaches  $V_{CCON}$ , the IC enters the *save* mode where the μPUVLO block controls  $V_{CC}$  between  $V_{CCON}$  and  $V_{CCSM}$  by switching ON/OFF the high voltage start-up generator.

- **HVSU (High-Voltage Start-Up generator):** a 600V internal MOS transistor structure controls the  $V_{CC}$  supply voltage during START UP and SAVE MODE conditions and it reduces the power losses during operating MODE by switching off the MOS transistor. The transistor has a source current capability of up to 30mA.

- **TPR (Two Point Regulator) & PWS:** during *operating* mode, the TPR block controls the PSW switch in order to regulate the IC supply voltage ( $V_{CC}$ ) to a value in the range between TPR(ON) and TPR(OFF) by switching ON and OFF the PSW transistor.

- $V_{CC} > TPR_{st}$ : the PSW is switched ON immediately;

- $TPR(ON) < V_{CC} < TPR_{st}$ : the PSW is switched ON at the following falling edge of LGI;

- $V_{CC} < TPR(OFF)$ : the PSW is switched OFF at the following falling edge on LGI.

When the PSW switch is OFF, the diodes build a charge pump structure so that, connecting the TPR pin to a switching voltage (through a capacitor) it is possible to supply the low voltage section of the chip without adding any further external component. The diodes and the switch are designed to withstand a peak current of at least  $200mA_{RMS}$ .

### 6.2 5V reference voltage

This block is used to supply the microcontroller; this source is able to supply 10mA in *save* mode and 30mA in normal mode; moreover, during *start-up* when  $V_{REF}$  is not yet available, an additional circuit ensures that, even sinking 3mA, the pin voltage doesn't exceed 1.2V.

The reference is available until  $V_{CC}$  is above  $V_{REF(OFF)}$ ; below that it turns off and the additional sinking circuit is enabled again.

## 6.3 Drivers

- **LSD (Low Side Driver)**: it consists of a level shifter from 5V logic signal (LSI) to Vcc MOS driving level; conceived for the half-bridge low-side power MOS, it is able to source and sink 120mA (min).

- **HSD (Level Shifter and High Side Driver)**: it consists of a level shifter from 5V logic signal (HSI) to the high side gate driver input up to 600V. Conceived for the half-bridge high-side power MOS, the HSD is able to source and sink 120mA.

- **PFD (Power Factor Driver)**: it consists of a level shifter from 5V logic signal (PFI) to Vcc MOS driving level: the driver is able to source 120mA from  $V_{CC}$  to PFG (turn-on) and to sink 250mA to GND (turn-off); it is suitable to drive the MOS of the PFC pre-regulator stage.

- **HED (Heat Driver)**: it consists of a level shifter from 5V logic signal (HEI) to Vcc MOS driving level; the driver is able to source 30mA from Vcc to HEG and to sink 75mA to GND and it is suitable for the filament heating when they are supplied by independent winding.

- **Bootstrap Circuit**: it generates the supply voltage for the high side Driver (HSD). This circuit sources current from  $V_{CC}$  to PIN HSB when LSG is ON. A patented integrated bootstrap section replaces an external bootstrap diode. This section together with a bootstrap capacitor provides the bootstrap voltage to drive the high side power MOSFET. This function is achieved using a high voltage DMOS driver which is driven synchronously with the low side external power MOSFET. For a safe operation, current flow between BOOT pin and Vcc is always inhibited, even though ZVS operation may not be ensured.

## 6.4 Internal logic, over current protection (OCP) and interlocking function

The DIM (*Digital Input Monitor*) block manages the input signals delivered to the drivers ensuring that they are low during the described start-up procedure; the DIM block controls the L6382D5 behaviour during both save and operating modes.

When the voltage on pin CSI overcomes the internal reference of 0.54V (typ.) the block latches the fault condition: in this state the OCP block forces low both HSG and LSG signals while CSO will be forced high. This condition remains latched until LSI and HSI are simultaneously low and CSI is below 0.54V.

This function is suitable to implement an over current protection or hard-switching detection by using an external sense resistor.

As the voltage on pin CSI can go negative, the current must be limited below 2mA by external components.

Another feature of the DIM block is the **internal interlocking** that avoids cross-conduction in the half-bridge FET's: if by chance both HSI and LSI input's are brought high at the same time, then LSG and HSG are forced low as long as this critical condition persists.

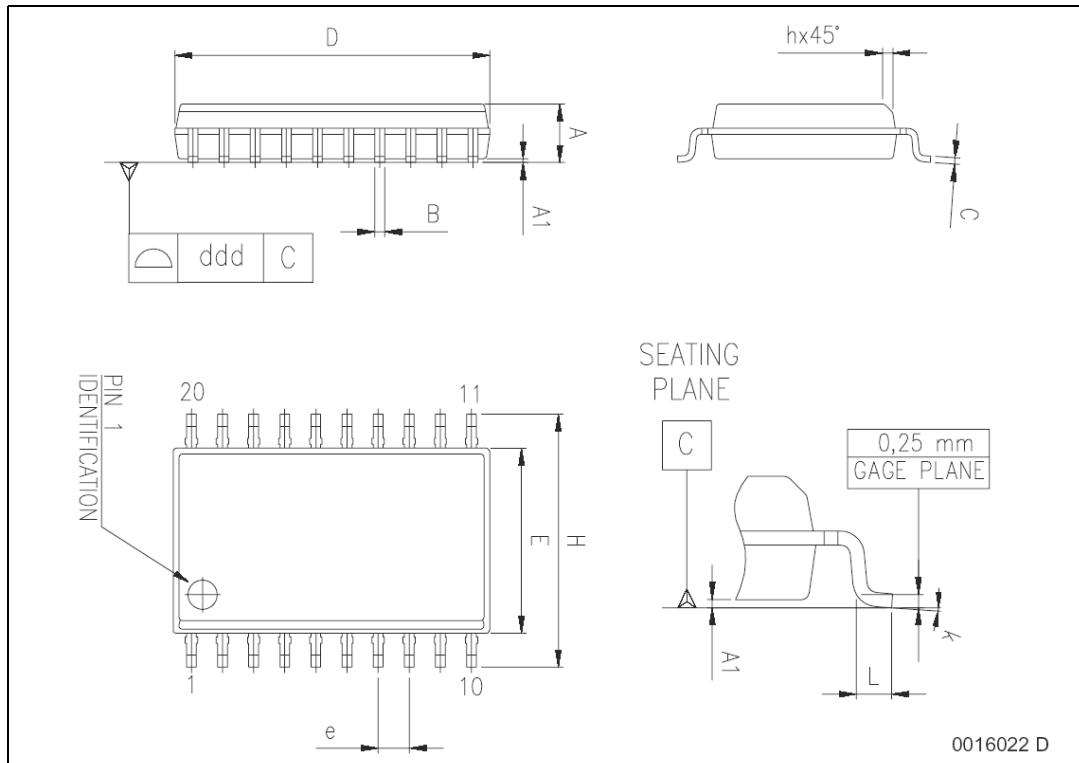

## 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: [www.st.com](http://www.st.com)

Table 5. SO-20 Mechanical data

| Dim.  | mm.                  |      |       | inch  |       |       |

|-------|----------------------|------|-------|-------|-------|-------|

|       | Min                  | Typ  | Max   | Min   | Typ   | Max   |

| A     | 2.35                 |      | 2.65  | 0.093 |       | 0.104 |

| A1    | 0.10                 |      | 0.30  | 0.004 |       | 0.012 |

| B     | 0.33                 |      | 0.51  | 0.013 |       | 0.200 |

| C     | 0.23                 |      | 0.32  | 0.009 |       | 0.013 |

| D (1) | 12.60                |      | 13.00 | 0.496 |       | 0.512 |

| E     | 7.40                 |      | 7.60  | 0.291 |       | 0.299 |

| e     |                      | 1.27 |       |       | 0.050 |       |

| H     | 10.0                 |      | 10.65 | 0.394 |       | 0.419 |

| h     | 0.25                 |      | 0.75  | 0.010 |       | 0.030 |

| L     | 0.40                 |      | 1.27  | 0.016 |       | 0.050 |

| k     | 0° (min.), 8° (max.) |      |       |       |       |       |

| ddd   |                      |      | 0.10  |       |       | 0.004 |

Figure 7. Package dimensions

## 8 Order codes

**Table 6. Order codes**

| Part number | Package | Packaging   |

|-------------|---------|-------------|

| L6382D5     | SO-20   | Tube        |

| L6382D5TR   | SO-20   | Tape & Reel |

## 9 Revision history

**Table 7. Revision history**

| Date        | Revision | Changes                |

|-------------|----------|------------------------|

| 15-Jan-2004 | 1        | First Issue            |

| 17-May-2006 | 2        | Document reformatted   |

| 22-Mar-2007 | 3        | Typo on <i>Table 2</i> |

**Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

**UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.**

**UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.**

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

[www.st.com](http://www.st.com)

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[STMicroelectronics](#):

[L6382D5](#) [L6382D5TR](#)