## Multi-Channel High Definition Audio Codec

## **DESCRIPTION**

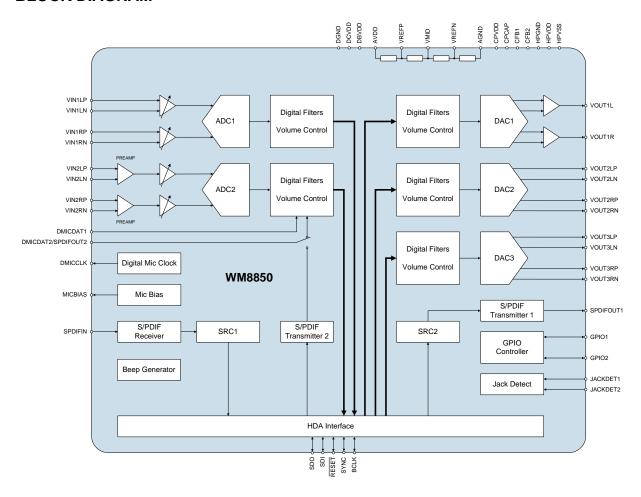

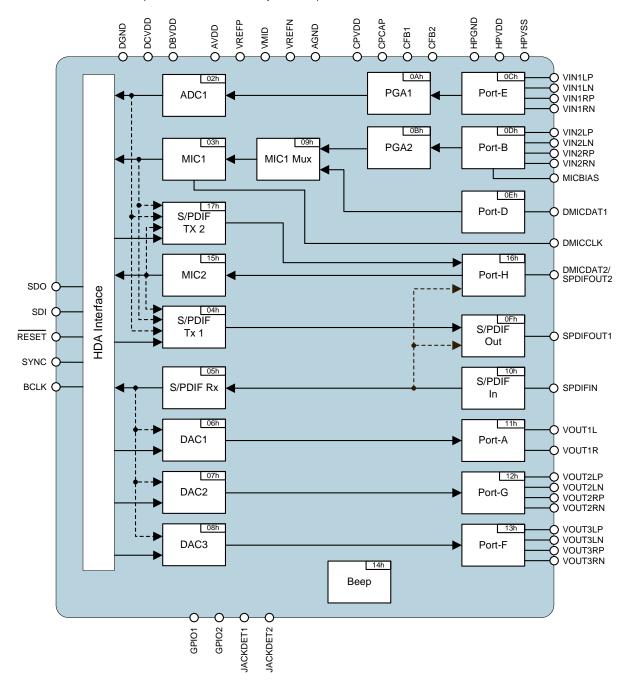

The WM8850 is a high performance multi-channel audio CODEC designed for high performance PC audio systems. The device offers full compatibility with the Intel High Definition Audio (HDA) specification revision 1.0, allowing seamless integration with industry-standard HDA controllers.

The WM8850 has three high performance stereo DACs to enable six channels of high definition audio, ideal for 5.1 channel applications. A high-performance ground-referenced stereo headphone amplifier utilises advanced charge pump and DC servo technology to minimise system cost and space without compromise on audio quality. Line outputs provide a high-quality differential connection to speaker amplifiers, enabling common mode noise rejection when these traces are routed across a PCB.

The WM8850 also has two high performance stereo ADCs to provide Hi-Fi quality analogue line-in and microphone input digitisation. A low noise microphone bias with programmable output voltage is provided. Additionally, the CODEC contains a digital microphone interface capable of supporting up to four independent digital microphones. One differential stereo input is provided for line level signals, while one pseudo-differential stereo input with integrated microphone preamplifier is provided.

The WM8850 also contains a S/PDIF transceiver which is fully compatible with IEC-60958-3. The S/PDIF receive and transmit paths each contain a sample rate converter (SRC) to enable asynchronous sample rate conversion between the S/PDIF receive/transmit and HDA interface clock domains. An additional S/PDIF transmitter is provided to allow direct output of a stereo stream from the HDA interface.

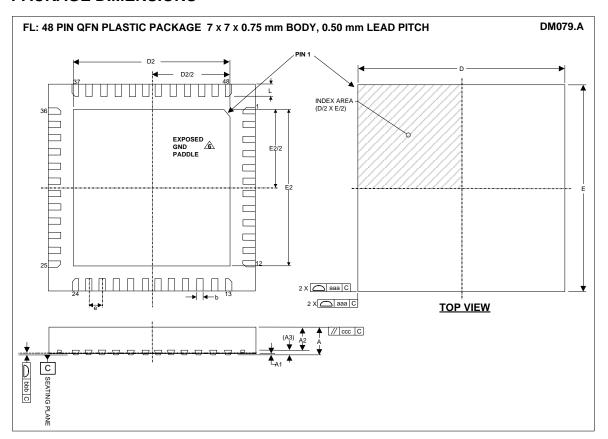

The WM8850 is supplied in a small 48-pin QFN package.

## **FEATURES**

- Multi-channel High Definition Audio CODEC

- Fully compatible with Intel High Definition Audio Revision 1.0

- 6-Channel DAC, 4-channel ADC

- DAC sampling frequency 8kHz 192kHz

- ADC sampling frequency 8kHz 96kHz

- DAC Performance:

- SNR 108 dB ('A' weighted)

- SNR 105dB (non weighted)

- THD -96dB (at 0dBFS)

- ADC Performance:

- SNR 105 dB ('A' weighted)

- SNR 102dB (non weighted)

- THD -95dB (at -1dBFS)

- · Ground-referenced stereo headphone driver

- Differential line inputs/outputs

- Stereo microphone interface with integrated pre-amp

- Multi-channel digital microphone interface

- IEC-60958-3 compatible S/PDIF transceiver

- Additional IEC-60958-3 compatible S/PDIF transmitter

- Jack detect and load impedance sensing

- Beep generator

- GPIO functionality

- IEEE-754 Single precision 32-bit floating point support

- Power supplies

Digital core: 1.62V - 1.98V

Digital buffer: 2.97V - 3.63V

Analogue: 4.5V - 5.25V

Charge pump: 4.5V - 5.25V

48-pin 7mm x 7mm QFN package

## **APPLICATIONS**

- High performance PC audio

- All-in-one desktop PC

- Notebook PC

## **BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| DESCRIPTION                                       |    |

|---------------------------------------------------|----|

| FEATURES                                          |    |

| APPLICATIONS                                      | 1  |

| BLOCK DIAGRAM                                     |    |

| TABLE OF CONTENTS                                 |    |

| PIN CONFIGURATION                                 |    |

|                                                   |    |

| ORDERING INFORMATION                              | _  |

| PIN DESCRIPTION                                   |    |

| ABSOLUTE MAXIMUM RATINGS                          |    |

| RECOMMENDED OPERATING CONDITIONS                  |    |

| THERMAL PERFORMANCE                               |    |

| ELECTRICAL CHARACTERISTICS                        | 13 |

| TERMINOLOGY                                       | 25 |

| POWER CONSUMPTION                                 | 26 |

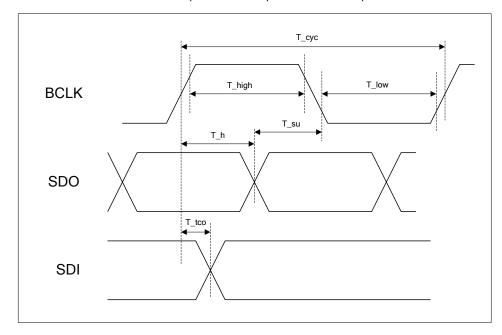

| SIGNAL TIMING REQUIREMENTS                        | _  |

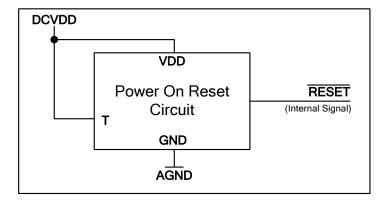

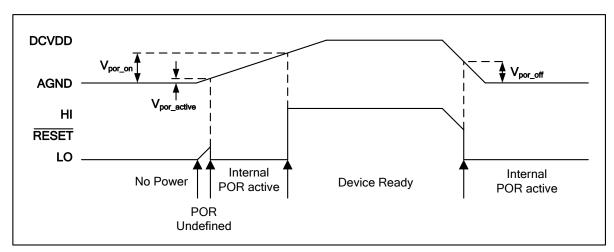

| INTERNAL POWER ON RESET CIRCUIT                   |    |

| INTRODUCTION                                      |    |

| CIRRUS LOGIC INTERPRETATION OF HDA SPECIFICATION  |    |

| DOLBY AC3 (IEC-61937)                             |    |

| FLOAT32                                           |    |

| AUDIO WIDGETS CAPABILITIES PARAMETER: DIGITAL     |    |

| LATENCY                                           |    |

| POWER STATES                                      |    |

| STREAM START/STOP                                 |    |

| SDI STREAM ORDER                                  |    |

| BANDWIDTH CONFLICTS                               |    |

| SOFTWARE FORMATTED (RAW) S/PDIF                   | 32 |

| SOURCE SYNCHRONOUS INPUT - S/PDIF RX              | 32 |

| S/PDIF TX VALIDITY FLAG                           |    |

| CHANNEL NUMBERING                                 |    |

| ILLEGAL REGISTER VALUES                           |    |

| RESPONSE FIELD                                    |    |

| CHIP HIERARCHY                                    |    |

| WIDGET DIAGRAM                                    |    |

| NODE LIST                                         |    |

| NODE/VERB SUMMARY                                 |    |

| DEVICE DESCRIPTION                                |    |

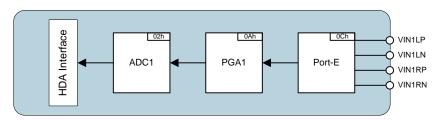

| STEREO ANALOGUE LINE RECORD                       |    |

| PORT-E (NID = 0CH)                                |    |

| PGA1 (NID = 0AH)                                  |    |

| ADC1 (NID = 02H)STEREO ANALOGUE MICROPHONE RECORD |    |

|                                                   |    |

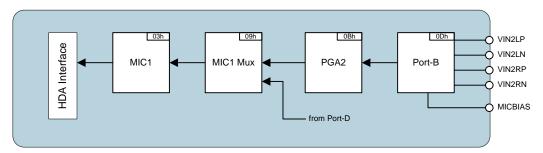

| PORT-B (NID = 0DH)<br>PGA2 (NID = 0BH)            |    |

| MIC1 MUX (NID = 09H)                              |    |

| MIC1 (NID = 09H)                                  |    |

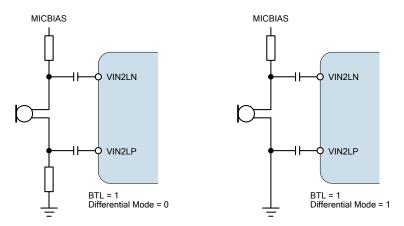

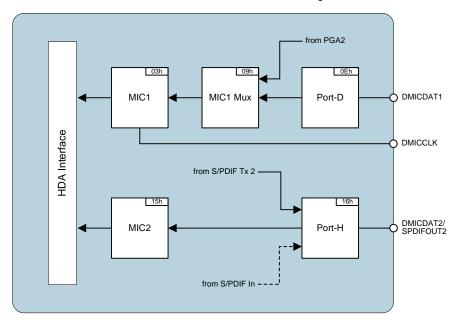

| DIGITAL MICROPHONE RECORD                         |    |

| PORT-D (NID = 0EH)                                |    |

| PORT-H (NID = 16H)                                |    |

| ` - /                                             |    |

| MIC2 (NID = 15H)                                             |     |

|--------------------------------------------------------------|-----|

| DIGITAL MICROPHONE INTERFACE CLOCK RATES                     |     |

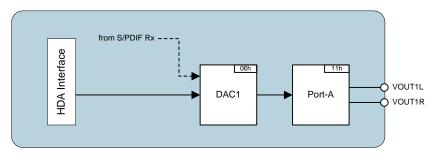

| STEREO HEADPHONE PLAYBACK                                    | 52  |

| DAC1 (NID = 06H)                                             | 52  |

| PORT-A (NID = 11H)                                           |     |

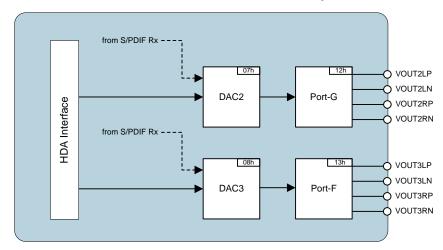

| STEREO LINE PLAYBACK                                         | 55  |

| DAC2 (NID = 07H) AND DAC3 (NID = 08H)                        | 55  |

| PORT-G (NID = 12H) AND PORT-F (NID = 13H)                    | 57  |

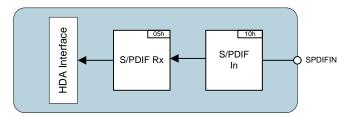

| S/PDIF RECEIVE                                               | 58  |

| S/PDIF IN (NID = 10H)                                        | 58  |

| S/PDIF RX (NID = 05H)                                        | 61  |

| S/PDIF RECEIVE USING SRC1                                    | 64  |

| S/PDIF RECEIVE WITHOUT USING SRC1                            | 64  |

| S/PDIF RECEIVE TO DACS                                       |     |

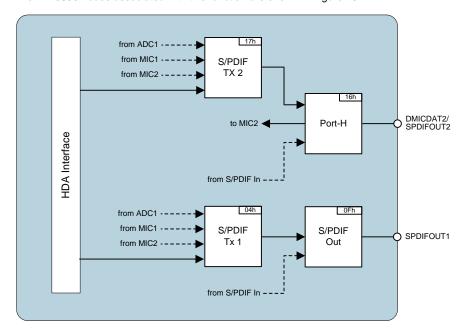

| S/PDIF TRANSMIT                                              | 66  |

| S/PDIF TX 1 (NID = 04H)                                      | 67  |

| S/PDIF OUT (NID = 0FH)                                       | 69  |

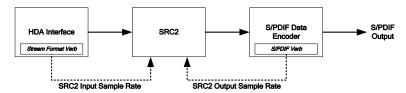

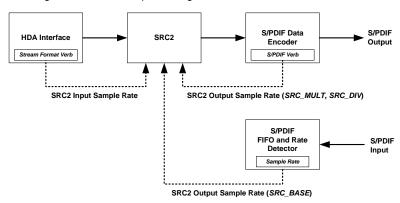

| S/PDIF TRANSMIT USING SRC2                                   | 70  |

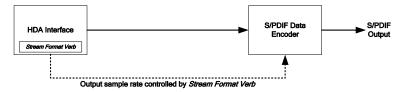

| S/PDIF TRANSMIT WITHOUT USING SRC2                           | 71  |

| S/PDIF TX 2 (NID = 17H)                                      | 72  |

| ANCILLARY FUNCTIONS                                          |     |

| BEEP (NID = 14H)                                             | 74  |

| AUDIO FUNCTION GROUP (NID = 01H)                             |     |

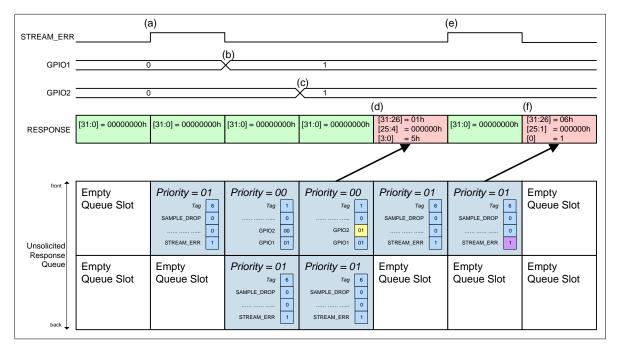

| UNSOLICITED RESPONSES                                        | 77  |

| GENERATING UNSOLICITED RESPONSES                             | 77  |

| PRIORITY QUEUING                                             | 77  |

| IN-QUEUE-UPDATE                                              | 77  |

| UNSOLICITED RESPONSE TYPES                                   | 79  |

| SF = UNSOLICITED RESPONSE STATUS FLAG                        | 79  |

| UF = UNSOLICITED RESPONSE UPDATE FLAG                        | 79  |

| EF = UNSOLICITED RESPONSE EVENT FLAG                         |     |

| UNSOLICITED RESPONSE DEFINITIONS                             |     |

| DETAILED VERB DESCRIPTIONS                                   | 87  |

| ROOT NODE (NID = 00H)                                        | 87  |

| AUDIO FUNCTION GROUP (NID = 01H)                             | 89  |

| FUNCTION RESET VERB                                          | 89  |

| GET PARAMETER VERB                                           | 89  |

| POWER STATE VERB                                             | 91  |

| UNSOLICITED RESPONSE VERB                                    | 91  |

| GPIO DATA VERB                                               | 92  |

| GPIO ENABLE MASK VERB                                        | 92  |

| GPIO DIRECTION VERB                                          | 92  |

| GPIO WAKE ENABLE MASK VERB                                   | 92  |

| GPIO UNSOLICITED ENABLE MASK VERB                            | 93  |

| GPIO STICKY MASK VERB                                        | 93  |

| IMPLEMENTATION ID / SUBSYSTEM ID VERB                        | 93  |

| VMID CONTROL VERB (VENDOR SPECIFIC)                          |     |

| GPIO AUTOMATIC CONTROL VERB (VENDOR-SPECIFIC)                |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC) |     |

| ADC1 AUDIO INPUT CONVERTER WIDGET (NID = 02H)                | 97  |

| STREAM FORMAT VERB                                           | 97  |

| GET PARAMETER VERB                                           |     |

| GET CONNECTION LIST ENTRY VERB                               |     |

| PROCESSING STATE VERB                                        | 100 |

| POWER STATE VERB                                                                |     |

|---------------------------------------------------------------------------------|-----|

| CONVERTER STREAM, CHANNEL VERB                                                  | 100 |

| UNSOLICITED RESPONSE VERB                                                       |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                    |     |

| CHANNEL COPY VERB (VENDOR-SPECIFIC)                                             |     |

| MIC1 AUDIO INPUT CONVERTER WIDGET (NID = 03H)                                   |     |

| STREAM FORMAT VERB                                                              |     |

| GET PARAMETER VERB                                                              |     |

| GET CONNECTION LIST ENTRY VERB                                                  |     |

| PROCESSING STATE VERB                                                           |     |

| POWER STATE VERB                                                                |     |

| CONVERTER STREAM, CHANNEL VERB                                                  |     |

| UNSOLICITED RESPONSE VERB                                                       |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                    |     |

| CHANNEL COPY VERB (VENDOR-SPECIFIC)                                             |     |

| S/PDIF TX 1 AUDIO OUTPUT CONVERTER WIDGET (NID = 04H)                           |     |

| STREAM FORMAT VERB                                                              |     |

| GET PARAMETER VERB                                                              |     |

| PROCESSING STATE VERB                                                           |     |

| CONVERTER STREAM, CHANNEL VERB                                                  |     |

| UNSOLICITED RESPONSE VERB                                                       |     |

| S/PDIF CONVERTER CONTROL VERB                                                   |     |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                                            |     |

| S/PDIF VERB (VENDOR-SPECIFIC)  TX CHANNEL STATUS CONTROL VERB (VENDOR-SPECIFIC) |     |

| CHANNEL STATUS CONTROL VERB (VENDOR-SPECIFIC)                                   |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                    |     |

| S/PDIF RX AUDIO INPUT CONVERTER WIDGET (NID = 05H)                              |     |

| STREAM FORMAT VERB                                                              |     |

| GET PARAMETER VERB                                                              |     |

| GET CONNECTION LIST ENTRY VERB                                                  |     |

| PROCESSING STATE VERB                                                           |     |

| CONVERTER STREAM, CHANNEL VERB                                                  |     |

| UNSOLICITED RESPONSE VERB                                                       |     |

| DIGITAL CONVERTER CONTROL VERB                                                  |     |

| S/PDIF VERB (VENDOR-SPECIFIC)                                                   |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                    |     |

| GET CHANNEL STATUS VERB (VENDOR-SPECIFIC)                                       | 122 |

| GET NON-AUDIO FLAG VERB (VENDOR-SPECIFIC)                                       |     |

| OVERWRITE CONTROL VERB (VENDOR-SPECIFIC)                                        |     |

| DAC1 AUDIO OUTPUT CONVERTER WIDGET (NID = 06H)                                  | 125 |

| STREAM FORMAT VERB                                                              | 125 |

| AMPLIFIER GAIN/MUTE VERB                                                        | 126 |

| GET PARAMETER VERB                                                              | 127 |

| POWER STATE VERB                                                                | 128 |

| CONVERTER STREAM, CHANNEL VERB                                                  | 128 |

| UNSOLICITED RESPONSE VERB                                                       | 129 |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                                            |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                    |     |

| DAC2 AUDIO OUTPUT CONVERTER WIDGET (NID = 07H)                                  |     |

| STREAM FORMAT VERB                                                              |     |

| AMPLIFIER GAIN/MUTE VERB                                                        |     |

| GET PARAMETER VERB                                                              |     |

| POWER STATE VERB                                                                | _   |

| CONVERTER STREAM, CHANNEL VERB                                                  | 134 |

| UNSOLICITED RESPONSE VERB                                                                                    | 135                                     |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                                                                         | 135                                     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)  DAC3 AUDIO OUTPUT CONVERTER WIDGET (NID = 08H) |                                         |

| STREAM FORMAT VERB                                                                                           |                                         |

| AMPLIFIER GAIN/MUTE VERB                                                                                     |                                         |

| GET PARAMETER VERB                                                                                           |                                         |

| POWER STATE VERB                                                                                             |                                         |

| CONVERTER STREAM, CHANNEL VERB                                                                               |                                         |

| UNSOLICITED RESPONSE VERB                                                                                    |                                         |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                                                                         | 141                                     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                                                 | 141                                     |

| MIC1 MUX SELECTOR WIDGET (NID = 09H)                                                                         | 143                                     |

| GET PARAMETER VERB                                                                                           | 143                                     |

| CONNECTION SELECT CONTROL VERB                                                                               | 143                                     |

| GET CONNECTION LIST ENTRY VERB                                                                               | 144                                     |

| PGA1 SELECTOR WIDGET (NID = 0AH)                                                                             | 145                                     |

| AMPLIFIER GAIN/MUTE VERB                                                                                     | 145                                     |

| GET PARAMETER VERB                                                                                           | 146                                     |

| GET CONNECTION LIST ENTRY VERB                                                                               | 146                                     |

| PGA CONTROL VERB (VENDOR-SPECIFIC)                                                                           |                                         |

| PGA2 SELECTOR WIDGET (NID = 0BH)                                                                             | 149                                     |

| AMPLIFIER GAIN/MUTE VERB                                                                                     | 149                                     |

| GET PARAMETER VERB                                                                                           |                                         |

| GET CONNECTION LIST ENTRY VERB                                                                               |                                         |

| PGA CONTROL VERB (VENDOR-SPECIFIC                                                                            |                                         |

| PORT-E PIN COMPLEX WIDGET (NID = 0CH)                                                                        |                                         |

| GET PARAMETER VERB                                                                                           |                                         |

| PIN WIDGET CONTROL VERB                                                                                      |                                         |

| UNSOLICITED RESPONSE VERB                                                                                    |                                         |

| PIN SENSE VERB                                                                                               |                                         |

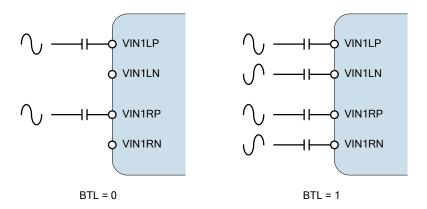

| EAPD/BTL VERB                                                                                                |                                         |

| CONFIGURATION DEFAULT VERB                                                                                   |                                         |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                                                 |                                         |

| AUTO-MUTE CONTROL VERB (VENDOR-SPECIFIC)                                                                     |                                         |

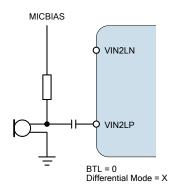

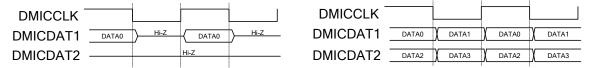

| PORT-B PIN COMPLEX WIDGET (NID = 0DH)                                                                        |                                         |

| AMPLIFIER GAIN/MUTE VERB                                                                                     |                                         |

| GET PARAMETER VERB                                                                                           |                                         |

| PIN WIDGET CONTROL VERB                                                                                      | • • • • • • • • • • • • • • • • • • • • |

| UNSOLICITED RESPONSE VERB                                                                                    |                                         |

| PIN SENSE VERB                                                                                               |                                         |

| EAPD/BTL VERB                                                                                                |                                         |

| CONFIGURATION DEFAULT VERBUNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                       |                                         |

| DIFFERENTIAL VERB (VENDOR-SPECIFIC)                                                                          |                                         |

| AUTO-MUTE CONTROL VERB (VENDOR-SPECIFIC)                                                                     |                                         |

| PORT-D PIN COMPLEX WIDGET (NID = 0EH)                                                                        |                                         |

| AMPLIFIER GAIN/MUTE VERB                                                                                     |                                         |

| GET PARAMETER VERB                                                                                           |                                         |

| PIN WIDGET CONTROL VERB                                                                                      |                                         |

| CONFIGURATION DEFAULT VERB                                                                                   |                                         |

| S/PDIF OUT PIN COMPLEX WIDGET (NID = 0FH)                                                                    |                                         |

| GET PARAMETER VERB                                                                                           |                                         |

| GET CONNECTION LIST ENTRY VERB                                                                               |                                         |

| PIN WIDGET CONTROL VERB                                                                                      |                                         |

|                                                                                                              |                                         |

| UNSOLICITED RESPONSE VERB                                                             |     |

|---------------------------------------------------------------------------------------|-----|

| PIN SENSE VERB                                                                        |     |

| CONFIGURATION DEFAULT VERB                                                            |     |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                                                  |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                          |     |

| S/PDIF IN PIN COMPLEX WIDGET (NID = 10H)                                              |     |

| GET PARAMETER VERB                                                                    |     |

| PIN WIDGET CONTROL VERB                                                               |     |

| UNSOLICITED RESPONSE VERB                                                             |     |

| PIN SENSE VERB                                                                        |     |

| CONFIGURATION DEFAULT VERB                                                            | _   |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                          |     |

| S/PDIF IN CONTROL VERB (VENDOR-SPECIFIC)                                              |     |

| PORT-A PIN COMPLEX WIDGET (NID = 11H)                                                 | 185 |

| GET PARAMETER VERB                                                                    |     |

| GET CONNECTION LIST ENTRY VERB                                                        |     |

| PIN WIDGET CONTROL VERB                                                               |     |

| UNSOLICITED RESPONSE VERB                                                             |     |

| PIN SENSE VERB                                                                        |     |

| CONFIGURATION DEFAULT VERB                                                            |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                          | 189 |

| PORT-G PIN COMPLEX WIDGET (NID = 12H)                                                 | 191 |

| GET PARAMETER VERB                                                                    | 191 |

| GET CONNECTION LIST ENTRY VERB                                                        | 192 |

| PIN WIDGET CONTROL VERB                                                               |     |

| UNSOLICITED RESPONSE VERB                                                             |     |

| PIN SENSE VERB                                                                        |     |

| CONFIGURATION DEFAULT VERB                                                            |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                          |     |

| PORT-F PIN COMPLEX WIDGET (NID = 13H)                                                 |     |

| GET CONNECTION LIST ENTRY VERB                                                        |     |

| PIN WIDGET CONTROL VERB                                                               |     |

| UNSOLICITED RESPONSE VERB                                                             |     |

| PIN SENSE VERB                                                                        |     |

| CONFIGURATION DEFAULT VERB                                                            |     |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)                          |     |

| BEEP GENERATOR WIDGET (NID = 14H)                                                     | 203 |

| AMPLIFIER GAIN/MUTE VERB                                                              | 203 |

| GET PARAMETER VERB                                                                    | 204 |

| BEEP GENERATION VERB                                                                  |     |

| BEEP MASK SELECTION VERB (VENDOR SPECIFIC)                                            |     |

| MIC2 AUDIO INPUT CONVERTER WIDGET (NID = 15H)                                         |     |

| STREAM FORMAT VERB                                                                    |     |

| GET PARAMETER VERB                                                                    |     |

| GET CONNECTION LIST ENTRY VERB                                                        |     |

| PROCESSING STATE VERBCONVERTER STREAM, CHANNEL VERB                                   |     |

| UNSOLICITED RESPONSE VERB                                                             |     |

| UNSOLICITED RESPONSE VERBUNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC) |     |

| CHANNEL COPY VERB (VENDOR-SPECIFIC)                                                   |     |

| PORT-H PIN COMPLEX WIDGET (NID = 16H)                                                 |     |

| AMPLIFIER GAIN/MUTE VERB                                                              |     |

| GET PARAMETER VERB                                                                    |     |

| GET CONNECTION LIST ENTRY VERB                                   | 215 |

|------------------------------------------------------------------|-----|

| PIN WIDGET CONTROL VERB                                          | 215 |

| CONFIGURATION DEFAULT VERB                                       | 216 |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                             | 218 |

| S/PDIF TX 2 AUDIO OUTPUT CONVERTER WIDGET (NID = 17H)            |     |

| STREAM FORMAT VERB                                               | 219 |

| GET PARAMETER VERB                                               | 220 |

| CONVERTER STREAM, CHANNEL VERB                                   | 221 |

| UNSOLICITED RESPONSE VERB                                        | 221 |

| S/PDIF CONVERTER CONTROL VERB                                    | 222 |

| INTERNAL PATH VERB (VENDOR-SPECIFIC)                             | 223 |

| TX CHANNEL STATUS CONTROL VERB (VENDOR-SPECIFIC)                 | 223 |

| CHANNEL STATUS DATA PACKING CONFIGURATION VERB (VENDOR-SPECIFIC) | 224 |

| UNSOLICITED RESPONSE PRIORITY CONTROL VERB (VENDOR-SPECIFIC)     | 224 |

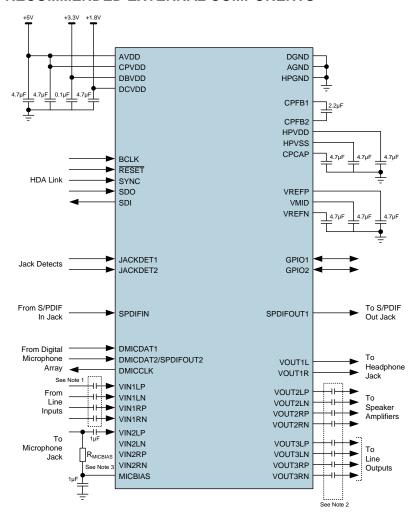

| APPLICATIONS INFORMATION                                         | 225 |

| RECOMMENDED EXTERNAL COMPONENTS                                  | 225 |

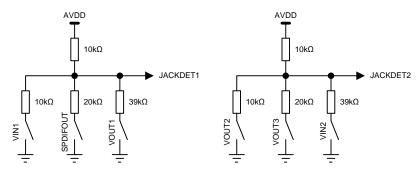

| REQUIRED JACK DETECT COMPONENTS                                  |     |

| PACKAGE DIMENSIONS                                               | 227 |

| IMPORTANT NOTICE                                                 |     |

| REVISION HISTORY                                                 | 229 |

| KEVISION HISTORT                                                 |     |

8

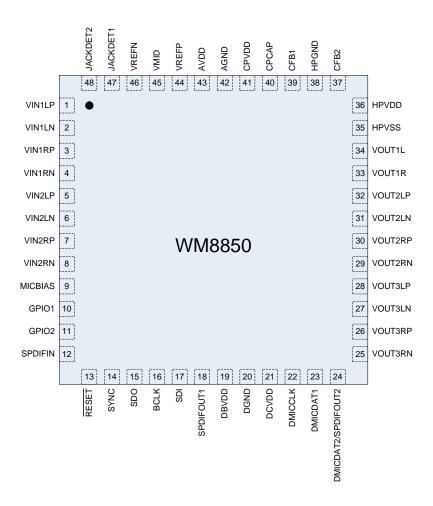

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| ORDER CODE    | TEMPERATURE RANGE | PACKAGE                                | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|-------------------|----------------------------------------|-------------------------------|-------------------------------|

| WM8850GEFL/V  | -40°C to +85°C    | 48-pin QFN<br>(Pb-free)                | MSL3                          | 260°C                         |

| WM8850GEFL/RV | -40°C to +85°C    | 48-pin QFN<br>(Pb-free, tape and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 2200

## **PIN DESCRIPTION**

| PIN NO         | NAME              | TYPE                             | DESCRIPTION                                                                               |

|----------------|-------------------|----------------------------------|-------------------------------------------------------------------------------------------|

| 1              | VIN1LP            | Analogue input                   | Left channel 1 positive input                                                             |

| 2              | VIN1LN            | Analogue input                   | Left channel 1 negative input                                                             |

| 3              | VIN1RP            | Analogue input                   | Right channel 1 positive input                                                            |

| 4              | VIN1RN            | Analogue input                   | Right channel 1 negative input                                                            |

| 5              | VIN2LP            | Analogue input                   | Left channel 2 positive input                                                             |

| 6              | VIN2LN            | Analogue input                   | Left channel 2 negative input                                                             |

| 7              | VIN2RP            | Analogue input                   | Right channel 2 positive input                                                            |

| 8              | VIN2RN            | Analogue input                   | Right channel 2 negative input                                                            |

| 9              | MICBIAS           | Analogue output                  | Microphone bias output                                                                    |

| 10             | GPIO1             | Digital input / output           | General purpose digital input/output 1                                                    |

| 11             | GPIO2             | Digital input / output           | General purpose digital input/output 2                                                    |

| 12             | SPDIFIN           | Digital input                    | S/PDIF Input                                                                              |

| 13             | /RESET            | Digital input                    | Global reset (active low)                                                                 |

| 14             | SYNC              | Digital input                    | HDA frame sync, 48kHz                                                                     |

| 15             | SDO               | Digital input                    | Serial data output from HDA controller                                                    |

| 16             | BCLK              | Digital input                    | HDA Link bit clock, 24MHz                                                                 |

| 17             | SDI               | Digital input / output           | Serial data input to HDA controller                                                       |

| 18             | SPDIFOUT1         | Digital output                   | S/PDIF output 1                                                                           |

| 19             | DBVDD             | Supply input                     | Digital buffer supply input                                                               |

| 20             | DGND              | Supply input                     | Digital ground (return for DBVDD and DCVDD)                                               |

| 21             | DCVDD             | Supply input                     | Digital core supply input                                                                 |

| 22             | DMICCLK           | Digital output                   | Digital microphone clock output                                                           |

| 23             | DMICDAT1          | Digital input                    | Digital microphone data input 1                                                           |

| 24             | DMICDAT2/         | Digital input / output           | Digital microphone data input 2 /                                                         |

|                | SPDIFOUT2         |                                  | S/PDIF output 2                                                                           |

| 25             | VOUT3RN           | Analogue output                  | Right channel 3 negative output                                                           |

| 26             | VOUT3RP           | Analogue output                  | Right channel 3 positive output                                                           |

| 27             | VOUT3LN           | Analogue output                  | Left channel 3 negative output                                                            |

| 28             | VOUT3LP           | Analogue output                  | Left channel 3 positive output                                                            |

| 29             | VOUT2RN           | Analogue output                  | Right channel 2 negative output                                                           |

| 30             | VOUT2RP           | Analogue output                  | Right channel 2 positive output                                                           |

| 31             | VOUT2LN           | Analogue output                  | Left channel 2 negative output                                                            |

| 32             | VOUT2LP           | Analogue output                  | Left channel 2 positive output                                                            |

| 33             | VOUT1R            | Analogue output                  | Right channel 1 output                                                                    |

| 34             | VOUT1L            | Analogue output                  | Left channel 1 output                                                                     |

| 35             | HPVSS             | Supply output                    | Charge pump negative supply decoupling point                                              |

| 36             | HPVDD             | Supply output                    | Charge pump positive supply decoupling point                                              |

| 37             | CFB2              | Analogue output                  | Charge pump flyback capacitor pin 2                                                       |

| 38<br>39       | HPGND<br>CFB1     | Supply input  Analogue output    | Charge pump ground (return path for HPVDD and HPVSS)  Charge pump flyback capacitor pin 1 |

|                | CPCAP             | Supply output                    | Internally generated regulated charge pump supply decoupling point                        |

| 40<br>41       | CPCAP             | Supply output  Supply input      | Charge pump supply input                                                                  |

| 42             | AGND              | Supply input Supply input        | Analogue ground (return path for AVDD and CPVDD)                                          |

| 43             | AGND              | Supply input                     | Analogue supply input                                                                     |

| 43             | VREFP             | Analogue output                  | Analogue supply input  Analogue positive reference decoupling point                       |

| 44             | VMID              | Analogue output                  | Midrail voltage decoupling point                                                          |

| <del>1</del> 0 |                   | Analogue output  Analogue output | Analogue negative reference decoupling point                                              |

| 46             | \/DLLN            |                                  |                                                                                           |

| 46<br>47       | VREFN<br>JACKDET1 | Analogue output  Analogue output | Jack detect sense 1                                                                       |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Cirrus Logic tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                   | MIN        | MAX         |

|---------------------------------------------|------------|-------------|

| Analogue supply voltage (AVDD)              | -0.3V      | +7V         |

| Charge pump supply voltage (CPVDD)          | -0.3V      | +7V         |

| Digital core supply voltage (DCVDD)         | -0.3V      | +2.5V       |

| Digtial buffer supply voltage (DBVDD)       | -0.3V      | +7V         |

| Voltage range digital inputs                | DGND -0.3V | DBVDD +0.3V |

| Voltage range analogue inputs               | AGND -0.3V | AVDD +0.3V  |

| Operating temperature range, T <sub>A</sub> | -40°C      | +85°C       |

| Junction temperature, T <sub>JMAX</sub>     | -40°C      | +150°C      |

| Storage temperature after soldering         | -65°C      | +150°C      |

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER SYMBOL            |                   | MIN  | TYP | MAX  | UNIT |  |

|-----------------------------|-------------------|------|-----|------|------|--|

| CODEC Power Supplies        |                   |      |     |      |      |  |

| Digital core supply range   | DCVDD             | 1.62 | 1.8 | 1.98 | V    |  |

| Digital buffer supply range | DBVDD             | 2.97 | 3.3 | 3.63 | V    |  |

| Analogue supply range       | AVDD              | 4.5  | 5.0 | 5.25 | V    |  |

| Charge pump supply range    | CPVDD             | 4.5  | 5.0 | 5.25 | V    |  |

| Ground                      | DGND, AGND, HPGND |      | 0   |      | V    |  |

## Notes:

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other (i.e. not internally connected).

## THERMAL PERFORMANCE

Thermal analysis should be performed in the intended application to prevent the WM8850 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device on the PCB in relation to surrounding components and the number of PCB layers. Connecting the GND paddle through thermal vias and into a large ground plane will aid heat extraction.

Three main heat transfer paths exist to surrounding air as illustrated below in Figure 1:

- Package top to air (radiation).

- Package bottom to PCB (radiation).

- Package leads & paddle to PCB (conduction).

Figure 1 Heat Transfer Paths

The temperature rise  $T_R$  is given by  $T_R$  =  $P_D$  \*  $\Theta_{JA}$

- $P_D$  is the power dissipated in the device.

- O<sub>JA</sub> is the thermal resistance from the junction of the die to the ambient temperature and is therefore a measure of heat transfer from the die to surrounding air. O<sub>JA</sub> is determined with reference to JEDEC standard JESD51-9.

The junction temperature  $T_J$  is given by  $T_J = T_A + T_R$ , where  $T_A$  is the ambient temperature.

| PARAMETER                      | SYMBOL         | MIN | TYP | MAX | UNIT |

|--------------------------------|----------------|-----|-----|-----|------|

| Operating temperature range    | T <sub>A</sub> | -40 |     | 85  | °C   |

| Operating junction temperature | $T_J$          | -40 |     | 125 | °C   |

| Thermal Resistance             | $\Theta_{JA}$  |     | 29  |     | °C/W |

## **ELECTRICAL CHARACTERISTICS**

## **Test Conditions**

$AVDD = CPVDD = 5V, \ DBVDD = 3.3V, \ DCVDD = 1.8V, \ T_A = +25^{\circ}C, \ 1kHz \ signal, \ fs = 48kHz, \ 24-bit \ data \ unless \ otherwise \ stated.$

| PARAMETER                                  | SYMBOL                                            | TEST CONDITIONS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN | TYP              | MAX | UNIT      |  |  |

|--------------------------------------------|---------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-----------|--|--|

| Analogue Input 1 (VIN1LP,                  | Analogue Input 1 (VIN1LP, VIN1LN, VIN1RP, VIN1RN) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                  |     |           |  |  |

| Maximum Differential<br>Input Signal Level | V <sub>INDIFF(max)</sub>                          | 0dB gain         | VINIUN or VINIUN OdB, VINIUP or VINIUP OT VINIUP OF VINI |     | 2.25 x<br>AVDD/5 |     | $V_{RMS}$ |  |  |

| Maximum Single-ended<br>Input Signal Level | V <sub>INSE(max)</sub>                            | 0dB gain         | VINILIN OF VINILIP OF VINIRIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 1.6 x<br>AVDD/5  |     | $V_{RMS}$ |  |  |

|                                            |                                                   | -12dB gain       | VINILN or VINIRN VINILP or VINIRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 42               |     | kΩ        |  |  |

| Input impedance                            | Z <sub>IN</sub>                                   | 0dB gain         | VINTLN or VINTRN VINTLP or VINTRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 27               |     | kΩ        |  |  |

|                                            |                                                   | +12dB<br>gain    | VINTLN or VINTRN VINTLP or VINTRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 9                |     | kΩ        |  |  |

| Common Mode Rejection<br>Ratio             | CMRR                                              | 20Hz to<br>20kHz | VINILI OR OBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 55               |     | dB        |  |  |

| Minimum PGA Gain<br>Setting                |                                                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | -12              |     | dB        |  |  |

| Maximum PGA Gain<br>Setting                |                                                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | +12              |     | dB        |  |  |

| PGA Gain Step Size                         |                                                   | G                | uaranteed monotonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 0.5              |     | dB        |  |  |

$AVDD = CPVDD = 5V, DBVDD = 3.3V, DCVDD = 1.8V, T_A = +25^{\circ}C, 1 kHz \ signal, fs = 48kHz, 24-bit \ data \ unless \ otherwise \ stated.$

| PARAMETER                                  | SYMBOL                   |                                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MIN | TYP                 | MAX | UNIT      |

|--------------------------------------------|--------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|-----------|

| Analogue Input 2 (VIN2LP,                  | VIN2LN, VIN2             | 2RP, VIN2RN)                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                     |     |           |

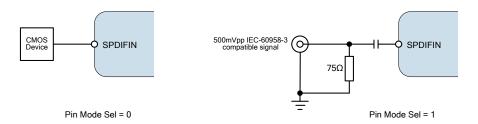

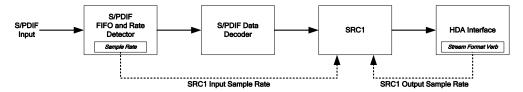

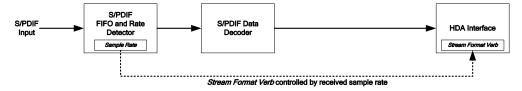

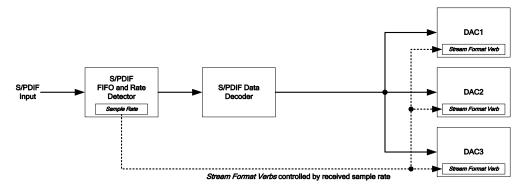

| Maximum Differential<br>Input Signal Level | V <sub>INDIFF(max)</sub> | 0dB gain                                           | VINZLN or VINZRN OdB OdB To ADC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 2.25 x<br>AVDD/5    |     | $V_{RMS}$ |