# **EXTENDED COMMON-MODE RS-485 TRANSCEIVERS**

#### **FEATURES**

- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of -55°C to 125°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree<sup>†</sup>

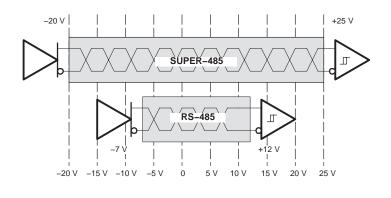

- Common-Mode Voltage Range (-20 V to 25 V)

More Than Doubles TIA/EIA-485 Requirement

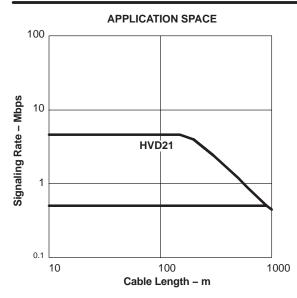

- Receiver Equalization Extends Cable Length, Signaling Rate (HVD23, HVD24)

- Reduced Unit-Load for up to 256 Nodes

- Bus I/O Protection to Over 16-kV HBM

- Failsafe Receiver for Open-Circuit, Short-Circuit and Idle-Bus Conditions

- Low Standby Supply Current 1.5-µA Max

- More Than 100 mV Receiver Hysteresis

- † Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

#### **APPLICATIONS**

- Long Cable Solutions

- Factory Automation

- Security Networks

- Building HVAC

- Severe Electrical Environments

- Electrical Power Inverters

- Industrial Drives

- Avionics

#### **DESCRIPTION**

The SN65HVD21M offers performance exceeding typical RS-485 devices. In addition to meeting all requirements of the TIA/EIA-485-A standard, the HVD2x family operates over an extended range of common-mode voltage, and has features such as high ESD protection, wide receiver hysteresis, and failsafe operation. This family of devices is ideally suited for long-cable networks, and other applications where the environment is too harsh for ordinary transceivers.

The SN65HVD21M is designed for bidirectional data transmission on multipoint twisted-pair cables. Example applications are digital motor controllers, remote sensors and terminals, industrial process control, security stations, and environmental control systems.

The SN65HVD21M combines a 3-state differential driver and a differential receiver, which operates from a single 5-V power supply. The driver differential outputs and the receiver differential inputs are connected internally to form a differential bus port that offers minimum loading to the bus. This port features an extended common-mode voltage range making the device suitable for multipoint applications over long cable runs.

The SN65HVD21M allows up to 256 connected nodes at moderate data rates (up to 5 Mbps). The driver output slew rate is controlled to provide reliable switching with shaped transitions which reduce high-frequency noise emissions.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SN65HVDM21 Operates Over a Wider Common-Mode Voltage Range

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION** (continued)

The receiver also includes a failsafe circuit that provides a high-level output within 250  $\mu$ s after loss of the input signal. The most common causes of signal loss are disconnected cables, shorted lines, or the absence of any active transmitters on the bus. This feature prevents noise from being received as valid data under these fault conditions. This feature may also be used for Wired-Or bus signaling.

The SN65HVD21M is characterized for operation over the temperature range of -55°C to 125°C.

#### PRODUCT SELECTION GUIDE

| PART NUMBERS CABLE LENGTH AND SIGNALING RATE <sup>(1)</sup> |                                              | NODES     | MARKING   |

|-------------------------------------------------------------|----------------------------------------------|-----------|-----------|

| SN65HVD21MDREP                                              | Up to 150 m at 5 Mbps (with slew rate limit) | Up to 256 | D: V21MEP |

<sup>(1)</sup> Distance and signaling rate predictions based upon Belden 3105A cable and 15% eye pattern jitter.

#### **AVAILABLE OPTIONS**

| PLASTIC SMALL-OUTLINE(1) |  |  |  |  |

|--------------------------|--|--|--|--|

| D PACKAGE                |  |  |  |  |

| (JEDEC MS-012)           |  |  |  |  |

| SN65HVD21MDREP           |  |  |  |  |

(1) Add R suffix for taped and reeled carriers.

#### **DRIVER FUNCTION TABLE**

| INPUT | ENABLE | OUTPUTS |   |  |

|-------|--------|---------|---|--|

| D     | DE     | Α       | В |  |

| Н     | Н      | Н       | L |  |

| L     | Н      | L       | Н |  |

| X     | L      | Z       | Z |  |

| X     | OPEN   | Z       | Z |  |

| OPEN  | Н      | Н       | L |  |

H = high level, L= low level, X = don't care, Z = high impedance (off), ? = indeterminate

#### **RECEIVER FUNCTION TABLE**

| DIFFERENTIAL INPUT                               | ENABLE | OUTPUT         |

|--------------------------------------------------|--------|----------------|

| $V_{ID} = (V_A - V_B)$                           | RE     | R              |

| 0.2 V ≤ V <sub>ID</sub>                          | L      | Н              |

| $-0.2 \text{ V} < \text{V}_{1D} < 0.2 \text{ V}$ | L      | H (see Note A) |

| $V_{ID} \le -0.2 V$                              | L      | L              |

| X                                                | Н      | Z              |

| X                                                | OPEN   | Z              |

| Open circuit                                     | L      | Н              |

| Short Circuit                                    | L      | Н              |

| Idle (terminated) bus                            | L      | Н              |

H = high level, L= low level, Z = high impedance (off)

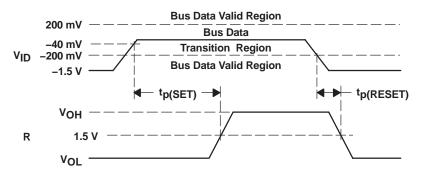

NOTE A: If the differential input V<sub>ID</sub> remains within the transition range for more than 250 μs, the integrated failsafe circuitry detects a bus fault, and set the receiver output to a high state. See Figure 15.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

| Supply voltage <sup>(2)</sup> , V <sub>CC</sub> |                                           |            | –0.5 V to 7 V                      |  |

|-------------------------------------------------|-------------------------------------------|------------|------------------------------------|--|

| Voltage at any bus I/O term                     | ninal                                     |            | –27 V to 27 V                      |  |

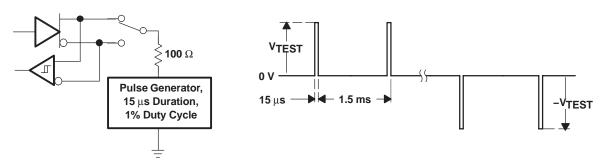

| Voltage input, transient puls                   | se, A and B, (through 100 $\Omega$ , see  | Figure 16) | –60 V to 60 V                      |  |

| Voltage input at any D, DE                      | Voltage input at any D, DE or RE terminal |            |                                    |  |

| Receiver output current, IO                     | Receiver output current, IO               |            |                                    |  |

|                                                 | Human Body Model(3)                       | A, B, GND  | 16 kV                              |  |

| Electronic Confloring                           |                                           | All pins   | 5 kV                               |  |

| Electrostatic discharge                         | Charged-Device Model <sup>(4)</sup>       | All pins   | 1.5 kV                             |  |

|                                                 | Machine Model <sup>(5)</sup>              | All pins   | 200 V                              |  |

| Continuous total power dissipation              |                                           |            | See Power Dissipation Rating Table |  |

| Junction temperature, T <sub>J</sub>            |                                           |            | 150°C                              |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with JEDEC Standard 22, Test Method A114-A.

<sup>(4)</sup> Tested in accordance with JEDEC Standard 22, Test Method C101.

<sup>(5)</sup> Tested in accordance with JEDEC Standard 22, Test Method A115-A.

# **POWER DISSIPATION RATINGS**

| PACKAGE | CIRCUIT BOARD<br>MODEL | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR <sup>(3)</sup> ABOVE $T_A = 25^{\circ}C$ | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|------------------------|----------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|---------------------------------------|

| D       | Low-K(1)               | 577 mW                                                                     | 4.62 mW/°C                                               | 369 mW                                | 300 mW                                |

|         | High-K <sup>(2)</sup>  | 913 mW                                                                     | 7.3 mW/°C                                                | 584 mW                                | 474 mW                                |

<sup>(1)</sup> In accordance with the Low-K thermal metric definitions of EIA/JESD51-3.

# THERMAL CHARACTERISTICS

| PARAMETER                               |                                | TEST CONDITIONS                                                                                                                                                                                                     |                                                                                                                                                                                                           |        | UNITS |      |

|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|

| θЈВ                                     | Junction-to-board thermal res  | istance                                                                                                                                                                                                             |                                                                                                                                                                                                           |        | 86.2  | 0000 |

| θЈС                                     | Junction-to-case thermal resis | stance                                                                                                                                                                                                              |                                                                                                                                                                                                           |        | 47.1  | °C/W |

| P <sub>D</sub> Device power dissipation | Typical                        | V <sub>CC</sub> = 5 V, T <sub>J</sub> = 25°C,<br>R <sub>L</sub> = 54 Ω, C <sub>L</sub> = 50 pF (driver),<br>C <sub>L</sub> = 15 pF (receiver),<br>50% Duty cycle square-wave signal,<br>Driver and receiver enabled | 5 Mbps                                                                                                                                                                                                    | 260    | mW    |      |

|                                         |                                | Worst case                                                                                                                                                                                                          | V <sub>CC</sub> = 5.5 V, T <sub>J</sub> = 125°C,R <sub>L</sub> = 54 Ω,<br>C <sub>L</sub> = 50 pF, C <sub>L</sub> = 15 pF (receiver),<br>50% Duty cycle square-wave signal,<br>Driver and receiver enabled | 5 Mbps | 342   |      |

| T <sub>SD</sub>                         | Thermal shut-down junction to  | emperature                                                                                                                                                                                                          |                                                                                                                                                                                                           |        | 170   | °C   |

# RECOMMENDED OPERATING CONDITIONS

|                                          |                     |   | MIN | NOM | MAX | UNIT |

|------------------------------------------|---------------------|---|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>          |                     |   | 4.5 | 5   | 5.5 | V    |

| Voltage at any bus I/O terminal          | A, B                |   | -20 |     | 25  | V    |

| High-level input voltage, VIH            | DE RE               |   | 2   |     | VCC | .,   |

| Low-level input voltage, V <sub>IL</sub> | D, DE, RE           |   | 0   |     | 0.8 | V    |

| Differential input voltage, VID          | A with respect to B |   | -25 |     | 25  | V    |

|                                          | Driver              | • |     |     | 110 |      |

| Output current                           | Receiver            |   | -8  |     | 8   | mA   |

| Operating free-air temperature, Ta       | (1)                 |   | -55 |     | 125 | °C   |

| Junction temperature, T <sub>J</sub>     |                     |   | -55 |     | 130 | °C   |

<sup>(1)</sup> Maximum free-air temperature operation is allowed as long as the device recommended junction temperature is not exceeded.

<sup>(2)</sup> In accordance with the High-K thermal metric definitions of EIA/JESD51-7.

<sup>(3)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

# **DRIVER ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)(1)

|                        | PARAMETER                                                               | TEST CONDITIONS                                              | MIN  | TYP(1)     | MAX | UNIT |

|------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------|------------|-----|------|

| VIK                    | Input clamp voltage                                                     | I <sub>I</sub> = -18 mA                                      | -1.5 | 0.75       |     | V    |

| VO                     | Open-circuit output voltage                                             | A or B, No load                                              | 0    |            | VCC | V    |

|                        |                                                                         | No load (open circuit)                                       | 3.3  | 4.2        | VCC |      |

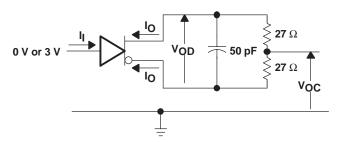

| V <sub>OD(SS)</sub>    | Steady-state differential output voltage magnitude                      | $R_L$ = 54 Ω, See Figure 1                                   | 1.8  | 2.5        |     | V    |

| (,                     | magnitude                                                               | With common-mode loading, See Figure 2                       | 1.8  |            |     |      |

| Δ V <sub>OD</sub> (SS) | Change in steady-state differential output voltage between logic states | See Figure 1 and Figure 3                                    | -0.1 |            | 0.1 | V    |

| Voc(ss)                | Steady-state common-mode output voltage                                 | See Figure 1                                                 | 2.1  | 2.5        | 2.9 | V    |

| ΔV <sub>OC</sub> (SS)  | Change in steady-state common-mode output voltage, VOC(H) – VOC(L)      | See Figure 1 and Figure 4                                    | -0.1 |            | 0.1 | V    |

| VOC(PP)                | Peak-to-peak common-mode output voltage,  VOC(MAX) - VOC(MIN)           | $R_L$ = 54 $Ω$ , $C_L$ = 50 pF,<br>See Figure 1 and Figure 4 |      | 0.35       |     | V    |

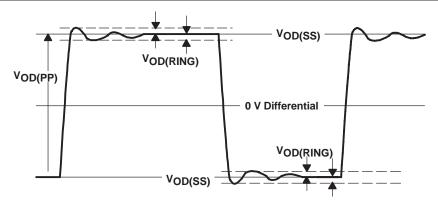

| VOD(RING)              | Differential output voltage over and under shoot                        | $R_L$ = 54 Ω, $C_L$ = 50 pF, See Figure 5                    |      |            | 10% |      |

| l <sub>l</sub>         | Input current                                                           | D, DE                                                        | -100 |            | 100 | μΑ   |

| I <sub>O(OFF)</sub>    | Output current with power off                                           | V <sub>CC</sub> <= 2.5 V                                     | 100  |            | 125 | ^    |

| loz                    | High impedance state output current                                     | DE at 0 V                                                    | -100 | 1 - 100    |     | μΑ   |

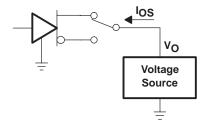

| los                    | Short-circuit output current                                            | $V_O = -7 \text{ V to } 12 \text{ V},$ See Figure 9          | -270 |            | 250 | mA   |

| C <sub>OD</sub>        | Differential output capacitance                                         |                                                              | Se   | e receiver | Cl  |      |

<sup>(1)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $25^{\circ}\text{C}$ .

# **DRIVER SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                                   | TEST CONDITIONS                                     | MIN | TYP(1) | MAX | UNIT |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----|--------|-----|------|

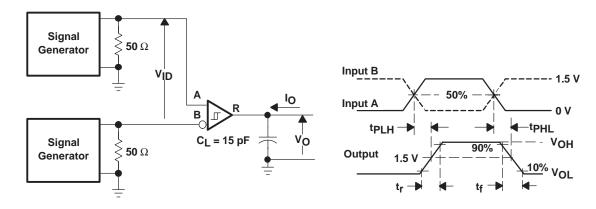

| <sup>t</sup> PHL        | Differential output propagation delay, high-to-low          | $R_L = 54 \Omega$ , $C_L = 50 pF$ ,<br>See Figure 3 | 15  | 32     | 60  | ns   |

| t <sub>r</sub>          | Differential output rise time                               | $R_L = 54 \Omega$ , $C_L = 50 pF$ ,                 | 15  | 40     | 60  | ns   |

| t <sub>f</sub>          | Differential output fall time                               | See Figure 3                                        | 15  | 40     | 60  | 115  |

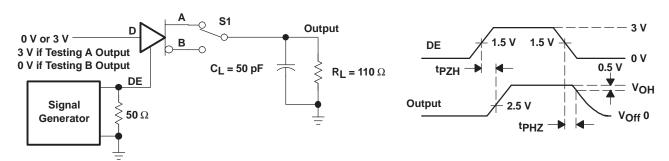

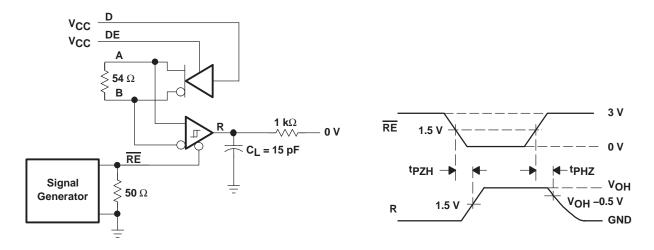

| <sup>t</sup> PZH        | Propagation delay time, high impedance-to-high level output | RE at 0 V, See Figure 6                             |     |        | 140 |      |

| <sup>t</sup> PHZ        | Propagation delay time, high level-output-to-high impedance | RE at 0 v, See Figure 6                             |     |        | 140 | ns   |

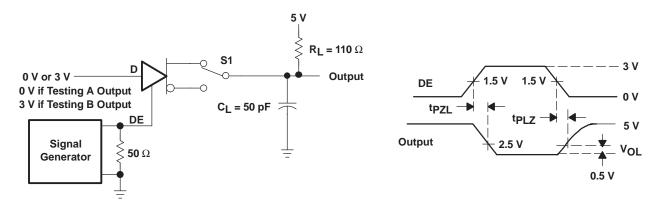

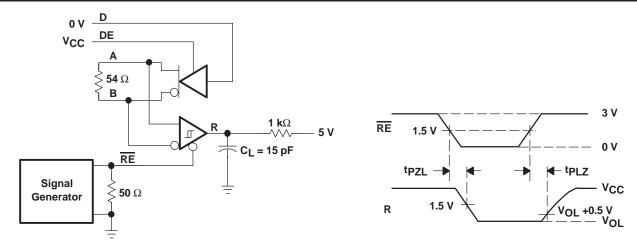

| tPZL                    | Propagation delay time, high impedance-to-low level output  | RE at 0 V, See Figure 7                             |     |        | 140 | 20   |

| t <sub>PLZ</sub>        | Propagation delay time, low level output-to-high impedance  | RE at 0 v, see Figure 7                             |     |        | 140 | ns   |

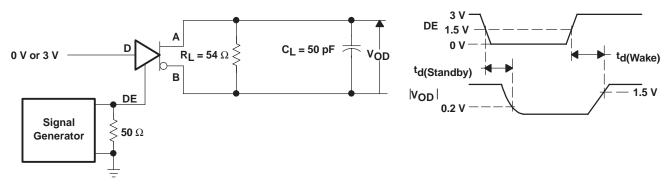

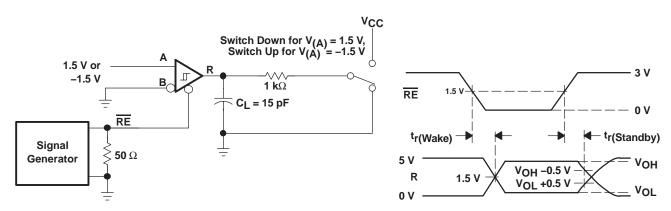

| <sup>t</sup> d(standby) | Time from an active differential output to standby          | RE at V <sub>CC</sub> , See Figure 8                |     |        | 4   | μs   |

| td(wake)                | Wake-up time from standby to an active differential output  | TRE at VCC, see Figure 8                            |     |        | 10  | μs   |

| tsk(p)                  | Pulse skew   tpLH - tpHL                                    |                                                     |     | •      | 10  | ns   |

<sup>(1)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $25^{\circ}\text{C}$ .

# RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions

|                     | PARAMETER                                                 |                                       | TEST CONDITIONS                            |      | TYP(1) | MAX | UNIT |

|---------------------|-----------------------------------------------------------|---------------------------------------|--------------------------------------------|------|--------|-----|------|

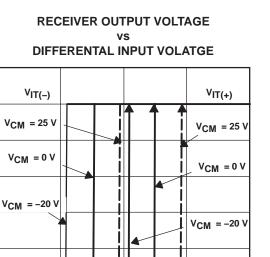

| VIT(+)              | Positive-going differential input voltage threshold       | Soo Figure 10                         | $V_O = 2.4 \text{ V}, I_O = -8 \text{ mA}$ |      | 60     | 200 | mV   |

| VIT(-)              | Negative-going differential input voltage threshold       | See Figure 10                         | $V_O = 0.4 \text{ V}, I_O = 8 \text{ mA}$  | -200 | -60    |     | IIIV |

| VHYS                | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                                       |                                            | 100  | 130    |     | mV   |

| V                   | Positive-going differential input failsafe voltage        | Soo Figure 15                         | $V_{CM} = -7 \text{ V to } 12 \text{ V}$   | 40   | 120    | 200 | mV   |

| V <sub>IT(F+)</sub> | threshold                                                 | See Figure 15                         | $V_{CM} = -20 \text{ V to } 25 \text{ V}$  |      | 120    | 250 | IIIV |

| \/\                 | Negative-going differential input failsafe voltage        | See Figure 15                         | $V_{CM} = -7 \text{ V to } 12 \text{ V}$   | -200 | -120   | -40 | m\/  |

| VIT(F-)             | threshold                                                 |                                       | $V_{CM} = -20 \text{ V to } 25 \text{ V}$  | -250 | -120   |     | mV   |

| VIK                 | Input clamp voltage                                       | I <sub>I</sub> = -18 mA               |                                            | -1.5 |        |     | V    |

| Vон                 | High-level output voltage                                 | $V_{ID}$ = 200 mV, $I_{OH}$           | = -8 mA, See Figure 11                     | 4    |        |     | V    |

| VOL                 | Low-level output voltage                                  | $V_{ID} = -200 \text{ mV}, I_{OL}$    | = 8 mA, See Figure 11                      |      |        | 0.4 | V    |

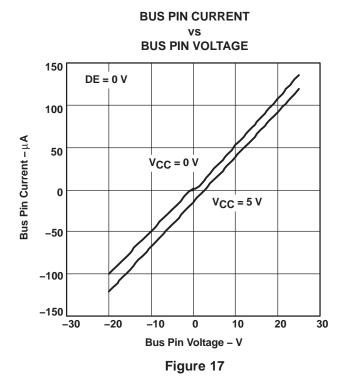

| I(BUS)              | Bus input current (power on or power off)                 | $V_I = -7$ to 12 V, Other input = 0 V |                                            | -100 |        | 125 | μΑ   |

| II                  | Input current                                             | RE                                    |                                            | -100 |        | 125 | μΑ   |

| R <sub>I</sub>      | Input resistance                                          |                                       |                                            | 96   |        |     | kΩ   |

| C <sub>ID</sub>     | Differential input capacitance                            | $V_{ID} = 0.5 + 0.4 \sin\theta$       | e (2π x 1.5 x 10 <sup>6</sup> t)           |      |        | 20  | pF   |

<sup>(1)</sup> All typical values are at 25°C.

# **RECEIVER SWITCHING CHARACTERISTICS**

over recommended operating conditions

|                         | PARAMETER                                              | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |

|-------------------------|--------------------------------------------------------|------------------------------------|-----|-----|-----|------|

| tPHL                    | Propagation delay time, high-to-low level output       | See Figure 11                      |     | 25  | 70  | ns   |

| t <sub>r</sub>          | Receiver output rise time                              | See Figure 44                      |     | 2   | 7   | 20   |

| tf                      | Receiver output fall time                              | See Figure 11                      |     | 2   | ′   | ns   |

| <sup>t</sup> PZH        | Receiver output enable time to high level              | 0 5: 40                            |     | 90  | 145 | 20   |

| <sup>t</sup> PHZ        | Receiver output disable time from high level           | See Figure 12                      |     | 16  | 45  | ns   |

| tPZL                    | Receiver output enable time to low level               | 0 5 40                             |     | 90  | 145 |      |

| tPLZ                    | Receiver output disable time from low level            | See Figure 13                      |     | 16  | 45  | ns   |

| <sup>t</sup> r(standby) | Time from an active receiver output to standby         |                                    |     |     | 4   |      |

| tr(wake)                | Wake-up time from standby to an active receiver output | See Figure 14, DE at 0 V           |     |     | 11  | μs   |

| tsk(p)                  | Pulse skew   tpLH - tpHL                               |                                    |     |     | 7   | ns   |

| tp(set)                 | Delay time, bus fail to failsafe set                   | Coo Figure 45, pulso mate. 4 ld la |     | 250 | 385 | μs   |

| tp(reset)               | Delay time, bus recovery to failsafe reset             | See Figure 15, pulse rate = 1 kHz  |     |     | 70  | ns   |

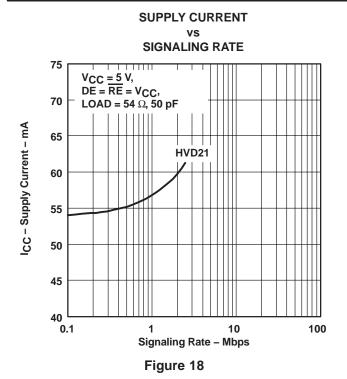

# **SUPPLY CURRENT**

over recommended operating conditions (unless otherwise noted)

|     | PARAMETER      | TEST CONDITIONS                                                                                             | MIN | TYP | MAX | UNIT |

|-----|----------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|     |                | Driver enabled (DE at $V_{CC}$ ), Receiver enabled (RE at 0 V) No load, $V_I = 0 \text{ V or } V_{CC}$      |     | 8   | 15  | mA   |

| laa | Cumply ourrent | Driver enabled (DE at $V_{CC}$ ), Receiver disabled (RE at $V_{CC}$ )<br>No load, $V_{I} = 0$ V or $V_{CC}$ |     | 7   | 14  | mA   |

| Icc | Supply current | Driver disabled (DE at 0 V), Receiver enabled (RE at 0 V) No load                                           |     | 5   | 15  | mA   |

|     |                | Driver disabled (DE at 0 V), Receiver disabled (RE at V <sub>CC</sub> ) D open                              |     |     | 1.5 | μΑ   |

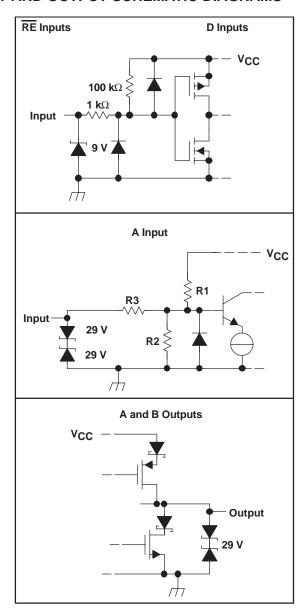

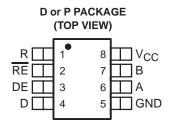

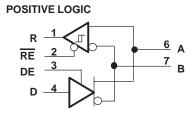

# **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

|       | R1/R2         | R3             |

|-------|---------------|----------------|

| HVD21 | <b>36 k</b> Ω | <b>180 k</b> Ω |

# PARAMETER MEASUREMENT INFORMATION

#### **NOTES:**

Test load capacitance includes probe and jig capacitance (unless otherwise specified). Signal generator characteristics: rise and fall time < 6 ns, pulse rate 100 kHz, 50% duty cycle,  $Z_0$  = 50  $\Omega$  (unless otherwise specified)

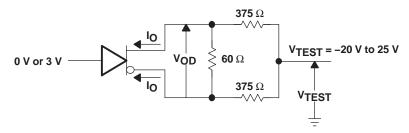

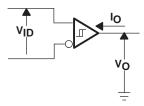

Figure 1. Driver Test Circuit, V<sub>OD</sub> and V<sub>OC</sub> Without Common-Mode Loading

Figure 2. Driver Test Circuit,  $V_{\mbox{\scriptsize OD}}$  With Common-Mode Loading

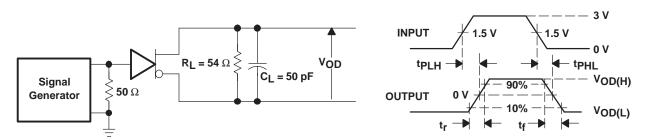

Figure 3. Driver Switching Test Circuit and Waveforms

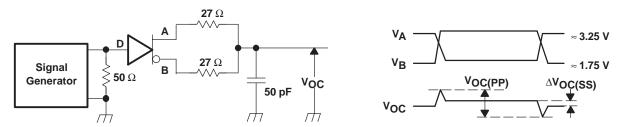

Figure 4. Driver V<sub>OC</sub> Test Circuit and Waveforms

NOTE:  $V_{OD(RING)}$  is measured at four points on the output waveform, corresponding to overshoot and undershoot from the  $V_{OD(H)}$  and  $V_{OD(L)}$  steady state values.

Figure 5. V<sub>OD(RING)</sub> Waveform and Definitions

Figure 6. Driver Enable/Disable Test, High Output

Figure 7. Driver Enable/Disable Test, Low Output

Figure 8. Driver Standby/Wake Test Circuit and Waveforms

Figure 9. Driver Short-Circuit Test

Figure 10. Receiver DC Parameter Definitions

Figure 11. Receiver Switching Test Circuit and Waveforms

Figure 12. Receiver Enable Test Circuit and Waveforms, Data Output High

Figure 13. Receiver Enable Test Circuit and Waveforms, Data Output Low

Figure 14. Receiver Standby and Wake Test Circuit and Waveforms

Figure 15. Receiver Active Failsafe Definitions and Waveforms

Figure 16. Test Circuit and Waveforms, Transient Overvoltage Test

# **PIN ASSIGNMENTS**

# **LOGIC DIAGRAM**

# **TYPICAL CHARACTERISTICS**

6

5

4

3

2

1

0

-0.2

Vo- Receiver Output Voltage - V

0

V<sub>ID</sub> - Differential Input Voltage - V

0.1

0.2

-0.1

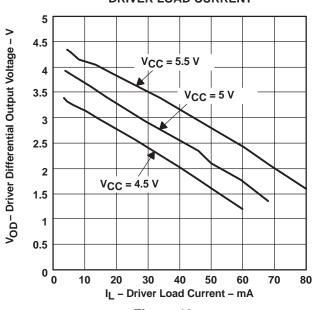

# DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs DRIVER LOAD CURRENT

Figure 19

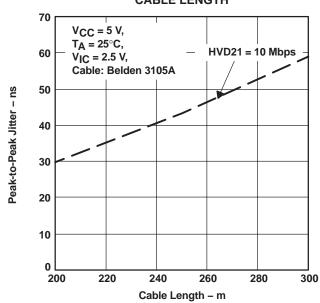

#### PEAK-TO-PEAK JITTER vs CABLE LENGTH

Figure 21

#### APPLICATION INFORMATION

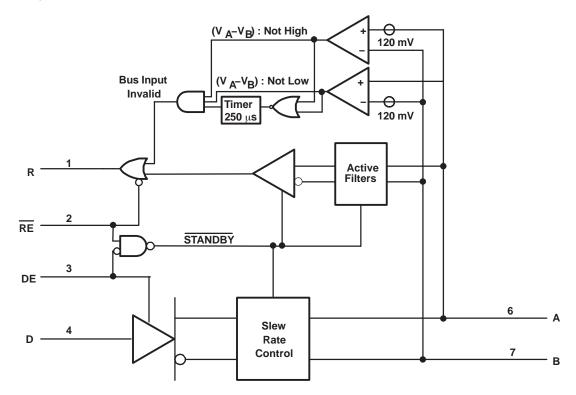

#### THEORY OF OPERATION

The SN65HVD21M integrates a differential receiver and differential driver with additional features for improved performance in electrically-noisy, long-cable, or other fault-intolerant applications.

The receiver hysteresis (typically 130 mV) is much larger than found in typical RS-485 transceivers. This helps reject spurious noise signals which would otherwise cause false changes in the receiver output state.

Slew rate limiting on the driver outputs reduces the high-frequency content of signal edges. This decreases reflections from bus discontinuities, and allows longer stub lengths between nodes and the main bus line. Designers should consider the maximum signaling rate and cable length required for a specific application, and choose the transceiver best matching those requirements.

When DE is low, the differential driver is disabled, and the A and B outputs are in high-impedance states. When DE is high, the differential driver is enabled, and drives the A and B outputs according to the state of the D input.

When  $\overline{RE}$  is high, the differential receiver output buffer is disabled, and the R output is in a high-impedance state. When  $\overline{RE}$  is low, the differential receiver is enabled, and the R output reflects the state of the differential bus inputs on the A and B pins.

If both the driver and receiver are disabled, (DE low and  $\overline{RE}$  high) then all nonessential circuitry, including auxiliary functions such as failsafe and receiver equalization is placed in a low-power standby state. This reduces power consumption to less than 5  $\mu$ W. When either enable input is asserted, the circuitry again becomes active.

In addition to the primary differential receiver, these devices incorporate a set of comparators and logic to implement an active receiver failsafe feature. These components determine whether the differential bus signal is valid. Whenever the differential signal is close to zero volts (neither high nor low), a timer initiates, If the differential input remains within the transition range for more than 250  $\mu$ s, the timer expires and set the receiver output to the high state. If a valid bus input (high or low) is received at any time, the receiver output reflects the valid bus state, and the timer is reset.

Figure 22. Function Block Diagram

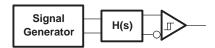

| $ H(s) \ = \ k_0 \Bigg[ \left( 1 - k_1 \right) + \frac{k_1 p_1}{\left( s + p_1 \right)} \Bigg] \Bigg[ \left( 1 - k_2 \right) + \frac{k_2 p_2}{\left( s + p_2 \right)} \Bigg] \Bigg[ \left( 1 - k_3 \right) + \frac{k_3 p_3}{\left( s + p_3 \right)} \Bigg] \Bigg] $ | k0<br>(DC<br>loss) | p1<br>(MHz) | k1  | p2<br>(MHz) | k2  | p3<br>(MHz) | k3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|-----|-------------|-----|-------------|----|

| Similar to 160m of Belden 3105A                                                                                                                                                                                                                                     | 0.95               | 0.25        | 0.3 | 3.5         | 0.5 | 15          | 1  |

| Similar to 250m of Belden 3105A                                                                                                                                                                                                                                     | 0.9                | 0.25        | 0.4 | 3.5         | 0.7 | 12          | 1  |

| Similar to 500m of Belden 3105A                                                                                                                                                                                                                                     | 0.8                | 0.25        | 0.6 | 2.2         | 1   | 8           | 1  |

| Similar to 1000m of Belden 3105A                                                                                                                                                                                                                                    | 0.6                | 0.3         | 1   | 3           | 1   | 6           | 1  |

Figure 23. Cable Attenuation Model for Jitter Measurements

# NOISE CONSIDERATIONS FOR EQUALIZED RECEIVERS

The simplest way of overcoming the effects of cable losses is to increase the sensitivity of the receiver. If the maximum attenuation of frequencies of interest is 20 dB, increasing the receiver gain by a factor of ten compensates for the cable. However, this means that both signal and noise are amplified. Therefore, the receiver with higher gain is more sensitive to noise and it is important to minimize differential noise coupling to the equalized receiver.

Differential noise is crated when conducted or radiated noise energy generates more voltage on one line of the differential pair than the other. For this to occur from conducted or electric far-field noise, the impedance to ground of the lines must differ.

For noise frequency out to 50 MHz, the input traces can be treated as a lumped capacitance if the receiver is approximately 10 inches or less from the connector. Therefore, matching impedance of the lines is accomplished by matching the lumped capacitance of each.

The primary factors that affect the capacitance of a trace are in length, thickness, width, dielectric material, distance from the signal return path, stray capacitance, and proximity to other conductors. It is difficult to match each of the variables for each line of the differential pair exactly, but a reasonable effort to do so keeps the lines balanced and less susceptible to differential noise coupling.

Another source of differential noise is from near-field coupling. In this situation, an assumption of equal noise-source impedance cannot be made as in the far-field. Familiarly known as crosstalk, more energy from a nearby signal is coupled to one line of the differential pair. Minimization of this differential noise is accomplished by keeping the signal pair close together and physical separation from high-voltage, high-current, or high-frequency signals.

In summary, follow these guidelines in board layout for keeping differential noise to a minimum.

- Keep the differential input traces short.

- Match the length, physical dimensions, and routing of each line of the pair.

- Keep the lines close together.

- Match components connected to each line.

- Separate the inputs from high-voltage, high-frequency, or high-current signals.

# PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| SN65HVD21MDREP   | ACTIVE | SOIC         | D       | 8    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -55 to 125   | V21MEP         | Samples |

| SN65HVD21MDREPG4 | ACTIVE | SOIC         | D       | 8    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -55 to 125   | V21MEP         | Samples |

| V62/06615-01XE   | ACTIVE | SOIC         | D       | 8    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -55 to 125   | V21MEP         | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

6-Feb-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Jan-2013

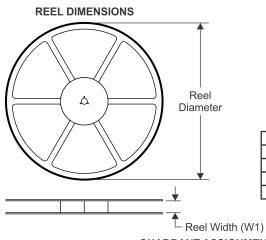

# TAPE AND REEL INFORMATION

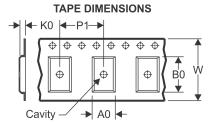

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

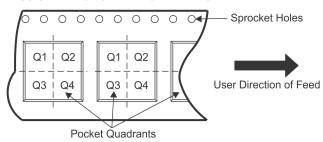

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65HVD21MDREP | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 26-Jan-2013

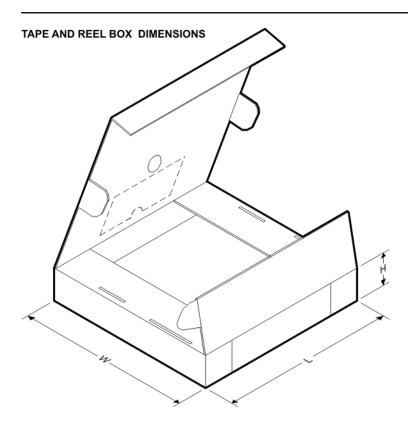

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVD21MDREP | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

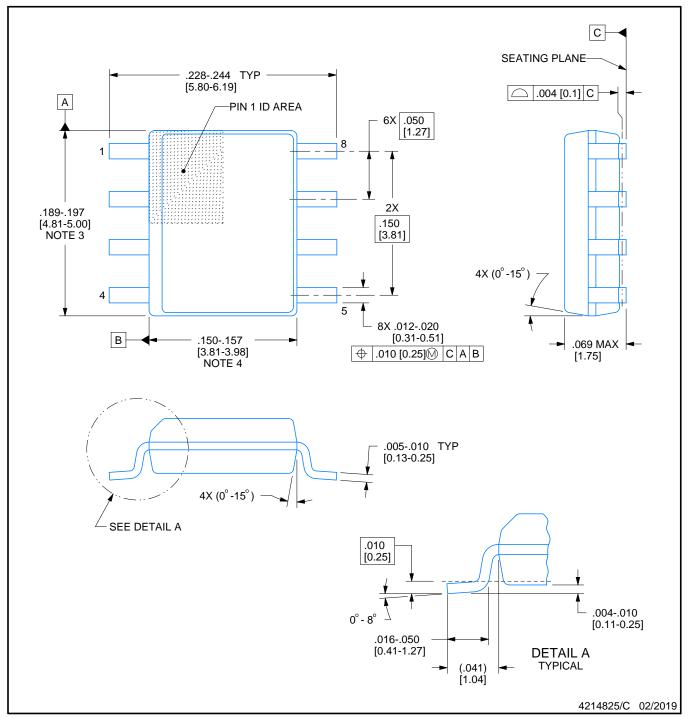

SMALL OUTLINE INTEGRATED CIRCUIT

# NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

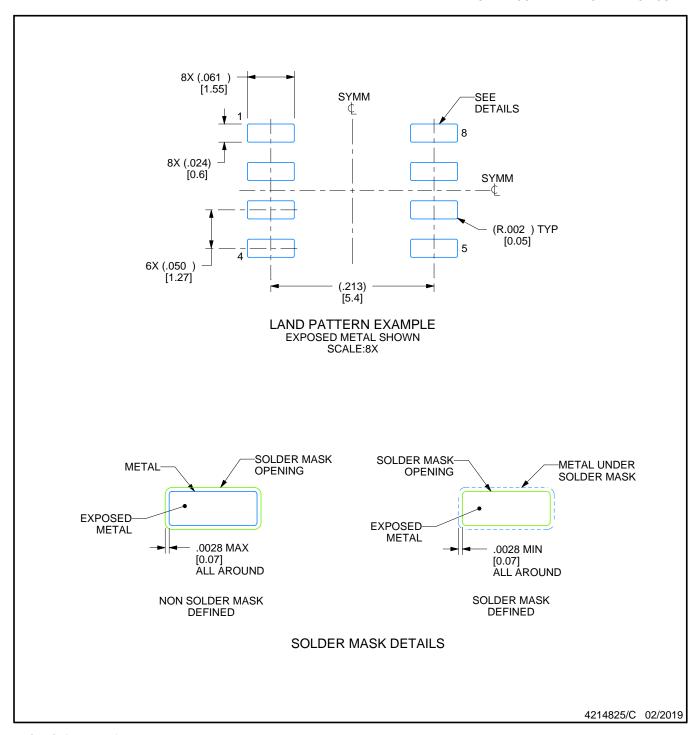

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

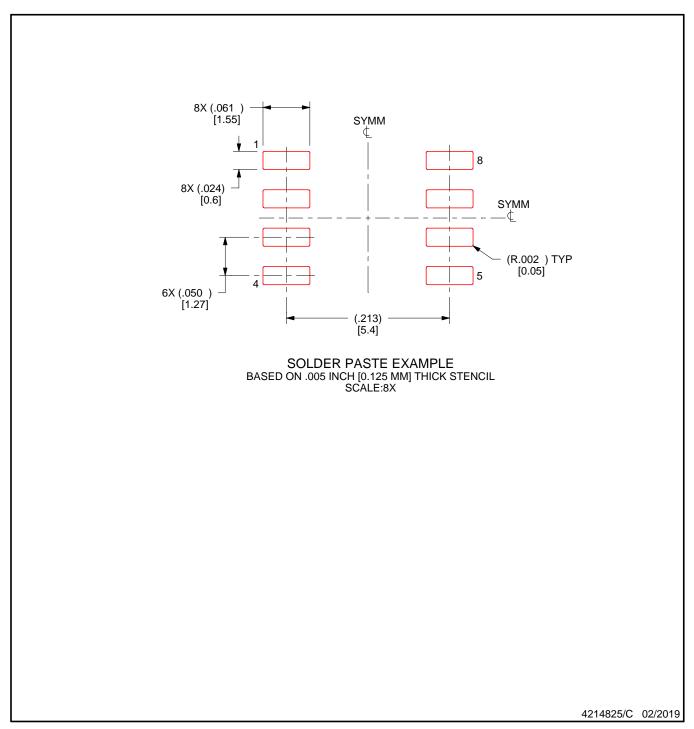

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated