###

### **Data Sheet**

#### **FEATURES**

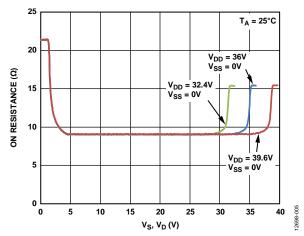

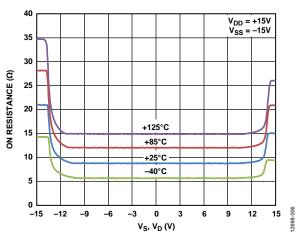

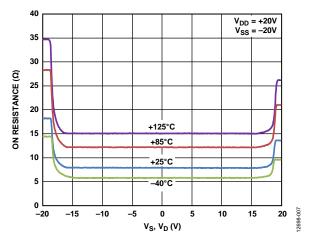

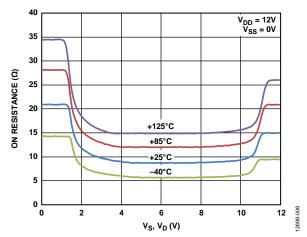

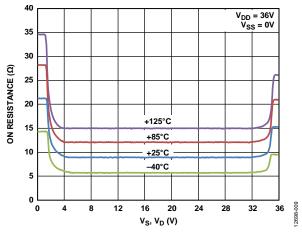

User defined secondary supplies set overvoltage level Overvoltage protection up to -55 V and +55 V Power-off protection up to -55 V and +55 V Overvoltage detection on source pins Minimum secondary supply level: 4.5 V single-supply Interrupt flag indicates fault status Low on resistance: 10 Ω typical On-resistance flatness: 0.5 Ω maximum 4 kV human body model (HBM) ESD rating Latch-up immune under any circumstance V<sub>SS</sub> to V<sub>DD</sub> analog signal range ±5 V to ±22 V dual supply operation 8 V to 44 V single-supply operation Fully specified at ±15 V, ±20 V, +12 V, and +36 V

#### APPLICATIONS

Analog input/output modules Process control/distributed control systems Data acquisition Instrumentation Avionics Automatic test equipment Communication systems

#### **GENERAL DESCRIPTION**

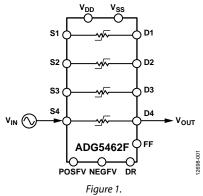

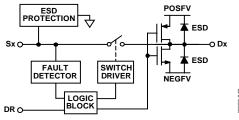

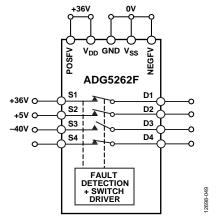

The ADG5462F contains four channels that are overvoltage protected. The channel protector is placed in series with the signal path and protects sensitive components from overvoltage faults in that path. The channel protector prevents overvoltages when powered and unpowered, and it is ideal for use in applications where correct power supply sequencing cannot always be guaranteed. The primary supply voltages define the on-resistance profile, while the secondary supply voltages define the voltage level at which the overvoltage protection engages.

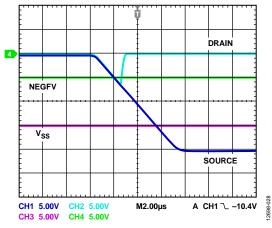

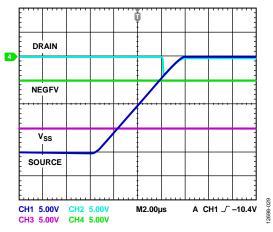

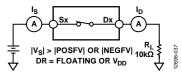

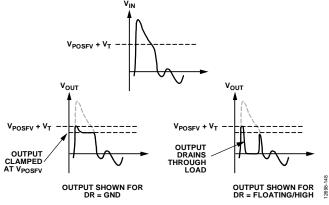

When no power supplies are present, the channel remains in the off condition, and the channel inputs are high impedance. Under normal operating conditions, if the analog input signal levels on any Sx pin exceed positive fault voltage (POSFV) or negative fault voltage (NEGFV) by a threshold voltage ( $V_T$ ), the channel turns off and that Sx pin becomes high impedance. If the DR pin is driven low, the drain pin (Dx) is pulled to the secondary supply voltage that was exceeded. The output profile for each DR voltage level is shown in Figure 49. Input signal levels up to -55 V or +55 V relative to ground are blocked in both the powered and unpowered conditions.

#### Rev. C

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# ADG5462F

#### FUNCTIONAL BLOCK DIAGRAM

The low on-resistance of these switches, combined with the on-resistance flatness over a significant portion of the signal range make them an ideal solution for data acquisition and instrumentation applications where excellent linearity and low distortion are critical.

#### **PRODUCT HIGHLIGHTS**

- Source pins (Sx) are protected against voltages greater than the secondary supply rails (POSFV and NEGFV), up to -55 V and +55 V.

- 2. In an unpowered state, source pins (Sx) are protected against voltages from -55 V to +55 V.

- 3. Overvoltage detection with digital output indicates the operating state of the channels.

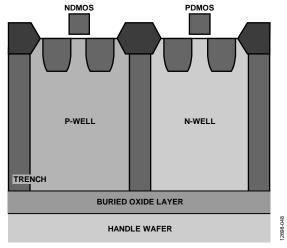

- 4. Trench isolation guards against latch-up.

- 5. Optimized for low on-resistance and on-resistance flatness.

- 6. The ADG5462F operates from a dual power supply range of ±5 V to ±22 V or a single power supply range of 8 V to 44 V.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2015-2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                     | 1    |

|----------------------------------------------|------|

| Applications                                 | 1    |

| Functional Block Diagram                     | 1    |

| General Description                          | 1    |

| Product Highlights                           | 1    |

| Revision History                             | 2    |

| Specifications                               | 3    |

| ±15 V Dual Supply                            | 3    |

| ±20 V Dual Supply                            | 5    |

| 12 V Single Supply                           | 7    |

| 36 V Single Supply                           | 9    |

| Continuous Current per Channel, Sx or Dx     | . 10 |

| Absolute Maximum Ratings                     | .11  |

| ESD Caution                                  | . 11 |

| Pin Configurations and Function Descriptions | . 12 |

| Typical Performance Characteristics          | . 13 |

### **REVISION HISTORY**

#### 10/2017-Rev. B to Rev. C

| Changes to Fault Drain Leakage Current With Overvoltage |      |

|---------------------------------------------------------|------|

| Parameter, Table 1                                      | 3    |

| Changes to Fault Drain Leakage Current With Overvoltage |      |

| Parameter, Table 2                                      | 7    |

| Changes to Fault Drain Leakage Current With Overvoltage |      |

| Parameter, Table 4                                      | 9    |

| Updated Outline Dimensions                              | . 29 |

| Changes to Ordering Guide                               | . 29 |

#### 1/2016—Rev. A to Rev. B

| Changes to General Description Section                  | . 1 |

|---------------------------------------------------------|-----|

| Changes to Table 1                                      | . 3 |

| Changes to Channel On Leakage, ID (On), IS (On) Maximum |     |

| Parameter, Table 2                                      | . 5 |

| Changes to Table 3                                      | .7  |

| Changes to Table 4                                      | . 9 |

| Test Circuits                         | . 19 |

|---------------------------------------|------|

| Terminology                           | . 23 |

| Theory of Operation                   | . 24 |

| Switch Architecture                   | . 24 |

| User Defined Fault Protection         | . 25 |

| Applications Information              | . 27 |

| Power Supply Rails                    | . 27 |

| Power Supply Sequencing Protection    | . 27 |

| Power Supply Recommendations          | . 27 |

| User Defined Signal Range             | . 27 |

| Low Impedance Channel Protection      | . 27 |

| High Voltage Surge Suppression        | . 27 |

| Intelligent Fault Detection           | . 28 |

| Large Voltage, High Frequency Signals | . 28 |

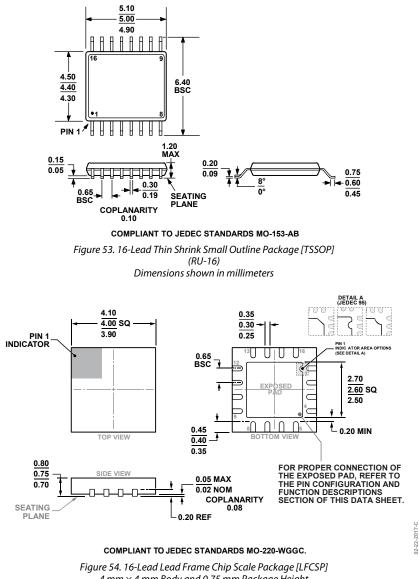

| Outline Dimensions                    | . 29 |

| Ordering Guide                        | . 29 |

#### 5/2015—Rev. 0 to Rev. A

| Added 16-Lead LFCSP Package Universal                  |

|--------------------------------------------------------|

| Changes to Drain Leakage Current, ID, with Overvoltage |

| Parameter Test Condition/Comment, Table 37             |

| Changes to Drain Leakage Current, ID, with Overvoltage |

| Parameter Test Condition/Comment, Table 49             |

| Changes to Table 5 10                                  |

| Changes to Table 6 11                                  |

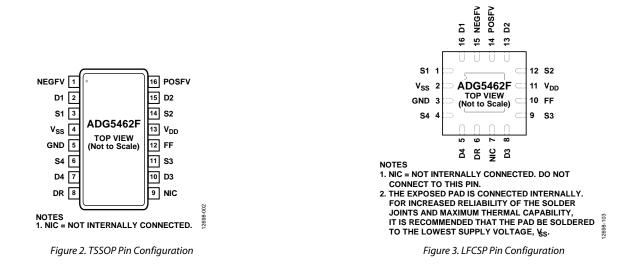

| Added Figure 3; Renumbered Sequentially 12             |

| Changes to Table 7 12                                  |

| Added Figure 54 29                                     |

| Updated Outline Dimensions                             |

| Changes to Ordering Guide 29                           |

|                                                        |

1/2015—Revision 0: Initial Version

## **SPECIFICATIONS**

### ±15 V DUAL SUPPLY

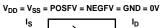

$V_{\text{DD}}$  = 15 V  $\pm$  10%,  $V_{\text{SS}}$  = –15 V  $\pm$  10%, GND = 0 V,  $C_{\text{DECOUPLING}}$  = 0.1  $\mu\text{F},$  unless otherwise noted.

#### Table 1.

| Parameter                                                    | +25°C | -40°C to<br>+85°C | -40°C to<br>+125°C                 | Unit   | Test Conditions/Comments                                                                                                              |

|--------------------------------------------------------------|-------|-------------------|------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

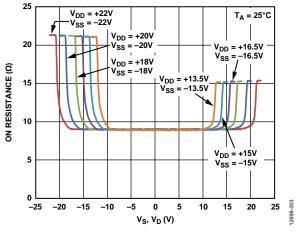

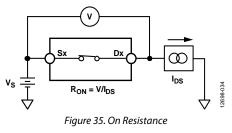

| ANALOG SWITCH                                                |       |                   |                                    |        | $V_{DD} = +13.5 V$ , $V_{SS} = -13.5 V$ , see Figure 35                                                                               |

| Analog Signal Range                                          |       |                   | V <sub>DD</sub> to V <sub>SS</sub> | V      |                                                                                                                                       |

| On Resistance, R <sub>ON</sub>                               | 10    |                   |                                    | Ωtyp   | $V_s = \pm 10 V$ , $I_s = -10 mA$                                                                                                     |

|                                                              | 11.2  | 14                | 16.5                               | Ωmax   |                                                                                                                                       |

|                                                              | 9.5   |                   |                                    | Ωtyp   | $V_s = \pm 9 V$ , $I_s = -10 mA$                                                                                                      |

|                                                              | 10.7  | 13.5              | 16                                 | Ωmax   |                                                                                                                                       |

| On-Resistance Match Between Channels, $\Delta R_{ON}$        | 0.05  |                   |                                    | Ωtyp   | $V_s = \pm 10 V$ , $I_s = -10 mA$                                                                                                     |

|                                                              | 0.5   | 0.6               | 0.7                                | Ωmax   |                                                                                                                                       |

|                                                              | 0.05  |                   |                                    | Ωtyp   | $V_s = \pm 9 V$ , $I_s = -10 mA$                                                                                                      |

|                                                              | 0.35  | 0.5               | 0.5                                | Ωmax   |                                                                                                                                       |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                | 0.6   |                   |                                    | Ωtyp   | $V_{s} = \pm 10 V$ , $I_{s} = -10 mA$                                                                                                 |

|                                                              | 0.9   | 1.1               | 1.1                                | Ωmax   |                                                                                                                                       |

|                                                              | 0.1   |                   |                                    | Ωtyp   | $V_{s} = \pm 9 V$ , $I_{s} = -10 mA$                                                                                                  |

|                                                              | 0.4   | 0.5               | 0.5                                | Ωmax   |                                                                                                                                       |

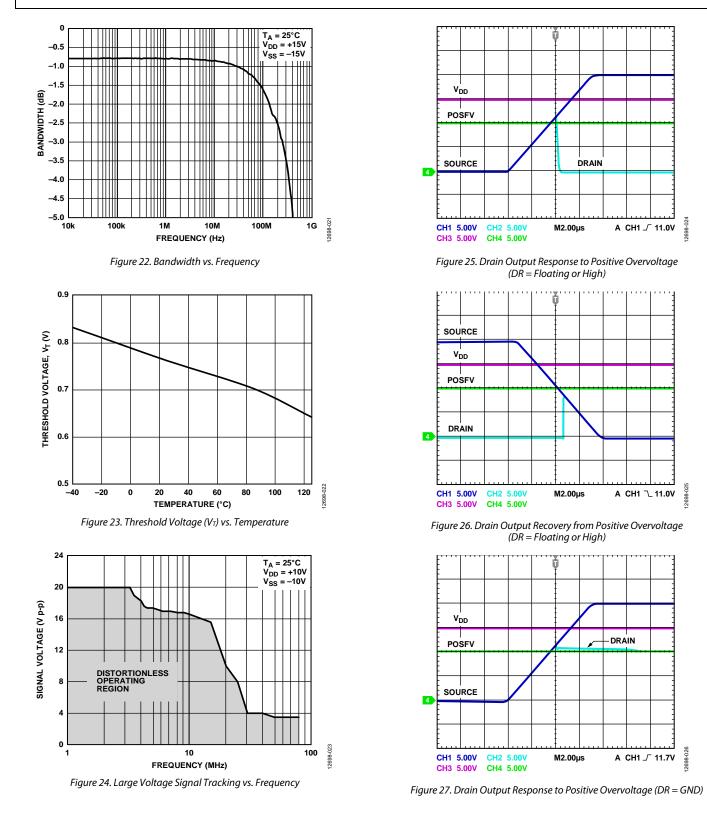

| Threshold Voltage, V⊤                                        | 0.7   |                   |                                    | V typ  | See Figure 23                                                                                                                         |

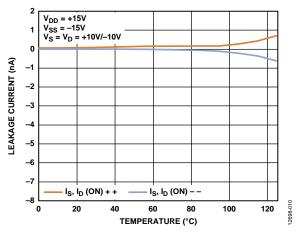

| LEAKAGE CURRENTS                                             |       |                   |                                    |        | $V_{DD} = +16.5 \text{ V}, \text{V}_{SS} = -16.5 \text{ V}$                                                                           |

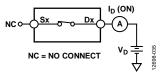

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On) | ±0.3  |                   |                                    | nA typ | $V_{s} = V_{D} = \pm 10 V$ , see Figure 36                                                                                            |

|                                                              | ±1.5  | ±2.0              | ±4.5                               | nA max |                                                                                                                                       |

| FAULT                                                        |       |                   |                                    |        |                                                                                                                                       |

| Source Leakage Current, Is                                   |       |                   |                                    |        |                                                                                                                                       |

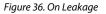

| With Overvoltage                                             |       |                   | ±78                                | μA typ | $V_{DD} = +16.5 V$ , $V_{SS} = -16.5 V$ , $GND = 0 V$ ,<br>$V_{S} = \pm 55 V$ , see Figure 37                                         |

| Power Supplies Grounded or Floating                          |       |                   | ±40                                | μA typ | $V_{DD} = 0 V$ or floating, $V_{SS} = 0 V$ or floating, GND = 0 V, V <sub>S</sub> = ±55 V, see Figure 38                              |

| Drain Leakage Current, I <sub>D</sub>                        |       |                   |                                    |        | $DR = floating or V_{DD}$                                                                                                             |

| With Overvoltage                                             | ±2.0  |                   |                                    | nA typ | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, \text{ GND} = 0 \text{ V},$<br>$V_{S} = \pm 55 \text{ V}, \text{ see Figure 37}$ |

|                                                              | ±20   | ±30               | ±65                                | nA max |                                                                                                                                       |

| Power Supplies Grounded                                      | ±10   |                   |                                    | nA typ | $V_{DD} = 0 V$ , $V_{SS} = 0 V$ , $GND = 0 V$ ,<br>$V_{S} = \pm 55 V$ , see Figure 38                                                 |

|                                                              | ±30   | ±50               | ±100                               | nA max |                                                                                                                                       |

| Power Supplies Floating                                      | ±10   | ±10               | ±10                                | μA typ | $V_{DD}$ = floating, $V_{SS}$ = floating, GND = 0 V,<br>$V_{S}$ = ±55 V, see Figure 38                                                |

| DIGITAL INPUTS/OUTPUTS (DR/FF)                               |       |                   |                                    |        |                                                                                                                                       |

| Input Voltage High, VINH                                     |       |                   | 2.0                                | V min  |                                                                                                                                       |

| Input Voltage Low, V <sub>INL</sub>                          |       |                   | 0.8                                | V max  |                                                                                                                                       |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>          | ±0.7  |                   |                                    | μA typ | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                                                                                 |

| -                                                            |       |                   | ±1.2                               | µA max |                                                                                                                                       |

| Digital Input Capacitance, C <sub>IN</sub>                   | 5.0   |                   |                                    | pF typ |                                                                                                                                       |

| Output Voltage High, V <sub>OH</sub>                         | 2.0   |                   |                                    | Vmin   |                                                                                                                                       |

| Output Voltage Low, Vol                                      | 0.8   |                   |                                    | V max  |                                                                                                                                       |

| Parameter                                                                         | +25°C  | -40°C to<br>+85°C | -40°C to<br>+125°C | Unit    | Test Conditions/Comments                                                                      |

|-----------------------------------------------------------------------------------|--------|-------------------|--------------------|---------|-----------------------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>                                              |        |                   |                    |         |                                                                                               |

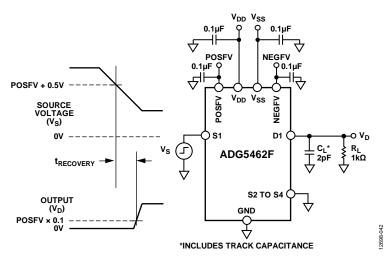

| Overvoltage Response Time, tresponse                                              | 460    |                   |                    | ns typ  | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 42                              |

| <u> </u>                                                                          | 585    | 615               | 630                | ns max  |                                                                                               |

| Overvoltage Recovery Time, trecovery                                              | 720    |                   |                    | ns typ  | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 43                              |

|                                                                                   | 930    | 1050              | 1100               | ns max  |                                                                                               |

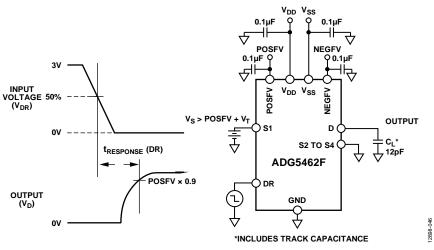

| Drain Pull-Up/Pull-Down Time Following<br>Overvoltage, t <sub>RESPONSE</sub> (DR) | 4      |                   |                    | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 47                                                         |

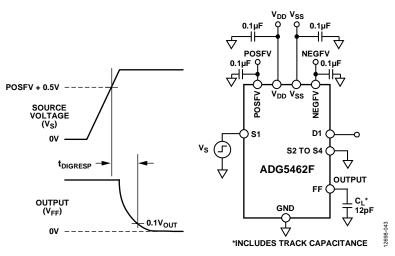

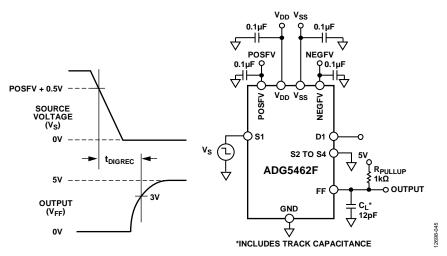

| Interrupt Flag Response Time, t <sub>DIGRESP</sub>                                | 85     |                   | 115                | ns typ  | $C_L = 12 \text{ pF}$ , see Figure 44                                                         |

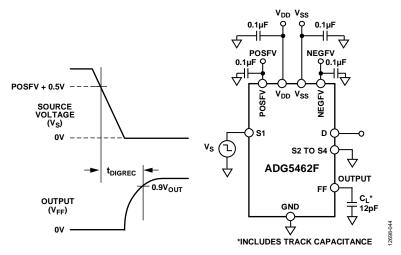

| Interrupt Flag Recovery Time, tDIGREC                                             | 60     |                   | 85                 | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 45                                                         |

|                                                                                   | 600    |                   |                    | ns typ  | $C_L = 12 \text{ pF}, R_{PULLUP} = 1 \text{ k}\Omega$ , see Figure 46                         |

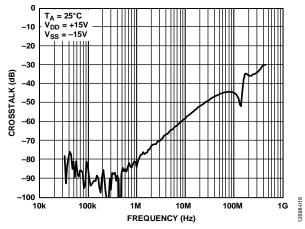

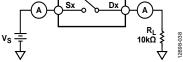

| Channel-to-Channel Crosstalk                                                      | -90    |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 39                                |

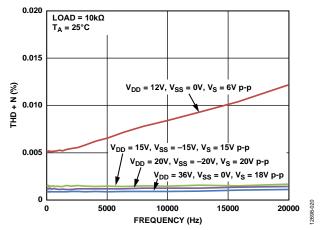

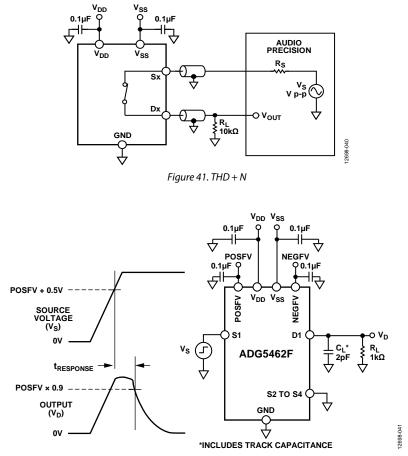

| Total Harmonic Distortion Plus Noise, THD + N                                     | 0.0015 |                   |                    | % typ   | $R_L = 10 \text{ k}\Omega$ , $V_S = 15 \text{ V p-p}$ ,<br>f = 20 Hz to 20 kHz, see Figure 41 |

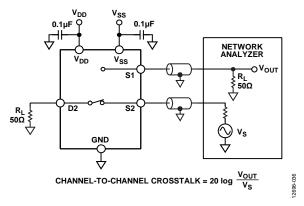

| –3 dB Bandwidth                                                                   | 318    |                   |                    | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 40                                              |

| Insertion Loss                                                                    | -0.8   |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 40                                |

| C <sub>D</sub> (On), C <sub>s</sub> (On)                                          | 24     |                   |                    | pF typ  | $V_{s} = 0 V, f = 1 MHz$                                                                      |

| POWER REQUIREMENTS                                                                |        |                   |                    |         | $V_{DD} = POSFV = +16.5 V$ , $V_{SS} = NEGFV = -16.5 V$<br>GND = 0 V                          |

| Normal Mode                                                                       |        |                   |                    |         |                                                                                               |

| ldd                                                                               | 0.9    |                   |                    | mA typ  |                                                                                               |

| POSFV                                                                             | 0.1    |                   |                    | mA typ  |                                                                                               |

| I <sub>DD</sub> + I <sub>POSFV</sub>                                              | 1.2    |                   | 1.3                | mA max  |                                                                                               |

| Ignd                                                                              | 0.4    |                   |                    | mA typ  |                                                                                               |

|                                                                                   | 0.55   |                   | 0.6                | mA max  |                                                                                               |

| lss                                                                               | 0.5    |                   |                    | mA typ  |                                                                                               |

| I <sub>NEGFV</sub>                                                                | 0.1    |                   |                    | mA typ  |                                                                                               |

| Iss + I <sub>NEGFV</sub>                                                          | 0.65   |                   | 0.7                | mA max  |                                                                                               |

| Fault Mode                                                                        |        |                   |                    |         | $V_S = \pm 55 V$                                                                              |

| l <sub>DD</sub>                                                                   | 1.2    |                   |                    | mA typ  |                                                                                               |

| IPOSFV                                                                            | 0.1    |                   |                    | mA typ  |                                                                                               |

| IDD + IPOSEV                                                                      | 1.6    |                   | 1.8                | mA max  |                                                                                               |

| I <sub>GND</sub>                                                                  | 0.8    |                   |                    | mA typ  |                                                                                               |

|                                                                                   | 1.0    |                   | 1.1                | mA max  |                                                                                               |

| I <sub>ss</sub>                                                                   | 0.5    |                   |                    | mA typ  |                                                                                               |

| INEGEV                                                                            | 0.1    |                   |                    | mA typ  |                                                                                               |

| Iss + Inegfv                                                                      | 1.0    |                   | 1.8                | mA max  |                                                                                               |

| V <sub>DD</sub> /V <sub>ss</sub>                                                  |        |                   | ±5                 | V min   | GND = 0 V                                                                                     |

|                                                                                   |        |                   | ±22                | V max   | GND = 0V                                                                                      |

<sup>1</sup> Guaranteed by design; not subject to production test.

### ±20 V DUAL SUPPLY

$V_{\text{DD}}$  = 20 V  $\pm$  10%,  $V_{\text{SS}}$  = -20 V  $\pm$  10%, GND = 0 V,  $C_{\text{DECOUPLING}}$  = 0.1  $\mu\text{F}$  unless otherwise noted.

### Table 2.

| Parameter                                             | +25°C        | -40°C to<br>+85°C | -40°C to<br>+125°C                 | Unit          | Test Conditions/Comments                                                                                   |

|-------------------------------------------------------|--------------|-------------------|------------------------------------|---------------|------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |              |                   |                                    | •             | $V_{DD} = +18 \text{ V}, \text{ V}_{SS} = -18 \text{ V}, \text{ see Figure 35}$                            |

| Analog Signal Range                                   |              |                   | V <sub>DD</sub> to V <sub>SS</sub> | v             | ······································                                                                     |

| On Resistance, R <sub>on</sub>                        | 10           |                   |                                    | Ωtyp          | $V_s = \pm 15 V$ , $I_s = -10 mA$                                                                          |

|                                                       | 11.5         | 14.5              | 16.5                               | $\Omega$ max  |                                                                                                            |

|                                                       | 9.5          |                   |                                    | Ωtyp          | $V_s = \pm 13.5 V$ , $I_s = -10 mA$                                                                        |

|                                                       | 11           | 14                | 16.5                               | $\Omega$ max  | 5, 5 .                                                                                                     |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 0.05         |                   |                                    | Ωtyp          | $V_{s} = \pm 15 V, I_{s} = -10 mA$                                                                         |

| ,,,,,,, _                                             | 0.35         | 0.5               | 0.5                                | $\Omega \max$ |                                                                                                            |

|                                                       | 0.05         |                   |                                    | Ωtyp          | $V_s = \pm 13.5 V$ , $I_s = -10 mA$                                                                        |

|                                                       | 0.35         | 0.5               | 0.5                                | $\Omega \max$ |                                                                                                            |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>         | 1.0          | 0.0               | 0.0                                | Ωtyp          | $V_{s} = \pm 15 V, I_{s} = -10 mA$                                                                         |

|                                                       | 1.4          | 1.5               | 1.5                                | $\Omega \max$ |                                                                                                            |

|                                                       | 0.1          | 1.5               | 1.5                                | Ωtyp          | $V_s = \pm 13.5 V$ , $I_s = -10 mA$                                                                        |

|                                                       | 0.4          | 0.5               | 0.5                                | Ωmax          |                                                                                                            |

| Threshold Voltage, V₁                                 | 0.7          | 0.5               | 0.5                                | V typ         | See Figure 23                                                                                              |

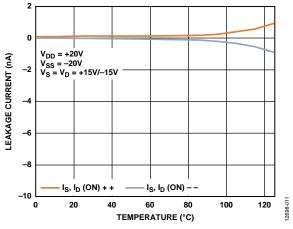

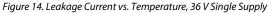

| LEAKAGE CURRENTS                                      | 0.7          |                   |                                    | Vtyp          | $V_{DD} = +22 V, V_{SS} = -22 V$                                                                           |

| Channel On Leakage, $I_D$ (On), $I_s$ (On)            | ±0.3         |                   |                                    | nA typ        | $V_{\rm DD} = \pm 22$ V, $V_{\rm SS} = \pm 22$ V<br>V <sub>S</sub> = V <sub>D</sub> = ±15 V, see Figure 36 |

| Charmer on Leakage, in (Oh), is (Oh)                  | ±0.5<br>±1.5 | ±2.0              | ±4.5                               | nA max        | v <sub>5</sub> = v <sub>0</sub> = ±15 v, see Figure 50                                                     |

| FAULT                                                 | 1.5          | ±2.0              | <u>1</u> 4.J                       | пл шах        |                                                                                                            |

| Source Leakage Current, Is                            |              |                   |                                    |               |                                                                                                            |

| With Overvoltage                                      |              |                   | ±78                                | μA typ        | $V_{DD} = +22 V$ , $V_{SS} = -22 V$ , $GND = 0 V$ ,<br>$V_{S} = \pm 55 V$ , see Figure 37                  |

| Power Supplies Grounded or Floating                   |              |                   | ±40                                | μA typ        | $V_{DD} = 0$ V or floating, $V_{SS} = 0$ V or<br>floating, GND = 0 V, $V_S = \pm 55$ V,<br>see Figure 38   |

| Drain Leakage Current, I <sub>D</sub>                 |              |                   |                                    |               | $DR = floating or V_{DD}$                                                                                  |

| With Overvoltage                                      | ±5.0         |                   |                                    | nA typ        | $V_{DD} = +22 V, V_{ss} = -22 V, GND = 0 V,$<br>$V_s = \pm 55 V,$ see Figure 37                            |

|                                                       | ±1.0         | ±1.0              | ±1.0                               | µA max        |                                                                                                            |

| Power Supplies Grounded                               | ±10          |                   |                                    | nA typ        | $V_{DD} = 0 V$ , $V_{SS} = 0 V$ , $GND = 0 V$ ,<br>$V_{S} = \pm 55 V$ , see Figure 38                      |

|                                                       | ±30          | ±50               | ±100                               | nA max        | -                                                                                                          |

| Power Supplies Floating                               | ±10          | ±10               | ±10                                | μA typ        | $V_{DD} =$ floating, $V_{SS} =$ floating, GND = 0 V,<br>$V_{S} = \pm 55$ V, see Figure 38                  |

| DIGITAL INPUTS/OUTPUTS                                |              |                   |                                    |               |                                                                                                            |

| Input Voltage High, V <sub>INH</sub>                  |              |                   | 2.0                                | V min         |                                                                                                            |

| Input Voltage Low, V <sub>INL</sub>                   |              |                   | 0.8                                | V max         |                                                                                                            |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>   | 0.7          |                   |                                    | μA typ        | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                                                      |

|                                                       |              |                   | 1.2                                | µA max        |                                                                                                            |

| Digital Input Capacitance, C <sub>IN</sub>            | 5.0          |                   |                                    | pF typ        |                                                                                                            |

| Output Voltage High, Voн                              | 2.0          |                   |                                    | Vmin          |                                                                                                            |

| Output Voltage Low, Vol                               | 0.8          |                   |                                    | V max         |                                                                                                            |

| Parameter                                                                         | +25°C | -40°C to<br>+85°C | -40°C to<br>+125°C | Unit    | Test Conditions/Comments                                                                      |

|-----------------------------------------------------------------------------------|-------|-------------------|--------------------|---------|-----------------------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>                                              | 125 C | 105 C             | 1125 C             |         |                                                                                               |

| Overvoltage Response Time, tresponse                                              | 370   |                   |                    | ns typ  | $R_L = 1 k\Omega$ , $C_L = 2 pF$ , see Figure 42                                              |

|                                                                                   | 480   | 500               | 515                | ns max  |                                                                                               |

| Overvoltage Recovery Time, tRECOVERY                                              | 840   |                   |                    | ns typ  | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 43                              |

|                                                                                   | 1200  | 1400              | 1700               | ns max  | ······································                                                        |

| Drain Pull-Up/Pull-Down Time Following<br>Overvoltage, t <sub>RESPONSE</sub> (DR) | 4     |                   |                    | μs typ  | $C_L = 12 \text{ pF}$ , see Figure 47                                                         |

| Interrupt Flag Response Time, t <sub>DIGRESP</sub>                                | 85    |                   | 115                | ns typ  | $C_L = 12 \text{ pF}$ , see Figure 44                                                         |

| Interrupt Flag Recovery Time, tDIGREC                                             | 60    |                   | 85                 | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 45                                                         |

|                                                                                   | 600   |                   |                    | ns typ  | $C_L = 12 \text{ pF}, R_{PULLUP} = 1 \text{ k}\Omega$ , see Figure 46                         |

| Channel-to-Channel Crosstalk                                                      | -90   |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 39                                |

| Total Harmonic Distortion Plus Noise, THD + N                                     | 0.001 |                   |                    | % typ   | $R_L = 10 \text{ k}\Omega$ , $V_S = 20 \text{ V p-p}$ ,<br>f = 20 Hz to 20 kHz, see Figure 41 |

| –3 dB Bandwidth                                                                   | 310   |                   |                    | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 40                                              |

| Insertion Loss                                                                    | -0.8  |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 40                                |

| C <sub>D</sub> (On), C <sub>s</sub> (On)                                          | 23    |                   |                    | pF typ  | $V_{s} = 0 V, f = 1 MHz$                                                                      |

| POWER REQUIREMENTS                                                                |       |                   |                    |         | $V_{DD} = POSFV = +22 V, V_{SS} = NEGFV = -22 V$                                              |

| Normal Mode                                                                       |       |                   |                    |         |                                                                                               |

| lod                                                                               | 0.9   |                   |                    | mA typ  |                                                                                               |

| IPOSFV                                                                            | 0.1   |                   |                    | mA typ  |                                                                                               |

| IDD + IPOSFV                                                                      | 1.2   |                   | 1.3                | mA max  |                                                                                               |

| I <sub>GND</sub>                                                                  | 0.4   |                   |                    | mA typ  |                                                                                               |

|                                                                                   | 0.55  |                   | 0.6                | mA max  |                                                                                               |

| lss                                                                               | 0.5   |                   |                    | mA typ  |                                                                                               |

| INEGFV                                                                            | 0.1   |                   |                    | mA typ  |                                                                                               |

| Iss + Inegfv                                                                      | 0.65  |                   | 0.7                | mA max  |                                                                                               |

| Fault Mode                                                                        |       |                   |                    |         | $V_s = \pm 55 V$                                                                              |

| l <sub>DD</sub>                                                                   | 1.2   |                   |                    | mA typ  |                                                                                               |

| POSFV                                                                             | 0.1   |                   |                    | mA typ  |                                                                                               |

| IDD + IPOSFV                                                                      | 1.6   |                   | 1.8                | mA max  |                                                                                               |

| I <sub>GND</sub>                                                                  | 0.8   |                   |                    | mA typ  |                                                                                               |

|                                                                                   | 1.0   |                   | 1.1                | mA max  |                                                                                               |

| I <sub>SS</sub>                                                                   | 0.5   |                   |                    | mA typ  |                                                                                               |

| I <sub>NEGFV</sub>                                                                | 0.1   |                   |                    | mA typ  |                                                                                               |

| Iss + Inegfv                                                                      | 1.0   |                   | 1.8                | mA max  |                                                                                               |

| V <sub>DD</sub> /V <sub>SS</sub>                                                  |       |                   | ±5                 | V min   | GND = 0V                                                                                      |

|                                                                                   |       |                   | ±22                | V max   | GND = 0 V                                                                                     |

<sup>1</sup> Guaranteed by design; not subject to production test.

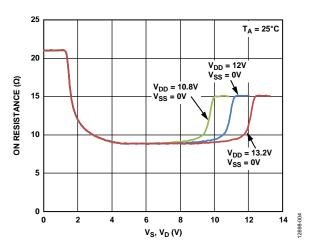

### **12 V SINGLE SUPPLY**

$V_{\text{DD}}$  = 12 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V, GND = 0 V,  $C_{\text{DECOUPLING}}$  = 0.1  $\mu\text{F}$  unless otherwise noted.

### Table 3.

| <b>-</b>                                              |              | -40°C to | -40°C to               |                  |                                                                                                                                  |

|-------------------------------------------------------|--------------|----------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                             | +25°C        | +85°C    | +125°C                 | Unit             | Test Conditions/Comments                                                                                                         |

| ANALOG SWITCH                                         |              |          |                        |                  | $V_{DD} = +10.8 V$ , $V_{SS} = 0 V$ , see Figure 35                                                                              |

| Analog Signal Range                                   | 22           |          | 0 V to V <sub>DD</sub> | V                |                                                                                                                                  |

| On Resistance, R <sub>ON</sub>                        | 22           | 21       | 27                     | Ω typ            | $V_{s} = 0 V to + 10 V$ , $I_{s} = -10 mA$                                                                                       |

|                                                       | 24.5         | 31       | 37                     | $\Omega$ max     |                                                                                                                                  |

|                                                       | 10           | 14       | 16.5                   | Ω typ            | $V_{s} = +3.5 V \text{ to } +8.5 V$ , $I_{s} = -10 \text{ mA}$                                                                   |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 11.2<br>0.05 | 14       | 16.5                   | Ω max<br>Ω typ   | $V = 0 V t_0 + 10 V L = -10 m A$                                                                                                 |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 0.05         | 0.6      | 0.7                    |                  | $V_{s} = 0 V to +10 V$ , $I_{s} = -10 mA$                                                                                        |

|                                                       | 0.5          | 0.6      | 0.7                    | $\Omega$ max     | $V = 125V t_{0} + 85V t_{1} = 10 m$                                                                                              |

|                                                       | 0.05         | 0.6      | 0.7                    | Ω typ<br>Ω max   | $V_{s} = +3.5 V \text{ to } +8.5 V, I_{s} = -10 \text{ mA}$                                                                      |

| On Pasistance Flatness B                              | 0.5<br>12.5  | 0.6      | 0.7                    |                  | $V = 0 V t_0 + 10 V L = -10 m A$                                                                                                 |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>         |              | 10       | 22                     | Ω typ            | $V_{s} = 0 V to +10 V$ , $I_{s} = -10 mA$                                                                                        |

|                                                       | 14.5<br>0.6  | 19       | 23                     | $\Omega$ max     | $V = 125V t_0 + 85V t_1 = 10 m A$                                                                                                |

|                                                       |              | 1 1      | 1 2                    | Ω typ            | $V_{s} = +3.5 V \text{ to } +8.5 V$ , $I_{s} = -10 \text{ mA}$                                                                   |

| Threshold Voltage, V <sub>T</sub>                     | 0.9<br>0.7   | 1.1      | 1.3                    | Ω max            | See Figure 23                                                                                                                    |

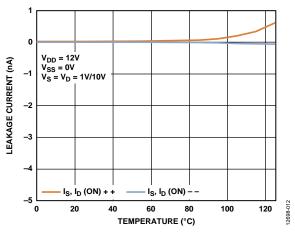

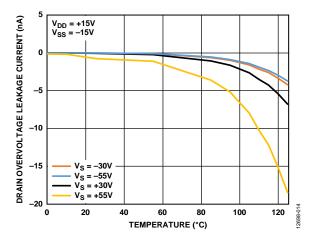

| LEAKAGE CURRENTS                                      | 0.7          |          |                        | V typ            |                                                                                                                                  |

| Channel On Leakage, $I_D$ (On), $I_S$ (On)            | ±0.3         |          |                        | n A turn         | $V_{DD} = +13.2 \text{ V}, V_{SS} = 0 \text{ V}$<br>$V_{S} = V_{D} = 1 \text{ V}/10 \text{ V}, \text{ see Figure 36}$            |

| Charmer Off Leakage, ib (Off), is (Off)               | ±0.5<br>±1.5 | ±2.0     | ±4.5                   | nA typ<br>nA max | $v_{\rm S} = v_{\rm D} = 1$ v/10 v, see Figure 30                                                                                |

| FAULT                                                 | ±1.5         | ±2.0     | ±4.5                   | na max           |                                                                                                                                  |

|                                                       |              |          |                        |                  |                                                                                                                                  |

| Source Leakage Current, Is                            |              |          | 170                    |                  |                                                                                                                                  |

| With Overvoltage                                      |              |          | ±78                    | μA typ           | $V_{DD} = +13.2 \text{ V}, V_{SS} = 0 \text{ V}, \text{GND} = 0 \text{ V},$<br>$V_{S} = \pm 55 \text{ V}, \text{ see Figure 37}$ |

| Power Supplies Grounded or Floating                   |              |          | ±40                    | μA typ           | $V_{DD} = 0 V$ or floating, $V_{SS} = 0 V$ or floating,                                                                          |

|                                                       |              |          |                        |                  | $GND = 0 V, V_s = \pm 55 V$ , see Figure 38                                                                                      |

| Drain Leakage Current, I <sub>D</sub>                 |              |          |                        |                  | $DR = floating \text{ or } V_{DD}$                                                                                               |

| With Overvoltage                                      | ±2.0         |          |                        | nA typ           | $V_{DD} = +13.2 \text{ V}, V_{SS} = 0 \text{ V}, \text{ GND} = 0 \text{ V}, V_S = \pm55 \text{ V},$<br>see Figure 37             |

|                                                       | ±20          | ±30      | ±65                    | nA max           |                                                                                                                                  |

| Power Supplies Grounded                               | ±10          |          |                        | nA typ           | $V_{DD} = 0 V, V_{SS} = 0 V, GND = 0 V,$<br>$V_{S} = \pm 55 V,$ see Figure 38                                                    |

|                                                       | ±30          | ±50      | ±100                   | nA max           | _                                                                                                                                |

| Power Supplies Floating                               | ±10          | ±10      | ±10                    | μA typ           | $V_{DD}$ = floating, $V_{SS}$ = floating,<br>GND = 0 V, $V_S$ = ±55 V, see Figure 38                                             |

| DIGITAL INPUTS/OUTPUTS                                | 1            |          |                        |                  |                                                                                                                                  |

| Input Voltage High, V <sub>INH</sub>                  |              |          | 2.0                    | V min            |                                                                                                                                  |

| Input Voltage Low, V <sub>INL</sub>                   |              |          | 0.8                    | V max            |                                                                                                                                  |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>   | 0.7          |          |                        | μA typ           | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                                                                            |

|                                                       |              |          | 1.2                    | µA max           |                                                                                                                                  |

| Digital Input Capacitance, C <sub>№</sub>             | 5.0          |          |                        | pF typ           |                                                                                                                                  |

| Output Voltage High, Vон                              | 2.0          |          |                        | Vmin             |                                                                                                                                  |

| Output Voltage Low, Vol                               | 0.8          |          |                        | V max            |                                                                                                                                  |

| Parameter                                                                         | +25°C | -40°C to<br>+85°C | -40°C to<br>+125°C | Unit    | Test Conditions/Comments                                                                  |

|-----------------------------------------------------------------------------------|-------|-------------------|--------------------|---------|-------------------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>                                              |       |                   |                    |         |                                                                                           |

| Overvoltage Response Time, tresponse                                              | 560   |                   |                    | ns typ  | $R_L = 1 k\Omega$ , $C_L = 2 pF$ , see Figure 42                                          |

|                                                                                   | 660   | 700               | 720                | ns max  |                                                                                           |

| Overvoltage Recovery Time, tRECOVERY                                              | 640   |                   |                    | ns typ  | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 43                          |

| <b>5</b> , <b>7</b> , <b>1</b>                                                    | 800   | 865               | 960                | ns max  |                                                                                           |

| Drain Pull-Up/Pull-Down Time Following<br>Overvoltage, t <sub>RESPONSE</sub> (DR) | 4     |                   |                    | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 47                                                     |

| Interrupt Flag Response Time, t <sub>DIGRESP</sub>                                | 85    |                   | 115                | ns typ  | $C_L = 12 \text{ pF}$ , see Figure 44                                                     |

| Interrupt Flag Recovery Time, t <sub>DIGREC</sub>                                 | 60    |                   | 85                 | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 45                                                     |

|                                                                                   | 600   |                   |                    | ns typ  | $C_L = 12 \text{ pF}, R_{PULLUP} = 1 \text{ k}\Omega$ , see Figure 46                     |

| Channel-to-Channel Crosstalk                                                      | -90   |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 39                            |

| Total Harmonic Distortion Plus Noise, THD + N                                     | 0.007 |                   |                    | % typ   | $R_L$ = 10 k $\Omega,$ $V_S$ = 6 V p-p, f = 20 Hz to 20 kHz, see Figure 41                |

| –3 dB Bandwidth                                                                   | 284   |                   |                    | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 40                                          |

| Insertion Loss                                                                    | -0.9  |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ , see Figure 40                            |

| C <sub>D</sub> (On), C <sub>s</sub> (On)                                          | 25    |                   |                    | pF typ  | $V_{s} = 6 V, f = 1 MHz$                                                                  |

| POWER REQUIREMENTS                                                                |       |                   |                    |         | $V_{DD} = +13.2 \text{ V}, V_{SS} = 0 \text{ V},$<br>digital inputs = 0 V, 5 V, or V_{DD} |

| Normal Mode                                                                       |       |                   |                    |         |                                                                                           |

| lod                                                                               | 0.9   |                   |                    | mA typ  |                                                                                           |

| IPOSFV                                                                            | 0.1   |                   |                    | mA typ  |                                                                                           |

| $I_{DD} + I_{POSFV}$                                                              | 1.2   |                   | 1.3                | mA max  |                                                                                           |

| Ignd                                                                              | 0.4   |                   |                    | mA typ  |                                                                                           |

|                                                                                   | 0.55  |                   | 0.6                | mA max  |                                                                                           |

| lss                                                                               | 0.5   |                   |                    | mA typ  |                                                                                           |

| I <sub>NEGFV</sub>                                                                | 0.1   |                   |                    | mA typ  |                                                                                           |

| Iss + I <sub>NEGFV</sub>                                                          | 0.65  |                   | 0.7                | mA max  |                                                                                           |

| Fault Mode                                                                        |       |                   |                    |         | $V_s = \pm 55 V$                                                                          |

| IDD                                                                               | 1.2   |                   |                    | mA typ  |                                                                                           |

| IPOSFV                                                                            | 0.1   |                   |                    | mA typ  |                                                                                           |

| IDD + IPOSFV                                                                      | 1.6   |                   | 1.8                | mA max  |                                                                                           |

| I <sub>GND</sub>                                                                  | 0.8   |                   |                    | mA typ  |                                                                                           |

|                                                                                   | 1.0   |                   | 1.1                | mA max  |                                                                                           |

| I <sub>ss</sub>                                                                   | 0.5   |                   |                    | mA typ  | Digital inputs = 5 V                                                                      |

| INEGEV                                                                            | 0.1   |                   |                    | mA typ  |                                                                                           |

| Iss + I <sub>NEGFV</sub>                                                          | 1.0   |                   | 1.8                | mA max  | $V_{S} = \pm 55 V, V_{D} = 0 V$                                                           |

| V <sub>DD</sub>                                                                   |       |                   | 8                  | V min   | GND = 0 V                                                                                 |

|                                                                                   |       |                   | 44                 | V max   | GND = 0V                                                                                  |

<sup>1</sup> Guaranteed by design; not subject to production test.

### **36 V SINGLE SUPPLY**

$V_{\text{DD}}$  = 36 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V, GND = 0 V,  $C_{\text{DECOUPLING}}$  = 0.1  $\mu\text{F}$  unless otherwise noted.

### Table 4.

| Parameter                                             | +25°C | -40°C to<br>+85°C | -40°C to<br>+125°C     | Unit          | Test Conditions/Comments                                                                                                      |

|-------------------------------------------------------|-------|-------------------|------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                         |       |                   |                        | •             | $V_{DD} = +32.4 \text{ V}, V_{SS} = 0 \text{ V}, \text{ see Figure 35}$                                                       |

| Analog Signal Range                                   |       |                   | 0 V to V <sub>DD</sub> | v             | 1921 197 1921 197 193                                                                                                         |

| On Resistance, R <sub>ON</sub>                        | 22    |                   | ••••••                 | Ω typ         | $V_s = 0 V \text{ to } +30 V$ , $I_s = -10 \text{ mA}$                                                                        |

|                                                       | 24.5  | 31                | 37                     | $\Omega \max$ |                                                                                                                               |

|                                                       | 10    | 51                | 57                     | Ωtyp          | $V_s = +4.5 V \text{ to } +28 V$ , $I_s = -10 \text{ mA}$                                                                     |

|                                                       | 11    | 14                | 16.5                   | $\Omega \max$ |                                                                                                                               |

| On-Resistance Match Between Channels, $\Delta R_{ON}$ | 0.05  |                   | 10.5                   | Ωtyp          | $V_s = 0 V to +30 V$ , $I_s = -10 mA$                                                                                         |

| on resistance match between channels, anon            | 0.5   | 0.6               | 0.7                    | $\Omega \max$ | v5=0v to 150 v, i5= 10 m/t                                                                                                    |

|                                                       | 0.05  | 0.0               | 0.7                    | Ωtyp          | $V_s = +4.5 V \text{ to } +28 V$ , $I_s = -10 \text{ mA}$                                                                     |

|                                                       | 0.35  | 0.5               | 0.5                    | $\Omega \max$ |                                                                                                                               |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>         | 12.5  | 0.5               | 0.5                    | Ωtyp          | $V_s = 0 V to + 30 V$ , $I_s = -10 mA$                                                                                        |

| Off hesistance hatness, helai(ON)                     | 14.5  | 19                | 23                     | $\Omega \max$ |                                                                                                                               |

|                                                       | 0.1   | 15                | 25                     | Ωtyp          | $V_s = +4.5$ V to $+28$ V, $I_s = -10$ mA                                                                                     |

|                                                       | 0.1   | 0.5               | 0.5                    | $\Omega \max$ | $v_3 = 17.5$ v to $+20$ v, $v_5 = -10$ mA                                                                                     |

| Threshold Voltage, V <sub>T</sub>                     | 0.4   | 0.5               | 0.5                    | V typ         | See Figure 23                                                                                                                 |

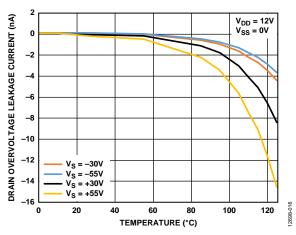

|                                                       | 0.7   |                   |                        | vtyp          | $V_{DD} = +39.6 V, V_{SS} = 0 V$                                                                                              |

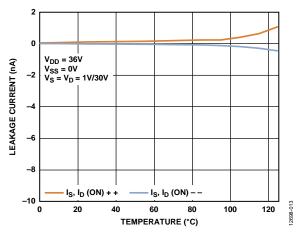

| Channel On Leakage, $I_D$ (On), $I_S$ (On)            | ±0.3  |                   |                        | nA typ        | $V_{DD} = +39.6 \text{ V}, \text{ V}_{SS} = 0 \text{ V}$<br>$V_{S} = V_{D} = 1 \text{ V}/30 \text{ V}, \text{ see Figure 36}$ |

| Channel On Leakage, ID (ON), IS (ON)                  |       | 120               | 1.4 E                  |               | $v_{\rm S} = v_{\rm D} = 1.0730$ v, see Figure 30                                                                             |

|                                                       | ±1.5  | ±2.0              | ±4.5                   | nA max        |                                                                                                                               |

| FAULT                                                 |       |                   |                        |               |                                                                                                                               |

| Source Leakage Current, Is                            |       |                   | . 70                   |               |                                                                                                                               |

| With Overvoltage                                      |       |                   | ±78                    | μA typ        | $V_{DD} = +39.6 V$ , $V_{SS} = 0 V$ , $GND = 0 V$ ,<br>$V_{S} = -40 V$ to $+55 V$ , see Figure 37                             |

| Power Supplies Grounded or Floating                   |       |                   | ±40                    | μA typ        | $V_{DD} = 0$ V or floating, $V_{SS} = 0$ V or<br>floating, GND = 0 V, $V_S = +55$ V, $-40$ V,<br>see Figure 38                |

| Drain Leakage Current, I <sub>D</sub>                 |       |                   |                        |               | $DR = floating or V_{DD}$                                                                                                     |

| With Overvoltage                                      | ±2.0  |                   |                        | nA typ        | $V_{DD} = +39.6 V$ , $V_{SS} = 0 V$ , $GND = 0 V$ ,<br>$V_{S} = -40 V$ to $+55 V$ , see Figure 37                             |

|                                                       | ±20   | ±30               | ±65                    | nA max        |                                                                                                                               |

| Power Supplies Grounded                               | ±10   |                   |                        | nA typ        | $V_{DD} = 0 V, V_{SS} = 0 V, GND = 0 V,$<br>$V_{S} = -40 V$ to +55 V, see Figure 38                                           |

|                                                       | ±30   | ±50               | ±100                   | nA max        |                                                                                                                               |

| Power Supplies Floating                               | ±10   | ±10               | ±10                    | μA typ        | $V_{DD}$ = floating, $V_{SS}$ = floating, GND = 0 V,<br>$V_{S}$ = -40 V to +55 V, see Figure 38                               |

| DIGITAL INPUTS/OUTPUTS                                |       |                   |                        |               |                                                                                                                               |

| Input Voltage High, V <sub>INH</sub>                  |       |                   | 2.0                    | V min         |                                                                                                                               |

| Input Voltage Low, V <sub>INL</sub>                   |       |                   | 0.8                    | V max         |                                                                                                                               |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>   | 0.7   |                   |                        | μA typ        | $V_{IN} = V_{GND} \text{ or } V_{DD}$                                                                                         |

| 1                                                     |       |                   | 1.2                    | μA max        |                                                                                                                               |

| Digital Input Capacitance, C <sub>IN</sub>            | 5.0   |                   |                        | pF typ        |                                                                                                                               |

| Output Voltage High, Voн                              | 2.0   |                   |                        | Vmin          |                                                                                                                               |

|                                                       |       | 1                 | 1                      | V max         |                                                                                                                               |

| Parameter                                          | +25°C | -40°C to<br>+85°C | -40°C to<br>+125°C | Unit    | Test Conditions/Comments                                              |

|----------------------------------------------------|-------|-------------------|--------------------|---------|-----------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>               | T23 C | +05 C             | T123 C             |         |                                                                       |

|                                                    | 250   |                   |                    | ns turn | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 42      |

| Overvoltage Response Time, tresponse               | 350   | 360               | 375                | ns typ  | $R_L = 1 \text{ K}_2, C_L = 2 \text{ pr, see Figure 42}$              |

| Quanualtaga Pasayany Tima t                        | 1500  | 500               | 5/5                | ns max  | $B = 1 k Q C = 2 m E \cos Eigure 42$                                  |

| Overvoltage Recovery Time, trecovery               | 2000  | 2300              | 2700               | ns typ  | $R_L = 1 \text{ k}\Omega$ , $C_L = 2 \text{ pF}$ , see Figure 43      |

| Drain Pull-Up/Pull-Down Time Following             | 2000  | 2500              | 2700               | ns max  | C∟ = 12 pF, see Figure 47                                             |

| Overvoltage, t <sub>RESPONSE</sub> (DR)            | 4     |                   |                    | µs typ  | CL = 12 pr, see Figure 47                                             |

| Interrupt Flag Response Time, t <sub>DIGRESP</sub> | 85    |                   | 115                | ns typ  | $C_L = 12 \text{ pF}$ , see Figure 44                                 |

| Interrupt Flag Recovery Time, t <sub>DIGREC</sub>  | 60    |                   | 85                 | µs typ  | $C_L = 12 \text{ pF}$ , see Figure 45                                 |

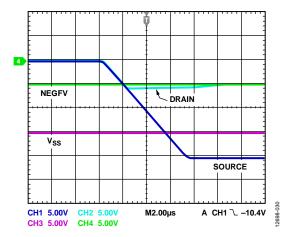

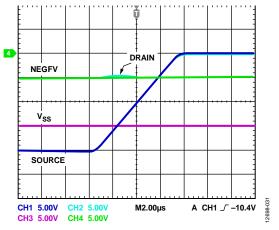

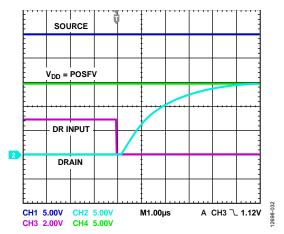

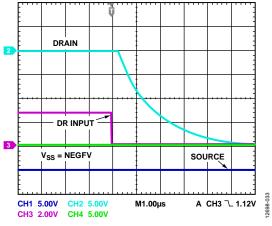

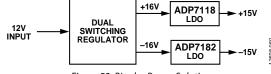

|                                                    | 600   |                   |                    | ns typ  | $C_L = 12 \text{ pF}, R_{PULLUP} = 1 \text{ k}\Omega$ , see Figure 46 |