# XIO1100

## Data Manual

Literature Number: SLLS690C April 2006 Revised August 2011

## **Contents**

| Se     | ction  |                                                                           | Page |  |  |  |  |  |  |

|--------|--------|---------------------------------------------------------------------------|------|--|--|--|--|--|--|

| 1      | XIO110 | D1100 Features                                                            |      |  |  |  |  |  |  |

| 2      | Descri | ption                                                                     |      |  |  |  |  |  |  |

|        | 2.1    | Ordering Information                                                      |      |  |  |  |  |  |  |

|        | 2.2    | Functional Description                                                    | 2    |  |  |  |  |  |  |

|        | 2.3    | Power Management                                                          | 2    |  |  |  |  |  |  |

|        |        | 2.3.1 P0                                                                  | (    |  |  |  |  |  |  |

|        |        | 2.3.2 P0s                                                                 | 3    |  |  |  |  |  |  |

|        |        | 2.3.3 P1                                                                  | 3    |  |  |  |  |  |  |

|        | 2.4    | Clock                                                                     | (    |  |  |  |  |  |  |

|        | 2.5    | Reset                                                                     | (    |  |  |  |  |  |  |

|        | 2.6    | Receiver Detection                                                        | 4    |  |  |  |  |  |  |

|        | 2.7    | Receiver Clock Tolerance Compensation                                     | 4    |  |  |  |  |  |  |

|        | 2.8    | Error Detection                                                           | 2    |  |  |  |  |  |  |

|        |        | 2.8.1 8B/10B Decode Error                                                 | ŗ    |  |  |  |  |  |  |

|        |        | 2.8.2 Elastic Buffer Overflow Error                                       | ŗ    |  |  |  |  |  |  |

|        |        | 2.8.3 Elastic Buffer Underflow Error                                      | ŗ    |  |  |  |  |  |  |

|        |        | 2.8.4 Disparity Error                                                     |      |  |  |  |  |  |  |

|        | 2.9    | Loopback                                                                  | ŗ    |  |  |  |  |  |  |

|        | 2.10   | Electrical Idle                                                           | ŗ    |  |  |  |  |  |  |

|        | 2.11   | Polarity Inversion                                                        | ŗ    |  |  |  |  |  |  |

|        | 2.12   | Setting Negative Parity                                                   | 5    |  |  |  |  |  |  |

|        | 2.13   | Terminal Assignments                                                      | 6    |  |  |  |  |  |  |

|        | 2.14   | Terminal Descriptions                                                     |      |  |  |  |  |  |  |

| 3      |        | cal Characteristics                                                       | 12   |  |  |  |  |  |  |

| •      | 3.1    | Absolute Maximum Ratings†                                                 | 12   |  |  |  |  |  |  |

|        | 3.2    | Recommended Operating Conditions                                          | 12   |  |  |  |  |  |  |

|        | 3.3    | PCI Express Differential Transmitter Output Ranges                        | 13   |  |  |  |  |  |  |

|        | 3.4    | PCI Express Differential Receiver Input Ranges                            | 15   |  |  |  |  |  |  |

|        | 3.5    | Express Differential Reference Clock Input Ranges                         | 18   |  |  |  |  |  |  |

|        | 3.6    | Electrical Characteristics Over Recommended Operating Conditions (VDD IO) | 19   |  |  |  |  |  |  |

|        | 3.7    | Implementation-Specific Timing                                            | 19   |  |  |  |  |  |  |

| 4      |        | Diagrams                                                                  | 20   |  |  |  |  |  |  |

| -<br>5 | _      | ation Information                                                         | 24   |  |  |  |  |  |  |

| •      | 5.1    | Component Connection                                                      | 24   |  |  |  |  |  |  |

|        | 5.2    | XIO1100 Component Placement                                               | 25   |  |  |  |  |  |  |

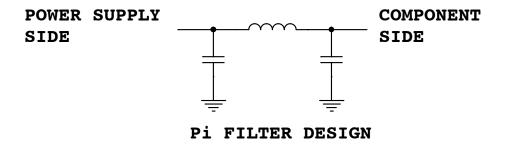

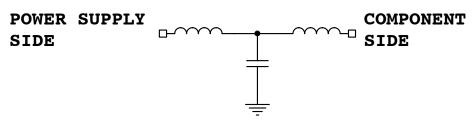

|        | 5.3    | Power Supply Filtering Recommendations                                    | 25   |  |  |  |  |  |  |

|        | 5.4    | PCIe Layout Guidelines                                                    | 27   |  |  |  |  |  |  |

|        | 5.5    | PIPE Interface Layout Guidelines                                          |      |  |  |  |  |  |  |

| 6      |        | nical Data                                                                | 28   |  |  |  |  |  |  |

# List of Figures

| Figure                                       | Page |

|----------------------------------------------|------|

| Figure 2–1. XIO1100 Functional Block Diagram | 2    |

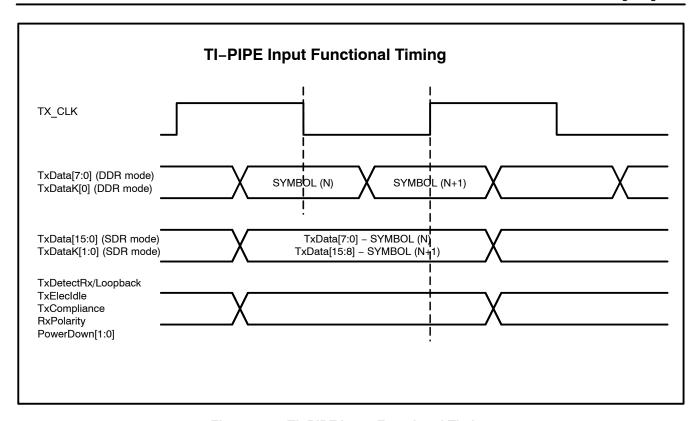

| Figure 4–1. TI–PIPE Input Timing             | 20   |

| Figure 4–2. TI–PIPE Data Output Timing       | 21   |

| Figure 4–3. TI–PIPE Output Functional Timing | 22   |

| Figure 4–4. TI–PIPE Input Functional Timing  | 23   |

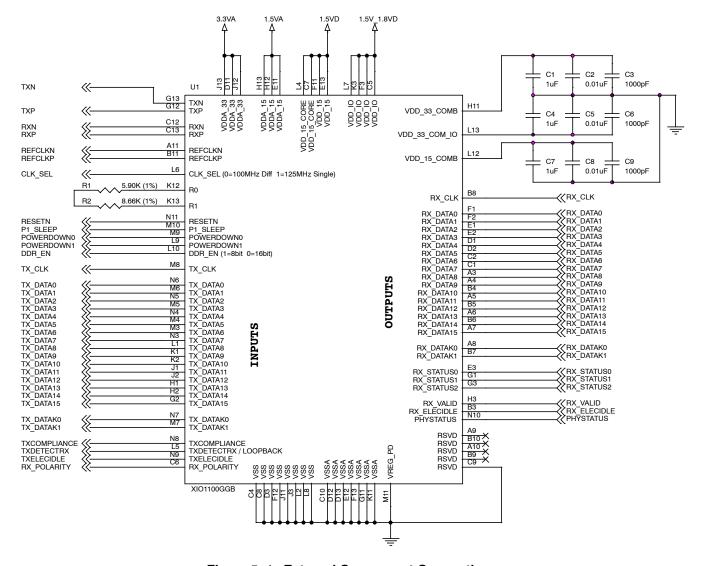

| Figure 5–1. External Component Connections   | 24   |

| Figure 5–2. Filter Designs                   | 26   |

## **List of Tables**

| Table      |                                                   | Page |

|------------|---------------------------------------------------|------|

| Table 2-1. | Clock Selection                                   | 3    |

| Table 2-2. | RX_STATUS Loopback Detection Code                 | 4    |

| Table 2-3. | 100-pin GGB Signal Name Sorted by Terminal Number | 6    |

| Table 2-4. | 100-pin GGB Signal Name Sorted Alphabetically     | 7    |

| Table 2-5  | XIO1100 Terminals                                 | 9    |

#### 1 XIO1100 Features

- X1 PCI Express™ Serial Link

- PCI Express 1.1 Compliant

- Selectable Reference Clock (100 MHz, 125 MHz)

- Low-Power Capability

- TI-PIPE MAC Interface

- Source-Synchronous TX and RX Ports

- 125 MHz TX/RX Clocks

- Selectable 16-Bit SDR or 8-Bit DDR Mode

- 100-Pin MicroStar™ BGA Package

- Selectable 1.5-V or 1.8-V LVCMOS Buffers.

TI and MicroStar BGA are trademarks of Texas Instruments Incorporated PCI Express is a trademark of PCI-SIG

## 2 Description

The XIO1100 is a PCI Express™ PHY that is compliant with *PCI Express Base Specification Revision 1.1* and that interfaces the PCI Express Media Access Layer (MAC) to a PCI Express serial link by using a modified version of the interface described in *PHY Interface for the PCI Express™ Architecture* (also known as PIPE interface) by Intel Corporation. This modified version of the PIPE interface is referred to as a TI-PIPE interface throughout this data manual.

The TI-PIPE interface is a pin-configurable interface that can be configured as either a 16-bit or an 8-bit interface.

- The 16-bit TI-PIPE interface is a 125 MHz 16-bit parallel interface with a 16-bit output bus (RXDATA) that

is clocked by the RXCLK output clock and a 16-bit input bus (TXDATA) that is clocked by the TXCLK input

clock. Both buses are clocked using Single Data Rate (SDR) clocking in which the data transitions are

on the rising edge of the associated clock.

- The 8-bit TI-PIPE interface is a 250 MHz 8-bit parallel interface with an 8-bit output bus (RXDATA) that

is clocked by the RXCLK output clock and an 8-bit input bus (TXDATA) that is clocked by the TXCLK input

clock. Both buses are clocked using Double Data Rate (DDR) clocking in which the data transitions are

on both the rising edge and the falling edge of the clock.

The XIO1100 PHY interfaces to a 2.5 Gbps PCI Express serial link with a transmit differential pair (TXP and TXN) and a receive differential pair (RXP and RXN). Incoming data at the XIO1100 PHY receive differential pair (RXP and RXN) is forwarded to the MAC on the RXDATA output bus. Data received from the MAC on the TXDATA input bus is forwarded to the XIO1100 PHY transfer differential pair (TXP and TXN).

The XIO1100 is also responsible for handling the 8B/10B encoding/decoding and scrambling/unscrambling of the outgoing data. In addition, XIO1100 can recover/interpolate the clock on the receiver side based on the transitions guaranteed by the use of the 8B/10B mechanism and supply this to the receive side of the data link layer logic.

In addition to the TI-PIPE interface, the XIO1100 has some TI-proprietary side-band signals that some customers may wish to use to take advantage of additional XIO1100 low-power state features (for example, disabling the PLL during the L1 power state).

## 2.1 Ordering Information

| ORDERING NUMBER | ORDERING NUMBER VOLTAGE |  | PACKAGE          |  |

|-----------------|-------------------------|--|------------------|--|

| XIO1100         | XIO1100 3.3/1.8/1.5     |  | 100-terminal GGB |  |

### 2.2 Functional Description

The XIO1100 meets all of the requirements for a PCI–Express PHY as defined by Section 4, Physical Layer Specifications, of the PCI–SIG document *PCI Express Base Specification*. The XIO1100 conforms to the functional behavior described in *PHY Interface for the PCI Express* ™ *Architecture* by Intel Corporation. There are only two differences between the XIO1100 TI–PIPE interface and the Intel PIPE interface.

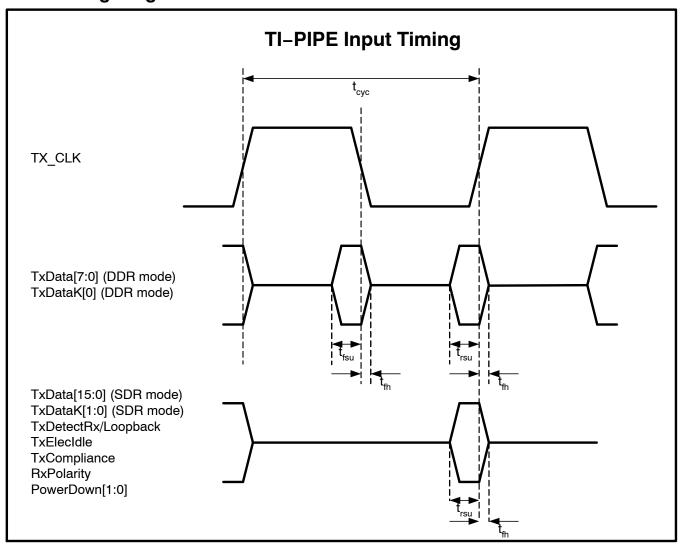

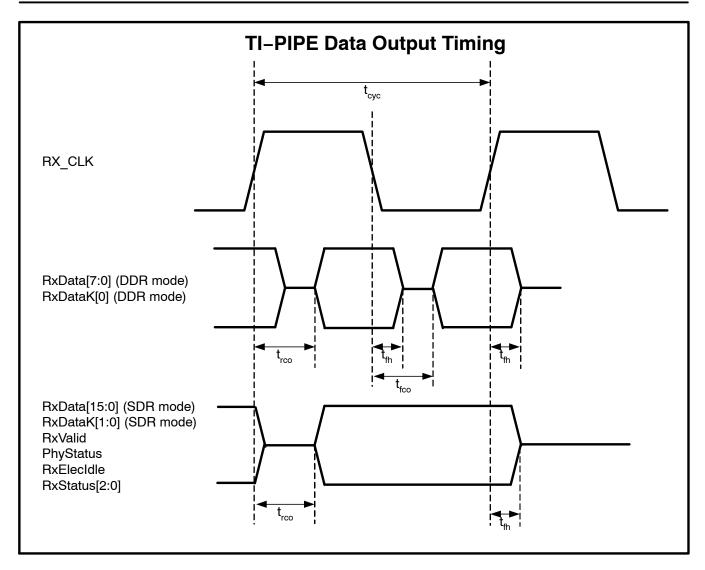

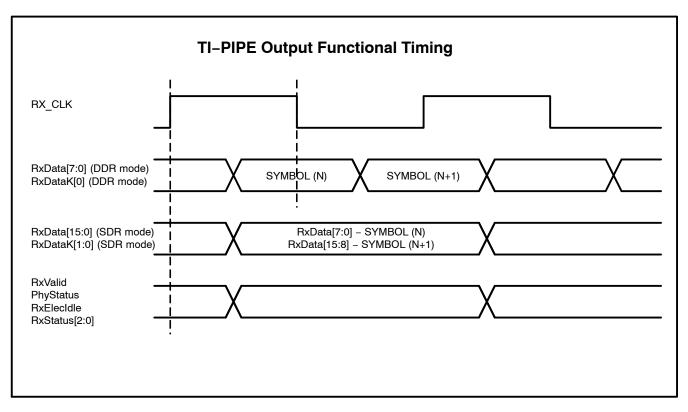

The PIPE interface uses a single SDR clock source to clock both the RXDATA and the TXDATA. The TI-PIPE interface uses two source synchronous clocks, RX\_CLK and TX\_CLK, to clock the RXDATA and TXDATA. RXDATA uses RX\_CLK and TXDATA uses TX\_CLK.

In the 8-bit mode, the TI-PIPE interface is a DDR (Double Data Rate) interface. In the 16-bit mode, it is an SDR (Single Data Rate) interface. The PIPE interface is always an SDR interface.

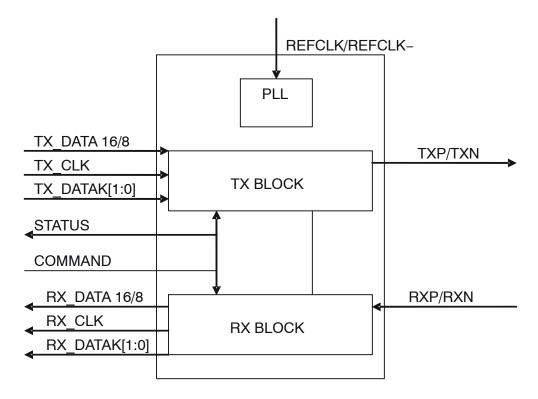

Figure 2-1 shows a functional block diagram of the XIO1100.

Figure 2-1. XIO1100 Functional Block Diagram

## 2.3 Power Management

The three power states are:

- P0

- P0s

- P1

#### 2.3.1 PO

P0 is the normal operation state for the XIO1100. The POWERDOWN[1:0] input signals define which of the three power states that an XIO110 is in at any given time. In states P0, P0s, and P1, the XIO1100 is required to keep P\_CLK operational. For all state transitions between these three states, the XIO1100 indicates successful transition into the designated power state by a single cycle assertion of PHY\_STATUS. For all power state transitions, the MAC must not begin any operational sequence or more power state transitions until the XIO1100 has indicated that the initial state transition is finished. P2 state and beacon are not supported.

In the P0 state, all internal clocks in the XIO1100 are operational. P0 is the only state where the XIO1100 transmits and receives PCI Express signaling. P0 is the appropriate PHY power management state for most states in the Link Training and Status State Machine (LTSSM). Exceptions are listed as follows for each lower power XIO1100 state.

#### 2.3.2 P0s

In the P0s state, RX\_CLK output stays operational. The MAC moves the XIO1100 to this state only when the transmit channel is idle. P0s state is used when the transmitter is in state Tx\_L0s.ldle. If the receiver detects an electrical idle while the XIO1100 is in either P0 or P0s power states, the receiver portion of the XIO1100 takes appropriate power saving measures.

#### 2.3.3 P1

In the P1 state, selected internal clocks in the XIO1100 will be turned off. RX\_CLK output will stay operational. The MAC moves the XIO1100 to this state only when both transmit and receive channels are idle. The XIO1100 does not indicate successful entry into P1 (by asserting PhyStatus) until RX\_CLK is stable and the operating dc common mode voltage is stable and within specification (in accordance with *PCI Express Base Specification*). P1 is used for the Disabled state, all Detect states, and L1.Idle state of the Link Training and Status State Machine (LTSSM). While in P1 state, the optional P1\_SLEEP input signal can be used to reduce even more power consumption by disabling the RX\_CLK signal. However, the P1\_SLEEP input must not be asserted when the XIO1100 is in any state other than P1 state, and the XIO1100 must not be transitioned out of the P1 state as long as P1\_SLEEP is asserted.

#### 2.4 Clock

The RX\_CLK of XIO1100 is derived from the REFCLK input. A 100 MHz differential clock or a 125 MHz single ended clock can be used as the source clock. The frequency selection is determined by CLK\_SEL. If CLK\_SEL is low during /RESET transitioning from a low state to a high state, the source clock at REFCLK+/REFCLK- is a 100 MHz differential clock. If CLK\_SEL is high during /RESET transitioning from a low state to a high state, the source clock at REFCLK+ is a 125 MHz single ended clock. In this case, REFCLK-needs to be tied to VSS.

Table 2-1. Clock Selection

|             | RX_CLK                     |

|-------------|----------------------------|

| CLK_SEL = 0 | 100 MHz differential clock |

| CLK_SEL = 1 | 125 MHz single ended clock |

#### 2.5 Reset

When the MAC resets the XIO1100 (initial power on), the MAC must hold the XIO1100 in reset until power and REFCLK to the XIO1100 are stable. The XIO1100 signals that RX\_CLK is valid (RX\_CLK has been running at its operational frequency for at least one clock), and the XIO1100 is in the specified power state by the de-assertion of PhyStatus. While Reset# is asserted, the MAC must have TxDetectRx/Loopback de-asserted, TxElecIdle asserted, TxCompliance de-asserted, RxPolarity de-asserted, and PowerDown = P1.

#### 2.6 Receiver Detection

While in the P1 power state, XIO1100 can be instructed to perform a receiver detection operation to determine if there is a receiver at the other end of the link. The MAC requests XIO1100 to do a receiver detect sequence by asserting TXDETECTRX/LOOPBACK high. Upon completion of the receiver detection operation, the XIO1100 asserts PHY\_STATUS high for one RX\_CLK cycle. While PHY\_STATUS is high, XIO1100 drives the proper receiver status code onto the RX\_STATUS[2:0] signals according to Table 2–2. After the receiver detection has completed (as signaled by the assertion of PhyStatus), the MAC must de-assert TxDetectRx/Loopback before initiating another receiver detection or a power state transition.

Table 2-2. RX STATUS Loopback Detection Code

| RX_STATUS[2:0] | RECEIVER STATUS      |

|----------------|----------------------|

| 000            | Receiver not present |

| 011            | Receiver present     |

NOTE: TX\_DET\_LOOPBACK must remain asserted until XIO1100 asserts the PHY\_STATUS.

## 2.7 Receiver Clock Tolerance Compensation

The XIO1100 receiver contains an elastic buffer that compensates for differences in frequencies between bit rates at the two ends of a link. The elastic buffer is capable of holding at least seven symbols to tolerate worst-case differences (600ppm) in frequency and worst-case intervals between SKP ordered-sets, where an SKP order-set is a set of symbols transmitted as a group. The first symbol of a SKP ordered-set is a COM (0xBC) and is followed by three SKP (0x1C) symbols. The purpose of SKP ordered-sets is to allow the receiving device (in this case, XIO1100) to adjust the data stream that is being received to prevent the elastic buffer from either overflowing or underflowing due to any differences between the clocking frequencies of the transmitting device and the receiving device. The XIO1100 monitors the data stream received at the RXP/RXN differential pair for SKP ordered-sets.

When the XIO1100 detects that an SKP ordered-set is being received, it either adds or removes SKP symbols from the data stream, depending on the current state of the elastic buffer. If the elastic buffer is in danger of underflowing, SKP symbols are added to the ordered-set before it is loaded into the buffer. If the elastic buffer is in danger of overflowing, SKP symbols are removed from the ordered-set before it is loaded into the buffer.

When the XIO1100 detects a SKP ordered-set, the XIO1100 asserts an Add SKP code (001b) on the RX\_STATUS[2:0] bus in the same RX\_CLK cycle that it asserts the COM (0xBC) symbol on the RX\_DATA[15:0] bus, if it is adding a SKP symbol to the data stream. In the case of removing an SKP symbol, the XIO1100 asserts the Remove SKP code (010b) to the RX\_STATUS[2:0] when the COM symbol is asserted.

#### 2.8 Error Detection

If a detectable receive error occurs, the appropriate error code is asserted on the RX\_STATUS[2:0] pins for one RX\_CLK cycle as close as possible to the point in the data stream where the error occurred. There are four error conditions that can be encoded on the RXSTATUS signals. If more than one error happens to occur on a received byte (or set of bytes transferred across a 16-bit interface), the errors are signaled with the following priority:

- 8B/10B decode error

- Elastic buffer overflow

- Elastic buffer underflow

- Disparity error

If an error occurs during a SKP ordered-set, such that the error code and the SKP code occur concurrently, the error code has priority over the SKP code.

#### 2.8.1 8B/10B Decode Error

When XIO1100 detects an 8B/10B decode error, it asserts an EDB (0xFE) symbol in the data on the RX\_DATA[15:0] where the bad byte occurred (only the erroneous byte is replaced with the EDB symbol; the other byte is still valid data). In the same RX\_CLK clock cycle that the EDB symbol is asserted on the RX\_DATA[15:0] bus, the 8B/10B decode error code (100b) is asserted on the RX\_STATUS[2:0] bus. Since the 8B/10B decoding error has priority over all other receive error codes, it could mask out a disparity error occurring on the other byte of data being clocked onto the RX\_DATA[15:0] with the EDB symbol.

#### 2.8.2 Elastic Buffer Overflow Error

When the elastic buffer overflows, data is lost during reception. XIO1100 generates an elastic buffer overflow error when this occurs. The elastic buffer overflow error code (101b) is asserted on the RX\_STATUS[2:0] on the RX\_CLK clock cycle that the omitted data would have been asserted. The remaining data asserted on the RX\_DATA[15:0]] bus is still valid data, but the elastic buffer overflow error code on the RX\_STATUS[2:0] just marks a discontinuity point in the data stream being received.

#### 2.8.3 Elastic Buffer Underflow Error

When the elastic buffer underflows, EDB (0xFE) symbols are inserted into the data stream on the RX\_DATA[15:0] bus to fill the holes created by the gaps between valid data. For every RX\_CLK clock cycle, an EDB symbol is asserted on the RX\_DATA[15:0] bus, and an elastic buffer underflow error code (111b) is asserted on the RX\_STATUS[2:0] bus.

### 2.8.4 Disparity Error

When the XIO1100 detects a disparity error, it asserts a disparity error code (111b) on the RX\_STATUS[2:0] bus in the same RX\_CLK clock cycle that it asserts the erroneous data on the RX\_DATA[15:0] bus. However, it is not possible to discern which byte had the disparity error.

### 2.9 Loopback

The XIO1100 begins a loopback operation when the MAC asserts TX\_DET\_LOOPBACK while holding TX\_ELECIDLE de-asserted. The XIO1100 stops transmitting data to the TXP/TXN signaling pair from the TI-PIPE interface and begins transmitting the data received at the RXP/RXN signaling pair on the TXP/TXN signaling pair. This data is not routed through the 8B/10B coding/encoding paths. While in the loopback operation, the received data is still sent to the RXDATA[15:0] bus of the TI-PIPE interface. The data sent to the RXDATA[15:0] bus is routed through the 10B/8B decoder. The XIO1100 terminates the loopback operation and returns to transmitting TXDATA[15:0] over the TXP/TXN signaling pair when the TX\_DET\_LOOPBACK signal is de-asserted.

#### 2.10 Electrical Idle

The XIO1100 expects the MAC to issue the required COM (K28.5) symbol and the required number of IDL symbols (K28.3) on TXDATA[7:0] before asserting the TX\_ELECTRICAL signal. The XIO1100 meets the requirements of the Electrical Requirements of a PCI Express PHY (for these requirements, see Section 4.3.1.9, Electrical Idle, and Table B–2 in Appendix B of *PCI Express Base Specification Revision 1.1*).

#### 2.11 Polarity Inversion

Polarity inversion can happen in many places in the receive chain, including somewhere in the serial path, as symbols are placed into the elastic buffer or as symbols are removed from the elastic buffer. The XIO1100 inverts the data received on the RXP/RXN signaling pair when RxPolarity is asserted. The inverted data will begin showing up on the RXDATA within 20 RX CLKS of when RxPolarity is asserted.

#### 2.12 Setting Negative Parity

To set the running disparity to negative, TxCompliance is asserted for one clock cycle that matches with the data that is to be transmitted with negative disparity.

## 2.13 Terminal Assignments

The XIO1100 is packaged in a 100-pin GGB BGA package. See Section 6 for GGB-package terminal diagram.

Table 2–3 lists the terminal assignments in terminal-number order with corresponding signal names for the GGB package.

Table 2–4 lists the terminal assignments arranged in alphanumerical order by signal name with corresponding terminal numbers for the GGB package.

Table 2-3. 100-pin GGB Signal Name Sorted by Terminal Number

| GGB<br>NUMBER | SIGNAL NAME | GGB<br>NUMBER | SIGNAL<br>NAME | GGB<br>NUMBER | SIGNAL NAME             | GGB<br>NUMBER | SIGNAL NAME   |

|---------------|-------------|---------------|----------------|---------------|-------------------------|---------------|---------------|

| А3            | RX_DATA8    | C9            | RESERVED       | G11           | VSSA                    | L6            | CLK_SEL       |

| A4            | RX_DATA9    | C10           | VSSA           | G12           | TXP                     | L7            | VDD_IO        |

| A5            | RX_DATA11   | C12           | RXN            | G13           | TXN                     | L8            | VSS           |

| A6            | RX_DATA13   | C13           | RXP            | H1            | TX_DATA13               | L9            | POWERDOWN1    |

| A7            | RX_DATA15   | D1            | RX_DATA4       | H2            | TX_DATA14               | L10           | DDR_EN        |

| A8            | RX_DATAK0   | D2            | RX_DATA5       | НЗ            | RX_VALID                | L12           | VDD_15_COMB   |

| A9            | RESERVED    | D3            | VSS            | H11           | VDD_33_COMB             | L13           | VDD_33_COM_IO |

| A10           | RESERVED    | D11           | VDDA_33        | H12           | VDDA_15                 | МЗ            | TX_DATA6      |

| A11           | REFCLK-     | D12           | VSSA           | H13           | VDDA_15                 | M4            | TX_DATA5      |

| В3            | RX_ELECIDLE | D13           | VSSA           | J1            | TX_DATA11               | M5            | TX_DATA3      |

| B4            | RX_DATA10   | E1            | RX_DATA2       | J2            | TX_DATA12               | M6            | TX_DATA1      |

| B5            | RX_DATA12   | E2            | RX_DATA3       | J3            | VSS                     | M7            | TX_DATAK1     |

| B6            | RX_DATA14   | E3            | RX_STATUS0     | J11           | VSS                     | M8            | TX_CLK        |

| B7            | RX_DATAK1   | E11           | VDDA_15        | J12           | VDDA_33                 | M9            | POWERDOWN0    |

| B8            | RX_CLK      | E12           | VSSA           | J13           | VDDA_33                 | M10           | P1_SLEEP      |

| B9            | RESERVED    | E13           | VDD_15         | K1            | TX_DATA9                | M11           | VREG_PD       |

| B10           | RESERVED    | F1            | RX_DATA0       | K2            | TX_DATA10               | N3            | TX_DATA7      |

| B11           | REFCLK+     | F2            | RX_DATA1       | КЗ            | VDD_IO                  | N4            | TX_DATA4      |

| C1            | RX_DATA7    | F3            | VDD_IO         | K11           | VSSA                    | N5            | TX_DATA2      |

| C2            | RX_DATA6    | F11           | VDD_15         | K12           | R0                      | N6            | TX_DATA0      |

| C4            | VSS         | F12           | VSS            | K13           | R1                      | N7            | TX_DATAK0     |

| C5            | VDD_IO      | F13           | VSSA           | L1            | TX_DATA8                | N8            | TXCOMPLIANCE  |

| C6            | RX_POLARITY | G1            | RX_STATUS1     | L2            | VSS                     | N9            | TXELECIDLE    |

| C7            | VDD_15_CORE | G2            | TX_DATA15      | L4            | VDD_15_CORE             | N10           | PHY_STATUS    |

| C8            | VSS         | G3            | RX_STATUS2     | L5            | TXDETECTRX/L<br>OOPBACK | N11           | RESETN        |

Table 2-4. 100-pin GGB Signal Name Sorted Alphabetically

| SIGNAL NAME | GGB<br>NUMBER | SIGNAL NAME | GGB<br>NUMBER | SIGNAL NAME             | GGB<br>NUMBER | SIGNAL NAME | GGB<br>NUMBER |

|-------------|---------------|-------------|---------------|-------------------------|---------------|-------------|---------------|

| CLK_SEL     | L6            | RX_DATA8    | А3            | TX_DATA6                | МЗ            | VDD_IO      | F3            |

| P1_SLEEP    | M10           | RX_DATA9    | A4            | TX_DATA7                | N3            | VDD_IO      | КЗ            |

| DDR_EN      | L10           | RX_DATA10   | B4            | TX_DATA8                | L1            | VDD_IO      | L7            |

| PHY_STATUS  | N10           | RX_DATA11   | A5            | TX_DATA9                | K1            | VDD_IO      | C5            |

| POWERDOWN0  | M9            | RX_DATA12   | B5            | TX_DATA10               | K2            | VDDA_15     | H12           |

| POWERDOWN1  | L9            | RX_DATA13   | A6            | TX_DATA11               | J1            | VDDA_15     | E11           |

| R0          | K12           | RX_DATA14   | B6            | TX_DATA12               | J2            | VDDA_15     | H13           |

| R1          | K13           | RX_DATA15   | A7            | TX_DATA13               | H1            | VDDA_33     | J13           |

| REFCLK-     | A11           | RX_DATAK0   | A8            | TX_DATA14               | H2            | VDDA_33     | D11           |

| REFCLK+     | B11           | RX_DATAK1   | В7            | TX_DATA15               | G2            | VREG_PD     | M11           |

| RESERVED    | В9            | RX_ELECIDLE | В3            | TX_DATAK0               | N7            | VSS         | D3            |

| RESERVED    | A10           | RX_POLARITY | C6            | TX_DATAK1               | M7            | VSS         | J3            |

| RESERVED    | B10           | RX_STATUS0  | E3            | TXCOMPLIANCE            | N8            | VSS         | L2            |

| RESERVED    | A9            | RX_STATUS1  | G1            | TXDETECTRX/<br>LOOPBACK | L5            | VSS         | L8            |

| RESERVED    | C9            | RX_STATUS2  | G3            | TXELECIDLE              | N9            | VSS         | J11           |

| /RESET      | N11           | RX_VALID    | НЗ            | TXN                     | G13           | VSS         | F12           |

| RX_CLK      | B8            | RXN         | C12           | TXP                     | G12           | VSS         | C8            |

| RX_DATA0    | F1            | RXP         | C13           | VDD_15                  | F11           | VSS         | C4            |

| RX_DATA1    | F2            | TX_CLK      | M8            | VDD_15                  | E13           | VSSA        | K11           |

| RX_DATA2    | E1            | TX_DATA0    | N6            | VDD_15_COMB             | L12           | VSSA        | G11           |

| RX_DATA3    | E2            | TX_DATA1    | M6            | VDD_15_CORE             | L4            | VSSA        | F13           |

| RX_DATA4    | D1            | TX_DATA2    | N5            | VDD_15_CORE             | C7            | VSSA        | E12           |

| RX_DATA5    | D2            | TX_DATA3    | M5            | VDDA_33                 | J12           | VSSA        | D13           |

| RX_DATA6    | C2            | TX_DATA4    | N4            | VDD_33_COM_IO           | L13           | VSSA        | D12           |

| RX_DATA7    | C1            | TX_DATA5    | M4            | VDD_33_COMB             | H11           | VSSA        | C10           |

## 2.14 Terminal Descriptions

Table 2–5 describes the XIO1100 terminals. The terminals are grouped by functionality.

Table 2-5. XIO1100 Terminals

| TERMINAL       |                                                         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----------------|---------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME           | NO.                                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| PIPE INTERFACE | PIPE INTERFACE                                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| /RESET         | N11                                                     | I   | Reset the device. This signal is active low and asynchronous.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| POWERDOWN[1:0] | L9, M9                                                  | 1   | Power State Control:                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                |                                                         |     | Value: Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                |                                                         |     | 00: P0, normal operation (used for all Polling, Configuration, Recovery, Loop-back, and Hot-Reset states, and the L0 state of the LTSSM)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                |                                                         |     | 01: P0s, low recovery time latency, power–saving state (used for the TX_L0s.idle state of the LTSSM)                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                |                                                         |     | 10: P1, longer recovery time (64µs max) latency, lower power state (used for the disabled state, all detect states, and the L1.idle state of the LTSSM)                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| PHY_STATUS     | N10                                                     | 0   | Used to communicate completion of several PHY functions, including power management state transitions and receiver detection                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| TX_CLK         | M8                                                      | I   | Synchronous input clock for TX_DATA[15:0] and TX_DATAK[1:0] inputs                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                |                                                         |     | If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, TX_CLK is a SDR clock and TX_DATA[15:0] and TX_DATAK[1:0] are latched on the rising edge of TX_CLK.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                |                                                         |     | If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, TX_CLK is a DDR clock and TX_DATA[7:0] and TX_DATAK[0] are latched on both the rising and the falling edge of TX_CLK.TX_DATA[15:8] and TX_DATAK[1] are not used.                                                                                                                                                                                                        |  |  |  |  |  |  |

| TX_DATA[15:0]  | G2, H2, H1, J2,                                         | I   | Parallel Data Transmit Bus                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                | J1, K2, K1, L1,<br>N3, M3, M4,<br>N4, M5, N5,<br>M6, N6 | 1,  | If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, TX_DATA[15:0] is latched off the bus on the rising edge of TX_CLK. TX_DATA[7:0] represents the first symbol and TX_DATA[15:8] represents the second symbol to be transmitted over the TXN and TXP differential signal pair.                                                                                                                                              |  |  |  |  |  |  |

|                |                                                         |     | If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, TX_DATA[7:0] is latched off the bus on both edges of the TX_CLK. TX_DATA[15:8] is not used and should be grounded. The data on TX_DATA[7:0] during the rising edge of the clock represents the first symbol and data on TX_DATA[7:0] during the falling edge of the clock represents the second symbol to be transmitted over the TXN and TXP differential signal pair. |  |  |  |  |  |  |

| TX_DATAK[1:0]  | M7, N7                                                  | I   | Data/Control for the Parallel Data Transmit Bus                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                |                                                         |     | If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, TX_DATAK[0] corresponds to the TX_DATA[7:0] and TX_DATAK[1] to TX_DATA[15:8].                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                |                                                         |     | If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, the state of TX_DATAK[0] corresponds to the data on the TX_DATA[7:0] bus during the same phase of the clock. TX_DATAK[1] is not used and should be grounded.                                                                                                                                                                                                            |  |  |  |  |  |  |

|                |                                                         |     | A value of zero indicates that the corresponding TXDATA bits contain data information; a value of one indicates that the corresponding TXDATA bits contain a control byte.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

NOTE: The TI-PIPE interface can operate at either 1.5 V or 1.8 V, depending on the voltage level of  $V_{DD\_IO}$ . If  $V_{DD\_IO}$  is 1.5 V, the TI-PIPE interface operates at 1.5 V level. If  $V_{DD\_IO}$  is 1.8 V, the TI-PIPE interface operates at 1.8 V level.

Table 2-5. XIO1100 Terminals (Continued)

| TERMIN          | AL                                                                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_ELECIDLE     | N9                                                                      | ı   | Forces TXN/TXP outputs to electrical idle.  When de-asserting low while in P0 state (POWERDOWN[1:0] = 00), indicates that valid data is on the TXDATA bus and that this data should be transmitted.  When asserted high while in P0s state (POWERDOWN[1:0] = 01), always asserted for P0s state.  When asserted high while in P1 state (POWERDOWN[1:0] = 10), always asserted                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TX_COMPLIANCE   | N8                                                                      | I   | for P1 state.  Transmit Compliance Pattern  When asserted high, the XIO1100 sets the running disparity to negativity. Used when transmitting the compliance pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TX_DET_LOOPBACK | L5                                                                      | I   | Begin Receive Detect/Begin Loop-Back Input to device to either begin a receive detect operation or enter loop-back mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RX_CLK          | B8                                                                      | 0   | Synchronous Output Clock for RX_DATA[15:0] and RX_DATAK[1:0] outputs  If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, RX_CLK is a SDR clock, and RX_DATA[15:0] and RX_DATAK[1:0] are latched on the rising edge of RX_CLK.  If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, RX_CLK is a DDR clock and RX_DATA[7:0] and RX_DATAK[0] are latched on both the rising and falling edge of the RX_CLK. RX_DATA[15:8] and RX_DATAK[1] are not used.  RX_CLK is also used as the internal PCLK for the XIO1100.                                                                                                                                                                                                                 |

| RX_DATA[15:0]   | A7, B6, A6, B5,<br>A5, B4, A4, A3,<br>C1, C2, D2, D1,<br>E2, E1, F2, F1 | 0   | Parallel Data Receive Bus  If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, RX_DATA[15:0] is latched on the rising edge of the RX_CLK. RX_DATA[7:0] represents the first symbol received, and RX_DATA[15:8] represents the second symbol received from the RXN and RXP differential signal pair.  If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, RX_DATA[7:0] is latched on both the rising edge and falling edge of the RX_CLK. The data on RX_DATA[7:0] during the rising edge of the RX_CLK represents the first symbol received, and the data on RX_DATA[7:0] during the falling edge of the RX_CLK represents the second symbol received from the RXN and RXP differential signal pair.  RX_DATA[15:8] is not used. |

| RX_DATAK[1:0]   | B7, A8                                                                  | 0   | Data/Control for the parallel data receive bus  If the DDR_EN signal is low during /RESET transitioning from a low state to a high state, the state of RX_DATAK[0] corresponds to RX_DATA[7:0], and RX_DATAK[1] corresponds to RX_DATA[15:8].  If the DDR_EN signal is high during /RESET transitioning from a low state to a high state, the state of RX_DATA[0] corresponds to the data on RX_DATA[7:0] during the same phase of the clock. RX_DATAK[1] is not used.  A value of zero indicates that the corresponding RXDATA bits contain data information. A value of one indicates that the corresponding RXDATA bits contain a control byte.                                                                                                                                                            |

NOTE: The TI-PIPE interface can operate at either 1.5 V or 1.8 V, depending on the voltage level of  $V_{DD\_IO}$ . If  $V_{DD\_IO}$  is 1.5 V, the TI-PIPE interface operates at 1.5 V level. If  $V_{DD\_IO}$  is 1.8 V, the TI-PIPE interface operates at 1.8 V level.

Table 2-5. XIO1100 Terminals (Continued)

| TERMINAL           |            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RX_STATUS[2:0]     | G3, G1, E3 | 0   | Encodes receiver status and error codes for the received data stream and receive detection, as follows:  Value: Description  000: Received data ok  001: 1 SKP added  010: 1 SKP removed  011: Receiver detected  100: 8B/10B decode error  101: Elastic buffer overflow  110: Elastic buffer underflow  111: Receive disparity error                                                                                                                                                                |  |  |

| RX_VALID           | НЗ         | 0   | Indicates symbol lock and valid data on RX_DATA[15:0] and RX_DATAK[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RX_POLARITY        | C6         | I   | Instructs the XIO1100 to perform polarity inversion on the RXN and RXP differential signal pair. Asserting a high on this signal instructs the XIO1100 to perform the polarity inversion.                                                                                                                                                                                                                                                                                                            |  |  |

| RX_ELECIDLE        | B3         | 0   | Indicates receiver detection of an electrical idle of the RXP and RXN signal pair. This is an asynchronous signal.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| REFERENCE CLOCK    | K PIN      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| REFCLK+<br>REFCLK- | B11<br>A11 | I   | The positive and negative terminals for the input reference clock. If CLK_SEL is low during /RESET transitioning from low to high, a 100 MHz clock source has to be applied to REFCLK+ and REFCLK If CLK_SEL is high during /RESET transitioning from low to high, a 125 MHz clock source has to be applied to REFCLK+. REFCLK- is not used and should be grounded.                                                                                                                                  |  |  |

| R0<br>R1           | K12<br>K13 | ı   | Terminals for a 14.56Kù 1% resistors (recommended 5.90K and 8.66K resistors in series)                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| TRANSMIT AND RE    | CEIVE PIN  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TXP                | G12        | 0   | PCI express link differential pair TX positive terminal                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| TXN                | G13        | 0   | PCI express link differential pair TX negative terminal                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RXP                | C13        | I   | PCI express link differential pair RX positive terminal. The XIO1100 has integrated $50-\Omega$ termination resistor to VSS on the RXP terminal, eliminating the need for external components.                                                                                                                                                                                                                                                                                                       |  |  |

| RXN                | C12        | I   | PCI express link differential pair RX negative terminal. The XIO1100 has integrated 50- $\Omega$ termination resistor to VSS on the RXN terminal, eliminating the need for external components.                                                                                                                                                                                                                                                                                                      |  |  |

| MISC               |            | •   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| P1_SLEEP           | M10        | I   | P1 low-power enable.  This input, when asserted high, enables a low-power mode when the XIO1100 enters the P1 state. If the input is asserted when the power-down state is P1 (POWERDOWN[1:0] = 10), the device enters a low-power mode. In this mode, the PLL is disabled and the RX_CLK is unavailable. The P1_SLEEP input must not be asserted when the XIO1100 is in any state other than P1 state and the XIO1100 must not be transitioned out of the P1 state as long as P1_SLEEP is asserted. |  |  |

NOTE: The TI-PIPE interface can operate at either 1.5 V or 1.8 V, depending on the voltage level of  $V_{DD\_IO}$ . If  $V_{DD\_IO}$  is 1.5 V, the TI-PIPE interface operates at 1.5 V level. If  $V_{DD\_IO}$  is 1.8 V, the TI-PIPE interface operates at 1.8 V level.

Table 2-5. XIO1100 Terminals (Continued)

| TERMINAL I/O                         |               |     | DESCRIPTION                                                                                                                                                                                                 |  |  |

|--------------------------------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK_SEL                              | L6 I          |     | Clock Select                                                                                                                                                                                                |  |  |

|                                      |               |     | This input, when asserted low during /RESET transitioning from low to high, selects the 100 MHz differential clock source. A 100MHz clock source has to be applied to REFCLK+ and REFCLK                    |  |  |

|                                      |               |     | This input, when asserted high during /RESET transitioning to high, selects the 125 MHz single ended clock source. A 125 MHz clock source has to be applied to REFCLK+. REFCLK- has to be connected to VSS. |  |  |

| VREG_PD                              | M11           | I   | This pin must be pulled to GND during normal operation.                                                                                                                                                     |  |  |

| DDR_EN                               | L10           | I   | DDR_EN                                                                                                                                                                                                      |  |  |

|                                      |               |     | This input, when asserted high during /RESET transitioning to low state to high state, defines the TI-PIPE interface to be a 8-bit DDR interface; otherwise, it is an 16-bit SDR interface.                 |  |  |

|                                      |               |     | Value: Description                                                                                                                                                                                          |  |  |

|                                      |               |     | 1: DDR_EN is an 8-bit DDR interface                                                                                                                                                                         |  |  |

|                                      |               |     | 0: DDR_EN is a 16-bit SDR interface                                                                                                                                                                         |  |  |

| RESERVED                             |               |     |                                                                                                                                                                                                             |  |  |

| RESERVED                             | B9            |     | RESERVED                                                                                                                                                                                                    |  |  |

| RESERVED                             | A10           |     | RESERVED                                                                                                                                                                                                    |  |  |

| RESERVED                             | B10           |     | RESERVED                                                                                                                                                                                                    |  |  |

| RESERVED                             | A9            |     | RESERVED                                                                                                                                                                                                    |  |  |

| RESERVED                             | C9            |     | RESERVED. This pin needs to be pulled to GND during normal operation.                                                                                                                                       |  |  |

| POWER SUPPLY TER                     | RMINALS       |     |                                                                                                                                                                                                             |  |  |

| VDD_15                               | E13, F11      | PWR | 1.5-V digital power supply.                                                                                                                                                                                 |  |  |

| VDD_15_CORE                          | C7, L4        | PWR | 1.5-V core voltage.                                                                                                                                                                                         |  |  |

| VDDA_15                              | E11, H12, H13 | PWR | 1.5-V analog power supply.                                                                                                                                                                                  |  |  |

| VDD_15_COMB                          | L12           | PWR | 1.5–V main power output. It should be connected to a filter network of 0.01 $\mu$ F, 1 $\mu$ F, and 1000pF capacitors.                                                                                      |  |  |

| VDDA_33                              | D11, J12, J13 | PWR | 3.3-V analog power supply.                                                                                                                                                                                  |  |  |

| VDD_33_COMB                          | H11           | PWR | 3.3–V main output. It should be connected to a filter network of $0.01\mu F$ , $1\mu F$ , and $1000pF$ capacitors.                                                                                          |  |  |

| VDD_33_COMB_IO L13 PWR               |               | PWR | 3.3–V I/O output. It should be connected to a filter network of 0.01 $\mu$ F, 1 $\mu$ F, and 1000pF capacitors.                                                                                             |  |  |

| VDD_IO                               |               | PWR | Power supply for digital I/O. Can be either 1.5 V or 1.8 V depending on desired signaling level.                                                                                                            |  |  |

| VSS D3, J3, L2, L8, J11, F12, C4, C8 |               | GND | Digital ground.                                                                                                                                                                                             |  |  |

|                                      |               | GND | Analog ground.                                                                                                                                                                                              |  |  |

NOTE: The TI-PIPE interface can operate at either  $\overline{1.5\,\text{V}}$  or 1.8 V, depending on the voltage level of  $V_{DD\_IO}$ . If  $V_{DD\_IO}$  is 1.5 V, the TI-PIPE interface operates at 1.5 V level. If  $V_{DD\_IO}$  is 1.8 V, the TI-PIPE interface operates at 1.8 V level.

#### 3 **Electrical Characteristics**

#### 3.1 Absolute Maximum Ratings<sup>†</sup>

| Supply voltage range:   | 3.3 V Supply –0.5 V to                                                             | 3.6 V  |

|-------------------------|------------------------------------------------------------------------------------|--------|

|                         | 1.8 V Supply –0.5 V to 1                                                           | 1.95 V |

|                         | 1.5 V Supply –0.5 V to 1                                                           | 1.65 V |

| Input voltage range,    | V <sub>I</sub> : PCI Express (RX)0.6 V to                                          | 0.6 V  |

|                         | V <sub>I</sub> : PCI Express REFCLK (single-ended) –0.5 V to V <sub>DDA_33</sub> + | 0.5 V  |

|                         | V <sub>I</sub> : PCI Express REFCLK (differential)                                 | 0.5 V  |

| Input clamp current, (V | I < 0 or V <sub>I</sub> > V <sub>DD</sub> ) (see Note 1)                           | 20 mA  |

| Output clamp current, ( | $(V_O < 0 \text{ or } V_O > V_{DD}) \text{ (see Note 2)} \qquad \pm 2$             | 20 mA  |

- NOTES: 1. Applies for external input and bidirectional buffers.  $V_1 < 0$  or  $V_1 > V_{DD}$ .

- 2. Applies to external output and bidirectional buffers.  $V_O < 0$  or  $V_O > V_{DD}$ .

### 3.1.1 Current Consumption

| MODE | TX       | RX   | VDDIO | VDD15 | VDD33 | UNITS |

|------|----------|------|-------|-------|-------|-------|

| LO   | on       | on   | 89    | 102   | 5.4   | mA    |

|      | idle     | on   | 89    | 81    | 1.3   | mA    |

| L0s  | on       | idle | 66    | 93    | 4.3   | mA    |

|      | idle     | idle | 66    | 72    | 1.3   | mA    |

|      | on       | idle | 66    | 94    | 4.3   | mA    |

| L1   | idle     | idle | 65    | 72    | 1.3   | mA    |

|      | L1_sleep |      | 75    | 10    | 1.3   | mA    |

#### **Recommended Operating Conditions** 3.2

|                            |                                       | OPERATION | MIN  | NOM | MAX  | UNIT |

|----------------------------|---------------------------------------|-----------|------|-----|------|------|

| V <sub>DD_15</sub>         |                                       |           |      |     |      |      |

| V <sub>DDA_15</sub>        | Supply voltage                        | 1.5 V     | 1.35 | 1.5 | 1.65 | V    |

| V <sub>DD_15_CORE</sub>    |                                       |           |      |     |      |      |

| V <sub>DDA_33</sub>        | Supply voltage                        | 3.3 V     | 3    | 3.3 | 3.6  | V    |

| V <sub>DD_IO</sub> (1.5 V) | Supply voltage (I/O)                  | 1.5V      | 1.35 | 1.5 | 1.65 | V    |

| V <sub>DD_IO</sub> (1.8 V) | Supply voltage (I/O)                  | 1.8V      | 1.65 | 1.8 | 1.95 | V    |

| T <sub>A</sub>             | Operating ambient temperature range   |           | 0    | 25  | 70   | °C   |

| TJ                         | Virtual junction temperature (Note 3) |           | 0    | 25  | 115  | °C   |

NOTES: 3. The junction temperature reflects simulated conditions. The customer is responsible for verifying junction temperature.

NOTE: The TI-PIPE interface can operate either at 1.5 V or 1.8 V, depending on the voltage level of V<sub>DD IO</sub>. If V<sub>DD IO</sub> is 1.5 V, the TI-PIPE interface operates at 1.5 V level. If  $V_{DD\ IO}$  is 1.8 V, the TI-PIPE interface operates at 1.8 V level.

<sup>†</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 3.3 PCI Express Differential Transmitter Output Ranges

| PARAMETER                                                                                                                              | TERMINALS | MIN    | NOM  | MAX    | UNIT | COMMENTS                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI<br>Unit interval                                                                                                                    | TXP, TXN  | 399.88 | 400  | 400.12 | ps   | Each UI is 400 ps ±300 ppm. UI does not account for SSC-dictated variations.  See Note 4.                                                                                                                                                                                                                                                                |

| V <sub>TX-DIFFp-p</sub><br>Differential peak-to-<br>peak output voltage                                                                | TXP, TXN  | 0.8    |      | 1.2    | V    | $V_{TX-DIFFp-p} = 2* V_{TXP} - V_{TXN} $<br>See Note 5.                                                                                                                                                                                                                                                                                                  |

| V <sub>TX-DE-RATIO</sub> De-em-<br>phasized differential<br>output voltage (ratio)                                                     | TXP, TXN  | -3.0   | -3.5 | -4.0   | dB   | This is the ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 5.                                                                                                                                                                           |

| T <sub>TX-EYE</sub><br>Minimum TX eye width                                                                                            | TXP, TXN  | 0.75   |      |        | UI   | The maximum transmitter jitter can be derived as $T_{TXMAX-JITTER} = 1 - T_{TX-EYE} = 0.3 UI$ See Notes 5 and 6.                                                                                                                                                                                                                                         |

| T <sub>TX</sub> -EYE-MEDIAN-to-<br>MAX-JITTER<br>Maximum time between<br>the jitter median and<br>maximum deviation<br>from the median | TXP, TXN  |        |      | 0.15   | UI   | Jitter is defined as the measurement variation of the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation to recovered TX UI. A recovered TX UI is calculated over 3500 consecutive UIs of sample data. Jitter is measured using all edges of the 250 consecutive UIs in the center of the 3500 UIs used for calculating the TX UI. See Notes 5 and 6. |

| T <sub>TX-RISE</sub> ,<br>T <sub>TX-FALL</sub><br>P/N TX output rise/fall<br>time                                                      | TXP, TXN  | 0.125  |      |        | UI   | See Notes 5 and 8.                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX</sub> -CM-ACp<br>RMS ac peak common<br>mode output voltage                                                                   | TXP, TXN  |        |      | 20     | mV   | $\begin{split} &V_{TX-CM-ACp} = RMS( V_{TXP} + V_{TXN} /2 - V_{TX-CM-DC}) \\ &V_{TX-CM-DC} = DC_{(avg)} \text{ of }  V_{TXP} + V_{TXN} /2 \\ &\text{See Note 5.} \end{split}$                                                                                                                                                                            |

| V <sub>TX-CM-DC-ACTIVE-</sub> IDLE-DELTA Absolute delta of dc common mode voltage during L0 and electrical idle.                       | TXP, TXN  | 0      |      | 100    | mV   | $\begin{split} & V_{TX-CM-DC}-V_{TX-CM-Idle-DC}  \leq 100 \text{ mV} \\ &V_{TX-CM-DC} = DC_{(avg)} \text{ of }  V_{TXP}+V_{TXN} /2 \text{ [during L0]} \\ &V_{TX-CM-Idle-DC} = DC_{(avg)} \text{ of }  V_{TXP}+V_{TXN} /2 \text{ [during electrical idle]} \\ &See \text{ Note 5}. \end{split}$                                                          |

| VTX-CM-DC-LINE-DELTA<br>Absolute delta of dc<br>common mode voltage<br>between P and N                                                 | TXP, TXN  | 0      |      | 25     | mV   | $\begin{split} & V_{TXP-CM-DC}-V_{TXN-CM-DC}  \leq 25 \text{ mV when} \\ &V_{TXP-CM-DC} = DC_{(avg)} \text{ of }  V_{TXP}  \\ &V_{TXN-CM-DC} = DC_{(avg)} \text{ of }  V_{TXN}  \\ &\text{See Note 5.} \end{split}$                                                                                                                                      |

NOTES: 4. No test load is necessarily associated with this value.

- Specified at the measurement point into a timing and voltage compliance test load and measured over any 250 consecutive TX Uls.

- 6. A T<sub>TX-EYE</sub> = 0.75 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.25 UI for the transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It must be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal, as opposed to the averaged time value.

- 7. The transmitter input impedance results in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50  $\Omega$  to ground for both the P and N lines. Note that the use of the series capacitors  $C_{TX}$  is optional for the return loss measurement.

- 8. Measured between 20% and 80% at transmitter package terminals into a test load for both  $V_{TXP}$  and  $V_{TXN}$

| PARAMETER                                                                                                                           | TERMINALS | MIN | NOM | MAX | UNIT | COMMENTS                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-IDLE-DIFFp</sub><br>Electrical idle differen-<br>tial peak output voltage                                                 | TXP, TXN  | 0   |     | 20  | mV   | $V_{TX-IDLE-DIFFp} =  V_{TXP-Idle} - V_{TXN-Idle}  \le 20 \text{ mV}$<br>See Note 5.                                                                                                                                                     |