# WT32i BLUETOOTH AUDIO MODULE

**DATA SHEET**

Monday, 23 October 2017

Version 1.23

# **VERSION HISTORY**

| VERSION | COMMENT                                                                                           |

|---------|---------------------------------------------------------------------------------------------------|

| 1.0     | First version                                                                                     |

| 1.1     | Added example how to protect the battery by shutting down the regulators at certain voltage level |

| 1.2     | Fixed PCM pin numbering                                                                           |

| 1.21    | Design check list added                                                                           |

| 1.22    | UART brake signal updated                                                                         |

| 1.23    | Chapter 9.3.1 added                                                                               |

# **TABLE OF CONTENTS**

| 1  | De   | sign C   | Check List                                                                  | 7  |

|----|------|----------|-----------------------------------------------------------------------------|----|

| 2  | W٦   | Г32і Р   | roduct Numbering                                                            | 8  |

| 3  | Blo  | ock dia  | gram                                                                        | 9  |

| 4  | Pin  | nout ar  | nd Terminal Description                                                     | 10 |

| 5  | Ele  | ectrica  | l Characteristics                                                           | 13 |

|    | 5.1  | Abso     | olute Maximum Ratings                                                       | 13 |

|    | 5.2  | Rec      | ommended Operating Conditions                                               | 13 |

|    | 5.3  | Digit    | al Terminals                                                                | 13 |

|    | 5.4  | Audi     | o Characteristics                                                           | 14 |

|    | 5.4  | l.1      | ADC                                                                         | 14 |

|    | 5.4  | 1.2      | DAC                                                                         | 15 |

|    | 5.4  | 1.3      | A2DP Codecs                                                                 | 15 |

|    | 5.5  | RF (     | Characteristics                                                             | 17 |

|    | 5.5  | 5.1      | RF Transceiver                                                              | 17 |

|    | 5.5  | 5.2      | Antenna Characteristics                                                     | 18 |

|    | 5.6  | Curr     | ent Consumption                                                             | 21 |

| 6  | Po   | wer C    | ontrol and Regulation                                                       | 22 |

|    | 6.1  | Prot     | ecting the Battery by Configuring the Module to Turn Off at Certain Voltage | 24 |

|    | 6.2  | Res      | et                                                                          | 25 |

|    | 6.2  | 2.1      | Internal POR                                                                | 25 |

| 7  | Ba   | ttery C  | Charger                                                                     | 27 |

| 8  | GF   | PIO an   | d AIO Functions                                                             | 28 |

|    | 8.1  | iWR      | AP supported GPIO Functions                                                 | 28 |

|    | 8.2  | Outp     | outting Internal Clocks                                                     | 28 |

|    | 8.3  | Auxi     | liary ADC                                                                   | 29 |

|    | 8.4  | Soft     | ware I2C Interface                                                          | 29 |

| 9  | Se   | rial Int | erfaces                                                                     | 30 |

|    | 9.1  | UAR      | T Interface                                                                 | 30 |

|    | 9.1  | .1       | Resetting Through UART Break Signal                                         | 31 |

|    | 9.1  | .2       | UART Configuration While Reset is Active                                    | 31 |

|    | 9.1  | .3       | UART Bypass Mode                                                            | 31 |

|    | 9.2  | USB      | Interface                                                                   | 32 |

|    | 9.3  | Prog     | gramming and Debug Interface (SPI)                                          | 33 |

|    | 9.3  | 3.1      | Multi-slave Operation                                                       | 33 |

| 10 | ) A  | Audio    | Interfaces                                                                  | 34 |

|    | 10.1 |          | Stereo Audio Codec Interface                                                | 34 |

|    | 10   | 1 1      | ADC.                                                                        | 34 |

| 10.1.2    | DAC                                             | 36 |

|-----------|-------------------------------------------------|----|

| 10.1.3    | Microphone Input                                | 37 |

| 10.1.4    | Line Input                                      | 38 |

| 10.1.5    | Output Stage                                    | 39 |

| 10.1.6    | Mono Operation                                  | 41 |

| 10.1.7    | Side Tone                                       | 41 |

| 10.2      | PCM Interface                                   | 41 |

| 10.3      | I2S Interface                                   | 41 |

| 10.4      | IEC 60958 Interface                             | 43 |

| 11 Desig  | n Guidelines                                    | 45 |

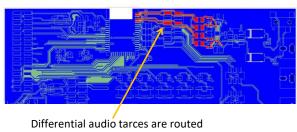

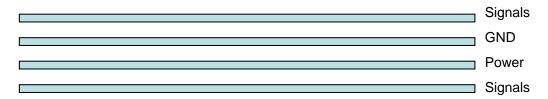

| 11.1      | Audio Layout Guide                              | 45 |

| 11.1.1    | EMC Considerations                              | 45 |

| 11.1.2    | Choosing Capacitors and Resistors               | 45 |

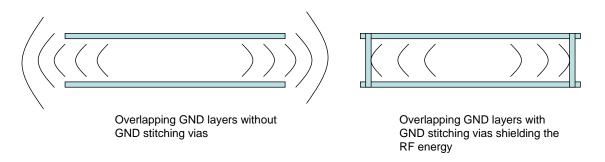

| 11.2      | RF Layout Guide                                 | 46 |

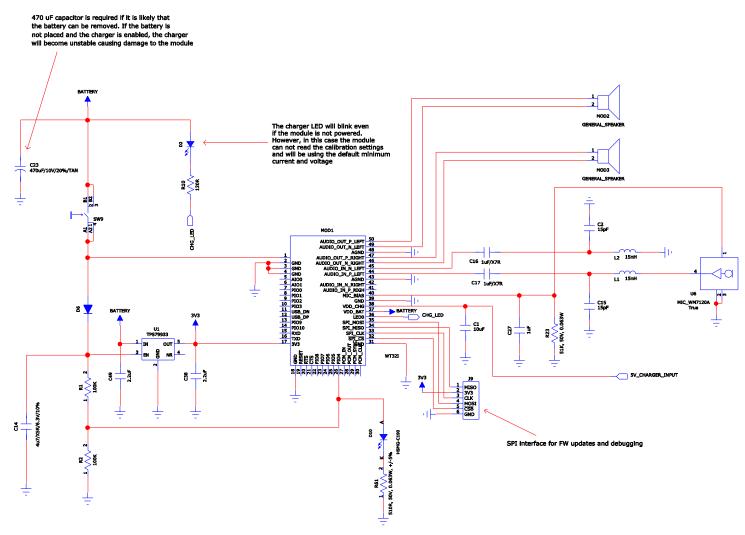

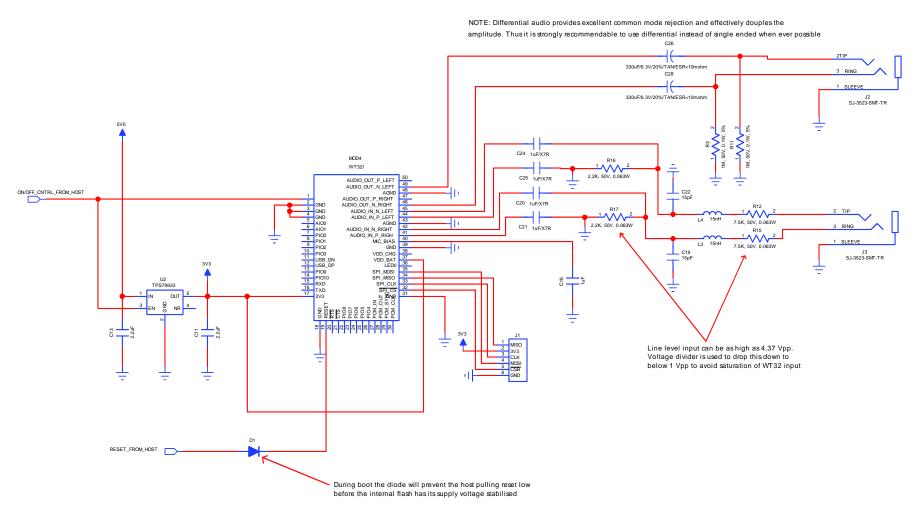

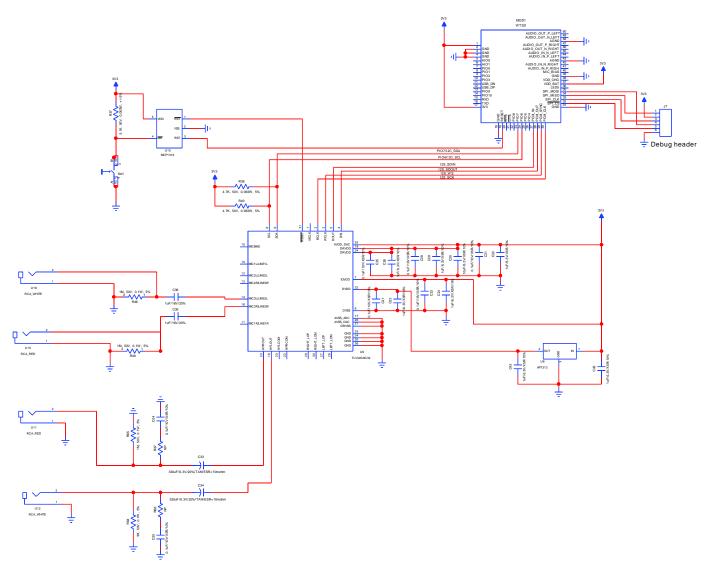

| 11.3      | Example Application Schematics                  | 49 |

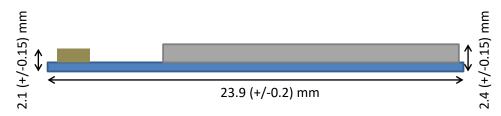

| 12 Physi  | cal Dimensions                                  | 53 |

| 13 Solde  | ring Recommendations                            | 55 |

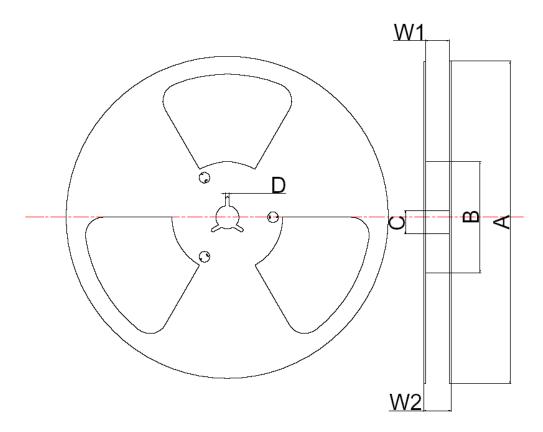

| 14 Packa  | age                                             | 56 |

| 15 Certif | ication Guidance for an End Product Using WT32i | 58 |

| 15.1      | Bluetooth End Product Listing                   | 58 |

| 15.2      | CE Approval of an End-Product                   | 58 |

| 15.3      | FCC Certification of an End Product             | 59 |

| 15.3.1    | Co-location with Other Transmitters             | 60 |

| 15.4      | IC Certification of an End Product              | 60 |

| 15.5      | MIC Japan Certification of an End Product       | 60 |

| 16 WT32   | 2i Certifications                               | 60 |

| 16.1      | Bluetooth                                       | 60 |

| 16.2      | CE                                              | 60 |

| 16.3      | FCC                                             | 61 |

| 16.4      | IC                                              | 62 |

| 16.4.1    | IC                                              | 62 |

| 16.5      | MIC Japan                                       | 63 |

| 16.6      | KCC (South-Korea)                               | 63 |

| 16.7      | Qualified Antenna Types for WT32i-E             | 63 |

| 17 Conta  | net Information                                 | 64 |

#### WT32i Bluetooth® Audio Module

#### **DESCRIPTION**

WT32i is an audio specific Bluetooth 3.0 module with excellent radio frequency performance and enhanced audio features, enabling a best in class Bluetooth audio experience. In addition to certified Bluetooth radio and software stack, WT32i also contains a DSP, stereo audio codec, and battery charger making it ideal for fixed and portable audio applications. WT32i includes Bluegiga's iWRAP6 Bluetooth stack software which implements A2DP, AVRCP v.1.5 profiles and supports aptX® and AAC audio codecs for stereo audio applications. For hands-free iWRAP6 applications software supports HFP HSP, MAP v.1.6, PBAP and CVC® echo cancellation software. For data communications to Android and iWRAP6 iOS applications also implements Bluetooth Serial Port Profile (SPP) and Apple iAP profiles. WT32i is an ideal solution for developers who want to quickly integrate the latest Bluetooth audio technologies without the time and costs typically involved with a Bluetooth audio chipset design.

#### **APPLICATIONS:**

- Stereo speakers and sound bars

- Hi-Fi devices

- Hands-free kits

- Stereo headsets

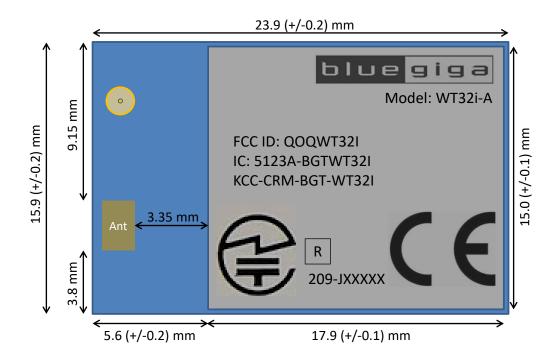

Figure 1: WT32i Bluetooth Audio Module

#### **KEY FEATURES:**

- Bluetooth 3.0 compliant

- Excellent Radio Performance

- o Transmit power: +6.5 dBm

- o Receiver sensitivity: -90 dBm

- o Link budget: 96.5 dB

- Integrated chip antenna or U.FL antenna connector

- Audio features

- o Integrated DSP

- o 16-bit stereo codec

- o 44.1kHz ADC, 48kHz DAC

- Analog, I2S, PCM, SPDIF, and microphone interfaces

- Optional aptX® and AAC stereo audio codecs

- Optional CVC® echo cancellation

- Wide Band Speech

- Built-in battery charger

- UART host interface

- 802.11 co-existence interface

- 10 software programmable IO pins

- Operating voltage: 1.8V to 3.6V

- Temperature range: -40C to +85C

- Bluetooth, CE, FCC, IC, Korea and Japan qualified

- Integrated iWRAP6 Bluetooth stack

- o 13 Bluetooth profiles

- Apple iAP1 and iAP2 compatibility

# **Design Check List**

# POWERING THE MODULE

- > Make sure that VRE\_ENA is connected correctly

- ➤ Use iWRAP command SET CONTROL VREGEN command to configure the VREG ENA pin according to the HW

- > Reserve test points for SPI interface for debugging and FW updates

- > The internal power on reset does not work properly if the host pulls the reset line low during boot. To prevent this, place a diode to the reset input.

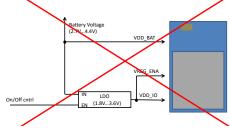

# Battery Voltage (2.7V...4.4V) VREG\_ENA

# **RF LAYOUT**

> Make sure that the layout for the antenna is done as instrcucted.

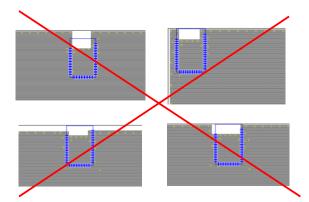

# **AUDIO DESIGN AND LAYOUT**

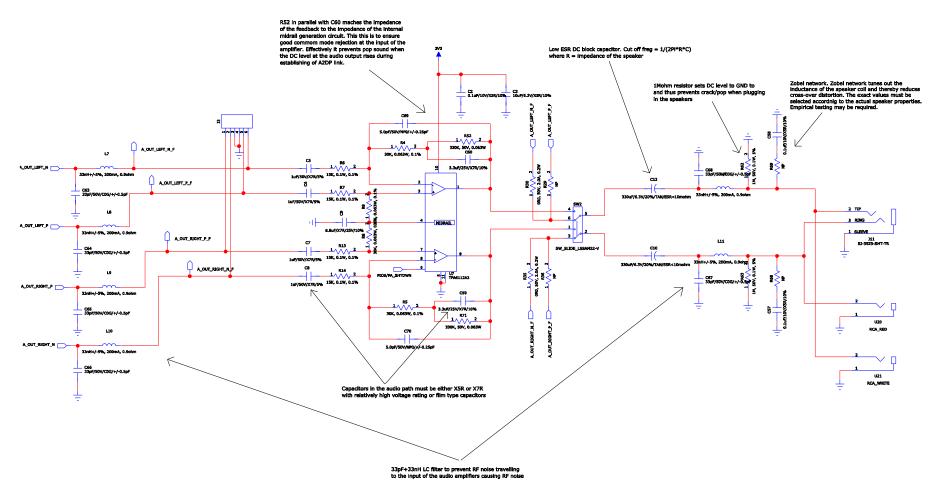

- > See the example schematics on pages 49 -52

- Avoid using single ended audio traces. Always use differential audio signaling when possible

- Use solid GND plane and make sure that all the GND pins are connected to it by placing a GND via right next to any GND pins.

- > When routing single ended audio traces, make sure that the return current (i.e. GND) follows the traces all the way from start to the end

- > DO NOT COMPROMISE AUDIO ROUTING

symmetrically and parallel

# 2 WT32i Product Numbering

| Product code     | Description                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WT32i-A-Al6      | WT32i Bluetooth Module with internal chip antenna and iWRAP6 <i>Bluetooth</i> software                                                                                                            |

| WT32i-A-Al6-APTX | WT32i Bluetooth Module with internal chip antenna and aptX® audio codec capable iWRAP6 <i>Bluetooth</i> software.                                                                                 |

| WT32i-A-Al6IAP   | WT32i Bluetooth Module with internal chip antenna and Apple iAP capable iWRAP6 <i>Bluetooth</i> software. Available only to Apple MFI licensees. Contact sales@bluegiga.com for more information. |

| WT32i-E-Al6      | WT32i Bluetooth Module with U.FL connector and iWRAP6 Bluetooth software                                                                                                                          |

| WT32i-E-Al6-APTX | WT32i Bluetooth Module with U.FL connector and aptX® audio codec capable iWRAP6 <i>Bluetooth</i> software.                                                                                        |

| WT32i-E-Al6IAP   | WT32i Bluetooth Module with U.FL connector and Apple iAP capable iWRAP6 <i>Bluetooth</i> software. Available only to Apple MFI licensees. Contact sales@bluegiga.com for more information.        |

| DKWT32i-A        | WT32i development kit                                                                                                                                                                             |

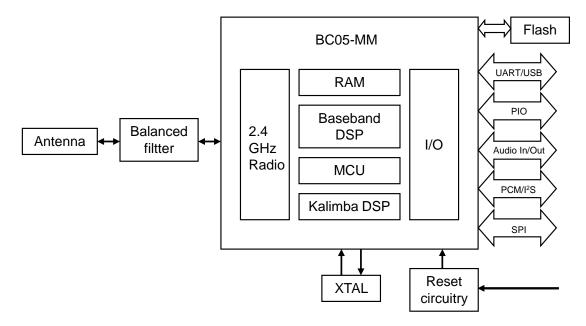

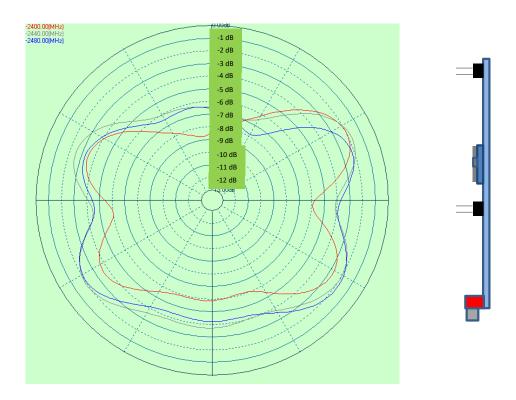

# 3 Block diagram

Figure 2: Block Diagram of WT32i

#### BC05-MM

The BlueCore®5-Multimedia External is a single-chip radio and baseband IC for Bluetooth 2.4GHz systems. It provides a fully compliant Bluetooth v3.0 specification system for data and voice. BlueCore5-Multimedia External contains the Kalimba DSP coprocessor with double the MIPS of BlueCore3-Multimedia External, supporting enhanced audio applications.

#### **XTAL**

Ther reference clock of WT32i is generated with 26 MHz crystal. All BC05-MM internal digital clocks are generated using a phase locked loop, which is locked to the frequency of either the 26 MHz crystal or an internally generated watchdog clock frequency of 1kHz.

#### **RESET CIRCUITRY**

The internal reset circuitry keeps BC05-MM in reset during boot in order for the supply voltages to stabilize. This is to prevent corruption of the flash memory during booting. Please see chapter 6.1 for more detailed description.

#### **BALANCED FILTER**

The internal balanced filter provides optimal impedance matching and band pass filtering in order to achieve lowest possible in-band and out-of-band emissions.

#### **ANTENNA**

The antenna is a ceramic chip antenna with high efficiency. The antenna is insensitive to surrounding dielectric materials and requires only a small clearance underneath which makes it compatible with previous WT32I designs and well suitable for designs with high density.

#### **FLASH**

16 Mbit flash memory is used for storing the Bluetooth protocol stack and Virtual Machine applications. It can also be used as an optional external RAM for memory-intensive applications.

# 4 Pinout and Terminal Description

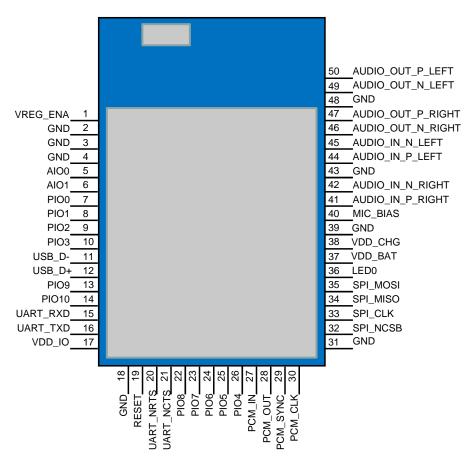

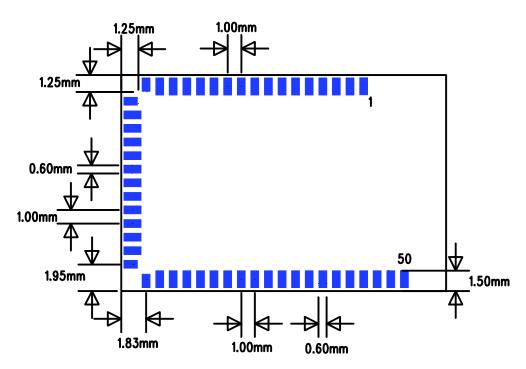

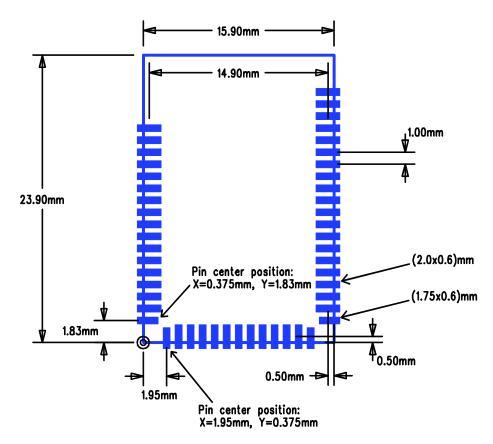

Figure 3: WT32i

| Pin Number                 | Pin Name | Pad Type                      | Description                                                                              |

|----------------------------|----------|-------------------------------|------------------------------------------------------------------------------------------|

| 1                          | VREG_ENA | Input                         | SW configurable enable pin for the internal regulators                                   |

| 2-4, 18, 31,<br>39, 43, 48 | GND      | GND GND                       |                                                                                          |

| 17                         | VDD_IO   | Power supply                  | 1.7V - 3.6V power supply for the serial interfaces and GPIOs                             |

| 37                         | VDD_BAT  | Power supply / Charger output | 2.7V - 4.4V supply voltage for the internal regulators and output of the battery charger |

| 38                         | VDD_CHG  | Power supply                  | Nominal 5V supply voltage for the battery charger                                        |

**Table 1: Supply Terminal Descriptions**

| Pin<br>Number | Pin Name                  | Pin Type                                     | Description                                                                                                                                                                                                                                                                       |  |  |  |

|---------------|---------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 19            | RESET                     | RESET                                        | Active high reset. If not used, leave floating. When connected, make sure that the reset is either pulled high or floating (connected to high impedance) during boot.                                                                                                             |  |  |  |

| 5             | AIO0                      |                                              | AIO0 and AIO1 can be used to read the voltage level through the internal ADC (refer to iWRAP User Guide for details). AIO pins can also be                                                                                                                                        |  |  |  |

| 6             | AIO1                      | Configurable I/O                             | configured to be used as general digital IO pins through PS settings. Internal clocks can be routed out through AIO pins by setting corresponding PS settings. Note that the AIO pins are powered from internal 1.5V supply so the maximum voltage level of the AIO pins is 1.5V. |  |  |  |

|               |                           |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 7             | PIO0                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 8             | PIO1                      |                                              | General purpose IO's can be configured with iWRAP for various functions. Each IO can be                                                                                                                                                                                           |  |  |  |

| 9             | PIO2                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 10            | PIO3                      |                                              | configured individually as output or input with strong or weak pull-up/-down. Using particular PS setting GPIO pins can be used to implement WiFi co-existence signaling between WT32i and a WiFi                                                                                 |  |  |  |

| 13            | PIO9                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 14            | PIO10                     | Configurable CMOS I/O                        |                                                                                                                                                                                                                                                                                   |  |  |  |

| 22            | PIO8                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 23            | PIO7                      |                                              | radio. Software I2C interface can be implemented                                                                                                                                                                                                                                  |  |  |  |

| 24            | PIO6                      |                                              | for slow I2C functions such as configuring external audio codec or display.                                                                                                                                                                                                       |  |  |  |

| 25            | PIO5                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 26            | PIO4                      |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

|               |                           |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 11            | USB_D-                    | I/O                                          | USB data minus                                                                                                                                                                                                                                                                    |  |  |  |

| 12            | USB_D+                    | I/O                                          | USB data plus with selectable internal 1.5k pull-up resistor                                                                                                                                                                                                                      |  |  |  |

|               |                           |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 15            | UART_RXD                  | CMOS Input, weak internal pull-down          | UART data input                                                                                                                                                                                                                                                                   |  |  |  |

| 16            | UART_TXD                  | CMOS output, tristate, weak internal pull-up | UART data output                                                                                                                                                                                                                                                                  |  |  |  |

| 20            | UART_NRTS                 | CMOS output, tristate, weak internal pull-up | UART request to send, active low                                                                                                                                                                                                                                                  |  |  |  |

| 21            | CMOS Input, weak internal |                                              | UART clear to send, active low                                                                                                                                                                                                                                                    |  |  |  |

|               |                           |                                              |                                                                                                                                                                                                                                                                                   |  |  |  |

| 32            | SPI_NCSB                  | CMOS Input, weak internal pull-down          | SPI chip select                                                                                                                                                                                                                                                                   |  |  |  |

| 33            | SPI_CLK                   | CMOS Input, weak internal pull-down          | SPI clock                                                                                                                                                                                                                                                                         |  |  |  |

| 34 | SPI_MISO | CMOS Input, weak internal pull-down            | SPI data input  |

|----|----------|------------------------------------------------|-----------------|

| 35 | SPI_MOSI | CMOS output, tristate, weak internal pull-down | SPI data output |

|    |          |                                                |                 |

| 36 | LED0     | Open drain output                              | LED driver      |

**Table 2: Terminal Descriptions**

| Pin<br>Number        | Pin Name          | Pin Type                                       | Description                                                                                                            |

|----------------------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 40                   | MIC_BIAS          | Analog                                         |                                                                                                                        |

| 41                   | AUDIO_IN_P_RIGHT  | Analog                                         |                                                                                                                        |

| 42                   | AUDIO_IN_N_RIGHT  | Analog                                         |                                                                                                                        |

| 44                   | AUDIO_IN_P_LEFT   | Analog                                         |                                                                                                                        |

| 45                   | AUDIO_IN_N_LEFT   | Analog                                         |                                                                                                                        |

| 46                   | AUDIO_OUT_N_RIGHT | Analog                                         |                                                                                                                        |

| 47                   | AUDIO_OUT_P_RIGHT | Analog                                         |                                                                                                                        |

| 49                   | AUDIO_OUT_N_LEFT  | Analog                                         |                                                                                                                        |

| 50                   | AUDIO_OUT_P_LEFT  | Analog                                         |                                                                                                                        |

|                      |                   |                                                |                                                                                                                        |

| 27                   | PCM_IN / I2S IN   | CMOS input, weak internal pull-down            | PCM or I2S data input                                                                                                  |

| 28                   | PCM_OUT / I2S_OUT | CMOS outptu, tristate, weak internal pull-down | PCM or I2S data output                                                                                                 |

| 29 PCM_SYNC / I2S_WS |                   | Bidirectional, weak internal down              | PCM sync or I2S word select. WT32i can operate as a PCM/I2S master providing the sync or as a slave receiving the sync |

| 30 PCM_CLK / I2S_SCK |                   | Bidirectional, weak internal down              | PCM or I2S clock. WT32i can operate as a PCM/I2S master providing the clock or as a slave receiving the clock.         |

**Table 3: Audio Terminal Descriptions**

# 5 Electrical Characteristics

# 5.1 Absolute Maximum Ratings

|                             | Min        | Max        | Unit |

|-----------------------------|------------|------------|------|

| Storage temperature range   | -40        | +85        | °C   |

| Operating temperature range | -40        | +85        | °C   |

| VDD_IO                      | -0.4       | 3.6        | V    |

| VDD_BAT                     | -0.4       | 4.4        | V    |

| VDD_CHG                     | -0.4       | 6.5        | V    |

| Digital Terminal voltages   | VSS - 0.4V | VDD + 0.4V | V    |

| AIO voltages                | VSS - 0.4V | 1.9V       | V    |

**Table 4: Absolute Maximum Ratings**

# 5.2 Recommended Operating Conditions

|                             | Min | Max  | Unit |

|-----------------------------|-----|------|------|

| Storage temperature range   | -40 | +85  | °C   |

| Operating temperature range | -40 | +85  | °C   |

| VDD_IO                      | 1.7 | 3.6  | V    |

| VDD_BAT                     | 2.7 | 4.4  | V    |

| VDD_CHG                     | 0   | 6.5  | V    |

| Digital Terminal voltages   | 0   | VDD  | V    |

| AIO voltages                | 0   | 1.5V | V    |

**Table 5: Recommended Operating Conditions**

# 5.3 Digital Terminals

| Input/Output Characteristic                                       | Min         | Max        | Unit |

|-------------------------------------------------------------------|-------------|------------|------|

| V <sub>I</sub> input logic level low                              | -0.3        | 0.25 x VDD | V    |

| Vı∟input logic level high                                         | 0.625 x VDD | VDD + 0.3  | V    |

| Vol output logic level low, IoL = 4.0mA                           | 0           | 0.125      | V    |

| V <sub>OL</sub> output logic level high, I <sub>OL</sub> = -4.0mA | 0.75 x VDD  | VDD        | V    |

| Strong pull-up                                                    | -100        | -10        | μA   |

| Strong pull-down                                                  | 10          | 100        | μA   |

| Weak pull-up                                                      | -5          | -0.2       | μA   |

| Weak pull-down                                                    | 0.2         | 5          | μΑ   |

**Table 6: Digital Terminal Characteristics**

# 5.4 Audio Characteristics

# 5.4.1 ADC

| Parameter                                 | Conditions                                      |                     | Min | Тур  | Max  | Unit   |

|-------------------------------------------|-------------------------------------------------|---------------------|-----|------|------|--------|

| Resolution                                | Resolution -                                    |                     | -   | -    | 16   | Bits   |

| Input Sample<br>Rate, F <sub>sample</sub> | -                                               |                     | 8   | -    | 44.1 | kHz    |

|                                           |                                                 | F <sub>sample</sub> |     |      |      |        |

|                                           |                                                 | 8kHz                | -   | 79   | -    | dB     |

| Signal to Noise                           |                                                 | 11.025kHz           | -   | 77   | -    | dB     |

| Ratio, SNR                                |                                                 | 16kHz               | -   | 76   | -    | dB     |

|                                           |                                                 | 22.050kHz           | -   | 76   | -    | dB     |

|                                           |                                                 | 32kHz               | -   | 75   | -    | dB     |

|                                           |                                                 | 44.1kHz             | -   | 75   | -    | dB     |

| Input full scale a                        | Input full scale at maximum gain (differential) |                     |     | 4    | -    | mV rms |

| Input full scale                          | Input full scale at minimum gain (differential) |                     |     | 800  | -    | mV rms |

| 3dB Bandwidth                             |                                                 |                     | -   | 20   | -    | kHz    |

| Microphone mode input impedance           |                                                 |                     | -   | 6.0  | -    | kHz    |

| THD+1                                     | THD+N @ 30mV rms input                          |                     |     | 0.04 | -    | %      |

**Table 7: ADC characteristics**

### 5.4.2 DAC

| Parameter                                  |                 | Condition   | ons                 | Min  | Тур | Max  | Unit   |

|--------------------------------------------|-----------------|-------------|---------------------|------|-----|------|--------|

| Resolution                                 | -               |             | -                   | -    | 16  | Bits |        |

| Output Sample<br>Rate, F <sub>sample</sub> | -               |             | 8                   | -    | 48  | kHz  |        |

|                                            |                 |             | F <sub>sample</sub> |      |     |      |        |

|                                            |                 |             | 8kHz                | -    | 95  | -    | dB     |

| Signal to Noise                            | Signal to Noise |             | 11.025kHz           | -    | 95  | -    | dB     |

| Ratio, SNR                                 |                 |             | 16kHz               | -    | 95  | -    | dB     |

|                                            |                 |             | 22.050kHz           | -    | 95  | -    | dB     |

|                                            |                 |             | 32kHz               | -    | 95  | -    | dB     |

|                                            |                 |             | 44.1kHz             | -    | 95  | -    | dB     |

| Output Full \                              | /oltage         | Swing (diff | erential)           | -    | 750 | -    | mV rms |

| Re                                         |                 | Res         | sistive             | 16   | -   | O.C. | Ω      |

| Allowed Loa                                | u               | Capacitive  |                     | 500  | pF  |      |        |

| THD+N 16Ω Load                             |                 | -           | -                   | 0.1  | %   |      |        |

| THD+N 100Ω Load                            |                 | -           | -                   | 0.01 | %   |      |        |

**Table 8: DAC Characteristics**

#### 5.4.3 A2DP Codecs

#### 5.4.3.1 SBC

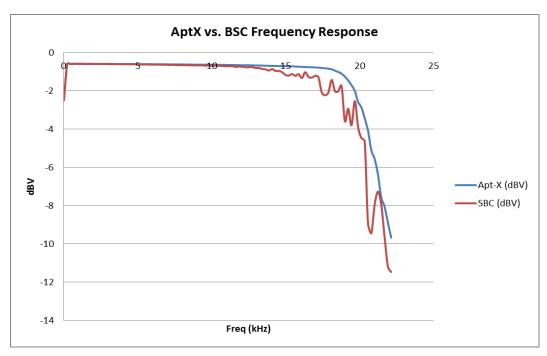

SBC codec is the default codec used for Bluetooth A2DP connections. Any Bluetooth device supporting A2DP audio profile supports SBC codec. SBC was originally design to provide reasonable good audio quality while keeping low computational complexity. SBC does not require high bit rates. Thus it works sufficiently with Bluetooth where the bandwidth and the processing power are limited.

#### 5.4.3.2 aptX®

The aptX is widely used in high quality audio devices. aptX can provide dynamic range up to 120 dB and it has the shortest coding delay (<2ms) than other coding algorithms. Using aptX® the whole system latency can be reduced significantly because unlike SBC, it does not require buffering the audio. SBC reproduces a limited audio band width whereas aptX® encode the entire frequency range of audio.

aptX<sup>®</sup> is more robust and resilient coding scheme than SBC and thus re-transmits does not occur as with SBC.

Both SBC and aptX<sup>®</sup> have flat frequency response up to 14 kHz. Up to 14 kHz both algorithms produce good quality audio with very little distortion. At frequencies higher than 14 kHz the benefit of aptX<sup>®</sup> becomes obvious. SBC exhibits increasing attenuation with increasing frequency but aptX<sup>®</sup> retains high reproduction quality.

aptX® requires purchasing a license for each Bluetooth address and the license agreement must be done with CSR. The combination of aptX® license and the Bluetooth address is programmed into the module in the module production line.

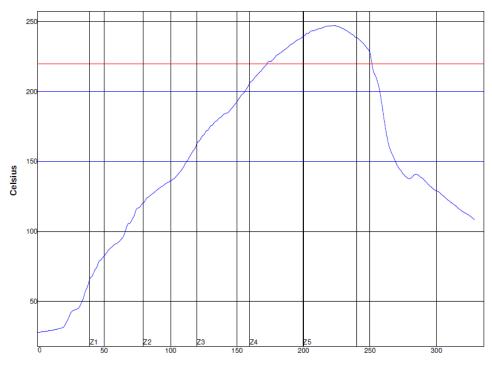

Figure 4: Frequency response of aptX and SBC codecs

#### 5.4.3.3 AAC

AAC (Advanced Audio Coding) achieves better sound quality than MP3 and it is the default audio format for YouTube and iPhone among others. AAC has long latency (>100ms) compared to aptX®. Because of high processing capacity requirement for encoding, WT32i does not support AAC as A2DP source. Thus WT32i can be used for receiving (A2DP sink) AAC (from iPhone for example) but it cannot transmit AAC coded audio.

# 5.5 RF Characteristics

# 5.5.1 RF Transceiver

| Transceiver characteristic                          |      | Min | Тур     | Max | Unit |

|-----------------------------------------------------|------|-----|---------|-----|------|

| Maximum transmit power                              |      | 5   | 6.5     | 8   | dBm  |

| Minimum transmit power                              |      |     | -17     |     | dBm  |

| Transmit power stability over the temperature range |      |     | +/- 0.5 |     | dB   |

| Transmit power variation within the BT band         |      |     |         | 1   | dB   |

|                                                     | RT   |     | -90     |     | dBm  |

| Sensitivity DH1                                     | -40C |     | -91     |     | dBm  |

|                                                     | +85C |     | -86     |     | dBm  |

| RT                                                  |      |     | -83     |     | dBm  |

| Sensitivity 3DH5                                    | -40C |     | -84     |     | dBm  |

|                                                     | +85C |     | -80     |     | dBm  |

**Table 9: Transceiver characteristics**

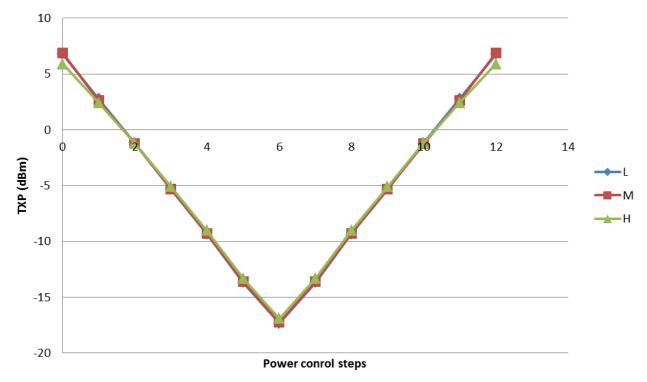

Table 10: Power control of WT32i

| Standard                              | Band /<br>Frequency                   | Min<br>(AVG /<br>PEAK) | Typ<br>(AVG /<br>PEAK) | Max<br>(AVG /<br>PEAK) | Limit by the Standard<br>(AVG / PEAK) | Unit   |

|---------------------------------------|---------------------------------------|------------------------|------------------------|------------------------|---------------------------------------|--------|

|                                       | 2nd harmonic                          |                        | 50 / 61                |                        | 54 / 74                               | dBuV/m |

|                                       | 3rd harmonic                          |                        | < 40 /<br>50           |                        | 54 / 74                               | dBuV/m |

|                                       | Band edge<br>2390MHz                  |                        |                        |                        | 54 / 74                               | dBuV/m |

| FCC part 15 transmitter               | Band edge<br>2483.5MHz                |                        |                        |                        | 54 / 74                               | dBuV/m |

| spurious<br>emissions                 | Band edge<br>2400MHz<br>(conducted)   |                        |                        |                        | -20                                   | dBc    |

|                                       | Band edge<br>2483.5MHz<br>(conducted) |                        |                        |                        | -20                                   | dBc    |

| ETSI EN 300<br>328 transmitter        | Band edge<br>2400MHz                  |                        |                        |                        | -30                                   | dBm    |

| spurious                              | 2nd harmonic                          |                        | -35                    |                        | -30                                   | dBm    |

| emissions                             | 3rd harmonic                          |                        | <-40                   |                        | -30                                   | dBm    |

| ETSI EN 300                           | (2400 - 2479)<br>MHz                  |                        |                        |                        | -47                                   | dBm    |

| 328 receiver<br>spurious<br>emissions | (1600 - 1653)<br>MHz                  |                        |                        |                        | -47                                   | dBm    |

Table 11: WT32i-A spurious emissions

Note: All the emissions tested with maximum 8 dBm TX power

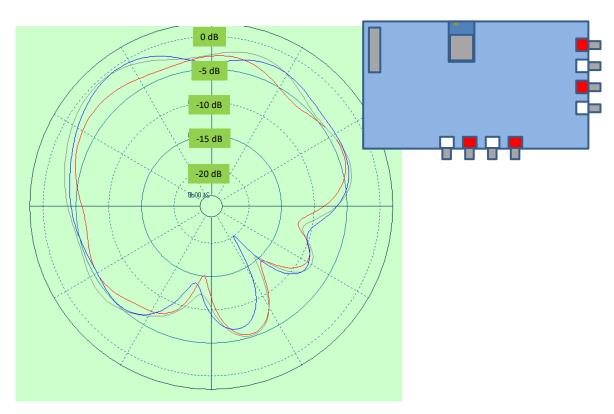

# 5.5.2 Antenna Characteristics

Note: Antenna characteristics may vary depending on the mother board layout. Following characteristics have been measured using DKWT32i

- Antenna efficiency -3.5 dB (45%)

- Peak gain 0 dBi

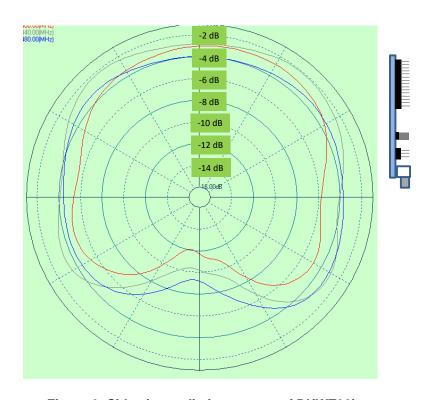

Figure 5: Top view radiation pattern of DKWT32i

Figure 6: Side view radiation pattern of DKWT32i

Figure 7: Front view radiation pattern

# 5.6 Current Consumption

| Oper                      | ation Mode                  | Peak | Average | Unit |

|---------------------------|-----------------------------|------|---------|------|

|                           | SET BT PAGEMODE 0 2000 0    |      | 2.0     |      |

|                           | SET BT PAGEMODE 0 2000 1    | 12   | 2.0     |      |

|                           | SET BT PAGEMODE 0 2000 2    |      | 2.0     |      |

|                           | SET BT PAGEMODE 1 2000 0    |      | 2.0     |      |

|                           | SET BT PAGEMODE 1 2000 1    |      | 2.1     | mA   |

|                           | SET BT PAGEMODE 1 2000 2    |      | 2.1     |      |

|                           | SET BT PAGEMODE 2 2000 0    |      | 23      |      |

| Idle                      | SET BT PAGEMODE 2 2000 1    |      | 2.2     |      |

|                           | SET BT PAGEMODE 2 2000 2    | 32   | 2.1     |      |

|                           | SET BT PAGEMODE 3 2000 0    | 32   | 23      |      |

|                           | SET BT PAGEMODE 3 2000 1    |      | 2.3     |      |

|                           | SET BT PAGEMODE 3 2000 2    |      | 2.2     |      |

|                           | SET BT PAGEMODE 4 2000 0    |      | 23      |      |

|                           | SET BT PAGEMODE 4 2000 1    |      | 2.3     |      |

|                           | SET BT PAGEMODE 4 2000 2    |      | 2.2     |      |

|                           | SET BT PAGEMODE 0 2000 0    |      | 0.08    |      |

|                           | SET BT PAGEMODE 0 2000 1    | 12   | 0.08    |      |

|                           | SET BT PAGEMODE 0 2000 2    |      | 0.08    |      |

|                           | SET BT PAGEMODE 1 2000 0    |      | 0.18    |      |

|                           | SET BT PAGEMODE 1 2000 1    |      | 0.18    |      |

|                           | SET BT PAGEMODE 1 2000 2    |      | 0.18    |      |

|                           | SET BT PAGEMODE 2 2000 0    |      | 23.5    |      |

| Sleep                     | SET BT PAGEMODE 2 2000 1    |      | 0.31    |      |

| ·                         | SET BT PAGEMODE 2 2000 2    |      | 0.19    |      |

|                           | SET BT PAGEMODE 3 2000 0    |      | 23      |      |

|                           | SET BT PAGEMODE 3 2000 1    |      | 0.4     | mA   |

|                           | SET BT PAGEMODE 3 2000 2    | 32   | 0.29    |      |

|                           | SET BT PAGEMODE 4 2000 0    |      | 23      |      |

|                           | SET BT PAGEMODE 4 2000 1    |      | 0.4     |      |

|                           | SET BT PAGEMODE 4 2000 2    |      | 0.29    |      |

| Connected, Sniff disabled | SET BT SNIFF 0 20 1 8       |      | 4.7     |      |

| Connected + Sniff, Master | SET BT SNIFF 40 20 1 8      |      | 3.9     |      |

| Connected + Sniff, Master | SET BT SNIFF 1000 20 1 8    |      | 2.5     |      |

| Connected + Sniff, Slave  | ,                           |      | 3.6     |      |

| Connected + Sniff, Slave  | SET BT SNIFF 1000 20 1 8    |      | 2.5     |      |

| A2DP Audio Streaming      | A2DP SINK, INTERNAL CODEC   | 75   | 28      |      |

| A2DP Audio Streaming      | A2DP SOURCE, INTERNAL CODEC | 70   | 23      | mA   |

Table 12: Current consumption of WT32i

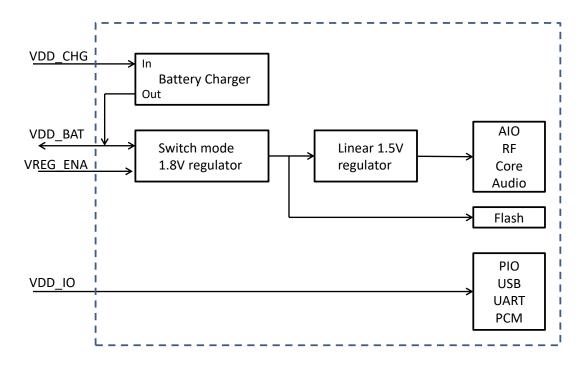

# 6 Power Control and Regulation

WT32i contains an internal battery charger and a switch mode regulator that is mainly used for internal blocks of the module. The module can be powered from a single 3.3 V supply provided that VDD\_CHG is floating. Alternatively the module can be powered from a battery connected to VDD\_BAT and using an external regulator for VDD\_IO. 1.8 V to 3.3 V supply voltage for VDD\_IO can be used to give desired signal levels for the digital interfaces of the module. USB, however, requires 3.3 V for proper operation and thus, when USB is in use, 3.3 V for VDD\_IO is required.

Figure 8: Power supply configuration of WT32i

VDD\_ENA is software configurable enable pin for the internal regulators. Using iWRAP the enable pin can be configured to

- 1. Latch on the internal regulators at the rising edge

- 2. Turn the regulators on at rising edge and turn off the regulators at falling edge

- 3. Latch the regulators on at the rising edge and turn off the regulators at the following rising edge

GPIO can be configured to control an external regulator.

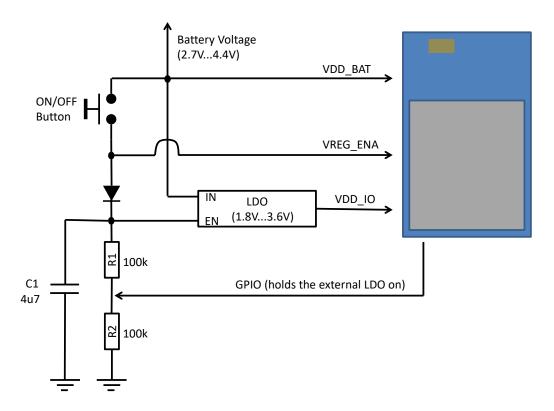

Figure 9: Example of making a power on/off button using the latch feature of the internal regulators

iWRAP Example: Creating an on/off button with PIO2 holding the external regulator on "SET CONTROL VREGEN 2 4"

(PIO is defined with a bit mask. 4 in hexadecimal is 100 in binary corresponding to PIO2)

**NOTE:** With the configuration shown above, when doing a SW reset for the module C1 will hold the enable pin of the external regulator high until iWRAP has booted. This will prevent the module from turning off during reset. When resetting through the reset pin one has to make sure that the enable pin is held high as long as the reset pin is held active.

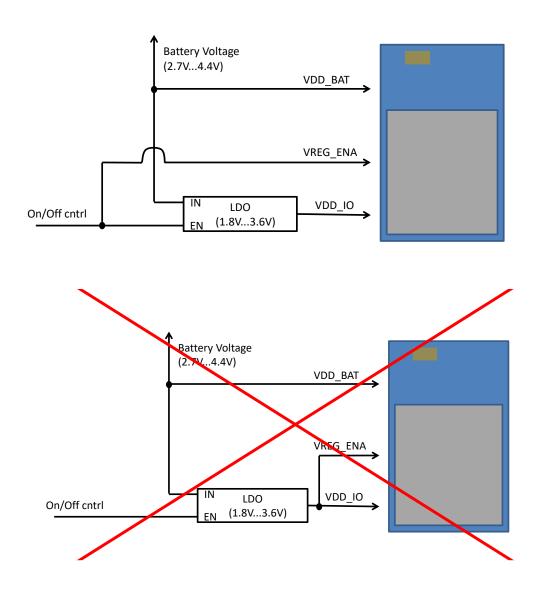

Figure 10 shows an example how to arrange power control when on/off button is not implemented. VREG\_ENA pin must not be connected to VDD\_IO because leakage from VDD\_BAT to VDD\_IO will prevent VREG\_ENA to fall low enough to turn off the internal regulators.

Figure 10: Correct and wrong connection for the power on/off control

# 6.1 Protecting the Battery by Configuring the Module to Turn Off at Certain Voltage

It is important not to let the battery be drained to voltages below 2.8V. In iWRAP it is possible to define certain level when the module turns off the regulators.

iWRAP Example: Configure WT32i to start sending low battery warning at 3.4V, turn off at 3.3V and cease the low battery warning at 4.0V. Set PIO0 to indicate low batter

"SET CONTROL BATTERY 3400 3300 4000 10"

# 6.2 Reset

WT32i may be reset from several sources: reset pin, power on reset, a UART break character or through software configured watchdog timer.

At reset, the digital I/O pins are set to inputs for bi-directional pins and outputs are tri-state.

The chip status after a reset is as follows:

- Warm Reset: data rate and RAM data remain available

- Cold Reset: data rate and RAM data are not available

Table 13 shows the pin states of WT32i on reset. Pull-up (PU) and pull-down (PD) default to weak values unless specified otherwise.

| Pin Name / Group | I/O Type                          | No Core Voltage<br>Reset | Full Chip Reset |  |

|------------------|-----------------------------------|--------------------------|-----------------|--|

| USB              | Digital bi-directional            | N/A                      | N/A             |  |

| UART_RX          | Digital input with PD             | PD                       | PD              |  |

| UART_CTS         | Digital input with FD             | FD                       |                 |  |

| UART_TX          | Digital output with PU            | PU                       | PU              |  |

| UART_RTS         | Digital output with Po            | PU                       | PU              |  |

| SPI_MOSI         | Digital input with PD             |                          |                 |  |

| SPI_CLK          | Digital input with FD             | PD                       | PD              |  |

| SPI_MISO         | Digital tristate output with PD   | 1.5                      |                 |  |

| SPI_CS           | Digital input with PU             | PU                       | PU              |  |

| PCM_IN           | Digital input with PD             |                          |                 |  |

| PCM_CLK          | Digital bi-directional with PD    |                          |                 |  |

| PCM_SYNC         | Digital bi-directional with FD    | PD                       | PD              |  |

| PCM_OUT          | Digital tri-state output with PD  |                          |                 |  |

| GPIO             | Digital bi-directional with PU/PD | PD                       | PD              |  |

Table 13: Pin states on reset

# 6.2.1 Internal POR

WT32i has two internal POR circuits. One is internally to the BC5 chip. In BC5 the power on reset occurs when the core supply voltage (output of the internal 1.5V regulator) falls below typically 1.26V and is released when VDD\_CORE rises above typically 1.31V.

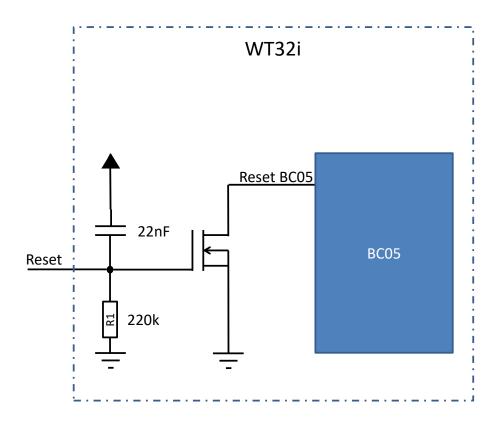

Another POR circuit is embedded to the module and it keeps the module in reset until supply voltages have stabilized. This is to prevent corruption of the internal flash memory during boot. The embedded POR is shown in the figure Figure 2Figure 11.

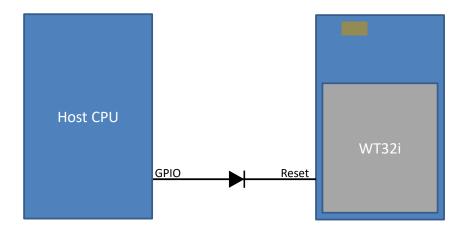

Because the POR is based on a simple RC time constant it will not work if the supply voltage ramps very slowly or if the reset pin is not connected to high impedance. It is recommended that the power ramp will not take more than 10 msec. If the reset pin is connected to a host it is good to place a diode between the host and the module as shown in Figure 12. A diode will prevent the host from pulling the reset low before the internal flash has its supply stabilized.

Figure 11: Embedded POR of WT32i

Figure 12: An example how to connect CPU GPIO to the reset pin of the module

# 7 Battery Charger

The battery charger is a constant current / constant voltage charger circuit, and is suitable for lithium ion/polymer batteries only. It shares a connection to the battery terminal, VDD\_BAT, with the switch-mode regulator. The charger is initially calibrated by Bluegiga Technologies to have  $V_{float} = 4.15V - 4.2 V$ .

The constant current level can be varied to allow charging of different capacity batteries. WT32i allows a number of different currents to be used in the battery charger hardware. Values written to PS key 0x039b CHARGER\_CURRENT in the range 1..15 specify the charger current from 40..135mA in even steps. Values outside the valid 0..15 range result in no change to the charging current. The default charging current (Key = 0) is nominally 40mA. Setting 0 is interpreted as "no-change" so it will be ignored

The charger enters various states of operation as it charges a battery. These are shown below:

- Off: entered when the charger is disconnected.

- Trickle Charge: entered when the battery voltage is below 2.9V.

- Fast Charge Constant Current: entered when the battery voltage is above 2.9V.

- Fast Charge Constant Voltage: entered when the battery has reached V<sub>float</sub>, the charger switches mode to maintain the cell voltage at V<sub>float</sub> voltage by adjusting the constant charge current.

- Standby: this is the state when the battery is fully charged and no charging takes place.

When a voltage is applied to the charger input terminal VDD\_CHG, and the battery is not fully charged, the charger will operate and a LED connected to the terminal LED0 will illuminate. By default, until the firmware is running, the LED will pulse at a low-duty cycle to minimize current consumption.

The battery charger circuitry auto-detects the presence of a power source, allowing the firmware to detect when the charger is powered. Therefore, when the charger supply is not connected to VDD\_CHG, the terminal must be left open circuit. The VDD\_CHG pin, when not connected, must be allowed to float and not be pulled to a power rail. When the battery charger is not enabled, this pin may float to a low undefined voltage. Any DC connection will increase current consumption of the device. Capacitive components such as diodes, FETs, and ESD protection, may be connected.

The battery charger is designed to operate with a permanently connected battery. If the application permits the charger input to be connected while the battery is disconnected, the VDD\_BAT pin voltage may become unstable. This, in turn, may cause damage to the internal switch-mode regulator. Connecting a 470µF capacitor to VDD\_BAT limits these oscillations thus preventing damage.

#### **WARNING:**

Use good consideration for battery safety. Do not charge with too much current. Do not charge when the temperature is above 60°C or below 0°C. WT32i is initially calibrated to stop charging when battery voltage is at 4.2 V. Do not try to charge batteries above 4.2 V. Do not short circuit the battery or discharge below 1.5 V.

# 8 GPIO and AIO Functions

# 8.1 iWRAP supported GPIO Functions

Various GPIO functions are supported by iWRAP. These include:

- Setting each GPIO state individually

- Binding certain iWRAP commands to GPIO to trigger the command at either the rising or falling edge

of the GPIO

- Carrier detect signal to indicate an active Bluetooth connection

- Implementing RS232 modem signals

- iWRAP ready indicator to signal to a host that iWRAP is ready to use

- UART bypass mode to route UART signals to GPIO pins instead of iWRAP

- Driving low frequency pulsed signal from a GPIO

Some of the functions are FW dependent. Refer to latest iWRAP user manual for the detailed information about the GPIO functions.

# 8.2 Outputting Internal Clocks

Internal clocks can be routed to either AIO0 or AIO1 by setting PS Keys. To route internal clock to AIO0 set PSKEY\_AMUX\_AIO0 to 0x00fe. Following table shows how to set the PSKEY\_AMUX\_CLOCK to get certain frequency from AIO0.

| AMUX_CLOCK | Freq (MHz) @ AlO0 |

|------------|-------------------|

| 0x0014     | 1                 |

| 0x0004     | 2                 |

| 0x0013     | 3                 |

| 0x0017     | 4                 |

| 0x0003     | 6                 |

| 0x0016     | 6.5               |

| 0x0007     | 8                 |

| 0x0011     | 12                |

| 0x0006     | 13                |

| 0x0002     | 16                |

| 0x0009     | 24                |

| 0x0005     | 32                |

Table 14: Selectable internal clock frequencies from AlO0

iWRAP does not support this feature. To use this feature either the particular PS Keys must be set to each module separately or then ask for custom FW from Bluegiga.

# 8.3 Auxiliary ADC

Simple iWRAP command can be used to read the ADC output from either of the two AIO pins. Refer to latest iWRAP user manual for the detailed information.

# 8.4 Software I2C Interface

PIO6 and PIO7 can be used to form a master I<sup>2</sup>C interface. The interface is formed using software to drive these lines. Therefore it is suited only to relatively slow functions such as driving a dot matrix LCD, keyboard scanner or configuring external audio codec. I<sup>2</sup>C interface requires a custom FW.

| PIO  | I2C Signal |

|------|------------|

| PIO6 | SCL        |

| PIO7 | SDA        |

Table 15: I2C Interface of WT32i

# 9 Serial Interfaces

# 9.1 UART Interface

WT32i has a standard UART serial interface that provides a simple mechanism for communicating with other serial devices using the RS232 protocol. UART configuration parameters, such as baud rate, parity and stop bits can be configured with an iWRAP command.

The hardware flow control is enabled by default. HW flow control can be disabled in HW by connecting UART\_NCTS to GND and leaving UART\_NRTS floating.

| Parameter           |                   | Possible Values      |

|---------------------|-------------------|----------------------|

|                     | N disaissa a sasa | 1200 baud (≤2%Error) |

| Baud rate           | Minimum           | 9600 (≤1%Error)      |

|                     | Maximum           | 4Mbaud (≤1%Error)    |

| Flow control        |                   | RTS/CTS or None      |

| Parity              |                   | None, Odd, Even      |

| Number of stop bits | 1 or 2            |                      |

| Bits per byte       |                   | 8                    |

**Table 16: Possible UART settings**

iWRAP Example: Configuring local UART to 9600bps, 8 data bits, no parity and 1 stop bit

SET CONTROL BAUD 9600, 8N1

(9600 = baud rate, N = No parity, 1 = 1 stop bit)

| Baud Rate | Error  |

|-----------|--------|

| 1200      | 1.73%  |

| 2400      | 1.73%  |

| 4800      | 1.73%  |

| 9600      | -0.82% |

| 19200     | 0.45%  |

| 38400     | -0.18% |

| 57600     | 0.03%  |

| 76800     | 0.14%  |

| 115200    | 0.03%  |

| 230400    | 0.03%  |

| 460800    | -0.02% |

| 921600    | 0.00%  |

| 1382400   | -0.01% |

| 1843200   | 0.00%  |

| 2764800   | 0.00%  |

| 3686400   | 0.00%  |

**Table 17: Standard Baud Rates**

# 9.1.1 Resetting Through UART Break Signal

The UART interface can reset WT32i on reception of a break signal. A break is identified by a continuous logic low (0V) on the UART\_RX terminal. If tbrk is longer than the value (in microseconds), defined by PSKEY\_HOSTIO\_UART\_RESET\_TIMEOUT, (0x1a4), a reset occurs. Values below 1000 are treated as zero and values above 255000 are truncated to 255000. This feature allows a host to initialise the system to a known state. Also, WT32i can emit a break character that may be used to wake the host.

Default PSKEY\_HOSTIO\_UART\_RESET\_TIMEOUT setting in WT32i is zero, which means that this feature is disabled. To use this feature, either the PS setting has to be changed for each module separately or ask for modules with custom FW with appropriate settings.

# 9.1.2 UART Configuration While Reset is Active

The UART interface for WT32i is tristate while the chip is being held in reset. This allows the user to daisy chain devices onto the physical UART bus. The constraint on this method is that any devices connected to this bus must tristate when WT32i reset is de-asserted and the firmware begins to run.

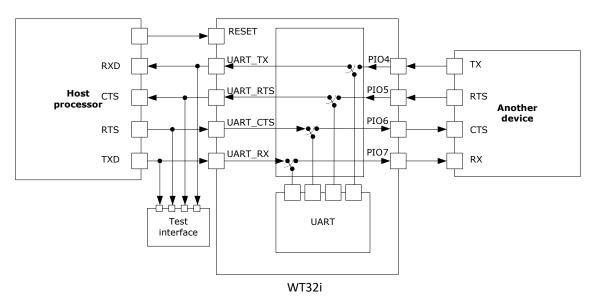

# 9.1.3 UART Bypass Mode

Alternatively, for devices that do not tristate the UART bus, the UART bypass mode on WT32i can be used. The default state of WT32i after reset is de-asserted; this is for the host UART bus to be connected to the WT32i UART, thereby allowing communication to WT32i via the UART. All UART bypass mode connections are implemented using CMOS technology and have signalling levels of 0V and VDD\_IO.

The bypass mode is enabled with a simple iWRAP command. When in bypass mode, the module is automatically set into deep sleep state indefinitely. Physical reset is required to return to normal operation mode. The current consumption of a module in bypass mode is equal to a module in standby (idle) mode.

It is important for the host to ensure a clean Bluetooth disconnection of any active links before the bypass mode is invoked. Therefore, it is not possible to have active Bluetooth links while operating the bypass mode.

Figure 13: UART bypass architecture

# 9.2 USB Interface

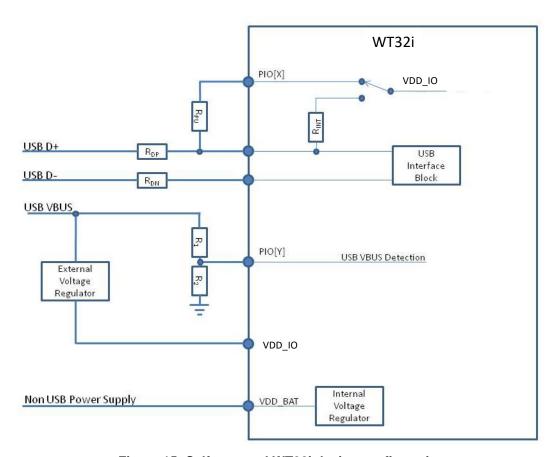

WT32i has a full-speed (12Mbps) USB interface for communicating with other compatible digital devices. The USB interface on WT32i acts as an USB peripheral, responding to requests from a master host controller. WT32i can be used as bus-powered or self-powered device. See the WT\_USB\_Design\_Guide available in the Bluegiga techforum for details about the SW and HW configuration of the USB interface.

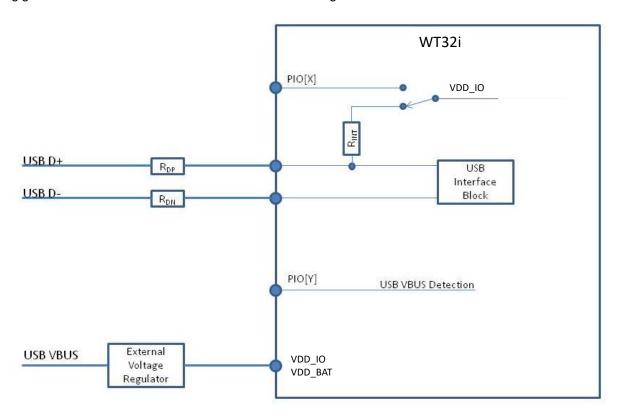

Figure 14: Bus-powered WT32i device configuration

Figure 15: Self powered WT32i device configuration

# 9.3 Programming and Debug Interface (SPI)

The synchronous serial port interface (SPI) is for interfacing with other digital devices. The SPI port can be used for system debugging. It can also be used for programming the Flash memory. SPI interface is connected by using the MOSI, MISO, CSB and CLK pins.

SPI interface cannot be used for any application purposes.

# 9.3.1 Multi-slave Operation

WT32i should not be connected in a multi-slave arrangement by simple parallel connection of slave MISO lines. When WT32i is deselected (SPI\_CS# = 1), the SPI\_MISO line does not float. Instead, WT32i outputs 0 if the processor is running or 1 if it is stopped.

# 10 Audio Interfaces

### 10.1 Stereo Audio Codec Interface

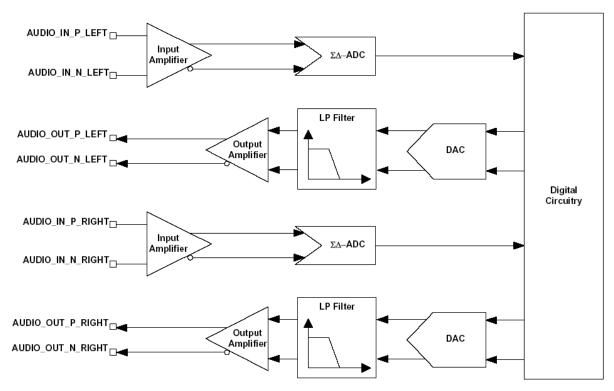

Stereo audio CODEC operates from an internal 1.5V power supply. It uses fully differential architecture in analog signal path for the best possible common mode noise rejection while effectively doubling the signal amplitude.

The stereo audio bus standard I2S is supported and a software I2C interface can be implemented using GPIOs to configure an external audio CODEC.

Figure 16: Stereo CODEC input and output stages

#### 10.1.1 ADC

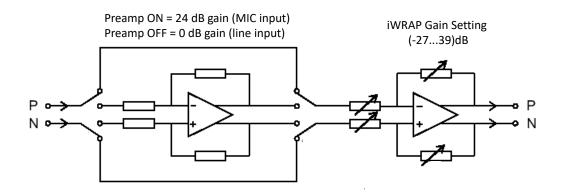

The ADC consists of two second-order sigma-delta converters and gain stages. The gain stage consists of digital and analog gain stages which are controlled by iWRAP. The optimal combination of digital and analog gain is automatically selected by iWRAP. The analog gain stage consist selectable 24 dB preamplifier for selecting microphone or line input levels and an amplifier which can be configured in 3 dB steps. The iWRAP gain selection values are shown in the Table 19.

Following sample rates are supported

- 8kHz

- 11.025kHz

- 16kHz

- 22.05kHz

- 24kHz

- 32kHz

- 44.1kHz

Table 18: ADC amplifier block diagram

| Gain Setting In iWRAP | ADC Gain (dB) Preamp OFF (Line input mode) | ADC GAIN (dB) Preamp ON (MIC input mode) |

|-----------------------|--------------------------------------------|------------------------------------------|

| 0                     | -27                                        | -3                                       |

| 1                     | -24                                        | 0                                        |

| 2                     | -21                                        | 3                                        |

| 3                     | -18                                        | 6                                        |

| 4                     | -15                                        | 9                                        |

| 5                     | -12                                        | 12                                       |

| 6                     | -9                                         | 15                                       |

| 7                     | -6                                         | 18                                       |

| 8                     | -3                                         | 21                                       |

| 9                     | 0                                          | 24                                       |

| A                     | 3                                          | 27                                       |

| В                     | 6                                          | 30                                       |

| С                     | 9                                          | 33                                       |

| D                     | 12                                         | 36                                       |

| E                     | 15                                         | 39                                       |

| F                     | 18                                         | 42                                       |

| 10                    | 21                                         | 45                                       |

| 11                    | 24                                         | 48                                       |

| 12                    | 27                                         | 51                                       |

| 13                    | 30                                         | 54                                       |

| 14                    | 33                                         | 57                                       |

| 15                    | 36                                         | 60                                       |

| 16                    | 39                                         | 63                                       |

Table 19: ADC Gain Selection In iWRAP

iWRAP Example: Setting line input with 0 dB gain

"SET CONTROL PREAMP 0"

"SET CONTROL GAIN 9 x" (x is the DAC gain)

#### 10.1.2 DAC

The DAC consists of two second-order sigma-delta converters and gain stages. The gain stage consists of digital and analog gain stages which are controlled by iWRAP. The optimal combination of digital and analog gain is automatically selected by iWRAP. The analog gain stage consist selectable 24 dB preamplifier for selecting microphone or line input levels and an amplifier which can be configured in 3 dB steps. The iWRAP gain selection values are shown in Table 20.

Following sample rates are supported

- 8kHz

- 11.025kHz

- 16kHz

- 22.05kHz

- 24kHz

- 32kHz

- 44.1kHz

- 48kHz

| Gain Setting In iWRAP | DAC Gain (dB) |

|-----------------------|---------------|

| 0                     | -42           |

| 1                     | -39           |

| 2                     | -36           |

| 3                     | -33           |

| 4                     | -30           |

| 5                     | -27           |

| 6                     | -24           |

| 7                     | -21           |

| 8                     | -18           |

| 9                     | -15           |

| A                     | -12           |

| В                     | -9            |

| С                     | -6            |

| D                     | -3            |

| E                     | 0             |

| F                     | 3             |

| 10                    | 6             |

| 11                    | 9             |

| 12                    | 12            |

| 13                    | 15            |

| 14                    | 18            |

| 15                    | 21            |

| 16                    | 24            |

Table 20: DAC gain selection in iWRAP

iWRAP Example: Setting output with 0 dB gain

"SET CONTROL GAIN x E" (x is the ADC gain)

# 10.1.3 Microphone Input

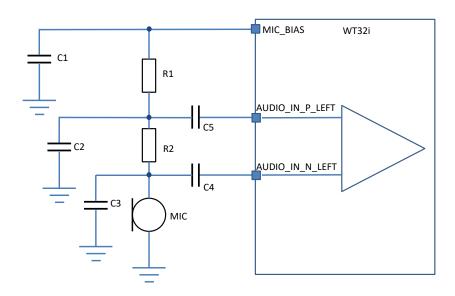

Figure 17 shows the recommended microphone biasing. The microphone bias, MIC\_BIAS, derives its power from the VDD BAT and requires 1uF capacitor on its output (C1).

The input impedance at AUDIO\_IN\_P\_LEFT and AUDIO\_IN\_N\_LEFT is typically 6kohm and C5 and C4 are typically 1uF. If bass roll-off is required to limit the wind noise on the microphone then C4 and C5 should be 150 nF.

R2 sets the microphone load impedance and is normally in the range of  $1k\Omega$  to  $2k\Omega$

R1, C2 and C3 improve the supply rejection by decoupling supply noise from the microphone. Values should be selected as required. R1 can be connected or to the MIC\_BIAS output (which is ground referenced and provides good rejection of the supply) as shown in Figure 17. MIC\_BIAS is configured to provide bias only when the microphone is required. R1 may also be connected to a convenient supply, in which case the bias network is permanently enabled.

Figure 17: Microphone connection to audio input

The MIC\_BIAS is like any voltage regulator and requires a minimum load to maintain regulation. The MIC\_BIAS maintains regulation within the limits 0.200mA to 1.230mA. If the microphone sits below these limits, then the microphone output must be pre-loaded with a large value resistor to ground.

The audio input is intended for use in the range from  $1\mu A$  @ 94dB SPL to about  $10\mu A$  @ 94dB SPL. With biasing resistors R1 and R2 equal to  $1k\Omega$ , this requires microphones with sensitivity between about -40dBV and -60dBV.

| Table 21 lists the | possible voltage and | d current setting in iWRA | P for the MIC BIAS. |

|--------------------|----------------------|---------------------------|---------------------|

|                    |                      |                           |                     |

| Setting in iWRAP | Voltage (V) | Current (mA) |

|------------------|-------------|--------------|

| 0                | 1.71        | 0.200        |

| 1                | 1.76        | 0.280        |

| 2                | 1.82        | 0.340        |

| 3                | 1.87        | 0.420        |

| 4                | 1.95        | 0.480        |

| 5                | 2.02        | 0.530        |

| 6 | 2.10 | 0.610 |

|---|------|-------|

| 7 | 2.18 | 0.670 |

| 8 | 2.32 | 0.750 |

| 9 | 2.43 | 0.810 |

| A | 2.56 | 0.860 |

| В | 2.69 | 0.950 |

| С | 2.90 | 1.000 |

| D | 3.08 | 1.090 |

| E | 3.33 | 1.140 |

| F | 3.57 | 1.230 |

Table 21: MIC\_BIAS settings in iWRAP

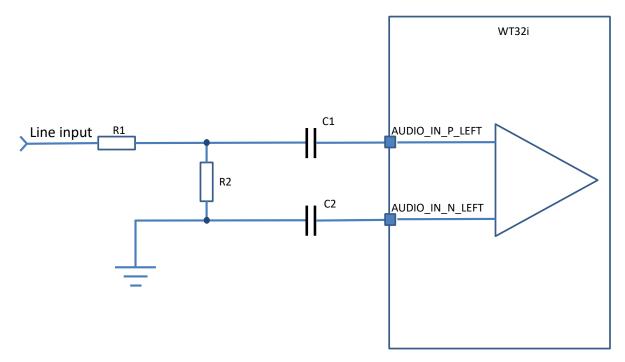

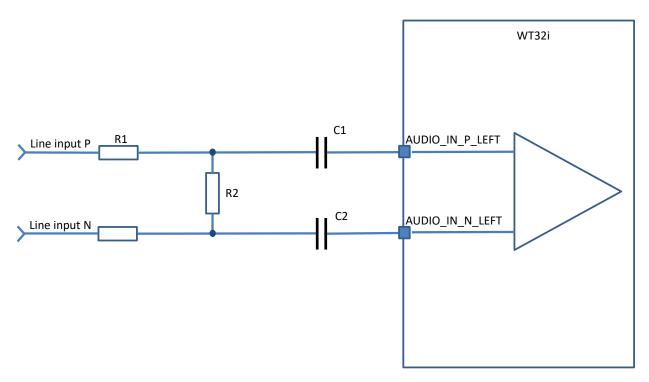

### 10.1.4 Line Input

Line input mode is selected by setting the ADC preamplifier off (see chapter 10.1.1). In the line input mode the input impedance varies from 6k to 30 kohm depending on the gain setting.

Figure 18 and Figure 19 show examples of line input connection with WT32i. The maximum line level rms voltage can vary from 0.3 up to 1.6 Vrms depending on the application, while the maximum for WT32i is 0.4Vrms (0.8Vrms differential). Thus it may be necessary to use a voltage divider (R1 and R2) at the input to attenuate the incoming signal. C1 and C2 are typically 1uF ceramic X7R or film type capacitors.

It is a good practice to place a LC (22nH + 15pF) filter close to each input to filter out any RF noise that might couple to the audio traces.

Figure 18: Single ended line input example

Figure 19: Differential line input example

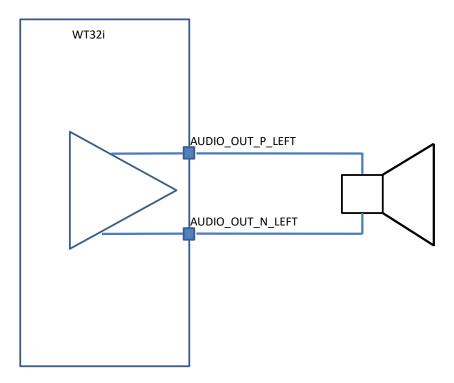

### 10.1.5 Output Stage

The output stage digital circuitry converts the signal from 16-bit per sample, linear PCM of variable sampling frequency to bit stream, which is fed into the analogue output circuitry. The output stage circuit comprises a DAC with gain setting and class AB output stage amplifier.

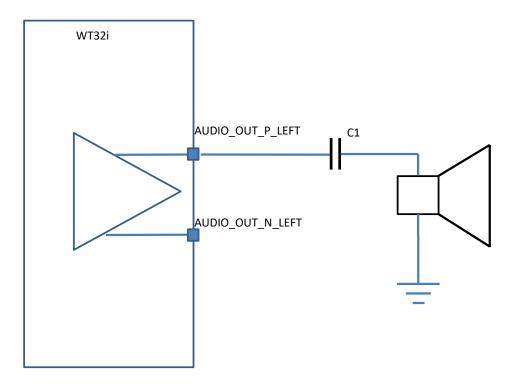

The output is available as a differential signal between AUDIO\_OUT\_N\_LEFT and AUDIO\_OUT\_P\_LEFT for left channel and AUDIO\_OUT\_N\_RIGHT and AUDIO\_OUT\_P\_RIGHT for right channel.

The output stage is capable of driving a speaker directly when its impedance is at least  $16\Omega$ .

Figure 20 show an example of differentially connected speaker and Figure 21 show an example of speaker connected single-ended. Differential (balanced) connection provides perfect common mode rejection ratio with effectively 3 dB higher amplitude so it is recommended to use differential signaling always when possible.

Figure 20: Differentially connected speaker

Figure 21: Single-ended speaker connection

### 10.1.6 Mono Operation

Mono operation is a single-channel operation of the stereo codec. The left channel represents the single mono channel for audio in and audio out. In mono operation the right channel is the auxiliary mono channel that may be used in dual mono channel operation. Dual mono feature is FW dependent and iWRAP does not generally support it.

#### 10.1.7 Side Tone

In some applications it is necessary to implement side tone. This involves feeding an attenuated version of the microphone signal to the earpiece. The WT32i codec contains side tone circuitry to do this. There is no iWRAP support for the side tone but the side tone is configurable through PS Keys. To implement a side tone, either the PS setting has to be programmed for each module separately or ask for modules with custom FW with appropriate settings.

The side tone hardware is configured through the following PS Keys:

- PSKEY\_SIDE\_TONE\_ENABLE

- PSKEY SIDE TONE GAIN

- PSKEY\_SIDE\_TONE\_AFTER\_ADC

- PSKEY\_SIDE\_TONE\_AFTER\_DAC

### 10.2 PCM Interface

The audio PCM interface supports continuous transmission and reception of PCM encoded audio data over Bluetooth.

PCM is a standard method used to digitise audio, particularly voice, for transmission over digital communication channels. Through its PCM interface, WT32i has hardware support for continual transmission and reception of PCM data, so reducing processor overhead. WT32i offers a bidirectional digital audio interface that routes directly into the baseband layer of the on-chip firmware. It does not pass through the HCl protocol layer.

Hardware on WT32i allows the data to be sent to and received from a SCO connection.

Using HCI FW up to 3 SCO connections can be supported by the PCM interface at any one time. However iWRAP supports only 1 SCO connection at a time.

WT32i can operate as the PCM interface master generating PCM\_SYNC and PCM\_CLK or as a PCM interface slave accepting externally generated PCM\_SYNC and PCM\_CLK. WT32i is compatible with various clock formats, including Long Frame Sync, Short Frame Sync and GCI timing environments.

WT32i supports 13-bit or 16-bit linear, 8-bit  $\mu$ -law or A-law companded sample formats, and can receive and transmit on any selection of 3 of the first four slots following PCM\_SYNC. The PCM configuration options are enabled by setting the PS Key PSKEY\_PCM\_CONFIG32. Please contact Bluegiga technical support for details about the PCM configuration.

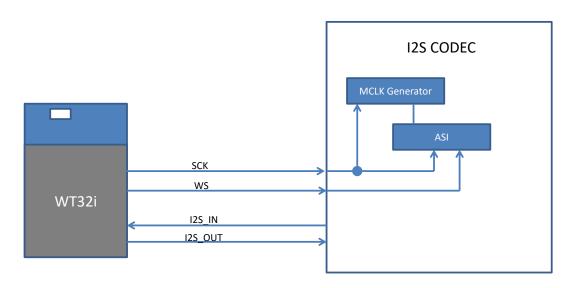

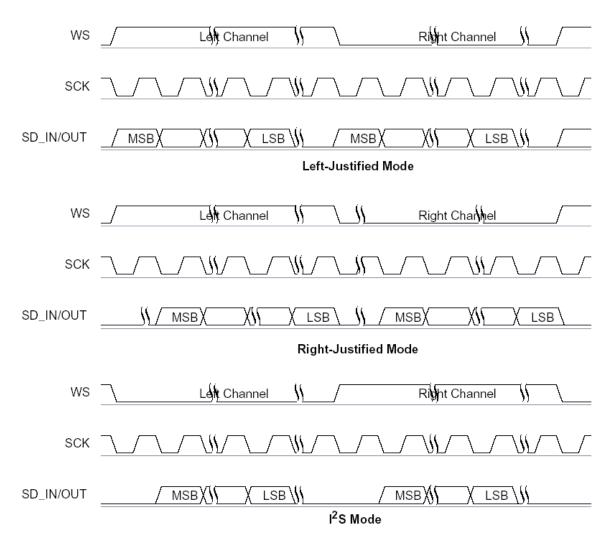

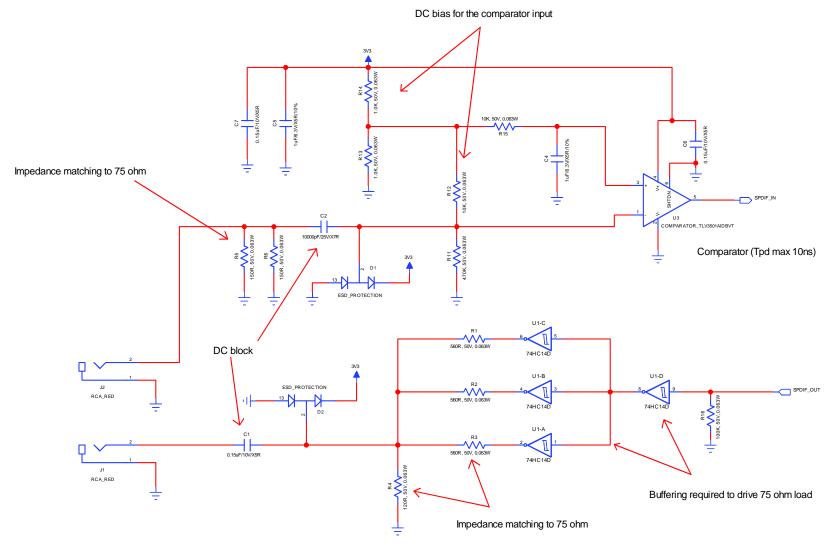

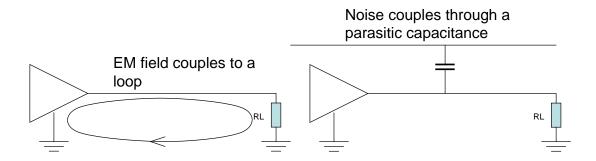

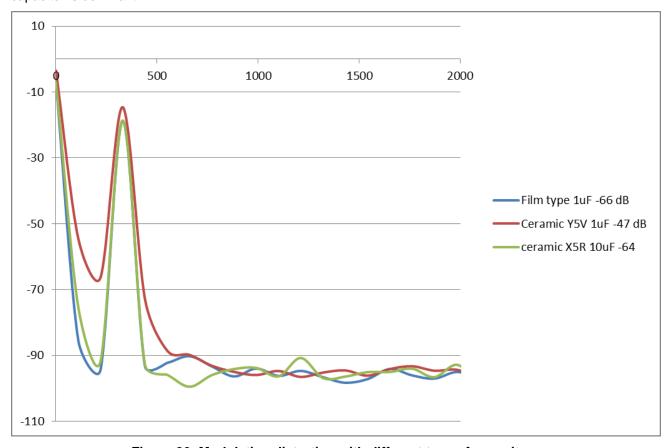

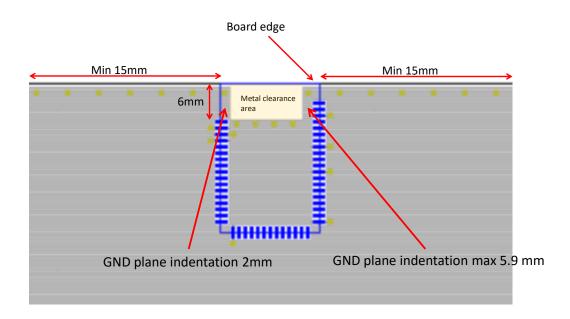

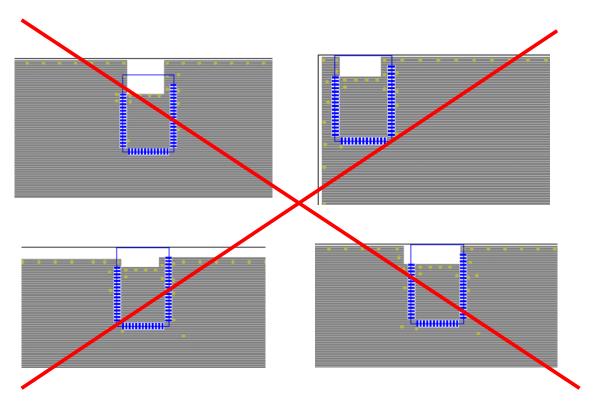

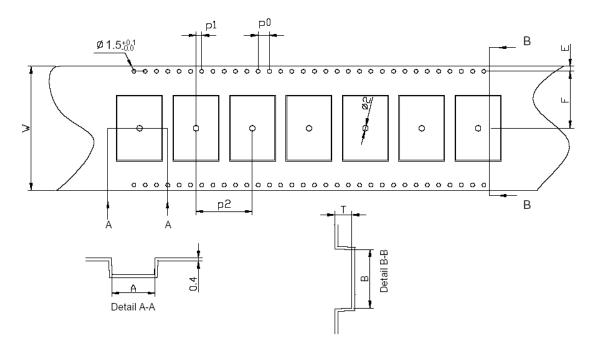

#### 10.3 I2S Interface