## INTEGRATED 100-V IEEE 802.3af PD AND DC/DC CONTROLLER

#### **FEATURES**

- Complete 802.3af PoE Interface

- Features derived from the TPS2375

- 100 V, 0.6 Ω Internal Pass MOSFET

- Standard and Legacy UVLO Choices

- Fixed 140 mA Inrush Limit

- Primary Side DC/DC Converter Control

- Minimum External Component Count

- Current Mode Control

- Isolated and Non-Isolated Topologies

- Programmable Operating Frequency

- Current Sense Leading-edge Blanking

- 50% Duty Cycle Limiting

- Voltage Output Error Amplifier

- Internal PoE and Converter Sequencing

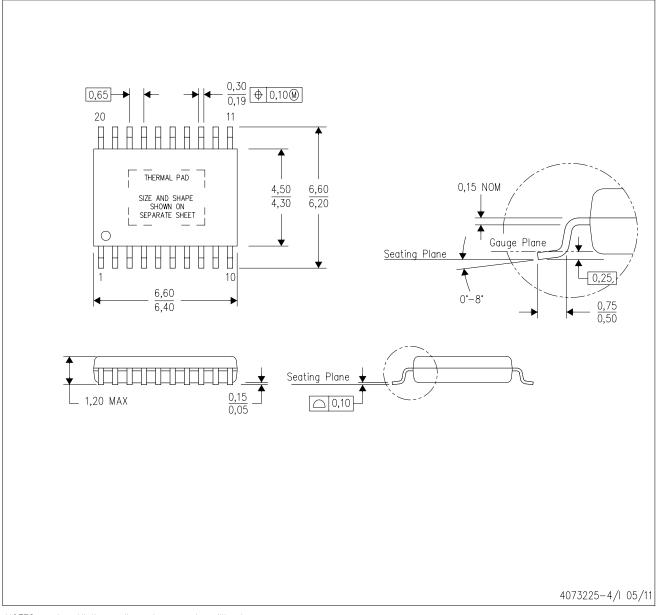

- Industry-Standard 20 Lead Package

- Industrial Temperature Range: –40°C to 85°C

### **APPLICATIONS**

- All PoE PD Devices Including:

- Wireless Access Points

- VoIP Phones

- Security Cameras

### DESCRIPTION

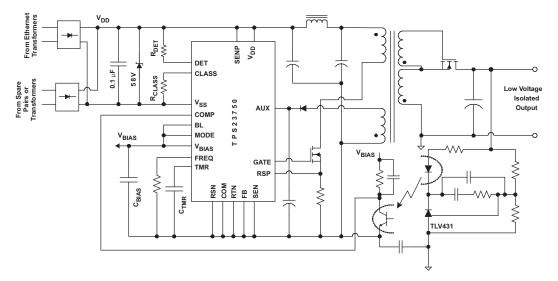

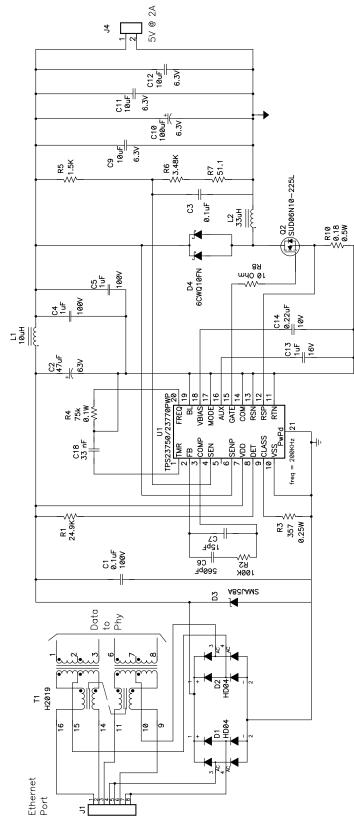

The TPS23750 integrates the functionality of the TPS2375 with a primary-side dc/dc PWM controller. The designer can create a front-end solution for PoE-PD applications with minimum external components. The TPS23770 is identical to the TPS23750 with the exception of the undervoltage lockout turn-on voltage, which is compatible with legacy systems.

The PoE front end has all the necessary IEEE 802.3af functions including detection, classification, undervoltage lockout and inrush control. The PoE input switch is integrated within the TPS23750.

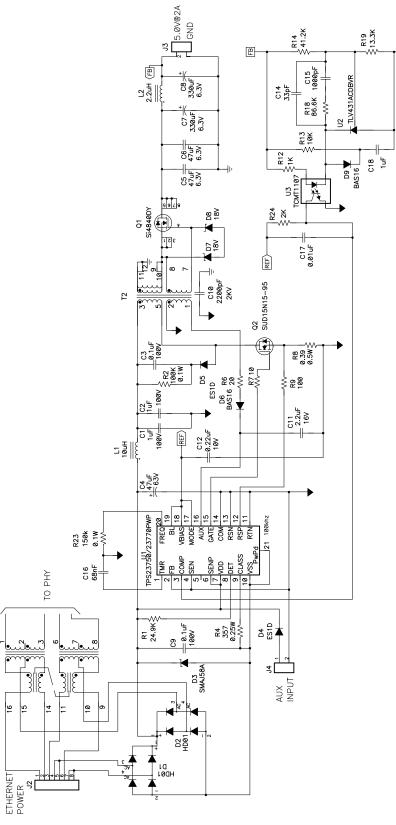

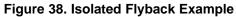

The dc/dc controller section is designed to support flyback, forward, and nonsynchronous low-side switch buck topologies.

The external switching MOSFET and current sense resistor provide flexibility in topology, power level, and current limit. The full-featured dc/dc controller includes programmable soft start, hiccup type fault limiting, 50% maximum duty cycle, programmable constant switching frequency, and a true voltage-output error amplifier. Additional protection features provide for robust designs.

**Figure 1. Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

#### **TPS23750 TPS23770** SLVS590B-JULY 2005-REVISED FEBRUARY 2008

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

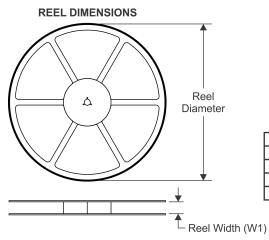

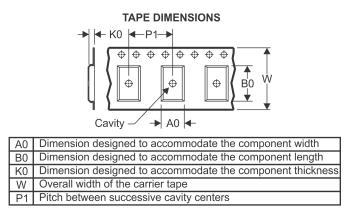

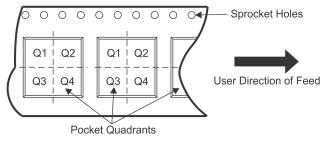

#### ORDERING INFORMATION<sup>(1)</sup>

| т             | UVLO THRESHOLDS |        |        | PACKAGE <sup>(2)</sup> | MARKING  |

|---------------|-----------------|--------|--------|------------------------|----------|

| I A           | TYPE            | LOW    | HIGH   | TSSOP-20 PowerPAD™     | WARKING  |

| -40°C to 85°C | Standard        | 30.5 V | 39.3 V | TPS23750PWP            | TPS23750 |

| -40 0 10 85 0 | Legacy          | 30.5 V | 35.1 V | TPS23770PWP            | TPS23770 |

(1) Add an R suffix to the device type for tape and reel.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range and with respect to V<sub>SS</sub> unless otherwise noted<sup>(1)</sup>

|                   |                                          |                                                                 | UNIT                         |

|-------------------|------------------------------------------|-----------------------------------------------------------------|------------------------------|

|                   | Input voltage range <sup>(2)</sup>       | RSN, COM, RTN, SEN                                              | -0.7 V to 100 V              |

|                   | Input voltage range                      | AUX, VDD, DET, SENP                                             | –0.3 V to 100 V              |

|                   | Input voltage range <sup>(3)</sup>       | [V <sub>BIAS</sub> , BL, TMR, FB, COMP, FREQ, RSP, MODE] to RTN | –0.3 V to 6.5 V              |

|                   | Input voltage range [GATE or AUX] to COM |                                                                 | –0.3 V to 20 V               |

|                   | Input voltage range                      | [RSN to RTN] and [COM to RTN]                                   | –0.3 V to 0.3 V              |

|                   |                                          | SENP to SEN                                                     | –0.3 V to 100 V              |

|                   | Input voltage range <sup>(3)</sup>       | CLASS                                                           | –0.3 V to 12 V               |

|                   | Sourcing current                         | AUX                                                             | Internally limited           |

| V <sub>BIAS</sub> | Sourcing current                         |                                                                 | Internally limited           |

|                   | Sourcing or sinking curre                | nt, COMP                                                        | Internally limited           |

|                   | Average sourcing or sink                 | ing current, GATE                                               | 25 mA <sub>rms</sub>         |

|                   | HBM ESD rating                           |                                                                 | 2 kV                         |

|                   | ESD – system level (cont                 | act/air) at RJ-45 <sup>(4)</sup>                                | 8 kV / 15 kV                 |

|                   | Continuous total power d                 | issipation                                                      | See Dissipation Rating Table |

| TJ                | Maximum operating junction temperature   |                                                                 | Internally limited           |

| T <sub>stg</sub>  | Storage temperature range                |                                                                 | –65°C to 150°C               |

|                   | Lead temperature 1.6mm                   | (1/16-inch) from case for 10 seconds                            | 260°C                        |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2)  $I_{RTN} = 0$  for  $V_{RTN} > 80$  V. Maximum  $I_{RTN} = 500$  mA at 80 V.

(3) Do not apply external voltage sources to CLASS, DET, GATE, FREQ, V<sub>BIAS</sub>, and TMR.

(4) Surges applied to RJ-45 of TPS23750EVM-107 between pins of RJ-45, and between pins and output voltage rails per EN61000-4-2, 1999 with no device failure.

### **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup> <sup>(2)</sup>

All voltage values are with respect to V<sub>SS</sub> unless otherwise noted.

|                 |                                    |                    | MIN  | NOM MAX           | UNIT |

|-----------------|------------------------------------|--------------------|------|-------------------|------|

| V <sub>DD</sub> | Input voltage range <sup>(3)</sup> | COM, SEN, SENP     | 0    | 67                | V    |

|                 |                                    | FB, COMP, MODE, BL | 0    | V <sub>BIAS</sub> |      |

|                 | Input voltage range                | AUX to COM         | 0    | 16                | V    |

|                 |                                    | RSP to RSN         | 0    | 1                 |      |

|                 |                                    | AUX                | 0    | 2                 |      |

|                 | Sourcing current                   | V <sub>BIAS</sub>  | 0    | 2                 | mA   |

|                 |                                    | COMP               | 0    | 2                 |      |

| Q <sub>G</sub>  | GATE loading                       |                    |      | 20                | nC   |

|                 | AUX load capacitance               |                    | 0.8  | 25                | μF   |

|                 | V <sub>BIAS</sub> load capacitance |                    | 0.08 | 1.5               | μF   |

|                 | R <sub>FREQ</sub>                  |                    | 30   | 300               | kΩ   |

| TJ              | Operating junction temperat        | ure range          | -40  | 125               | °C   |

| T <sub>A</sub>  | Operating ambient temperat         | ure range          | -40  | 85                | °C   |

(1) RSN, COM, and RTN should be tied together. SENP should be tied to V<sub>DD</sub> except for the buck configuration, where it should be tied to the output positive rail.

(2)

TMR, FREQ, CLASS, DET,  $V_{\text{BIAS}}$ , and GATE should not be externally driven. Junction temperature may be a constraining factor for high bias power designs. (3)

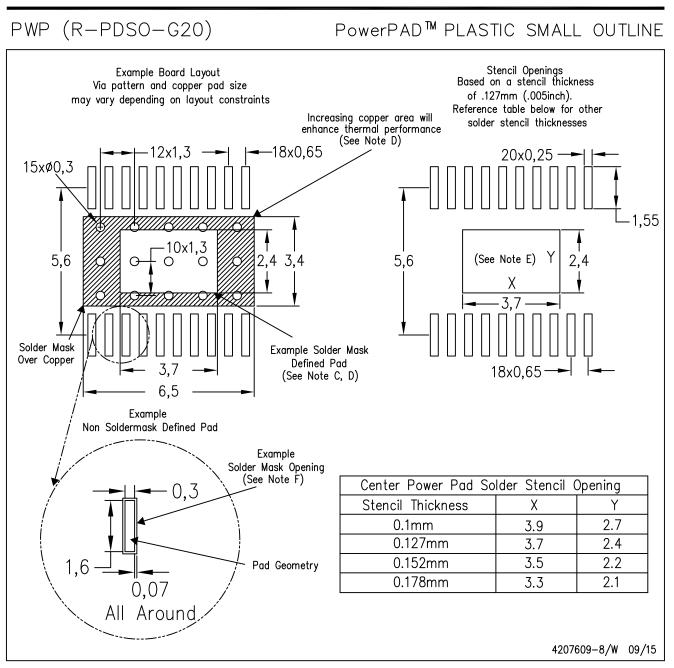

### **DISSIPATION RATINGS TABLE**

| PACKAGE        | °C/W <sup>(1)</sup> | °C/W  | °C/W <sup>(2)</sup> | °C/W <sup>(3)</sup> | °C/W <sup>(4)</sup> | MAXIMUM POWER RATING<br>(W) <sup>(5)</sup> |

|----------------|---------------------|-------|---------------------|---------------------|---------------------|--------------------------------------------|

| PWP (TSSOP-20) | 1.4                 | 26.62 | 32.6                | 151.9               | 73.8                | 1.2                                        |

Thermal resistance junction to pad. (1)

(2) See TI document SLMA002 for recommended layout. This is a best case, zero airflow number.

JEDEC method with low-k board (2 signal layers) and power pad not soldered (worst case). (3)

JEDEC method with high-k board (4 layers, 2 signal and 2 planes) and power pad not soldered. (4)

(5) Based on TI recommended layout and 85°C ambient.

3

TPS23750 TPS23770 SLVS590B-JULY 2005-REVISED FEBRUARY 2008

### **ELECTRICAL CHARACTERISTICS**

Characteristics are for: –40°C ≤  $T_J$  ≤ 125°C;  $V_{DD} - V_{SS}$  = 48 V.  $V_{DD}$ , CLASS, and DET referenced to  $V_{SS}$ , and all other pin voltages are referenced to RSN, COM, and RTN shorted together unless otherwise noted. SEN=MODE=BL=RSP=RTN, FB= $V_{BIAS}$ , SENP= $V_{DD}$ ,  $C_{TMR}$  = 1000 pF,  $C_{VBIAS}$  = 0.1  $\mu$ F,  $C_{VAUX}$  = 0.1  $\mu$ F,  $R_{FREQ}$  = 150 kΩ,  $R_{DET}$  = 24.9 kΩ,  $R_{CLASS}$  = 255 Ω, GATE is unloaded, and  $V_{BIAS}$  and AUX have no external loads unless otherwise noted.

### **DC/DC CONTROLLER SECTION**

$RTN = V_{SS}$  for this section only.

|                   | PARAMETER                         | TEST CONDITIONS                                                                                                                                                                                                                 | MIN   | TYP   | MAX   | UNIT |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| BIAS SUP          | PPLY (VBIAS)                      | - [                                                                                                                                                                                                                             |       |       |       |      |

| V <sub>BIAS</sub> | Output voltage                    | $0 \le I_{LOAD} \le 5 \text{ mA}$                                                                                                                                                                                               | 4.60  | 5.1   | 5.5   | V    |

| AUX SUP           | PLY (AUX)                         |                                                                                                                                                                                                                                 |       |       |       |      |

| V <sub>AUX</sub>  | Supply output voltage             | 18 V $\leq$ V <sub>VDD - COM</sub> $\leq$ 57 V, 0 mA $\leq$ I <sub>AUX</sub> $\leq$ 10 mA                                                                                                                                       | 9     | 10    | 11    | V    |

|                   | Current limit                     | V <sub>AUX</sub> = 0 V                                                                                                                                                                                                          | 12    | 23.5  | 28    | mA   |

| OSCILLA           | TOR (FREQ)                        |                                                                                                                                                                                                                                 |       |       |       |      |

| D <sub>MAX</sub>  | Maximum duty cycle                | $R_{FREQ}$ = 30 kΩ, $V_{COMP}$ = 3.9 V, MODE = $V_{BIAS},$ Measure GATE voltage at 50% rising to 50% falling                                                                                                                    | 48.8  | 49.2  | 49.5  | %    |

|                   |                                   | MODE = $V_{BIAS}$ , $V_{COMP}$ = 3 V, Measure at GATE                                                                                                                                                                           |       |       |       |      |

| f <sub>osc</sub>  | Oscillator frequency              | $R_{FREQ} = 30 \text{ k}\Omega$                                                                                                                                                                                                 | 435   | 487   | 565   | kHz  |

|                   |                                   | R <sub>FREQ</sub> = 150 kΩ                                                                                                                                                                                                      | 90    | 100   | 110   |      |

| ERROR A           | MPLIFIER (FB, COMP)               |                                                                                                                                                                                                                                 |       |       |       |      |

|                   | COMP source current               | $0 \le V_{COMP} \le 4 \text{ V}, \text{ FB} = \text{RTN}, \text{ V}_{TMR} = 2.5 \text{ V}$                                                                                                                                      | 2.5   |       |       | mA   |

|                   | COMP sink current                 | $1.2 \text{ V} \le \text{V}_{\text{COMP}} \le \text{V}_{\text{BIAS}}, \text{ V}_{\text{TMR}} = 2.5 \text{ V}$                                                                                                                   | 2.4   |       |       | mA   |

| V <sub>REF</sub>  | FB regulation voltage             | $V_{\text{COMP}} = 2.5 \text{ V}, V_{\text{TMR}} = 2.5 \text{ V}$                                                                                                                                                               | 1.47  | 1.50  | 1.53  | V    |

|                   | Open loop voltage gain            | $1.2 \text{ V} \le \text{V}_{\text{COMP}} \le 4 \text{ V}, \text{ V}_{\text{TMR}} = 2.5 \text{ V}$                                                                                                                              | 80    |       |       | dB   |

|                   | Small signal unity gain bandwidth | $V_{\text{COMP}} = 2.5 \text{ V}, V_{\text{TMR}} = 2.5 \text{ V}$                                                                                                                                                               | 1.5   | 2     |       | MHz  |

|                   | COMP input resistance             | $MODE = V_{BIAS}, 1.1 \le V_{COMP} \le 4.4, V_{TMR} = 2.5 V$                                                                                                                                                                    | 70    | 100   | 130   | kΩ   |

|                   | FB leakage (source or sink)       | $0 \le V_{FB} \le V_{BIAS}, V_{TMR} = 2.5 V$                                                                                                                                                                                    |       |       | 1     | μA   |

| SOFT ST           | ART TIMER (TMR)                   |                                                                                                                                                                                                                                 |       |       |       |      |

|                   | Source current                    | TMR charging, $V_{\text{TMR}}$ between lower threshold and clamp                                                                                                                                                                | 38    | 50    | 62    | μA   |

|                   | Ratio of source/sink current      |                                                                                                                                                                                                                                 | 9     | 10    | 11    | -    |

|                   | ON duty cycle                     | MODE = $V_{BIAS}$ , $V_{COMP}$ = 4.4 V, Second cycle and beyond                                                                                                                                                                 | 8     | 9.1   | 10    | %    |

| CURREN            | T SENSE (RSP, RSN, BL)            |                                                                                                                                                                                                                                 | _     | -     | -     |      |

|                   |                                   | MODE = V <sub>BIAS</sub> , V <sub>COMP</sub> = 4.2 V, V <sub>TMR</sub> = 2.5 V, Increase                                                                                                                                        | 0.46  | 0.5   | 0.54  | V    |

|                   | Current limit threshold           | $V_{RSP-RSN}$ until the duty cycle switches from 50% to the minimum                                                                                                                                                             | 0.10  | 0.0   | 0.01  | ·    |

|                   | Fault current threshold           | $\begin{array}{l} \text{MODE} = V_{BIAS}, \ V_{COMP} = 4.2 \ V, \ V_{TMR} = 2.5 \ V, \ \text{Increase} \\ V_{RSP\text{-}RSN} \ \text{until no gate pulses occur} \end{array}$                                                   | 0.70  | 0.765 | 0.83  | V    |

|                   |                                   | $\begin{array}{l} V_{RSP-RSN} = 0.6 \; V, \; V_{AUX} = 12 \; V, \; MODE = V_{BIAS}, \; V_{COMP} = 4.2 \; V, \\ V_{TMR} = 2.5 \; V. \; Measure \; 50\% \; of \; V_{GATE} \uparrow to \; 50\% \; V_{GATE} \downarrow \end{array}$ |       |       |       |      |

|                   |                                   | Minimum propagation delay, BL floating                                                                                                                                                                                          | 40    | 60    | 90    |      |

| t <sub>BLNK</sub> | Current limit delay               | Blanking period (pulse width above minimum), BL connected to RSN                                                                                                                                                                | 45    | 70    | 95    | ns   |

|                   |                                   | Blanking period (pulse width above minimum), BL connected to $V_{\text{BIAS}}$                                                                                                                                                  | 70    | 105   | 140   |      |

|                   | RSP current                       | $\label{eq:FREQ} \begin{array}{l} FREQ = V_{BIAS}, \ MODE = V_{BIAS}, \ V_{COMP} = 4 \ V, \\ V_{RSP\text{-}RSN} = 0.4 \ V, \ I_{RSP} \ sourcing \end{array}$                                                                    | 2.5   | 4     | 8     | μA   |

| GATE DR           | IVER (GATE)                       |                                                                                                                                                                                                                                 |       |       |       |      |

|                   |                                   | 5 mA source, V <sub>AUX</sub> = 12 V                                                                                                                                                                                            | 11.9  |       |       | V    |

|                   | Output voltage swing              | 5 mA sink, $V_{AUX}$ = 12 V                                                                                                                                                                                                     |       |       | 0.05  | V    |

|                   | Peak source current               | V <sub>AUX</sub> = 12 V, pulse test                                                                                                                                                                                             | 0.33  | 0.58  | 0.8   | Α    |

|                   | Peak sink current                 | $V_{AUX}$ = 12 V, AC test or pulse test with TMR = RSN                                                                                                                                                                          | 0.7   | 1.0   | 1.3   | Α    |

| VOLTAGE           | E TRANSLATOR (SEN, SENP)          | •                                                                                                                                                                                                                               |       |       |       |      |

|                   | (SENP - SEN) regulation voltage   | $V_{\text{TMR}}$ = 2.5 V, Measure with servo loop that includes the error amplifier                                                                                                                                             | 1.456 | 1.492 | 1.526 | V    |

4

Copyright © 2005–2008, Texas Instruments Incorporated

## **DC/DC CONTROLLER SECTION (continued)**

$RTN = V_{SS}$  for this section only.

| PARAMETER                    | TEST CONDITIONS                                                                                                        | MIN   | TYP  | MAX   | UNIT |

|------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Translator output resistance | $V_{SENP-SEN}$ = 1.5 V, TMR = RSN, $I_{FB}$ = 0 $\mu A$ and 10 $\mu A,$ $R_{FB}$ = $\Delta V_{FB}$ / $\Delta$ $I_{FB}$ | 11.25 | 15   | 18.75 | kΩ   |

| SEN sinking current          | $V_{SENP-SEN} = 1.50 \text{ V}, \text{ V}_{TMR} = \text{RSN}$                                                          |       |      | 1     | μΑ   |

| SENP sinking current         | V <sub>SENP-SEN</sub> = 1.50 V, V <sub>TMR</sub> = RSN                                                                 | 17    | 22.5 | 28    | μA   |

#### **PoE SECTION**

|                     | PARAMETER                                        | TEST COND                                                    | TEST CONDITIONS                                               |      | TYP  | MAX  | UNIT |

|---------------------|--------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| DETECTIO            | DN (DET)                                         |                                                              |                                                               |      |      |      |      |

| Offset current      |                                                  | DET open, $V_{DD} = V_{RTN} = 1.9 V$ , Mea                   | asure I <sub>VDD</sub> + I <sub>RTN</sub> + I <sub>SENP</sub> |      | 0.45 | 4    | μA   |

|                     | Sleep current                                    | DET open, V <sub>DD</sub> = V <sub>RTN</sub> = 10.1 V, Me    | asure I <sub>VDD</sub> + I <sub>RTN</sub> + I <sub>SENP</sub> |      | 5.6  | 12   | μA   |

|                     | DET leakage current                              | $V_{DET} = V_{DD} = 57 \text{ V}$ , Measure I <sub>DET</sub> |                                                               |      | 0.3  | 5    | μΑ   |

|                     |                                                  | RTN = $V_{DD}$ , Measure $I_{VDD}$ + $I_{RTN}$ +             | V <sub>DD</sub> = 1.4 V                                       | 51.5 | 55   | 58.7 | A    |

|                     | Detection current                                | I <sub>DET</sub> + I <sub>SENP</sub>                         | V <sub>DD</sub> = 10.1 V                                      | 395  | 411  | 417  | μA   |

| CLASSIFI            | CATION (CLASS)                                   |                                                              |                                                               |      |      |      |      |

|                     |                                                  | $RTN = V_{DD}$ , Measure $I_{VDD} + I_{RTN} + I_{E}$         | DET + I <sub>SENP</sub>                                       |      |      |      |      |

|                     |                                                  | $R_{CLASS} = 4420 \ \Omega, \ 13 \le V_{DD} \le 21 \ V$      |                                                               | 2.2  | 2.5  | 2.8  |      |

|                     | Classification surrant                           | $R_{CLASS} = 953 \ \Omega, \ 13 \le V_{DD} \ \le 21 \ V$     |                                                               | 10.3 | 10.6 | 11.3 | A    |

| ICLASS              | Classification current                           | $R_{CLASS} = 549 \ \Omega, \ 13 \le V_{DD} \ \le 21 \ V$     |                                                               | 17.7 | 18.3 | 19.5 | mA   |

|                     |                                                  | $R_{CLASS} = 357 \ \Omega, \ 13 \le V_{DD} \le 21 \ V$       |                                                               | 27.1 | 28.0 | 29.5 |      |

|                     |                                                  | $R_{CLASS} = 255 \ \Omega, \ 13 \le V_{DD} \ \le 21 \ V$     | 38.0                                                          | 39.4 | 41.2 |      |      |

| V <sub>CL_ON</sub>  |                                                  | Regulator turns on, V <sub>DD</sub> rising                   |                                                               | 10.2 | 11.3 | 13.0 | V    |

| V <sub>CL_H</sub>   | Classification lower threshold Hysteresis        |                                                              | 1                                                             | 1.75 | 3    | v    |      |

| V <sub>CU_OFF</sub> | Regulator turns off, V <sub>DD</sub> rising      |                                                              | 21                                                            | 21.9 | 23   | V    |      |

| V <sub>CU_H</sub>   | Classification upper threshold                   | Hysteresis                                                   | ysteresis                                                     |      | 0.83 | 1    |      |

| PASS DEV            | VICE (RTN)                                       | ·                                                            |                                                               |      |      |      |      |

|                     | On resistance                                    | I <sub>RTN</sub> = 300 mA                                    |                                                               |      | 0.60 | 1    | Ω    |

|                     | Current limit                                    | V <sub>RTN</sub> = 1 V                                       |                                                               | 405  | 450  | 515  | mA   |

| I <sub>INR</sub>    | Inrush limit                                     | V <sub>RTN</sub> = 1.6 V                                     |                                                               | 100  | 140  | 180  | mA   |

| CONTROL             | -                                                |                                                              |                                                               |      |      |      |      |

|                     | Inrush current state termination                 | $I_{RTN}$ falling from $I_{INR}$ , $I_{RTN}/I_{INR}$         |                                                               | 0.85 |      | 1.00 |      |

| UVLO                |                                                  |                                                              |                                                               |      |      |      |      |

| V <sub>UVLO_R</sub> |                                                  | $V_{DD}$ rising, monitor I <sub>RTN</sub>                    |                                                               | 38.4 | 39.3 | 40.4 |      |

| V <sub>UVLO_F</sub> | Standard UVLO threshold                          | V <sub>DD</sub> falling, monitor I <sub>RTN</sub>            |                                                               | 29.6 | 30.5 | 31.5 | V    |

|                     |                                                  | Hysteresis                                                   |                                                               | 8.3  | 8.8  | 9.1  |      |

| V <sub>UVLO_R</sub> | V <sub>DD</sub> rising, monitor I <sub>RTN</sub> |                                                              |                                                               | 34.1 | 35.1 | 36.0 |      |

| V <sub>UVLO_F</sub> | Legacy UVLO threshold                            | $V_{DD}$ falling, monitor I <sub>RTN</sub>                   |                                                               | 29.7 | 30.5 | 31.4 | V    |

|                     |                                                  | Hysteresis                                                   | 4.3                                                           | 4.5  | 4.8  |      |      |

## **ELECTRICAL CHARACTERISTICS – COMBINED**

| PARAMETER         |                      | TEST CONDITIONS                           | MIN TYP | MAX  | UNIT |

|-------------------|----------------------|-------------------------------------------|---------|------|------|

| BIAS CU           | RRENT                |                                           |         |      |      |

| I <sub>VDDQ</sub> | Quiescent current    |                                           | 1       | 1.3  | mA   |

|                   | Operational current  | COMP = FB                                 | 1.1     | 1.4  | mA   |

|                   |                      | COMP = FB, $R_{FREQ}$ = 30 k $\Omega$     | 1.3     | 1.75 | ША   |

|                   | Off state current    | $RTN = COM = RSN = V_{DD}, V_{DD} = 33 V$ | 0.18    | 0.5  | mA   |

| THERMA            | AL SHUTDOWN          |                                           |         |      |      |

|                   | Shutdown temperature | Temperature rising                        | 140     |      | °C   |

|                   | Hysteresis           |                                           | 17      |      | °C   |

6

Copyright © 2005–2008, Texas Instruments Incorporated

### **DEVICE INFORMATION**

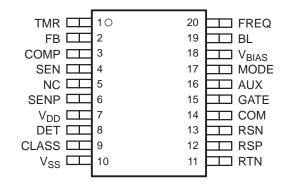

Figure 2. Pinout

#### **TERMINAL FUNCTIONS**

| TERMINAL          |     | 1/0 | DECODIDEION                                                                                                                                                                                                             |

|-------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO. | I/O | DESCRIPTION                                                                                                                                                                                                             |

| TMR               | 1   | 0   | Multifunction pin, serves as a converter soft start and a hiccup timer. A capacitor to RTN determines the softstart and hiccup timing.                                                                                  |

| FB                | 2   | I   | Converter error amplifier inverting input. Tie to RTN when not used.                                                                                                                                                    |

| COMP              | 3   | I/O | Converter error amplifier output and PWM block input. COMP is used for loop compensation or PWM control with an external error amplifier and opto-isolator.                                                             |

| SEN               | 4   | I   | Voltage-level translator's sense input and enable; connect to RTN to disable. SEN is regulated to 1.5 V below SENP by the control loop when the translator is used. Typically used in a low-side switch buck converter. |

| NC                | 5   | -   | No connect. There are no internal connections.                                                                                                                                                                          |

| SENP              | 6   | I   | Voltage-level translator's positive reference voltage (sense positive) used in conjunction with SEN. Tie to the regulated voltage positive rail when the translator is used, and $V_{DD}$ otherwise.                    |

| V <sub>DD</sub>   | 7   | PWR | Positive supply input.                                                                                                                                                                                                  |

| DET               | 8   | 0   | PoE detection pin; a 24.9 k $\Omega$ resistor to V_{DD} establishes a valid signature. It is pulled to V_{SS} during detection.                                                                                         |

| CLASS             | 9   | 0   | Classification pin for PoE. A resistor to $V_{SS}$ sets the PoE device class. This pin is driven to 10 V during classification.                                                                                         |

| V <sub>SS</sub>   | 10  | PWR | Negative supply input from the PoE feed (after required ORing bridges).                                                                                                                                                 |

| RTN               | 11  | I   | The switched PoE negative output. RTN is the converter's negative input rail. COM and RSN should be tied to RTN.                                                                                                        |

| RSP               | 12  | I   | Connect to the converter switching MOSFET current-sense resistor (current Sense Resistor Positive end).                                                                                                                 |

| RSN               | 13  | I   | Converter switching MOSFET current-sense reference (current Sense Resistor Negative end) and quiet analog return (ground). Connect to RTN.                                                                              |

| COM               | 14  | I   | Converter MOSFET gate driver circuit return. Connect to RTN.                                                                                                                                                            |

| GATE              | 15  | 0   | Converter switching MOSFET gate drive.                                                                                                                                                                                  |

| AUX               | 16  | I/O | Converter gate driver supply; outputs 10 V and can accept inputs up to 16 V. Connect a bypass capacitor to COM.                                                                                                         |

| MODE              | 17  | I   | Connect to V <sub>BIAS</sub> to disable the error amplifier, otherwise to RTN.                                                                                                                                          |

| V <sub>BIAS</sub> | 18  | 0   | Converter internal 5 V bias supply output, also used to bias external optocoupler. A bypass capacitor to RTN is required.                                                                                               |

| BL                | 19  | I   | Converter current sense blanking selector. Leave floating for minimum blanking, tie BL to RTN for a short period, and to $V_{\text{BIAS}}$ for a long period.                                                           |

| FREQ              | 20  | Ι   | Connect a resistor to RTN to program the switching frequency.                                                                                                                                                           |

| PowerPAD          | -   | PWR | Internally connected to $V_{SS}$ ; used to heatsink the part to the circuit board traces. Must be connected to the $V_{SS}$ pin.                                                                                        |

7

TPS23750 TPS23770

SLVS590B-JULY 2005-REVISED FEBRUARY 2008

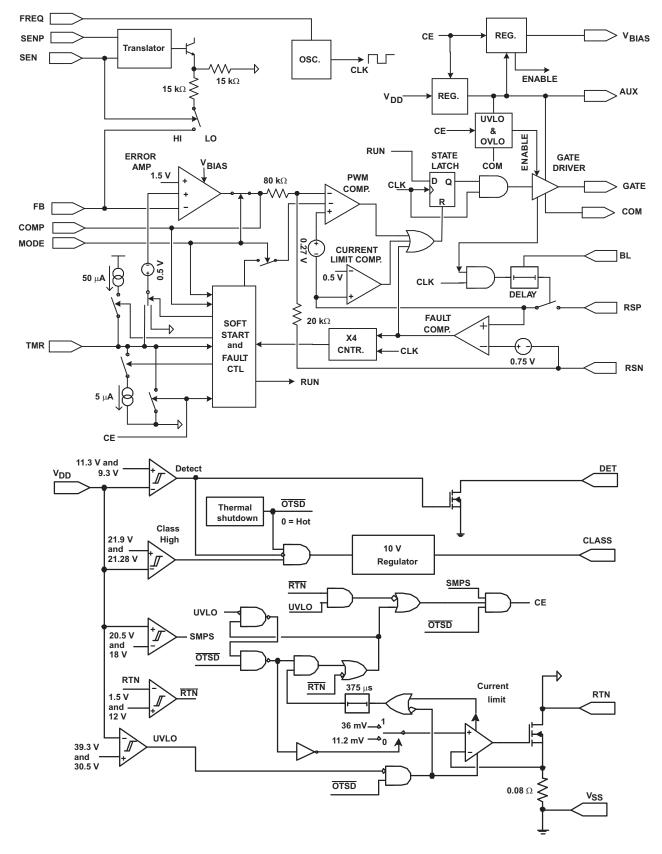

#### **BLOCK DIAGRAM**

8

## DETAILED DESCRIPTION

**AUX** – This pin is the junction between the internal 10 V converter-bias regulator, the gate driver supply, and the 5-V regulator that powers the rest of the converter control circuit. Voltage may be applied to this pin during normal converter operation to improve efficiency and reduce the TPS23750 temperature rise. A UVLO of about 8 V monitors  $V_{AUX-COM}$  to prevent operation with inadequate or weak bias. A converter overvoltage lockout protects the IC when a bias winding is used and  $V_{AUX}$  rises above 17.5 V.

A low ESR bypass capacitor of at least 0.8  $\mu$ F must be connected from AUX to COM.

**BL** – This pin selects the desired blanking operation. The blanking function prevents the sensed MOSFET current from tripping the PWM and current limit comparators for a predetermined period after the GATE switches high. This prevents the comparators from being falsely triggered by the gate drive current and recovery currents in the external power rectifiers. The recovery currents are strongly influenced by the topology, device selection, and device parasitics. The current limit comparator, logic, and gate driver account for the minimum delay which is obtained with the BL pin open. There are two preset delay choices, as shown below. Shorter periods may be obtained by leaving BL open and using an RC filter.

| BL CONNECTION     | BLANKING OPERATION                      |

|-------------------|-----------------------------------------|

| Open              | None (Minimum current-sense loop delay) |

| RSN               | Minimum plus 70 ns                      |

| V <sub>BIAS</sub> | Minimum plus 105 ns                     |

#### Table 1. BL Connections

**CLASS** – Classification is a PoE function implemented by means of an external resistor,  $R_{CLASS}$ , connected between CLASS and  $V_{SS}$ . Current is drawn from  $V_{DD}$  through  $R_{CLASS}$  for input voltages between 13 V and 21 V. Classification allows the PD to indicate the required average power requirements to the PSE as shown in Table 2.

| CLASS | PD POWER<br>(W) | R <sub>CLASS</sub><br>(Ω) | 802.3af CLASS<br>CURRENT<br>LIMITS<br>(mA) | NOTE                 |

|-------|-----------------|---------------------------|--------------------------------------------|----------------------|

| 0     | 0.44 – 12.95    | 4420 ±1%                  | 0 - 4                                      | Default class        |

| 1     | 0.44 – 3.84     | 953 ±1%                   | 9 – 12                                     |                      |

| 2     | 3.84 - 6.49     | 549 ±1%                   | 17 – 20                                    |                      |

| 3     | 6.49 – 12.95    | 357 ±1%                   | 26 - 30                                    |                      |

| 4     | Reserved        | 255 ±1%                   | 36 – 44                                    | Treated like class 0 |

#### **Table 2. Classification**

Approximately 10 V is applied to the CLASS resistor for up to 75 ms. The resistor's wattage rating need only be based on this transient condition.

The CLASS pin must not be shorted to ground. The recommended CLASS 0 resistor serves as a bleeder for capacitance connected around the TPS23750 after power is removed.

**COM** – Switching regulator gate driver return. This signal is internally separated from RTN and RSN to minimize noise coupling, but it should always be connected to RSN and RTN on the circuit board.

**COMP** – The TPS23750 is a traditional current-mode controller. The COMP pin represents the junction between the voltage control loop's error amplifier output and the current control loop's reference input. The name refers to the traditional connection of loop compensation components, which are connected between COMP and FB.

MODE alters the function of COMP. If MODE is tied to RTN, the internal error amplifier is enabled. If MODE is tied to  $V_{BIAS}$ , the internal amplifier disconnects from COMP, allowing an optocoupler to be fed directly into the PWM comparator circuit. The COMP pin should only be driven between RTN and  $V_{BIAS}$  when in this mode. Tie FB to RTN when the amplifier is disabled.

The current-mode control range includes COMP voltages between 1.35 V and just under 4 V. Converter switching is inhibited for COMP voltages below 1.35 V. COMP voltages higher than of 4.1 V cause the TMR circuit to begin hiccup operation. COMP is forced low during a hiccup-cycle off period when the internal error amplifier is used.

Copyright © 2005–2008, Texas Instruments Incorporated

TPS23770 SLVS590B-JULY 2005-REVISED FEBRUARY 2008

TPS23750

The COMP output should not be over-driven when the internal error amplifier is active. The amplifier can source and sink significant currents which will greatly increase power dissipation. TMR may be pulled low to turn the converter off when the internal error amplifier is used. The error amplifier will source current when COMP is pulled below its saturated low voltage due to the nature of the class AB amplifier stage.

**DET** – Connect a 24.9 k $\Omega$ , ±1% resistor (R<sub>DET</sub>), between DET and V<sub>DD</sub>. R<sub>DET</sub> is connected across the input line when V<sub>DD</sub> lies between 1.4 V and 10.1 V, and is disconnected when the line voltage exceeds 12 V to conserve power. R<sub>DET</sub> may be adjusted to compensate for input diode characteristics.

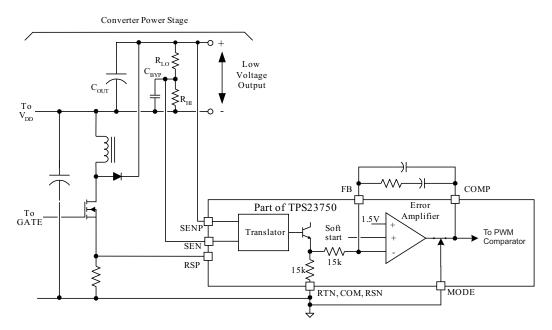

**FB** – This is the internal dc/dc converter error amplifier's inverting input. FB is used for output voltage feedback and loop compensation. FB equals 1.5 V when the feedback loop is in regulation. FB should be tied to RTN when the error amplifier is disabled using MODE. The internal level translator drives this pin with a source impedance of about 15 k $\Omega$  when it is enabled using SEN.

**FREQ** – A resistor connected from FREQ to RTN programs the converter switching frequency. This feature allows an existing design to be easily upgraded to use the TPS23750 without requiring redesign of the magnetics and filtering. While the oscillator is characterized between 100 kHz and 500 kHz, it operates properly down to a frequency of a few kilohertz.

$$R_{FREQ}(k\Omega) = \frac{15000}{Switching\_Frequency (kHz)}$$

(1)

Although this expression is reasonably accurate, the frequency will be slightly lower than predicted at higher frequencies.

FREQ must not be shorted to ground or have voltage applied.

**GATE** – DC/DC converter's switching MOSFET driver output. This pin has an internal pull-down to keep the external switching MOSFET off when the converter is inactive.

**MODE** – This pin disables the converter error amplifier, allowing an optocoupler to drive the PWM comparator directly from COMP. Connecting MODE to RTN enables the error amplifier, and to  $V_{BIAS}$  disables it. MODE should not be left floating.

**RSN** – This pin is the current-mode controller's quiet "ground" reference for current sensing and other low-level signals. RTN, RSN, and COM should be tied together.

**RSP** – This pin is the current-mode controller's current-sense input. Current-mode control monitors the switching MOSFET peak current, which is sensed as voltage between RSP and RSN, to set the PWM duty cycle. The peak current limit is established by limiting the maximum sense voltage to about 0.5 V.

MOSFET current may rise to high levels during the blanking period when there is a short in the power circuit. If the RSP peak voltage exceeds 0.75 V on four successive switching cycles, the converter is turned off and a hiccup cycle is started.

If the blanking is sufficient to eliminate the need for an input RC filter, this pin may be directly connected to the sense resistor.

**RTN** – An internal MOSFET connects this pin to  $V_{SS}$ . This MOSFET is controlled by the PoE section UVLO, inrush limit, current limit, thermal limit, and fault voltage limiting.

Most applications connect RSN, COM, and RTN together through a ground plane.

**SEN** – SEN is the negative input for the level translator. It can be used in buck converters as demonstrated in Figure 40. The translator is enabled by connecting SEN above 1 V with respect to RTN. The level translator applies  $V_{\text{SENP-SEN}}$  to the FB pin through an internal 15 k $\Omega$  resistor. This feature simplifies feedback voltage sensing above RTN. Connect SEN to RSN if the level translator is not used.

**SENP** – SENP is the positive input for the level translator. It is used in conjunction with SEN as demonstrated in Figure 40. The presence of this pin allows a filter inductor to be placed in the positive power rail between  $V_{DD}$  and the output. Connect SENP to  $V_{DD}$  when the level translator is disabled. The voltage on SENP should always be greater than the voltage on SEN.

**TMR** – Connect a capacitor from TMR to RTN to program the softstart and hiccup timer functions. Pull this pin to RTN to disable the converter.

Copyright © 2005–2008, Texas Instruments Incorporated

TMR controls softstart, overload time-out, and automatic restart on overload, which is referred to as a hiccup function.

$V_{BIAS}$  – This 5-V bias supply powers the bulk of the converter functions.  $V_{BIAS}$  can be used to power the feedback optocoupler in isolated applications. External loading should be minimized to avoid excessive power dissipation.  $V_{BIAS}$  has a UVLO function that inhibits converter operation at outputs of less than 4.6 V.  $V_{BIAS}$  should be bypassed with a capacitor between 0.08  $\mu F$  and 1.5  $\mu F$ . Do not apply external bias to this pin.

$V_{DD}$  – This is the positive power pin to the IC.

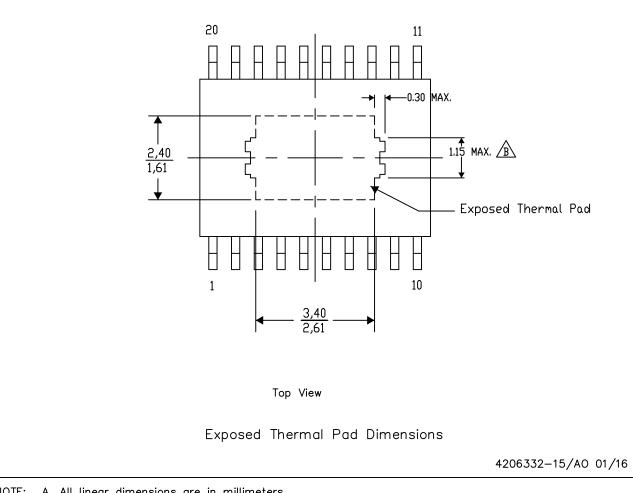

$V_{SS}$  – Common ground for the internal PoE circuits. This pin is connected to the low side of the rectified PoE voltage. An internal power MOSFET connects RTN to V<sub>SS</sub> under control of the PoE section. The PowerPAD on the bottom of the package is internally connected to V<sub>SS</sub>. The PowerPAD is used to remove heat from the die through the PCB.

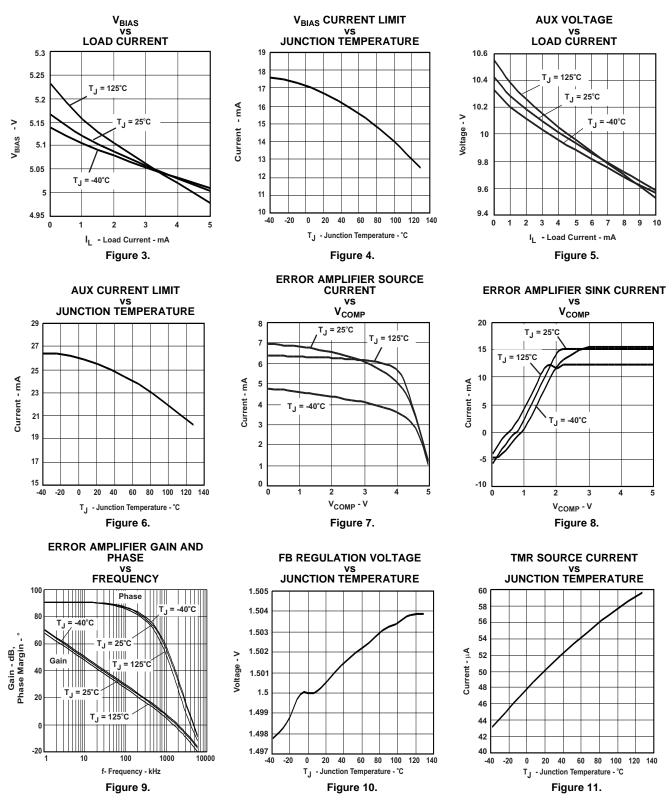

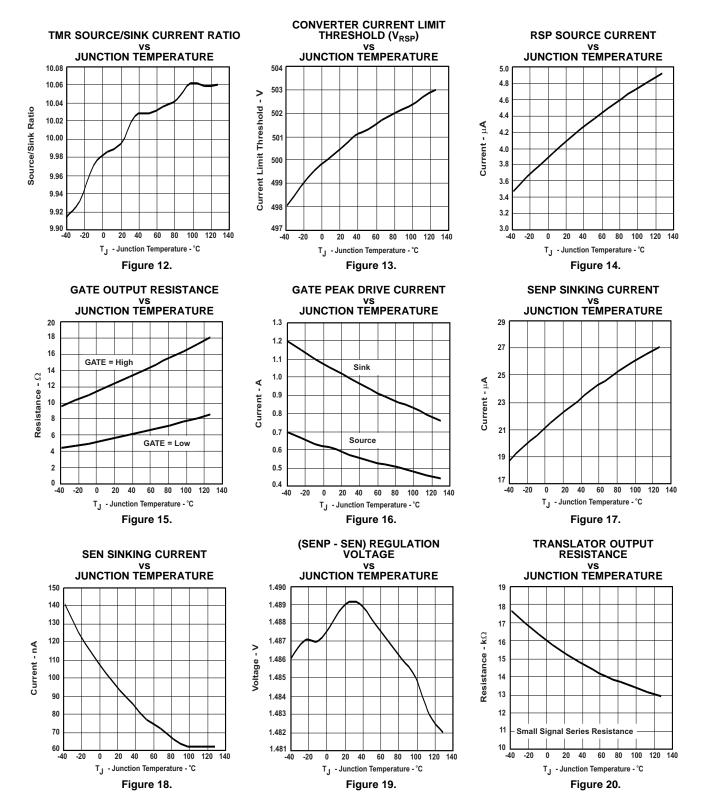

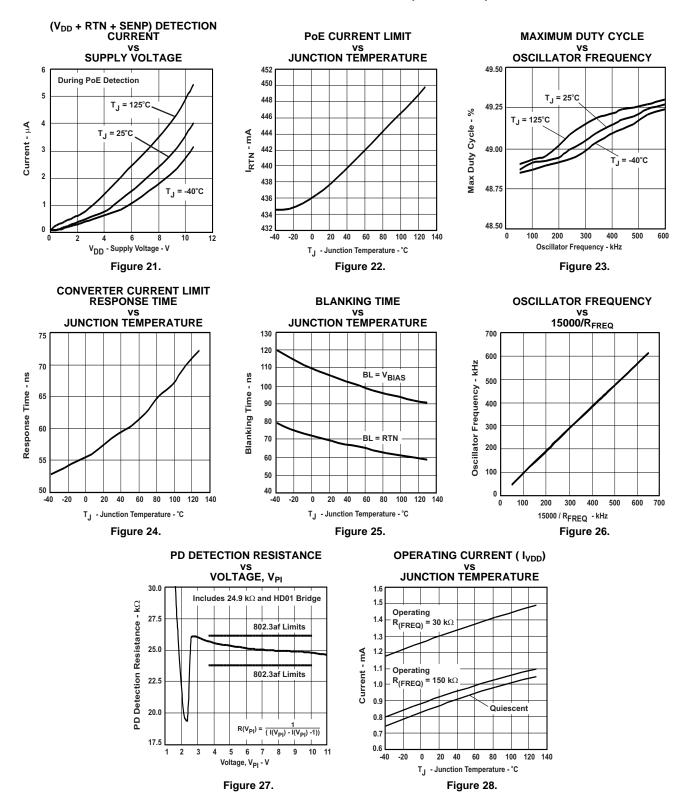

### **TYPICAL CHARACTERISTICS**

Copyright © 2005–2008, Texas Instruments Incorporated

### **TYPICAL CHARACTERISTICS (continued)**

### **TYPICAL CHARACTERISTICS (continued)**

Copyright © 2005–2008, Texas Instruments Incorporated

### **APPLICATION INFORMATION**

#### **PoE OVERVIEW**

The following text is intended as an aid in understanding the operation of the TPS23750 but not as a substitute for the actual IEEE 802.3af standard. Standards change and should always be referenced when making design decisions.

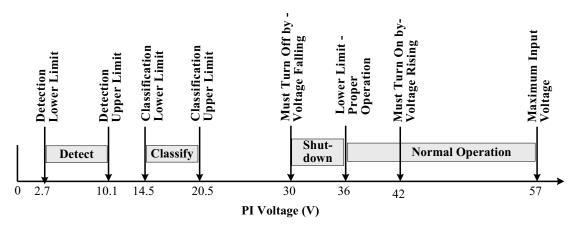

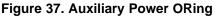

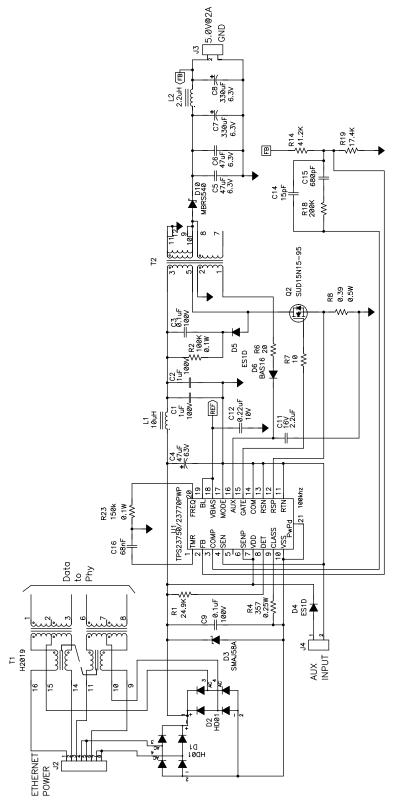

The IEEE 802.3af specification defines a method of safely powering a PD over a cable, and then removing power if a PD is disconnected. The process proceeds through the three operational states of detection, classification, and operation. The PSE leaves the cable unpowered while it periodically looks to see if something has been plugged in; this is referred to as detection. The low power levels used during detection are unlikely to damage devices not designed for PoE. If a valid PD signature is present, then the PSE may optionally inquire how much power the PD requires; this is referred to as classification. The PD may return a default full-power signature, or one of four other choices. The PSE may then power the PD if it has adequate capacity. Once started, the PD must present the maintain power signature (MPS) to assure the PSE that it is still there. The PSE monitors its output for a valid MPS, and turns the port off if it loses the MPS. Loss of the MPS returns the PSE to the initial state of detection. Figure 29 shows the operational states as a function of PD input voltage.

The PD input is typically an RJ-45 eight-lead connector which is referred to as the power interface (PI). PD input requirements differ from PSE output requirements to account for voltage drops in the cable and operating margin. The specification uses a cable resistance of 20  $\Omega$  to derive the voltage limits at the PD from the PSE output requirements. Although the standard specifies an output power of 15.4 W at the PSE output, only 12.95 W is available at the input of the PD due to the worst-case power loss in the cable.

The PSE can apply voltage either between the RX and TX pairs (pins 1–2 and 3–6), or between the two spare pairs (4–5 and 7–8). The applied voltage can be of either polarity and can only be applied to one set of pairs at a time. The PD uses input diode bridges to accept power from any of the possible PSE configurations. The voltage drops associated with the input bridges create a difference between the IEEE 802.3af limits at the PI and the TPS23750 specifications.

The PSE is required to current limit at an average of between 350 mA and 400 mA during normal operation, and it must disconnect the PD if it draws this current for more than 75 ms. Class 0 and 3 PDs may draw up to 400 mA peak currents. The PSE may set lower output current limits based on the PD's declared power requirements, as discussed below.

Figure 29. IEEE 802.3 PD Limits

TPS23750 TPS23770 SLVS590B-JULY 2005-REVISED FEBRUARY 2008

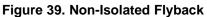

#### PoE THRESHOLDS

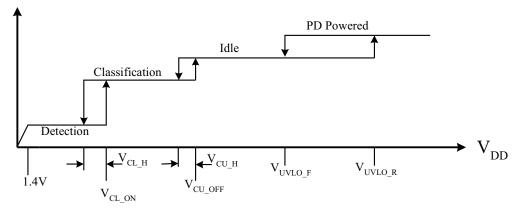

The TPS23750 has a number of internal comparators with hysteresis for stable switching between the various states as shown in Figure 29. Figure 30 relates the parameters in the Electrical Characteristics section to the PoE states. The mode labeled *idle* between classification and operation implies that the DET, CLASS, and RTN pins are all high impedance.

Figure 30. Threshold Voltages

#### DETECTION

This feature of IEEE 802.3af reduces the risk of damaging Ethernet devices not intended for application of 48 V. When a voltage in the range of 2.7 V to 10.1 V is applied to the PI, an incremental resistance of 25 k $\Omega$  signals the PSE that the PD is both capable of, and ready to, accept power. The incremental resistance is measured by applying at least two different voltages to the PI and measuring the current it draws. These two test voltages must be within the specified range and be at least 1 V apart. The incremental resistance equals the difference between the voltages divided by the difference between the currents. The allowed range of resistance is 23.75 k $\Omega$  to 26.25 k $\Omega$ .

The TPS23750 is in detection mode whenever the supply voltage is below the lower classification threshold. The TPS23750 draws a minimum of bias power in this condition, while RTN is high impedance and almost all the internal circuits are disabled. The DET pin is pulled to ground during detection, so a 24.9 k $\Omega$ , 1% resistor from V<sub>DD</sub> to DET presents the correct signature. R<sub>DET</sub> may be a small, low-power resistor since it only sees a stress of about 5 mW. When the input voltage rises above the 11.3 V upper detection comparator threshold, the DET pin goes to an open-drain condition to conserve power.

The input diode bridge's incremental resistance may be hundreds of Ohms at the very low currents seen at 2.7 V on the PI. The bridge's resistance is in series with  $R_{DET}$  and increases the total resistance seen by the PSE. The nonlinearity in the detection signature of Figure 29 is caused by the diode bridge. This varies with the type of diode selected by the designer, and it is not usually specified on the diode data sheet. The value of  $R_{DET}$  may be adjusted downwards to accommodate a particular diode type.

#### CLASSIFICATION

Once the PSE has detected a PD, it may optionally classify the PD. Classification allows a PSE to determine a PD's power requirements rather than assuming every PD requires 15.4 W, which allows the PSE to power the maximum number of PDs from its 48-V power supply. This step is optional because some PSEs can afford to allot the full power to every powered port.

The classification process applies a voltage between 14.5 V and 20.5 V to the input of the PD, which in turn draws a fixed current set by  $R_{CLASS}$ . The PSE measures the PD current to determine which of the five available classes (see Table 2) that the PD falls into. The total current drawn from the PSE during classification is the sum of bias currents and current through  $R_{CLASS}$ . The TPS23750 disconnects  $R_{CLASS}$  at voltages above the classification range to avoid excessive power dissipation (see Figure 29 and Figure 30).

16 Submit Documentation Feedback

Copyright © 2005–2008, Texas Instruments Incorporated

The value of  $R_{CLASS}$  should be chosen from the values listed in Table 2 based on the average power requirements of the PD. The power rating of this resistor should be chosen so that it is not overstressed for the required 75 ms classification period, during which 10 V is applied. The PD could be in classification for extended periods during bench test conditions, or if an auxiliary power source with voltage within the classification range is connected to the PD front end. Thermal protection may activate and turn classification off if it continues for more than 75 ms, but the design must not rely on this function to protect the resistor.

#### NORMAL OPERATION AND PoE UNDERVOLTAGE LOCKOUT (UVLO)

The TPS23750 incorporates an undervoltage lockout (UVLO) circuit that monitors PoE input voltage to determine when to apply power to the converter, allowing the PD to power up and run. The IEEE 802.3af specification dictates a maximum PD turn-on voltage of 42 V and a minimum turn-off voltage of 30 V (see Figure 30). The IEEE 802.3af standard assumes an 8 V drop in the cabling based on a 20  $\Omega$  feed resistance and a 400 mA maximum inrush limit. Because the minimum PSE output voltage is 44 V, the PD must continue to operate properly with input voltages as low as 36 V. The TPS23750 allows an input diode drop of 1.5 V and sets its nominal turn-on at 39.3 V and its turn-off at 30.5 V, while the TPS23770 turns on at 35 V with the same turn-off.

The TPS23770 UVLO limits are designed to support legacy systems whose minimum output voltage is less than 44 V. These systems required a lower turn-on voltage and smaller hysteresis. Although the TPS23770 works with compliant PSEs, it could potentially exhibit startup instabilities if the PSE output voltage rises slowly. The TPS23750 is recommended for applications with compliant PSEs.

The MPS is an electrical signature presented by the PD to assure the PSE that it is still present. A valid MPS consists of a minimum dc current of 10 mA and an ac impedance lower than a series 26.25 k $\Omega$  and 0.05  $\mu$ F load. The ac impedance is usually overshadowed by the minimum capacitance requirement of 5  $\mu$ F.

#### PD STATE MACHINE AND CONVERTER OPERATION

The TPS23750 incorporates a state machine that controls the inrush and operational current limit states. When  $V_{DD}$  is below the lower UVLO limit, the pass MOSFET is off. Consequently, the RTN pin is high impedance, and at  $V_{DD}$  once the output capacitor is discharged by the converter. When  $V_{DD}$  rises above the UVLO turn-on threshold with RTN high, the TPS23750 enables the internal power MOSFET with the current limit set to 140 mA. The converter is disabled while the output capacitor charges and  $V_{RTN}$  falls from  $V_{DD}$  to nearly  $V_{SS}$ . Once the inrush current falls about 10% below the programmed limit, the current limit switches to the internal 450 mA operational level after a 375  $\mu$ s delay. The converter section is enabled once the current limit is switched and the converter begins a softstart cycle. If the input voltage drops below the lower UVLO, the PoE MOSFET turns off, but the converter is allowed to operate to a ( $V_{VDD}$ -  $V_{SS}$ ) of about 18 V.

The internal pass MOSFET is protected against output faults with a current limit and a form of foldback when it is operating in the full current limit state. The PSE output cannot be relied on to protect the PD MOSFET against transient conditions, so the PD implements its own output protection. High stress conditions include converter output shorts, shorts from  $V_{DD}$  to RTN, or transients on the input line. An overload on the pass MOSFET engages the current limit, with ( $V_{RTN} - V_{SS}$ ) rising as a result. If  $V_{RTN}$  rises above 12 V, the current limit state machine resets to the 140 mA inrush current limit, and turns off the converter. The thermal shutdown activates to protect the device if the power dissipation from current limit overheats the TPS23750 as described in the thermal protection section below. The RTN comparator is capable of detecting even short excursions of RTN over 12 V that can be caused during overloads and input transients. If the fault that caused the overload disappears, the TPS23750 goes through a normal startup cycle as discussed above. This form of protection limits the peak dissipation in the MOSFET, prevents lockup of the converter in current limit, protects the load from a harmful voltage droop, and allows an orderly recovery from a known state if the problem disappears.

The TPS23750 allows startup and operation from a 24 V to 48 V adapter when it is connected from  $V_{DD}$  to RTN without PoE power available. Converter operation is enabled if

- The PoE section is not in inrush, and

- +  $V_{\text{DD}}$   $V_{\text{SS}}$  has exceeded 20.5 V with RTN less than 1.5 V, and

- V<sub>DD</sub> V<sub>SS</sub> is greater than 18 V.

The thresholds are defined in terms of  $V_{DD}$  -  $V_{SS}$  even though the converter really operates from  $V_{DD}$  to RTN. The internal PoE pass MOSFET has a reverse diode which clamps  $V_{SS}$  to one diode drop above RTN when the device is powered from the output side.

Copyright © 2005–2008, Texas Instruments Incorporated

**TPS23750 TPS23770** SLVS590B–JULY 2005–REVISED FEBRUARY 2008

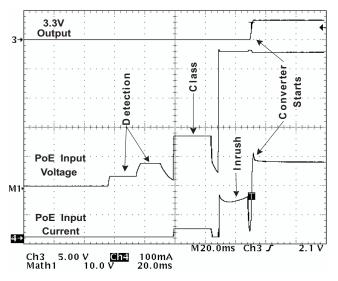

#### PoE STARTUP EXAMPLE

Figure 31 demonstrates detection, classification, and startup. The PSE controls the voltage on the PI, while the PD controls the current. The waveforms presented are the PI voltage, PI current, and dc/dc converter output voltage. Testing with different PSEs may result in waveforms that are not exactly the same because the IEEE 802.3af standard allows for different implementations.

The first event is detection. Two voltage levels of about 4 V and 8 V are seen, but the detection current levels are not seen because of the current scale. The second event is classification. The PD draws about 28 mA while the PI voltage is about 17 V, indicating it is a class 3 device. The third event is startup. The PI voltage ramps to about 46 V and the PD draws an inrush current between 120 mA and 140 mA as the downstream bulk capacitor is charged. The PI current drops once the bulk capacitor is charged, allowing the inrush state to terminate and the converter to enable. The final event is converter startup into a fixed 1- $\Omega$  load. The converter output voltage ramps to 3.3 V with a corresponding PI current draw. The PI current increases to a steady-state value of 260 mA with only a small overshoot as the output capacitor is charged. The PD is powered, and the applications circuits are operational at the end of startup.

Figure 31. Typical Startup Waveforms

#### THERMAL PROTECTION

The TPS23750 enters a low-power mode if the die temperature exceeds 140°C. The pass MOSFET, dc/dc converter, AUX regulator, and CLASS regulator are turned off when this occurs. Sources of internal dissipation include bias currents, the pass MOSFET, and the AUX,  $V_{BIAS}$ , and CLASS regulators. Loading on AUX and  $V_{BIAS}$  is a dominant contributor when the AUX rail is not externally biased. The TPS23750 automatically restarts when the die temperature has fallen approximately 17°C with the pass MOSFET set in the inrush state, the converter disabled, and the TMR capacitor discharged.

The TPS23750 is built using a PowerPAD package to provide a low thermal resistance from the junction to the circuit board. The PowerPAD should be soldered to a large copper area on the circuit board to provide good thermal performance.

Other sources of local PCB heating should be considered during the thermal design. Typical calculations assume that the TPS23750 is the only heat source contributing to the PCB temperature rise.

#### CONVERTER CONTROLLER OVERVIEW

The TPS23750 dc/dc controller implements a typical current-mode control topology reminiscent of the UC3844, but with a number of enhancements.

A class AB inverting error amplifier, with a 1.5 V fixed reference, connects between input FB and output COMP. The error amplifier has a 1.5 MHz gain-bandwidth product and can source or sink several milliamps. This amplifier can be disabled to allow an optocoupler feedback circuit to drive the PWM section

COMP is also the input to the current-mode PWM section. A 1/5 divider scales the COMP input to the current comparators. Offsets built into the comparator assure that the duty cycle can be driven to 0%. The current limit comparator threshold of 0.5 V on the RSP pin provides a regulated current limit. The fault comparator detects a runaway condition when the peak voltage on RSP is greater than 0.75 V. This can occur with a shorted transformer winding, a short on the switching MOSFET drain, or a shorted buck converter inductor. The TPS23750 shuts down immediately after four consecutive fault comparator trips and enters a TMR-based hiccup cycle.

The duty cycle is limited to 50% based on typical circuits used in PoE, providing a number of benefits. First, it eliminates the complexity of a stabilizing current ramp. Second, it gives an assured reset period for the magnetics. Third, many forward converters with a 1:1 reset winding require a 50% or less duty cycle. Most applications that use a transformer or buck-mode converter prefer this lower duty cycle.

User-programmable current sense blanking eliminates the need for an RC filter. A 70 ns blanking period is provided to serve higher-frequency switching circuits with low output-rectifier recovery periods. A 115 ns blanking period is provided to serve medium-to-slow frequency circuits that have significant gate drive and recovery requirements. The minimum blanking option is provided to allow short period RC filters to be used.

The TMR pin provides a closed-loop softstart when the error amplifier is used. An open-loop softstart is provided if the internal error amplifier is disabled. TMR also implements a synthesized hiccup, or pause and restart, to limit average power dissipation when there is a fault in the converter. Cascading failures are avoided during a fault because the converter operates only about 9% of the time, allowing the power components to cool. A hiccup can be triggered when the COMP pin is railed high for a programmed period, which occurs when there is an overload, or the input voltage is too low.

The internal bias regulators eliminate external bootstrap resistors and startup regulators. The internal regulators allow the converter to start and run as soon as inrush completes. This avoids the pitfalls associated with the bootstrap-startup topology including failure to start and excessive startup delay.

Some PD designs use a 24 V wall adapter to operate when PoE is not available. The converter control allows startup with at least 20.5 V applied  $V_{DD}$  - RTN, and operation down to about 18 V.

#### ERROR AMPLIFIER CONNECTIONS

The TPS23750 accommodates many types of converters and feedback methods. A level translator supports a simple low-side switch buck converter, a class-AB voltage error amplifier supports non-isolated converters, and an error amplifier disable supports optocoupler feedback.

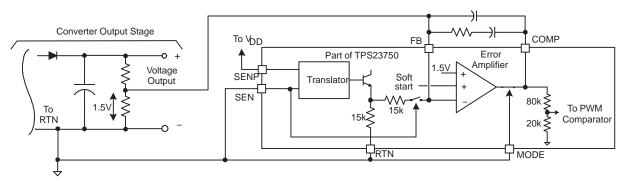

Some PD designers prefer to create multi-output power supplies using a flyback or forward topology, but do not require metallic isolation between the PoE front end and the application circuits. Figure 32 shows a configuration that enables the internal error amplifier and disables the level shifter. A standard output voltage divider and compensation scheme utilizes the FB and COMP pins. The control loop design should account for a 0.2 V/V attenuation factor from the error amplifier to the PWM comparator. The TMR pin ramps the reference voltage to the error amplifier giving a closed-loop softstart.

Figure 32. Nonisolated Converter Configuration

TPS23750 TPS23770 SLVS590B-JULY 2005-REVISED FEBRUARY 2008

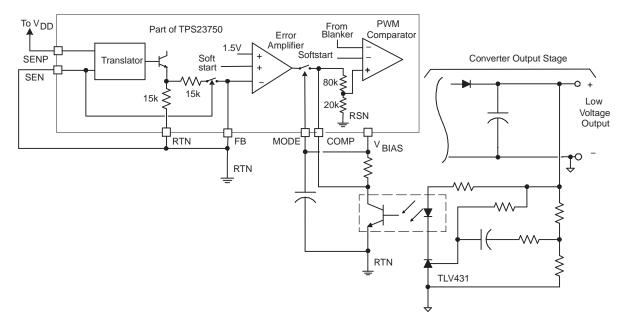

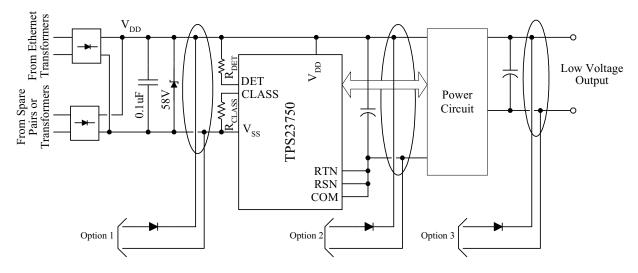

Isolated PD converters that use an optocoupler, such as TL431-based circuits, should use the configuration of Figure 33. The MODE connection disables the internal error amplifier, rendering its output high impedance. A primary-side PWM softstart is internally implemented when the error amplifier is disabled. The same gain of 0.2 V/V appears before the PWM comparator. The COMP pin is still monitored to implement hiccup in this configuration.

Figure 33. Isolated Converter Configuration

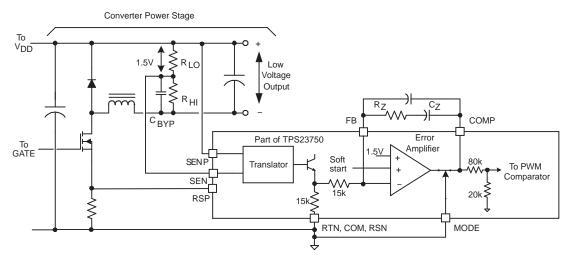

The buck converter configuration is shown in Figure 34. The loop regulates the voltage across  $R_{LO}$  to 1.5 V. The translator topology provides a gain of 1 V/V from  $V_{SENP-SEN}$  to the 15 k $\Omega$  internal series resistor. The error amplifier gain expression is ( $Z_{COMP-FB}$  / 15 k $\Omega$ ). The output divider and translator attenuate both the ac and dc components, unlike the configuration of Figure 32 where the ac signal is not divided because the virtual ground at the amplifier input cancels the effect of  $R_{LO}$ . Addition of  $C_{BYP}$  across  $R_{HI}$  applies the full ac signal to the error amplifier. The  $R_{HI}C_{BYP}$  corner frequency should be at least an octave lower than the  $R_zC_z$  zero frequency. This method assures  $C_{BYP}$  has little effect on standard loop design practices.

Figure 34. Buck Converter Configuration

### ADDITIONAL USES OF SENP AND SEN

The level translator inputs, SENP and SEN, are not limited to the buck application shown in Figure 34. They may

be used at voltages above  $V_{DD}$ , but within their recommended voltage range with respect to  $V_{SS}$ . SENP draws about 22.5  $\mu$ A of current, while the SEN pin draws less than 1  $\mu$ A. The SENP current can cause a small offset in the output voltage if connected to the center tap of an output voltage divider. If necessary, the offset can be minimized or compensated. The following example shows a method of creating a voltage greater than  $V_{DD}$  for a telecom application that requires a voltage greater than battery ground.

Figure 35. Buck-Boost Configuration Example

TPS23750 TPS23770 SLVS590B-JULY 2005-REVISED FEBRUARY 2008

#### **Bias Supplies**

The TPS23750 has two bias supplies, the AUX input/output and the V<sub>BIAS</sub> supply, each with its own UVLO.

The AUX supply is a current-limited, 10 V regulator that draws its current from  $V_{DD}$ . It may be overridden by feeding a higher external voltage into this pin to improve efficiency. The gate driver draws large current pulses from this rail. It requires low-impedance bypass capacitors, such as a 1  $\mu$ F ceramic capacitor, located next to the TPS23750 and connected by low-impedance connections. A UVLO prevents gate drive if the voltage is less than 8 V. A 17.5 V overvoltage lockout (OVLO) on AUX prevents an open-loop converter, such as the one in Figure 1, from damaging the part by inhibiting gate drive. The V<sub>BIAS</sub> regulator draws its power from the AUX pin.

The V<sub>BIAS</sub> regulator is a current-limited, 5.1 V regulator that requires a capacitor between 0.08  $\mu$ F–1.5  $\mu$ F from its output to RTN. An optocoupler can be powered from this rail. Current drawn from the V<sub>BIAS</sub> pin should not exceed 5 mA. This regulator also has a UVLO that turns the converter off if it is pulled below 4.6 V.

### **BLANKING CONSIDERATIONS AND RSP**

Programmable blanking typically eliminates the need for the traditional RC filter on the RSP input. Blanking prevents the current-mode and current-limit comparators from reacting to the current spike that occurs as the converter's switching MOSFET turns on. This current spike consists of the MOSFET gate current, parasitic drain capacitance current, and output rectifier recovery current. The required blanking period is highly dependent on the specific design. Having too short a blanking time causes the converter to current limit, or switch erratically at less than full load. A longer blanking time increases the minimum load required before cycle skipping occurs. The power required to run an Ethernet link should provide most PDs adequate load to prevent cycle skipping.

Starting recommendations for the BL setting are:

- Use the long blanking period for transformer-based designs operating below about 150 kHz or using synchronous rectifiers.

- Use the short blanking period for transformer-based designs operating above 150 kHz or using Schottky output diodes.

- Use the short blanking period for buck or boost converter topologies.

BL pin connections to achieve each blanking length are listed below.

| BL CONNECTION     | BLANKING OPERATION                      |

|-------------------|-----------------------------------------|

| Open              | None (Minimum current-sense loop delay) |

| RSN               | Minimum plus 70 ns                      |

| V <sub>BIAS</sub> | Minimum plus 105 ns                     |

An RC filter may be used on the RSP pin should the need arise. A bias current of less than 8  $\mu$ A flows out of the RSP pin.

The blanking period is specified as an increase in observable minimum gate on-time. The blanking circuit, current limit or PWM comparator, control logic, and loaded gate driver contribute to the observable current-sense loop delay. The PWM and current limit comparators do not respond to signals shorter than 20 ns, providing some inherent blanking within the current-sense loop delay measurement. The blanking circuit contributes almost negligible loop delay when the BL pin is open. The blanking periods are measured as the difference between the observed gate on-time with BL open, and its period with the BL pin connected high or low. The blanking periods shown do not include the comparator delays.

While many converter designs do not require a resistor in series with RSP, there may be instances where one is required to protect the pin from harmful currents. Even though the RSP pin has an absolute maximum voltage rating of -0.3 V, the ESD clamp can withstand occasional negative current pulses, provided they are limited to less than 100 mA. Some supply topologies, such as the self-driven synchronous rectifier circuit of Figure 38, have the ability to drive energy back through the transformer. This causes negative voltages on RSP and currents that can exceed the 100 mA. A small series protection resistor on RSP protects the device without requiring a Schottky diode clamp.

### **CONVERTER STARTUP**

An imbalance between converter output capacitance, converter current limit, input bulk capacitance, and softstart time causes the converter to hiccup when attempting to start. The converter has a hard input current limit enforced by either the internal hotswap MOSFET or the PSE. If this current is exceeded, the converter meets its energy demands by drawing down the voltage on the bulk capacitor. As the capacitor voltage falls, the voltage across the internal MOSFET increases. If the voltage across the TPS23750's MOSFET reaches 12 V, it turns the converter off, falls back into inrush, and tries to restart.

To successfully start up, the design should balance the output capacitance, converter current limit, input bulk capacitance, and softstart time. Minimize the output capacitance and converter current limit. Use a long softstart period to control the output capacitor charge current. Finally, use a larger input capacitor that provides an energy store to get over this peak demand. The input bulk capacitor voltage droop should generally not exceed 5 V.

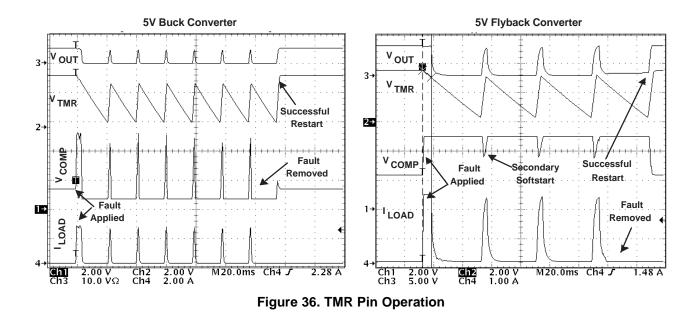

#### TMR OPERATION

TMR provides both a softstart and fault protection by means of a hiccup mode. Each cycle of hiccup operation consists of time-limited overload, followed by an enforced quiescent period, and an automatic restart. The benefits of hiccup operation include reduction of average thermal stress during faults and an automatic restart if a transient condition shuts the converter down.

During softstart, the converter is enabled and  $C_{TMR}$  charges at 50  $\mu$ A from a low voltage towards 3 V. If  $V_{COMP}$  is less than 4.2 V when  $V_{TMR}$  reaches 3 V,  $C_{TMR}$  continues to charge towards the 3.5 V clamp level and the converter remains enabled. Internal scaling assures that a  $V_{COMP}$  less than 4 V will yield the maximum peak current limit. A  $V_{COMP}$  of less than 4.2 V means that the voltage loop is in regulation. A high  $V_{COMP}$  is an indication that there is a problem, with the most likely problem being an output overload. If  $V_{COMP}$  is above 4.2 V when  $V_{TMR}$  reaches 3.0 V, the converter disables and  $C_{TMR}$  discharges at 5  $\mu$ A. A new softstart cycle begins when TMR reaches 0.3 V.

If the converter is operating normally, and V<sub>COMP</sub> exceeds 4.2 V, C<sub>TMR</sub> begins to discharge at 5  $\mu$ A towards 3 V. If TMR reaches 3 V, the converter shuts off and a hiccup cycle begins. If V<sub>COMP</sub> falls below 4.2 V before TMR reaches 3 V, C<sub>TMR</sub> recharges at 50  $\mu$ A and converter operation continues uninterrupted. Brief transients does not cause a hiccup due to the inherent filtering set by the value of C<sub>TMR</sub>.

Softstart behaves differently when the internal error amplifier is used or disabled. The error amplifier, if used, regulates the voltage on FB to equal the voltage on TMR minus 0.5 V during softstart. The output voltage rises slowly and is in regulation when FB equals 1.5 V. If the error amplifier is disabled, the PWM comparator trip point ramps from 0 V to 0.5 V as  $V_{TMR}$  transitions from 0.54 V to 1.54 V.

TMR is discharged with a 1 k $\Omega$  pull down resistance when the converter is disabled.

Several other conditions interact with TMR:

- TMR is held low when the PoE control disables the converter.

- TMR is held low if converter UVLOs are not satisfied.

- TMR is held low in thermal shutdown.

- TMR hiccups after four consecutive fault comparator trips. Switching is suspended immediately while a hiccup cycle occurs.