# LM9071 Low-Dropout System Voltage Regulator with Delayed Reset

Check for Samples: LM9071

#### **FEATURES**

- **Automotive Application Reliability**

- 3% Output Voltage Tolerance

- Insensitive to Radiated RFI

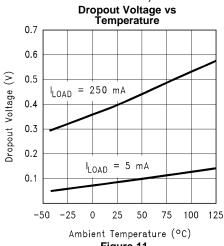

- Dropout Voltage Less than 800 mV with 250 **mA Output Current**

- **Externally Programmed Reset Delay Interval**

- **Thermal Shutdown**

- **Short Circuit Protection**

- **Reverse Battery Protection**

- Wide Operating Temperature Range −40°C to +125°C

- TO-220 and TO-263 Power Surface Mount **Power Packages**

- Pin for Pin Compatible with the LM2927, L4947 and TLE4260

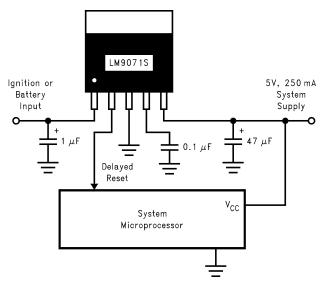

# **Typical Application and Connection Diagrams**

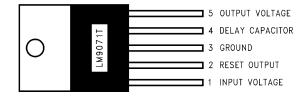

(Top View)

Figure 1.

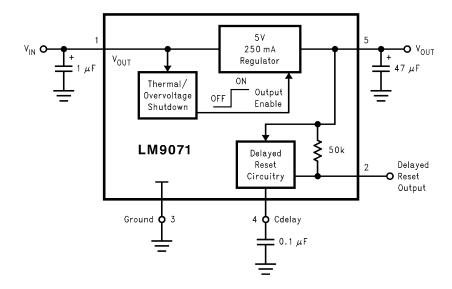

### DESCRIPTION

The LM9071 is a 5V, 250 mA low-dropout voltage regulator. The regulator features an active low delayed reset output flag which can be used to reset a microprocessor system on turn-ON and in the event that the regulator output falls out of regulation for any reason. An external capacitor programs a delay time interval before the reset output can return high.

Designed for automotive application the LM9071 contains a variety of protection features such as reverse battery, over-voltage shutdown, thermal shutdown, input transient protection and a wide operating temperature range.

Design techniques have been employed to allow the regulator to remain operational and not generate false reset signals when subjected to high levels of RF energy (300V/m from 2 MHz to 400 MHz).

Figure 2. 5-Lead TO-220 Package Package Number KC0005A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

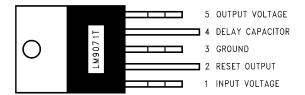

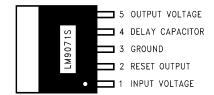

Tab and Backside metal on all packages internally connected to ground.

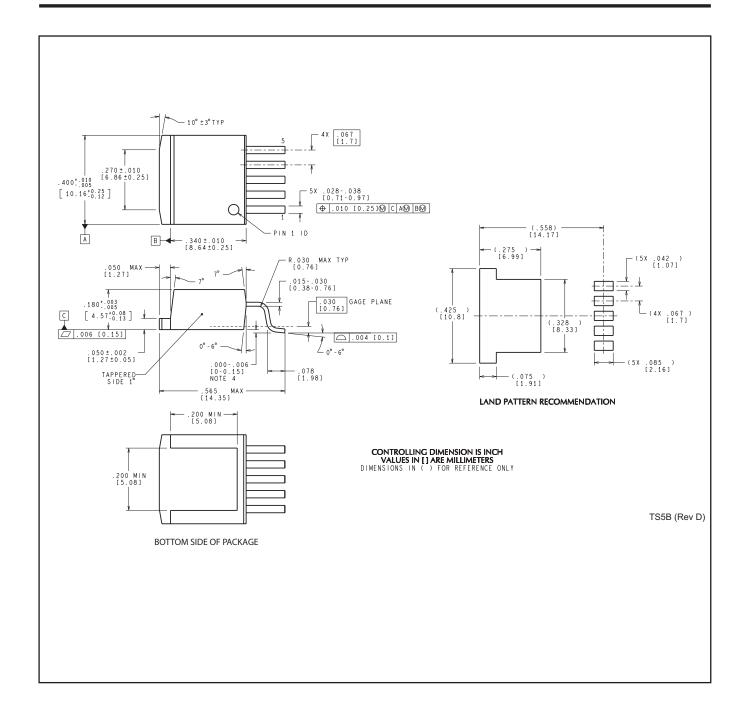

Figure 3. 5-Lead TO-220 Package Package Number NDH0005D

Figure 4. 5-Lead TO-263 Surface Mount Package Package Number KTT0005B

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)

| DC Input Voltage                         | -26V to +40V       |

|------------------------------------------|--------------------|

| Positive Input Transient (t<100 ms)      | 60V                |

| Negative Input Transient (t<1 ms)        | -50V               |

| Reset Output Sink Current                | 5 mA               |

| Power Dissipation                        | Internally Limited |

| Junction Temperature                     | 150°C              |

| ESD Susceptibility (2)                   | 12 kV, 2 kV        |

| Lead Temperature (Soldering, 10 seconds) | 260°C              |

| Storage Temperature                      | -50°C to +150°C    |

|                                          |                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and conditions, see the Electrical Characteristics.

- (2) All pins will survive an ESD impulse of ±2000V using the human body model of 100 pF discharged through a 1.5 kΩ resistor. In addition the input voltage pin will withstand ten pulses of ±12 kV from a 150 pF capacitor discharged through a 560Ω resistor when bypassed with a 22 nF, 100V capacitor.

# Operating Ratings (1)

| Input Voltage                                          | 6V to 26V       |

|--------------------------------------------------------|-----------------|

| Ambient Temperature                                    | -40°C to +125°C |

| TO-220 Thermal Resistance, $\theta_{\text{J-C}}$       | 3°C/W           |

| TO-220 Thermal Resistance, $\theta_{\text{J-A}}^{(2)}$ | 73°C/W          |

| TO-263 Thermal Resistance, $\theta_{\text{J-C}}$       | 3°C/W           |

| TO-263 Thermal Resistance, $\theta_{\text{J-A}}^{(3)}$ | 80°C/W          |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and conditions, see the Electrical Characteristics.

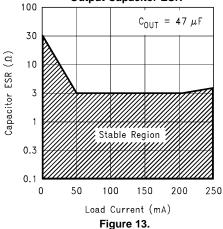

- (2) Exceeding the Maximum Allowable power dissipation will cause excessive die temperature, and the device will go into thermal shutdown. The θ<sub>J-A</sub> value for the TO-220 package (still air, no additional heat sink) is 73°C/W. The effective θ<sub>J-A</sub> value of the TO-220 package can be reduced by using conventional heat sink methods.

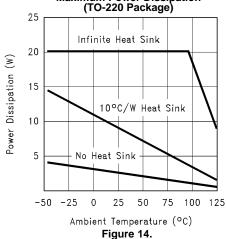

- (3) Exceeding the Maximum Allowable power dissipation will cause excessive die temperature, and the device will go into thermal shutdown. The θ<sub>J-A</sub> value for the TO-263 package (still air, no additional heat sink) is 80°C/W. The effective θ<sub>J-A</sub> value of the TO-263 package can be reduced by increasing the printed circuit board area that is connected (soldered) to the package tab. Using 1 ounce (1.4 mils thick) copper clad with no solder mask, an area of 0.5 square inches will reduce θ<sub>J-A</sub> to 50°C/W, an area of 1.0 square inches will reduce θ<sub>J-A</sub> to 37°C/W, ad an area of 1.6 square inches will reduce θ<sub>J-A</sub> to 32°C/W. If the printed circuit board uses a solder mask, the copper clad area should be increased by at least 50% to maintain a similar θ<sub>J-A</sub> rating.

# Electrical Characteristics (1)

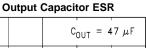

The following specifications apply for  $V_{CC}$ = 6V to 26V,  $-40^{\circ}C \le T_{A} \le +125^{\circ}C$ , unless otherwise specified.  $C_{OUT}$ = 47 $\mu$ F with an ESR < 3 $\Omega$ .  $C_{IN}$ =1 $\mu$ F.

| Symbol                   | Parameter                               | Conditions                                                                         | Min                  | Max  | Units |

|--------------------------|-----------------------------------------|------------------------------------------------------------------------------------|----------------------|------|-------|

| REGULATOR (              | ОИТРИТ                                  |                                                                                    | ,                    |      |       |

| V <sub>OUT</sub>         | Output Voltage                          | 5 mA ≤ I <sub>OUT</sub> ≤ 250 mA                                                   | 4.85                 | 5.15 | V     |

| ΔV <sub>OUT</sub> Line   | Line Regulation                         | $I_{OUT} = 5 \text{ mA}, 9V \le V_{IN} \le 16.5V$                                  |                      | 25   | mV    |

|                          |                                         | I <sub>OUT</sub> = 250 mA                                                          |                      | 50   | mV    |

| ΔV <sub>OUT</sub> Load   | Load Regulation                         | V <sub>IN</sub> = 14.4V, 5 mA ≤ I <sub>OUT</sub> ≤ 250 mA                          |                      | 60   | mV    |

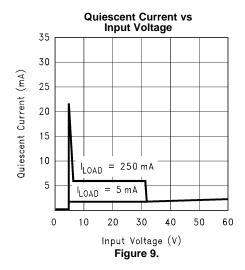

| Iq                       | Quiescent Current                       | I <sub>OUT</sub> = 5 mA                                                            |                      | 4    | mA    |

|                          |                                         | I <sub>OUT</sub> = 250 mA, V <sub>IN</sub> ≥ 8V                                    |                      | 25   | mA    |

|                          |                                         | I <sub>OUT</sub> = 5 mA, V <sub>IN</sub> = 5V                                      |                      | 10   | mA    |

|                          |                                         | I <sub>OUT</sub> = 250 mA, V <sub>IN</sub> = 6V                                    |                      | 50   | mA    |

| Vdo                      | Dropout Voltage                         | I <sub>OUT</sub> = 5 mA                                                            |                      | 300  | mV    |

|                          |                                         | I <sub>OUT</sub> = 250 mA                                                          |                      | 800  | mV    |

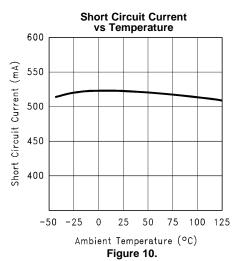

| Isc                      | Short Circuit Current                   | $R_L = 1\Omega$                                                                    | 0.35                 | 1.5  | Α     |

| PSRR                     | Ripple Rejection                        | $V_{IN} = (14V_{DC}) + (1V_{RMS} @ 120Hz)$<br>$I_{OUT} = 50 \text{ mA}$            | 60                   |      | dB    |

| OVthr                    | Overvoltage Shutdown Threshold          |                                                                                    | 27                   |      | V     |

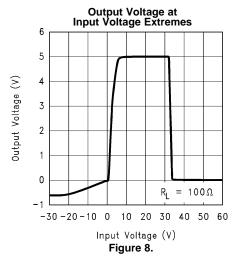

| V <sub>O</sub> Transient | V <sub>OUT</sub> during Transients      | V <sub>IN</sub> Peak ≤ 60V, R <sub>L</sub> = 100Ω, τ = 100 ms                      |                      | 7    | V     |

| V <sub>O</sub> Rev Batt  | V <sub>OUT</sub> during Reverse Battery | V <sub>IN</sub> = −15V                                                             | -0.8                 | 0.0  | V     |

| RESET OUTPL              | JT                                      |                                                                                    |                      |      |       |

| Vth                      | Threshold Voltage                       | $\Delta V_{OUT}$ Required to Generate a Reset Output 4.8V $\leq V_{OUT} \leq 5.2V$ | -300                 | -500 | mV    |

| Vlow                     | Reset Output Low Voltage                | Isink = 1.6 mA, V <sub>OUT</sub> > 3.2V                                            |                      | 0.4  | V     |

|                          |                                         | 1.4V ≤ V <sub>OUT</sub> ≤ 3.2V                                                     |                      | 0.8  | V     |

| Vhigh                    | Reset Output High Voltage               |                                                                                    | 0.8 V <sub>OUT</sub> |      | V     |

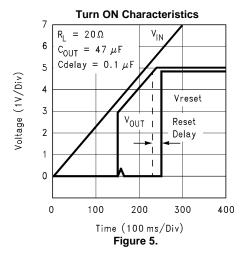

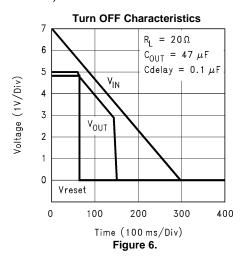

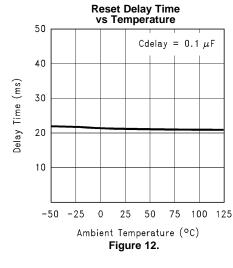

| t <sub>DELAY</sub>       | Delay Time                              | $C_{DELAY} = 0.1 \mu F$                                                            | 7.6                  | 35   | ms    |

| I <sub>DELAY</sub>       | Charging Current for C <sub>DELAY</sub> |                                                                                    | 10                   | 30   | μΑ    |

| Rpu                      | Internal Pull-up Resistance             |                                                                                    | 12                   | 80   | kΩ    |

<sup>(1)</sup> Datasheet min/max specifications are ensured by design, test, and/or statistical analysis.

Copyright © 1999–2013, Texas Instruments Incorporated

# **Typical Performance Characteristics**

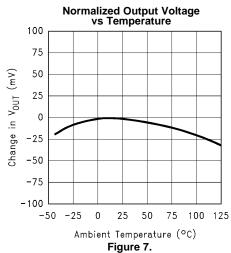

(T<sub>A</sub> = 25°C unless indicated otherwise)

Submit Documentation Feedback

Copyright © 1999–2013, Texas Instruments Incorporated

# **Typical Performance Characteristics (continued)**

(T<sub>A</sub> = 25°C unless indicated otherwise)

Maximum Power Dissipation (TO-220 Package)

Maximum Power Dissipation (TO-263 Package)

Figure 15.

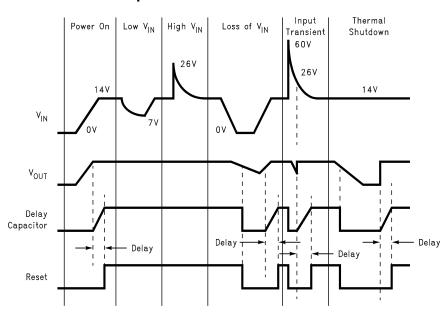

## **Reset Operation and Protection Features**

## **Block Diagram**

# **APPLICATION HINTS**

The LM9071 voltage regulator has been optimized for use in microprocessor based automotive systems. Several unique design features have been incorporated to address many FMEA (Failure Mode Effects Analysis) concerns for fail-safe system performance.

## **FAULT TOLERANT FEATURES**

While not specifically ensured due to production testing limitations, the LM9071 has been tested and shown to continue to provide a regulated output and, not generate an erroneous system reset signal while subjected to high levels of RF electric field energy (up to 300 V/m signal strength over a 2 MHz to 400 MHz frequency range). This is very important in vehicle safety related applications where the system must continue to operate normally. To maintain this immunity to RFI the output bypass capacitor is important (47 µF is recommended).

An output bypass capacitor of at least 10  $\mu F$  is required for stability (47  $\mu F$  is recommended). The ESR of this capacitor should be less than 3 $\Omega$ . An input capacitor of 1  $\mu F$  or larger is recommended to improve line transient and noise performance.

Conventional load dump protection is built in to withstand up to +60V and -50V transients. Protection against reverse polarity battery connections is also built in. With a reversed battery connection the output of the LM9071 will not go more negative than one diode drop below ground. This will prevent damage to any of the 5V load circuits.

#### **RESET FLAG**

Excessive loading of the output to the point where the output voltage drops by 300 mV to 500 mV will signal a reset flag to the micro. This will warn of a  $V_{CC}$  supply that may produce unpredictable operation of the system. On power-up and recovery from a fault condition the delay capacitor is used to hold the micro in a reset condition for a programmable time interval to allow the system operating voltages and clock to stabilize before executing code. The delay time interval can be estimated by the following equation:

t<sub>DELAY</sub> =

$$\frac{3.8V \times C_{DELAY}}{20 \ \mu A}$$

(1)

#### **INPUT STABILITY**

Low dropout voltage regulators which utilize a PNP power transistor usually exhibit a large increase in current when in dropout ( $V_{IN} < 5.5V$ ). This increase is caused by the saturation characteristics ( $\beta$  reduction) of the PNP transistor. To significantly minimize this increase in current the LM9071 detects when the PNP enters saturation and reduces the operating current.

This reduction in input current can create a stability problem in applications with higher load current (> 100 mA) where the input voltage is applied through a long length of wire, which in effect adds a significant amount of inductance in series with the input. The drop in input current may create a positive input voltage transient which may take the PNP out of saturation. If the input voltage is held constant at the threshold where the PNP is going in and out of saturation, an oscillation may be created.

This is only observed where a large series inductance is present in the input supply line and when the rise and fall time of the input supply is very slow. If the application and removal of the input voltage changes at a rate greater than 500 mV/ $\mu$ s it will move through the dropout region of the regulator ( $V_{IN}$  of 3V to 5.5V) too quickly for an oscillation to be established.

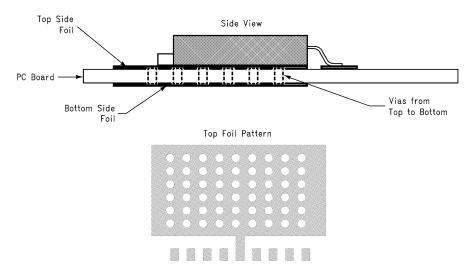

#### THERMAL MANAGEMENT

The LM9071 is packaged in both a TO-263 surface mount power package and a narrow lead-pitch TO-220 package. To obtain operation over the highest possible load current and input voltage ranges, care must be taken to control the operating temperature of the device. Thermal shutdown protection is built in, with a threshold above 150°C. Conventional heat-sinking techniques can be used with the TO-220 package. When applying the TO-263 package, on board heat-sinking is important to prevent premature thermal shutdown. More copper foil area under the tab of the device will directly improve the operating  $\theta_{\text{J-A}}$  of the TO-263 package, which will reduce the junction temperature of the device.

The  $\theta_{J-A}$  value for the TO-263 package (still air, no additional heat sink) is rated at 80°C/W. The effective  $\theta_{J-A}$  value of the TO-263 package can be reduced by increasing the printed circuit board area that is connected (soldered) to the package tab. Using 1 ounce (1.4 mils thick) copper clad with no solder mask, an area of 0.5 square inches will reduce  $\theta_{J-A}$  to 50°C/W, an area of 1.0 square inches will reduce  $\theta_{J-A}$  to 32°C/W. If the printed circuit board uses a solder mask, the copper clad area under the solder mask should be increased by at least 50% to maintain a similar  $\theta_{J-A}$  rating.

The use of a double sided PC board with soldered filled vias between two planes of copper, as shown in Figure 16, will improve thermal performance while optimizing the PC board surface area required. Using the double sided PC board arrangement shown in Figure 16, with 1 ounce (1.4 mils thick) copper clad with no solder mask and solder filled vias, an area of 0.5 square inches on both sides will reduce  $\theta_{\text{L-A}}$  to 43°C/W.

Figure 16. Typical TO-263 PC Board Heatsinking

# **REVISION HISTORY**

| Changes from Revision C (April 2013) to Revision D |                                                    |   |  |  |

|----------------------------------------------------|----------------------------------------------------|---|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format | 8 |  |  |

# PACKAGE OPTION ADDENDUM

6-Feb-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type     | •       | Pins | _   | Eco Plan                 | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|------------------|---------|------|-----|--------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |                  | Drawing |      | Qty | (2)                      | (6)              | (3)                 |              | (4/5)          |         |

| LM9071S/NOPB     | ACTIVE | DDPAK/<br>TO-263 | KTT     | 5    | 45  | Pb-Free (RoHS<br>Exempt) | SN               | Level-3-245C-168 HR | -40 to 125   | LM9071S        | Samples |

| LM9071SX/NOPB    | ACTIVE | DDPAK/<br>TO-263 | KTT     | 5    | 500 | Pb-Free (RoHS<br>Exempt) | SN               | Level-3-245C-168 HR | -40 to 125   | LM9071S        | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

6-Feb-2020

PACKAGE MATERIALS INFORMATION

www.ti.com 5-Dec-2014

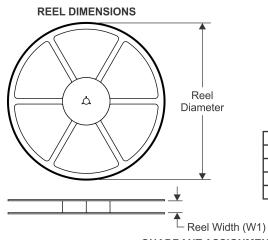

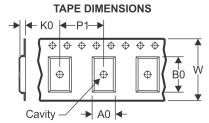

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

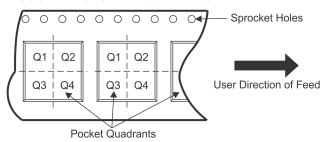

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type  | Package<br>Drawing |   |     | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------------------|--------------------|---|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM9071SX/NOPB | DDPAK/<br>TO-263 | KTT                | 5 | 500 | 330.0                    | 24.4                     | 10.75      | 14.85      | 5.0        | 16.0       | 24.0      | Q2               |

www.ti.com 5-Dec-2014

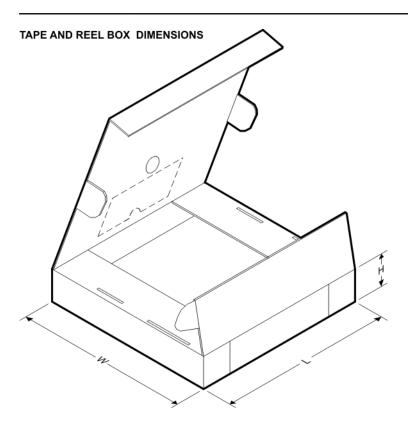

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|-----|-------------|------------|-------------|--|

| LM9071SX/NOPB | DDPAK/TO-263 | KTT             | 5    | 500 | 367.0       | 367.0      | 45.0        |  |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated