# SERIES 65 Optical Encoder Interface

### FEATURES

- Interfaces with all Grayhill and Most Standard Quadrature Optical Encoders

- Power Reduction of Up to 75-90% in Optical Encoder Use Through Power Management Feature

- User Selectable Output Modes: Magnitude/Direction, Up/Down, Standard Quadrature

- Simplified Microprocessor Interface Reduces Design Time

- Debounces Encoder Integral Pushbutton Switch

- Ideal for Battery Powered Applications that Include Optical Encoders

## DESCRIPTION

The GH65C11-X is designed to receive input from standard quadrature optical encoders. The power management feature allows power to the encoder to be applied only during sampling intervals, thus conserving power (especially advantageous in battery powered systems). Sample rate is a nominal 4K per second allowing high speed quadrature input. The optical encoder interface can operate in 1 of 3 user-selectable output modes. These modes are: magnitude and direction, up and down count, and standard quadrature. Debouncing of an integral pushbutton switch within the optical encoder can also be accomplished.

| Name                   | Type* | Description                                           |                              |                                  |                                          |                                              |

|------------------------|-------|-------------------------------------------------------|------------------------------|----------------------------------|------------------------------------------|----------------------------------------------|

| M0, M1                 | I     | Mode selection input pins                             |                              |                                  |                                          |                                              |

| V <sub>nn</sub>        | Р     | 3–6 Vdc power source                                  |                              |                                  |                                          |                                              |

| V <sub>DD</sub><br>RES | I     | Reset pin, normally connected to V <sub>DD</sub>      | SOIC/DIP                     |                                  | SSOP                                     |                                              |

| V <sub>ss</sub>        | Р     | GND, 0v nominal power return                          | M0 🖬 1<br>M1 🖬 2             | 18 □ ØBO/DN/DR<br>17 □ ØAO/UP/MG | M0 🖬 1<br>M1 🖬 2                         | 20 🗅 ØBO/DN/DR<br>19 🗆 ØAO/UP/MG             |

| ØÅI, ØBI               | I     | Phase A and B quadrature input pins                   | V <sub>DD</sub> 3            | 16 🗆 RC                          |                                          | 18 🗆 RC                                      |

| SWI                    | I     | Switch input pin                                      | RES 4                        |                                  | RES 4                                    |                                              |

| SWO                    | 0     | Debounced switch output pin                           | V <sub>ss</sub> ⊟5<br>ØAI ⊒6 | 14 □ V₀₀<br>13 □ PW              | V <sub>ss</sub> □5<br>V <sub>ss</sub> □6 | 16 □ V <sub>DD</sub><br>15 □ V <sub>DD</sub> |

| NC                     | 0     | No connect, this pin must be left unconnected         | ØBI 🗖 7                      | 12 🗆 PW                          | ØAI 🗖 7                                  | 14 🗆 PW                                      |

| PW                     | 0     | Power source for encoder power management             | SWI □8<br>SWO□9              | 11 🗆 PW<br>10 🗖 PW               | ØBI⊏I8<br>SWI⊏I9                         | 13 🗆 PW<br>12 🗖 PW                           |

| RC                     | I/O   | RC oscillator pin                                     | 30049                        |                                  | SWO II 10                                | 11 P PW                                      |

| ØBO/DN/DR              | 0     | Phase B, down, direction, mode conditional output pin |                              |                                  |                                          |                                              |

| ØAO/UP/MG              | 0     | Phase A, up, magnitude, mode conditional output pin   |                              |                                  |                                          |                                              |

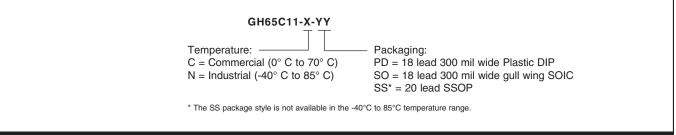

### **ORDERING INFORMATION**

Available from your local Grayhill Distributor. For prices and discounts, contact a local Sales Office, an authorized local Distributor or Grayhill.

For additional information about the use of the GH65 interface chips with optical encoders request Grayhill Application Note #719.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Grayhill:

GH65C11-C-SO GH65C11-N-SO GH65C11-C-SS GH65C11-N-PD