#### InvenSense Inc.

1745 Technology Drive, San Jose, CA 95110 U.S.A. Tel: +1 (408) 988-7339 Fax: +1 (408) 988-8104 Website: www.invensense.com Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

# MPU-6500 Product Specification Revision 1.1

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

# **TABLE OF CONTENTS**

| T | ABLE ( | OF TABLES                                                              | 5  |

|---|--------|------------------------------------------------------------------------|----|

| 1 | DOC    | UMENT INFORMATION                                                      | 6  |

|   | 1.1    | REVISION HISTORY                                                       | 6  |

|   | 1.2    | PURPOSE AND SCOPE                                                      | 7  |

|   | 1.3    | PRODUCT OVERVIEW                                                       | 7  |

|   | 1.4    | APPLICATIONS                                                           | 7  |

| 2 | FEA    | TURES                                                                  | 8  |

|   | 2.1    | GYROSCOPE FEATURES                                                     | 8  |

|   | 2.2    | ACCELEROMETER FEATURES                                                 | 8  |

|   | 2.3    | ADDITIONAL FEATURES                                                    | 8  |

|   | 2.4    | MOTIONPROCESSING                                                       | 8  |

| 3 | ELEC   | CTRICAL CHARACTERISTICS                                                | 9  |

|   | 3.1    | GYROSCOPE SPECIFICATIONS                                               | 9  |

|   | 3.2    | ACCELEROMETER SPECIFICATIONS                                           | 10 |

|   | 3.3    | ELECTRICAL SPECIFICATIONS                                              | 11 |

|   | 3.4    | I2C TIMING CHARACTERIZATION                                            | 15 |

|   | 3.5    | SPI TIMING CHARACTERIZATION                                            | 16 |

|   | 3.6    | ABSOLUTE MAXIMUM RATINGS                                               | 18 |

| 4 | APP    | LICATIONS INFORMATION                                                  | 19 |

|   | 4.1    | PIN OUT DIAGRAM AND SIGNAL DESCRIPTION                                 | 19 |

|   | 4.2    | TYPICAL OPERATING CIRCUIT                                              | 20 |

|   | 4.3    | BILL OF MATERIALS FOR EXTERNAL COMPONENTS                              | 20 |

|   | 4.4    | BLOCK DIAGRAM                                                          | 21 |

|   | 4.5    | Overview                                                               | 21 |

|   | 4.6    | THREE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING     | 22 |

|   | 4.7    | THREE-AXIS MEMS ACCELEROMETER WITH 16-BIT ADCS AND SIGNAL CONDITIONING | 22 |

|   | 4.8    | DIGITAL MOTION PROCESSOR                                               | 22 |

|   | 4.9    | PRIMARY I2C AND SPI SERIAL COMMUNICATIONS INTERFACES                   | 22 |

|   | 4.10   | AUXILIARY I2C SERIAL INTERFACE                                         | 24 |

|   | 4.11   | Self-Test                                                              | 25 |

|   | 4.12   | CLOCKING                                                               | 25 |

|   | 4.13   | SENSOR DATA REGISTERS                                                  | 26 |

|   | 4.14   | FIFO                                                                   | 26 |

Document Number: PS-MPU-6500A-01 Revision: 1.1 Release Date: 03/05/2014

|    | 4.15  | INTERRUPTS                        | 26 |

|----|-------|-----------------------------------|----|

|    | 4.16  | DIGITAL-OUTPUT TEMPERATURE SENSOR | 26 |

|    | 4.17  | BIAS AND LDOS                     | 27 |

|    | 4.18  | CHARGE PUMP                       | 27 |

|    | 4.19  | STANDARD POWER MODES              | 27 |

| 5  | PRO   | GRAMMABLE INTERRUPTS              | 28 |

|    | 5.1   | Wake-on-Motion Interrupt          | 29 |

| 6  | DIGIT | TAL INTERFACE                     | 30 |

|    | 6.1   | I2C AND SPI SERIAL INTERFACES     | 30 |

|    | 6.2   | I2C Interface                     | 30 |

|    | 6.3   | I2C COMMUNICATIONS PROTOCOL       | 30 |

|    | 6.4   | I <sup>2</sup> C TERMS            | 33 |

|    | 6.5   | SPI Interface                     | 34 |

| 7  | SERI  | AL INTERFACE CONSIDERATIONS       | 35 |

|    | 7.1   | MPU-6500 Supported Interfaces     | 35 |

| 8  | ASSE  | EMBLY                             | 36 |

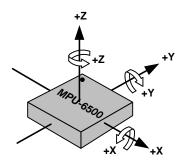

|    | 8.1   | ORIENTATION OF AXES               | 36 |

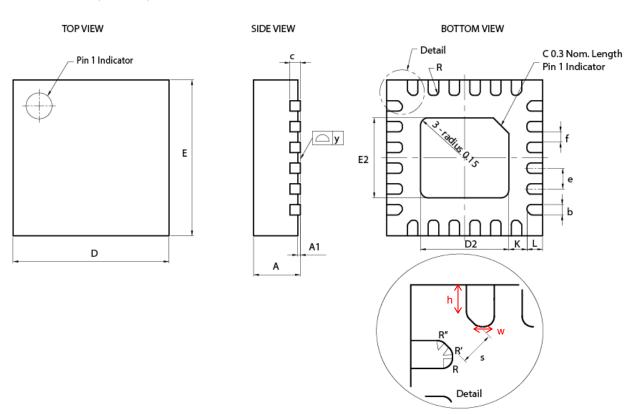

|    | 8.2   | PACKAGE DIMENSIONS                | 37 |

| 9  | PART  | F NUMBER PACKAGE MARKING          | 38 |

| 10 | RELI. | ABILITY                           | 39 |

|    | 10.1  | QUALIFICATION TEST POLICY         | 39 |

|    | 10.2  | QUALIFICATION TEST PLAN           | 39 |

| 11 | REFE  | RENCE                             | 40 |

Document Number: PS-MPU-6500A-01 Revision: 1.1 Release Date: 03/05/2014

# **Table of Figures**

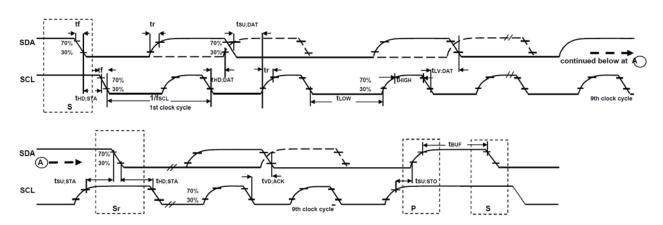

| Figure 1: | I2C Bus Timing Diagram                                                   | 15 |

|-----------|--------------------------------------------------------------------------|----|

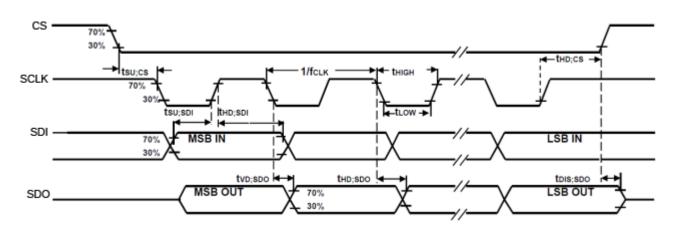

|           | SPI Bus Timing Diagram                                                   |    |

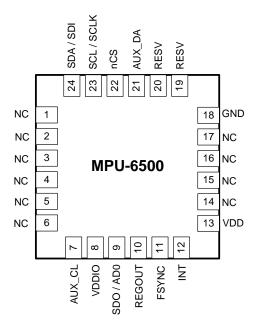

|           | Pin out Diagram for MPU-6500 3.0x3.0x0.9mm QFN                           |    |

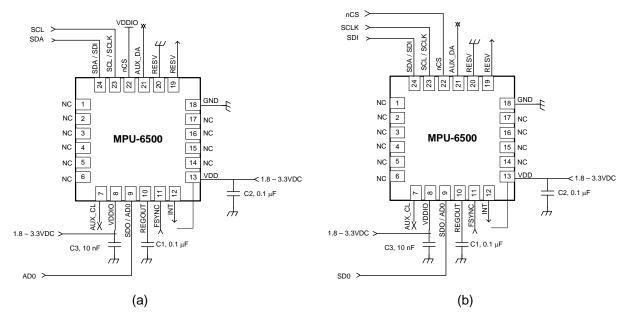

|           | MPU-6500 QFN Application Schematic. (a) I2C operation, (b) SPI operation |    |

|           | MPU-6500 Block Diagram                                                   |    |

|           | MPU-6500 Solution Using I <sup>2</sup> C Interface                       |    |

| Figure 7: | MPU-6500 Solution Using SPI Interface                                    | 24 |

|           | Wake-on-Motion Interrupt Configuration                                   |    |

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

## **Table of Tables**

| Table 1: Gyroscope Specifications                | 9  |

|--------------------------------------------------|----|

| Table 2: Accelerometer Specifications            |    |

| Table 3: D.C. Electrical Characteristics         | 11 |

| Table 4: A.C. Electrical Characteristics         | 13 |

| Table 5: Other Electrical Specifications         |    |

| Table 6: I <sup>2</sup> C Timing Characteristics | 15 |

| Table 7: SPI Timing Characteristics              | 16 |

| Table 8: fCLK = 20MHz                            | 17 |

| Table 9: Absolute Maximum Ratings                | 18 |

| Table 10: Signal Descriptions                    | 19 |

| Table 11: Bill of Materials                      | 20 |

| Table 12: Standard Power Modes for MPU-6500      | 27 |

| Table 13: Table of Interrupt Sources             | 28 |

| Table 14: Serial Interface                       | 30 |

| Table 15: 1 <sup>2</sup> C Torms                 | 33 |

Document Number: PS-MPU-6500A-01 Revision: 1.1 Release Date: 03/05/2014

#### **Document Information** 1

## 1.1 Revision History

| Revision<br>Date | Revision | Description                     |

|------------------|----------|---------------------------------|

| 09/18/2013       | 1.0      | Initial Release                 |

| 03/05/2014       | 1.1      | Updated Sections 1, 2, 4, 9, 11 |

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 1.2 Purpose and Scope

This document is a preliminary product specification, providing a description, specifications, and design related information on the MPU-6500™ MotionTracking device. The device is housed in a small 3x3x0.90mm QFN package.

Specifications are subject to change without notice. Final specifications will be updated based upon characterization of production silicon. For references to register map and descriptions of individual registers, please refer to the MPU-6500 Register Map and Register Descriptions document.

#### 1.3 Product Overview

The MPU-6500 is a 6-axis MotionTracking device that combines a 3-axis gyroscope, 3-axis accelerometer, and a Digital Motion Processor™ (DMP) all in a small 3x3x0.9mm package. It also features a 512-byte FIFO that can lower the traffic on the serial bus interface, and reduce power consumption by allowing the system processor to burst read sensor data and then go into a low-power mode. With its dedicated I²C sensor bus, the MPU-6500 directly accepts inputs from external I²C devices. MPU-6500, with its 6-axis integration, on-chip DMP, and run-time calibration firmware, enables manufacturers to eliminate the costly and complex selection, qualification, and system level integration of discrete devices, guaranteeing optimal motion performance for consumers. MPU-6500 is also designed to interface with multiple non-inertial digital sensors, such as pressure sensors, on its auxiliary I²C port.

The gyroscope has a programmable full-scale range of  $\pm 250$ ,  $\pm 500$ ,  $\pm 1000$ , and  $\pm 2000$  degrees/sec and very low rate noise at 0.01 dps/ $\sqrt{\text{Hz}}$ . The accelerometer has a user-programmable accelerometer full-scale range of  $\pm 2g$ ,  $\pm 4g$ , and  $\pm 16g$ . Factory-calibrated initial sensitivity of both sensors reduces production-line calibration requirements.

Other industry-leading features include on-chip 16-bit ADCs, programmable digital filters, a precision clock with 1% drift from -40°C to 85°C, an embedded temperature sensor, and programmable interrupts. The device features I<sup>2</sup>C and SPI serial interfaces, a VDD operating range of 1.71 to 3.6V, and a separate digital IO supply, VDDIO from 1.71V to 3.6V.

Communication with all registers of the device is performed using either I<sup>2</sup>C at 400kHz or SPI at 1MHz. For applications requiring faster communications, the sensor and interrupt registers may be read using SPI at 20MHz.

By leveraging its patented and volume-proven CMOS-MEMS fabrication platform, which integrates MEMS wafers with companion CMOS electronics through wafer-level bonding, InvenSense has driven the package size down to a footprint and thickness of 3x3x0.90mm (24-pin QFN), to provide a very small yet high performance low cost package. The device provides high robustness by supporting 10,000*g* shock reliability.

#### 1.4 Applications

- TouchAnywhere<sup>™</sup> technology (for "no touch" UI Application Control/Navigation)

- MotionCommand<sup>™</sup> technology (for Gesture Short-cuts)

- Motion-enabled game and application framework

- Location based services, points of interest, and dead reckoning

- Handset and portable gaming

- Motion-based game controllers

- 3D remote controls for Internet connected DTVs and set top boxes, 3D mice

- Wearable sensors for health, fitness and sports

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 2 Features

#### 2.1 Gyroscope Features

The triple-axis MEMS gyroscope in the MPU-6500 includes a wide range of features:

- Digital-output X-, Y-, and Z-axis angular rate sensors (gyroscopes) with a user-programmable full-scale range of ±250, ±500, ±1000, and ±2000°/sec and integrated 16-bit ADCs

- Digitally-programmable low-pass filter

- Gyroscope operating current: 3.2mA

- · Factory calibrated sensitivity scale factor

- Self-test

#### 2.2 Accelerometer Features

The triple-axis MEMS accelerometer in MPU-6500 includes a wide range of features:

- Digital-output X-, Y-, and Z-axis accelerometer with a programmable full scale range of ±2g, ±4g, ±8g and ±16g and integrated 16-bit ADCs

- Accelerometer normal operating current: 450µA

- Low power accelerometer mode current: 6.37μA at 0.98Hz, 17.75μA at 31.25Hz

- User-programmable interrupts

- Wake-on-motion interrupt for low power operation of applications processor

- Self-test

#### 2.3 Additional Features

The MPU-6500 includes the following additional features:

- Auxiliary master I<sup>2</sup>C bus for reading data from external sensors (e.g. magnetometer)

- 3.4mA operating current when all 6 motion sensing axes are active

- VDD supply voltage range of 1.8 3.3V ± 5%

- VDDIO reference voltage of 1.8 3.3V ± 5% for auxiliary I<sup>2</sup>C devices

- Smallest and thinnest QFN package for portable devices: 3x3x0.9mm

- Minimal cross-axis sensitivity between the accelerometer and gyroscope axes

- 512 byte FIFO buffer enables the applications processor to read the data in bursts

- Digital-output temperature sensor

- User-programmable digital filters for gyroscope, accelerometer, and temp sensor

- 10,000 g shock tolerant

- 400kHz Fast Mode I<sup>2</sup>C for communicating with all registers

- 1MHz SPI serial interface for communicating with all registers

- 20MHz SPI serial interface for reading sensor and interrupt registers

- MEMS structure hermetically sealed and bonded at wafer level

- RoHS and Green compliant

### 2.4 MotionProcessing

- Internal Digital Motion Processing<sup>™</sup> (DMP<sup>™</sup>) engine supports advanced MotionProcessing and low power functions such as gesture recognition using programmable interrupts

- In addition to the angular rate, this device optionally outputs the angular position (angle).

- Low-power pedometer functionality allows the host processor to sleep while the DMP maintains the step count.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3 Electrical Characteristics

#### 3.1 Gyroscope Specifications

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                           | CONDITIONS                           | MIN      | TYP   | MAX  | UNITS     | NOTES |

|-----------------------------------------------------|--------------------------------------|----------|-------|------|-----------|-------|

|                                                     | GYROSCOPE SENSITIVITY                |          |       |      |           |       |

| Full-Scale Range                                    | FS_SEL=0                             |          | ±250  |      | 0/s       | 3     |

|                                                     | FS_SEL=1                             |          | ±500  |      | °/s       | 3     |

|                                                     | FS_SEL=2                             |          | ±1000 |      | °/s       | 3     |

|                                                     | FS_SEL=3                             |          | ±2000 |      | °/s       | 3     |

| Gyroscope ADC Word Length                           |                                      |          | 16    |      | bits      | 3     |

| Sensitivity Scale Factor                            | FS_SEL=0                             |          | 131   |      | LSB/(º/s) | 3     |

|                                                     | FS_SEL=1                             |          | 65.5  |      | LSB/(º/s) | 3     |

|                                                     | FS_SEL=2                             |          | 32.8  |      | LSB/(º/s) | 3     |

|                                                     | FS_SEL=3                             |          | 16.4  |      | LSB/(º/s) | 3     |

| Sensitivity Scale Factor Tolerance                  | 25°C                                 |          | ±3    |      | %         | 2     |

| Sensitivity Scale Factor Variation Over Temperature | -40°C to +85°C                       |          | ±4    |      | %         | 1     |

| Nonlinearity                                        | Best fit straight line; 25°C         |          | ±0.1  |      | %         | 1     |

| Cross-Axis Sensitivity                              |                                      |          | ±2    |      | %         | 1     |

|                                                     | ZERO-RATE OUTPUT (ZRO)               |          |       |      |           |       |

| Initial ZRO Tolerance                               | 25°C                                 |          | ±5    |      | °/s       | 2     |

| ZRO Variation Over Temperature                      | -40°C to +85°C                       |          | ±0.24 |      | º/s/°C    | 1     |

| GYF                                                 | ROSCOPE NOISE PERFORMANCE (          | FS_SEL=0 | )     |      |           |       |

| Total RMS Noise                                     | DLPFCFG=2 (92 Hz)                    |          | 0.1   |      | º/s-rms   | 2     |

| Rate Noise Spectral Density                         |                                      |          | 0.01  |      | °/s/√Hz   | 4     |

| GYROSCOPE MECHANICAL FREQUENCIES                    |                                      | 25       | 27    | 29   | KHz       | 2     |

| LOW PASS FILTER RESPONSE                            | Programmable Range                   | 5        |       | 250  | Hz        | 3     |

| GYROSCOPE START-UP TIME                             | From Sleep mode                      |          | 35    |      | ms        | 1     |

| OUTPUT DATA RATE                                    | Programmable, Normal (Filtered) mode | 4        |       | 8000 | Hz        | 1     |

**Table 1: Gyroscope Specifications**

#### Notes:

- 1. Derived from validation or characterization of parts, not guaranteed in production.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Calculated from Total RMS Noise.

Please refer to the following document for information on Self-Test: MPU-6500 Accelerometer and Gyroscope Self-Test Implementation; AN-MPU-6500A-02

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3.2 Accelerometer Specifications

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V,  $T_A$ =25°C, unless otherwise noted.

| PARAMETER                           | CONDITIONS                            |                        | MIN  | TYP    | MAX  | UNITS           | NOTES |

|-------------------------------------|---------------------------------------|------------------------|------|--------|------|-----------------|-------|

|                                     | ACCELE                                | ROMETER SENSITIV       | /ITY |        |      |                 |       |

|                                     | AFS_SEL=0                             |                        |      | ±2     |      | g               | 3     |

| Full Cools Donne                    | AFS_SEL=1                             |                        |      | ±4     |      | g               | 3     |

| Full-Scale Range                    | AFS_SEL=2                             |                        |      | ±8     |      | g               | 3     |

|                                     | AFS_SEL=3                             | _                      |      | ±16    |      | g               | 3     |

| ADC Word Length                     | Output in two's comp                  | olement format         |      | 16     |      | bits            | 3     |

|                                     | AFS_SEL=0                             |                        |      | 16,384 |      | LSB/g           | 3     |

| Consistinistry Cools Footor         | AFS_SEL=1                             |                        |      | 8,192  |      | LSB/g           | 3     |

| Sensitivity Scale Factor            | AFS_SEL=2                             |                        |      | 4,096  |      | LSB/g           | 3     |

|                                     | AFS_SEL=3                             |                        |      | 2,048  |      | LSB/g           | 3     |

| Initial Tolerance                   | Component-level                       |                        |      | ±3     |      | %               | 2     |

| Sensitivity Change vs. Temperature  | -40°C to +85°C AFS<br>Component-level | _SEL=0                 |      | ±0.026 |      | %/°C            | 1     |

| Nonlinearity                        | Best Fit Straight Line                | Э                      |      | ±0.5   |      | %               | 1     |

| Cross-Axis Sensitivity              |                                       |                        |      | ±2     |      | %               | 1     |

|                                     | 2                                     | ZERO-G OUTPUT          |      |        |      |                 |       |

| Initial Tolerance                   | Component-level, al                   | l axes                 |      | ±60    |      | m <i>g</i>      | 2     |

| Zero-G Level Change vs. Temperature | -40°C to +85°C,                       | X and Y axes           |      | ±0.64  |      | m <i>g</i> /°C  | 1     |

| Zero-G Lever Change vs. Temperature | Board-level                           | Z axis                 |      | ±1     |      | m <i>g</i> /°C  | 1     |

|                                     | NOI                                   | SE PERFORMANCE         |      |        |      |                 |       |

| Power Spectral Density              | Low noise mode                        |                        |      | 300    |      | μ <i>g</i> /√Hz | 4     |

| LOW PASS FILTER RESPONSE            | Programmable Rang                     | је                     | 5    |        | 260  | Hz              | 3     |

| INTELLIGENCE FUNCTION INCREMENT     |                                       |                        |      | 4      |      | mg/LSB          | 3     |

| ACCELEROMETER STARTUP TIME          | From Sleep mode                       |                        |      | 20     |      | ms              | 1     |

| AGGELEROMETER GTARTOT TIME          | From Cold Start, 1m                   | s V <sub>DD</sub> ramp |      | 30     |      | ms              | 1     |

|                                     | Low power (duty-cycled)               |                        | 0.24 |        | 500  | Hz              |       |

| OUTPUT DATA RATE                    | Duty-cycled, over temp                |                        |      | ±15    |      | %               | 1     |

|                                     | Low noise (active)                    |                        | 4    |        | 4000 | Hz              |       |

**Table 2: Accelerometer Specifications**

#### Notes:

- 1. Derived from validation or characterization of parts, not guaranteed in production.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Calculated from Total RMS Noise.

Please refer to the following document for information on Self-Test: MPU-6500 Accelerometer and Gyroscope Self-Test Implementation; AN-MPU-6500A-02

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3.3 Electrical Specifications

#### 3.3.1 D.C. Electrical Characteristics

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                    | CONDITIONS                                                                   | MIN  | TYP   | MAX  | Units | Notes |  |  |  |

|------------------------------|------------------------------------------------------------------------------|------|-------|------|-------|-------|--|--|--|

| SUPPLY VOLTAGES              |                                                                              |      |       |      |       |       |  |  |  |

| VDD                          |                                                                              | 1.71 | 1.8   | 3.45 | V     | 1     |  |  |  |

| VDDIO                        |                                                                              | 1.71 | 1.8   | 3.45 | V     | 1     |  |  |  |

|                              | SUPPLY CURRENTS                                                              |      |       |      |       |       |  |  |  |

| Normal Mode                  | 6-axis                                                                       |      | 3.4   |      | mA    | 1     |  |  |  |

|                              | 3-axis Gyroscope                                                             |      | 3.2   |      | mA    | 1     |  |  |  |

|                              | 3-Axis Accelerometer, 4kHz ODR                                               |      | 450   |      | μΑ    | 1     |  |  |  |

| Accelerometer Low Power Mode | 0.98 Hz update rate                                                          |      | 7.27  |      | μΑ    | 1,2   |  |  |  |

|                              | 31.25 Hz update rate                                                         |      | 18.65 |      | μΑ    | 1,2   |  |  |  |

| Standby Mode                 |                                                                              |      | 1.6   |      | mA    | 1     |  |  |  |

| Full-Chip Sleep Mode         |                                                                              |      | 6     |      | μA    | 1     |  |  |  |

| TEMPERATURE RANGE            |                                                                              |      |       |      |       |       |  |  |  |

| Specified Temperature Range  | Performance parameters are not applicable beyond Specified Temperature Range | -40  |       | +85  | °C    | 1     |  |  |  |

**Table 3: D.C. Electrical Characteristics**

#### Notes:

- 1. Derived from validation or characterization of parts, not guaranteed in production.

- 2. Accelerometer Low Power Mode supports the following output data rates (ODRs): 0.24, 0.49, 0.98, 1.95, 3.91, 7.81, 15.63, 31.25, 62.50, 125, 250, 500Hz. Supply current for any update rate can be calculated as:

- a. Supply Current in  $\mu$ A = 6.9 + Update Rate \* 0.376

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

## A.C. Electrical Characteristics

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V,  $T_A$ =25°C, unless otherwise noted.

| Parameter                                                                       | Conditions                                                 | MIN                  | TYP                | MAX             | Units    | NOTES |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|--------------------|-----------------|----------|-------|--|--|

|                                                                                 | SUP                                                        | PLIES                |                    |                 |          |       |  |  |

| Supply Ramp Time                                                                | Monotonic ramp. Ramp rate is 10% to 90% of the final value | 0.1                  |                    | 100             | ms       | 1     |  |  |

|                                                                                 | TEMPERATI                                                  | JRE SENSOR           |                    |                 |          |       |  |  |

| Operating Range                                                                 | Ambient                                                    | -40                  |                    | 85              | °C       |       |  |  |

| Sensitivity                                                                     | Untrimmed                                                  |                      | 333.87             |                 | LSB/°C   | 1     |  |  |

| Room Temp Offset                                                                | 21°C                                                       |                      | 0                  |                 | LSB      |       |  |  |

|                                                                                 | Power-C                                                    | n RESET              |                    | <u>l</u>        |          | -1    |  |  |

| Supply Ramp Time (T <sub>RAMP</sub> )                                           | Valid power-on RESET                                       | 0.01                 | 20                 | 100             | ms       | 1     |  |  |

| Start-up time for register read/write                                           | From power-up                                              |                      | 11                 | 100             | ms       | 1     |  |  |

| I <sup>2</sup> C ADDRESS                                                        | AD0 = 0<br>AD0 = 1                                         |                      | 1101000<br>1101001 |                 |          |       |  |  |

|                                                                                 | DIGITAL INPUTS (FSYI                                       | NC, AD0, SCLK        | , SDI, CS)         |                 |          |       |  |  |

| V <sub>IH</sub> , High Level Input Voltage                                      |                                                            | 0.7*VDDIO            |                    |                 | V        |       |  |  |

| V <sub>IL</sub> , Low Level Input Voltage                                       |                                                            |                      |                    | 0.3*VDDIO       | V        | 1     |  |  |

| C <sub>I</sub> , Input Capacitance                                              |                                                            |                      | < 10               |                 | pF       | 1     |  |  |

|                                                                                 | DIGITAL OUT                                                | PUT (SDO, INT)       |                    |                 |          |       |  |  |

| V <sub>OH</sub> , High Level Output Voltage                                     | $R_{LOAD}=1M\Omega$ ;                                      | 0.9*VDDIO            |                    |                 | V        |       |  |  |

| V <sub>OL1</sub> , LOW-Level Output Voltage                                     | R <sub>LOAD</sub> =1MΩ;                                    |                      |                    | 0.1*VDDIO       | V        |       |  |  |

| V <sub>OL.INT1</sub> , INT Low-Level Output Voltage                             | OPEN=1, 0.3mA sink<br>Current                              |                      |                    | 0.1             | V        | 1     |  |  |

| Output Leakage Current                                                          | OPEN=1                                                     |                      | 100                |                 | nA       |       |  |  |

| t <sub>INT</sub> , INT Pulse Width                                              | LATCH_INT_EN=0                                             |                      | 50                 |                 | μs       |       |  |  |

|                                                                                 | 12C I/O (S                                                 | SCL, SDA)            |                    |                 |          |       |  |  |

| V <sub>IL</sub> , LOW Level Input Voltage                                       |                                                            | -0.5V                |                    | 0.3*VDDIO       | V        |       |  |  |

| V <sub>IH</sub> , HIGH-Level Input Voltage                                      |                                                            | 0.7*VDDIO            |                    | VDDIO +<br>0.5V | V        |       |  |  |

| V <sub>hys</sub> , Hysteresis                                                   |                                                            |                      | 0.1*VDDIO          |                 | V        |       |  |  |

| V <sub>OL</sub> , LOW-Level Output Voltage                                      | 3mA sink current                                           | 0                    |                    | 0.4             | V        | 1     |  |  |

| I <sub>OL</sub> , LOW-Level Output Current                                      | V <sub>OL</sub> =0.4V<br>V <sub>OL</sub> =0.6V             |                      | 3<br>6             |                 | mA<br>mA |       |  |  |

| Output Leakage Current                                                          |                                                            |                      | 100                |                 | nA       |       |  |  |

| $t_{\text{of}},$ Output Fall Time from $V_{\text{IHmax}}$ to $V_{\text{ILmax}}$ | C <sub>b</sub> bus capacitance in pf                       | 20+0.1C <sub>b</sub> |                    | 250             | ns       |       |  |  |

|                                                                                 | AUXILLIARY I/O (                                           | AUX_CL, AUX_         | DA)                |                 |          |       |  |  |

| V <sub>IL</sub> , LOW-Level Input Voltage                                       |                                                            | -0.5V                |                    | 0.3*VDDIO       | V        |       |  |  |

| V <sub>IH</sub> , HIGH-Level Input Voltage                                      |                                                            | 0.7* VDDIO           |                    | VDDIO +<br>0.5V | V        | 1     |  |  |

| V <sub>hys</sub> , Hysteresis                                                   |                                                            |                      | 0.1* VDDIO         |                 | V        | 1     |  |  |

| V <sub>OL1</sub> , LOW-Level Output Voltage                                     | VDDIO > 2V; 1mA sink current                               | 0                    |                    | 0.4             | V        |       |  |  |

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

| Parameter                                                                       | Conditions                                                          | MIN                  | TYP    | MAX        | Units    | NOTES |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|--------|------------|----------|-------|

| V <sub>OL3</sub> , LOW-Level Output Voltage                                     | VDDIO < 2V; 1mA sink current                                        | 0                    |        | 0.2* VDDIO | V        |       |

| I <sub>OL</sub> , LOW-Level Output Current                                      | $\begin{array}{ccc} V_{OL} & = & 0.4V \\ V_{OL} = 0.6V \end{array}$ |                      | 3<br>6 |            | mA<br>mA |       |

| Output Leakage Current                                                          |                                                                     |                      | 100    |            | nA       |       |

| $t_{\text{of}},$ Output Fall Time from $V_{\text{IHmax}}$ to $V_{\text{ILmax}}$ | C <sub>b</sub> bus capacitance in pF                                | 20+0.1C <sub>b</sub> |        | 250        | ns       |       |

|                                                                                 | INTERNAL CL                                                         | OCK SOURCE           |        |            |          |       |

|                                                                                 | Fchoice=0,1,2<br>SMPLRT_DIV=0                                       |                      | 32     |            | kHz      | 2     |

| Sample Rate                                                                     | Fchoice=3;<br>DLPFCFG=0 or 7<br>SMPLRT_DIV=0                        |                      | 8      |            | kHz      | 2     |

|                                                                                 | Fchoice=3;<br>DLPFCFG=1,2,3,4,5,6;<br>SMPLRT_DIV=0                  |                      | 1      |            | kHz      | 2     |

| Clash Francisco de la litical Talancas                                          | CLK_SEL=0, 6; 25°C                                                  | -2                   |        | +2         | %        | 1     |

| Clock Frequency Initial Tolerance                                               | CLK_SEL=1,2,3,4,5; 25°C                                             | -1                   |        | +1         | %        | 1     |

| Fraguency Variation over Townsersture                                           | CLK_SEL=0,6                                                         | -10                  |        | +10        | %        | 1     |

| Frequency Variation over Temperature                                            | CLK_SEL=1,2,3,4,5                                                   |                      | ±1     |            | %        | 1     |

**Table 4: A.C. Electrical Characteristics**

#### Notes:

- 1. Derived from validation or characterization of parts, not guaranteed in production.

- Guaranteed by design.

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

#### 3.3.3 **Other Electrical Specifications**

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                                         | CONDITIONS                   | MIN | TYP         | MAX | Units | Notes |  |  |

|-------------------------------------------------------------------|------------------------------|-----|-------------|-----|-------|-------|--|--|

| SERIAL INTERFACE                                                  |                              |     |             |     |       |       |  |  |

| SPI Operating Frequency, All<br>Registers Read/Write              | Low Speed Characterization   |     | 100<br>±10% |     | kHz   | 1     |  |  |

| Registers Read/Write                                              | High Speed Characterization  |     | 1 ±10%      |     | MHz   | 1     |  |  |

| SPI Operating Frequency, Sensor and Interrupt Registers Read Only |                              |     | 20 ±10%     |     | MHz   | 1     |  |  |

| I <sup>2</sup> C Operating Frequency                              | All registers, Fast-mode     |     |             | 400 | kHz   | 1     |  |  |

| To Operating Frequency                                            | All registers, Standard-mode |     |             | 100 | kHz   | 1     |  |  |

**Table 5: Other Electrical Specifications**

#### Notes:

1. Derived from validation or characterization of parts, not guaranteed in production.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3.4 I2C Timing Characterization

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| Parameters                                                        | Conditions                               | Min                  | Typical | Max | Units | Notes |

|-------------------------------------------------------------------|------------------------------------------|----------------------|---------|-----|-------|-------|

| I <sup>2</sup> C TIMING                                           | I <sup>2</sup> C FAST-MODE               |                      |         |     |       | 1     |

| f <sub>SCL</sub> , SCL Clock Frequency                            |                                          |                      |         | 400 | kHz   | 2     |

| t <sub>HD.STA</sub> , (Repeated) START Condition Hold Time        |                                          | 0.6                  |         |     | μs    | 2     |

| t <sub>LOW</sub> , SCL Low Period                                 |                                          | 1.3                  |         |     | μs    | 2     |

| t <sub>HIGH</sub> , SCL High Period                               |                                          | 0.6                  |         |     | μs    | 2     |

| t <sub>SU.STA</sub> , Repeated START Condition Setup<br>Time      |                                          | 0.6                  |         |     | μs    | 2     |

| t <sub>HD.DAT</sub> , SDA Data Hold Time                          |                                          | 0                    |         |     | μs    | 2     |

| t <sub>SU.DAT</sub> , SDA Data Setup Time                         |                                          | 100                  |         |     | ns    | 2     |

| t <sub>r</sub> , SDA and SCL Rise Time                            | C <sub>b</sub> bus cap. from 10 to 400pF | 20+0.1C <sub>b</sub> |         | 300 | ns    | 2     |

| t <sub>f</sub> , SDA and SCL Fall Time                            | C <sub>b</sub> bus cap. from 10 to 400pF | 20+0.1C <sub>b</sub> |         | 300 | ns    | 2     |

| t <sub>SU.STO</sub> , STOP Condition Setup Time                   |                                          | 0.6                  |         |     | μs    | 2     |

| t <sub>BUF</sub> , Bus Free Time Between STOP and START Condition |                                          | 1.3                  |         |     | μs    | 2     |

| C <sub>b</sub> , Capacitive Load for each Bus Line                |                                          |                      | < 400   |     | pF    | 2     |

| t <sub>VD.DAT</sub> , Data Valid Time                             | _                                        |                      |         | 0.9 | μs    | 2     |

| t <sub>VD.ACK</sub> , Data Valid Acknowledge Time                 |                                          |                      |         | 0.9 | μs    | 2     |

Table 6: I<sup>2</sup>C Timing Characteristics

#### Notes:

- 1. Timing Characteristics apply to both Primary and Auxiliary I2C Bus

- 2. Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets

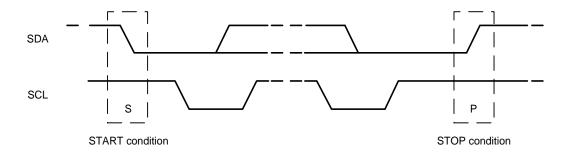

Figure 1: I2C Bus Timing Diagram

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3.5 SPI Timing Characterization

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| Parameters                                     | Conditions               | Min | Typical | Max | Units | Notes |

|------------------------------------------------|--------------------------|-----|---------|-----|-------|-------|

| SPI TIMING                                     |                          |     |         |     |       |       |

| f <sub>SCLK</sub> , SCLK Clock Frequency       |                          |     |         | 1   | MHz   | 1     |

| t <sub>LOW</sub> , SCLK Low Period             |                          | 400 |         |     | ns    | 1     |

| t <sub>HIGH</sub> , SCLK High Period           |                          | 400 |         |     | ns    | 1     |

| t <sub>SU.CS</sub> , CS Setup Time             |                          | 8   |         |     | ns    | 1     |

| t <sub>HD.CS</sub> , CS Hold Time              |                          | 500 |         |     | ns    | 1     |

| t <sub>SU.SDI</sub> , SDI Setup Time           |                          | 11  |         |     | ns    | 1     |

| t <sub>HD.SDI</sub> , SDI Hold Time            |                          | 7   |         |     | ns    | 1     |

| t <sub>VD.SDO</sub> , SDO Valid Time           | C <sub>load</sub> = 20pF |     |         | 100 | ns    | 1     |

| t <sub>HD.SDO</sub> , SDO Hold Time            | C <sub>load</sub> = 20pF | 4   |         |     | ns    | 1     |

| t <sub>DIS.SDO</sub> , SDO Output Disable Time |                          |     |         | 50  | ns    | 1     |

**Table 7: SPI Timing Characteristics**

#### Notes:

1. Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets

Figure 2: SPI Bus Timing Diagram

#### 3.5.1 fSCLK = 20MHz

| Parameters                               | Conditions | Min | Typical | Max | Units | Notes |

|------------------------------------------|------------|-----|---------|-----|-------|-------|

| SPI TIMING                               |            |     |         |     |       |       |

| f <sub>SCLK</sub> , SCLK Clock Frequency |            | 0.9 |         | 20  | MHz   | 1     |

| t <sub>LOW</sub> , SCLK Low Period       |            | -   |         | -   | ns    |       |

| t <sub>HIGH</sub> , SCLK High Period     |            | -   |         | -   | ns    |       |

| t <sub>SU.CS</sub> , CS Setup Time       |            | 1   |         |     | ns    | 1     |

| t <sub>HD.CS</sub> , CS Hold Time        |            | 1   |         |     | ns    | 1     |

Document Number: PS-MPU-6500A-01

Revision: 1.1 Release Date: 03/05/2014

| t <sub>SU.SDI</sub> , SDI Setup Time           |                          | 0 |    |    | ns | 1 |

|------------------------------------------------|--------------------------|---|----|----|----|---|

| t <sub>HD.SDI</sub> , SDI Hold Time            |                          | 1 |    |    | ns | 1 |

| t <sub>VD.SDO</sub> , SDO Valid Time           | C <sub>load</sub> = 20pF |   | 25 |    | ns | 1 |

| t <sub>DIS.SDO</sub> , SDO Output Disable Time |                          |   |    | 25 | ns | 1 |

Table 8: fCLK = 20MHz

#### Notes:

1. Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 3.6 Absolute Maximum Ratings

Stress above those listed as "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to the absolute maximum ratings conditions for extended periods may affect device reliability.

| Parameter                                               | Rating                           |

|---------------------------------------------------------|----------------------------------|

| Supply Voltage, VDD                                     | -0.5V to +4V                     |

| Supply Voltage, VDDIO                                   | -0.5V to +4V                     |

| REGOUT                                                  | -0.5V to 2V                      |

| Input Voltage Level (AUX_DA, AD0, FSYNC, INT, SCL, SDA) | -0.5V to VDD + 0.5V              |

| Acceleration (Any Axis, unpowered)                      | 10,000g for 0.2ms                |

| Operating Temperature Range                             | -40°C to +105°C                  |

| Storage Temperature Range                               | -40°C to +125°C                  |

| Electrostatic Discharge (ESD) Protection                | 2kV (HBM);<br>250V (MM)          |

| Latch-up                                                | JEDEC Class II (2),125°C, ±100mA |

**Table 9: Absolute Maximum Ratings**

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

## 4 Applications Information

## 4.1 Pin Out Diagram and Signal Description

| Pin Number     | Pin Name   | Pin Description                                                                                                                                                                         |  |  |  |

|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7              | AUX_CL     | I <sup>2</sup> C Master serial clock, for connecting to external sensors                                                                                                                |  |  |  |

| 8              | VDDIO      | Digital I/O supply voltage                                                                                                                                                              |  |  |  |

| 9              | AD0/SDO    | I <sup>2</sup> C Slave Address LSB (AD0); SPI serial data output (SDO)                                                                                                                  |  |  |  |

| 10             | REGOUT     | Regulator filter capacitor connection                                                                                                                                                   |  |  |  |

| 11             | FSYNC      | Frame synchronization digital input. Connect to GND if unused.                                                                                                                          |  |  |  |

| 12             | INT        | Interrupt digital output (totem pole or open-drain)  Note: The Interrupt line should be connected to a pin on the Application Processor (AP) that can bring the AP out of suspend mode. |  |  |  |

| 13             | VDD        | Power supply voltage and Digital I/O supply voltage                                                                                                                                     |  |  |  |

| 18             | GND        | Power supply ground                                                                                                                                                                     |  |  |  |

| 19             | RESV       | Reserved. Do not connect.                                                                                                                                                               |  |  |  |

| 20             | RESV       | Reserved. Connect to GND.                                                                                                                                                               |  |  |  |

| 21             | AUX_DA     | I <sup>2</sup> C master serial data, for connecting to external sensors                                                                                                                 |  |  |  |

| 22             | nCS        | Chip select (SPI mode only)                                                                                                                                                             |  |  |  |

| 23             | SCL / SCLK | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)                                                                                                                            |  |  |  |

| 24             | SDA / SDI  | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)                                                                                                                         |  |  |  |

| 1 – 6, 14 - 17 | NC         | No Connect pins. Do not connect.                                                                                                                                                        |  |  |  |

**Table 10: Signal Descriptions**

Figure 3: Pin out Diagram for MPU-6500 3.0x3.0x0.9mm QFN

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 4.2 Typical Operating Circuit

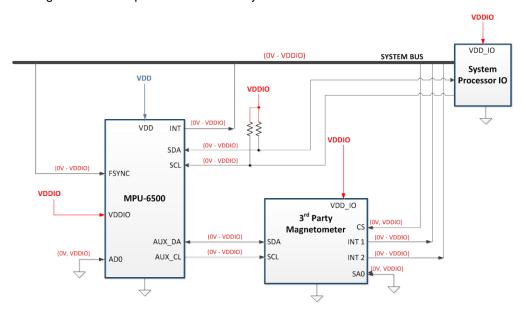

Figure 4: MPU-6500 QFN Application Schematic. (a) I2C operation, (b) SPI operation.

#### 4.3 Bill of Materials for External Components

| Component                  | Label | Specification                | Quantity |

|----------------------------|-------|------------------------------|----------|

| Regulator Filter Capacitor | C1    | Ceramic, X7R, 0.1µF ±10%, 2V | 1        |

| VDD Bypass Capacitor       | C2    | Ceramic, X7R, 0.1µF ±10%, 4V | 1        |

| VDDIO Bypass Capacitor     | C3    | Ceramic, X7R, 10nF ±10%, 4V  | 1        |

**Table 11: Bill of Materials**

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 4.4 Block Diagram

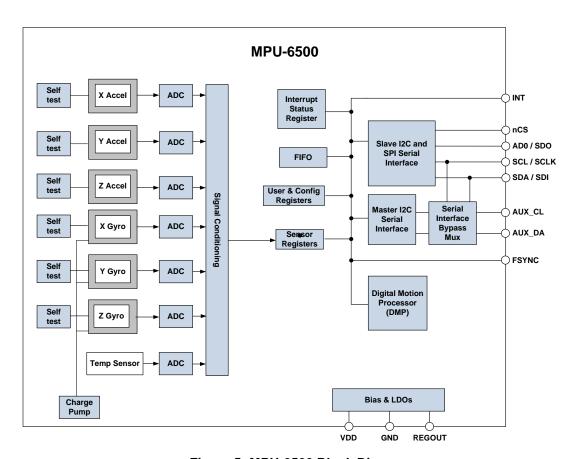

Figure 5: MPU-6500 Block Diagram

Note: The Interrupt line should be connected to a pin on the Application Processor (AP) that can bring the AP out of suspend mode.

#### 4.5 Overview

The MPU-6500 is comprised of the following key blocks and functions:

- Three-axis MEMS rate gyroscope sensor with 16-bit ADCs and signal conditioning

- Three-axis MEMS accelerometer sensor with 16-bit ADCs and signal conditioning

- Digital Motion Processor (DMP) engine

- Primary I<sup>2</sup>C and SPI serial communications interfaces

- Auxiliary I<sup>2</sup>C serial interface

- Self-Test

- Clocking

- Sensor Data Registers

- FIFO

- Interrupts

- Digital-Output Temperature Sensor

- Bias and LDOs

- Charge Pump

- Standard Power Modes

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 4.6 Three-Axis MEMS Gyroscope with 16-bit ADCs and Signal Conditioning

The MPU-6500 consists of three independent vibratory MEMS rate gyroscopes, which detect rotation about the X-, Y-, and Z- Axes. When the gyros are rotated about any of the sense axes, the Coriolis Effect causes a vibration that is detected by a capacitive pickoff. The resulting signal is amplified, demodulated, and filtered to produce a voltage that is proportional to the angular rate. This voltage is digitized using individual on-chip 16-bit Analog-to-Digital Converters (ADCs) to sample each axis. The full-scale range of the gyro sensors may be digitally programmed to ±250, ±500, ±1000, or ±2000 degrees per second (dps). The ADC sample rate is programmable from 8,000 samples per second, down to 3.9 samples per second, and user-selectable low-pass filters enable a wide range of cut-off frequencies.

#### 4.7 Three-Axis MEMS Accelerometer with 16-bit ADCs and Signal Conditioning

The MPU-6500's 3-Axis accelerometer uses separate proof masses for each axis. Acceleration along a particular axis induces displacement on the corresponding proof mass, and capacitive sensors detect the displacement differentially. The MPU-6500's architecture reduces the accelerometers' susceptibility to fabrication variations as well as to thermal drift. When the device is placed on a flat surface, it will measure 0g on the X- and Y-axes and +1g on the Z-axis. The accelerometers' scale factor is calibrated at the factory and is nominally independent of supply voltage. Each sensor has a dedicated sigma-delta ADC for providing digital outputs. The full scale range of the digital output can be adjusted to  $\pm 2g$ ,  $\pm 4g$ ,  $\pm 8g$ , or  $\pm 16g$ .

#### 4.8 Digital Motion Processor

The embedded Digital Motion Processor (DMP) within the MPU-6500 offloads computation of motion processing algorithms from the host processor. The DMP acquires data from accelerometers, gyroscopes, and additional 3<sup>rd</sup> party sensors such as magnetometers, and processes the data. The resulting data can be read from the FIFO. The DMP has access to one of the MPU's external pins, which can be used for generating interrupts.

The purpose of the DMP is to offload both timing requirements and processing power from the host processor. Typically, motion processing algorithms should be run at a high rate, often around 200Hz, in order to provide accurate results with low latency. This is required even if the application updates at a much lower rate; for example, a low power user interface may update as slowly as 5Hz, but the motion processing should still run at 200Hz. The DMP can be used to minimize power, simplify timing, simplify the software architecture, and save valuable MIPS on the host processor for use in applications.

The DMP supports the following functionality:

- Low Power Quaternion (3-Axis Gyroscope)

- Screen Orientation (A low-power implementation of Android's screen rotation algorithm)

- Pedometer (InvenSense implementation)

#### 4.9 Primary I2C and SPI Serial Communications Interfaces

The MPU-6500 communicates to a system processor using either a SPI or an I<sup>2</sup>C serial interface. The MPU-6500 always acts as a slave when communicating to the system processor. The LSB of the of the I<sup>2</sup>C slave address is set by pin 9 (AD0).

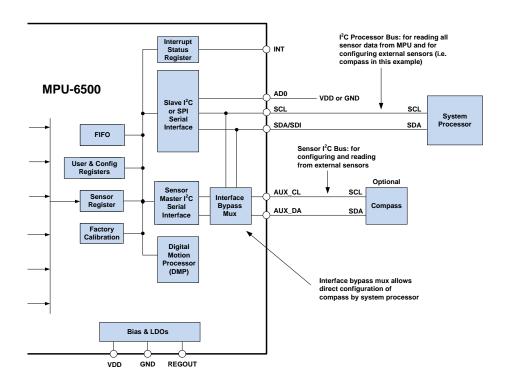

#### 4.9.1 MPU-6500 Solution Using I2C Interface

In the figure below, the system processor is an I<sup>2</sup>C master to the MPU-6500. In addition, the MPU-6500 is an I<sup>2</sup>C master to the optional external compass sensor. The MPU-6500 has limited capabilities as an I<sup>2</sup>C Master, and depends on the system processor to manage the initial configuration of any auxiliary sensors.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

The MPU-6500 has an interface bypass multiplexer, which connects the system processor I<sup>2</sup>C bus pins 23 and 24 (SDA and SCL) directly to the auxiliary sensor I<sup>2</sup>C bus pins 6 and 7 (AUX\_DA and AUX\_CL).

Once the auxiliary sensors have been configured by the system processor, the interface bypass multiplexer should be disabled so that the MPU-6500 auxiliary I<sup>2</sup>C master can take control of the sensor I<sup>2</sup>C bus and gather data from the auxiliary sensors.

For further information regarding I<sup>2</sup>C master control, please refer to section 6.

Figure 6: MPU-6500 Solution Using I<sup>2</sup>C Interface

Note: The Interrupt line should be connected to a pin on the Application Processor (AP) that can bring the AP out of suspend mode.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

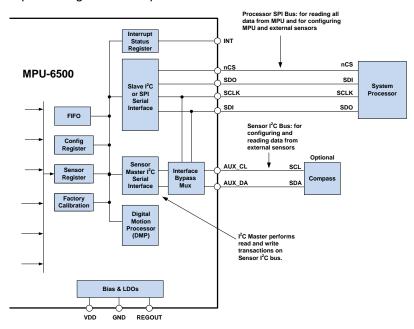

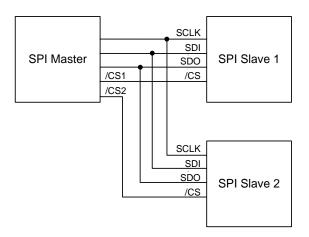

#### 4.9.2 MPU-6500 Solution Using SPI Interface

In the figure below, the system processor is an SPI master to the MPU-6500. Pins 8, 9, 23, and 24 are used to support the CS, SDO, SCLK, and SDI signals for SPI communications. Because these SPI pins are shared with the I<sup>2</sup>C slave pins (9, 23 and 24), the system processor cannot access the auxiliary I<sup>2</sup>C bus through the interface bypass multiplexer, which connects the processor I<sup>2</sup>C interface pins to the sensor I<sup>2</sup>C interface pins. Since the MPU-6500 has limited capabilities as an I<sup>2</sup>C Master, and depends on the system processor to manage the initial configuration of any auxiliary sensors, another method must be used for programming the sensors on the auxiliary sensor I<sup>2</sup>C bus pins 6 and 7 (AUX\_DA and AUX\_CL).

When using SPI communications between the MPU-6500 and the system processor, configuration of devices on the auxiliary  $I^2C$  sensor bus can be achieved by using  $I^2C$  Slaves 0-4 to perform read and write transactions on any device and register on the auxiliary  $I^2C$  bus. The  $I^2C$  Slave 4 interface can be used to perform only single byte read and write transactions. Once the external sensors have been configured, the MPU-6500 can perform single or multi-byte reads using the sensor  $I^2C$  bus. The read results from the Slave 0-3 controllers can be written to the FIFO buffer as well as to the external sensor registers.

For further information regarding the control of the MPU-6500's auxiliary I<sup>2</sup>C interface, please refer to the MPU-6500 Register Map and Register Descriptions document.

Figure 7: MPU-6500 Solution Using SPI Interface

Note: The Interrupt line should be connected to a pin on the Application Processor (AP) that can bring the AP out of suspend mode.

#### 4.10 Auxiliary I2C Serial Interface

The MPU-6500 has an auxiliary I<sup>2</sup>C bus for communicating to an off-chip 3-Axis digital output magnetometer or other sensors. This bus has two operating modes:

- I<sup>2</sup>C Master Mode: The MPU-6500 acts as a master to any external sensors connected to the auxiliary I<sup>2</sup>C bus

- <u>Pass-Through Mode</u>: The MPU-6500 directly connects the primary and auxiliary I<sup>2</sup>C buses together, allowing the system processor to directly communicate with any external sensors.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

## Auxiliary I<sup>2</sup>C Bus Modes of Operation:

• <u>I<sup>2</sup>C Master Mode</u>: Allows the MPU-6500 to directly access the data registers of external digital sensors, such as a magnetometer. In this mode, the MPU-6500 directly obtains data from auxiliary sensors without intervention from the system applications processor.

For example, In I<sup>2</sup>C Master mode, the MPU-6500 can be configured to perform burst reads, returning the following data from a magnetometer:

- X magnetometer data (2 bytes)

- Y magnetometer data (2 bytes)

- Z magnetometer data (2 bytes)

The I<sup>2</sup>C Master can be configured to read up to 24 bytes from up to 4 auxiliary sensors. A fifth sensor can be configured to work single byte read/write mode.

Pass-Through Mode: Allows an external system processor to act as master and directly communicate to the external sensors connected to the auxiliary I<sup>2</sup>C bus pins (AUX\_DA and AUX\_CL). In this mode, the auxiliary I<sup>2</sup>C bus control logic (3<sup>rd</sup> party sensor interface block) of the MPU-6500 is disabled, and the auxiliary I<sup>2</sup>C pins AUX\_DA and AUX\_CL (Pins 6 and 7) are connected to the main I<sup>2</sup>C bus (Pins 23 and 24) through analog switches internally. Pass-Through mode is useful for configuring the external sensors, or for keeping the MPU-6500 in a low-power mode when only the external sensors are used. In this mode the system processor can still access MPU-6500 data through the I<sup>2</sup>C interface.

#### 4.11 Self-Test

Please refer to the register map document for more details on self-test.

Self-test allows for the testing of the mechanical and electrical portions of the sensors. The self-test for each measurement axis can be activated by means of the gyroscope and accelerometer self-test registers (registers 13 to 16).

When the self-test is activated, the electronics cause the sensors to be actuated and produce an output signal. The output signal is used to observe the self-test response.

The self-test response is defined as follows:

Self-test response = Sensor output with self-test enabled - Sensor output without self-test enabled

The self-test response for each gyroscope axis is defined in the gyroscope specification table, while that for each accelerometer axis is defined in the accelerometer specification table.

When the value of the self-test response is within the specified min/max limits of the product specification, the part has passed self-test. When the self-test response exceeds the min/max values, the part is deemed to have failed self-test. It is recommended to use InvenSense MotionApps software for executing self-test.

#### 4.12 Clocking

The MPU-6500 has a flexible clocking scheme, allowing a variety of internal clock sources to be used for the internal synchronous circuitry. This synchronous circuitry includes the signal conditioning and ADCs, the DMP, and various control circuits and registers. An on-chip PLL provides flexibility in the allowable inputs for generating this clock.

Allowable internal sources for generating the internal clock are:

- An internal relaxation oscillator

- Any of the X, Y, or Z gyros (MEMS oscillators with a variation of ±1% over temperature)

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

Selection of the source for generating the internal synchronous clock depends on the requirements for power consumption and clock accuracy. These requirements will most likely vary by mode of operation. For example, in one mode, where the biggest concern is power consumption, the user may wish to operate the Digital Motion Processor of the MPU-6500 to process accelerometer data, while keeping the gyros off. In this case, the internal relaxation oscillator is a good clock choice. However, in another mode, where the gyros are active, selecting the gyros as the clock source provides for a more accurate clock source.

Clock accuracy is important, since timing errors directly affect the distance and angle calculations performed by the Digital Motion Processor (and by extension, by any processor).

There are also start-up conditions to consider. When the MPU-6500 first starts up, the device uses its internal clock until programmed to operate from another source. This allows the user, for example, to wait for the MEMS oscillators to stabilize before they are selected as the clock source.

#### 4.13 Sensor Data Registers

The sensor data registers contain the latest gyro, accelerometer, auxiliary sensor, and temperature measurement data. They are read-only registers, and are accessed via the serial interface. Data from these registers may be read anytime.

#### 4.14 FIFO

The MPU-6500 contains a 512-byte FIFO register that is accessible via the Serial Interface. The FIFO configuration register determines which data is written into the FIFO. Possible choices include gyro data, accelerometer data, temperature readings, auxiliary sensor readings, and FSYNC input. A FIFO counter keeps track of how many bytes of valid data are contained in the FIFO. The FIFO register supports burst reads. The interrupt function may be used to determine when new data is available.

For further information regarding the FIFO, please refer to the MPU-6500 Register Map and Register Descriptions document.

#### 4.15 Interrupts

Interrupt functionality is configured via the Interrupt Configuration register. Items that are configurable include the INT pin configuration, the interrupt latching and clearing method, and triggers for the interrupt. Items that can trigger an interrupt are (1) Clock generator locked to new reference oscillator (used when switching clock sources); (2) new data is available to be read (from the FIFO and Data registers); (3) accelerometer event interrupts; and (4) the MPU-6500 did not receive an acknowledge from an auxiliary sensor on the secondary I<sup>2</sup>C bus. The interrupt status can be read from the Interrupt Status register.

For further information regarding interrupts, please refer to the MPU-6500 Register Map and Register Descriptions document.

#### 4.16 Digital-Output Temperature Sensor

An on-chip temperature sensor and ADC are used to measure the MPU-6500 die temperature. The readings from the ADC can be read from the FIFO or the Sensor Data registers.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### 4.17 Bias and LDOs

The bias and LDO section generates the internal supply and the reference voltages and currents required by the MPU-6500. Its two inputs are an unregulated VDD and a VDDIO logic reference supply voltage. The LDO output is bypassed by a capacitor at REGOUT. For further details on the capacitor, please refer to the Bill of Materials for External Components.

#### 4.18 Charge Pump

An on-chip charge pump generates the high voltage required for the MEMS oscillators.

#### 4.19 Standard Power Modes

The following table lists the user-accessible power modes for MPU-6500.

| Mode | Name                         | Gyro     | Accel       | DMP       |

|------|------------------------------|----------|-------------|-----------|

| 1    | Sleep Mode                   | Off      | Off         | Off       |

| 2    | Standby Mode                 | Drive On | Off         | Off       |

| 3    | Low-Power Accelerometer Mode | Off      | Duty-Cycled | Off       |

| 4    | Low-Noise Accelerometer Mode | Off      | On          | Off       |

| 5    | Gyroscope Mode               | On       | Off         | On or Off |

| 6    | 6-Axis Mode                  | On       | On          | On or Off |

**Table 12: Standard Power Modes for MPU-6500**

#### Notes:

1. Power consumption for individual modes can be found in section 3.3.1.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

## 5 Programmable Interrupts

The MPU-6500 has a programmable interrupt system which can generate an interrupt signal on the INT pin. Status flags indicate the source of an interrupt. Interrupt sources may be enabled and disabled individually.

| Interrupt Name                                          | Module                  |

|---------------------------------------------------------|-------------------------|

| Motion Detection                                        | Motion                  |

| FIFO Overflow                                           | FIFO                    |

| Data Ready                                              | Sensor Registers        |

| I <sup>2</sup> C Master errors: Lost Arbitration, NACKs | I <sup>2</sup> C Master |

| I <sup>2</sup> C Slave 4                                | I <sup>2</sup> C Master |

**Table 13: Table of Interrupt Sources**

For information regarding the interrupt enable/disable registers and flag registers, please refer to the MPU-6500 Register Map and Register Descriptions document. Some interrupt sources are explained below.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

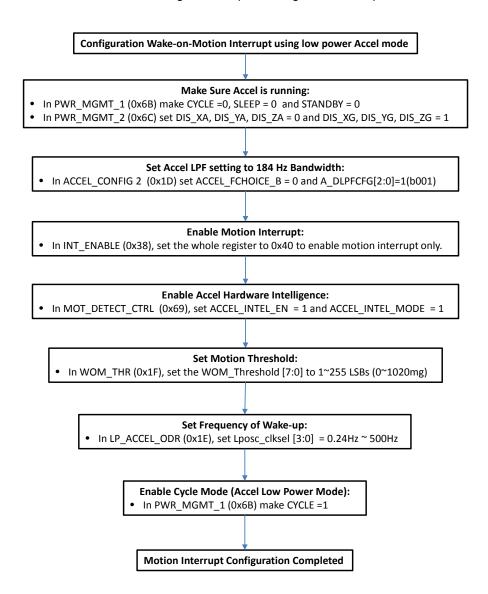

#### 5.1 Wake-on-Motion Interrupt

The MPU-6500 provides motion detection capability. A qualifying motion sample is one where the high passed sample from any axis has an absolute value exceeding a user-programmable threshold. The following flowchart explains how to configure the Wake-on-Motion Interrupt. For further details on individual registers, please refer to the MPU-6500 Registers Map and Registers Description document.

Figure 8: Wake-on-Motion Interrupt Configuration

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

## 6 Digital Interface

#### 6.1 I2C and SPI Serial Interfaces

The internal registers and memory of the MPU-6500 can be accessed using either I<sup>2</sup>C at 400 kHz or SPI at 1MHz. SPI operates in four-wire mode.

| Pin Number | Pin Name   | Pin Description                                                        |

|------------|------------|------------------------------------------------------------------------|

| 6          | VDDIO      | Digital I/O supply voltage.                                            |

| 7          | AD0/SDO    | I <sup>2</sup> C Slave Address LSB (AD0); SPI serial data output (SDO) |

| 21         | SCL / SCLK | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)           |

| 22         | SDA / SDI  | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)        |

**Table 14: Serial Interface**

#### Note:

To prevent switching into I<sup>2</sup>C mode when using SPI, the I<sup>2</sup>C interface should be disabled by setting the I2C\_IF\_DIS configuration bit. Setting this bit should be performed immediately after waiting for the time specified by the "Start-Up Time for Register Read/Write" in Section 6.3.

For further information regarding the *I2C\_IF\_DIS* bit, please refer to the MPU-6500 Register Map and Register Descriptions document.

#### 6.2 I2C Interface

I<sup>2</sup>C is a two-wire interface comprised of the signals serial data (SDA) and serial clock (SCL). In general, the lines are open-drain and bi-directional. In a generalized I<sup>2</sup>C interface implementation, attached devices can be a master or a slave. The master device puts the slave address on the bus, and the slave device with the matching address acknowledges the master.

The MPU-6500 always operates as a slave device when communicating to the system processor, which thus acts as the master. SDA and SCL lines typically need pull-up resistors to VDD. The maximum bus speed is 400 kHz.

The slave address of the MPU-6500 is b110100X which is 7 bits long. The LSB bit of the 7 bit address is determined by the logic level on pin AD0. This allows two MPU-6500s to be connected to the same I<sup>2</sup>C bus. When used in this configuration, the address of the one of the devices should be b1101000 (pin AD0 is logic low) and the address of the other should be b1101001 (pin AD0 is logic high).

#### 6.3 I2C Communications Protocol

START (S) and STOP (P) Conditions

Communication on the I<sup>2</sup>C bus starts when the master puts the START condition (S) on the bus, which is defined as a HIGH-to-LOW transition of the SDA line while SCL line is HIGH (see figure below). The bus is considered to be busy until the master puts a STOP condition (P) on the bus, which is defined as a LOW to HIGH transition on the SDA line while SCL is HIGH (see figure below).

Additionally, the bus remains busy if a repeated START (Sr) is generated instead of a STOP condition.

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

Figure 9: START and STOP Conditions

#### Data Format / Acknowledge

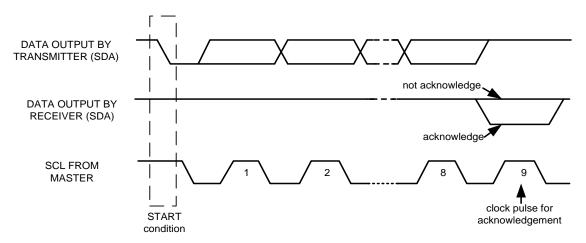

I<sup>2</sup>C data bytes are defined to be 8-bits long. There is no restriction to the number of bytes transmitted per data transfer. Each byte transferred must be followed by an acknowledge (ACK) signal. The clock for the acknowledge signal is generated by the master, while the receiver generates the actual acknowledge signal by pulling down SDA and holding it low during the HIGH portion of the acknowledge clock pulse.

If a slave is busy and cannot transmit or receive another byte of data until some other task has been performed, it can hold SCL LOW, thus forcing the master into a wait state. Normal data transfer resumes when the slave is ready, and releases the clock line (refer to the following figure).

Figure 10: Acknowledge on the I<sup>2</sup>C Bus

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014

#### Communications

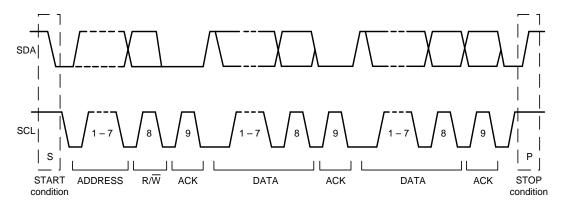

After beginning communications with the START condition (S), the master sends a 7-bit slave address followed by an 8<sup>th</sup> bit, the read/write bit. The read/write bit indicates whether the master is receiving data from or is writing to the slave device. Then, the master releases the SDA line and waits for the acknowledge signal (ACK) from the slave device. Each byte transferred must be followed by an acknowledge bit. To acknowledge, the slave device pulls the SDA line LOW and keeps it LOW for the high period of the SCL line. Data transmission is always terminated by the master with a STOP condition (P), thus freeing the communications line. However, the master can generate a repeated START condition (Sr), and address another slave without first generating a STOP condition (P). A LOW to HIGH transition on the SDA line while SCL is HIGH defines the stop condition. All SDA changes should take place when SCL is low, with the exception of start and stop conditions.

Figure 11: Complete I<sup>2</sup>C Data Transfer

To write the internal MPU-6500 registers, the master transmits the start condition (S), followed by the I<sup>2</sup>C address and the write bit (0). At the 9<sup>th</sup> clock cycle (when the clock is high), the MPU-6500 acknowledges the transfer. Then the master puts the register address (RA) on the bus. After the MPU-6500 acknowledges the reception of the register address, the master puts the register data onto the bus. This is followed by the ACK signal, and data transfer may be concluded by the stop condition (P). To write multiple bytes after the last ACK signal, the master can continue outputting data rather than transmitting a stop signal. In this case, the MPU-6500 automatically increments the register address and loads the data to the appropriate register. The following figures show single and two-byte write sequences.

#### Single-Byte Write Sequence

| Master | S | AD+W |     | RA |     | DATA |     | Р |

|--------|---|------|-----|----|-----|------|-----|---|

| Slave  |   |      | ACK |    | ACK |      | ACK |   |

#### Burst Write Sequence

| Master | S | AD+W |     | RA |     | DATA |     | DATA |     | Р |

|--------|---|------|-----|----|-----|------|-----|------|-----|---|

| Slave  |   |      | ACK |    | ACK |      | ACK |      | ACK |   |

Document Number: PS-MPU-6500A-01

Revision: 1.1

Release Date: 03/05/2014