# RENESAS

# DATASHEET

## D2-24044

Digital Audio Amplifier Power Stage

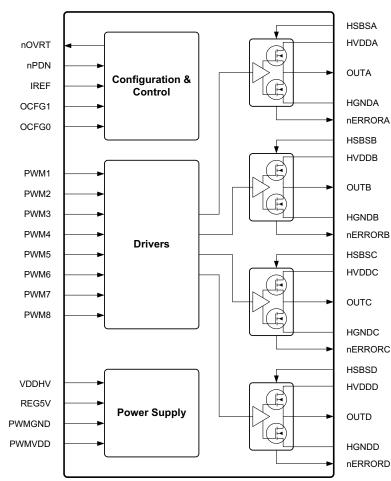

The D2-24044 device is a high performance, integrated Class-D amplifier power stage. The four power stage outputs are configurable as four separate Half-Bridge outputs, as two Full-Bridge outputs, or combinations of Half-Bridge and Full-Bridge. Individual power stage overload monitoring, on-chip temperature monitoring, and common alert logic outputs provide protection to integrate with the final system's controller. FN7678 Rev 0.00 Sep 3, 2010

## Features

- All Digital Class-D Power Stage

- 4 Configurable Power Stage Outputs Supporting:

- 2 Channels, Bridged

- 4 Channels, Half-Bridge

- 2 Channels, Half-Bridge, plus 1 Channel Bridged

- Output Power (Bridged)

- 25W (8Ω, <1% THD)

- 30W (8Ω, <10% THD)

- Single HV Supply Wide 9V-26V Range

- Gate Drive Supply Internally-Generated

- Individual Channel Protection Monitoring

- Temperature and Undervoltage Monitoring

- Efficient 38 Ld HTSSOP Package

# **Digital Amplifier Power Stage**

## **Ordering Information**

| PART<br>NUMBER<br>(Notes 2, 3) | NUMBER PART |            | TEMP.<br>RANGE (°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-------------|------------|---------------------|----------------------|----------------|

| D2-24044-MR                    | D2-24044-MR | Commercial | -10 to +85          | 38 Ld HTSSOP         | M38.173C       |

| D2-24044-MR-T (Note 1)         | D2-24044-MR | Commercial | -10 to +85          | 38 Ld HTSSOP         | M38.173C       |

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for the <u>D2-24044</u>. For more information on MSL please see techbrief <u>TB363</u>.

# **Table of Contents**

| Absolute Maximum Ratings                                                                                             | . 4                  |

|----------------------------------------------------------------------------------------------------------------------|----------------------|

| Thermal Information                                                                                                  | . 4                  |

| Recommended Operating Conditions                                                                                     | . 4                  |

| Electrical Specifications                                                                                            | . 4                  |

| Performance Specifications                                                                                           | . 5                  |

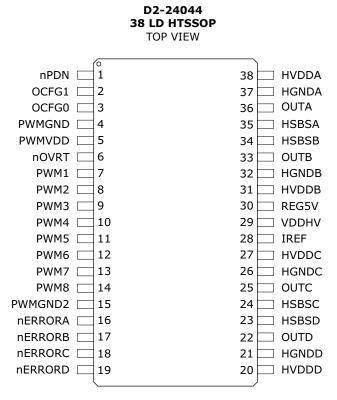

| Pin Configuration                                                                                                    | . 6                  |

| Pin Description                                                                                                      | . 6                  |

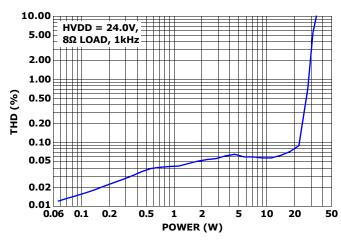

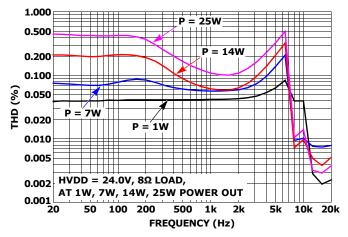

| Typical Performance Characteristics                                                                                  | . 8                  |

| Full-Bridge Typical Performance Curves<br>Half-Bridge Typical Performance Curves                                     |                      |

| Functional Overview                                                                                                  | 10                   |

| Output Options                                                                                                       | 10                   |

| Power Supply Requirements                                                                                            | 10                   |

| High Side Gate Drive Voltage<br>Supply Bypass Connection<br>REG5V                                                    | 10<br>10             |

| Input and Control Functions                                                                                          | 11                   |

| PWM Inputs<br>nPDN Input Pin<br>nERRORA-D Output Pins<br>nOVRT Output Pin<br>IREF Pin<br>OCFG0, OCFG1 Input Pins     | 11<br>11<br>11<br>11 |

| Protection                                                                                                           | 11                   |

| Short-Circuit and Overcurrent Sensing<br>Thermal Protection and Monitoring<br>Power Supply Voltage Monitoring        | 12                   |

| Output Mode Configurations                                                                                           | 14                   |

| Typical Application Examples   2-Channel Full Bridge Example.   2.1-Channel Example   4-Channel Half-Bridge Example. | 17<br>18<br>19       |

| Package Outline Drawing                                                                                              | 20                   |

#### **Absolute Maximum Ratings**

| Supply Voltage                |

|-------------------------------|

| HVDD[A:D], VDDHV 0V to +28.0V |

| PWMVDD                        |

| Input Voltage                 |

| Any Input                     |

#### **Thermal Information**

| Thermal Resistance (Typical)      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------|------------------------|------------------------|

| 38 Ld HTSSOP Package (Notes 4,    | 5) 29                  | 1.3                    |

| Maximum Storage Temperature       | 55°                    | 'C to +150°C           |

| Pb-Free Reflow Profile            | S                      | ee link below          |

| http://www.intersil.com/pbfree/Pb | -FreeReflow.           | <u>asp</u>             |

|                                   |                        |                        |

#### **Recommended Operating Conditions**

| Temperature Range10°C to +85°C                                             |

|----------------------------------------------------------------------------|

| High Voltage Supply Voltage,                                               |

| HVDD[A:D], VDDHV                                                           |

| Digital I/O Supply Voltage, PWMVDD                                         |

| Minimum Load Impedance (HVDD[A:D] $\leq$ 24.0V), Z <sub>L</sub> 4 $\Omega$ |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 6. Absolute Maximum parameters are not tested in production.

# **Electrical Specifications** $T_A = +25$ °C, PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| PARAMETER                                                                            | TEST<br>CONDITIONS                                                         | SYMBOL           | MIN        | түр  | мах | UNIT |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|------------|------|-----|------|

| Digital Input High Logic Level                                                       |                                                                            | V <sub>IH</sub>  | 2          | -    | -   | V    |

| Digital Input Low Logic Level                                                        |                                                                            | $V_{IL}$         | -          | -    | 0.4 | V    |

| High Level Output Drive Voltage<br>(I <sub>OUT</sub> at -Pin Drive Strength Current) |                                                                            | V <sub>OH</sub>  | PWMVDD-0.4 | -    | -   | V    |

| Low Level Output Drive Voltage<br>(I <sub>OUT</sub> at +Pin Drive Strength Current)  |                                                                            | V <sub>OL</sub>  | -          | -    | 0.4 | V    |

| Input Leakage Current                                                                | Pins 1, 2, 3                                                               | I <sub>IN</sub>  | -          | -    | ±10 | μA   |

|                                                                                      | PWM Input Pins (includes $100k\Omega$ internal pull-down resistor current) |                  | -          | -    | ±50 | μA   |

| Input Capacitance                                                                    |                                                                            | C <sub>IN</sub>  | -          | 9    | -   | pF   |

| Output Capacitance                                                                   | All Outputs Except OUT[A:D]                                                | C <sub>OUT</sub> | -          | 9    | -   | pF   |

|                                                                                      | OUT[A:D]                                                                   |                  | -          | 190  | -   |      |

| Internal Pull-Up Resistance to PWMVDD<br>(for nERRORA-D, nOVRT)                      |                                                                            |                  | -          | 100  | -   | kΩ   |

| Digital I/O Supply Pin Voltage, Current                                              |                                                                            | PWMVDD           | 3          | 3.3  | 3.6 | V    |

|                                                                                      | Active Current                                                             |                  | -          | 0.47 | -   | mA   |

|                                                                                      | Power-Down Current                                                         |                  | -          | 0.15 | -   | mA   |

| 3.3V (PWMVDD) BROWN-OUT DETECTION                                                    | 1                                                                          |                  | 1          | 1    | 1   | 1    |

| Logic Supply Undervoltage Threshold                                                  |                                                                            |                  | -          | 2.6  | -   | V    |

| Logic Supply Undervoltage Threshold Hysteresis                                       |                                                                            |                  | -          | 200  | -   | mV   |

| Logic Supply Undervoltage Glitch Rejection                                           |                                                                            |                  | -          | 50   | -   | ns   |

| GATE DRIVE INTERNAL +5V BROWN-OUT D                                                  | ETECTION                                                                   | 1                | 1          | 1    | 1   | 1    |

| Gate Drive Supply Undervoltage Threshold                                             |                                                                            |                  | -          | 4.5  | -   | V    |

# **Electrical Specifications** $T_A = +25$ °C, PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground. (Continued)

| PARAMETER                                                    | TEST<br>CONDITIONS | SYMBOL | MIN | ТҮР | мах | UNIT |

|--------------------------------------------------------------|--------------------|--------|-----|-----|-----|------|

| Gate Drive Supply Undervoltage Threshold<br>Hysteresis       |                    |        | -   | 200 | -   | mV   |

| Gate Drive Supply Undervoltage Threshold Glitch<br>Rejection |                    |        | -   | 50  | -   | ns   |

| PROTECTION DETECT                                            |                    |        |     |     |     | 1    |

| High Voltage Undervoltage Protection                         |                    |        | -   | 7   | 9   | V    |

| Overcurrent Trip Threshold                                   |                    |        | -   | 4   | -   | Α    |

| Overcurrent De-glitch                                        |                    |        | -   | 2.5 | -   | ns   |

| Short-Circuit Current Limit (Peak)                           |                    |        | -   | 8   | -   | Α    |

| Overcurrent Response Time                                    |                    |        | -   | 20  | -   | ns   |

| Thermal Shut-Down OTmax                                      |                    |        | -   | 140 | -   | °C   |

| Thermal Warning Temperature OTmin                            |                    |        | -   | 125 | -   | °C   |

| Thermal Shut-Down Hysteresis                                 |                    |        | -   | 30  | -   | °C   |

| Thermal Warning Hysteresis                                   |                    |        | -   | 20  | -   | °C   |

# **Performance Specifications** $T_A = +25$ °C, PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| PARAMETER                                                 | SYMBOL              | MIN | ТҮР  | MAX | UNIT     |

|-----------------------------------------------------------|---------------------|-----|------|-----|----------|

| r <sub>DS(ON)</sub> (MOSFETs @ +25°C)                     | r <sub>DS(ON)</sub> | -   | 200  | -   | mΩ       |

| r <sub>DS(ON)</sub> Mismatch                              |                     | -   | 1    | -   | %        |

| PWM Switching Rate                                        |                     | -   | 384  | -   | kHz      |

| Minimum PWM Pulse Width                                   |                     | -   | 3.5  | -   | ns       |

| PWM Off Sensor Time                                       |                     | -   | 10   | -   | μs       |

| PWM Input to Output Delay                                 |                     | -   |      | 50  | ns       |

| PWM Input to Output Delay Matching                        |                     | -   | 3    | -   | ns       |

| nPDN Input Off Delay                                      | T <sub>PDNOFF</sub> | -   | 1.4  | -   |          |

| nPDN Input On Delay                                       | T <sub>PDNON</sub>  | -   | 1.4  | -   |          |

| POWER OUTPUT                                              | I                   |     | 1    |     |          |

| <1% THD, Bridged, Load = $8\Omega$ , HVDD[A:D] = 24V      | POUT                | -   | 25   | -   | W        |

| <10% THD, Bridged, Load = $8\Omega$ , HVDD[A:D] = 24V     | POUT                | -   | 30   | -   | W        |

| <1% THD, Half-Bridge, Load = $8\Omega$ , HVDD[A:D] = 24V  | POUT                | -   | 7    | -   | W        |

| <10% THD, Half-Bridge, Load = $8\Omega$ , HVDD[A:D] = 24V | POUT                | -   | 9    | -   | W        |

| THD+N                                                     |                     |     | 1    | •   | <b>!</b> |

| Load = $8\Omega$ , Power = 25W, Bridged, 1kHz             | THD+N               | -   | 0.3  | -   | %        |

| Load = $8\Omega$ , Power = 1W, Bridged, 1kHz              |                     | -   | 0.05 | -   | %        |

| SNR                                                       | SNR                 | -   | 110  | -   | dB       |

| Efficiency (Load = $8\Omega$ )                            |                     | -   | 90   | -   | %        |

## **Pin Configuration**

## **Pin Description**

| PIN | PIN NAME<br>(Note 7) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                                                                                 |

|-----|----------------------|------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | nPDN                 | I    | 3.3                     | Power-down and mute input. Active low. When this input is low, all 4 outputs become inactive and their output stages float, and their output is muted. Internal logic and other references remain active during this power-down state.                      |

| 2   | OCFG1                | I    | 3.3                     | Output configuration control select. OCFG0 and OCFG1 are logic inputs to select the output configuration mode of the output stages. Connects to either PWMGND ground or PWMVDD (+3.3V) through nominal $10k\Omega$ resistor to select output configuration. |

| 3   | OCFG0                | I    | 3.3                     | Output configuration control select. OCFG0 and OCFG1 are logic inputs to select the output configuration mode of the output stages. Connects to either PWMGND ground or PWMVDD (+3.3V) through nominal $10k\Omega$ resistor to select output configuration. |

| 4   | PWMGND               | GND  | 0                       | Low-voltage ground. Connects to ground of circuitry providing PWM inputs. Both PWMGND and PWMGND2 are to tie together to the same ground.                                                                                                                   |

| 5   | PWMVDD               | Р    | 3.3                     | Low-voltage power. This 3.3V supply connects to the same system low-voltage power used for providing PWM inputs.                                                                                                                                            |

| 6   | nOVRT                | 0    | 3.3                     | Over-temperature warning output. Open drain, 16mA drive strength output with pull-up. Pulls low when active from over-temperature detection.                                                                                                                |

| 7   | PWM1                 | Ι    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

| 8   | PWM2                 | I    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

| 9   | PWM3                 | Ι    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

| 10  | PWM4                 | Ι    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

| 11  | PWM5                 | Ι    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

| 12  | PWM6                 | Ι    | 3.3                     | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                            |

# Pin Description (Continued)

|     | PIN NAME |      | VOLTAGE<br>LEVEL |                                                                                                                                                                                                                                                   |

|-----|----------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | (Note 7) | TYPE | (V)              | DESCRIPTION                                                                                                                                                                                                                                       |

| 13  | PWM7     | Ι    | 3.3              | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                  |

| 14  | PWM8     | Ι    | 3.3              | PWM Input. Routes to output channel, dependent on output configuration settings.                                                                                                                                                                  |

| 15  | PWMGND2  | GND  | 0                | Low-voltage ground. Connects to ground of circuitry providing PWM inputs. Both PWMGND and PWMGND2 are to tie together to the same ground.                                                                                                         |

| 16  | nERRORA  | 0    | 3.3              | Overcurrent protection output, channel A output stage. Open drain, 16mA drive strength output with pull-up. Pulls low when active from overcurrent detection of output stage.                                                                     |

| 17  | nERRORB  | 0    | 3.3              | Overcurrent protection output, channel B output stage. Open drain, 16mA drive strength output with pull-up. Pulls low when active from overcurrent detection of output stage.                                                                     |

| 18  | nERRORC  | 0    | 3.3              | Overcurrent protection output, channel C output stage. Open drain, 16mA drive strength output with pull-up. Pulls low when active from overcurrent detection of output stage.                                                                     |

| 19  | nERRORD  | 0    | 3.3              | Overcurrent protection output, channel D output stage. Open drain, 16mA drive strength output with pull-up. Pulls low when active from overcurrent detection of output stage.                                                                     |

| 20  | HVDDD    | Р    | HV               | Output stage D high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                         |

| 21  | HGNDD    | GND  | HV               | Output stage D high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 8).                                           |

| 22  | OUTD     | 0    | HV               | PWM power amplifier output, channel D.                                                                                                                                                                                                            |

| 23  | HSBSD    | Ι    | HV               | High side boot strap input, output channel D. Capacitor couples to OUTD amplifier output.                                                                                                                                                         |

| 24  | HSBSC    | Ι    | HV               | High side boot strap input, output channel C. Capacitor couples to OUTC amplifier output.                                                                                                                                                         |

| 25  | OUTC     | 0    | HV               | PWM power amplifier output, channel C.                                                                                                                                                                                                            |

| 26  | HGNDC    | GND  | HV               | Output stage C high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 8).                                           |

| 27  | HVDDC    | Р    | HV               | Output stage C high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                         |

| 28  | IREF     | Ι    | -                | Overcurrent reference analog input. Used in setting the overcurrent error detect externally-set threshold. The pin needs to be connected to a $100k\Omega$ resistor to ground to set the overcurrent threshold according to the specified limits. |

| 29  | VDDHV    | Р    | +HV              | High Voltage internal driver supply power. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source. The internal +5V supply regulators also operate from this VDDHV input.                                            |

| 30  | REG5V    | Р    | 5                | 5V internal regulator filter connect. A +5V supply is internally generated from the voltage source provided at the VDDHV pin. REG5V is used for external connection of a decoupling capacitor.                                                    |

| 31  | HVDDB    | Р    | HV               | Output stage B high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                         |

| 32  | HGNDB    | GND  | HV               | Output stage B high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 8).                                           |

| 33  | OUTB     | 0    | HV               | PWM power amplifier output, channel B.                                                                                                                                                                                                            |

| 34  | HSBSB    | Ι    | HV               | High side boot strap input, output channel B. Capacitor couples to OUTB amplifier output.                                                                                                                                                         |

| 35  | HSBSA    | Ι    | HV               | High side boot strap input, output channel A. Capacitor couples to OUTA amplifier output.                                                                                                                                                         |

| 36  | OUTA     | 0    | HV               | PWM power amplifier output, channel A.                                                                                                                                                                                                            |

|     |                      | -    |                         |                                                                                                                                                                                                           |

|-----|----------------------|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | PIN NAME<br>(Note 7) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                               |

| 37  | HGNDA                | GND  | ΗV                      | Output stage A high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 8).   |

| 38  | HVDDA                | Р    | ΗV                      | Output stage A high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source. |

## Pin Description (Continued)

NOTES:

7. Unless otherwise specified all pin names are active high. Those that are active low have an "n" prefix, such as nERRORA.

8. Thermal pad is internally connected to all 4 HGND ground pins (HGNDA, HGNDB, HGNDC, HGNDD). Any connection to the thermal pad must be made to the common ground for these 4 ground pins.

## **Typical Performance Characteristics**

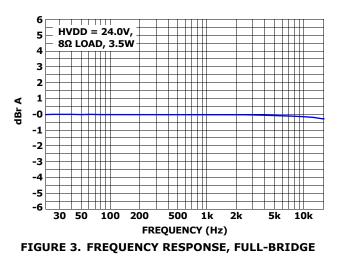

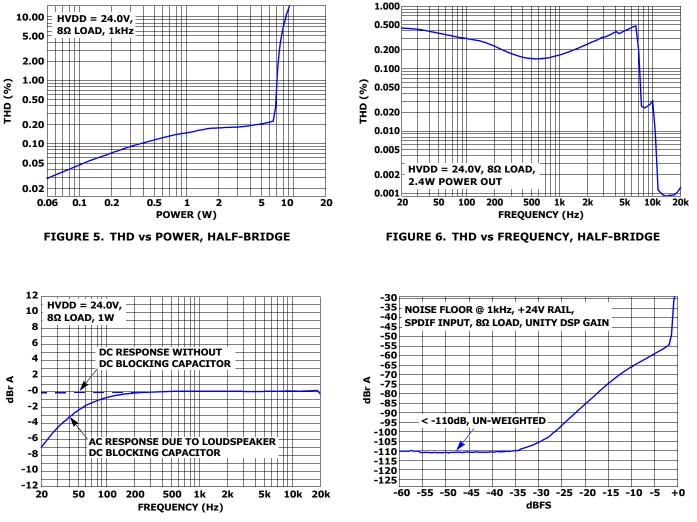

## **Full-Bridge Typical Performance Curves**

FIGURE 1. THD vs POWER, FULL-BRIDGE

FIGURE 2. THD vs FREQUENCY, FULL-BRIDGE

AT 1kHz, REFERENCE TO 30W -60 -65 -70 -75 -80 ∢ 툡 -85 -90 -95 -100 < -115dB, UN-WEIGHTED -105 -110 -115 -120 -60 -55 -50 -45 -40 -35 -30 -25 -20 -15 -10 -5 dBFS

$HVDD = 24.0V, 8\Omega LOAD,$

-50

-55

+0

#### Half-Bridge Typical Performance Curves

FIGURE 8. NOISE FLOOR, HALF-BRIDGE

## **Functional Overview**

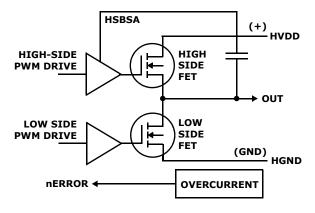

The devices include four independent output stages (Figure 9) that are each implemented using a high side (to positive VDDHV supply) and a low side (to HV supply ground) FET pair. Drivers and overcurrent monitoring are included in each of these four output stages. Depending on the selected configuration mode, these four stages can be used independently as single half-bridge outputs, or as pairs for full-bridge outputs.

Digital PWM inputs are connected to the PWM input pins, where their signals are routed through the configuration select logic to the individual output FETs and drivers.

On-chip temperature and undervoltage monitoring, and individual per-output current monitoring provides protection and status reporting outputs to the system controller.

Upon application of power, the on-chip voltage sensors monitor presence of the required power voltages. Until all voltages are at their design specifications, the outputs remain off and floating.

After supply voltages are within limits and stable, the output configuration is set by the logic levels at the OCFG0 and OCFG1 input pins, and the PWM inputs are routed to their appropriate output stage FETs.

FIGURE 9. OUTPUT STAGE

# **Output Options**

The D2-24044 devices provide four configuration options for the outputs. These options are selected by strapping the OCFG0 and OCFG1 pins high or low. These defined configurations include:

- 2 Channels of Full Bridge, 4-Quadrant Outputs,

- 2 Channels of Full Bridge, 2-Quadrant Outputs

- 4 Channels of Half-Bridge Outputs

- 2 Channels Half-Bridge, Plus 1 Channel Full Bridge

When a configuration is set that includes a full-bridge output, each input channel's PWM input signal is routed to the high and low side FETs, appropriate for that full bridge operation. Note however, that the device can be configured as 4 independent half-bridge outputs (using mode "11" as described in the configuration assignment table on page 14) and two of those outputs can be used in a full bridge configuration, simply by connecting the appropriate PWM input pins to the input source. This allows flexibility in applications where combinations may be desired other than the four defined by the output configuration modes.

# **Power Supply Requirements**

The device operates from two supply voltages:

- PWMVDD is a nominal 3.3V supply voltage, and operates the logic and control.

- HVDD (HVDD[A:D], and VDDHV) is the "high voltage" used for operating the output power stages.

Individual HVDD and its ground (HGND) pins are included for each of the four power stage outputs, providing channel isolation and low impedance source connections to each of the outputs. A separate VDDHV pin is used for the output drivers, and is the source for the on-chip regulated 5V source needed for the drivers. All the HVDD/VDDHV pins connect to the same voltage source.

PWMVDD is the reference for the PWM inputs and device control logic, and is the same voltage as used by the PWM/system controller.

## High Side Gate Drive Voltage

An on-chip bootstrap circuit provides the high-side gate drive voltage used by each output stage. A pin is included for each output channel (HSBS[A:D]) for connection of a capacitor (nominal,  $0.22\mu$ F/50V) from this pin to that channel's PWM output. The charge pumping actions uses this capacitor to filter and hold this gate drive voltage, and enables amplifier operation without need of connection to an additional power supply voltage.

## **Supply Bypass Connection**

Power supply bypass capacitors should be connected across each of the power supply connection pins, as:

- Four HVDD power pins and their respective HGND ground pins. These should be a parallel combination of a nominal  $100\mu F$  and  $0.1\mu F$  capacitors, located as close as possible to the HVDD/HGND pin pair.

- A  $0.1 \mu \text{F}$  capacitor also is to connect at the VDDHV pin.

- The PWMVDD power pin should include a  $1\mu\text{F}$  and  $0.1\mu\text{F}$  capacitor.

## REG5V

The on-chip gate drive power supply operates from the VDDHV power input, to produce the 5V supply voltage. The REG5V pin is used for external capacitor connection to filter this regulated voltage. A  $1.0\mu F$  and  $0.1\mu F$  capacitor should be connected to this pin, and the connection should be made as close as practical to the pin. No other connection is to be made to this pin.

## **Input and Control Functions**

## **PWM Inputs**

Eight PWM input pins provide the PWM inputs to the amplifier's output stages. The PWM input pins are electrically single-ended, referenced to the PWMVDD and PWMGND supplies.

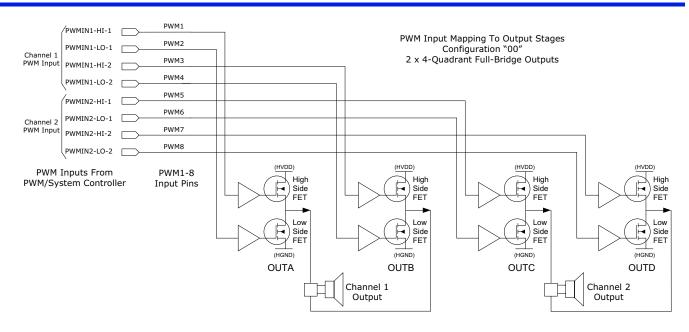

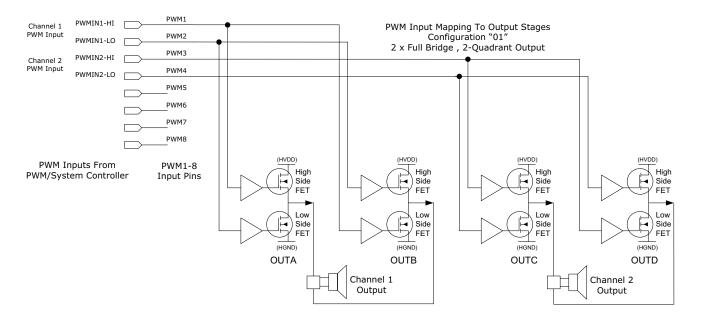

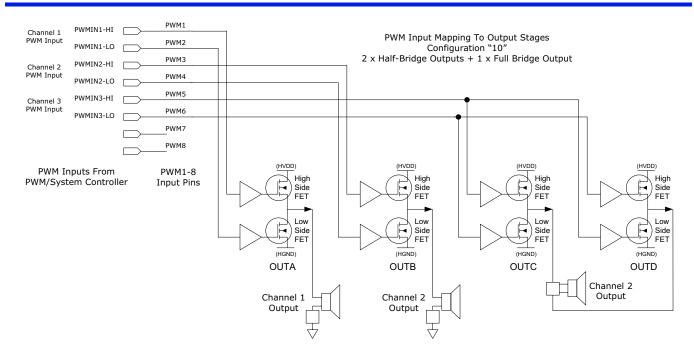

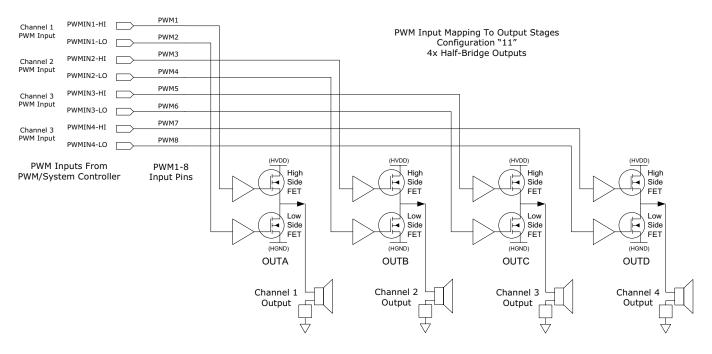

PWM drive to the output stages is provided differentially on-chip, with the PWM input channels mapped to each of the high-side output FETs and the low-side output FETs that implement the individual power stages. Routing and assignment of the PWM input pins to the output FETS is defined by the configuration mode. Figures 11, 12, 13, and 14 show the mapping of these input pins to the outputs for each of the four configuration modes.

All eight input pins however are not always used in each of the configuration modes. For example, in mode "00", providing 3-level drive of two channels of full bridge outputs, or in mode "11" providing four independent halfbridge outputs, one PWM input is dedicated to each of the FETs. But in mode "01" that implements two 2-quadrant full-bridge outputs, only four PWM inputs are used, and the logical high/low states are routed to the FETs as needed.

## **nPDN Input Pin**

The nPDN pin is a control input that is used to set the inactive (powered down) state, and also mute the outputs. It operates by turning off drive and internal sources to the PWM outputs, as well as turning off the PWM drive to those outputs.

When an overcurrent condition is detected on an output, causing its overcurrent protection to latch and turn off that output, asserting the nPDN input resets the device, and clears this overcurrent state.

The nPDN pin is active low, and inactive when at logic high level.

## **nERRORA-D** Output Pins

Each of the four outputs includes an overload and overcurrent monitor. An overcurrent or overload condition asserts the nERROR output for that channel. These outputs are active low, open drain. Depending on the output mode configuration and need to monitor more than one output, these nERROR pins can be wire-or connected together.

## **nOVRT Output Pin**

The nOVRT pin is an output that provides warning of a high temperature condition. It is an open drain, active low output. This pin provides only indication of high temperature.

#### **IREF Pin**

The IREF pin is used to control the overcurrent monitoring threshold. A  $100 k \Omega$  resistor connects from this pin to ground.

## **OCFG0, OCFG1 Input Pins**

These two pins are used to define the configuration of the four output stages. They are connected to logic high (PWMVDD) or logic ground (PWMGND) to set their level. Refer to "Output Mode Configurations" on page 14 for additional reference and definition.

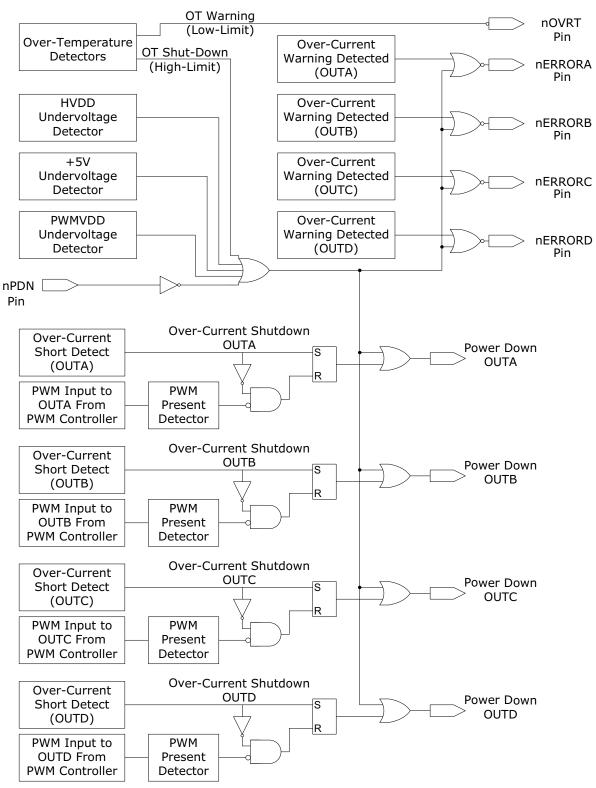

## Protection

The D2-24044 device includes monitors for protection of the system as well as the device itself. Certain levels of protection are managed on-chip, as shown in Figure 10. Other protection is integrated at the system level through the system controller, and involves system design decisions based on:

- A short circuit, over-temperature, or undervoltage event will shut down the outputs.

- Other operation depends on the PWM/system controller to properly manage full system protection operation.

- Power supply sensors shut down the device if supply voltages drop below their design thresholds.

- Overload and overcurrent monitors provide dual threshold status of high current conditions, providing both indication, and device shutdown if needed.

- Chip temperature monitoring provides dual threshold status of high temperature conditions, providing both indication, and device shutdown if needed.

#### Short-Circuit and Overcurrent Sensing

Each PWM output FET includes a dual-threshold overcurrent sensor. Multiple functions occur depending on detection of overcurrent conditions:

- The lower threshold is used to monitor fault conditions after the output stage filter inductor, such as shorts or overloads on the loudspeaker outputs.

- The higher threshold monitors fault conditions of the PWM output pin.

- The nERROR output asserts for the channel detecting the fault.

- For the lower level threshold, nERROR remains asserted only through the duration of the overcurrent event.

- For the higher level threshold, the output is shut down, and its nERROR output is asserted, and these remain latched until the controller acknowledges the fault event by turning off the channel's PWM drive. (When the output is shutdown, its PWM output pin floats.)

#### **Thermal Protection and Monitoring**

An on-chip temperature sensor provides two thresholds of temperature monitoring.

If the device reaches the lower threshold, the nOVRT output is asserted, providing warning indication to an external controller. The low threshold setting provides indication only, and does not have any effect on device operation.

• The lower high-temperature threshold (warning) is set at approximately +125°C.

If the device reaches the higher threshold, it will drive all four nERRORA-D outputs low (active) and shut down the device, in addition to asserting the nOVRT output. This shutdown in non-latching, and operation will resume automatically when temperature returns to normal.

• The higher high-temperature threshold (over-temp) is set at approximately +140°C.

#### **Power Supply Voltage Monitoring**

Undervoltage monitors are included for the output drive (HVDD) supply voltage, the on-chip generated gate drive (REG5V) supply voltage, and the low-level PWMVDD supply voltage. Detection occurs at approximately 2.5V for PWMVDD, approximately 4V for the gate drive supply, and approximately 7V for the HVDD supply. (Limits are listed in the electrical specification tables starting on page 4.)

If any of the monitored voltages drop below their threshold, the device shuts down its outputs and asserts all four of the nERROR outputs. Operation resumes normally after the undervoltage condition is cleared.

Over-Current (OC) Shutdown: OC detect condition is latched, shutting down output. Latched shutdown is then cleared after over-current condition has cleared, AND PWM data clocking has stopped from PWM controller.

FIGURE 10. PROTECTION AND MONITORING HIGH-LEVEL FUNCTIONAL OPERATION

## **Output Mode Configurations**

The D2-24044 device supports four amplifier output configuration modes, utilizing the device's 4 power stage outputs.

Configuration selection is controlled by the OCFG0 and OCFG1 pins, by connecting them to either a high (+3.3V, PWMVDD = 1) or low (ground = 0) level. Settings are chosen based on the output configuration and topology of the design. Their connection is to be hard-connected on the design, and they are not intended to be dynamic or subject to change during system operation. For each of the four configurations, the PWM input pin signals route to the individual FETs of each of the power stages to implement the channel drive and topology needed for those configurations. Figures 11, 12, 13, and 14 show this routing of the PWM inputs to each of the power stages, and how the particular topology is implemented for that configuration. Table 1 shows the configuration functions that are defined with the combinations of the OCFG pins, and these diagrams show the implementation that is listed in this table.

| CONFIG PINS |       |        | CONFIGURATION            | POWER STAGE OUTPUT |                                     |                 |                | nERROR CHANNEL USE     |                                                     |                                                     |                    |

|-------------|-------|--------|--------------------------|--------------------|-------------------------------------|-----------------|----------------|------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------|

| OCFG1       | OCFG0 | CONFIG | DESCRIPTION              | OUTA               | OUTB                                | Ουτς            | OUTD           | nERRORA                | nERRORB                                             | nERRORC                                             | nERRORD            |

|             |       |        | 2-Channel                |                    |                                     |                 | nERRORA 8      | (wire-or)<br>& nERRORB | Connect (wire-or)<br>nERRORC & nERRORD<br>together. |                                                     |                    |

|             |       | No.04  | Full Bridge<br>3-Level   | High-Sid           | e FET PWM                           | I Input Assi    | ignments       | Use for                | together.<br>Use for Output                         |                                                     | Output             |

| 0           | 0     | "00″   | PWM Drive                | PWM1               | PWM3                                | PWM5            | PWM7           | Channel                | 1 Protect                                           | Channel                                             | 2 Protect          |

|             |       |        | (Ref. Figure 11)         | Low-Side           | e FET PWM                           | Input Assi      | gnments        |                        |                                                     |                                                     |                    |

|             |       |        |                          | PWM2               | PWM4                                | PWM6            | PWM8           |                        |                                                     |                                                     |                    |

|             |       |        | 2-Channel                | Out<br>Chan        | put<br>Inel 1                       |                 | tput<br>Inel 2 | nERRORA 8              | (wire-or)<br>& nERRORB                              | RB nERRORC & nERRORD<br>together.<br>Use for Output |                    |

|             |       |        | Full Bridge,             | High-Sid           | e FET PWM                           | I Input Assi    | ignments       | 5                      | ther.<br>Output                                     |                                                     |                    |

| 0           | 1     | "01″   | 2-Quadrant PWM Drive     | PWM1               | PWM2                                | PWM3            | PWM4           |                        | 1 Protect                                           |                                                     |                    |

|             |       |        | (Ref. Figure 12)         | Low-Side           | e FET PWM                           | Input Assi      | gnments        |                        |                                                     |                                                     |                    |

|             |       |        |                          | PWM2               | PWM1                                | PWM4            | PWM3           |                        |                                                     |                                                     |                    |

|             |       |        | 2-Channel<br>Half-Bridge | Output<br>Ch. 1    | Output<br>Ch 2                      | Out<br>Chan     | tput<br>Inel 3 |                        |                                                     | Connect (wire-or)<br>nERRORC & nERRORD              |                    |

|             |       |        | plus                     | High-Sid           | e FET PWM                           | I Input Assi    | ignments       | nERRORA<br>Use for     | nERRORB<br>Use for                                  |                                                     |                    |

| 1           | 0     | "10″   | 1-Channel<br>Full Bridge | PWM1               | PWM3                                | PWM5            | PWM6           | Channel 1              | Channel 2                                           | 5                                                   | ther.<br>Output    |

|             |       |        | 5                        | Low-Side           | e FET PWM                           | Input Assi      | gnments        | Protect                | Protect                                             |                                                     | 3 Protect          |

|             |       |        | (Ref. Figure 13)         | PWM2               | PWM4                                | PWM6            | PWM5           |                        |                                                     |                                                     |                    |

|             |       |        |                          | Output<br>Ch. 1    | Output<br>Ch 2                      | Output<br>Ch. 3 | Output<br>Ch 4 |                        |                                                     |                                                     |                    |

|             |       |        | 4-Channel<br>Half-Bridge | High-Sid           | High-Side FET PWM Input Assignments |                 |                | nERRORA<br>Use for     | nERRORB                                             | nERRORC<br>Use for                                  | nERRORD<br>Use for |

| 1           | 1     | "11″   |                          | PWM1               | PWM3                                | PWM5            | PWM7           | Channel 1              | Use for<br>Channel 2<br>Protect                     | Channel 3                                           | Channel 4          |

|             |       |        | (Ref. Figure 14)         | Low-Side           | e FET PWM                           | Input Assi      | gnments        | Protect                |                                                     | Protect Protect                                     |                    |

|             |       |        |                          | PWM2               | PWM4                                | PWM6            | PWM8           | 1                      |                                                     |                                                     |                    |

#### TABLE 1. D2-24044 CONFIGURATION PWM AND OUTPUT CHANNEL ASSIGNMENTS

FIGURE 11. CONFIGURATION "00" PWM INPUT-TO-OUTPUT POWER STAGE MAPPING

FIGURE 12. CONFIGURATION "01" PWM INPUT-TO-OUTPUT POWER STAGE MAPPING

FIGURE 13. CONFIGURATION "10" PWM INPUT-TO-OUTPUT POWER STAGE MAPPING

FIGURE 14. CONFIGURATION "11" PWM INPUT-TO-OUTPUT POWER STAGE MAPPING

## **Typical Application Examples**

These examples show functional circuit examples of typical applications using the D2-24044 device. (Note: These examples are provided to show typical applications only and are not intended to represent complete production-qualified reference designs.)

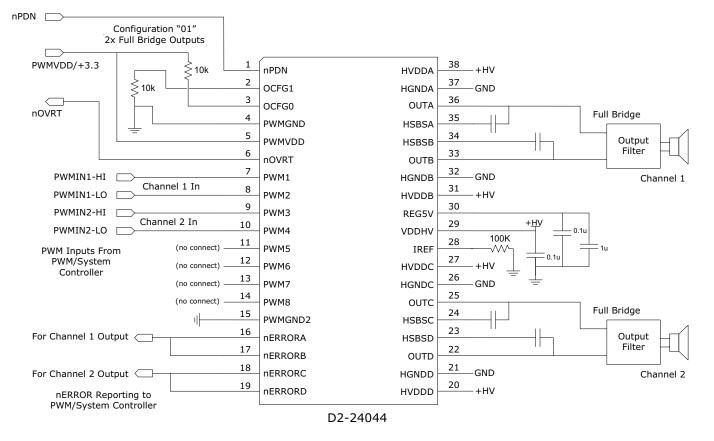

## 2-Channel Full Bridge Example

This example (Figure 15) uses configuration mode "01" to provide two full-bridge loudspeaker output channels. The PWM controller provides input into four PWM input pins.

FIGURE 15. 2-CHANNEL FULL BRIDGE EXAMPLE

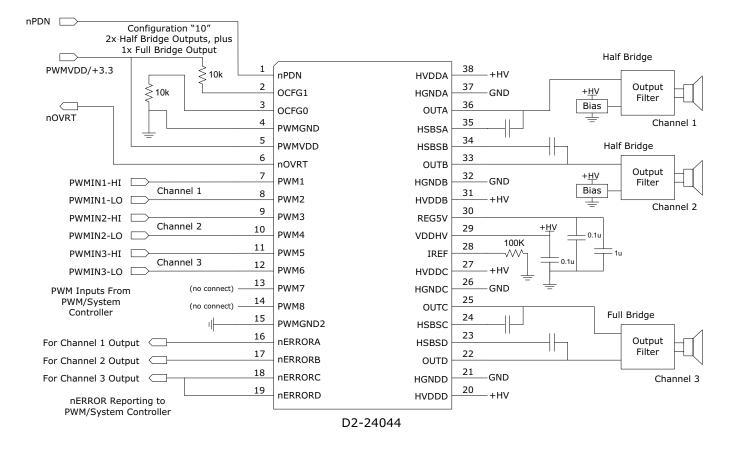

#### 2.1-Channel Example

This example (Figure 16) uses configuration mode "10" to provide two independent half-bridge loudspeaker output channels, plus one full-bridge loudspeaker output. The PWM controller provides input into all eight PWM input pins.

FIGURE 16. 2-CHANNEL HALF BRIDGE PLUS 1-CHANNEL FULL BRIDGE EXAMPLE

#### 4-Channel Half-Bridge Example

This example (Figure 17) uses configuration mode "11" to provide four independent half-bridge loudspeaker output channels. The PWM controller provides input into all eight PWM input pins.

| nPDN                                     |                                 |    |          |       |    |                     |              |                  |

|------------------------------------------|---------------------------------|----|----------|-------|----|---------------------|--------------|------------------|

|                                          | juration "11"<br>Bridge Outputs |    |          |       |    |                     |              |                  |

|                                          |                                 |    | /        |       |    |                     | Half         | Bridge           |

| PWMVDD/+3.3                              |                                 | 1  | nPDN     | HVDDA | 38 | -+HV                |              |                  |

|                                          |                                 | 2  | OCFG1    | HGNDA | 37 | -GND                | + <u>H</u> V | Output<br>Filter |

| nOVRT                                    |                                 | 3  | OCFG0    | OUTA  | 36 |                     |              |                  |

| novici                                   | ц <u>і — —</u>                  | 4  | PWMGND   | HSBSA | 35 |                     | -            | Channel 1        |

|                                          |                                 | 5  | PWMVDD   | HSBSB | 34 |                     | Half         | Bridge           |

| PWM Inputs From<br>PWM/System Controller |                                 | 6  | nOVRT    | OUTB  | 33 |                     |              |                  |

| PWMIN1-HI                                | Channel 1                       | 7  | PWM1     | HGNDB | 32 | -GND                | + <u>HV</u>  | Output<br>Filter |

| PWMIN1-LO                                |                                 | 8  | PWM2     | HVDDB | 31 | -+HV                |              | Channel 2        |

| PWMIN2-HI                                |                                 | 9  | PWM3     | REG5V | 30 |                     |              | Channel 2        |

| PWMIN2-LO                                | Channel 2                       | 10 | PWM4     | VDDHV | 29 | + <u>HV</u><br>100K | 0.1u         |                  |

| PWMIN3-HI 🗁                              |                                 | 11 | PWM5     | IREF  | 28 |                     | 1u           |                  |

| PWMIN3-LO 🗁                              | Channel 3                       | 12 | PWM6     | HVDDC | 27 | _+HV                | 0.1u         |                  |

| PWMIN4-HI 🗁                              |                                 | 13 | PWM7     | HGNDC | 26 | -GND – 📥            | Half         | Bridge           |

| PWMIN4-LO                                | Channel 3                       | 14 | PWM8     | оитс  | 25 |                     | [            |                  |

|                                          | ı  <b> </b>                     | 15 | PWMGND2  | HSBSC | 24 |                     | + <u>H</u> V | Output<br>Filter |

| For Channel 1 Output 🔇                   |                                 | 16 | nERRORA  | HSBSD | 23 |                     |              |                  |

| For Channel 2 Output                     |                                 | 17 | nERRORB  | OUTD  | 22 |                     |              | Channel 3        |

| For Channel 3 Output 🤇                   |                                 | 18 | nERRORC  | HGNDD | 21 | -GND                | Half         | Bridge           |

| For Channel 4 Output <                   |                                 | 19 | nERRORD  | HVDDD | 20 | -+HV                | +HV          | Output           |

| nERROR Reporting<br>PWM/System Contr     |                                 |    | D2-24044 |       |    |                     | Bias         | Filter           |

|                                          |                                 |    |          |       |    |                     | - <u>+</u>   | Channel 4        |

FIGURE 17. 4-CHANNEL HALF BRIDGE EXAMPLE

© Copyright Intersil Americas LLC 2010. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

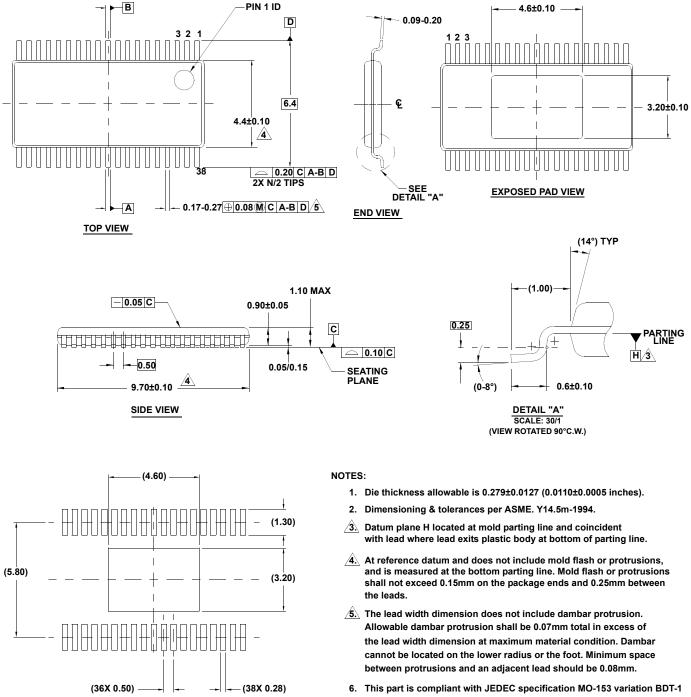

## Package Outline Drawing

## M38.173C

38 LEAD HEAT-SINK THIN SHRINK SMALL OUTLINE PLASTIC PACKAGE (HTSSOP) Rev 0, 4/10

TYPICAL RECOMMENDED LAND PATTERN