## SBS 1.1-COMPLIANT GAS GAUGE AND PROTECTION-ENABLED IC WITH IMPEDANCE TRACK<sup>™</sup>

Check for Samples: bq20z75

#### FEATURES

- Next Generation Patented Impedance Track<sup>™</sup> **Technology accurately Measures Available** Charge in Li-Ion and Li-Polymer Batteries

- Better than 1% Error Over Lifetime of the **Batterv**

- Instant Accuracy No Learning Cycle Required

- Supports the Smart Battery Specification **SBS V1.1**

- Flexible Configuration for 2 to 4 Series Li-Ion and Li-Polymer Cells

- Powerful 8-Bit RISC CPU With Ultra-Low **Power Modes**

- Full Array of Programmable Protection • Features

- Voltage, Current and Temperature

- **Supports SHA-1 Authentication**

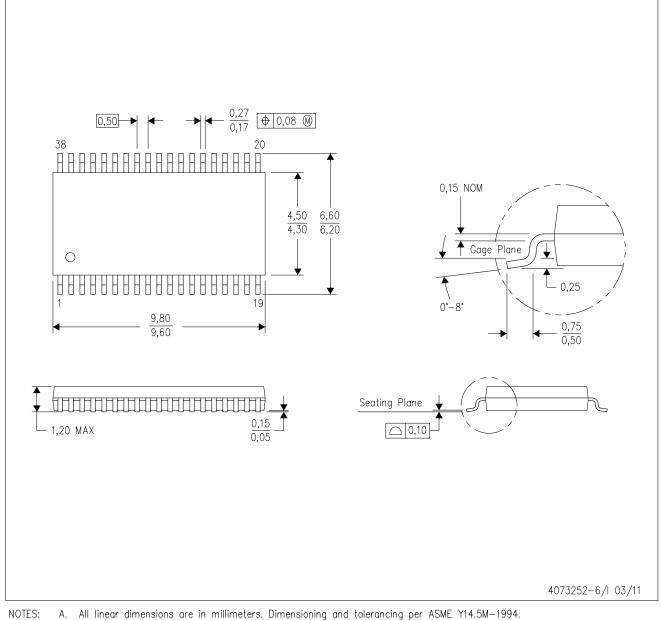

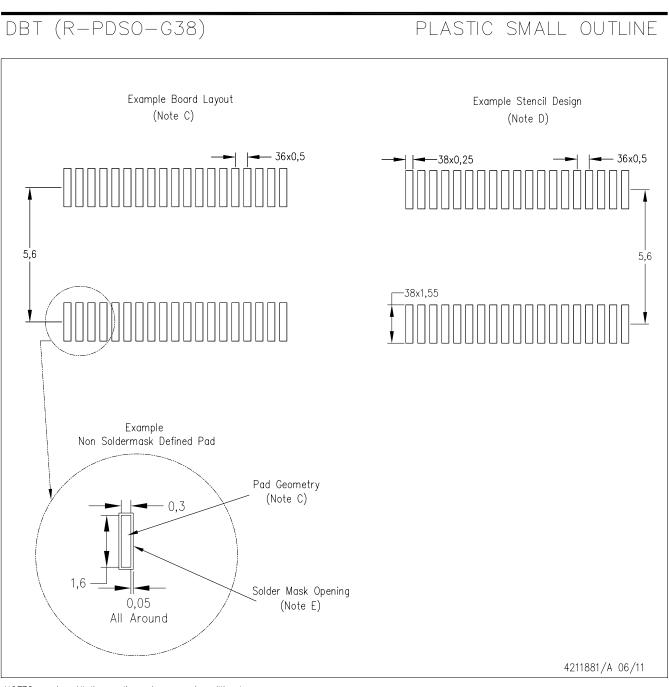

- small 38-Pin TSSOP (DBT) Package

#### APPLICATIONS

- Notebook PCs

- **Medical and Test Equipment**

- **Portable Instrumentation**

#### DESCRIPTION

The bq20z75 SBS-compliant gas gauge and protection IC is a single IC solution designed for battery-pack or in-system installation. The bg20z75 measures and maintains an accurate record of available charge in Li-ion or Li-polymer batteries using its integrated high-performance analog peripherals, monitors capacity change, battery impedance, open-circuit voltage, and other critical parameters of the battery pack as well and reports the information to the system host controller over a serial-communication bus. Together with the integrated analog front-end (AFE) short-circuit and bq20z75 overload protection the maximizes functionality, safety and minimize external component count, cost and size in smart battery circuits.

The implemented Impedance Track<sup>™</sup> gas gauging technology continuously analyzes the batterv impedance. resulting in superior gas-gauging accuracy. This enables remaining capacity to be calculated with discharge rate, temperature, and cell aging all accounted for during each stage of every cycle with high accuracy.

|                | PACKAGE                                   |                                                    |  |  |  |

|----------------|-------------------------------------------|----------------------------------------------------|--|--|--|

| Τ <sub>Α</sub> | 38-PIN TSSOP (DBT)<br>Tube <sup>(1)</sup> | 38-PIN TSSOP (DBT)<br>Tape and Reel <sup>(2)</sup> |  |  |  |

| -40°C to       | bq20z75DBT                                | bq20z75DBTR                                        |  |  |  |

| 85°C           | bq20z75DBT-v160                           | bq20z75DBTR-v160                                   |  |  |  |

**Table 1. AVAILABLE OPTIONS**

A single tube quantity is 50 units. (1)

A single reel quantity is 2000 units (2)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. IMPEDANCE TRACK is a trademark of Texas Instruments.

### bq20z75

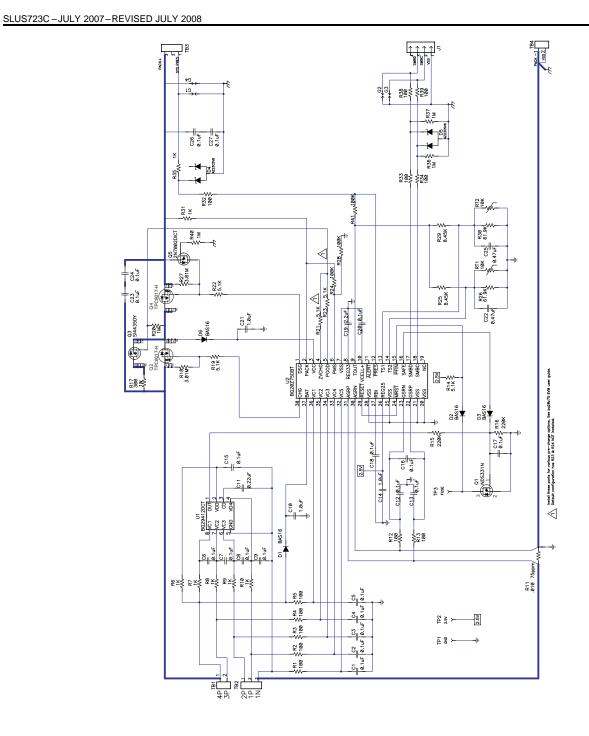

#### SLUS723C - JULY 2007 - REVISED JULY 2008

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

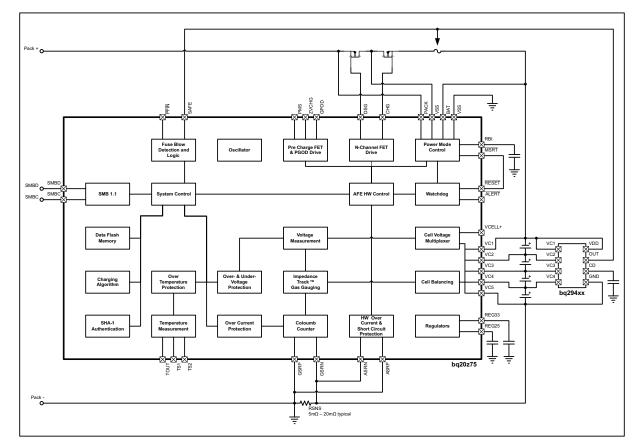

#### SYSTEM PARTITIONING DIAGRAM

#### TSSOP (PW) (TOP VIEW)

|                 |                     |          | _              |

|-----------------|---------------------|----------|----------------|

| DSG 🗆<br>PACK 🗆 | 1 <sup>●</sup><br>2 | 38<br>37 | □ CHG<br>□ BAT |

|                 | 3                   | 36       | □ VC1          |

| ZVCHG           | 4                   | 35       | D VC2          |

| GPOD 🗆          | 5                   | 34       | 🗆 VC3          |

| PMS 🗆           | 6                   | 33       | 🗅 VC4          |

| VSS 🗆           | 7                   | 32       | D VC5          |

| REG33 🗆         | 8                   | 31       |                |

| TOUT 🗆          | 9                   | 30       | 🗆 ASRN         |

| VCELL+          | 10                  | 29       | RESET          |

| ALERT [         | 11                  | 28       | □ vss          |

| PRES [          | 12                  | 27       | 🗆 RBI          |

| TS1 🗆           | 13                  | 26       | 🗅 REG25        |

| TS2 🗆           | 14                  | 25       | 🗆 VSS          |

| PFIN 🗆          | 15                  | 24       |                |

| SAFE 🗆          | 16                  | 23       |                |

| SMBD            | 17                  | 22       |                |

| SMBC            | 18                  | 21       | 🗅 vss          |

| NC 🗆            | 19                  | 20       | 🗅 vss          |

|                 |                     |          |                |

bq20z75

www.ti.com

Texas Instruments

#### SLUS723C -JULY 2007-REVISED JULY 2008

| TERMINAL FUNCTIO | NS |

|------------------|----|

|------------------|----|

| TEI | RMINAL | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                            |

|-----|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   | 10.                |                                                                                                                                                                                                                        |

| 1   | DSG    | 0                  | High side N-channel discharge FET gate drive                                                                                                                                                                           |

| 2   | PACK   | IA, P              | Battery pack input voltage sense input. It also serves as device wake up when device is in shutdow mode.                                                                                                               |

| 3   | VCC    | Р                  | Positive device supply input. Connect to the center connection of the CHG FET and DSG FET to ensure device supply either from battery stack or battery pack input                                                      |

| 4   | ZVCHG  | 0                  | P-channel pre-charge FET gate drive                                                                                                                                                                                    |

| 5   | GPOD   | OD                 | High voltage general purpose open drain output. Can be configured to be used in pre-charge condition                                                                                                                   |

| 6   | PMS    | I                  | Pre-charge mode setting input. Connect to PACK to enable 0v pre-charge using charge FET connected at CHG pin. Connect to VSS to disable 0V pre-charge using charge FET connected at CHG pin.                           |

| 7   | VSS    | Р                  | Negative device power supply input. Connect all VSS pins together for operation of device                                                                                                                              |

| 8   | REG33  | Р                  | 3.3V regulator output. Connect at least a 2.2 $\mu$ F capacitor to REG33 and VSS                                                                                                                                       |

| 9   | TOUT   | Р                  | Termistor bias supply output                                                                                                                                                                                           |

| 10  | VCELL+ | -                  | Internal cell voltage multiplexer and amplifier output. Connect a 0.1µF capacitor to VCELL+ and VS                                                                                                                     |

| 11  | ALERT  | I/OD               | Alert output. In case of short circuit condition, overload condition and watchdog time out this pin wil be triggered.                                                                                                  |

| 12  | PRES   | I/OD               | System / Host present input. Pull up to TOUT                                                                                                                                                                           |

| 13  | TS1    | IA                 | Temperature sensor 1 input                                                                                                                                                                                             |

| 14  | TS2    | IA                 | Temperature sensor 2 input                                                                                                                                                                                             |

| 15  | PFIN   | I/OD               | Fuse blow detection input                                                                                                                                                                                              |

| 16  | SAFE   | I/OD               | blow fuse signal output                                                                                                                                                                                                |

| 17  | SMBD   | I/OD               | SMBus data line                                                                                                                                                                                                        |

| 18  | SMBC   | I/OD               | SMBus clock line                                                                                                                                                                                                       |

| 19  | NC     | -                  | Not Connected                                                                                                                                                                                                          |

| 20  | VSS    | Р                  | Negative device power supply input. Connect all VSS pins together for operation of device.                                                                                                                             |

| 21  | VSS    | Р                  | Negative device power supply input. Connect all VSS pins together for operation of device.                                                                                                                             |

| 22  | GSRP   | IA                 | Coulomb counter differential input. Connect to one side of the sense resistor                                                                                                                                          |

| 23  | GSRN   | IA                 | Coulomb counter differential input. Connect to one side of the sense resistor                                                                                                                                          |

| 24  | MRST   | 1                  | Reset input for internal CPU core. connect to RESET for correct operation of device.                                                                                                                                   |

| 25  | VSS    | Р                  | Negative device power supply input. Connect all VSS pins together for operation of device.                                                                                                                             |

| 26  | REG25  | Р                  | 2.5V regulator output. Connect at least a $1\mu$ F capacitor to REG25 and VSS                                                                                                                                          |

| 27  | RBI    | Р                  | RAM backup input. Connect a capacitor to this pin and VSS to protect loss of RAM data in case of short-circuit condition                                                                                               |

| 28  | VSS    | Р                  | Negative device power supply input. Connect all VSS pins together for operation of device                                                                                                                              |

| 29  | RESET  | 0                  | Reset output. Connect to MSRT.                                                                                                                                                                                         |

| 30  | ASRN   | IA                 | Short-circuit and overload detection differential input                                                                                                                                                                |

| 31  | ASRP   | IA                 | Short-circuit and overload detection differential input                                                                                                                                                                |

| 32  | VC5    | IA,P               | Cell voltage sense input and cell balancing input for the negative voltage of the bottom cell in cell stack.                                                                                                           |

| 33  | VC4    | IA,P               | Cell voltage sense input and cell balancing input for the positive voltage of the bottom cell and the negative voltage of the second lowest cell in cell stack.                                                        |

| 34  | VC3    | IA,P               | Cell voltage sense input and cell balancing input for the positive voltage of the second lowest cell in cell stack and the negative voltage of the second highest cell in 4 cell applications.                         |

| 35  | VC2    | IA,P               | Cell voltage sense input and cell balancing input for the positive voltage of the second highest cell and the negative voltage of the highest cell in 4 cell applications. Connect to VC3 in 2 cell stack applications |

| 36  | VC1    | IA,P               | Cell voltage sense input and cell balancing input for the positive voltage of the highest cell in cell stack in 4 cell applications. Connect to VC2 in 3 or 2 cell stack applications                                  |

(1) I = Input, IA = Analog input, I/O = Input/output, I/OD = Input/Open-drain output, O = Output, OA = Analog output, P = Power

SLUS723C - JULY 2007 - REVISED JULY 2008

#### **TERMINAL FUNCTIONS (continued)**

| TER | RMINAL                                     | I/O <sup>(1)</sup> | DESCRIPTION                               |

|-----|--------------------------------------------|--------------------|-------------------------------------------|

| NO. | NO. NAME                                   |                    | DESCRIPTION                               |

| 37  | 37 BAT O Battery stack voltage sense input |                    | Battery stack voltage sense input         |

| 38  | CHG                                        | 0                  | High side N-channel charge FET gate drive |

#### **Absolute Maximum Ratings**

Over Operating Free-Air Temperature (unless otherwise noted) <sup>(1)</sup>

|                  | DESCRIPTION                                  | PIN                              | UNIT                               |

|------------------|----------------------------------------------|----------------------------------|------------------------------------|

| V <sub>MAX</sub> | Supply voltage range                         | VBAT, VCC                        | -0.3V to 34V                       |

|                  |                                              | PACK, PMS                        | -0.3V to 34V                       |

|                  |                                              | VC(n)-VC(n+1); n = 1,<br>2, 3, 4 | -0.3V to 8.5V                      |

|                  |                                              | VC1, VC2, VC3, VC4               | -0.3V to 34V                       |

|                  |                                              | VC5                              | -0.3V to 1.0V                      |

| V <sub>IN</sub>  | Input voltage range                          | PFIN, SMBD, SMBC,<br>DISP        | -0.3V to 6.0V                      |

|                  |                                              | TS1, TS2, VCELL+,<br>PRES; ALERT | –0.3 V to V $_{\rm REG25}$ + 0.3 V |

|                  |                                              | MRST, GSRN, GSRP,<br>RBI         | –0.3 V to V $_{\rm REG25}$ + 0.3 V |

|                  |                                              | ASRN, ASRP                       | -1.0V to 1.0V                      |

|                  |                                              | DSG, CHG, GPOD                   | -0.3V to 34V                       |

| V <sub>OUT</sub> |                                              | ZVCHG                            | –0.3V to V $_{BAT}$                |

|                  | Output voltage range                         | TOUT, ALERT,<br>REG33,           | –0.3 V to 6.0V                     |

|                  |                                              | RESET                            | –0.3 V to 7.0V                     |

|                  |                                              | REG25, SAFE, TOUT                | -0.3V to 2.75V                     |

| I <sub>SS</sub>  | Maximum combined sink current for input pins | PRES, PFIN, SMBD,<br>SMBC        | 50mA                               |

| T <sub>A</sub>   | Operating free-air temperature range         |                                  | -40°C to 85°C                      |

| Τ <sub>F</sub>   | Functional temperature                       |                                  | –40°C to 100°C                     |

| T <sub>stg</sub> | Storage temperature range                    |                                  | –65°C to 150°C                     |

| T <sub>sld</sub> | Lead temperature (soldering, 10s)            |                                  | 300°C                              |

|                  |                                              |                                  |                                    |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### SLUS723C - JULY 2007 - REVISED JULY 2008

#### **Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

| PARAME             | ETER                                     | PIN                        | MIN  | NOM MAX          | UNIT |

|--------------------|------------------------------------------|----------------------------|------|------------------|------|

| V <sub>SUP</sub>   | Supply voltage                           | VCC, VBAT                  | 4.5  | 25               | V    |

| V<br>startup       | Minimum startup voltage                  | VCC, BAT, PACK             | 5.5  |                  | V    |

|                    |                                          | VC(n)-VC(n+1); n = 1,2,3,4 | 0    | 5                | V    |

|                    |                                          | VC1, VC2, VC3, VC4         | 0    | V <sub>SUP</sub> | V    |

| V <sub>IN</sub>    | Input Voltage Range                      | VC5                        | 0    | 0.5              | V    |

| VIN                |                                          | ASRN, ASRP                 | -0.5 | 0.5              | V    |

|                    |                                          | PACK, PMS                  | 0    | 25               | V    |

| V <sub>GPOD</sub>  | Output Voltage Range                     | GPOD                       | 0    | 25               | V    |

| A <sub>GPOD</sub>  | Drain Current <sup>(1)</sup>             | GPOD                       |      | 1                | mA   |

| C <sub>REG25</sub> | 2.5V LDO Capacitor                       | REG25                      | 1    |                  | μF   |

| C <sub>REG33</sub> | 3.3V LDO Capacitor                       | REG33                      | 2.2  |                  | μF   |

| $C_{VCELL+}$       | Cell Voltage Output Capacitor            | VCELL+                     | 0.1  |                  | μF   |

| C <sub>PACK</sub>  | PACK input block resistor <sup>(2)</sup> | PACK                       | 1    |                  | kΩ   |

(1) Use external resistor to limit current to GPOD to 1mA in high voltage application.

(2) External resistor to limit inrush current PACK pin required.

#### **Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted),  $T_A = -40^{\circ}C$  to 85°C,  $V_{REG25} = 2.41$  V to 2.59 V,  $V_{BAT} = 14V$ ,  $C_{REG25} = 1\mu$ F,  $C_{REG33} = 2.2\mu$ F; typical values at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                           | PARAMETER                                                                                       | TEST CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT |

|---------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY                    | CURRENT                                                                                         |                                                                                           |      |      |      |      |

| INORMAL                   | Firmware running                                                                                |                                                                                           |      | 550  |      | μA   |

| I <sub>SLEEP</sub>        | Sleep Mode                                                                                      | CHG FET on; DSG FET on                                                                    |      | 124  |      | μA   |

|                           |                                                                                                 | CHG FET off; DSG FET on                                                                   |      | 90   |      | μA   |

|                           |                                                                                                 | CHG FET off; DSG FET off                                                                  |      | 52   |      | μA   |

| I <sub>SHUTDOW</sub><br>N | Shutdown Mode                                                                                   |                                                                                           |      | 0.1  | 1    | μA   |

| SHUTDO                    | WN WAKE; T <sub>A</sub> = 25°C (unless otherwise i                                              | noted)                                                                                    |      |      |      |      |

| I <sub>PACK</sub>         | Shutdown exit at VSTARTUP threshold                                                             |                                                                                           |      |      | 1    | μA   |

| SRx WAP                   | KE FROM SLEEP; T <sub>A</sub> = 25°C (unless other                                              | rwise noted)                                                                              |      |      |      |      |

| V <sub>WAKE</sub>         | Positive or negative wake threshold with 1.00 mV, 2.25 mV, 4.5 mV and 9 mV programmable options |                                                                                           | 1.25 |      | 10   | mV   |

| V <sub>WAKE_</sub> A      |                                                                                                 | V <sub>WAKE</sub> = 1.0mV;<br>IWAKE=0, RSNS1=0, RSNS0=1;                                  | -0.7 |      | 0.7  |      |

|                           |                                                                                                 | V <sub>WAKE</sub> = 2.25mV;<br>IWAKE =1, RSNS1=0, RSNS0=1;<br>IWAKE =0, RSNS1=1, RSNS0=0; | -0.8 |      | 0.8  |      |

| CR                        | Accuracy of V <sub>WAKE</sub>                                                                   | V <sub>WAKE</sub> = 4.5mV;<br>IWAKE =1, RSNS1=1, RSNS0=1;<br>IWAKE =0, RSNS1=1, RSNS0=0;  | -1.0 |      | 1.0  | mV   |

|                           |                                                                                                 | V <sub>WAKE</sub> = 9mV;<br>IWAKE =1, RSNS1=1, RSNS0=1;                                   | -1.4 |      | 1.4  |      |

| V <sub>WAKE_T</sub><br>co | Temperature drift of V <sub>WAKE</sub> accuracy                                                 |                                                                                           |      | 0.5  |      | %/°C |

| t <sub>WAKE</sub>         | Time from application of current and wake of bq20z75                                            |                                                                                           |      | 1    | 10   | ms   |

| POWER-                    | ON RESET                                                                                        |                                                                                           |      |      |      |      |

| V <sub>IT-</sub>          | Negative-going voltage input                                                                    | Voltage at REG25 pin                                                                      | 1.70 | 1.80 | 1.90 | V    |

Copyright © 2007–2008, Texas Instruments Incorporated

# SLUS723C – JULY 2007–REVISED JULY 2008

| <b>Electrical Characteristics</b> | (continued) |

|-----------------------------------|-------------|

|-----------------------------------|-------------|

over operating free-air temperature range (unless otherwise noted),  $T_A = -40^{\circ}C$  to 85°C,  $V_{REG25} = 2.41$  V to 2.59 V,  $V_{BAT} = 14V$ ,  $C_{REG25} = 1\mu$ F,  $C_{REG33} = 2.2\mu$ F; typical values at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                             | PARAMETER                                                        | TEST CONDITIONS                                                                                 | MIN                                       | TYP                   | MAX                                       | UNIT |

|-----------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|-------------------------------------------|------|

| V <sub>hys</sub>            | Hysteresis                                                       | $V_{IT+} - V_{IT-}$                                                                             | 50                                        | 150                   | 250                                       | mV   |

| t <sub>RST</sub>            | RESET active low time                                            | active low time after power up or watchdog reset                                                | 100                                       | 250                   | 560                                       | μs   |

| WATCHD                      | OG TIMER                                                         |                                                                                                 |                                           |                       |                                           |      |

| t <sub>WDTINT</sub>         | Watchdog start up detect time                                    |                                                                                                 | 250                                       | 500                   | 1000                                      | ms   |

| t <sub>WDWT</sub>           | Watchdog detect time                                             |                                                                                                 | 50                                        | 100                   | 150                                       | μs   |

| 2.5V LDO                    | ; I <sub>REG33OUT</sub> = 0mA; T <sub>A</sub> = 25°C (unless oth | nerwise noted)                                                                                  | 1                                         |                       |                                           |      |

| V <sub>REG25</sub>          | Regulator output voltage                                         | 4.5 < VCC or BAT < 25V; $I_{REG25OUT}$<br>≤16mA; $T_A = -40^{\circ}$ C to 100°C                 | 2.41                                      | 2.5                   | 2.59                                      | V    |

| ∆V <sub>REG25</sub><br>temp | Regulator output change with temperature                         | $I_{REG25OUT} = 2mA; T_A = -40^{\circ}C$ to 100°C                                               |                                           | ±0.2                  |                                           | %    |

| $\Delta V_{REG25L}$ INE     | Line regulation                                                  | 5.4 < VCC or BAT < 25V; $I_{REG25OUT}$<br>= 2mA                                                 |                                           | 3                     | 10                                        | mV   |

| $\Delta V_{REG25L}$         | Lood Degulation                                                  | $0.2\text{mA} \le I_{\text{REG25OUT}} \le 2\text{mA}$                                           |                                           | 7                     | 25                                        | m)/  |

| OAD                         | Load Regulation                                                  | $0.2\text{mA} \le I_{\text{REG25OUT}} \le 16\text{mA}$                                          |                                           | 15                    | 50                                        | mV   |

| I <sub>REG25MA</sub><br>X   | Current Limit                                                    | drawing current until REG25 = 2V to 0V                                                          | 5                                         | 40                    | 75                                        | mA   |

| 3.3V LDO                    | ; I <sub>REG25OUT</sub> = 0mA; T <sub>A</sub> = 25°C (unless oth | nerwise noted)                                                                                  | ·                                         |                       |                                           |      |

| V <sub>REG33</sub>          | Regulator output voltage                                         | 4.5 < VCC or BAT < 25V; $I_{REG33OUT}$<br>≤ 25mA; $T_{A} = -40^{\circ}$ C to 100°C              | 3                                         | 3.3                   | 3.6                                       | V    |

| ΔV <sub>REG33</sub><br>temp | Regulator output change with temperature                         | $I_{REG33OUT} = 2mA; T_A = -40^{\circ}C$ to 100°C                                               |                                           | ±0.2                  |                                           | %    |

| $\Delta V_{REG33L}$         | Line regulation                                                  | 5.4 < VCC or BAT < 25V; I <sub>REG33OUT</sub><br>= 2mA                                          |                                           | 3                     | 17                                        | mV   |

| $\Delta V_{REG33L}$         | Load Regulation                                                  | $0.2\text{mA} \le I_{\text{REG33OUT}} \le 2\text{mA}$                                           |                                           | 7                     | 17                                        | m)/  |

| OAD                         |                                                                  | $0.2\text{mA} \le I_{\text{REG33OUT}} \le 25\text{mA}$                                          |                                           | 40                    | 100                                       | mV   |

| I <sub>REG33MA</sub>        | Current Limit                                                    | drawing current until REG33 = 3V                                                                | 25                                        | 100                   | 145                                       | mA   |

| Х                           |                                                                  | short REG33 to VSS, REG33 = 0V                                                                  | 12                                        |                       | 65                                        | ША   |

| THERMIS                     | TOR DRIVE                                                        |                                                                                                 |                                           |                       |                                           |      |

| V <sub>TOUT</sub>           | Output voltage                                                   | $I_{TOUT} = 0mA; T_A = 25^{\circ}C$                                                             |                                           | V <sub>REG25</sub>    |                                           | V    |

| R <sub>DS(ON)</sub>         | TOUT pass element resistance                                     | $I_{TOUT} = 1mA; R_{DS(ON)} = (V_{REG25} - V_{TOUT}) / 1mA; T_A = -40^{\circ}C to 100^{\circ}C$ |                                           | 50                    | 100                                       | Ω    |

| VCELL+ I                    | HIGH VOLTAGE TRANSLATION                                         |                                                                                                 |                                           |                       | ·                                         |      |

| V <sub>VCELL+O</sub>        |                                                                  | $VC(n) - VC(n+1) = 0V; T_A = -40^{\circ}C$<br>to 100°C                                          | 0.950                                     | 0.975                 | 1                                         |      |

| UT                          |                                                                  | $VC(n) - VC(n+1) = 4.5V; T_A = -40^{\circ}C$<br>to 100°C                                        | 0.275                                     | 0.3                   | 0.375                                     |      |

| V <sub>VCELL+R</sub><br>ef  | Translation output                                               | internal AFE reference voltage ; $T_A = -40^{\circ}$ C to 100°C                                 | 0.965                                     | 0.975                 | 0.985                                     | V    |

| V <sub>VCELL+P</sub><br>ACK |                                                                  | Voltage at PACK pin; $T_A = -40^{\circ}C$ to 100°C                                              | 0.98*V <sub>PAC</sub><br><sub>K</sub> /18 | V <sub>PACK</sub> /18 | 1.02*V <sub>PA</sub><br><sub>CK</sub> /18 |      |

| V <sub>VCELL+B</sub>        |                                                                  | Voltage at BAT pin; $T_A = -40^{\circ}C$ to 100°C                                               | 0.98*V <sub>BAT</sub> /<br>18             | V <sub>BAT</sub> /18  | 1.02*V <sub>BA</sub><br><sub>T</sub> /18  |      |

| CMMR                        | Common mode rejection ratio                                      | VCELL+                                                                                          | 40                                        |                       |                                           | dB   |

| K                           | Coll scale factor                                                | K= {VCELL+ output (VC5=0V;<br>VC4=4.5V) - VCELL+ output<br>(VC5=0V; VC4=0V)}/4.5                | 0.147                                     | 0.150                 | 0.153                                     |      |

| К                           | Cell scale factor                                                | K= {VCELL+ output (VC2=13.5V;<br>VC1=18V) - VCELL+ output<br>(VC5=13.5V; VC1=13.5V)}/4.5        | 0.147                                     | 0.150                 | 0.153                                     |      |

#### **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted),  $T_A = -40^{\circ}$ C to 85°C,  $V_{REG25} = 2.41$  V to 2.59 V,  $V_{BAT} = 14$ V,  $C_{REG25} = 1\mu$ F,  $C_{REG33} = 2.2\mu$ F; typical values at  $T_A = 25^{\circ}$ C (unless otherwise noted)

|                            | PARAMETER                                             | TEST CONDITIONS                                                                                                | MIN         | TYP    | MAX  | UNIT |  |

|----------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|--------|------|------|--|

| I <sub>VCELL+OU</sub><br>T | Drive Current to VCELL+ capacitor                     | $VC(n) - VC(n+1) = 0V; VCELL+ = 0V; T_A = -40^{\circ}C \text{ to } 100^{\circ}C$                               | 12          | 18     |      | μA   |  |

| V <sub>VCELL+O</sub>       | CELL offset error                                     | CELL output (VC2 = VC1 = 18V) –<br>CELL output (VC2 = VC1 = 0V)                                                | -18         | -1     | 18   | mV   |  |

| VCnL                       | VC(n) pin leakage current                             | VC1, VC2, VC3, VC4, VC5 = 3V                                                                                   | -1          | 0.01   | 1    | μA   |  |

| CELL BAI                   | LANCING                                               | •                                                                                                              |             |        |      |      |  |

| R <sub>BAL</sub>           | internal cell balancing FET resistance                | $R_{DS(on)}$ for internal FET switch at V <sub>DS</sub> = 2V; T <sub>A</sub> = 25°C                            | 200         | 400    | 600  | Ω    |  |

| HARDWA                     | RE SHORT CIRCUIT AND OVERLOAD PI                      | ROTECTION; T <sub>A</sub> = 25°C (unless other                                                                 | wise noted) |        |      |      |  |

|                            |                                                       | V <sub>OL</sub> = 25mV (min)                                                                                   | 15          | 25     | 35   |      |  |

| V <sub>(OL)</sub>          | OL detection threshold voltage accuracy               | V <sub>OL</sub> = 100mV; RSNS = 0, 1                                                                           | 90          | 100    | 110  | mV   |  |

|                            |                                                       | V <sub>OL</sub> = 205mV (max)                                                                                  | 185         | 205    | 225  | ſ    |  |

|                            |                                                       | V <sub>SCC</sub> = 50mV (min)                                                                                  | 30          | 50     | 70   |      |  |

| V <sub>(SCC)</sub>         | SCC detection threshold voltage accuracy              | V <sub>SCC</sub> = 200mV; RSNS = 0, 1                                                                          | 180         | 200    | 220  | mV   |  |

|                            | accuracy                                              | V <sub>SCC</sub> = 475mV (max)                                                                                 | 428         | 475    | 523  |      |  |

|                            |                                                       | $V_{SCD} = -50 \text{mV} \text{ (min)}$                                                                        | -30         | -50    | -70  |      |  |

| V <sub>(SCD)</sub>         | SCD detection threshold voltage                       | V <sub>SCD</sub> = -200mV; RSNS = 0, 1                                                                         | -180        | -200   | -220 | mV   |  |

| . /                        | accuracy                                              | $V_{SCD} = -475 \text{mV} \text{ (max)}$                                                                       | -428        | -475   | -523 | ]    |  |

| t <sub>da</sub>            | Delay time accuracy                                   |                                                                                                                |             | ±15.25 |      | μS   |  |

| t <sub>pd</sub>            | Protection circuit propagation delay                  |                                                                                                                |             | 50     |      | μS   |  |

|                            | E CIRCUIT; $T_A = 25^{\circ}C$ (unless otherwise      | noted)                                                                                                         |             |        |      |      |  |

| V <sub>DSGON</sub>         | DSG pin output on voltage                             | $V_{DSGON} = V_{DSG} - V_{PACK}; V_{GS} =$<br>10M $\Omega$ ;DSG and CHG on; T <sub>A</sub> =<br>-40°C to 100°C | 8           | 12     | 16   | V    |  |

| V <sub>CHGON</sub>         | CHG pin output on voltage                             | $V_{CHGON} = V_{CHG} - V_{BAT}$ ; $V_{GS} = 10M\Omega$ ;DSG and CHG on; $T_A = -40^{\circ}$ C to 100°C         | 8           | 12     | 16   | V    |  |

| V <sub>DSGOFF</sub>        | DSG pin output off voltage                            | V <sub>DSGOFF</sub> = V <sub>DSG</sub> - V <sub>PACK</sub>                                                     |             |        | 0.2  | V    |  |

| V <sub>CHGOFF</sub>        | CHG pin output off voltage                            | $V_{CHGOFF} = V_{CHG} - V_{BAT}$                                                                               |             |        | 0.2  | V    |  |

| t <sub>R</sub>             | Rise time                                             | $C_L=4700 \text{pF}; V_{PACK} \le \text{DSG} \le V_{PACK} + 4V$                                                |             | 400    | 1000 | μS   |  |

| TX .                       |                                                       | $C_L$ =4700pF; $V_{BAT}$ ≤ CHG ≤ $V_{BAT}$ + 4V                                                                |             | 400    | 1000 |      |  |

|                            | F-II (inc                                             | $C_L$ =4700pF; $V_{PACK}$ + $V_{DSGON} \le DSG \le V_{PACK}$ + 1V                                              |             | 40     | 200  |      |  |

| t <sub>F</sub>             | Fall time                                             | $C_L=4700pF; V_{BAT} + V_{CHGON} \le CHG \le V_{BAT} + 1V$                                                     |             | 40     | 200  | μS   |  |

| V <sub>ZVCHG</sub>         | ZVCHG clamp voltage                                   | BAT = 4.5V                                                                                                     | 3.3         | 3.5    | 3.7  | V    |  |

| LOGIC; T                   | $_{A} = -40^{\circ}$ C to 100°C (unless otherwise not | ted)                                                                                                           |             |        |      |      |  |

| <b>D</b>                   |                                                       | ALERT                                                                                                          | 60          | 100    | 200  | 1.0  |  |

| R <sub>PULLUP</sub>        | Internal pullup resistance                            | RESET                                                                                                          | 1           | 3      | 6    | kΩ   |  |

|                            |                                                       | ALERT                                                                                                          |             |        | 0.2  |      |  |

| V <sub>OL</sub>            | Logic low output voltage level                        | $\overline{\frac{RESET}{RESET}}; V_{BAT} = 7V; V_{REG25} = 1.5V; I$ $\overline{RESET} = 200\muA$               |             |        | 0.4  | V    |  |

|                            |                                                       | GPOD; $I_{GPOD} = 50\mu A$                                                                                     |             |        | 0.6  | 1    |  |

|                            | IBC, SMBD, PFIN, PRES, SAFE, ALERT                    |                                                                                                                | 4           |        |      | L    |  |

| LOGIC SN                   |                                                       |                                                                                                                |             |        |      |      |  |

| VIH                        | High-level input voltage                              |                                                                                                                | 2.0         |        |      | V    |  |

#### SLUS723C -JULY 2007-REVISED JULY 2008

### Electrical Characteristics (continued)

over operating free-air temperature range (unless otherwise noted), T<sub>A</sub> = -40°C to 85°C, V<sub>REG25</sub> = 2.41 V to 2.59 V, V<sub>BAT</sub> = 14V,  $C_{REG25} = 1\mu F$ ,  $C_{REG33} = 2.2\mu F$ ; typical values at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITIONS                               | MIN                         | TYP    | MAX                         | UNIT                |

|------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|--------|-----------------------------|---------------------|

| V <sub>OH</sub>        | Output voltage high <sup>(1)</sup>         | SAFE, $I_L = -0.5 \text{ mA}$                 | V <sub>REG25</sub> –0.<br>5 |        |                             | V                   |

| V <sub>OL</sub>        | Low-level output voltage                   | PRES, PFIN, ALERT, $I_L = 7 \text{ mA}$ ;     |                             |        | 0.4                         | V                   |

| CI                     | Input capacitance                          |                                               |                             | 5      |                             | pF                  |

| I <sub>(SAFE)</sub>    | SAFE source currents                       | SAFE active, SAFE = V <sub>REG25</sub> –0.6 V | -3                          |        |                             | mA                  |

| I <sub>lkg(SAFE)</sub> | SAFE leakage current                       | SAFE inactive                                 | -0.2                        |        | 0.2                         | μA                  |

| l <sub>lkg</sub>       | Input leakage current                      |                                               |                             |        | 1                           | μA                  |

| ADC <sup>(2)</sup>     |                                            |                                               |                             |        |                             |                     |

|                        | Input voltage range                        | TS1,TS2, using external V <sub>ref</sub>      | -0.2                        |        | V <sub>REG25</sub> +<br>0.2 | V                   |

|                        | Conversion time                            |                                               |                             | 31.5   |                             | ms                  |

|                        | Resolution (no missing codes)              |                                               | 16                          |        |                             | bits                |

|                        | Effective resolution                       |                                               | 14                          | 15     |                             | bits                |

|                        | Integral nonlinearity                      |                                               |                             |        | ±0.03                       | %FSR <sup>(3)</sup> |

|                        | Offset error <sup>(4)</sup>                |                                               |                             | 140    | 250                         | μV                  |

|                        | Offset error drift <sup>(4)</sup>          | $T_A = 25^{\circ}C$ to $85^{\circ}C$          |                             | 2.5    | 18                          | μV/°C               |

|                        | Full-scale error <sup>(5)</sup>            |                                               |                             | ±0.1%  | ±0.7%                       |                     |

|                        | Full-scale error drift                     |                                               |                             | 50     |                             | PPM/°C              |

|                        | Effective input resistance <sup>(6)</sup>  |                                               | 8                           |        |                             | MΩ                  |

| COULON                 | IB COUNTER                                 |                                               |                             |        |                             |                     |

|                        | Input voltage range                        |                                               | -0.20                       |        | 0.20                        | V                   |

|                        | Conversion time                            | Single conversion                             |                             | 250    |                             | ms                  |

|                        | Effective resolution                       | Single conversion                             | 15                          |        |                             | bits                |

|                        |                                            | -0.1 V to 0.20 V                              |                             | ±0.007 | ±0.034                      | 0/ FOD              |

|                        | Integral nonlinearity                      | -0.20 V to -0.1 V                             |                             | ±0.007 |                             | %FSR                |

|                        | Offset error <sup>(7)</sup>                | $T_A = 25^{\circ}C$ to $85^{\circ}C$          |                             | 10     |                             | μV                  |

|                        | Offset error drift                         |                                               |                             | 0.4    | 2.45                        | µV/°C               |

|                        | Full-scale error <sup>(8) (9)</sup>        |                                               |                             | ±0.35% |                             |                     |

|                        | Full-scale error drift                     |                                               |                             | 150    |                             | PPM/°C              |

|                        | Effective input resistance <sup>(10)</sup> | $T_A = 25^{\circ}C$ to $85^{\circ}C$          | 2.5                         |        |                             | MΩ                  |

| INTERNA                | AL TEMPERATURE SENSOR                      |                                               |                             |        |                             |                     |

| V <sub>(TEMP)</sub>    | Temperature sensor voltage <sup>(11)</sup> |                                               |                             | -2.0   |                             | mV/°C               |

| VOLTAG                 | EREFERENCE                                 |                                               |                             |        |                             |                     |

|                        | Output voltage                             |                                               | 1.215                       | 1.225  | 1.230                       | V                   |

|                        | Output voltage drift                       |                                               |                             | 65     |                             | PPM/°C              |

| HIGH FR                | EQUENCY OSCILLATOR                         |                                               |                             |        |                             |                     |

| f <sub>(OSC)</sub>     | Operating frequency                        |                                               |                             | 4.194  |                             | MHz                 |

RC[0:7] bus (1)

(2) Unless otherwise specified, the specification limits are valid at all measurement speed modes

(3) Full-scale reference

(4) Post-calibration performance and no I/O changes during conversion with SRN as the ground reference

(5) Uncalibrated performance. This gain error can be eliminated with external calibration.

(6) The A/D input is a switched-capacitor input. Since the input is switched, the effective input resistance is a measure of the average resistance.

Post-calibration performance (7)

(8) Reference voltage for the coulomb counter is typically  $V_{ref}$ /3.969 at  $V_{REG25}$  = 2.5 V,  $T_A$  = 25°C. (9) Uncalibrated performance. This gain error can be eliminated with external calibration.

- (10) The CC input is a switched capacitor input. Since the input is switched, the effective input resistance is a measure of the average resistance.

(11) -53.7 LSB/°C

#### **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted),  $T_A = -40^{\circ}$ C to 85°C,  $V_{REG25} = 2.41$  V to 2.59 V,  $V_{BAT} = 14$ V,  $C_{REG25} = 1\mu$ F,  $C_{REG33} = 2.2\mu$ F; typical values at  $T_A = 25^{\circ}$ C (unless otherwise noted)

|                     | PARAMETER                            | TEST CONDITIONS                      | MIN   | TYP    | MAX  | UNIT |

|---------------------|--------------------------------------|--------------------------------------|-------|--------|------|------|

| 4                   | Frequency error <sup>(12)</sup> (13) |                                      | -3%   | 0.25%  | 3%   |      |

| f <sub>(EIO)</sub>  | (EIO) Frequency error (15) (15)      | $T_A = 20^{\circ}C$ to $70^{\circ}C$ | -2%   | 0.25%  | 2%   |      |

| t <sub>(SXO)</sub>  | Start-up time <sup>(14)</sup>        |                                      |       | 2.5    | 5    | ms   |

| LOW FR              | REQUENCY OSCILLATOR                  |                                      | ·     |        |      |      |

| f <sub>(LOSC)</sub> | Operating frequency                  |                                      |       | 32.768 |      | kHz  |

| £                   | Frequency error <sup>(13)</sup> (15) |                                      | -2.5% | 0.25%  | 2.5% |      |

| f <sub>(LEIO)</sub> | I(LEIO) Frequency error (1/2)        | $T_A = 20^{\circ}C$ to $70^{\circ}C$ | -1.5% | 0.25%  | 1.5% |      |

| t <sub>(LSXO)</sub> | Start-up time <sup>(14)</sup>        |                                      |       |        | 500  | μs   |

(12) The frequency error is measured from 4.194 MHz.

(13) The frequency drift is included and measured from the trimmed frequency at  $V_{REG25} = 2.5V$ ,  $T_A = 25^{\circ}C$

(14) The startup time is defined as the time it takes for the oscillator output frequency to be  $\pm 3\%$

(15) The frequency error is measured from 32.768 kHz.

#### Data Flash Characteristics Over Recommended Operating Temperature and Supply Voltage

Typical Values at  $T_A = 25^{\circ}C$  and  $V_{REG25} = 2.5 V$  (unless otherwise noted)

|                          | PARAMETER                                      | TEST CONDITIONS                                                                                                            | MIN | TYP  | MAX    | UNIT   |  |

|--------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------|--------|--------|--|

|                          | Data retention                                 |                                                                                                                            | 10  |      |        | Years  |  |

|                          | Flash programming write-cycles                 |                                                                                                                            | 20k |      |        | Cycles |  |

| t <sub>(ROWPROG)</sub>   | Row programming time                           | See <sup>(1)</sup>                                                                                                         |     |      | 2      | ms     |  |

| t <sub>(MASSERASE)</sub> | Mass-erase time                                |                                                                                                                            |     |      | 200    | ms     |  |

| t <sub>(PAGEERASE)</sub> | Page-erase time                                |                                                                                                                            |     |      | 20     | ms     |  |

| I(DDPROG)                | Flash-write supply current                     |                                                                                                                            |     | 5    | 10     | mA     |  |

| I(DDERASE)               | Flash-erase supply current                     |                                                                                                                            |     | 5    | 10     | mA     |  |

| RAM BACKU                | JP                                             |                                                                                                                            |     |      |        |        |  |

|                          |                                                | $V_{(\text{RBI})} > V_{(\text{RBI})\text{MIN}}$ , $V_{\text{REG25}} < V_{\text{IT-}},$ $T_{\text{A}} = 85^{\circ}\text{C}$ |     | 1000 | 2500   | - 1    |  |

| I <sub>(RB)</sub>        | RB data-retention input current                | $V_{(RBI)} > V_{(RBI)MIN}$ , $V_{REG25} < V_{IT-}$ ,<br>$T_A = 25^{\circ}C$                                                |     | 90   | 220 nA |        |  |

| V <sub>(RB)</sub>        | RB data-retention input voltage <sup>(1)</sup> |                                                                                                                            | 1.7 |      |        | V      |  |

(1) Assured by design. Not production tested.

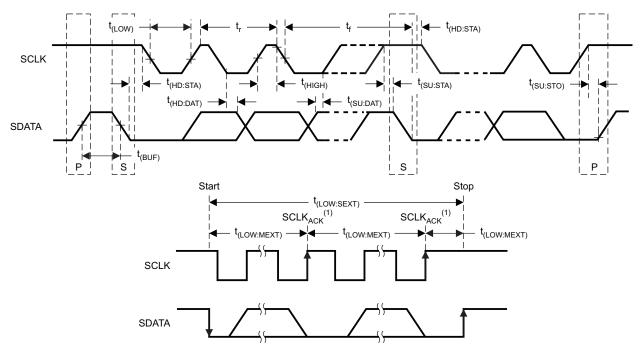

#### **SMBus Timing Characteristics**

$T_A = -40^{\circ}C$  to 85°C Typical Values at  $T_A = 25^{\circ}C$  and  $V_{(REG25)} = 2.5$  V (Unless Otherwise Noted)

|                       | PARAMETER                                           | TEST CONDITIONS                        | MIN | TYP  | MAX | UNIT |

|-----------------------|-----------------------------------------------------|----------------------------------------|-----|------|-----|------|

| f <sub>SMB</sub>      | SMBus operating frequency                           | Slave mode, SMBC 50% duty cycle        | 10  |      | 100 | kHz  |

| f <sub>MAS</sub>      | SMBus master clock frequency                        | Master mode, No clock low slave extend |     | 51.2 |     | kHz  |

| $t_{(BUF)}$           | Bus free time between start and stop (see Figure 1) |                                        | 4.7 |      |     | μs   |

| t <sub>(HD:STA)</sub> | Hold time after (repeated) start (see Figure 1)     |                                        | 4.0 |      |     | μs   |

| t <sub>(SU:STA)</sub> | Repeated start setup time (see Figure 1)            |                                        | 4.7 |      |     | μs   |

| t <sub>(SU:STO)</sub> | Stop setup time (see Figure 1)                      |                                        | 4.0 |      |     | μs   |

| t <sub>(HD:DAT)</sub> |                                                     | Receive mode                           | 0   |      |     | ns   |

|                       | Data hold time (see Figure 1)                       | Transmit mode                          | 300 |      |     |      |

| t <sub>(SU:DAT)</sub> | Data setup time (see Figure 1)                      |                                        | 250 |      |     | ns   |

INSTRUMENTS

Texas

#### SMBus Timing Characteristics (continued)

$T_A = -40$ °C to 85°C Typical Values at  $T_A = 25$ °C and  $V_{(REG25)} = 2.5$  V (Unless Otherwise Noted)

|                         | PARAMETER                                              | TEST CONDITIONS    | MIN | TYP | MAX  | UNIT |

|-------------------------|--------------------------------------------------------|--------------------|-----|-----|------|------|

| t <sub>(TIMEOUT)</sub>  | Error signal/detect (see Figure 1)                     | See <sup>(1)</sup> | 25  |     | 35   | μs   |

| t <sub>(LOW)</sub>      | Clock low period (see Figure 1)                        |                    | 4.7 |     |      | μs   |

| t <sub>(HIGH)</sub>     | Clock high period (see Figure 1)                       | See <sup>(2)</sup> | 4.0 |     | 50   | μs   |

| t <sub>(LOW:SEXT)</sub> | Cumulative clock low slave extend time                 | See <sup>(3)</sup> |     |     | 25   | μs   |

| t <sub>(LOW:MEXT)</sub> | Cumulative clock low master extend time (see Figure 1) | See <sup>(4)</sup> |     |     | 10   | μs   |

| t <sub>f</sub>          | Clock/data fall time                                   | See <sup>(5)</sup> |     |     | 300  | ns   |

| t <sub>r</sub>          | Clock/data rise time                                   | See <sup>(6)</sup> |     |     | 1000 | ns   |

(1)

The bq20z75 times out when any clock low exceeds  $t_{(TIMEOUT)}$ .  $t_{(HIGH)}$ , Max, is the minimum bus idle time. SMBC = SMBD = 1 for t > 50 ms causes reset of any transaction involving bq20z75 that is in (2) progress. This specification is valid when the NC\_SMB control bit remains in the default cleared state (CLK[0]=0).

- (3)t(LOW:SEXT) is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

- (4) t(LOW:MEXT) is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

- (5) Rise time  $t_r = VILMAX - 0.15$  to (VIHMIN + 0.15)

- Fall time  $t_f = 0.9V_{DD}$  to (VILMAX 0.15) (6)

(1) SCLK<sub>ACK</sub> is the acknowledge-related clock pulse generated by the master.

#### Figure 1. SMBus Timing Diagram

Texas

INSTRUMENTS

# SLUS723C – JULY 2007 – REVISED JULY 2008

#### FEATURE SET

#### Primary (1st Level) Safety Features

The bq20z75 supports a wide range of battery and system protection features that can easily be configured. The primary safety features include:

- Cell over/under voltage protection

- Charge and Discharge over current

- Short Circuit

- Charge and Discharge Over temperature

- AFE Watchdog

#### Secondary (2nd Level) Safety Features

The secondary safety features of the bq20z75 can be used to indicate more serious faults via the SAFE (pin 7). This pin can be used to blow an in-line fuse to permanently disable the battery pack from charging or discharging. The secondary safety protection features include:

- Safety overvoltage

- Safety overcurrent in Charge and Discharge

- Safety overtemperature in Charge and Discharge

- Charge FET and 0 Volt Charge FET fault

- Discharge FET fault

- AFE communication fault

#### Charge Control Features

The bq20z75 charge control features include:

- Reports the appropriate charging current needed for constant current charging and the appropriate charging voltage needed for constant voltage charging to a smart charger using SMBus broadcasts.

- Determines the chemical state of charge of each battery cell using Impedance Track<sup>™</sup> and can reduce the charge difference of the battery cells in fully charged state of the battery pack gradually using cell balancing algorithm during charging. This prevents fully charged cells from overcharging and causing excessive degradation and also increases the usable pack energy by preventing premature charge termination

- Supports pre-charging/zero-volt charging

- Support fast charging

- Supports charge inhibit and charge suspend if battery pack temperature is out of temperature range

- Reports charging fault and also indicate charge status via charge and discharge alarms.

#### Gas Gauging

The bq20z75 uses the Impedance Track<sup>™</sup> Technology to measure and calculate the available charge in battery cells. The achievable accuracy is better than 1% error over the lifetime of the battery and there is no full charge discharge learning cycle required.

See Theory and Implementation of Impedance Track Battery Fuel-Gauging Algorithm application note (SLUA364) for further details.

#### Authentication

The bq20z75 supports authentication by the host using SHA-1.

#### **Power Modes**

The bq20z75 supports 3 different power modes to reduce power consumption:

In Normal Mode, the bq20z75 performs measurements, calculations, protection decisions and data updates in 1 second intervals. Between these intervals, the bq20z75 is in a reduced power stage.

- In Sleep Mode, the bq20z75 performs measurements, calculations, protection decisions and data update in adjustable time intervals. Between these intervals, the bq20z75 is in a reduced power stage. The bq20z75 has a wake function that enables exit from Sleep mode, when current flow or failure is detected.

- In Shutdown Mode the bq20z75 is completely disabled.

#### CONFIGURATION

#### **Oscillator Function**

The bq20z75 fully integrates the system oscillators. Therefore the bq20z75 requires no external components for this feature.

#### System Present Operation

<u>The bq20z75</u> checks the PRES pin periodically (1 s). Connect the PRES pin to TOUT with a 100k $\Omega$  resistor. If PRES input is pulled to ground by external system host, the bq20z75 detects this as system present.

#### BATTERY PARAMETER MEASUREMENTS

The bq20z75 uses an integrating delta-sigma analog-to-digital converter (ADC) for current measurement, and a second delta-sigma ADC for individual cell and battery voltage, and temperature measurement.

#### Charge and Discharge Counting

The integrating delta-sigma ADC measures the charge/discharge flow of the battery by measuring the voltage drop across a small-value sense resistor between the SRP and SRN pins. The integrating ADC measures bipolar signals from -0.25 V to 0.25 V. The bq20z75 detects charge activity when  $V_{SR} = V_{(SRP)} - V_{(SRN)}$  is positive and discharge activity when  $V_{SR} = V_{(SRP)} - V_{(SRN)}$  is negative. The bq20z75 continuously integrates the signal over time, using an internal counter. The fundamental rate of the counter is 0.65 nVh.

#### Voltage

The bq20z75 updates the individual series cell voltages at one second intervals. The internal ADC of the bq20z75 measures the voltage, scales and calibrates it appropriately. This data is also used to calculate the impedance of the cell for the Impedance Track<sup>™</sup> gas-gauging.

#### Current

The bq20z75 uses the GSRP and GSRN inputs to measure and calculate the battery charge and discharge current using a 5 m $\Omega$  to 20 m $\Omega$  typ. sense resistor.

#### Auto Calibration

The bq20z75 provides an auto-calibration feature to cancel the voltage offset error across GSRN and GSRP for maximum charge measurement accuracy. The bq20z75 performs auto-calibration when the SMBus lines stay low continuously for a minimum of 5 s.

#### Temperature

The bq20z75 has an internal temperature sensor and 2 external temperature sensor inputs TS1 and TS2 used in conjunction with two identical NTC thermistors (default are Semitec 103AT) to sense the battery environmental temperature. The bq20z75 can be configured to use internal or external temperature sensors.

#### COMMUNICATIONS

The bq20z75 uses SMBus v1.1 with Master Mode and package error checking (PEC) options per the SBS specification.

#### SMBus On and Off State

The bq20z75 detects an SMBus off state when SMBC and SMBD are logic-low for  $\geq$  2 seconds. Clearing this state requires either SMBC or SMBD to transition high. Within 1 ms, the communication bus is available.

SLUS723C - JULY 2007 - REVISED JULY 2008

#### www.ti.com

#### SBS and Dataflash Values

| SBS<br>Cmd | Mode | Name                   | Format       | Size in<br>Bytes | Min<br>Value | Max<br>Value | Default<br>Value     | Unit            |

|------------|------|------------------------|--------------|------------------|--------------|--------------|----------------------|-----------------|

| 0x00       | R/W  | ManufacturerAccess     | hex          | 2                | 0x0000       | Oxffff       | —                    |                 |

| 0x01       | R/W  | RemainingCapacityAlarm | unsigned int | 2                | 0            | 65535        | _                    | mAh or<br>10mWh |

| 0x02       | R/W  | RemainingTimeAlarm     | unsigned int | 2                | 0            | 65535        | —                    | min             |

| 0x03       | R/W  | BatteryMode            | hex          | 2                | 0x0000       | Oxffff       | —                    |                 |

| 0x04       | R/W  | AtRate                 | signed int   | 2                | -32768       | 32767        | —                    | mA or 10mW      |

| 0x05       | R    | AtRateTimeToFull       | unsigned int | 2                | 0            | 65535        | —                    | min             |

| 0x06       | R    | AtRateTimeToEmpty      | unsigned int | 2                | 0            | 65535        | —                    | min             |

| 0x07       | R    | AtRateOK               | unsigned int | 2                | 0            | 65535        | —                    |                 |

| 0x08       | R    | Temperature            | unsigned int | 2                | 0            | 65535        | —                    | 0.1°K           |

| 0x09       | R    | Voltage                | unsigned int | 2                | 0            | 20000        | —                    | mV              |

| 0x0a       | R    | Current                | signed int   | 2                | -32768       | 32767        | —                    | mA              |

| 0x0b       | R    | AverageCurrent         | signed int   | 2                | -32768       | 32767        | —                    | mA              |

| 0x0c       | R    | MaxError               | unsigned int | 1                | 0            | 100          | —                    | %               |

| 0x0d       | R    | RelativeStateOfCharge  | unsigned int | 1                | 0            | 100          | _                    | %               |

| 0x0e       | R    | AbsoluteStateOfCharge  | unsigned int | 1                | 0            | 100          | _                    | %               |

| 0x0f       | R/W  | RemainingCapacity      | unsigned int | 2                | 0            | 65535        | —                    | mAh or<br>10mWh |

| 0x10       | R    | FullChargeCapacity     | unsigned int | 2                | 0            | 65535        | —                    | mAh or<br>10mWh |

| 0x11       | R    | RunTimeToEmpty         | unsigned int | 2                | 0            | 65535        | —                    | min             |

| 0x12       | R    | AverageTimeToEmpty     | unsigned int | 2                | 0            | 65535        | _                    | min             |

| 0x13       | R    | AverageTimeToFull      | unsigned int | 2                | 0            | 65535        | _                    | min             |

| 0x14       | R    | ChargingCurrent        | unsigned int | 2                | 0            | 65535        | _                    | mA              |

| 0x15       | R    | ChargingVoltage        | unsigned int | 2                | 0            | 65535        | —                    | mV              |

| 0x16       | R    | BatteryStatus          | unsigned int | 2                | 0x0000       | Oxffff       | —                    |                 |

| 0x17       | R/W  | CycleCount             | unsigned int | 2                | 0            | 65535        | _                    |                 |

| 0x18       | R/W  | DesignCapacity         | unsigned int | 2                | 0            | 65535        | _                    | mAh or<br>10mWh |

| 0x19       | R/W  | DesignVoltage          | unsigned int | 2                | 7000         | 16000        | 14400                | mV              |

| 0x1a       | R/W  | SpecificationInfo      | unsigned int | 2                | 0x0000       | Oxffff       | 0x0031               |                 |

| 0x1b       | R/W  | ManufactureDate        | unsigned int | 2                | 0            | 65535        | 0                    |                 |

| 0x1c       | R/W  | SerialNumber           | hex          | 2                | 0x0000       | Oxffff       | -                    |                 |

| 0x20       | R/W  | ManufacturerName       | String       | 11+1             | -            | _            | Texas<br>Instruments | ASCII           |

| 0x21       | R/W  | DeviceName             | String       | 7+1              | _            | —            | bq20z75              | ASCII           |

| 0x22       | R/W  | DeviceChemistry        | String       | 4+1              | _            | _            | LION                 | ASCII           |

| 0x23       | R    | ManufacturerData       | String       | 14+1             | _            | _            | _                    | ASCII           |

| 0x2f       | R/W  | Authenticate           | String       | 20+1             | _            | _            | _                    | ASCII           |