The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

### How to Check the Ordering Part Number

- 1. Go to <u>www.cypress.com/pcn</u>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to www.cypress.com.

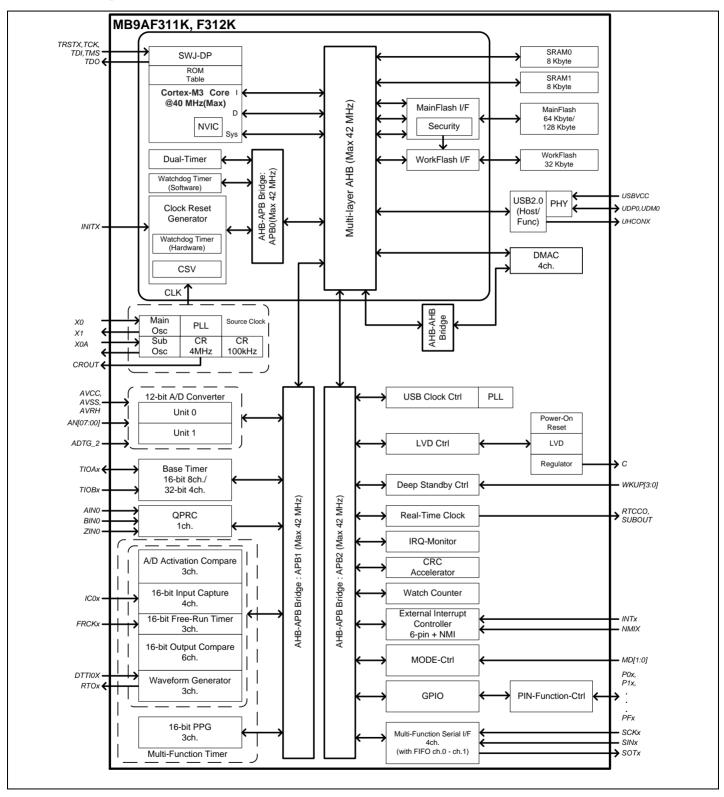

## **MB9A310K Series**

## 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M3 FM3 Microcontroller

The MB9A310K Series are a highly integrated 32-bit microcontrollers dedicated for embedded controllers with high-performance and low cost.

These series are based on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 Processor with on-chip Flash memory and SRAM, and has peripheral functions such as Motor Control Timers, ADCs and Communication Interfaces (USB, UART, CSIO, I<sup>2</sup>C, LIN).

The products which are described in this Datasheet are placed into TYPE5 product categories in "FM3 Family Peripheral Manual".

## Features

#### 32-bit ARM Cortex-M3 Core

- Processor version: r2p1

- ■Up to 40MHz Frequency Operation

- Integrated Nested Vectored Interrupt Controller (NVIC): 1 NMI (non-maskable interrupt) and 48 peripheral interrupts and 16 priority levels

- 24-bit System timer (Sys Tick): System timer for OS task management

#### **On-chip Memories**

#### [Flash memory]

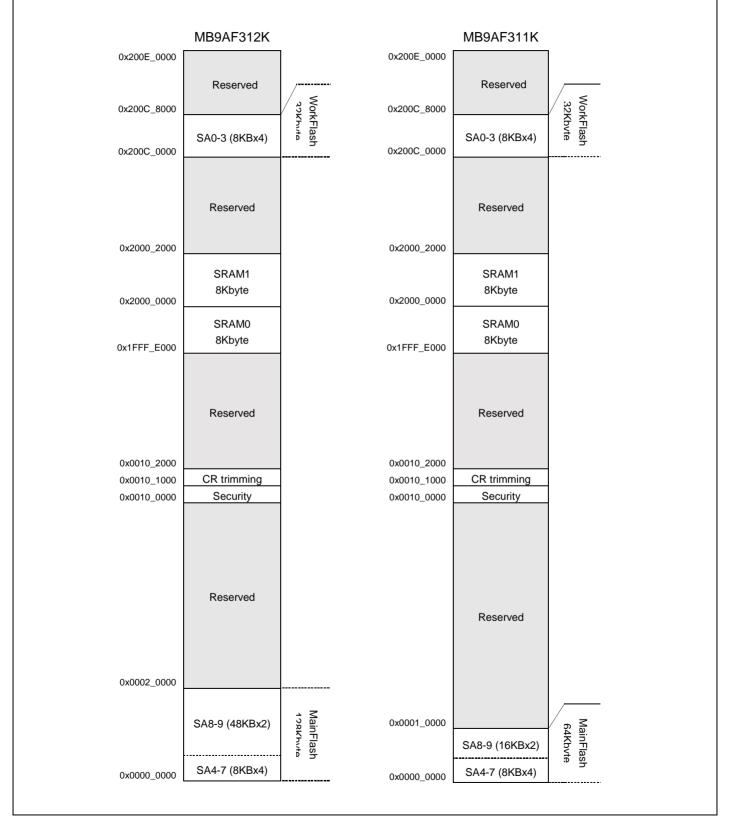

This Series are based on two independent on-chip Flash memories.

#### ■ MainFlash

- □ Up to 128Kbyte □ Read cycle: 0 wait-cycle

- $\square$  Security function for code protection

#### ■WorkFlash

- □ 32Kbyte

- □ Read cycle: 0 wait-cycle

- □ Security function is shared with code protection

#### [SRAM]

This Series contain a total of up to 16Kbyte on-chip SRAM. This is composed of two independent SRAM (SRAM0, SRAM1) . SRAM0 is connected to I-code bus and D-code bus of Cortex-M3 core. SRAM1 is connected to System bus.

SRAM0: 8 Kbyte

#### SRAM1: 8 Kbyte

#### **USB** Interface

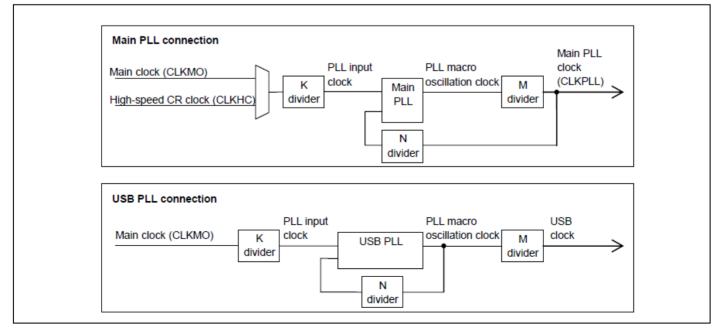

USB interface is composed of Device and Host. PLL for USB is built-in, USB clock can be generated by multiplication of Main clock.

#### [USB device]

- ■USB2.0 Full-Speed supported

- Max 6 EndPoint supported

- □ EndPoint 0 is control transfer

- □ EndPoint 1, 2 can be selected Bulk-transfer, Interrupttransfer or Isochronous-transfer

- □ EndPoint 3 to 5 can be selected Bulk-transfer or Interrupttransfer

- □ EndPoint 1 to 5 is comprised Double Buffer

- □ The size of each EndPoint is as follows.

- EndPoint 0, 2 to 5: 64 bytes

- EndPoint 1: 256 bytes

#### [USB host]

- ■USB2.0 Full/Low-speed supported

- Bulk-transfer, interrupt-transfer and Isochronous-transfer support

- ■USB Device connected/dis-connected automatically detect

- ■IN/OUT token handshake packet automatically

- Max 256-byte packet-length supported

- ■Wake-up function supported

#### Multi-function Serial Interface (Max 4 channels)

- 2 channels with 16-steps × 9-bits FIFO (ch.0, ch.1), 2 channels without FIFO (ch.3, ch.5)

- Operation mode is selectable from the followings for each channel.

(In ch.5, only UART and LIN are available.) □ UART □ CSIO □ LIN □ I<sup>2</sup>C

#### [UART]

- Full-duplex double buffer

- Selection with or without parity supported

- Built-in dedicated baud rate generator

- External clock available as a serial clock

- Hardware Flow control: Automatically control the transmission by CTS/RTS (only ch.4)

- Various error detect functions available (parity errors, framing errors, and overrun errors)

#### [CSIO]

- Full-duplex double buffer

- Built-in dedicated baud rate generator

- Overrun error detect function available

#### [LIN]

- LIN protocol Rev.2.1 supported

- Full-duplex double buffer

- Master/Slave mode supported

- LIN break field generate (can be changed 13 to 16-bit length)

- LIN break delimiter generate (can be changed 1 to 4-bit length)

- Various error detect functions available (parity errors, framing errors, and overrun errors)

### [l<sup>2</sup>C]

Standard mode (Max 100 kbps) / Fast-mode (Max 400 kbps) supported

#### **DMA Controller (4 channels)**

DMA Controller has an independent bus for CPU, so CPU and DMA Controller can process simultaneously.

- 8 independently configured and operated channels

- Transfer can be started by software or request from the builtin peripherals

- ■Transfer address area: 32-bit (4 Gbyte)

- Transfer mode: Block transfer/Burst transfer/Demand transfer

- Transfer data type: byte/half-word/word

- Transfer block count: 1 to 16

- ■Number of transfers: 1 to 65536

#### A/D Converter (Max 8 channels)

#### [12-bit A/D Converter]

- Successive Approximation Register type

- ■Built-in 2 unit

- Conversion time: 1.0 µs@5 V

- Priority conversion available (priority at 2 levels)

- Scanning conversion mode

- Built-in FIFO for conversion data storage (for SCAN conversion: 16 steps, for Priority conversion: 4 steps)

#### **Base Timer (Max 8 channels)**

Operation mode is selectable from the followings for each channel.

- 16-bit PWM timer

- ■16-bit PPG timer

- ■16-/32-bit reload timer

- ■16-/32-bit PWC timer

#### **General Purpose I/O Port**

This series can use its pins as General Purpose I/O ports when they are not used for external bus or peripherals. Moreover, the port relocate function is built in. It can set which I/O port the peripheral function can be allocated.

- Capable of pull-up control per pin

- Capable of reading pin level directly

- Built-in the port relocate function

- ■Up 36 fast General Purpose I/O Ports

- Some pin is 5V tolerant I/O. See "Pin Description" to confirm the corresponding pins.

#### **Multi-function Timer**

The Multi-function timer is composed of the following blocks.

- ■16-bit free-run timer × 3 ch.

- ■Input capture × 4 ch.

- ■Output compare × 6 ch.

- ■A/D activating compare × 3 ch.

- ■Waveform generator × 3 ch.

- ■16-bit PPG timer × 3 ch.

The following function can be used to achieve the motor control.

- PWM signal output function

- DC chopper waveform output function

- Dead time function

- Input capture function

- A/D convertor activate function

DTIF (Motor emergency stop) interrupt function

#### Real-time clock (RTC)

The Real-time clock can count Year/Month/Day/Hour/Minute/Second/A day of the week from 00 to 99.

- ■Interrupt function with specifying date and time (Year/Month/Day/Hour/Minute) is available. This function is also available by specifying only Year, Month, Day, Hour or Minute.

- Timer interrupt function after set time or each set time.

- Capable of rewriting the time with continuing the time count.

- Leap year automatic count is available.

#### **Quadrature Position/Revolution Counter (QPRC)**

The Quadrature Position/Revolution Counter (QPRC) is used to measure the position of the position encoder. Moreover, it is possible to use up/down counter.

- The detection edge of the three external event input pins AIN, BIN and ZIN is configurable.

- ■16-bit position counter

- ■16-bit revolution counter

- Two 16-bit compare registers

#### Dual Timer (32-/16-bit Down Counter)

The Dual Timer consists of two programmable 32-/16-bit down counters.

Operation mode is selectable from the followings for each channel.

- ■Free-running

- Periodic ( = Reload)

- ■One-shot

#### Watch Counter

The Watch counter is used for wake up from Low Power Consumption mode.

■Interval timer: up to 64 s (Max) @ Sub Clock: 32.768 kHz

#### **External Interrupt Controller Unit**

- ■Up to 6 external interrupt input pin

- Include one non-maskable interrupt (NMI)

#### Watchdog Timer (2channels)

A watchdog timer can generate interrupts or a reset when a time-out value is reached.

This series consists of two different watchdogs, a "Hardware" watchdog and a "Software" watchdog.

"Hardware" watchdog timer is clocked by low-speed internal CR oscillator. Therefore, "Hardware" watchdog is active in any power saving mode except RTC and STOP and Deep standby RTC and Deep stand-by STOP.

#### CRC (Cyclic Redundancy Check) Accelerator

The CRC accelerator helps a verify data transmission or storage integrity.

CCITT CRC16 and IEEE-802.3 CRC32 are supported.

- CCITT CRC16 Generator Polynomial: 0x1021

- ■IEEE-802.3 CRC32 Generator Polynomial: 0x04C11DB7

#### **Clock and Reset**

#### [Clocks]

Five clock sources (2 external oscillators, 2 internal CR oscillator, and Main PLL) that are dynamically selectable.

- ■Main Clock: 4 MHz to 48 MHz

- ■Sub Clock: 32.768 kHz

- ■High-speed internal CR Clock: 4 MHz

- Low-speed internal CR Clock: 100 kHz

- Main PLL Clock

#### [Resets]

- Reset requests from INITX pin

- Power on reset

- Software reset

- Watchdog timers reset

- Low-voltage detector reset

- Clock supervisor reset

#### **Clock Super Visor (CSV)**

Clocks generated by internal CR oscillators are used to supervise abnormality of the external clocks.

- External OSC clock failure (clock stop) is detected, reset is asserted.

- External OSC frequency anomaly is detected, interrupt or reset is asserted.

#### Low-Voltage Detector (LVD)

This Series include 2-stage monitoring of voltage on the VCC pins. When the voltage falls below the voltage has been set, Low-Voltage Detector generates an interrupt or reset.

- LVD1: error reporting via interrupt

- LVD2: auto-reset operation

#### Low Power Consumption Mode

Six Low Power Consumption modes supported.

- ■SLEEP

- ■TIMER

- ■RTC

- ■STOP

- ■Deep stand-by RTC

- ■Deep stand-by STOP

#### Debug

Serial Wire JTAG Debug Port (SWJ-DP)

#### **Power Supply**

■Wide range voltage: VCC = 2.7 V to 5.5 V

Power supply for USB I/O: USBVCC0 = 3.0 V to 3.6 V (when USB is used) = 2.7 V to 5.5 V (when GPIO is used)

## Contents

|        | Product Lineup                                                                             |    |

|--------|--------------------------------------------------------------------------------------------|----|

|        | Packages                                                                                   |    |

|        | Pin Assignment                                                                             |    |

| 4.     | List of Pin Functions                                                                      | 12 |

|        | I/O Circuit Type                                                                           |    |

| 6.     | Handling Precautions                                                                       | 26 |

| 6.1    | Precautions for Product Design                                                             | 26 |

| 6.2    | Precautions for Package Mounting                                                           | 27 |

| 6.3    | Precautions for Use Environment.                                                           | 28 |

| 7.     | Handling Devices                                                                           | 29 |

| 8.     | Block Diagram                                                                              | 32 |

| 9.     | Memory Size                                                                                | 32 |

|        | Memory Map                                                                                 |    |

|        | Pin Status in Each CPU State                                                               |    |

| 12.    | Electrical Characteristics                                                                 |    |

| 12.1   | Absolute Maximum Ratings                                                                   |    |

| 12.2   | Recommended Operating Conditions                                                           |    |

| 12.3   | DC Characteristics                                                                         |    |

| 12.3.1 |                                                                                            |    |

| -      | Pin Characteristics                                                                        |    |

| 12.4   | AC Characteristics                                                                         |    |

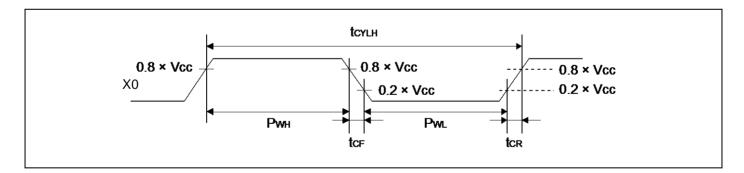

|        | Main Clock Input Characteristics                                                           |    |

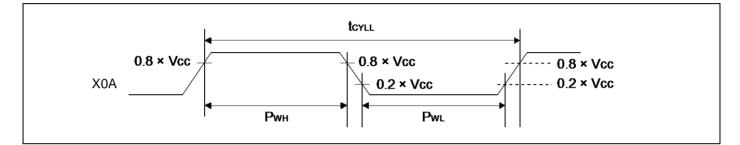

|        | Sub Clock Input Characteristics                                                            |    |

|        | Internal CR Oscillation Characteristics                                                    |    |

|        | Operating Conditions of Main and USB PLL (In the case of using main clock for input of PLL |    |

|        | Operating Conditions of Main PLL (In the case of using high-speed internal CR)             |    |

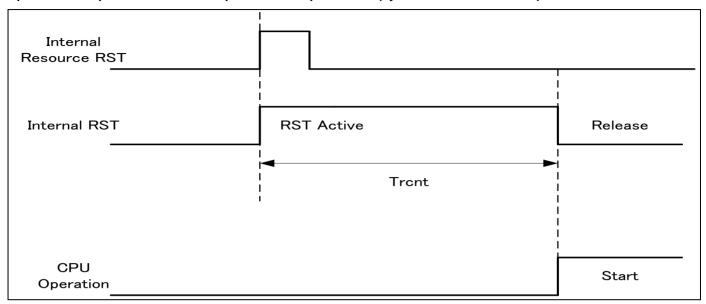

|        | Reset Input Characteristics                                                                |    |

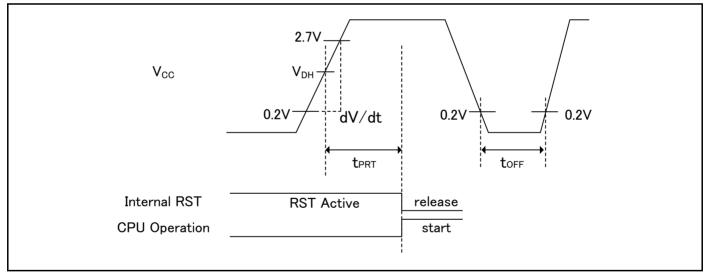

|        | Power-on Reset Timing                                                                      |    |

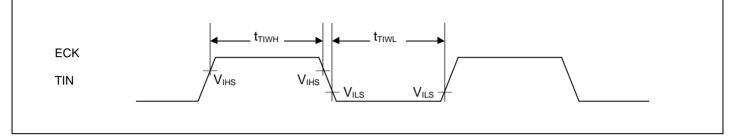

|        | Base Timer Input Timing                                                                    |    |

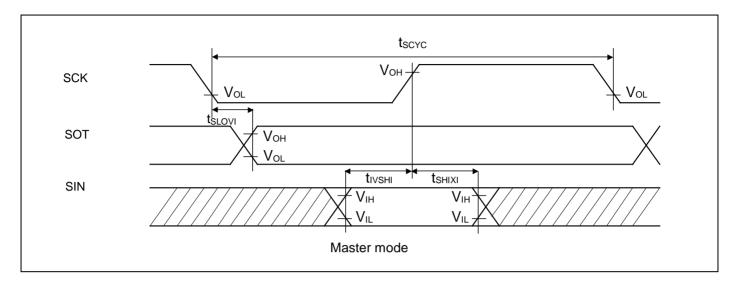

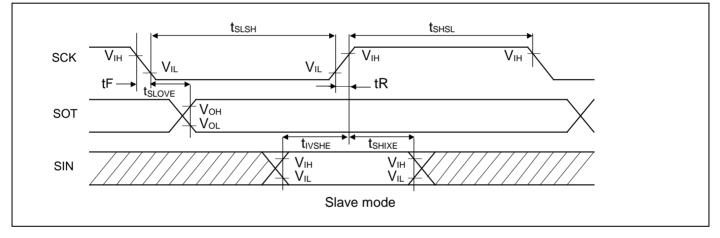

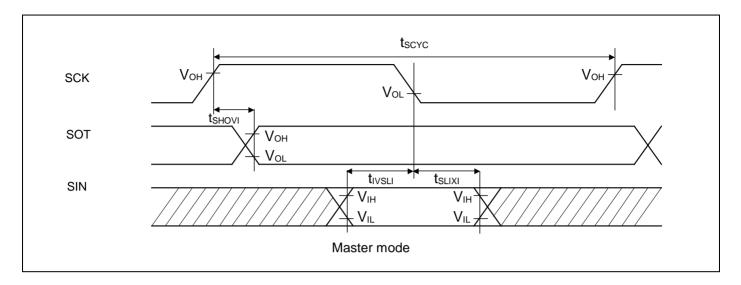

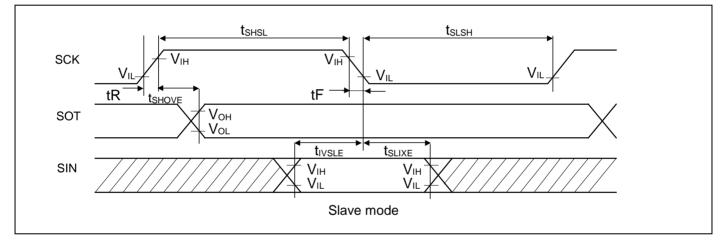

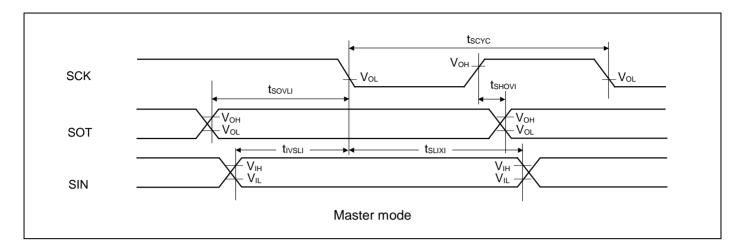

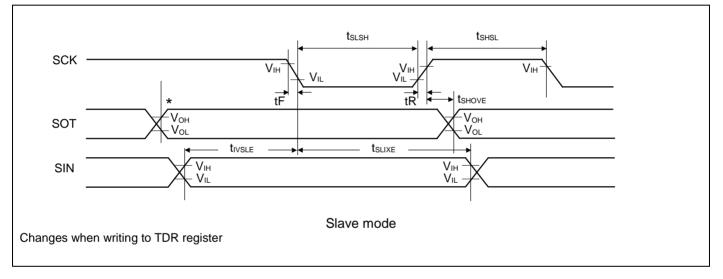

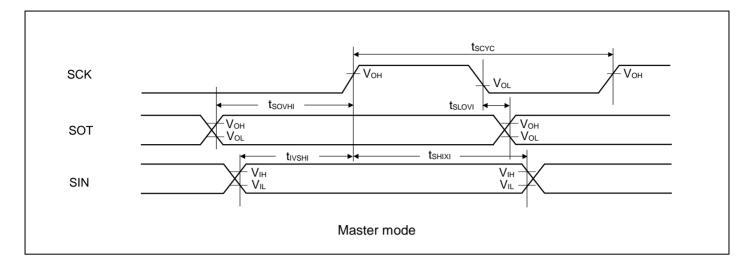

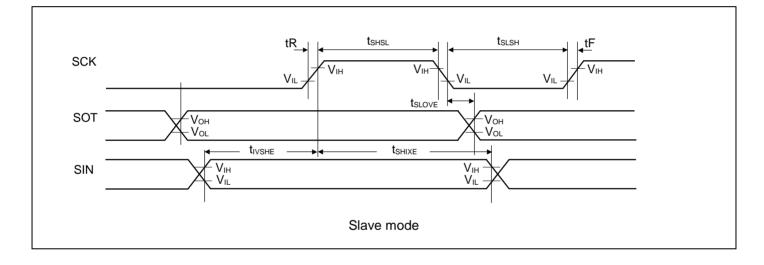

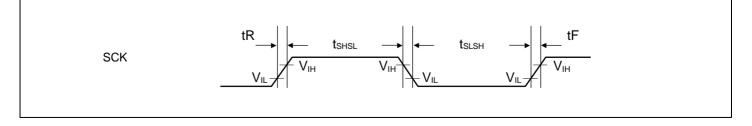

|        | CSIO/UART Timing                                                                           |    |

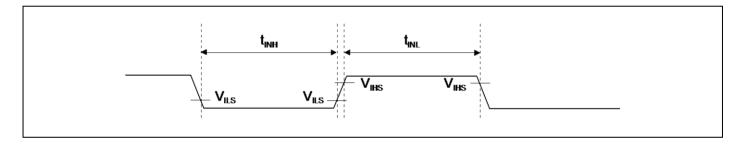

|        | 0 External Input Timing                                                                    |    |

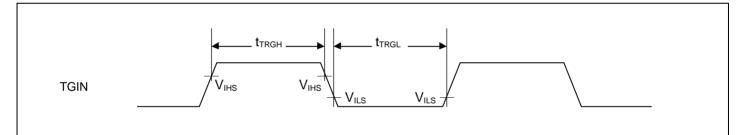

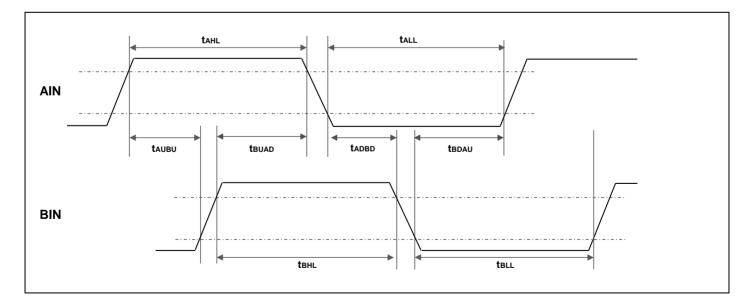

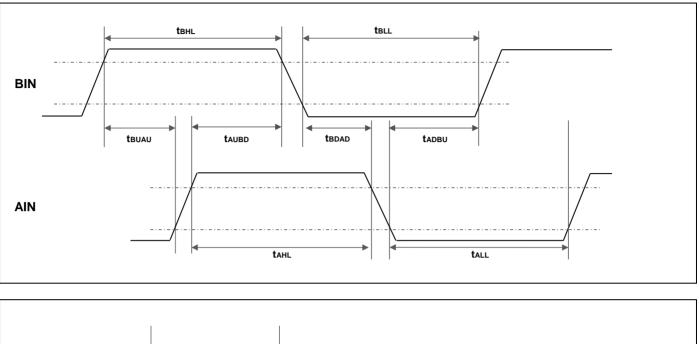

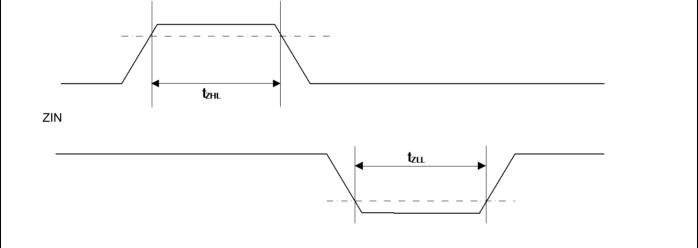

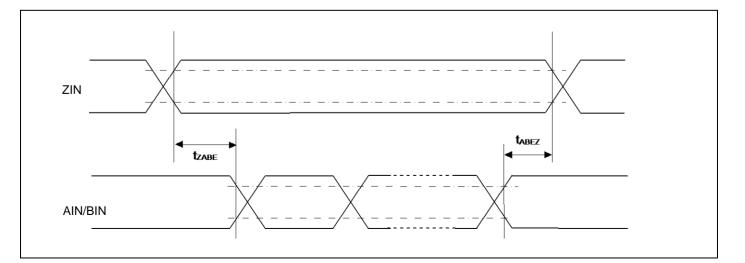

|        | 1 Quadrature Position/Revolution Counter timing                                            |    |

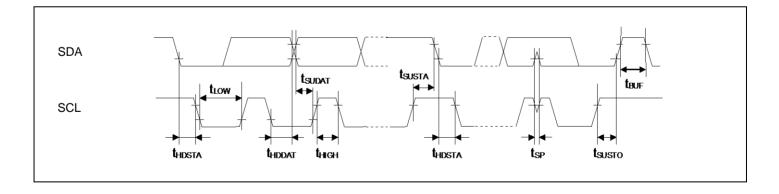

|        | 2 I <sup>2</sup> C Timing                                                                  |    |

|        |                                                                                            |    |

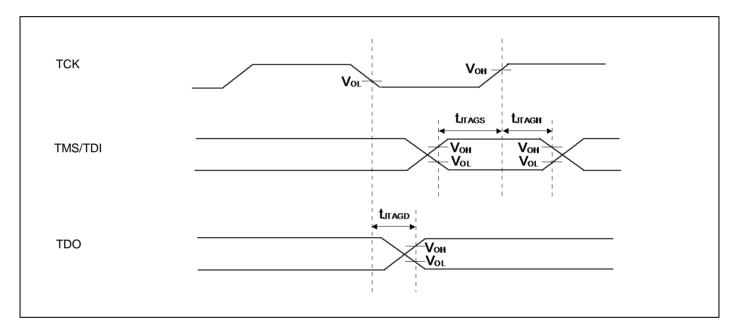

|        | 3 JTAG Timing                                                                              |    |

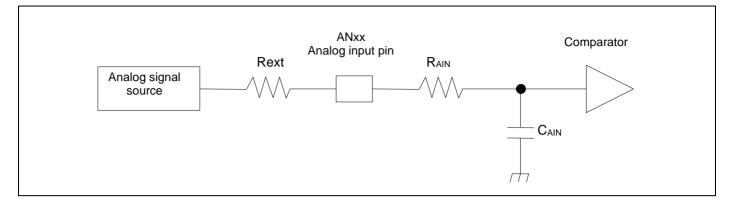

| 12.5   | 12-bit A/D Converter                                                                       |    |

| 12.6   | USB Characteristics                                                                        | -  |

| 12.7   | Low-voltage Detection Characteristics                                                      |    |

|        | Low-voltage Detection Reset                                                                |    |

|        | Interrupt of Low-voltage Detection                                                         |    |

| 12.8   | MainFlash Memory Write/Erase Characteristics                                               |    |

|        | Write / Erase time                                                                         |    |

|        | Erase/write cycles and data hold time                                                      |    |

| 12.9   | WorkFlash Memory Write/Erase Characteristics                                               |    |

|        | Write / Erase time                                                                         |    |

|        | Erase/write cycles and data hold time                                                      |    |

|        | Return Time from Low-Power Consumption Mode                                                |    |

|        | 1 Return Factor: Interrupt/WKUP                                                            |    |

|        | 2 Return Factor: Reset                                                                     |    |

|        | Ordering Information                                                                       |    |

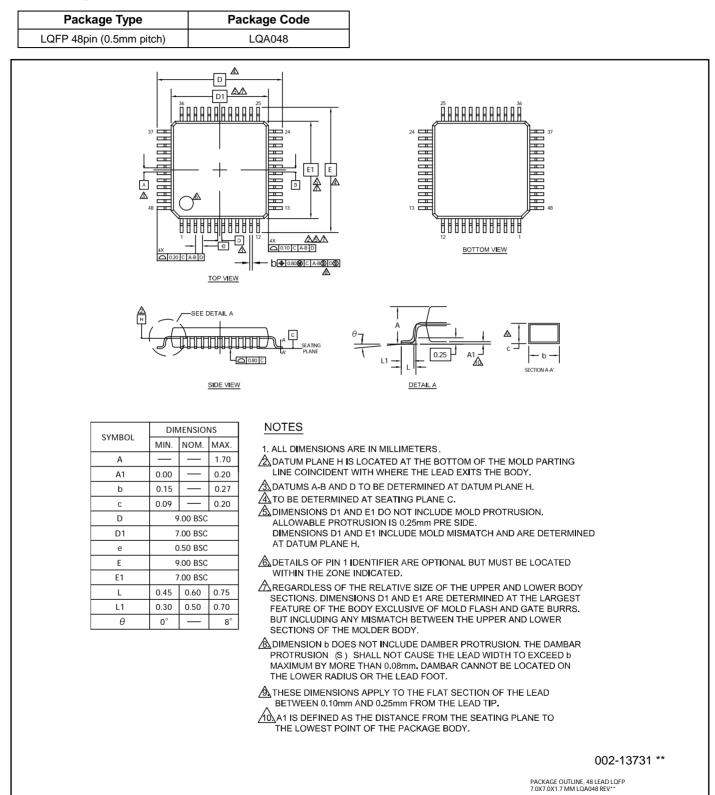

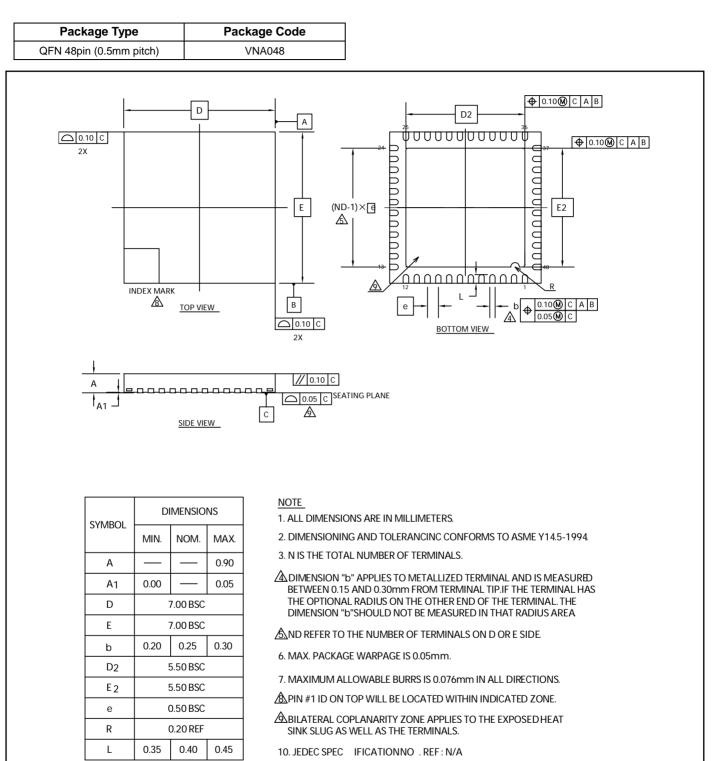

|        | Package Dimensions                                                                         |    |

| 15.    | Major Changes                                                                              | 84 |

| <b>Document History</b> |                     |

|-------------------------|---------------------|

| Sales, Solutions, and   | l Legal Information |

## 1. Product Lineup

#### Memory size

| Product      | t name    | MB9AF311K | MB9AF312K |

|--------------|-----------|-----------|-----------|

| On-chip      | MainFlash | 64 Kbyte  | 128 Kbyte |

| Flash memory | WorkFlash | 32 Kbyte  | 32 Kbyte  |

|              | SRAM0     | 8 Kbyte   | 8 Kbyte   |

| On-chip SRAM | SRAM1     | 8 Kbyte   | 8 Kbyte   |

|              | Total     | 16 Kbyte  | 16 Kbyte  |

#### Function

| Product name        |                                         | ie    | MB9AF311K<br>MB9AF312K                                                                                                           |

|---------------------|-----------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| Pin count           |                                         |       | 48/52                                                                                                                            |

| CPU                 |                                         |       | Cortex-M3                                                                                                                        |

| CPU                 | Freq.                                   |       | 40 MHz                                                                                                                           |

| Power s             | ower supply voltage range               |       | 2.7 V to 5.5 V<br>(USBVCC: 3.0 V to 3.6 V)                                                                                       |

| USB2.0              | (Device/Host)                           |       | 1 ch. (Max)                                                                                                                      |

| DMAC                | (                                       |       | 4 ch. (Max)                                                                                                                      |

|                     | nction Serial Interfac<br>CSIO/LIN/I²C) | e     | 4 ch. (Max)<br>with 16-steps × 9-bits FIFO : ch.0, ch.1<br>without FIFO : ch.3, ch.5 (In ch.5, only UART and LIN are available.) |

| Base Tin<br>(PWC/ R | ner<br>Reload timer/PWM/P               | PG)   | 8 ch. (Max)                                                                                                                      |

|                     | A/D activation compare                  | 3 ch. |                                                                                                                                  |

|                     | Input capture                           | 4 ch. |                                                                                                                                  |

| MF-                 | Free-run timer                          | 3 ch. |                                                                                                                                  |

| Timer               | Output<br>compare                       | 6 ch. | 1 unit (Max)                                                                                                                     |

|                     | Waveform generator                      | 3 ch. |                                                                                                                                  |

|                     | PPG                                     | 3 ch. |                                                                                                                                  |

| QPRC                |                                         |       | 1 ch. (Max)                                                                                                                      |

| Dual Tim            | -                                       |       | 1 unit                                                                                                                           |

| Real-tim            | e clock                                 |       | 1 unit                                                                                                                           |

| Watch C             | counter                                 |       | 1 unit                                                                                                                           |

| CRC Acc             | celerator                               |       | Yes                                                                                                                              |

| Watchdo             |                                         |       | 1 ch. (SW) + 1 ch. (HW)                                                                                                          |

|                     | Interrupts                              |       | 6 pins (Max) + NMI × 1                                                                                                           |

| General             | Purpose I/O ports                       |       | 36 pins (Max)                                                                                                                    |

|                     | D converter                             |       | 8 ch. (2 units)                                                                                                                  |

|                     | ock Super Visor)                        |       | Yes                                                                                                                              |

| LVD (Lov            | w-Voltage Detector)                     |       | 2 ch.                                                                                                                            |

| Built-in C          | High-spee                               | d     | 4 MHz                                                                                                                            |

|                     | Low-speed                               | t l   | 100 kHz                                                                                                                          |

| Debug F             | unction                                 |       | SWJ-DP                                                                                                                           |

#### Note:

All signals of the peripheral function in each product cannot be allocated by limiting the pins of package. It is necessary to use the port relocate function of the General I/O port according to your function use. See "12. Electrical Characteristics 12.4. AC Characteristics" for accuracy of built-in CR.

## 2. Packages

| Package | Product name           | MB9AF311K<br>MB9AF312K |

|---------|------------------------|------------------------|

| LQFP:   | LQA048 (0.5 mm pitch)  | 0                      |

| QFN:    | VNA048 (0.5 mm pitch)  | 0                      |

| LQFP:   | LQC052 (0.65 mm pitch) | 0                      |

## O: Supported

Note:

- See "14.Package Dimensions" for detailed information on each package.

## 3. Pin Assignment

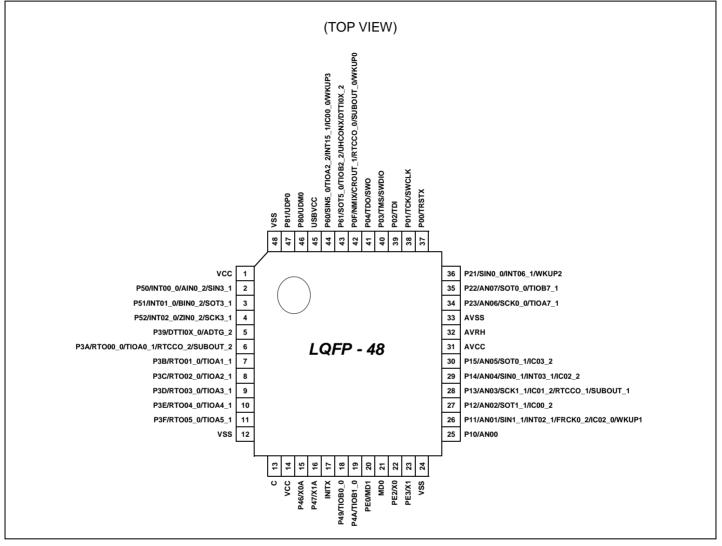

LQA048

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

## MB9A310K Series

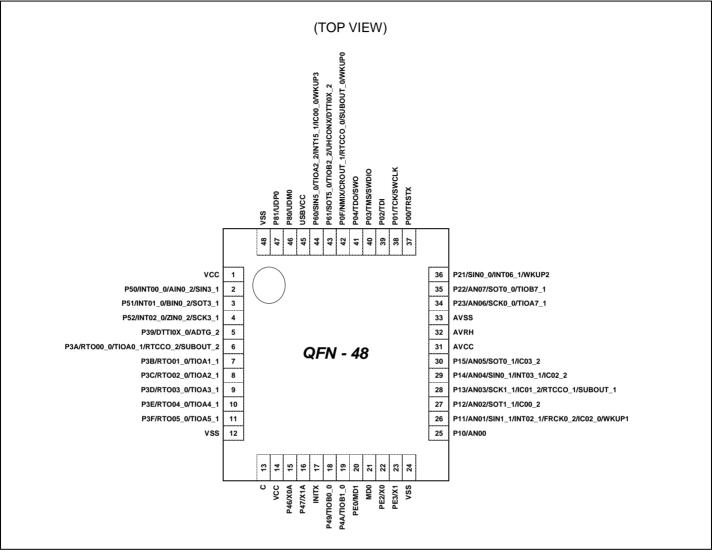

#### **VNA048**

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

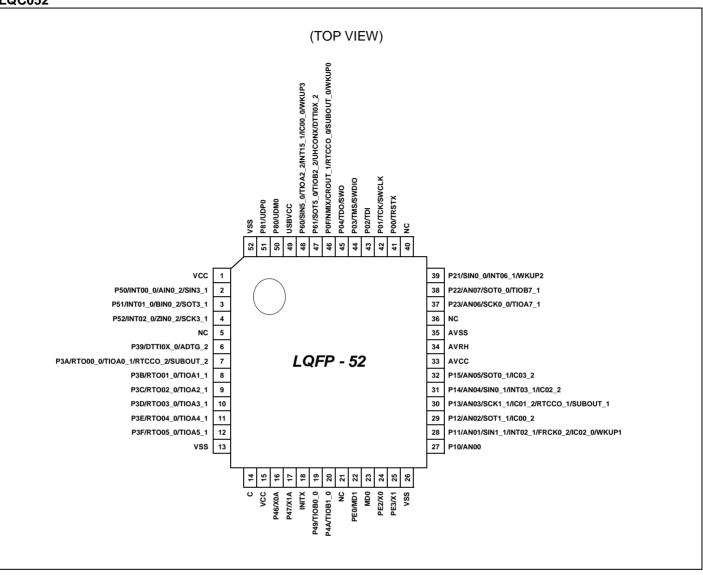

## **MB9A310K Series**

#### Note:

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

## 4. List of Pin Functions

#### List of pin numbers

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

| Pin No            |                      |             | I/O circuit | Pin state |

|-------------------|----------------------|-------------|-------------|-----------|

| LQFP-48<br>QFN-48 | LQFP-52              | Pin Name    | type        | type      |

| 1                 | 1                    | VCC         |             | -         |

|                   |                      | P50         |             |           |

| 2                 | 2                    | INT00_0     | I *1        | н         |

| 2                 | 2                    | AIN0_2      |             | п         |

|                   |                      | SIN3_1      |             |           |

|                   |                      | P51         |             |           |

| 2                 | <u> </u>             | INT01_0     | I*1         |           |

| 3                 | 3 3 BIN0_2<br>SOT3_1 |             | Н           |           |

|                   |                      |             |             |           |

|                   |                      | P52         |             |           |

|                   |                      | INT02_0     | . *1        |           |

| 4                 | 4                    | ZIN0_2      | I *1        | Н         |

|                   |                      | SCK3_1      |             |           |

| -                 | 5                    | NC          |             | -         |

|                   |                      | P39         |             |           |

| 5                 | 6                    | DTTIOX_0    | E           | I         |

|                   |                      | ADTG_2      |             |           |

|                   |                      | <br>P3A     |             |           |

|                   |                      | RTO00_0     |             |           |

| 6                 | 7                    | <br>TIOA0_1 | G           | I         |

|                   |                      | <br>RTCCO_2 |             |           |

|                   |                      | SUBOUT_2    |             |           |

|                   |                      | P3B         |             |           |

| 7                 | 8                    | RTO01_0     | G           | I         |

|                   |                      | TIOA1_1     |             |           |

|                   |                      | P3C         |             |           |

| 8                 | 9                    | RTO02_0     | G           | I         |

| C C               |                      | TIOA2_1     |             |           |

|                   |                      | P3D         |             |           |

| 9                 | 10                   | RTO03_0     | G           | I         |

| Ŭ                 |                      | TIOA3_1     | Ŭ           |           |

|                   |                      | P3E         |             |           |

| 10                | 11                   | RTO04_0     | G           | I         |

| 10                |                      | TIOA4_1     | Ŭ           |           |

|                   |                      | P3F         |             |           |

| 11                | 12                   | RTO05_0     | G           | I         |

| 11                | 12                   |             |             | I         |

|                   |                      | TIOA5_1     |             |           |

| Pin No            |         | Pin No   |                     | Pin state |

|-------------------|---------|----------|---------------------|-----------|

| LQFP-48<br>QFN-48 | LQFP-52 | Pin Name | I/O circuit<br>type | type      |

| 12                | 13      | VSS      |                     |           |

| 13                | 14      | С        |                     |           |

| 14                | 15      | VCC      |                     |           |

| 15                | 16      | P46      | D                   | М         |

| 10                | 10      | ХОА      | D D                 | IVI       |

| 16                | 17      | P47      | D                   | Ν         |

| 10                | 17      | X1A      | D                   | IN        |

| 17                | 18      | INITX    | В                   | С         |

| 18                | 19      | P49      | — Е                 | I         |

| 10                | 19      | TIOB0_0  |                     | I         |

| 40                | 20      | P4A      | E                   |           |

| 19                | 20      | TIOB1_0  | E                   | I         |

| -                 | 21      | NC       |                     |           |

| 22                |         | PE0      | 2                   | 5         |

| 20                | 22      | MD1      | C                   | Р         |

| 21                | 23      | MD0      | J                   | D         |

|                   |         | PE2      |                     |           |

| 22                | 24      | X0       | Α                   | A         |

|                   |         | PE3      |                     | В         |

| 23                | 25      | X1       | Α                   |           |

| 24                | 26      | VSS      |                     |           |

|                   |         | P10      |                     | Τ         |

| 25                | 27      | AN00     | F                   | К         |

|                   |         | P11      |                     |           |

|                   |         | AN01     |                     |           |

|                   |         | SIN1_1   |                     |           |

| 26                | 28      | INT02_1  | F                   | F         |

| 20                |         | FRCK0_2  |                     | ·         |

|                   |         | IC02_0   |                     |           |

|                   |         | WKUP1    |                     |           |

|                   |         | P12      |                     |           |

|                   |         | AN02     |                     |           |

| 27                | 29      | SOT1_1   | — F                 | К         |

|                   |         | IC00_2   |                     |           |

|                   |         | P13      |                     |           |

|                   |         | AN03     |                     |           |

|                   |         |          |                     |           |

| 28                | 30      | SCK1_1   | — F                 | к         |

|                   |         | IC01_2   |                     |           |

|                   |         | RTCCO_1  |                     |           |

|                   |         | SUBOUT_1 |                     |           |

| Pin               | Pin No Dia Nome |          | I/O circuit | Pin state |

|-------------------|-----------------|----------|-------------|-----------|

| LQFP-48<br>QFN-48 | LQFP-52         | Pin Name | type        | type      |

|                   |                 | P14      |             |           |

|                   |                 | AN04     |             |           |

| 29                | 31              | SIN0_1   | F           | L         |

| 20                | <u> </u>        | INT03_1  |             | -         |

|                   |                 |          |             |           |

|                   |                 | IC02_2   |             |           |

|                   |                 | P15      |             |           |

| 30                | 32              | AN05     | — F         | к         |

|                   |                 | SOT0_1   |             |           |

|                   |                 | IC03_2   |             |           |

| 31                | 33              | AVCC     |             | -         |

| 32                | 34              | AVRH     |             |           |

| 33                | 35              | AVSS     |             | •         |

| -                 | 36              | NC       |             |           |

|                   |                 | P23      |             |           |

| 34                | 37              | AN06     | F           | к         |

|                   |                 | SCK0_0   |             |           |

|                   |                 | TIOA7_1  |             |           |

|                   |                 | P22      |             |           |

| 35                | 38              | AN07     | F           | к         |

|                   |                 | SOT0_0   |             |           |

|                   |                 | TIOB7_1  |             |           |

|                   |                 | P21      |             | G         |

| 36                | 39              | SIN0_0   | — Е         |           |

|                   |                 | INT06_1  |             |           |

|                   |                 | WKUP2    |             |           |

| -                 | 40              | NC       |             |           |

| 37                | 41              | P00      | — E         | Е         |

|                   |                 | TRSTX    |             |           |

|                   |                 | P01      |             | _         |

| 38                | 42              | тск      | E           | E         |

|                   |                 | SWCLK    |             |           |

| 39                | 43              | P02      | — Е         | E         |

| 00                | 10              | TDI      | _           | -         |

|                   |                 | P03      |             |           |

| 40                | 44              | TMS      | E           | E         |

|                   |                 | SWDIO    |             |           |

|                   |                 | P04      |             |           |

| 41                | 45              | TDO      | E           | E         |

|                   |                 | SWO      |             |           |

|                   |                 | P0F      |             |           |

|                   |                 | NMIX     |             |           |

| 40                |                 | CROUT_1  | -           |           |

| 42                | 46              | RTCCO_0  | E           | J         |

|                   |                 | SUBOUT_0 |             |           |

|                   |                 | WKUP0    |             |           |

| F                 | Pin No  |          |                     |                   |

|-------------------|---------|----------|---------------------|-------------------|

| LQFP-48<br>QFN-48 | LQFP-52 | Pin Name | I/O circuit<br>type | Pin state<br>Type |

|                   |         | P61      |                     |                   |

|                   |         | SOT5_0   |                     |                   |

| 43                | 47      | TIOB2_2  | E                   | I                 |

|                   |         | UHCONX   |                     |                   |

|                   |         | DTTI0X_2 |                     |                   |

|                   |         | P60      |                     |                   |

|                   |         | SIN5_0   |                     | G                 |

| 44                | 48      | TIOA2_2  | *1                  |                   |

| 44                | 40      | INT15_1  |                     |                   |

|                   |         | IC00_0   |                     |                   |

|                   |         | WKUP3    |                     |                   |

| 45                | 49      | USBVCC   |                     | _                 |

| 46                | 50      | P80      |                     | 0                 |

| 46                | 50      | UDM0     | — Н                 |                   |

| 47                | 54      | P81      |                     | 0                 |

| 47                | 51      | UDP0     | — Н                 | 0                 |

| 48                | 52      | VSS      |                     | -                 |

\*1:5V tolerant I/O

#### List of pin functions

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

|                 |          |                                                   | Pin               | No      |

|-----------------|----------|---------------------------------------------------|-------------------|---------|

| Module          | Pin name | Function                                          | LQFP-48<br>QFN-48 | LQFP-52 |

| ADC             | ADTG_2   | A/D converter external trigger input pin          | 5                 | 6       |

|                 | AN00     |                                                   | 25                | 27      |

|                 | AN01     |                                                   | 26                | 28      |

|                 | AN02     |                                                   | 27                | 29      |

|                 | AN03     | A/D converter analog input pin.                   | 28                | 30      |

|                 | AN04     | ANxx describes ADC ch.xx.                         | 29                | 31      |

|                 | AN05     |                                                   | 30                | 32      |

|                 | AN06     |                                                   | 34                | 37      |

|                 | AN07     |                                                   | 35                | 38      |

| Base Timer      | TIOA0_1  | Base timer ch.0 TIOA pin                          | 6                 | 7       |

| 0               | TIOB0_0  | Base timer ch.0 TIOB pin                          | 18                | 19      |

| Base Timer      | TIOA1_1  | Base timer ch.1 TIOA pin                          | 7                 | 8       |

| 1               | TIOB1_0  | Base timer ch.1 TIOB pin                          | 19                | 20      |

| Base Timer      | TIOA2_1  |                                                   | 8                 | 9       |

| 2               | TIOA2_2  | Base timer ch.2 TIOA pin                          | 44                | 48      |

|                 | TIOB2_2  | Base timer ch.2 TIOB pin                          | 43                | 47      |

| Base Timer<br>3 | TIOA3_1  | Base timer ch.3 TIOA pin                          | 9                 | 10      |

| Base Timer<br>4 | TIOA4_1  | Base timer ch.4 TIOA pin                          | 10                | 11      |

| Base Timer<br>5 | TIOA5_1  | Base timer ch.5 TIOA pin                          | 11                | 12      |

| Base Timer      | TIOA7_1  | Base timer ch.7 TIOA pin                          | 34                | 37      |

| 7               | TIOB7_1  | Base timer ch.7 TIOB pin                          | 35                | 38      |

| Debugger        | SWCLK    | Serial wire debug interface clock input pin       | 38                | 42      |

|                 | SWDIO    | Serial wire debug interface data input/output pin | 40                | 44      |

|                 | SWO      | Serial wire viewer output pin                     | 41                | 45      |

|                 | TCK      | JTAG test clock input pin                         | 38                | 42      |

|                 | TDI      | JTAG test data input pin                          | 39                | 43      |

|                 | TDO      | JTAG debug data output pin                        | 41                | 45      |

|                 | TMS      | JTAG test mode state input/output pin             | 40                | 44      |

|                 | TRSTX    | JTAG test reset Input pin                         | 37                | 41      |

| External        | INT00_0  | External interrupt request 00 input pin           | 2                 | 2       |

| Interrupt       | INT01_0  | External interrupt request 01 input pin           | 3                 | 3       |

|                 | INT02_0  |                                                   | 4                 | 4       |

|                 | INT02_1  | External interrupt request 02 input pin           | 26                | 28      |

|                 | INT03_1  | External interrupt request 03 input pin           | 29                | 31      |

|                 | INT06_1  | External interrupt request 06 input pin           | 36                | 39      |

|                 | INT15_1  | External interrupt request 15 input pin           | 44                | 48      |

| F               | NMIX     | Non-Maskable Interrupt input pin                  | 42                | 46      |

|        |          |                            | Pin               | No      |

|--------|----------|----------------------------|-------------------|---------|

| Module | Pin name | Function                   | LQFP-48<br>QFN-48 | LQFP-52 |

| GPIO   | P00      |                            | 37                | 41      |

|        | P01      |                            | 38                | 42      |

|        | P02      | General-purpose I/O port 0 | 39                | 43      |

|        | P03      | General-purpose I/O poir 0 | 40                | 44      |

|        | P04      |                            | 41                | 45      |

|        | P0F      |                            | 42                | 46      |

|        | P10      |                            | 25                | 27      |

|        | P11      |                            | 26                | 28      |

|        | P12      | General-purpose I/O port 1 | 27                | 29      |

|        | P13      | General-purpose I/O port 1 | 28                | 30      |

|        | P14      |                            | 29                | 31      |

|        | P15      |                            | 30                | 32      |

|        | P21      |                            | 36                | 39      |

|        | P22      | General-purpose I/O port 2 | 35                | 38      |

|        | P23      |                            | 34                | 37      |

|        | P39      | General-purpose I/O port 3 | 5                 | 6       |

|        | P3A      |                            | 6                 | 7       |

|        | P3B      |                            | 7                 | 8       |

|        | P3C      |                            | 8                 | 9       |

|        | P3D      |                            | 9                 | 10      |

|        | P3E      | -                          | 10                | 11      |

|        | P3F      |                            | 11                | 12      |

|        | P46      |                            | 15                | 16      |

|        | P47      | General-purpose I/O port 4 | 16                | 17      |

|        | P49      | General-purpose I/O port 4 | 18                | 19      |

|        | P4A      |                            | 19                | 20      |

|        | P50      |                            | 2                 | 2       |

|        | P51      | General-purpose I/O port 5 | 3                 | 3       |

|        | P52      |                            | 4                 | 4       |

|        | P60      |                            | 44                | 48      |

|        | P61      | General-purpose I/O port 6 | 43                | 47      |

| F      | P80      |                            | 46                | 50      |

| F      | P81      | General-purpose I/O port 8 | 47                | 51      |

| F      | PE0      |                            | 20                | 22      |

| F      | PE2      | General-purpose I/O port E | 22                | 24      |

| F      | PE3      |                            | 23                | 25      |

|                 |                    |                                                                                                                                                                                                                           |                   | No.     |

|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|

| Module          | Pin name           | Function                                                                                                                                                                                                                  | LQFP-48<br>QFN-48 | LQFP-52 |

| Multi- function | SIN0_0             | Multifunction entitlicterface ship involving                                                                                                                                                                              | 36                | 39      |

| Serial<br>0     | SIN0_1             | Multi-function serial interface ch.0 input pin                                                                                                                                                                            | 29                | 31      |

|                 | SOT0_0<br>(SDA0_0) | Multi-function serial interface ch.0 output pin.<br>This pin operates as SOT0 when it is used in a<br>UART/CSIO/LIN (operation modes                                                                                      | 35                | 38      |

|                 | SOT0_1<br>(SDA0_1) | 0 to 3) and as SDA0 when it is used in an I <sup>2</sup> C (operation mode 4).                                                                                                                                            | 30                | 32      |

|                 | SCK0_0<br>(SCL0_0) | Multi-function serial interface ch.0 clock I/O pin.<br>This pin operates as SCK0 when it is used in a CSIO<br>(operation modes 2) and as SCL0 when it is used in an<br>I <sup>2</sup> C (operation mode 4).               | 34                | 37      |

| Multi- function | SIN1_1             | Multi-function serial interface ch.1 input pin                                                                                                                                                                            | 26                | 28      |

| Serial<br>1     | SOT1_1<br>(SDA1_1) | Multi-function serial interface ch.1 output pin.<br>This pin operates as SOT1 when it is used in a<br>UART/CSIO/LIN (operation modes<br>0 to 3) and as SDA1 when it is used in an I <sup>2</sup> C (operation<br>mode 4). | 27                | 29      |

|                 | SCK1_1<br>(SCL1_1) | Multi-function serial interface ch.1 clock I/O pin.<br>This pin operates as SCK1 when it is used in a CSIO<br>(operation modes 2) and as SCL1 when it is used in an<br>I <sup>2</sup> C (operation mode 4).               | 28                | 30      |

| Multi- function | SIN3_1             | Multi-function serial interface ch.3 input pin                                                                                                                                                                            | 2                 | 2       |

| Serial<br>3     | SOT3_1<br>(SDA3_1) | Multi-function serial interface ch.3 output pin.<br>This pin operates as SOT3 when it is used in a<br>UART/CSIO/LIN (operation modes<br>0 to 3) and as SDA3 when it is used in an I <sup>2</sup> C (operation<br>mode 4). | 3                 | 3       |

|                 | SCK3_1<br>(SCL3_1) | Multi-function serial interface ch.3 clock I/O pin.<br>This pin operates as SCK3 when it is used in a CSIO<br>(operation modes 2) and as SCL3 when it is used in an<br>I <sup>2</sup> C (operation mode 4).               | 4                 | 4       |

| Multi- function | SIN5_0             | Multi-function serial interface ch.5 input pin                                                                                                                                                                            | 44                | 48      |

| Serial<br>5     | SOT5_0             | Multi-function serial interface ch.5 output pin.<br>This pin operates as SOT5 when it is used in a<br>UART/LIN (operation modes 0, 1, 3).                                                                                 | 43                | 47      |

|                         |                      |                                                                                                                                     | Pin No            |          |  |

|-------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|--|

| Module                  | Pin name             | Function                                                                                                                            | LQFP-48<br>QFN-48 | LQFP-52  |  |

| Multi- function         | DTTI0X_0             | Input signal controlling wave form generator outputs                                                                                | 5                 | 6        |  |

| Timer<br>0              | DTTI0X_2             | RTO00 to RTO05 of multi-function timer 0.                                                                                           | 43                | 47       |  |

|                         | FRCK0_2              | 16-bit free-run timer ch.0 external clock input pin                                                                                 | 26                | 28       |  |

|                         | IC00_0               |                                                                                                                                     | 44                | 48       |  |

|                         | IC00_2               | 40 bit insut contum of 0 insut sin of sould function times                                                                          | 27                | 29       |  |

|                         | IC01_2               | 16-bit input capture ch.0 input pin of multi-function timer<br>0.                                                                   | 28                | 30       |  |

|                         | IC02_0               | ICxx describes channel number.                                                                                                      | 26                | 28       |  |

|                         | IC02_2               |                                                                                                                                     | 29                | 31       |  |

|                         | IC03_2               |                                                                                                                                     | 30                | 32       |  |

|                         | RTO00_0<br>(PPG00_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG00 when it is used in PPG0<br>output modes. | 6                 | 7        |  |

|                         | RTO01_0<br>(PPG00_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG00 when it is used in PPG0<br>output modes. | 7                 | 8        |  |

|                         | RTO02_0<br>(PPG02_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG02 when it is used in PPG0<br>output modes. | 8                 | 9        |  |

|                         | RTO03_0<br>(PPG02_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG02 when it is used in PPG0<br>output modes. | 9                 | 10       |  |

|                         | RTO04_0<br>(PPG04_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG04 when it is used in PPG0<br>output modes. | 10                | 11       |  |

|                         | RTO05_0<br>(PPG04_0) | Wave form generator output pin of multi-function timer<br>0.<br>This pin operates as PPG04 when it is used in PPG0<br>output modes. | 11                | 12       |  |

| Quadrature<br>Position/ | AIN0_2               | QPRC ch.0 AIN input pin                                                                                                             | 2                 | 2        |  |

| Revolution<br>Counter   | BIN0_2               | QPRC ch.0 BIN input pin                                                                                                             | 3                 | 3        |  |

| 0                       | ZIN0_2               | QPRC ch.0 ZIN input pin                                                                                                             | 4                 | 4        |  |

| Real-time clock         | RTCCO_0              |                                                                                                                                     | 42                | 46       |  |

|                         | RTCCO_1              | 0.5 seconds pulse output pin of Real-time clock                                                                                     | 28                | 30       |  |

|                         | RTCCO_2              |                                                                                                                                     | 6                 | 7        |  |

|                         | SUBOUT_0             |                                                                                                                                     | 42                | 46       |  |

|                         | SUBOUT_1             | Sub clock output pin                                                                                                                | 28                | 30       |  |

|                         | SUBOUT_2             |                                                                                                                                     | 6                 | 7        |  |

| Low Power               |                      | Deep stand-by mode return signal input pin 0                                                                                        | 42                | 46       |  |

| Consumption             | WKUP1                | Deep stand-by mode return signal input pin 0                                                                                        | 26                | 28       |  |

| Mode                    | WKUP2                | Deep stand-by mode return signal input pin 1                                                                                        | 36                | 39       |  |

|                         | WKUP2                | Deep stand-by mode return signal input pin 2<br>Deep stand-by mode return signal input pin 3                                        | 44                | 39<br>48 |  |

|                         |                      |                                                                                                                                     |                   | -        |  |

| USB                     | UDM0                 | USB ch.0 device/host D – pin                                                                                                        | 46                | 50       |  |

|                         | UDP0                 | USB ch.0 device/host D + pin                                                                                                        | 47                | 51       |  |

|                         | UHCONX               | USB external pull-up control pin                                                                                                    | 43                | 47       |  |

|                 |          |                                                                                                                                            | Pin No            |         |  |

|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|--|

| Module          | Pin name | Function                                                                                                                                   | LQFP-48<br>QFN-48 | LQFP-52 |  |

| Reset           | INITX    | External Reset Input pin.<br>A reset is valid when INITX = "L".                                                                            | 17                | 18      |  |

| Mode            | MD0      | Mode 0 pin.<br>During normal operation, MD0 = "L" must be input.<br>During serial programming to Flash memory, MD0 = "H"<br>must be input. | 21                | 23      |  |

|                 | MD1      | Mode 1 pin.<br>During serial programming to Flash memory, MD1 = "L"<br>must be input.                                                      | 20                | 22      |  |

| Power           | VCC      | Power supply Pin                                                                                                                           | 1                 | 1       |  |

|                 | VCC      | Power supply Pin                                                                                                                           | 14                | 15      |  |

|                 | USBVCC   | 3.3V Power supply port for USB I/O                                                                                                         | 45                | 49      |  |

| GND             | VSS      | GND Pin                                                                                                                                    | 12                | 13      |  |

|                 | VSS      | GND Pin                                                                                                                                    | 24                | 26      |  |

|                 | VSS      | GND Pin                                                                                                                                    | 48                | 52      |  |

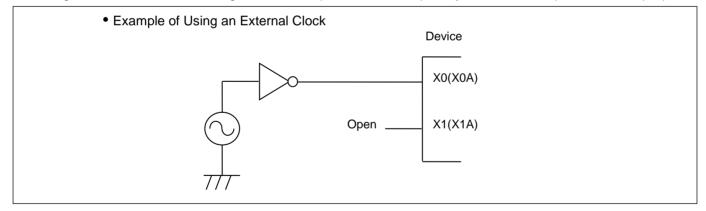

| Clock           | X0       | Main clock (oscillation) input pin                                                                                                         | 22                | 24      |  |

|                 | X0A      | Sub clock (oscillation) input pin                                                                                                          | 15                | 16      |  |

|                 | X1       | Main clock (oscillation) I/O pin                                                                                                           | 23                | 25      |  |

|                 | X1A      | Sub clock (oscillation) I/O pin                                                                                                            | 16                | 17      |  |

| Γ               | CROUT_1  | Built-in high-speed CR-osc clock output port                                                                                               | 42                | 46      |  |

| Analog<br>Power | AVCC     | A/D converter analog power pin                                                                                                             | 31                | 33      |  |

|                 | AVRH     | A/D converter analog reference voltage input pin                                                                                           | 32                | 34      |  |

| Analog<br>GND   | AVSS     | A/D converter GND pin                                                                                                                      | 33                | 35      |  |

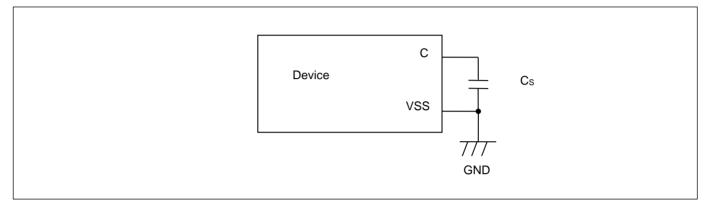

| C pin           | С        | Power stabilization capacity pin                                                                                                           | 13                | 14      |  |

| NC pin          | NC       | NC pin.<br>NC pin should be kept open.                                                                                                     | -                 | 5       |  |

|                 | NC       | NC pin.<br>NC pin should be kept open.                                                                                                     | -                 | 21      |  |

|                 | NC       | NC pin.<br>NC pin should be kept open.                                                                                                     | -                 | 36      |  |

|                 | NC       | NC pin.<br>NC pin should be kept open.                                                                                                     | -                 | 40      |  |

#### Note:

While this device contains a Test Access Port (TAP) based on the IEEE 1149.1-2001 JTAG standard, it is not fully compliant to all requirements of that standard. This device may contain a 32-bit device ID that is the same as the 32-bit device ID in other devices with different functionality. The TAP pins may also be configurable for purposes other than access to the TAP controller.

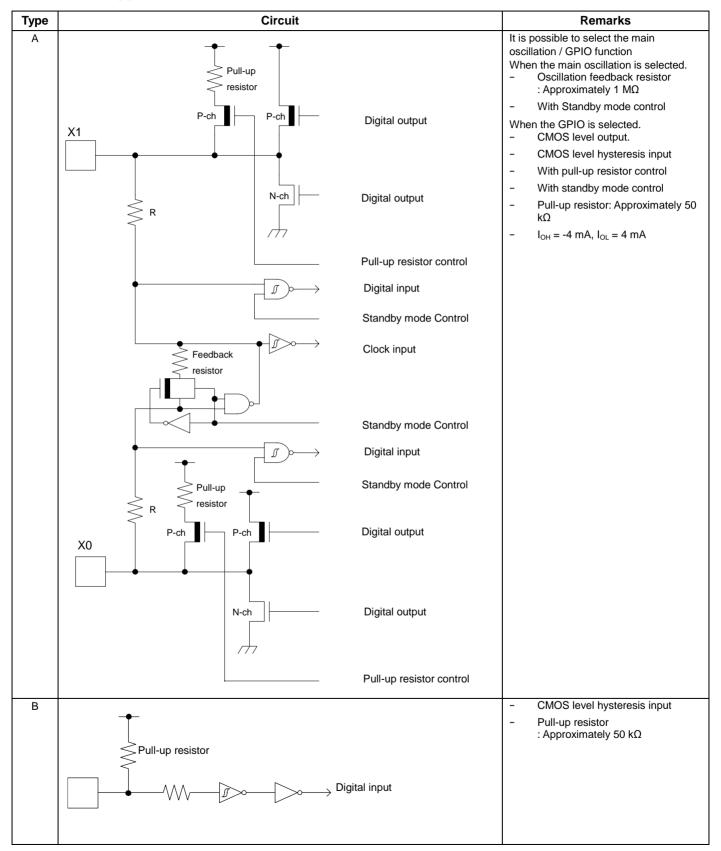

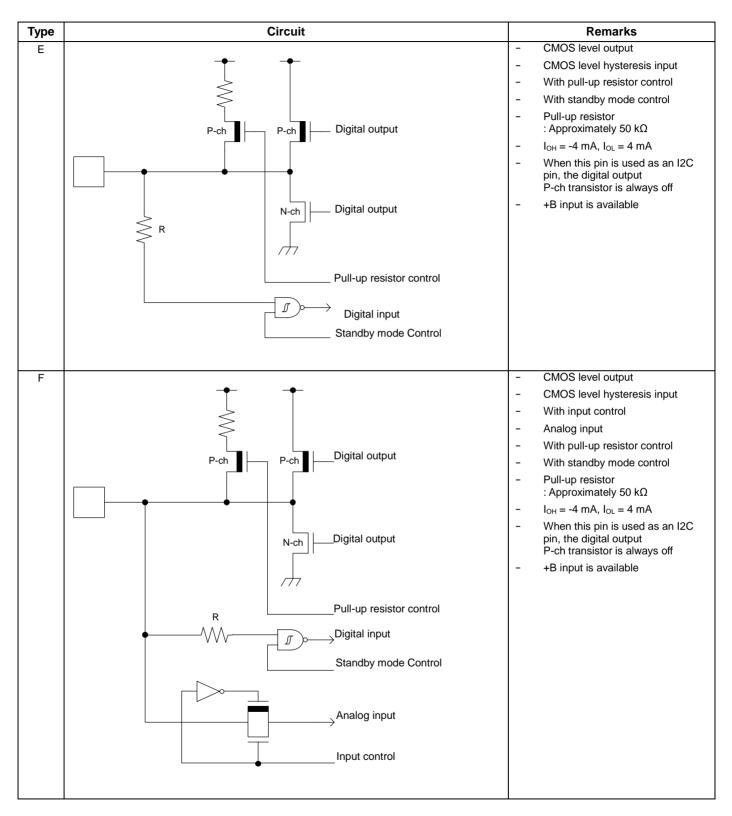

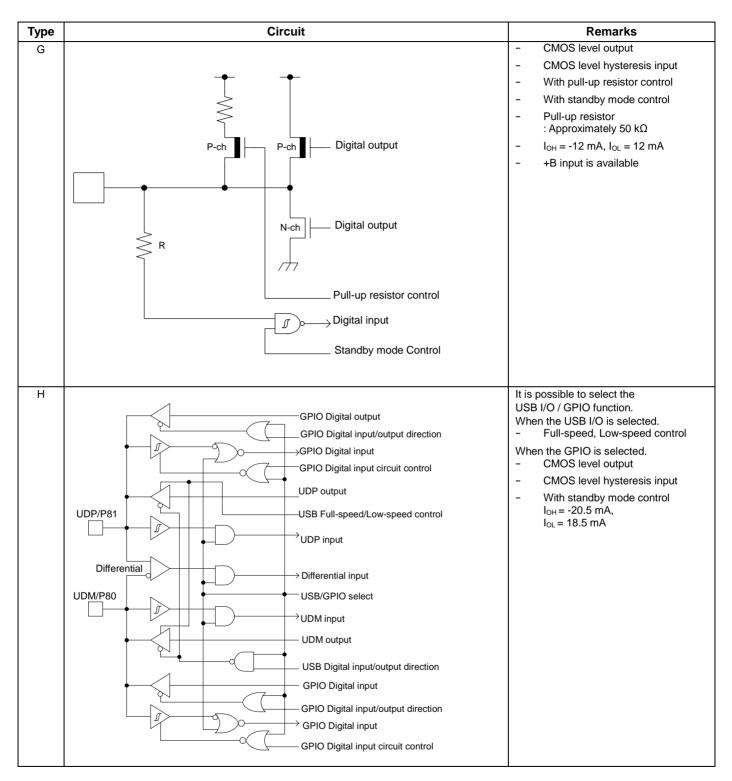

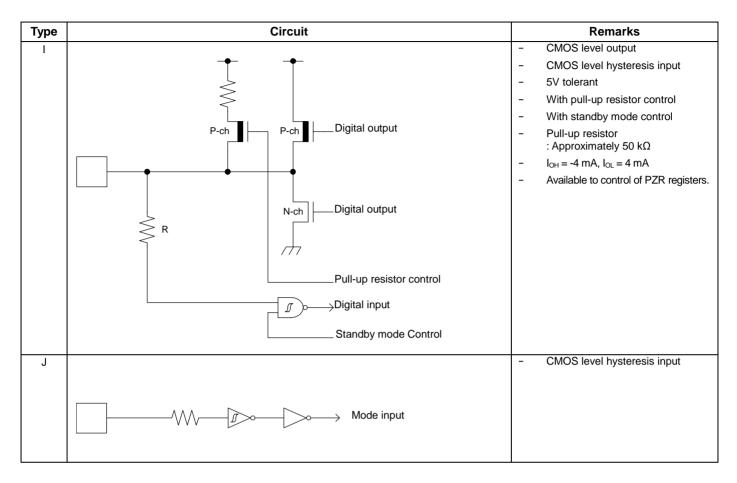

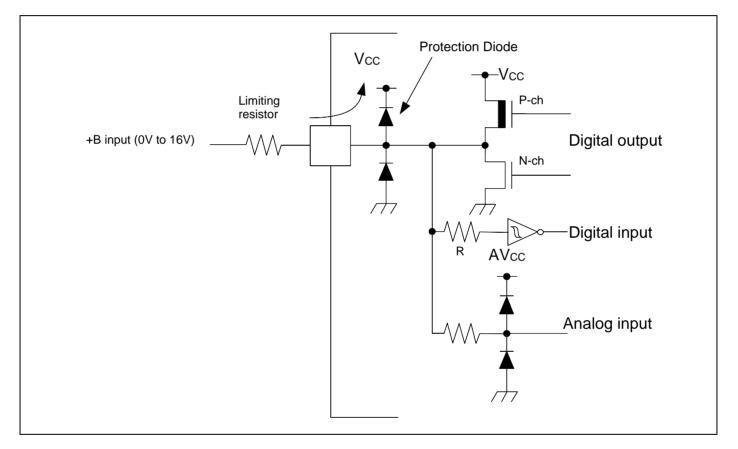

## 5. I/O Circuit Type

## **MB9A310K Series**

| Туре | Circuit                                               | Remarks                                                                                                                                                                                            |

|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C    |                                                       | <ul> <li>Open drain output</li> </ul>                                                                                                                                                              |

|      | □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                 | <ul> <li>CMOS level hysteresis input</li> </ul>                                                                                                                                                    |

|      | N-ch                                                  |                                                                                                                                                                                                    |

| D    |                                                       |                                                                                                                                                                                                    |

| D    | Pull-up<br>resistor<br>P-ch                           | It is possible to select the sub oscillation<br>/ GPIO function<br>When the sub oscillation is selected.<br>- Oscillation feedback resistor<br>: Approximately 5 MΩ<br>- With Standby mode control |

|      |                                                       | When the GPIO is selected.         -       CMOS level output.         -       CMOS level hysteresis input         -       With pull-up resistor control                                            |

|      | R Digital output                                      | <ul> <li>With standby mode control</li> <li>Pull-up resistor         <ul> <li>Approximately 50 kΩ</li> </ul> </li> <li>I<sub>OH</sub> = -4 mA, I<sub>OL</sub> = 4 mA</li> </ul>                    |

|      | Pull-up resistor control                              |                                                                                                                                                                                                    |

|      | □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                 |                                                                                                                                                                                                    |

|      | Standby mode Control                                  |                                                                                                                                                                                                    |

|      | Feedback<br>resistor                                  |                                                                                                                                                                                                    |

|      | Standby mode Control                                  |                                                                                                                                                                                                    |

|      | $f \rightarrow Digital input$                         |                                                                                                                                                                                                    |

|      | R Pull-up Standby mode Control                        |                                                                                                                                                                                                    |

|      | X0A<br>P-ch<br>P-ch<br>P-ch<br>P-ch<br>Digital output |                                                                                                                                                                                                    |

|      | N-ch Digital output                                   |                                                                                                                                                                                                    |

|      | Pull-up resistor control                              |                                                                                                                                                                                                    |

## 6. Handling Precautions

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Cypress semiconductor devices.

#### 6.1 Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

#### **Absolute Maximum Ratings**

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

#### **Recommended Operating Conditions**

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the Datasheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

#### **Processing and Protection of Pins**

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

- Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

- 2. Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device. Therefore, avoid this type of connection.

3. Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- 1. Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- 2. Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 6.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Cypress recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Cypress ranking of recommended conditions.

#### Lead-Free Packaging

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

#### **Storage of Semiconductor Devices**

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- 1. Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between 5°C and 30°C.

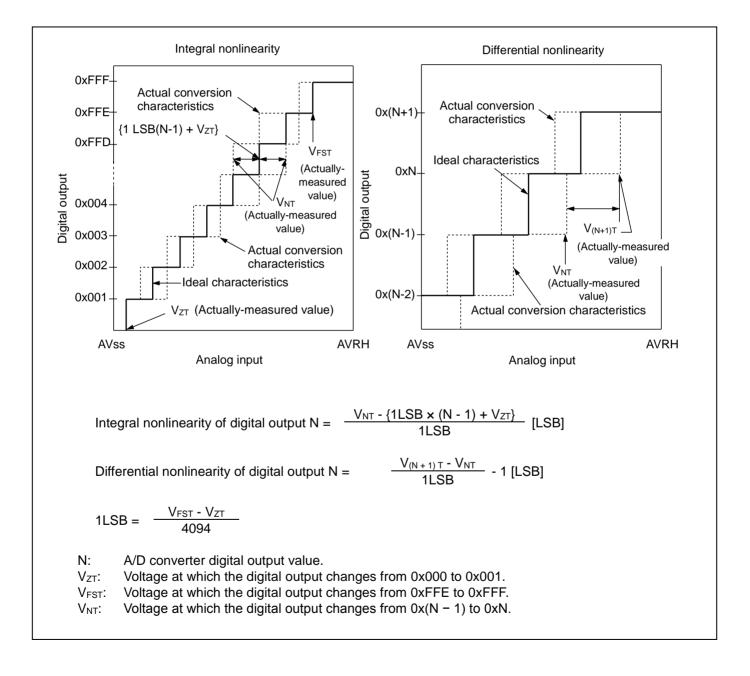

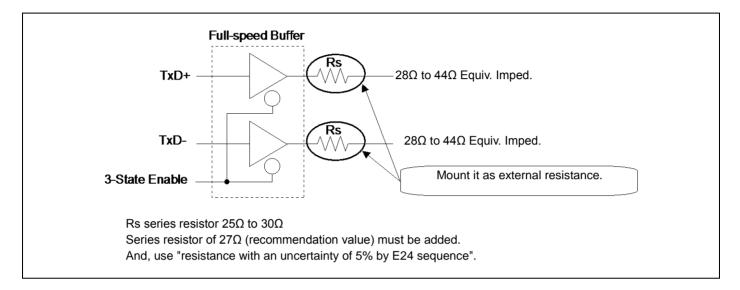

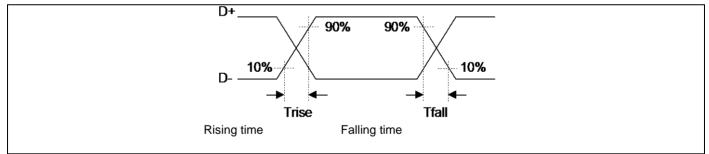

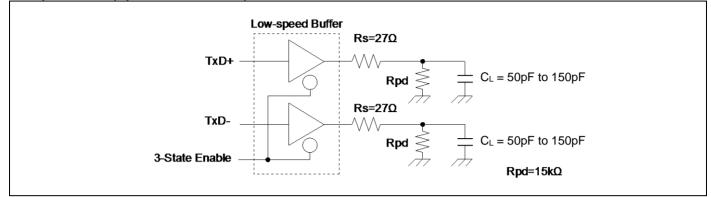

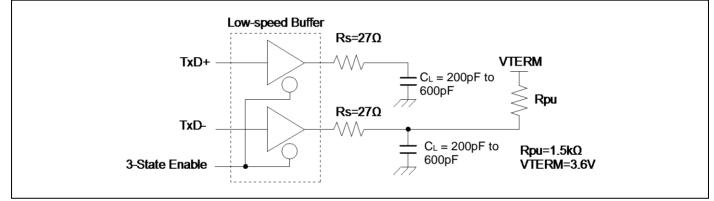

When you open Dry Package that recommends humidity 40% to 70% relative humidity.