# Automotive Grade Non-Synchronous Boost Controller

The NCV8871 is an adjustable output non-synchronous boost controller which drives an external N-channel MOSFET. The device uses peak current mode control with internal slope compensation. The IC incorporates an internal regulator that supplies charge to the gate driver.

Protection features include internally-set soft-start, undervoltage lockout, cycle-by-cycle current limiting, hiccup-mode short-circuit protection and thermal shutdown.

Additional features include low quiescent current sleep mode and externally-synchronizable switching frequency.

#### **Features**

- Peak Current Mode Control with Internal Slope Compensation

- 1.2 V ±2% Reference voltage

- Fixed Frequency Operation

- Wide Input Voltage Range of 3.2 V to 40 Vdc, 45 V Load Dump

- Input Undervoltage Lockout (UVLO)

- Internal Soft-Start

- Low Quiescent Current in Sleep Mode

- Cycle-by-Cycle Current Limit Protection

- Hiccup-Mode Overcurrent Protection (OCP)

- Hiccup-Mode Short-Circuit Protection (SCP)

- Thermal Shutdown (TSD)

- This is a Pb-Free Device

## ON Semiconductor®

www.onsemi.com

#### MARKING DIAGRAM

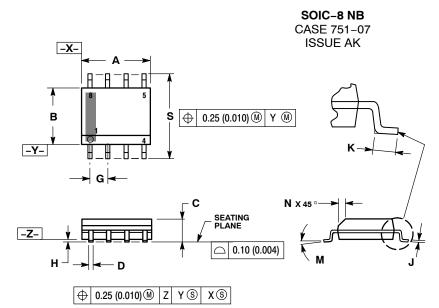

SOIC-8 D SUFFIX CASE 751

8871xx = Specific Device Code

xx = 00, 01, 02, 03, 04 = Assembly Location

A = Assembly L

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

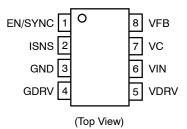

#### **PIN CONNECTIONS**

## **ORDERING INFORMATION**

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCV887100D1R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCV887101D1R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCV887102D1R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCV887103D1R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCV887104D1R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

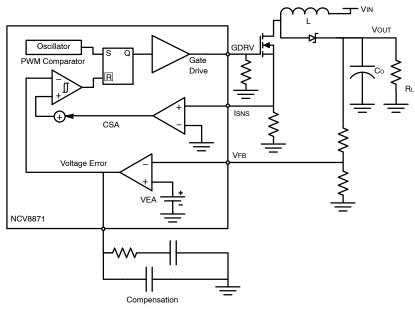

Figure 1. Simplified Block Diagram and Application Schematic

## PACKAGE PIN DESCRIPTIONS

| Pin No. | Pin<br>Symbol | Function                                                                                                                                                                                                                          |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN/SYNC       | Enable and synchronization input. The falling edge synchronizes the internal oscillator. The part is disabled into sleep mode when this pin is brought low for longer than the enable time-out period.                            |

| 2       | ISNS          | Current sense input. Connect this pin to the source of the external N-MOSFET, through a current-sense resistor to ground to sense the switching current for regulation and current limiting.                                      |

| 3       | GND           | Ground reference.                                                                                                                                                                                                                 |

| 4       | GDRV          | Gate driver output. Connect to gate of the external N–MOSFET. A series resistance can be added from GDRV to the gate to tailor EMC performance. An $R_{GND}$ = 15 k $\Omega$ (typical) GDRV–GND resistor is strongly recommended. |

| 5       | VDRV          | Driving voltage. Internally-regulated supply for driving the external N-MOSFET, sourced from VIN. Bypass with a 1.0 $\mu$ F ceramic capacitor to ground.                                                                          |

| 6       | VIN           | Input voltage. If bootstrapping operation is desired, connect a diode from the input supply to VIN, in addition to a diode from the output voltage to VDRV and/or VIN.                                                            |

| 7       | VC            | Output of the voltage error amplifier. An external compensator network from VC to GND is used to stabilize the converter.                                                                                                         |

| 8       | VFB           | Output voltage feedback. A resistor from the output voltage to VFB with another resistor from VFB to GND creates a voltage divider for regulation and programming of the output voltage.                                          |

## ABSOLUTE MAXIMUM RATINGS (Voltages are with respect to GND, unless otherwise indicated)

| Rating                                                                 | Value       | Unit |

|------------------------------------------------------------------------|-------------|------|

| Dc Supply Voltage (VIN)                                                | -0.3 to 40  | V    |

| Peak Transient Voltage (Load Dump on VIN)                              | 45          | V    |

| Dc Supply Voltage (VDRV, GDRV)                                         | 12          | V    |

| Peak Transient Voltage (VFB)                                           | -0.3 to 6   | V    |

| Dc Voltage (VC, VFB, ISNS)                                             | -0.3 to 3.6 | V    |

| Dc Voltage (EN/SYNC)                                                   | -0.3 to 6   | V    |

| Dc Voltage Stress (VIN – VDRV)*                                        | -0.7 to 45  | V    |

| Operating Junction Temperature                                         | -40 to 150  | °C   |

| Storage Temperature Range                                              | -65 to 150  | °C   |

| Peak Reflow Soldering Temperature: Pb-Free, 60 to 150 seconds at 217°C | 265 peak    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

\*An external diode from the input to the VIN pin is required if bootstrapping VDRV and VIN off of the output voltage.

### **PACKAGE CAPABILITIES**

| Cha                        | Value                                          | Unit         |         |

|----------------------------|------------------------------------------------|--------------|---------|

| ESD Capability (All Pins)  | Human Body Model<br>Machine Model              | ≥2.0<br>≥200 | kV<br>V |

| Moisture Sensitivity Level |                                                | 1            | -       |

| Package Thermal Resistance | Junction-to-Ambient, R <sub>θJA</sub> (Note 1) | 100          | °C/W    |

<sup>1. 1</sup> in<sup>2</sup>, 1 oz copper area used for heatsinking.

## **Device Variations**

The NCV8871 features several variants to better fit a multitude of applications. The table below shows the typical values of parameters for the parts that are currently available.

## **TYPICAL VALUES**

| Part No.  | D <sub>max</sub> | f <sub>s</sub> | t <sub>ss</sub> | Sa       | V <sub>cl</sub> | I <sub>src</sub> | I <sub>sink</sub> | V <sub>DRV</sub> | SCE |

|-----------|------------------|----------------|-----------------|----------|-----------------|------------------|-------------------|------------------|-----|

| NCV887100 | 88%              | 170 kHz        | 7.4 ms          | 53 mV/μs | 400 mV          | 800 mA           | 600 mA            | 10.5 V           | Υ   |

| NCV887101 | 86%              | 1000 kHz       | 1.25 ms         | 16 mV/μs | 400 mV          | 575 mA           | 350 mA            | 6.3 V            | Υ   |

| NCV887102 | 91%              | 1000 kHz       | 1.25 ms         | 53 mV/μs | 400 mV          | 800 mA           | 600 mA            | 6.3 V            | N   |

| NCV887103 | 93%              | 340 kHz        | 3.7 ms          | 53 mV/μs | 200 mV          | 575 mA           | 350 mA            | 8.4 V            | Υ   |

| NCV887104 | 93%              | 340 kHz        | 3.7 ms          | 53 mV/μs | 200 mV          | 800 mA           | 600 mA            | 8.4 V            | N   |

## **DEFINITIONS**

| Symbol            | Characteristic             | Symbol          | Characteristic             | Symbol           | Characteristic              |

|-------------------|----------------------------|-----------------|----------------------------|------------------|-----------------------------|

| D <sub>max</sub>  | Maximum Duty Cycle         | f <sub>s</sub>  | Switching Frequency        | t <sub>ss</sub>  | Soft-Start Time             |

| Sa                | Slope Compensating Ramp    | V <sub>cl</sub> | Current Limit Trip Voltage | I <sub>src</sub> | Gate Drive Sourcing Current |

| I <sub>sink</sub> | Gate Drive Sinking Current | $V_{DRV}$       | Drive Voltage              | SCE              | Short Circuit Enable        |

$\textbf{ELECTRICAL CHARACTERISTICS} \ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.2 \ \text{V} < \text{V}_{\text{IN}} < 40 \ \text{V}, \ \text{unless otherwise specified)} \ \text{Min/Max values are guaranteed by test, design or statistical correlation.}$

| Characteristic                                 | Symbol                 | Conditions                                                                                                                                    | Min                             | Тур                               | Max                               | Unit  |

|------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|-----------------------------------|-------|

| GENERAL                                        |                        |                                                                                                                                               |                                 |                                   |                                   |       |

| Quiescent Current, Sleep Mode                  | I <sub>q,sleep</sub>   | V <sub>IN</sub> = 13.2 V, EN = 0, T <sub>J</sub> = 25°C                                                                                       | _                               | 2.0                               | -                                 | μΑ    |

| Quiescent Current, Sleep Mode                  | I <sub>q,sleep</sub>   | V <sub>IN</sub> = 13.2 V, EN = 0, -40°C < T <sub>J</sub> < 125°C                                                                              | _                               | 2.0                               | 6.0                               | μΑ    |

| Quiescent Current, No switching                | $I_{q,off}$            | Into VIN pin, EN = 1, No switching                                                                                                            | _                               | 1.5                               | 2.5                               | mA    |

| Quiescent Current, Switching, normal operation | I <sub>q,on</sub>      | Into VIN pin, EN = 1, Switching                                                                                                               | -                               | 3.0                               | 6.0                               | mA    |

| OSCILLATOR                                     | •                      |                                                                                                                                               |                                 | •                                 |                                   | •     |

| Minimum pulse width                            | t <sub>on,min</sub>    |                                                                                                                                               | 90                              | 115                               | 140                               | ns    |

| Maximum duty cycle                             | D <sub>max</sub>       | NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                                                                 | 86<br>84<br>89<br>91            | 88<br>86<br>91<br>93<br>93        | 90<br>88<br>93<br>95<br>95        | %     |

| Switching frequency                            | f <sub>s</sub>         | NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                                                                 | 153<br>900<br>900<br>306<br>306 | 170<br>1000<br>1000<br>340<br>340 | 187<br>1100<br>1100<br>374<br>374 | kHz   |

| Soft-start time                                | t <sub>ss</sub>        | From start of switching with V <sub>FB</sub> = 0 until reference voltage = V <sub>REF</sub> NCV887100 NCV887101 NCV887102 NCV887103 NCV887104 | 6.0<br>1.0<br>1.0<br>3.0<br>3.0 | 7.4<br>1.25<br>1.25<br>3.7<br>3.7 | 8.8<br>1.5<br>1.5<br>4.4<br>4.4   | ms    |

| Soft-start delay                               | t <sub>ss,dly</sub>    | From EN $\rightarrow$ 1 until start of switching with $V_{FB} = 0$                                                                            | -                               | 240                               | 280                               | μs    |

| Slope compensating ramp                        | Sa                     | NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                                                                 | 46<br>13<br>46<br>46<br>46      | 53<br>16<br>53<br>53<br>53        | 60<br>19<br>60<br>60<br>60        | mV/μs |

| ENABLE/SYNCHRONIZATION                         | 1                      |                                                                                                                                               | 1                               | <u>I</u>                          | l                                 |       |

| EN/SYNC pull-down current                      | I <sub>EN/SYNC</sub>   | V <sub>EN/SYNC</sub> = 5 V                                                                                                                    | _                               | 5.0                               | 10                                | μΑ    |

| EN/SYNC input high voltage                     | V <sub>s,ih</sub>      | V <sub>IN</sub> > V <sub>UVLO</sub>                                                                                                           | 2.0                             | _                                 | 5.0                               | V     |

| EN/SYNC input low voltage                      | V <sub>s,il</sub>      |                                                                                                                                               | 0                               | _                                 | 800                               | mV    |

| EN/SYNC time-out ratio                         | %t <sub>en</sub>       | From SYNC falling edge, to oscillator control (EN high) or shutdown (EN low), Percent of typical switching period                             | -                               | -                                 | 350                               | %     |

| SYNC minimum frequency ratio                   | %f <sub>sync,min</sub> | Percent of f <sub>s</sub>                                                                                                                     | _                               | -                                 | 80                                | %     |

| SYNC maximum frequency                         | f <sub>sync,max</sub>  |                                                                                                                                               | 1.1                             | -                                 | -                                 | MHz   |

| Synchronization delay                          | t <sub>s,dly</sub>     | From SYNC falling edge to GDRV falling edge under open loop conditions                                                                        | -                               | 50                                | 100                               | ns    |

| Synchronization duty cycle                     | D <sub>sync</sub>      |                                                                                                                                               | 25                              | -                                 | 75                                | %     |

| CURRENT SENSE AMPLIFIER                        |                        |                                                                                                                                               |                                 |                                   |                                   |       |

| Low-frequency gain                             | A <sub>csa</sub>       | Input-to-output gain at dc, ISNS ≤ 1 V                                                                                                        | 0.9                             | 1.0                               | 1.1                               | V/V   |

| Bandwidth                                      | BW <sub>csa</sub>      | Gain of A <sub>csa</sub> – 3 dB                                                                                                               | 2.5                             | _                                 | -                                 | MHz   |

| ISNS input bias current                        | I <sub>sns,bias</sub>  | Out of ISNS pin                                                                                                                               | _                               | 30                                | 50                                | μΑ    |

$\textbf{ELECTRICAL CHARACTERISTICS} \ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.2 \ \text{V} < \text{V}_{\text{IN}} < 40 \ \text{V}, \ \text{unless otherwise specified)} \ \text{Min/Max values are guaranteed by test, design or statistical correlation.}$

| Characteristic                               | Symbol                | Conditions                                                                                                                          | Min                             | Тур                              | Max                             | Unit |

|----------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|---------------------------------|------|

| CURRENT SENSE AMPLIFIER                      |                       |                                                                                                                                     |                                 |                                  |                                 |      |

| Current limit threshold voltage              | V <sub>cl</sub>       | Voltage on ISNS pin<br>NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                                | 360<br>360<br>360<br>180<br>180 | 400<br>400<br>400<br>200<br>200  | 440<br>440<br>440<br>220<br>220 | mV   |

| Current limit,<br>Response time              | t <sub>cl</sub>       | CL tripped until GDRV falling edge,<br>V <sub>ISNS</sub> = V <sub>cl</sub> (typ) + 60 mV                                            | -                               | 80                               | 125                             | ns   |

| Overcurrent protection,<br>Threshold voltage | %V <sub>ocp</sub>     | Percent of V <sub>cl</sub>                                                                                                          | 125                             | 150                              | 175                             | %    |

| Overcurrent protection,<br>Response Time     | t <sub>ocp</sub>      | From overcurrent event, Until switching stops, V <sub>ISNS</sub> = V <sub>OCP</sub> + 40 mV                                         | -                               | -                                | 125                             | ns   |

| VOLTAGE ERROR OPERATIONA                     | L TRANSCON            | DUCTANCE AMPLIFIER                                                                                                                  |                                 |                                  |                                 |      |

| Transconductance                             | g <sub>m,vea</sub>    | $V_{FB} - V_{ref} = \pm 20 \text{ mV}$                                                                                              | 0.8                             | 1.2                              | 1.63                            | mS   |

| VEA output resistance                        | R <sub>o,vea</sub>    |                                                                                                                                     | 2.0                             | -                                | -                               | MΩ   |

| VFB input bias current                       | I <sub>vfb,bias</sub> | Current out of VFB pin                                                                                                              | -                               | 0.5                              | 2.0                             | μΑ   |

| Reference voltage                            | $V_{ref}$             |                                                                                                                                     | 1.176                           | 1.200                            | 1.224                           | V    |

| VEA maximum output voltage                   | V <sub>c,max</sub>    |                                                                                                                                     | 2.5                             | -                                | -                               | V    |

| VEA minimum output voltage                   | $V_{c,min}$           |                                                                                                                                     | -                               | -                                | 0.3                             | V    |

| VEA sourcing current                         | I <sub>src,vea</sub>  | VEA output current, Vc = 2.0 V                                                                                                      | 80                              | 100                              | -                               | μΑ   |

| VEA sinking current                          | I <sub>snk,vea</sub>  | VEA output current, Vc = 0.7 V                                                                                                      | 80                              | 100                              | -                               | μΑ   |

| GATE DRIVER                                  |                       | -                                                                                                                                   | <u> </u>                        |                                  |                                 |      |

| Sourcing current                             | I <sub>src</sub>      | V <sub>DRV</sub> ≥ 6 V, V <sub>DRV</sub> − V <sub>GDRV</sub> = 2 V<br>NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104 | 600<br>400<br>600<br>400<br>600 | 800<br>575<br>800<br>575<br>800  | -<br>-<br>-<br>-                | mA   |

| Sinking current                              | Isink                 | V <sub>GDRV</sub> ≥ 2 V<br>NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                            | 500<br>250<br>500<br>250<br>500 | 600<br>350<br>600<br>350<br>600  | -<br>-<br>-<br>-                | mA   |

| Driving voltage dropout                      | $V_{drv,do}$          | $V_{IN} - V_{DRV}$ , $Iv_{DRV} = 25 \text{ mA}$                                                                                     | -                               | 0.3                              | 0.6                             | V    |

| Driving voltage source current               | I <sub>drv</sub>      | V <sub>IN</sub> – V <sub>DRV</sub> = 1 V                                                                                            | 35                              | 45                               | _                               | mA   |

| Backdrive diode voltage drop                 | $V_{d,bd}$            | $V_{DRV} - V_{IN}$ , $I_{d,bd} = 5 \text{ mA}$                                                                                      | -                               | -                                | 0.7                             | V    |

| Driving voltage                              | V <sub>DRV</sub>      | I <sub>VDRV</sub> = 0.1 – 25 mA<br>NCV887100<br>NCV887101<br>NCV887102<br>NCV887103<br>NCV887104                                    | 10<br>6.0<br>6.0<br>8.0<br>8.0  | 10.5<br>6.3<br>6.3<br>8.4<br>8.4 | 11<br>6.6<br>6.6<br>8.8<br>8.8  | V    |

| UVLO                                         | •                     | •                                                                                                                                   | -                               |                                  |                                 |      |

| Undervoltage lock-out,<br>Threshold voltage  | V <sub>uvlo</sub>     | V <sub>IN</sub> falling                                                                                                             | 3.0                             | 3.1                              | 3.2                             | V    |

| Undervoltage lock-out,<br>Hysteresis         | V <sub>uvlo,hys</sub> | V <sub>IN</sub> rising                                                                                                              | 50                              | 125                              | 200                             | mV   |

$\textbf{ELECTRICAL CHARACTERISTICS} \ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.2 \ \text{V} < \text{V}_{\text{IN}} < 40 \ \text{V}, \ \text{unless otherwise specified)} \ \text{Min/Max values are guaranteed by test, design or statistical correlation.}$

| Characteristic                  | Symbol                | Conditions                                                          | Min | Тур | Max | Unit |

|---------------------------------|-----------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| SHORT CIRCUIT PROTECTION        |                       |                                                                     |     |     |     |      |

| Startup blanking period         | %t <sub>scp,dly</sub> | From start of soft-start, Percent of t <sub>ss</sub>                | 100 | 120 | 150 | %    |

| Hiccup-mode period              | %t <sub>hcp,dly</sub> | From shutdown to start of soft-start,<br>Percent of t <sub>ss</sub> | 70  | 85  | 100 | %    |

| Short circuit threshold voltage | %V <sub>scp</sub>     | V <sub>FB</sub> as percent of V <sub>ref</sub>                      | 60  | 67  | 75  | %    |

| Short circuit delay             | t <sub>scp</sub>      | From V <sub>FB</sub> < V <sub>scp</sub> to stop switching           | -   | 35  | 100 | ns   |

| THERMAL SHUTDOWN                |                       |                                                                     |     |     |     |      |

| Thermal shutdown threshold      | T <sub>sd</sub>       | T <sub>J</sub> rising                                               | 160 | 170 | 180 | °C   |

| Thermal shutdown hysteresis     | T <sub>sd,hys</sub>   | T <sub>J</sub> falling                                              | 10  | 15  | 20  | °C   |

| Thermal shutdown delay          | t <sub>sd,dly</sub>   | From T <sub>J</sub> > T <sub>sd</sub> to stop switching             | -   | -   | 100 | ns   |

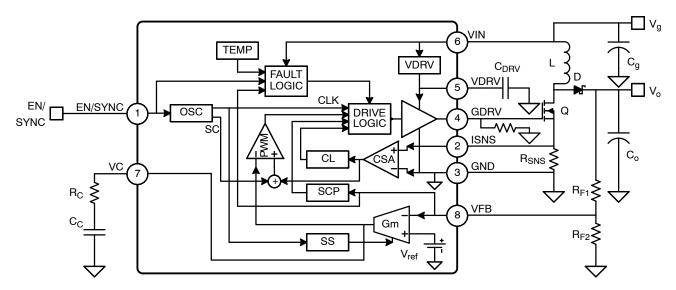

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 7. Normalized Current Limit vs. Temperature

Figure 6. Minimum On Time vs. Temperature

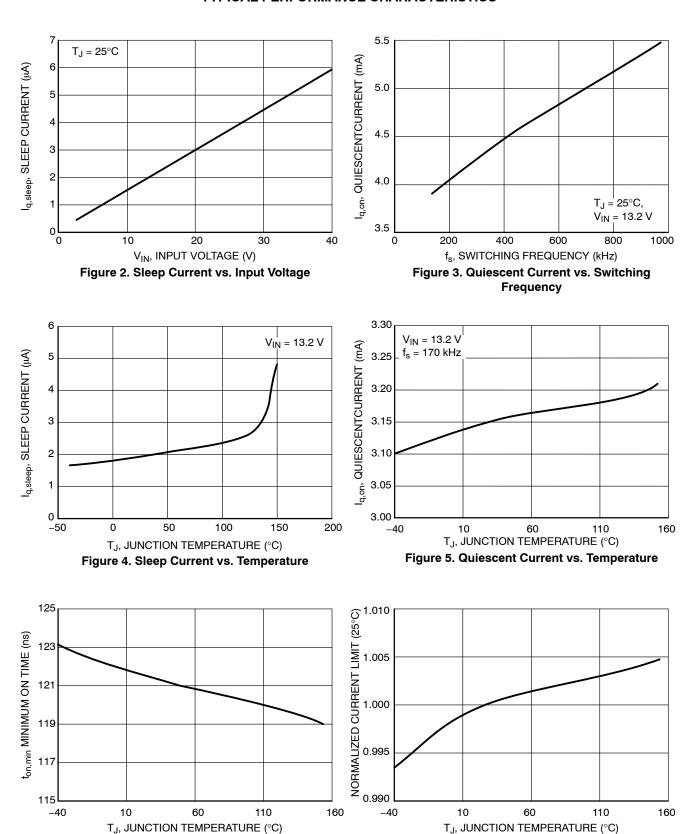

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 8. Reference Voltage vs. Temperature

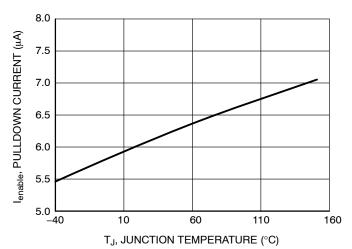

Figure 9. Enable Pulldown Current vs. Voltage

Figure 10. Enable Pulldown Current vs. Temperature

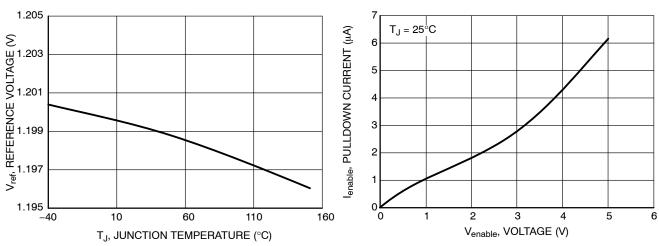

### THEORY OF OPERATION

Figure 11. Current Mode Control Schematic

#### **Current Mode Control**

The NCV8871 incorporates a current mode control scheme, in which the PWM ramp signal is derived from the power switch current. This ramp signal is compared to the output of the error amplifier to control the on-time of the power switch. The oscillator is used as a fixed-frequency clock to ensure a constant operational frequency. The resulting control scheme features several advantages over conventional voltage mode control. First, derived directly from the inductor, the ramp signal responds immediately to line voltage changes. This eliminates the delay caused by the output filter and the error amplifier, which is commonly found in voltage mode controllers. The second benefit comes from inherent pulse-by-pulse current limiting by merely clamping the peak switching current. Finally, since current mode commands an output current rather than voltage, the filter offers only a single pole to the feedback loop. This allows for a simpler compensation.

The NCV8871 also includes a slope compensation scheme in which a fixed ramp generated by the oscillator is added to the current ramp. A proper slope rate is provided to improve circuit stability without sacrificing the advantages of current mode control.

#### **Current Limit**

The NCV8871 features two current limit protections, peak current mode and over current latch off. When the current sense amplifier detects a voltage above the peak current limit between ISNS and GND after the current limit leading edge blanking time, the peak current limit causes the power switch to turn off for the remainder of the cycle. Set the current limit with a resistor from ISNS to GND, with R =  $V_{\rm CL}$  /  $I_{\rm limit}$ .

If the voltage across the current sense resistor exceeds the over current threshold voltage the device enters over current hiccup mode. The device will remain off for the hiccup time and then go through the soft–start procedure.

#### **Short Circuit Protection**

If the short circuit enable bit is set (SCE = Y) the device will attempt to protect the power MOSFET from damage. When the output voltage falls below the short circuit trip voltage, after the initial short circuit blanking time, the device enters short circuit latch off. The device will remain off for the hiccup time and then go through the soft–start.

#### **EN/SYNC**

The Enable/Synchronization pin has three modes. When a dc logic high (CMOS/TTL compatible) voltage is applied to this pin the NCV8871 operates at the programmed frequency. When a dc logic low voltage is applied to this pin the NCV8871 enters a low quiescent current sleep mode. When a square wave of at least %f<sub>sync,min</sub> of the free running switching frequency is applied to this pin, the switcher operates at the same frequency as the square wave. If the signal is slower than this, it will be interpreted as enabling and disabling the part. The falling edge of the square wave corresponds to the start of the switching cycle. If device is disabled, it must be disabled for 7 clock cycles before being re-enabled.

If the VIN pin voltage falls below V<sub>UVLO</sub> when EN/SYNC pin is at logic-high, the IC may not power up when VIN returns back above the UVLO. To resume a normal operating state, the EN/SYNC pin must be cycled with a single logic-low to logic-high transition.

#### **UVLO**

Input Undervoltage Lockout (UVLO) is provided to ensure that unexpected behavior does not occur when VIN is too low to support the internal rails and power the controller. The IC will start up when enabled and VIN surpasses the UVLO threshold plus the UVLO hysteresis and will shut down when VIN drops below the UVLO threshold or the part is disabled.

To avoid any lock state under UVLO conditions, the EN/SYNC pin should be in logic-low state. For further details, please refer to EN/SYNC paragraph.

#### Internal Soft-Start

To insure moderate inrush current and reduce output overshoot, the NCV8871 features a soft start which charges a capacitor with a fixed current to ramp up the reference voltage. This fixed current is based on the switching frequency, so that if the NCV8871 is synchronized to twice the default switching frequency the soft start will last half as long.

#### **VDRV**

An internal regulator provides the drive voltage for the gate driver. Bypass with a ceramic capacitor to ground to ensure fast turn on times. The capacitor should be between 0.1  $\mu F$  and 1  $\mu F$ , depending on switching speed and charge requirements of the external MOSFET.

#### **GDRV**

An  $R_{GND}$  = 15 k $\Omega$  (typical) GDRV-GND resistor is strongly recommended.

## **APPLICATION INFORMATION**

## **Design Methodology**

This section details an overview of the component selection process for the NCV8871 in continuous conduction mode boost. It is intended to assist with the design process but does not remove all engineering design work. Many of the equations make heavy use of the small ripple approximation. This process entails the following steps:

- 1. Define Operational Parameters

- 2. Select Current Sense Resistor

- 3. Select Output Inductor

- 4. Select Output Capacitors

- 5. Select Input Capacitors

- 6. Select Feedback Resistors

- 7. Select Compensator Components

- 8. Select MOSFET(s)

- 9. Select Diode

- 10. Determine Feedback Loop Compensation Network

### 1. Define Operational Parameters

Before beginning the design, define the operating parameters of the application. These include:

V<sub>IN(min)</sub>: minimum input voltage [V]

V<sub>IN(max):</sub> maximum input voltage [V]

V<sub>OUT</sub>: output voltage [V]

I<sub>OUT(max)</sub>: maximum output current [A]

I<sub>CL</sub>: desired typical cycle-by-cycle current limit [A]

From this the ideal minimum and maximum duty cycles can be calculated as follows:

$$D_{min} = 1 - \frac{V_{IN(max)}}{V_{OUT}}$$

$$D_{max} = 1 - \frac{V_{IN(min)}}{V_{OUT}}$$

Both duty cycles will actually be higher due to power loss in the conversion. The exact duty cycles will depend on conduction and switching losses. If the maximum input voltage is higher than the output voltage, the minimum duty cycle will be negative. This is because a boost converter cannot have an output lower than the input. In situations where the input is higher than the output, the output will follow the input, minus the diode drop of the output diode and the converter will not attempt to switch.

If the calculated  $D_{max}$  is higher the  $D_{max}$  of the NCV8871, the conversion will not be possible. It is important for a boost converter to have a restricted  $D_{max}$ , because while the ideal conversion ration of a boost converter goes up to infinity as D approaches 1, a real converter's conversion ratio starts to decrease as losses overtake the increased power transfer. If the converter is in this range it will not be able to regulate properly.

If the following equation is not satisfied, the device will skip pulses at high  $V_{IN}$ :

$$\frac{\mathsf{D}_{\mathsf{min}}}{f_{\mathsf{s}}} \geq \mathsf{t}_{\mathsf{on}(\mathsf{min})}$$

Where:  $f_s$ : switching frequency [Hz]  $t_{on(min)}$ : minimum on time [s]

### 2. Select Current Sense Resistor

Current sensing for peak current mode control and current limit relies on the MOSFET current signal, which is measured with a ground referenced amplifier. The easiest method of generating this signal is to use a current sense resistor from the source of the MOSFET to device ground. The sense resistor should be selected as follows:

$$R_S = \frac{V_{CL}}{I_{CL}}$$

Where:  $R_S$ : sense resistor  $[\Omega]$

V<sub>CL</sub>: current limit threshold voltage [V]

I<sub>CL</sub>: desire current limit [A]

#### 3. Select Output Inductor

The output inductor controls the current ripple that occurs over a switching period. A high current ripple will result in excessive power loss and ripple current requirements. A low current ripple will result in a poor control signal and a slow current slew rate in case of load steps. A good starting point for peak to peak ripple is around  $20{\text -}40\%$  of the inductor current at the maximum load at the worst case  $V_{\rm IN}$ , but

operation should be verified empirically. The worst case  $V_{IN}$  is half of  $V_{OUT}$ , or whatever  $V_{IN}$  is closest to half of  $V_{OUT}$ . After choosing a peak current ripple value, calculate the inductor value as follows:

$$L = \frac{V_{IN(WC)} D_{WC}}{\Delta I_{L,max} f_s}$$

Where:  $V_{IN(WC)}$ :  $V_{IN}$  value as close as possible to half of  $V_{OUT}[V]$

D<sub>WC</sub>: duty cycle at V<sub>IN(WC)</sub>

$\Delta I_{L,max}$ : maximum peak to peak ripple [A]

The maximum average inductor current can be calculated as follows:

$$I_{L,AVG} = \frac{V_{OUT}I_{OUT(max)}}{V_{IN(min)}\eta}$$

The Peak Inductor current can be calculated as follows:

$$I_{L,peak} = I_{L,avg} + \frac{\Delta I_{L,max}}{2}$$

Where: I<sub>L,peak</sub>: Peak inductor current value [A]

## 4. Select Output Capacitors

The output capacitors smooth the output voltage and reduce the overshoot and undershoot associated with line transients. The steady state output ripple associated with the output capacitors can be calculated as follows:

$V_{OUT(ripple)} =$

$$\frac{\text{DI}_{\text{OUT}(\text{max})}}{\textit{fC}_{\text{OUT}}} + \left(\frac{\text{I}_{\text{OUT}(\text{max})}}{1-\text{D}} + \frac{\text{V}_{\text{IN}(\text{min})}\text{D}}{2\textit{fL}}\right) \! R_{\text{ESR}}$$

The capacitors need to survive an RMS ripple current as follows:

$$I_{Cout(RMS)} = I_{OUT} \sqrt{\frac{D_{WC}}{D'_{WC}} + \frac{D_{WC}}{12} \left(\frac{D'_{WC}}{\frac{L}{R_{OUT} \times T_{SW}}}\right)^2}$$

The use of parallel ceramic bypass capacitors is strongly encouraged to help with the transient response.

### 5. Select Input Capacitors

The input capacitor reduces voltage ripple on the input to the module associated with the ac component of the input current.

$$I_{Cin(RMS)} = \frac{V_{IN(min)}^{2} D_{WC}}{Lf_{s}V_{OUT}^{2}\sqrt{3}}$$

#### 6. Select Feedback Resistors

The feedback resistors form a resistor divider from the output of the converter to ground, with a tap to the feedback pin. During regulation, the divided voltage will equal  $V_{ref}$ . The lower feedback resistor can be chosen, and the upper feedback resistor value is calculated as follows:

$$R_{upper} = R_{lower} \frac{(V_{out} - V_{ref})}{V_{ref}}$$

The total feedback resistance ( $R_{upper} + R_{lower}$ ) should be in the range of 1 k $\Omega$  – 100 k $\Omega$ .

## 7. Select Compensator Components

Current Mode control method employed by the NCV8871 allows the use of a simple, Type II compensation to optimize the dynamic response according to system requirements.

#### 8. Select MOSFET(s)

In order to ensure the gate drive voltage does not drop out the MOSFET(s) chosen must not violate the following inequality:

$$Q_{g(total)} \le \frac{I_{drv}}{f_s}$$

Where:  $Q_{g(total)}$ : Total Gate Charge of MOSFET(s) [C]  $I_{drv}$ : Drive voltage current [A]  $f_s$ : Switching Frequency [Hz]

The maximum RMS Current can be calculated as follows:

$$I_{Q(max)} = I_{out} \frac{\sqrt{D}}{D'}$$

The maximum voltage across the MOSFET will be the maximum output voltage, which is the higher of the maximum input voltage and the regulated output voltaged:

$$V_{Q(max)} = V_{OUT(max)}$$

#### 9. Select Diode

The output diode rectifies the output current. The average current through diode will be equal to the output current:

$$I_{D(avg)} = I_{OUT(max)}$$

Additionally, the diode must block voltage equal to the higher of the output voltage and the maximum input voltage:

$$V_{D(max)} = V_{OUT(max)}$$

The maximum power dissipation in the diode can be calculated as follows:

$$P_D = V_{f(max)} I_{OUT(max)}$$

Where:  $P_d$ : Power dissipation in the diode [W]  $V_{f(max)}$ : Maximum forward voltage of the diode [V]

## 10. Determine Feedback Loop Compensation Network

The purpose of a compensation network is to stabilize the dynamic response of the converter. By optimizing the compensation network, stable regulation response is achieved for input line and load transients.

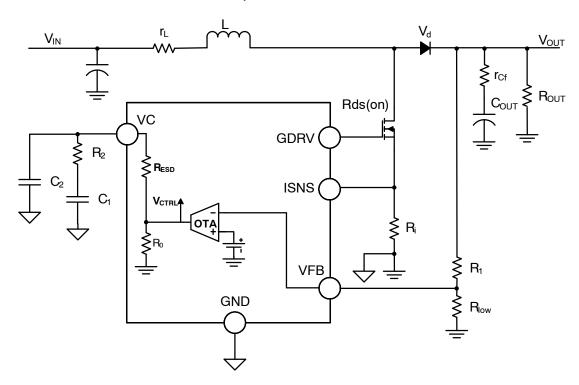

Compensator design involves the placement of poles and zeros in the closed loop transfer function. Losses from the boost inductor, MOSFET, current sensing and boost diode losses also influence the gain and compensation expressions. The OTA has an ESD protection structure  $(R_{ESD} \approx 502~\Omega)$ , data not provided in the datasheet) located on the die between the OTA output and the IC package compensation pin (VC). The information from the OTA PWM feedback control signal ( $V_{CTRL}$ ) may differ from the IC-VC signal if  $R_2$  is of similar order of magnitude as  $R_{ESD}$ .

The compensation and gain expressions which follow take influence from the OTA output impedance elements into account.

Type-I compensation is not possible due to the presence of  $R_{ESD}$ . The Figures 12 and 13 compensation networks correspond to a Type-II network in series with  $R_{ESD}$ . The resulting control-output transfer function is an accurate mathematical model of the IC in a boost converter topology. The model does have limitations and a more accurate SPICE model should be considered for a more detailed analysis:

- The attenuating effect of large value ceramic capacitors in parallel with output electrolytic capacitor ESR is not considered in the equations.

- The CCM Boost control-output transfer function includes operating efficiency as a correction factor to improve modeling accuracy under low input voltage and high output current operating conditions where operating losses becomes significant.

Figure 12. NCV8871 Boost Converter OTA and Compensation

Figure 13. NCV8871 Flyback Converter OTA and Compensation

The following equations may be used to select compensation components  $R_2$ ,  $C_1$ ,  $C_2$  for Figures 12 & 13 power supply. Required input design parameters for analysis are:

$V_d$  = Output diode  $V_f(V)$

$V_{IN}$  = Power supply input voltage (V)

$N = N_s/N_p$  (Flyback transformer turns ratio)

$R_i$  = Current sense resistor ( $\Omega$ )

$R_{DS(on)} = \text{MOSFET } R_{DS(on)}(\Omega)$

$(R_{SW\_eq} = R_{DS(on)} + R_i$  for the boost continuous conduction mode (CCM) expressions)

$C_{OUT}$  = Bulk output capacitor value (F)

$r_{CF}$  = Bulk output capacitor ESR ( $\Omega$ )

$R_{OUT}$  = Equivalent resistance of output load ( $\Omega$ )

$P_{out}$  = Output Power (W)

L = Boost inductor value or flyback transformer primary side inductance (H)

$r_L$  = Boost inductor ESR ( $\Omega$ )

$T_s = 1/f_s$ , where  $f_s =$  clock frequency (Hz)

$R_I$  and  $R_{low}$  = Feedback resistor divider values used to set the output voltage  $(\Omega)$

$V_{OUT}$  = Device specific output voltage (defined by R<sub>1</sub> and R<sub>low</sub> values) (V)

$R_0$  = OTA output resistance = 3 M $\Omega$

$S_a$  = IC slope compensation (e.g. 53 mV/ $\mu$ s for NCV887100)

$g_m$  = OTA transconductance = 1.2 mS

D = Controller duty ratio

D' = 1 - D

Necessary equations for describing the modulator gain  $(V_{ctrl}$ -to- $V_{out}$  gain)  $H_{ctrl\_output}(f)$  are described next. Boost continuous conduction mode (CCM) and discontinuous conduction mode (DCM) transfer function expressions are summarized in Table 1. Flyback CCM and DCM transfer function expressions are summarized in Table 2.

Table 1. BOOST CCM AND DCM TRANSFER FUNCTION EXPRESSIONS

|                                                                               | ССМ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DCM                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Duty Ratio ( <b>D</b> )                                                       | $ \begin{bmatrix} 2R_{OUT}V_{d}V_{IN} - \left[R_{sw\_eq} + R_{OUT}\left(\frac{V_{IN}}{V_{OUT}} - 2\right)\right]V_{OUT}^{2} \\ -V_{OUT}\sqrt{R_{OUT}\left(\frac{R_{OUT}V_{IN}^{2} + 2R_{sw\_eq}V_{IN}V_{OUT}^{2} - 4V_{d}R_{sw\_eq}V_{IN}}{-4R_{sw\_eq}V_{OUT}^{2} - 4r_{L}V_{d}V_{IN}^{2} - 4r_{L}V_{OUT}^{2}}}\right) + R_{sw\_eq}^{2}V_{OUT}^{2}} \\ \frac{2R_{OUT}\left(V_{OUT}^{2} + V_{d}V_{IN}\right)}{2R_{OUT}\left(V_{OUT}^{2} + V_{d}V_{IN}\right)} + R_{sw\_eq}^{2}V_{OUT}^{2} + V_{d}^{2}V_{IN}^{2}} + V_{d}^{2}V_{IN}^{2}$ | $\sqrt{2\tau_L M(M-1)}$ Where: $\tau_L = \frac{L}{R_{OUT} T_s}$                                                                                                                                           |

| V <sub>OUT</sub> /V <sub>IN</sub> DC<br>Voltage Gain ( <b>M</b> )             | $\frac{1}{1-D} \left[ 1 - \frac{(1-D)V_d}{V_{out}} \right] \left[ \frac{1}{1 + \frac{1}{(1-D)^2 \left(\frac{r_L + DR_{sw\_eq}}{R_{OUT}}\right)}} \right]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{1}{2}\left(1+\sqrt{1+\frac{2D^2}{\tau_L}}\right)$                                                                                                                                                  |

| Inductor On-slope $(S_n)$ , V/s                                               | $\frac{V_{IN}-I_{Lave}\!\!\left(r_L+R_{sw\_eq}\right)}{L}R_i$ Where average inductor current: $I_{Lave}=\frac{P_{out}}{V_{IN}\eta}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\frac{V_{IN}}{L}R_{i}$                                                                                                                                                                                   |

| Compensation<br>Ramp ( <b>m</b> <sub>c</sub> )                                | $1 + \frac{S_a}{S_n}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $1 + \frac{S_a}{S_n}$                                                                                                                                                                                     |

| $C_{out}$ ESR Zero $(\omega_{z1})$                                            | $\frac{1}{\mathrm{r_{CF}C_{OUT}}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{1}{\rm r_{CF}C_{OUT}}$                                                                                                                                                                             |

| Right-Half-Plane<br>Zero ( $\omega_{z2}$ )                                    | $\frac{\left(1-D\right)^{2}}{L}\left(R_{OUT}-\frac{r_{CF}R_{OUT}}{r_{CF}+R_{OUT}}\right)-\frac{r_{L}}{L}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{R_{OUT}}{M^2L}$                                                                                                                                                                                    |

| Low Frequency Modulator Pole $(\omega_{p1})$                                  | $\frac{\frac{2}{R_{OUT}} + \frac{T_s}{LM^3}m_c}{C_{OUT}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{1}{R_{CF}C_{OUT}} \cdot \frac{2M-1}{M-1}$                                                                                                                                                          |

| High Frequency<br>Modulator Pole<br>$(\omega_{p2})$                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $2F_{SW}\left(\frac{1-\frac{1}{M}}{D}\right)^2$                                                                                                                                                           |

| Sampling Double Pole $(\omega_n)$                                             | $rac{\pi}{T_s}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                         |

| Sampling Quality Coefficient $(Q_p)$                                          | $\frac{1}{\pi(m_{\rm c}(1-{\rm D})-0.5)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                         |

| F <sub>m</sub>                                                                | $\frac{1}{2M + \frac{R_{OUT}T_s}{LM^2} \left(\frac{1}{2} + \frac{S_a}{S_n}\right)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\frac{1}{S_n m_c T_s}$                                                                                                                                                                                   |

| H <sub>d</sub>                                                                | $\frac{\etaR_{\rm OUT}}{R_{\rm i}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\frac{2V_{OUT}}{D} \cdot \frac{M-1}{2M-1}$                                                                                                                                                               |