Document Number: MC34704 Rev. 8.0, 12/2014

**√RoHS**

# Multiple Channel DC-DC Power Management IC

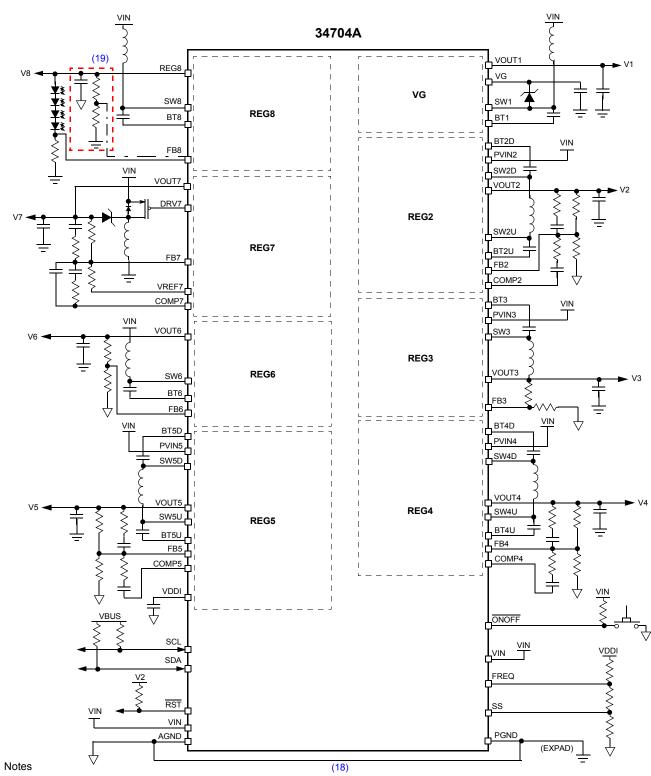

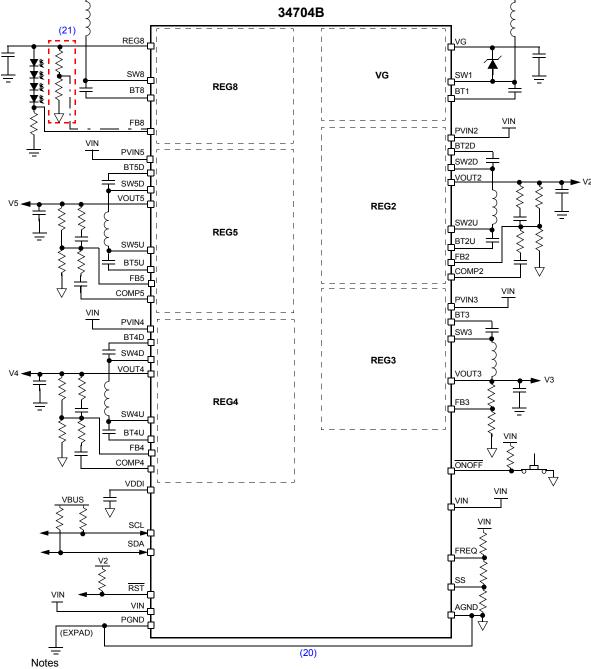

The 34704 is a multi-channel Power Management IC (PMIC) used to address power management needs for various multimedia application microprocessors. Its ability to provide either 5 or 8 independent output voltages with a single input power supply (2.7 and 5.5 V) together with its high efficiency, make it ideal for portable devices powered up by Li-lon/polymer batteries or for USB powered devices as well. This device is powered by SMARTMOS technology.

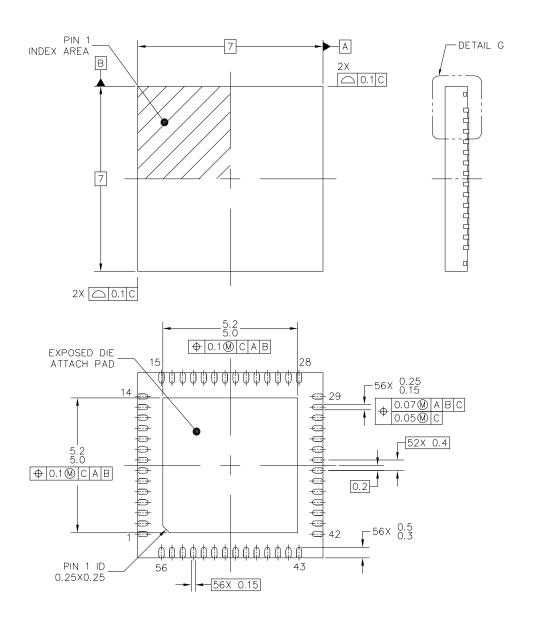

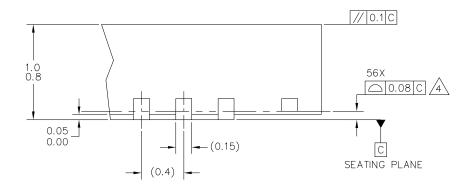

The 34704 is housed in a 7x7 mm, Pb-free, QFN56 and is capable of operating at a switching frequency of up to 2.0 MHz. This makes it possible to reduce external component size and to implement full space efficient power management solutions.

# **Features**

- 8 DC/DC (34704A) or 5 DC/DC (34704B) switching regulators with up to ±2% output voltage accuracy

- · Dynamic voltage scaling on all regulators.

- · Selectable output voltage or current regulation on REG8

- I<sup>2</sup>C programmability

- · Output undervoltage and overvoltage detection for each regulator

- Overcurrent limit detection and short-circuit protection for each regulator

- Thermal limit detection for each regulator, except REG7

- · Integrated compensation for REG1, REG3, REG6, and REG8

- 5.0 μA maximum shutdown current (All regulators are off, 5.5 V VIN)

- · True cutoff on all of the boost and buck-boost regulators

# 34704

# **MULTI-CHANNEL IC**

EP SUFFIX (PB-FREE) 98ASA00712D 56-PIN QFN

| ORDERING INFORMATION |                                        |           |  |  |  |

|----------------------|----------------------------------------|-----------|--|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package   |  |  |  |

| MC34704AEP/R2        | -20 °C to 85 °C                        | 56 QFN EP |  |  |  |

| MC34704BEP/R2        | -20 0 10 65 0                          | 30 QIN LF |  |  |  |

\* Available only in 34704A device

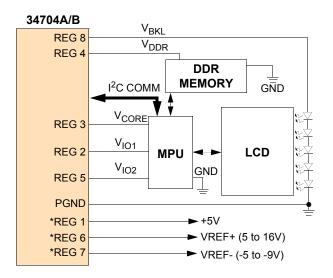

Figure 1. 34704 Simplified Application Diagram

# **DEVICE VARIATIONS**

#### **Table 1. Device Variations**

| Orderable Part Number | No. of Regulators | Regulator Number  |

|-----------------------|-------------------|-------------------|

| MC34704AEP/R2         | 8                 | Reg 1 - 8         |

| MC34704BEP/R2         | 5                 | Reg 2, 3, 4, 5, 8 |

#### INTERNAL BLOCK DIAGRAM REG8 voltage data voltage data REG1/VG Control Control VOUT1 (34704A) OUT8 🗆 Error Amp +□ SW1 SW8 VG Start-Up lpeak-det BT8 BT1 and blanking SW control FB8 □ REG2 REG7 (34704A) BT2D PVIN2 voltage data voltage data OUT7-SW2D Control Control Error Amp DRV7 VOUT2 Error Amp SW2U FB7 Amp VG VREF7 BT2U COMP7 COMP2 FB2 REG6 (34704A) voltage data REG3 Control voltage data ВТ3 VOUT6 <del>‡</del>⊤□ PVIN3 Control Error Amp □ SW3 SW6 Error Amp BT6 VOUT3 Error Amp PWM P-skip FB3 FB6 REG4 BT4D FT PVIN4 REG5 voltage data BT5D └ SW4D Control PVIN5 voltage data SW5D Control Ţ VOUT4 Error Amp VOUT5 ∰ SW4U Error Amp PWM P-skip SW5U VG +⊟ BT4U FB4 BT5U 🗀 COMP4 COMP5 <u>VIN</u> FB5 ONOFF – VG UVLO Startup Control VDDI VDDI (2.5V) VDDIMON (VDDIdet) Detection LION SCL 🗀 r ⊢ FREQ ADC SDA 🗀 Thermal Detection RST | OSC/Divider PGND (EXPAD) VIN AGND

Figure 2. 34704 Internal Block Diagram

# **PIN CONNECTIONS**

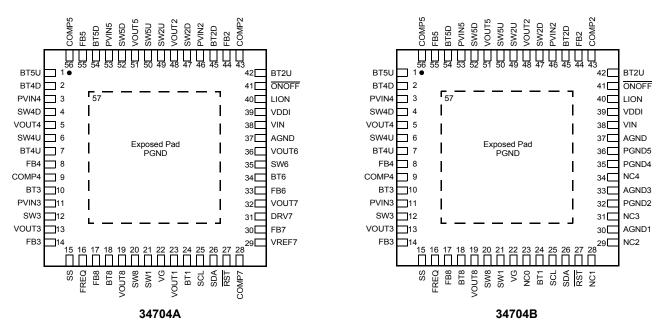

Figure 3. 34704 Pin Connections

Table 2. 34704 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number | Device | Pin Name | Pin Function | Formal Name                                                    | Definition                                                                                                                                                                                  |

|------------|--------|----------|--------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | A/B    | BT5U     | Passive      | REG5 Boost Stage<br>bootstrap capacitor input<br>pin           | Connect a 1.0 $\mu\text{F}$ capacitor between this pin and SW5U pin to enhance the gate of the Switch Power MOSFET.                                                                         |

| 2          | A/B    | BT4D     | Passive      | REG4 Buck Stage<br>bootstrap capacitor input<br>pin            | Connect a 0.01 $\mu\text{F}$ capacitor between this pin and SW4D pin to enhance the gate of the Switch Power MOSFET.                                                                        |

| 3          | A/B    | PVIN4    | Power        | REG4 power supply input voltage                                | This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG4 operation. Use a 10uf decoupling capacitor for better performance. |

| 4          | A/B    | SW4D     | Input/Output | REG4 Buck Stage switching node                                 | The inductor is connected between this pin and the SW4U pin.                                                                                                                                |

| 5          | A/B    | VOUT4    | Output       | REG4 regulated output voltage pin                              | Connect this pin to the load and to the output filter as close to the pin as possible.                                                                                                      |

| 6          | A/B    | SW4U     | Input/Output | REG4 Boost Stage switching node                                | The inductor is connected between this pin and the SW4D pin.                                                                                                                                |

| 7          | A/B    | BT4U     | Passive      | REG4 Boost Stage<br>bootstrap capacitor input<br>pin           | Connect a 0.01 $\mu\text{F}$ capacitor between this pin and SW4U pin to enhance the gate of the Switch Power MOSFET.                                                                        |

| 8          | A/B    | FB4      | Input        | REG4 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                          |

| 9          | A/B    | COMP4    | Passive      | REG4 compensation network connection                           | REG4 compensation network connection.                                                                                                                                                       |

| 10         | A/B    | ВТ3      | Passive      | REG3 bootstrap capacitor input pin                             | Connect a 0.01 $\mu\text{F}$ capacitor between this pin and SW3 pin to enhance the gate of the Switch Power MOSFET.                                                                         |

Table 2. 34704 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number        | Device | Pin Name | Pin Function | Formal Name                                                    | Definition                                                                                                                                                                                  |

|-------------------|--------|----------|--------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                | A/B    | PVIN3    | Power        | REG3 power supply input voltage                                | This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG3 operation. Use a 10uf decoupling capacitor for better performance. |

| 12                | A/B    | SW3      | Output       | REG3 switching node                                            | The inductor is connected between this pin and the regulated REG3 output.                                                                                                                   |

| 13                | A/B    | VOUT3    | Output       | REG3 output voltage return pin                                 | This is the discharge path of REG3 output voltage.                                                                                                                                          |

| 14                | A/B    | FB3      | Input        | REG3 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                          |

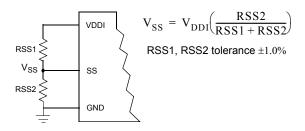

| 15                | A/B    | SS       | Input        | Soft start time                                                | The soft start time for all regulators can be adjusted by connecting this pin to an external resistor divider between VDDI and AGND pins.                                                   |

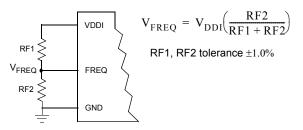

| 16                | A/B    | FREQ     | Input        | Oscillator frequency                                           | The oscillator frequency can be adjusted by connecting this pin to an external resistor divider between VDDI and AGND pins. This pin sets $F_{\text{SW1}}$ value.                           |

| 17                | A/B    | FB8      | Input        | REG8 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                          |

| 18                | A/B    | BT8      | Passive      | REG8 bootstrap capacitor input pin                             | Connect a 0.01 $\mu\text{F}$ capacitor between this pin and SW8 pin to enhance the gate of the Synchronous Power MOSFET.                                                                    |

| 19                | A/B    | VOUT8    | Output       | REG8 regulated output voltage pin                              | Connect this pin directly to the load directly and to the output filter as close to the pin as possible.                                                                                    |

| 20                | A/B    | SW8      | Output       | REG8 switching node                                            | The inductor is connected between this pin and the VIN pin.                                                                                                                                 |

| 21                | A/B    | SW1      | Output       | REG1 switching node                                            | The inductor is connected between this pin and the VIN Pin.                                                                                                                                 |

| 22                | A/B    | VG       | Passive      | REG1 regulated output voltage before the cutoff switch         | REG1 regulated output voltage before the cut-off switch. This supplies the internal circuits and the gate drive                                                                             |

| 23 <sup>(1)</sup> | Α      | VOUT1    | Output       | REG1 regulated output voltage pin.                             | Connect this pin directly to the load directly and to the output filter as close to the pin as possible.                                                                                    |

|                   | В      | NC0      | No Connect   | -                                                              | Pin 23 is not connected.                                                                                                                                                                    |

| 24                | A/B    | BT1      | Passive      | REG1 bootstrap capacitor input pin                             | Connect a 1.0 $\mu\text{F}$ capacitor between this pin and SW1 pin to enhance the gate of the Switch Power MOSFET.                                                                          |

| 25                | A/B    | SCL      | Input/Output | I <sup>2</sup> C serial interface clock input                  | I <sup>2</sup> C serial interface clock input.                                                                                                                                              |

| 26                | A/B    | SDA      | Input/Output | I <sup>2</sup> C serial interface data input                   | I <sup>2</sup> C serial interface data input.                                                                                                                                               |

| 27                | A/B    | RST      | Open Drain   | Power reset output signal (Microprocessor Reset)               | This is an open drain output and must be pulled up by an external resistor to a supply voltage like $V_{\rm IN}$ .                                                                          |

| 28                | Α      | COMP7    | Passive      | REG7 compensation network connection                           | REG7 compensation network connection.                                                                                                                                                       |

|                   | В      | NC1      | No Connect   | -                                                              | Pin 28 is not connected                                                                                                                                                                     |

| 29                | Α      | VREF7    | Output       | REG7 resistor feedback network reference voltage               | Connect this pin to the bottom of the feedback resistor divider.                                                                                                                            |

|                   | В      | NC2      | No Connect   | -                                                              | Pin 29 is not connected                                                                                                                                                                     |

# Table 2. 34704 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number | Device | Pin Name | Pin Function | Formal Name                                                    | Definition                                                                                                                                                                                 |

|------------|--------|----------|--------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30         | A      | FB7      | Input        | REG7 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                         |

|            | В      | AGND1    | -            | -                                                              | Pin 30 is connected to AGND                                                                                                                                                                |

| 31         | Α      | DRV7     | Output       | REG7 external Power<br>MOSFET gate drive                       | REG7 external Power MOSFET gate drive.                                                                                                                                                     |

|            | В      | NC3      | No Connect   | -                                                              | Pin 31 is not connected                                                                                                                                                                    |

| 32         | Α      | VOUT7    | Output       | REG7 output voltage return pin.                                | This is the discharge path of REG7 output voltage.                                                                                                                                         |

|            | В      | PGND1    | -            | -                                                              | Pin 32 is connected to PGND                                                                                                                                                                |

| 33         | А      | FB6      | Input        | REG6 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                         |

|            | В      | AGND2    | -            | -                                                              | Pin 33 is connected to AGND                                                                                                                                                                |

| 34         | Α      | BT6      | Passive      | REG6 bootstrap capacitor input pin.                            | Connect a 0.01 $\mu\text{F}$ capacitor between this pin and SW6 pin to enhance the gate of the Synchronous Power MOSFET.                                                                   |

|            | В      | NC4      | No Connect   | -                                                              | Pin 34 is not connected                                                                                                                                                                    |

| 35         | Α      | SW6      | Output       | REG6 switching node                                            | The inductor is connected between this pin and the VIN pin.                                                                                                                                |

|            | В      | PGND2    | -            | -                                                              | Pin 35 is connected to PGND                                                                                                                                                                |

| 36         | Α      | VOUT6    | Output       | REG6 regulated output voltage pin                              | Connect this pin directly to the load directly and to the output filter as close to the pin as possible.                                                                                   |

|            | В      | PGND3    | -            | -                                                              | Pin 36 is connected to PGND                                                                                                                                                                |

| 37         | A/B    | AGND     | Ground       | Analog ground of the IC                                        | Analog ground of the IC.                                                                                                                                                                   |

| 38         | A/B    | VIN      | Power        | Battery voltage connection                                     | Input decoupling /filtering is required for the device to operate properly.                                                                                                                |

| 39         | A/B    | VDDI     | Output       | Internal supply voltage                                        | Connect a 1.0 $\mu\text{F}$ low ESR decoupling filter capacitor between this pin and GND.                                                                                                  |

| 40         | A/B    | LION     | Input        | Battery Detection                                              | Always pull this pin High with a 470kohm Resistor to indicate Input power is present.                                                                                                      |

| 41         | A/B    | ONOFF    | Input        | Dual function IC turn On/<br>Off                               | This is a hardware enable/disable for the 34704A/B. It can be connected to a mechanical switch to turn the power On or Off.                                                                |

| 42         | A/B    | BT2U     | Passive      | REG2 Boost Stage<br>bootstrap capacitor input<br>pin           | Connect a 1.0 $\mu\text{F}$ capacitor between this pin and SW2U pin to enhance the gate of the Switch Power MOSFET.                                                                        |

| 43         | A/B    | COMP2    | Passive      | REG2 compensation network connection                           | REG2 compensation network connection.                                                                                                                                                      |

| 44         | A/B    | FB2      | Input        | REG2 voltage feedback input for voltage regulation/programming | Connect the feedback resistor divider to this pin.                                                                                                                                         |

| 45         | A/B    | BT2D     | Passive      | REG2 Buck Stage<br>bootstrap capacitor input<br>pin            | Connect a 1.0 $\mu\text{F}$ capacitor between this pin and SW2D pin to enhance the gate of the Switch Power MOSFET.                                                                        |

| 46         | A/B    | PVIN2    | Power        | REG2 power supply input voltage                                | This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG2 operation. Use a 10uf decoupling capacitor for better performance |

# Table 2. 34704 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number     | Device | Pin Name | Pin Function | Formal Name                                                         | Definition                                                                                                                                                                                 |

|----------------|--------|----------|--------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47             | A/B    | SW2D     | Input/Output | REG2 Buck Stage switching node                                      | The inductor is connected between this pin and the SW2U pin.                                                                                                                               |

| 48             | A/B    | VOUT2    | Output       | REG2 regulated output voltage pin                                   | Connect this pin to the load and to the output filter as close to the pin as possible.                                                                                                     |

| 49             | A/B    | SW2U     | Input/Output | REG2 Boost Stage switching node                                     | The inductor is connected between this pin and the SW2D pin.                                                                                                                               |

| 50             | A/B    | SW5U     | Input/Output | REG5 Boost Stage switching node                                     | The inductor is connected between this pin and the SW5D pin.                                                                                                                               |

| 51             | A/B    | VOUT5    | Output       | REG5 regulated output voltage pin                                   | Connect this pin to the load and to the output filter as close to the pin as possible.                                                                                                     |

| 52             | A/B    | SW5D     | Input/Output | REG5 Buck Stage switching node                                      | The inductor is connected between this pin and the SW5U pin.                                                                                                                               |

| 53             | A/B    | PVIN5    | Power        | REG5 power supply input voltage                                     | This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG5 operation. Use a 10uf decoupling capacitor for better performance |

| 54             | A/B    | BT5D     | Passive      | REG5 Buck Stage<br>bootstrap capacitor input<br>pin                 | Connect a 1.0 $\mu\text{F}$ capacitor between this pin and SW5D pin to enhance the gate of the Switch Power MOSFET.                                                                        |

| 55             | A/B    | FB5      | Input        | REG5 voltage feedback input for voltage regulation/programming      | Connect the feedback resistor divider to this pin.                                                                                                                                         |

| 56             | A/B    | COMP5    | Passive      | REG5 compensation network connection                                | REG5 compensation network connection.                                                                                                                                                      |

| Exposed<br>Pad | A/B    | PGND     | Ground       | Power Ground<br>Connection for all of the<br>regulators except REG7 | Power Ground Connection for all of the regulators except REG7. This pad is provided to enhance thermal performance.                                                                        |

- 1. If regulator 1 is not used, leave pin 23 Unconnected, All other components should be used to provide VG to the system

- 2. If regulators 5, 6, 7 and 8 are not used, connect the corresponding pins as follows: FB, SW and VOUT nodes: tied to GND; BT, COMP and PVIN pins: Not connected; DRV and VREF nodes (REG7 only): Not connected

- 3. REG 2,3 and 4 should always be populated.

### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                      | Symbol                           | Value        | Unit |

|------------------------------------------------------------------------------|----------------------------------|--------------|------|

| ELECTRICAL RATINGS                                                           | 1                                |              | · I  |

| Battery Input Supply Voltage (VIN) Pin                                       | V <sub>IN</sub>                  | -0.3 to 6.0  | V    |

| PVINx, RST, ONOFF, LION, DRV7 <sup>(8)</sup> , VG, SCL, SDA and VOUT1-5 Pins |                                  | -0.3 to 6.0  |      |

| VDDI, COMPx, FBx, VREF7 <sup>(8)</sup> , FREQ, and SS Pins                   |                                  | -0.3 to 3.0  |      |

| SW1-5 Pins                                                                   | V <sub>SW-LOW</sub>              | -1.0 to 6.0  | V    |

| SW8, SW6 <sup>(8)</sup> Pins                                                 | V <sub>SW-HIGH</sub>             | -1.0 to 27   | V    |

| BTx Pins (Referenced to switch node)                                         | V <sub>BT</sub> -V <sub>SW</sub> | -0.3 to 6.0  | V    |

| BTx Pins to GND                                                              | V <sub>BT</sub>                  | -0.3 to 27   | V    |

| VOUT8, VOUT6 <sup>(8)</sup> Pins                                             | V <sub>OUT-HIGH</sub>            | -0.3 to 27   | V    |

| VOUT7 Pin <sup>(8)</sup>                                                     | V <sub>OUT-NEG</sub>             | -10.0 to 0.3 | V    |

| Continuous Output Current                                                    |                                  |              | mA   |

| REG1 <sup>(8)</sup>                                                          |                                  | 500          |      |

| REG2,5                                                                       |                                  | 500          |      |

| REG3                                                                         |                                  | 550          |      |

| REG4<br>REG6.7 <sup>(8)</sup>                                                |                                  | 300<br>60    |      |

| REG8                                                                         |                                  | 30           |      |

| ESD Voltage                                                                  |                                  |              | V    |

| Human Body Model                                                             | V <sub>ESD1</sub>                | ±1000        |      |

| Charge Device Model                                                          | V <sub>ESD2</sub>                | ±500         |      |

| THERMAL RATINGS                                                              | 1                                |              | I    |

| Maximum Junction Temperature                                                 | $T_{J(MAX)}$                     | +150         | °C   |

| Storage Temperature                                                          | T <sub>STG</sub>                 | -65 to +150  | °C   |

| Maximum Power Dissipation (T <sub>A</sub> = 85°C)                            | PD                               | 2.5          | W    |

| THERMAL RESISTANCE <sup>(7)</sup>                                            | - I                              |              | I    |

| Thermal Resistance                                                           |                                  |              | °C/W |

| Junction to Ambient                                                          | $R_{\Theta JA}$                  | 26           |      |

| Junction to Board                                                            | R <sub>⊝JB</sub>                 | 10           |      |

| Peak Package Reflow Temperature During Reflow <sup>(5),(6)</sup>             | T <sub>PPRT</sub>                | Note 6       | °C   |

|                                                                              | ı L                              |              | 1    |

## Notes

- ESD testing is performed in accordance with the Human Body Model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), and the Charge Device Model (CDM), Robotic (C<sub>ZAP</sub> = 4.0 pF).

- 5. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 6. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 7. Thermal Resistance is based on a four-layer board (2s2p)

- 8. Available only on the 34704A

#### 34704

### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 4. Static Electrical Characteristics**

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                           | Symbol                   | Min  | Тур | Max | Unit |

|--------------------------------------------------------------------------|--------------------------|------|-----|-----|------|

| POWER INPUT                                                              |                          |      | •   |     | •    |

| Input Supply Voltage Typical Range                                       | $V_{IN}$                 | 2.7  | -   | 5.5 | V    |

| Input DC Supply Current <sup>(9)</sup>                                   | I <sub>IN</sub>          |      |     |     | mA   |

| VIN Pin Only                                                             |                          | -    | -   | -   |      |

| All regulators are ON, no load; $V_{IN}$ = 3.6 V, FSW =1.0 MHz           |                          | -    | 86  | -   |      |

| Regulators 1 - 5 On, Reg 6, 7 and 8 Off; $V_{IN}$ = 3.6 V, FSW = 1.0 MHz |                          | -    | 32  | -   |      |

| Input DC Shutdown Supply Current <sup>(9)</sup>                          | I <sub>OFF</sub>         |      |     |     | μА   |

| (Shutdown, All regulators are OFF and $V_{IN}$ = 5.5V)                   |                          | -    | -   | 5.0 |      |

| This includes any pin connected to the battery                           |                          |      |     |     |      |

| Rising UVLO Threshold                                                    | UVLO <sub>R</sub>        | -    | -   | 3.0 | V    |

| Falling UVLO Threshold                                                   | UVLO <sub>F</sub>        | -    | -   | 2.7 | V    |

| RST                                                                      |                          |      |     | •   | •    |

| RST Low Level Output Voltage                                             | V <sub>RST-OL</sub>      |      |     |     | V    |

| I <sub>OL</sub> = 1.0 mA                                                 |                          | -    | -   | 0.4 |      |

| RST Leakage Current, Off-state @ 25°C                                    | I <sub>RST-LKG</sub>     | -    | -   | 1.0 | μА   |

| Current Limit Monitoring                                                 |                          |      |     | •   | •    |

| Over and Short-circuit Current Limit Accuracy                            | -                        | -20  | -   | 20  | %    |

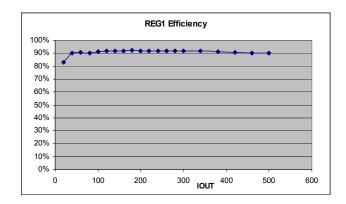

| REGULATOR 1 & VG                                                         |                          |      |     |     |      |

| VG Output Voltage                                                        | $V_{VG}$                 | -    | 5.0 | -   | V    |

| REG1 Output Voltage <sup>(10)</sup>                                      | V <sub>OUT</sub>         | -    | 5.0 | -   | V    |

| Output Accuracy                                                          | -                        | -4.0 | -   | 4.0 | %    |

| Line/Load Regulation <sup>(9)</sup>                                      | REG <sub>LN/LD</sub>     | -1.0 | -   | 1.0 | %    |

| Dynamic Voltage Scaling Range                                            | $V_{DYN}$                | -10  | -   | 10  | %    |

| Dynamic Voltage Scaling Step Size                                        | V <sub>DYN_STEP</sub>    | -    | 2.5 | -   | %    |

| Continuous Output Current <sup>(9)</sup>                                 | I <sub>OUT</sub>         | -    | 100 | 500 | mA   |

| Overcurrent Limit (Detected in Low-side FET)                             | I <sub>LIM_ION</sub>     | -    | 2.7 | -   | А    |

| Short-circuit Current Limit (Detected in the Blocking FET)               | I <sub>SHORT_ION</sub>   | -    | 4.0 | -   | Α    |

| Overcurrent Limit Accuracy                                               | -                        | -20  | -   | 20  | %    |

| N-CH Switch Power MOSFET R <sub>DS(on)</sub>                             | R <sub>DS(on)</sub> -SW  | -    | 100 | -   | mΩ   |

| N-CH Synch. Power MOSFET R <sub>DS(on)</sub>                             | R <sub>DS(on)</sub> -SY  | -    | 150 | -   | mΩ   |

| N-CH Shutdown Power MOSFET R <sub>DS(on)</sub>                           | R <sub>DS(on)</sub> -SH  | -    | 100 | -   | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                                     | R <sub>DS(on)</sub> -DIS | -    | 70  | -   | Ω    |

| Thermal Shutdown Threshold <sup>(9)</sup>                                | T <sub>SD</sub>          | -    | 170 | -   | °C   |

| Thermal Shutdown Hysteresis <sup>(9)</sup>                               | T <sub>SD-HYS</sub>      | -    | 25  | -   | °C   |

| SW1 Leakage Current (Off State) @ 25°C                                   | I <sub>SW1_LKG</sub>     | -    | -   | 1.0 | μА   |

| Peak Current Detection Threshold at Power Up <sup>(9)</sup>              | I <sub>PEAK</sub>        | -    | 300 | -   | mA   |

- 9. Guaranteed by Design

- 10. Available only on the 34704A

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                               | Symbol                   | Min   | Тур                   | Max  | Unit |

|--------------------------------------------------------------|--------------------------|-------|-----------------------|------|------|

| REGULATOR 2                                                  | •                        |       |                       |      |      |

| Output Voltage Range                                         | V <sub>OUT</sub>         | 0.6   | 3.3                   | 3.6  | V    |

| Output Accuracy                                              | -                        | -2.0  | -                     | 2.0  | %    |

| Line/Load Regulation <sup>(11)</sup>                         | REG <sub>LN/LD</sub>     | -1.0  | -                     | 1.0  | %    |

| Feedback Reference Voltage                                   | V <sub>FB</sub>          | -     | 0.600 <sup>(12)</sup> | -    | V    |

| Dynamic Voltage Scaling Range                                | $V_{DYN}$                | -17.5 | -                     | 17.5 | %    |

| Dynamic Voltage Scaling Step Size                            | V <sub>DYN_STEP</sub>    | -     | 2.5                   | -    | %    |

| Continuous Output Current <sup>(11)</sup>                    | I <sub>OUT</sub>         | -     | 200                   | 500  | mA   |

| Overcurrent Limit (Detected in buck high-side FET)           | I <sub>LIM_ION</sub>     | -     | 1.4                   | -    | Α    |

| Short-circuit Current Limit (Detected in buck high-side FET) | I <sub>SHORT_ION</sub>   | -     | 2.1                   | -    | Α    |

| Battery Overcurrent Limit Accuracy                           | -                        | -20   | -                     | 20   | %    |

| N-CH Buck Switch Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -SW  | -     | 120                   | -    | mΩ   |

| N-CH Buck Synch. Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -SY  | -     | 1000                  | -    | mΩ   |

| N-CH Boost Switch Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> -SW  | -     | 120                   | -    | mΩ   |

| N-CH Boost Synch. Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> -SY  | -     | 120                   | -    | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                         | R <sub>DS(on)</sub> -DIS | -     | 70                    | -    | Ω    |

| Thermal Shutdown Threshold <sup>(11)</sup>                   | T <sub>SD</sub>          | -     | 170                   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>(11)</sup>                  | T <sub>SD-HYS</sub>      | -     | 25                    | -    | °C   |

| PVIN2 Leakage Current (Off State) @25°C                      | I <sub>PVIN2G_LKG</sub>  | -     | -                     | 1.0  | μΑ   |

| SW2D Leakage Current (Off State) @25°C                       | I <sub>SW2D_LKG</sub>    | -     | -                     | 1.0  | μΑ   |

| SW2U Leakage Current (Off State) @25°C                       | I <sub>SW2U_LKG</sub>    | -     | -                     | 1.0  | μΑ   |

| REGULATOR 3                                                  |                          |       |                       |      | •    |

| Output Voltage Range                                         | V <sub>OUT</sub>         | 0.6   | 1.2                   | 1.8  | V    |

| Output Accuracy                                              | -                        | -4.0  | -                     | 4.0  | %    |

| Line/Load Regulation <sup>(11)</sup>                         | REG <sub>LN/LD</sub>     | -1.0  | -                     | 1.0  | %    |

| Feedback Reference Voltage                                   | $V_{FB}$                 | -     | 0.600 <sup>(12)</sup> | -    | V    |

| Dynamic Voltage Scaling Range                                | $V_{DYN}$                | -17.5 | -                     | 17.5 | %    |

| Dynamic Voltage Scaling Step Size                            | V <sub>DYN_STEP</sub>    | -     | 2.5                   | -    | %    |

| Continuous Output Current <sup>(11)</sup>                    | I <sub>OUT</sub>         | -     | 150                   | 550  | mA   |

| Overcurrent Limit (Detected in buck high-side FET)           | I <sub>LIM_ION</sub>     | -     | 1.0                   | -    | Α    |

| Short-circuit Current Limit (Detected in buck high-side FET) | I <sub>SHORT_ION</sub>   | -     | 1.5                   | -    | Α    |

| Overcurrent Limit Accuracy                                   | -                        | -20   | -                     | 20   | %    |

| N-CH Switch Power MOSFET R <sub>DS(on)</sub>                 | R <sub>DS(on)</sub> -SW  | -     | 500                   | -    | mΩ   |

| N-CH Synch. Power MOSFET R <sub>DS(on)</sub>                 | R <sub>DS(on)</sub> -sy  | -     | 500                   | -    | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                         | R <sub>DS(on)</sub> -DIS | -     | 70                    | -    | Ω    |

| Thermal Shutdown Threshold (11)                              | T <sub>SD</sub>          | -     | 170                   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>(11)</sup>                  | T <sub>SD-HYS</sub>      | -     | 25                    | -    | °C   |

| PVIN3 Leakage Current (Off State) @25°C                      | I <sub>PVIN3_LKG</sub>   | -     | -                     | 1.0  | μА   |

| SW3 Leakage Current (Off State) @25°C                        | I <sub>SW3_LKG</sub>     | -     | -                     | 1.0  | μА   |

|                                                              |                          |       |                       |      |      |

- 11. Guaranteed by Design

- 12.  $V_{FB}$  is 0.6V when the part is powered up and no DVS is changed. DVS is achieved by modifying  $V_{FB}$  reference.

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                               | Symbol                              | Min   | Тур                   | Max  | Unit |

|--------------------------------------------------------------|-------------------------------------|-------|-----------------------|------|------|

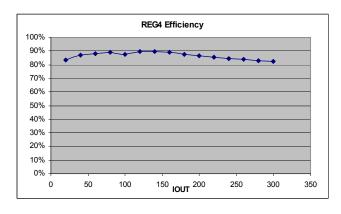

| REGULATOR 4                                                  |                                     |       |                       |      | •    |

| Output Voltage Range                                         | V <sub>OUT</sub>                    | 0.6   | 1.8                   | 3.6  | V    |

| Output Accuracy                                              | -                                   | -2.0  | -                     | 2.0  | %    |

| Line/Load Regulation <sup>(13)</sup>                         | REG <sub>LN/LD</sub>                | -1.0  | -                     | 1.0  | %    |

| Feedback Reference Voltage                                   | $V_{FB}$                            | -     | 0.600 <sup>(14)</sup> | -    | V    |

| Dynamic Voltage Scaling Range                                | $V_{DYN}$                           | -10   | -                     | 10   | %    |

| Dynamic Voltage Scaling Step Size                            | V <sub>DYN_STEP</sub>               | -     | 1.0                   | -    | %    |

| Continuous Output Current <sup>(13)</sup>                    | I <sub>OUT</sub>                    | -     | 100                   | 300  | mA   |

| Overcurrent Limit (Detected in buck high-side FET)           | I <sub>LIM_ION</sub>                | -     | 1.5                   | -    | Α    |

| Short-circuit Current Limit (Detected in buck high-side FET) | I <sub>SHORT_ION</sub>              | -     | 2.25                  | -    | Α    |

| Overcurrent Limit Accuracy                                   | -                                   | -20   | -                     | 20   | %    |

| N-CH Buck Switch Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -SW             | -     | 200                   | -    | mΩ   |

| N-CH Buck Synch. Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -sy             | -     | 600                   | -    | mΩ   |

| N-CH Boost Switch Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> - <sub>SW</sub> | -     | 200                   | -    | mΩ   |

| N-CH Boost Synch. Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> -sy             | -     | 600                   | -    | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                         | R <sub>DS(on)</sub> -DIS            | -     | 70                    | -    | Ω    |

| Thermal Shutdown Threshold <sup>(13)</sup>                   | T <sub>SD</sub>                     | -     | 170                   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>(13)</sup>                  | T <sub>SD-HYS</sub>                 | -     | 25                    | -    | °C   |

| PVIN4 Leakage Current (Off State) @25°C                      | I <sub>PVIN4_LKG</sub>              | -     | -                     | 1.0  | μΑ   |

| SW4D Leakage Current (Off State) @25°C                       | I <sub>SW4D_LKG</sub>               | -     | -                     | 1.0  | μΑ   |

| SW4U Leakage Current (Off State) @25°C                       | I <sub>SW4U_LKG</sub>               | -     | -                     | 1.0  | μА   |

| REGULATOR 5                                                  |                                     |       |                       |      | •    |

| Output Voltage Range                                         | V <sub>OUT</sub>                    | 0.6   | 3.3                   | 3.6  | V    |

| Output Accuracy                                              | -                                   | -2.0  | -                     | 2.0  | %    |

| Line/Load Regulation <sup>(13)</sup>                         | REG <sub>LN/LD</sub>                | -1.0  | -                     | 1.0  | %    |

| Feedback Reference Voltage                                   | $V_{FB}$                            | -     | 0.600 <sup>(14)</sup> | -    | V    |

| Dynamic Voltage Scaling Range                                | $V_{DYN}$                           | -17.5 | -                     | 17.5 | %    |

| Dynamic Voltage Scaling Step Size                            | V <sub>DYN_STEP</sub>               | -     | 2.5                   | -    | %    |

| Continuous Output Current <sup>(13)</sup>                    | I <sub>OUT</sub>                    | -     | 150                   | 500  | mA   |

| Overcurrent Limit (Detected in buck high-side FET)           | I <sub>LIM_ION</sub>                | -     | 1.4                   | -    | Α    |

| Short-circuit Current Limit (Detected in buck high-side FET) | I <sub>SHORT_ION</sub>              | -     | 2.1                   | -    | Α    |

| Overcurrent Limit Accuracy                                   | -                                   | -20   | -                     | 20   | %    |

| N-CH Buck Switch Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -sw             | -     | 120                   | -    | mΩ   |

| N-CH Buck Synch. Power MOSFET R <sub>DS(on)</sub>            | R <sub>DS(on)</sub> -SY             | -     | 1000                  | -    | mΩ   |

| N-CH Boost Switch Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> -sw             | -     | 120                   | -    | mΩ   |

| N-CH Boost Synch. Power MOSFET R <sub>DS(on)</sub>           | R <sub>DS(on)</sub> -SY             | -     | 120                   | -    | mΩ   |

| Discharge MOSFET R <sub>DS(on)</sub>                         | R <sub>DS(on)</sub> -DIS            | -     | 70                    | -    | Ω    |

| Thermal Shutdown Threshold <sup>(13)</sup>                   | T <sub>SD</sub>                     | -     | 170                   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>(13)</sup>                  | T <sub>SD-HYS</sub>                 | -     | 25                    | -    | °C   |

- 13. Guaranteed by Design

- 14.  $V_{FB}$  is 0.6V when the part is powered up and no DVS is changed. DVS is achieved by modifying  $V_{FB}$  reference.

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                  | Symbol                           | Min  | Тур                   | Max  | Unit |

|-----------------------------------------------------------------|----------------------------------|------|-----------------------|------|------|

| PVIN5 Leakage Current (Off State) @25°C                         | I <sub>PVIN5_LKG</sub>           | -    | -                     | 1.0  | μΑ   |

| SW5D Leakage Current (Off State) @25°C                          | I <sub>SW5D LKG</sub>            | -    | -                     | 1.0  | μΑ   |

| SW5U Leakage Current (Off State) @25°C                          | I <sub>SW5U_LKG</sub>            | -    | -                     | 1.0  | μΑ   |

| REGULATOR 6 <sup>(16)</sup>                                     |                                  |      |                       |      |      |

| Output Voltage Range                                            | V <sub>OUT</sub>                 | 5.0  | 15                    | 15   | V    |

| Output Accuracy                                                 | -                                | -4.0 | -                     | 4.0  | %    |

| Line/Load Regulation <sup>(15)</sup>                            | REG <sub>LN/LD</sub>             | -1.0 | -                     | 1.0  | %    |

| Feedback Reference Voltage                                      | V <sub>FB</sub>                  | -    | 0.600 <sup>(17)</sup> | -    | V    |

| Dynamic Voltage Scaling Range                                   | $V_{DYN}$                        | -10  | -                     | 10   | %    |

| Dynamic Voltage Scaling Step Size                               | V <sub>DYN_STEP</sub>            | -    | 2.5                   | -    | %    |

| Continuous Output Current <sup>(15)</sup>                       | I <sub>OUT</sub>                 | -    | 50                    | 60   | mA   |

| Overcurrent Limit (Detected in low-side FET)                    | I <sub>LIM_ION</sub>             | -    | 3.0                   | -    | Α    |

| Short-circuit Current Limit (Detected in the Blocking FET)      | I <sub>SHORT ION</sub>           | -    | 4.5                   | -    | Α    |

| Overcurrent Limit Accuracy                                      | -                                | -20  | -                     | 20   | %    |

| N-CH Switch Power MOSFET R <sub>DS(on)</sub>                    | R <sub>DS(on)</sub> -sw          | -    | 200                   | -    | mΩ   |

| N-CH Synch. Power MOSFET R <sub>DS(on)</sub>                    | R <sub>DS(on)</sub> -SY          | -    | 600                   | -    | mΩ   |

| N-CH Shutdown Power MOSFET R <sub>DS(on)</sub>                  | R <sub>DS(on)</sub> -SH          | -    | 200                   | -    | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                            | R <sub>DS(on)</sub> -DIS         | -    | 70                    | -    | Ω    |

| Thermal Shutdown Threshold <sup>(15)</sup>                      | T <sub>SD</sub>                  | -    | 170                   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>(15)</sup>                     | T <sub>SD-HYS</sub>              | -    | 25                    | -    | °C   |

| SW6 Leakage Current (Off State) @25°C                           | I <sub>SW6_LKG</sub>             | -    | -                     | 1.0  | μА   |

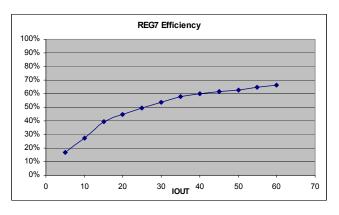

| REGULATOR 7 <sup>(16)</sup>                                     |                                  |      | '                     |      | •    |

| Output Voltage Range                                            | V <sub>OUT</sub>                 | -5.0 | -7.0                  | -9.0 | V    |

| Output Accuracy                                                 | -                                | -2.0 | -                     | 2.0  | %    |

| Line/Load Regulation <sup>(15)</sup>                            | REG <sub>LN/LD</sub>             | -1.0 | -                     | 1.0  | %    |

| Feedback Reference Voltage                                      | $V_{FB}$                         | -    | 0.600 <sup>(17)</sup> | -    | V    |

| Continuous Output Current <sup>(15)</sup>                       | I <sub>OUT</sub>                 | -    | 50                    | 60   | mA   |

| Discharge MOSFET R <sub>DS(on)</sub>                            | R <sub>DS(on)</sub> -DIS         | -    | 55                    | -    | Ω    |

| Gate Drive Voltage High Level (@ -50 mA, V <sub>IN</sub> =3.6V) | V <sub>IN</sub> -V <sub>OH</sub> | -    | 0.8                   | 1.4  | V    |

| Gate Drive Voltage Low Level (@ 50 mA, V <sub>IN</sub> =3.6V)   | V <sub>OL</sub>                  | -    | 1.1                   | 1.8  | V    |

| VREF7 Output Voltage                                            | V <sub>REF7</sub>                | -    | 1.5                   | -    | V    |

| VREF7 Voltage Accuracy                                          | -                                | 1.43 | -                     | 1.57 | V    |

| VREF7 Output Load Regulation (10 μA to 1.0 mA)                  | REG <sub>LD</sub>                | 1.43 | -                     | 1.57 | V    |

- 15. Guaranteed by Design

- 16. Available only on the 34704A

- 17.  $V_{FB}$  is 0.6V when the part is powered up and no DVS is changed. DVS is achieved by modifying  $V_{FB}$  reference.

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                             | Symbol                   | Min                 | Тур                   | Max | Unit |

|------------------------------------------------------------|--------------------------|---------------------|-----------------------|-----|------|

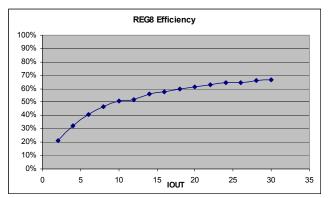

| REGULATOR 8                                                |                          |                     |                       |     |      |

| Output Voltage Range                                       | V <sub>OUT</sub>         | 5.0 <sup>(19)</sup> | 15                    | 15  | V    |

| Output Accuracy                                            | -                        | -4.0                | -                     | 4.0 | %    |

| Feedback Reference Voltage                                 | V <sub>FB</sub>          | -                   | 0.600 <sup>(20)</sup> | -   | V    |

| Feedback Reference Voltage on current regulation mode      | V <sub>FB</sub>          | -                   | 0.230 <sup>(21)</sup> | -   | V    |

| Dynamic Voltage Scaling Range                              | $V_{DYN}$                | -10                 | -                     | 10  | %    |

| Dynamic Voltage Scaling Step Size                          | V <sub>DYN_STEP</sub>    | -                   | 2.5                   | -   | %    |

| Line/Load Regulation <sup>(18)</sup>                       | REG <sub>LN/LD</sub>     | -1.0                | -                     | 1.0 | %    |

| Continuous Output Current <sup>(18)</sup>                  | I <sub>OUT</sub>         | -                   | 15                    | 30  | mA   |

| Overcurrent Limit (Detected in low-side FET)               | I <sub>LIM_ION</sub>     | -                   | 1.0                   | -   | Α    |

| Short-circuit Current Limit (Detected in the Blocking FET) | I <sub>SHORT_ION</sub>   | -                   | 1.5                   | -   | Α    |

| Overcurrent Limit Accuracy                                 | -                        | -20                 | -                     | 20  | %    |

| N-CH Switch Power MOSFET R <sub>DS(on)</sub>               | R <sub>DS(on)</sub> -SW  | -                   | 450                   | -   | mΩ   |

| N-CH Synch. Power MOSFET R <sub>DS(on)</sub>               | R <sub>DS(on)</sub> -SY  | -                   | 1000                  | -   | mΩ   |

| N-CH Shutdown Power MOSFET R <sub>DS(on)</sub>             | R <sub>DS(on)</sub> -SH  | -                   | 450                   | -   | mΩ   |

| Discharge MOSFET R <sub>DS(ON)</sub>                       | R <sub>DS(on)</sub> -DIS | -                   | 70                    | -   | Ω    |

| Thermal Shutdown Threshold <sup>(18)</sup>                 | T <sub>SD</sub>          | -                   | 170                   | -   | °C   |

| Thermal Shutdown Hysteresis <sup>(18)</sup>                | T <sub>SD-HYS</sub>      | -                   | 25                    | -   | °C   |

| SW8 Leakage Current (Off State) @25°C                      | I <sub>SW8_LKG</sub>     | -                   | -                     | 1.0 | μА   |

- 18. Guaranteed by Design

- When Battery voltage is higher than 5.0V and VOUT8 is 5.0V, a polarization diode is necessary to achieve accurate output voltage. See Component Calculation on page 39 for further details.

- 20.  $V_{FB}$  is 0.6V when the part is powered up and no DVS is changed. DVS is achieved by modifying  $V_{FB}$  reference.

- 21. When in Current regulation mode, the Voltage reference is set to 0.230mV to set the maximum current, and it is internally decreased to achieve a factor of the maximum current passing through the LED string

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

### **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                             | Symbol                 | Min | Тур  | Max  | Unit |

|--------------------------------------------|------------------------|-----|------|------|------|

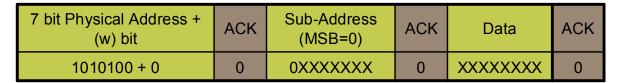

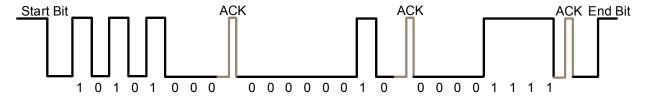

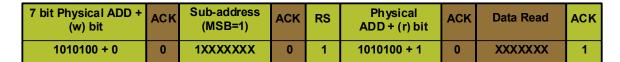

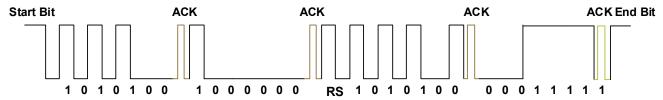

| <sup>2</sup> C COMMUNICATION               |                        |     |      |      |      |

| Device Physical Address (7 bit Address)    |                        | -   | \$54 | -    |      |

| Maximum I <sup>2</sup> C Speed             |                        | -   | -    | 400  | kHz  |

| FREQ                                       | ,                      |     | •    |      |      |

| Selectable Switching Frequency 1           | f <sub>SW1</sub>       | 750 | -    | 2000 | kHz  |

| Selectable Switching Frequency 2           | f <sub>SW2</sub>       | 250 | -    | 1000 | kHz  |

| Selectable Switching Frequency Step Size   | f <sub>STEP</sub>      | -   | 250  | -    | kHz  |

| Switching Frequency Accuracy               |                        | -10 | -    | 10   | %    |

| Retry Timeout Period <sup>(23)</sup>       | t <sub>TIMEOUT</sub>   | -   | 10   | -    | ms   |

| CURRENT LIMIT MONITORING                   |                        |     |      |      |      |

| Overcurrent Limit Timer <sup>(23)</sup>    | t <sub>LIMIT</sub>     | -   | 10   | -    | ms   |

| Retry Timeout Period <sup>(23)</sup>       | t <sub>RETRY</sub>     | -   | 10   | -    | ms   |

| OUTPUT OVERVOLTAGE/UNDERVOLTAGE MONITORING | ,                      |     | •    |      |      |

| Undervoltage Threshold (Response A)        | V <sub>UV-R</sub>      | -   | -20  | -    | %    |

| Overvoltage Threshold (Response A)         | V <sub>OV-R</sub>      | -   | 20   | -    | %    |

| Undervoltage Threshold (Response B)        | V <sub>UV-R</sub>      | -   | -20  | -    | %    |

| Overvoltage Threshold (Response B)         | V <sub>OV-R</sub>      | -   | 20   | -    | %    |

| Filter Delay Timer <sup>(23)</sup>         | t <sub>FILTER</sub>    | -   | 20   | -    | μS   |

| RST                                        |                        |     |      |      |      |

| RST Reset Delay <sup>(23)</sup>            | t <sub>RST-DELAY</sub> | -   | 10   |      | ms   |

| REGULATOR 1 & VG                           |                        |     |      |      |      |

| Operating Frequency <sup>(22), (23)</sup>  | f <sub>SW1</sub>       | 750 | -    | 1500 | kHz  |

| Operating Frequency Selection Step Size    | f <sub>STEP</sub>      | -   | 250  | -    | kHz  |

| Constant Time Off Value <sup>(23)</sup>    | t <sub>OFF</sub>       | -   | 1.0  | -    | μS   |

| Low-side Timeout <sup>(23)</sup>           | t <sub>TIMEOUT</sub>   | -   | 15   | -    | μS   |

| REGULATOR 2                                | ,                      |     | •    | •    |      |

| Operating Frequency <sup>(23)</sup>        | f <sub>SW1</sub>       | 750 | -    | 2000 | kHz  |

| Operating Frequency Selection Step Size    | f <sub>STEP</sub>      | -   | 250  | -    | kHz  |

|                                            |                        |     | 1    |      |      |

- 22. When REG1 is used, the maximum  $f_{SW1}$  Frequency programed with external components should be 1500 kHz

- 23. Guaranteed by design.

# **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                          | Symbol            | Min | Тур | Max  | Unit |

|-----------------------------------------|-------------------|-----|-----|------|------|

| REGULATOR 3                             | 1                 |     |     | •    |      |

| Operating Frequency                     | f <sub>SW1</sub>  | 750 | -   | 2000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

| REGULATOR 4                             | <u>.</u>          |     |     |      |      |

| Operating Frequency                     | f <sub>SW1</sub>  | 750 | -   | 2000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

| REGULATOR 5                             |                   |     |     |      |      |

| Operating Frequency                     | f <sub>SW1</sub>  | 750 | -   | 2000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

| REGULATOR 6                             |                   |     |     |      |      |

| Operating Frequency                     | f <sub>SW2</sub>  | 250 | -   | 1000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

| REGULATOR 7                             |                   |     |     |      |      |

| Operating Frequency Selections          | f <sub>SW2</sub>  | 250 | -   | 1000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

| REGULATOR 8                             |                   |     |     |      |      |

| Operating Frequency                     | f <sub>SW2</sub>  | 250 | -   | 1000 | kHz  |

| Operating Frequency Selection Step Size | f <sub>STEP</sub> | -   | 250 | -    | kHz  |

# **FUNCTIONAL DESCRIPTION**

#### **INTRODUCTION**

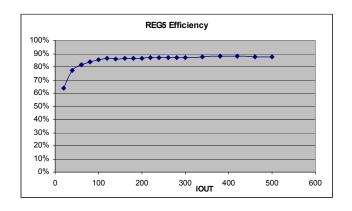

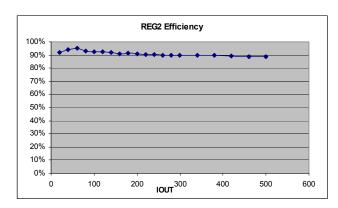

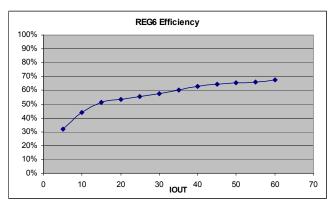

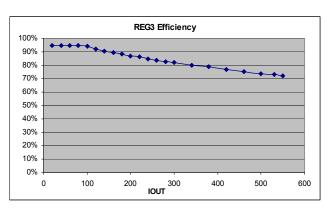

The 34704 is an multi-channel power management IC (PMIC) meant to address power management needs for various multimedia applications microprocessors in various configurations with a target overall efficiency of > 80% at typical loads.

The 34704 accepts an input voltage from various sources:

- •1 cell Li-Ion/Polymer (2.7 to 4.2 V)

- •5.0 V USB supply or AC wall adapter

The different channels are:

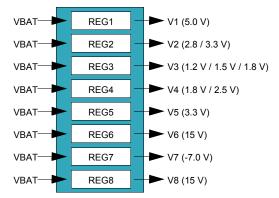

| REGULATOR            | REGULATOR TYPE         | V <sub>OUT</sub> TYP (V) | I <sub>OUT</sub> TYP (MA) | I <sub>OUT</sub> MAX (MA) | TARGET APPLICATION |

|----------------------|------------------------|--------------------------|---------------------------|---------------------------|--------------------|

| REG1 <sup>(25)</sup> | Synchronous Boost      | 5.0                      | 100                       | 500                       | +5.0 V REF         |

| REG2                 | Synchronous Buck-Boost | 2.8 / 3.3                | 200                       | 500                       | μP I/O             |

| REG3                 | REG3 Synchronous Buck  |                          | 150                       | 550                       | μP Core            |

| REG4                 | Synchronous Buck-Boost | 1.8 / 2.5                | 100                       | 300                       | DDR                |

| REG5                 | Synchronous Buck-Boost | 3.3                      | 150                       | 500                       | μP I/O             |

| REG6 <sup>(25)</sup> | Synchronous Boost      | 15.0                     | 20                        | 60                        | REF+               |

| REG7 <sup>(25)</sup> | Inverter Boost         | -7.0                     | 20                        | 60                        | REF -              |

| REG8                 | Synchronous Boost      | 15.0                     | 15                        | 30                        | Backlight Display  |

#### Notes

- 24. Synchronous Buck-Boost: These regulators can work as pure BUCK regulator when the output voltage is lower than the input voltage; and work as pure BOOST regulator when the input voltage is lower than the output voltage. Compensation should be done for the worst case scenario, which is in most of the cases when the device is working as a boost converter, after compensating for this scenario it is recommended to verify the buck operation to assure stability in the whole operating range.

- 25. Available only on the 34704A

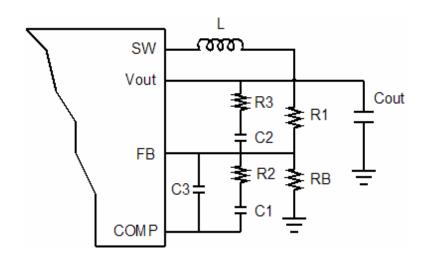

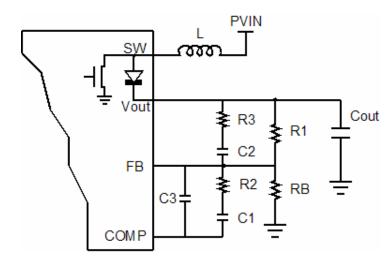

REG1, REG3, REG6, and REG8 use internal compensation, while REG2, REG4, REG5, and REG7 use external compensation.

The switching frequency of all regulators except REG6, 7, & 8 can be selected through the FREQ pin between 750 kHz and 2.0 MHz in 250 kHz steps. The high frequency operation is meant to minimize the size of external components while lower operating frequencies will allow for higher efficiency. REG7 is limited to operate at a lower frequency to minimize switching noise induced by driving the external switching MOSFET, but also can operate at the 1.0 MHz value with proper board layout. REG 6, 7, and 8 switching frequency can be selected between 250 kHz and 1.0 MHz in 250 kHz steps through  $\rm I^2C$ .

For all regulators and at lower loads, a pulse skipping mode is implemented to maintain high efficiency.

Note that pulse skipping occurs when the regulator enters into discontinuous conduction mode (DCM) at very light loads, however transitions between DCM and CCM may result in noisy switching nodes, therefore it is recommended to design the regulators to work in CCM all the time. Pulse skipping function is not guaranteed by circuit implementation. The 34704 uses 4 different phases of switching for all

regulators except REG6, 7, and 8, to spread out the current draw by the individual converters from the input supply over time, to reduce the peak input current demand. This allows for better EMI performance and reduction in the input filter requirements.

Each regulator except REG1 uses an external feedback resistor divider to set the output voltage. All output voltages can be adjusted dynamically (Dynamic Voltage Scaling) on the fly through an I<sup>2</sup>C serial interface. All converters, except REG1, utilize automatic soft-start by ramping the reference voltage to the error amplifier to prevent sudden change in duty cycle and output current/voltage at power up. REG1 (VG) will limit the inrush current by implementing a peak current detect and a constant off time.

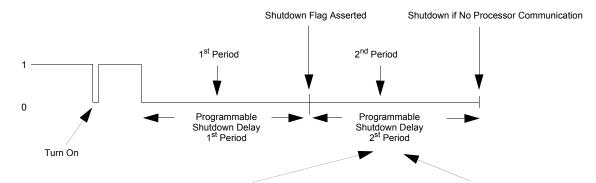

The 34704 is equipped with a dual function Power On/Off pin (ONOFF). This pin can be controlled by a mechanical switch to turn the device on or off. Pressing and releasing the mechanical switch turns the 34704 on while pressing and holding the switch for a time period (programmable through  $\rm I^2C$ ) turns the 34704 off. Enable/disable control is also granted through  $\rm I^2C$  for groups of regulators and the whole IC.

#### **FUNCTIONAL PIN DESCRIPTION**

# REG5 BOOST STAGE BOOTSTRAP CAPACITOR INPUT PIN (BT5U)

Connect a 1.0  $\mu$ F capacitor between this pin and SW5U pin to enhance the gate of the Switch Power MOSFET.

# REG4 BUCK STAGE BOOTSTRAP CAPACITOR INPUT PIN (BT4D)

Connect a 0.01  $\mu$ F capacitor between this pin and SW4D pin to enhance the gate of the Switch Power MOSFET.

### **REG4 POWER SUPPLY INPUT VOLTAGE (PVIN4)**

This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG4 operation.

### **REG4 BUCK STAGE SWITCHING NODE (SW4D)**

The inductor is connected between this pin and the SW4U pin.

# REG4 REGULATED OUTPUT VOLTAGE PIN (VOUT4)

Connect this pin to the load and to the output filter as close to the pin as possible.

#### **REG4 BOOST STAGE SWITCHING NODE (SW4U)**

The inductor is connected between this pin and the SW4D pin.

# REG4 BOOST STAGE BOOTSTRAP CAPACITOR INPUT PIN (BT4U)

Connect a 0.01  $\mu$ F capacitor between this pin and SW4U pin to enhance the gate of the Switch Power MOSFET.

# REG4 VOLTAGE FEEDBACK INPUT FOR VOLTAGE REGULATION/PROGRAMMING (FB4)

Connect the feedback resistor divider to this pin.

# REG4 COMPENSATION NETWORK CONNECTION (COMP4)

REG4 compensation network connection.

#### **REG3 BOOTSTRAP CAPACITOR INPUT PIN (BT3)**

Connect a 0.01  $\mu\text{F}$  capacitor between this pin and SW3 pin to enhance the gate of the Switch Power MOSFET.

# **REG3 POWER SUPPLY INPUT VOLTAGE (PVIN3)**

This is the connection to the drain of the high-side switch FET. Input decoupling /filtering is required for proper REG3 operation.

# **REG3 SWITCHING NODE (SW3)**

The inductor is connected between this pin and the regulated REG3 output.

#### **REG3 OUTPUT VOLTAGE RETURN PIN (VOUT3)**

This is the discharge path of REG3 output voltage.

# REG3 VOLTAGE FEEDBACK INPUT FOR VOLTAGE REGULATION/PROGRAMMING (FB3)

Connect the feedback resistor divider to this pin.

# **SOFT START TIME (SS)**

The soft start time for all regulators can be adjusted by connecting this pin to an external resistor divider between VDDI and AGND pins.

#### **OSCILLATOR FREQUENCY (FREQ)**

The oscillator frequency can be adjusted by connecting this pin to an external resistor divider between VDDI and AGND pins. This pin sets  $F_{SW1}$  value.

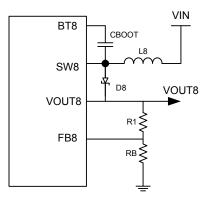

# REG8 VOLTAGE FEEDBACK INPUT FOR VOLTAGE REGULATION/PROGRAMMING (FB8)

Connect the feedback resistor divider to this pin, when voltage mode control is used. When current mode control is used, connect this pin between the LED string and an I<sub>SET</sub> resistor to GND to force the operating current. Refer to Figure 10 and Figure 11. Exclude the components not used.

### **REG8 BOOTSTRAP CAPACITOR INPUT PIN (BT8)**

Connect a 0.01  $\mu$ F capacitor between this pin and SW8 pin to enhance the gate of the Synchronous Power MOSFET.

# REG8 REGULATED OUTPUT VOLTAGE PIN (VOUT8)

Connect this pin directly to the load directly and to the output filter as close to the pin as possible.

# **REG8 SWITCHING NODE (SW8)**

The inductor is connected between this pin and VIN pin.

### **REG1 SWITCHING NODE (SW1)**

The inductor is connected between this pin and VIN pin.

# REG1 REGULATED OUTPUT VOLTAGE BEFORE THE CUT-OFF SWITCH (VG)

REG1 regulated output voltage before the cutoff switch. This supplies the internal circuits and the gate drive.

# REG1 REGULATED OUTPUT VOLTAGE PIN (VOUT1) (34704A ONLY)

Connect this pin directly to the load directly and to the output filter as close to the pin as possible.

#### **REG1 BOOTSTRAP CAPACITOR INPUT PIN (BT1)**

Connect a 1.0  $\mu$ F capacitor between this pin and SW1 pin to enhance the gate of the Switch Power MOSFET.

# I<sup>2</sup>C SERIAL INTERFACE CLOCK INPUT (SCL)

I<sup>2</sup>C serial interface clock input.

# I<sup>2</sup>C SERIAL INTERFACE DATA INPUT (SDA)

I<sup>2</sup>C serial interface data input

# POWER RESET OUTPUT SIGNAL (MICROPROCESSOR RESET) (RST)

This is an open drain output and must be pulled up by an external resistor to a supply voltage like  $V_{\text{IN}}$ .

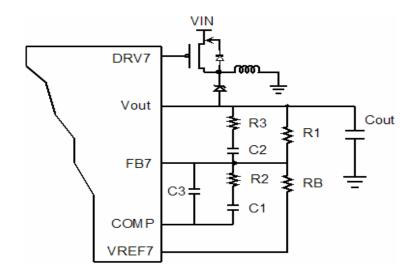

# REG7 COMPENSATION NETWORK CONNECTION (COMP7)

REG7 compensation network connection.

# REG7 RESISTOR FEEDBACK NETWORK REFERENCE VOLTAGE (VREF7) (34704A ONLY)

Connect this pin to the bottom of the feedback resistor divider.

# REG7 VOLTAGE FEEDBACK INPUT FOR VOLTAGE REGULATION/PROGRAMMING (FB7) (34704A ONLY)

Connect the feedback resistor divider to this pin.

# REG7 EXTERNAL POWER MOSFET GATE DRIVE (DRV7) (34704A ONLY)

REG7 external Power MOSFET gate drive.

# REG7 OUTPUT VOLTAGE RETURN PIN (VOUT7) (34704A ONLY)

This is the discharge path of REG7 output voltage.

# REG6 VOLTAGE FEEDBACK INPUT FOR VOLTAGE REGULATION/PROGRAMMING (FB6) (34704A ONLY)

Connect the feedback resistor divider to this pin.

# REG6 BOOTSTRAP CAPACITOR INPUT PIN (BT6) (34704A ONLY)

Connect a 0.01  $\mu\text{F}$  capacitor between this pin and SW6 pin to enhance the gate of the Synchronous Power MOSFET.

### **REG6 SWITCHING NODE (SW6) (34704A ONLY)**

The inductor is connected between this pin and the VIN pin.

# REG6 REGULATED OUTPUT VOLTAGE PIN (VOUT6) (34704A ONLY)

Connect this pin directly to the load directly and to the output filter as close to the pin as possible.

### **ANALOG GROUND (AGND)**

Analog ground of the IC.

#### **BATTERY VOLTAGE CONNECTION (VIN)**

Input decoupling /filtering is required for the device to operate properly.

#### **INTERNAL SUPPLY VOLTAGE (VDDI)**

Connect a 1.0  $\mu\text{F}$  low ESR decoupling filter capacitor between this pin and GND.

# **BATTERY DETECTION (LION)**