# Y Dual 500mA/50MHz Current Feedback Line Driver Amplifier

### **FEATURES**

- 500mA Output Drive Current

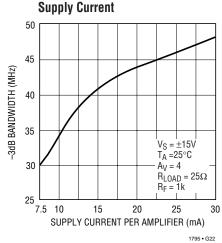

- 50MHz Bandwidth,  $A_V = 2$ ,  $R_L = 25\Omega$

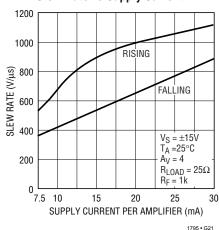

- 900V/ $\mu$ s Slew Rate,  $A_V = 2$ ,  $R_I = 25\Omega$

- Low Distortion: -75dBc at 1MHz

- High Input Impedance, 10MΩ

- Wide Supply Range, ±5V to ±15V

- Full Rate, Downstream ADSL Supported

- Low Power Shutdown Mode

- Power Saving Adjustable Supply Current

- Stable with  $C_L = 10,000pF$

- Power Enhanced Small Footprint Packages TSSOP-20, S0-20 Wide

- Available in a 20-Lead TSSOP Package

### **APPLICATIONS**

- ADSL HDSL2, G.lite Drivers

- Buffers

- Test Equipment Amplifiers

- Video Amplifiers

- Cable Drivers

# DESCRIPTION

The LT $^{\otimes}$ 1795 is a dual current feedback amplifier with high output current and excellent large signal characteristics. The combination of high slew rate, 500mA output drive and up to  $\pm$ 15V operation enables the device to deliver significant power at frequencies in the 1MHz to 2MHz range. Short-circuit protection and thermal shutdown insure the device's ruggedness. The LT1795 is stable with large capacitive loads and can easily supply the large currents required by the capacitive loading. A shutdown feature switches the device into a high impedance, low current mode, reducing power dissipation when the device is not in use. For lower bandwidth applications, the supply current can be reduced with a single external resistor.

The LT1795 comes in the very small, thermally enhanced, 20-lead TSSOP package for maximum port density in line driver applications.

7, LTC and LT are registered trademarks of Linear Technology Corporation.

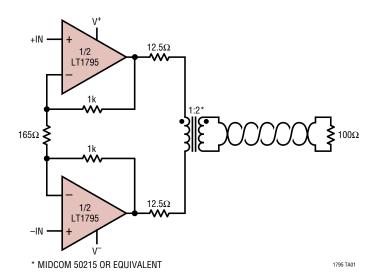

# TYPICAL APPLICATION

Low Loss, High Power Central Office ADSL Line Driver

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Voltage                         | ±18V          |

|----------------------------------------|---------------|

| Input Current                          | ±15mA         |

| Output Short-Circuit Duration (Note 2) | Indefinite    |

| Operating Temperature Range            | -40°C to 85°C |

| Specified Temperature Range (Note 3)40 | 0°C to 85°C |

|----------------------------------------|-------------|

| Junction Temperature                   | 150°C       |

| Storage Temperature Range65°           | °C to 150°C |

| Lead Temperature (Soldering, 10 sec)   | 300°C       |

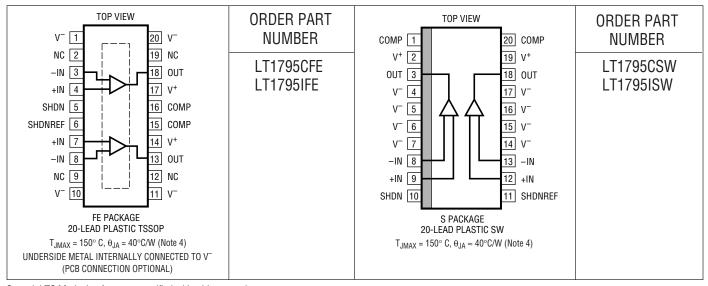

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS**

The ullet denotes the specifications which apply over the full specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CM} = 0V, \pm 5V \leq V_S \leq \pm 15V$ , pulse tested,  $V_{SHDN} = 2.5V$ ,  $V_{SHDNREF} = 0V$  unless otherwise noted. (Note 3)

| SYMBOL                       | PARAMETER                           | CONDITIONS                                                      |   | MIN | TYP          | MAX          | UNITS    |

|------------------------------|-------------------------------------|-----------------------------------------------------------------|---|-----|--------------|--------------|----------|

| V <sub>OS</sub>              | Input Offset Voltage                |                                                                 | • |     | ±3<br>±4.5   | ±13<br>±17   | mV<br>mV |

|                              | Input Offset Voltage Matching       |                                                                 | • |     | ±1<br>±1.5   | ±3.5<br>±5.0 | mV<br>mV |

|                              | Input Offset Voltage Drift          |                                                                 | • |     | 10           |              | μV/°C    |

| I <sub>IN</sub> +            | Noninverting Input Current          |                                                                 | • |     | ±2<br>±8     | ±5<br>±20    | μA<br>μA |

|                              | Noninverting Input Current Matching |                                                                 | • |     | ±0.5<br>±1.5 | ±2<br>±7     | μA<br>μA |

| I <sub>IN</sub> <sup>-</sup> | Inverting Input Current             |                                                                 | • |     | ±10<br>±20   | ±70<br>±100  | μA<br>μA |

|                              | Inverting Input Current Matching    |                                                                 | • |     | ±10<br>±20   | ±30<br>±50   | μA<br>μA |

| e <sub>n</sub>               | Input Noise Voltage Density         | $f = 10kHz$ , $R_F = 1k$ , $R_G = 10\Omega$ , $R_S = 0\Omega$   |   |     | 3.6          |              | nV/√Hz   |

| +i <sub>n</sub>              | Input Noise Current Density         | $f = 10kHz$ , $R_F = 1k$ , $R_G = 10\Omega$ , $R_S = 10k\Omega$ |   |     | 2            |              | pA/√Hz   |

| -i <sub>n</sub>              | Input Noise Current Density         | $f = 10kHz$ , $R_F = 1k$ , $R_G = 10\Omega$ , $R_S = 10k\Omega$ |   |     | 30           |              | pA/√Hz   |

# **ELECTRICAL CHARACTERISTICS**

The ullet denotes the specifications which apply over the full specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CM} = 0V$ ,  $\pm 5V \le V_S \le \pm 15V$ , pulse tested,  $V_{SHDN} = 2.5V$ ,  $V_{SHDNREF} = 0V$  unless otherwise noted. (Note 3)

| SYMBOL                            | PARAMETER                                                          | CONDITIONS                                                                                                         |   | MIN            | TYP             | MAX      | UNITS        |

|-----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---|----------------|-----------------|----------|--------------|

| R <sub>IN</sub> +                 | Input Resistance                                                   | $V_{1N} = \pm 12V, V_S = \pm 15V$                                                                                  | • | 1.5            | 10              |          | MΩ           |

| 0 +                               | Innut Conscitones                                                  | $V = \pm 2V, V_S = \pm 5V$                                                                                         | • | 0.5            | 5               |          | MΩ           |

| C <sub>IN</sub> <sup>+</sup>      | Input Capacitance                                                  | $V_{IN} = \pm 15V$                                                                                                 |   |                | 2               |          | pF           |

|                                   | Input Voltage Range (Note 5)                                       | $V_S = \pm 15V$<br>$V_S = \pm 5V$                                                                                  |   | ±12<br>±2      | ±13.5<br>±3.5   |          | V<br>V       |

| CMRR                              | Common Mode Rejection Ratio                                        | $V_S = \pm 15V, V_{CM} = \pm 12V$<br>$V_S = \pm 5V, V_{CM} = \pm 2V$                                               | • | 55<br>50       | 62<br>60        |          | dB<br>dB     |

|                                   | Inverting Input Current<br>Common Mode Rejection                   | $V_S = \pm 15V, V_{CM} = \pm 12V$<br>$V_S = \pm 5V, V_{CM} = \pm 2V$                                               | • |                | 1<br>1          | 10<br>10 | μΑ/V<br>μΑ/V |

| PSRR                              | Power Supply Rejection Ratio                                       | $V_S = \pm 5V \text{ to } \pm 15V$                                                                                 | • | 60             | 77              |          | dB           |

|                                   | Noninverting Input Current<br>Power Supply Rejection               | $V_S = \pm 5V$ to $\pm 15V$                                                                                        | • |                | 30              | 500      | nA/V         |

|                                   | Inverting Input Current<br>Power Supply Rejection                  | $V_S = \pm 5V$ to $\pm 15V$                                                                                        | • |                | 1               | 5        | μΑ/V         |

| A <sub>V</sub>                    | Large-Signal Voltage Gain                                          | $V_S = \pm 15V$ , $V_{OUT} = \pm 10V$ , $R_L = 25\Omega$<br>$V_S = \pm 5V$ , $V_{OUT} = \pm 2V$ , $R_L = 12\Omega$ | • | 55<br>55       | 68<br>68        |          | dB<br>dB     |

| R <sub>0L</sub>                   | Transresistance, ∆V <sub>OUT</sub> /∆I <sub>IN</sub> <sup>−</sup>  | $V_S = \pm 15V$ , $V_{OUT} = \pm 10V$ , $R_L = 25\Omega$<br>$V_S = \pm 5V$ , $V_{OUT} = \pm 2V$ , $R_L = 12\Omega$ | • | 75<br>75       | 200<br>200      |          | kΩ<br>kΩ     |

| V <sub>OUT</sub>                  | Maximum Output Voltage Swing                                       | $V_S = \pm 15V$ , $R_L = 25\Omega$                                                                                 | • | ±11.5<br>±10.0 | ±12.5<br>±11.5  |          | V            |

|                                   |                                                                    | $V_S = \pm 5V$ , $R_L = 12\Omega$                                                                                  | • | ±2.5<br>±2.0   | ±3<br>±3        |          | V            |

| I <sub>OUT</sub>                  | Maximum Output Current                                             | $V_S = \pm 15V$ , $R_L = 1\Omega$                                                                                  | • | 0.5            | 1               |          | А            |

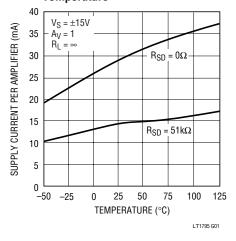

| Is                                | Supply Current Per Amplifier                                       | $V_S = \pm 15V, V_{SHDN} = 2.5V$                                                                                   | • |                | 29              | 34<br>42 | mA<br>mA     |

|                                   | Supply Current Per Amplifier,<br>R <sub>SHDN</sub> = 51k, (Note 6) | V <sub>S</sub> = ±15V                                                                                              | • |                | 15              | 20<br>25 | mA<br>mA     |

|                                   | Positive Supply Current, Shutdown                                  | $V_S = \pm 15V$ , $V_{SHDN} = 0.4V$                                                                                | • |                | 1               | 200      | μΑ           |

|                                   | Output Leakage Current, Shutdown                                   | $V_S = \pm 15V$ , $V_{SHDN} = 0.4V$                                                                                |   |                | 1               | 200      | μΑ           |

|                                   | Channel Separation                                                 | $V_S = \pm 15V$ , $V_{OUT} = \pm 10V$ , $R_L = 25\Omega$                                                           |   | 80             | 110             |          | dB           |

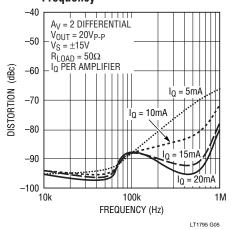

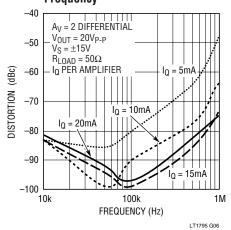

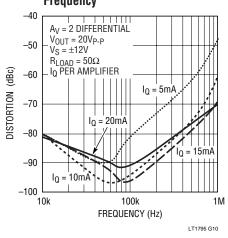

| HD <sub>2</sub> , HD <sub>3</sub> | 2nd and 3rd Harmonic Distortion<br>Differential Mode               | $f = 1MHz$ , $V_0 = 20V_{P-P}$ , $R_L = 50$ , $A_V = 2$                                                            |   |                | <del>-</del> 75 |          | dBc          |

| SR                                | Slew Rate (Note 7)                                                 | $A_V = 4$ , $R_L = 400\Omega$                                                                                      |   | 400            | 900             |          | V/µs         |

|                                   | Slew Rate                                                          | $A_V = 4$ , $R_L = 25\Omega$                                                                                       |   |                | 900             |          | V/µs         |

| BW                                | Small-Signal BW                                                    | $A_V = 2$ , $V_S = \pm 15V$ , Peaking $\leq 1.5 dB$<br>$R_F = R_G = 910\Omega$ , $R_L = 100\Omega$                 |   |                | 65              |          | MHz          |

|                                   |                                                                    | $A_V$ = 2, $V_S$ = ±15V, Peaking $\leq$ 1.5dB<br>$R_F$ = $R_G$ = 820 $\Omega$ , $R_L$ = 25 $\Omega$                |   |                | 50              |          | MHz          |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Applies to short-circuits to ground only. A short-circuit between the output and either supply may permanently damage the part when operated on supplies greater than  $\pm 10$ V.

**Note 3:** The LT1795C is guaranteed to meet specified performance from  $0^{\circ}$ C to  $70^{\circ}$ C and is designed, characterized and expected to meet these extended temperature limits, but is not tested at  $-40^{\circ}$ C and  $85^{\circ}$ C. The LT1795I is guaranteed to meet the extended temperature limits.

**Note 4:** Thermal resistance varies depending upon the amount of PC board metal attached to the device. If the maximum dissipation of the package is exceeded, the device will go into thermal shutdown and be protected.

Note 5: Guaranteed by the CMRR tests.

Note 6: R<sub>SHDN</sub> is connected between the SHDN pin and V<sup>+</sup>.

**Note 7:** Slew rate is measured at  $\pm5V$  on a  $\pm10V$  output signal while operating on  $\pm15V$  supplies with  $R_F$  = 1k,  $R_G$  = 333 $\Omega$  (A<sub>V</sub> = +4) and  $R_L$  = 400 $\Omega$ .

### **SMALL-SIGNAL BANDWIDTH**

$R_{SD}$  = 0\$\Omega\$, \$I\_S\$ = 30mA per Amplifer, \$V\_S\$ = \$\pm 15V\$, Peaking \$\leq\$ 1dB, \$R\_L\$ = 25\$\Omega\$

| A <sub>V</sub> | R <sub>F</sub> | R <sub>G</sub> | –3dB BW<br>(MHz) |

|----------------|----------------|----------------|------------------|

| -1             | 976            | 976            | 44               |

| 1              | 1.15k          | _              | 53               |

| 2              | 976            | 976            | 48               |

| 10             | 649            | 72             | 46               |

$R_{SD}$  = 51k $\Omega$ ,  $I_S$  = 15mA per Amplifer,  $V_S$  = ±15V, Peaking  $\leq$  1dB,  $R_L$  = 25 $\Omega$

| A <sub>V</sub> | R <sub>F</sub> | R <sub>G</sub> | –3dB BW<br>(MHz) |

|----------------|----------------|----------------|------------------|

| -1             | 976            | 976            | 30               |

| 1              | 1.15k          | _              | 32               |

| 2              | 976            | 976            | 32               |

| 10             | 649            | 72             | 27               |

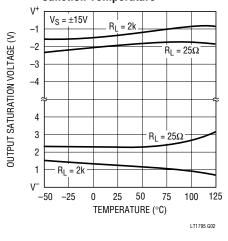

## TYPICAL PERFORMANCE CHARACTERISTICS

### Supply Current vs Ambient Temperature

#### Output Saturation Voltage vs Junction Temperature

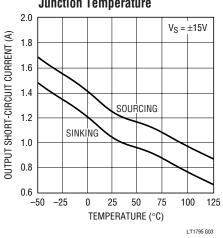

Output Short-Circuit Current vs Junction Temperature

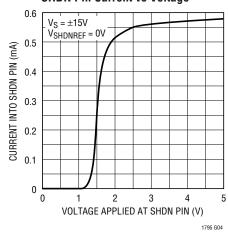

### **SHDN Pin Current vs Voltage**

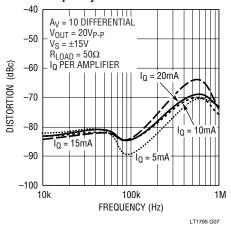

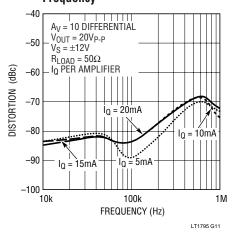

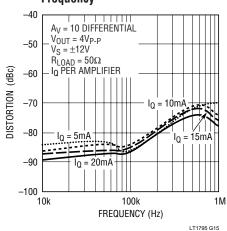

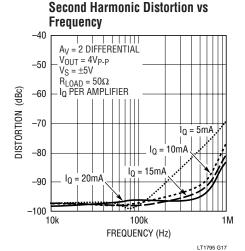

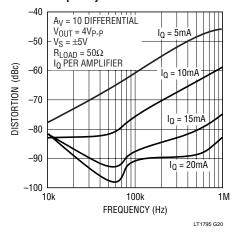

### Second Harmonic Distortion vs Frequency

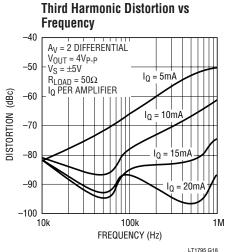

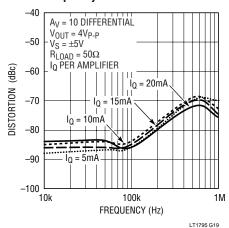

# Third Harmonic Distortion vs Frequency

# TYPICAL PERFORMANCE CHARACTERISTICS

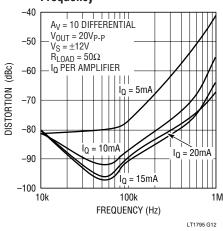

### Second Harmonic Distortion vs Frequency

#### Third Harmonic Distortion vs Frequency

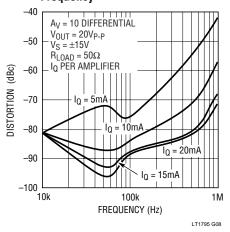

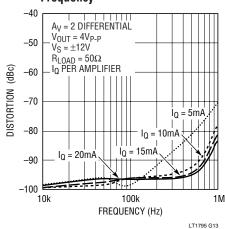

### Second Harmonic Distortion vs Frequency

#### Third Harmonic Distortion vs Frequency

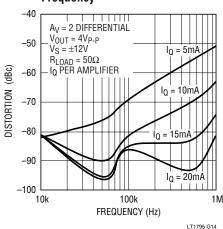

#### Second Harmonic Distortion vs Frequency

Third Harmonic Distortion vs Frequency

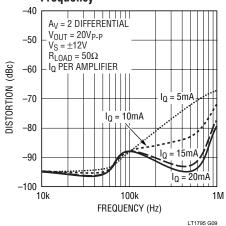

### Second Harmonic Distortion vs Frequency

### Third Harmonic Distortion vs Frequency

### Second Harmonic Distortion vs Frequency

DISTORTION (dBc)

-90

-100

-110 <u>└</u> 10k

# TYPICAL PERFORMANCE CHARACTERISTICS

Frequency  $-40 \\

-50 \\

-60 \\

-60 \\

-70 \\

-80$  -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80 -80

100k

FREQUENCY (Hz)

Third Harmonic Distortion vs

### Second Harmonic Distortion vs Frequency

LT1795 G16

1M

$I_Q = 20 \text{mA}$

### Third Harmonic Distortion vs Frequency

### Slew Rate vs Supply Current

# -3dB Bandwidth vs

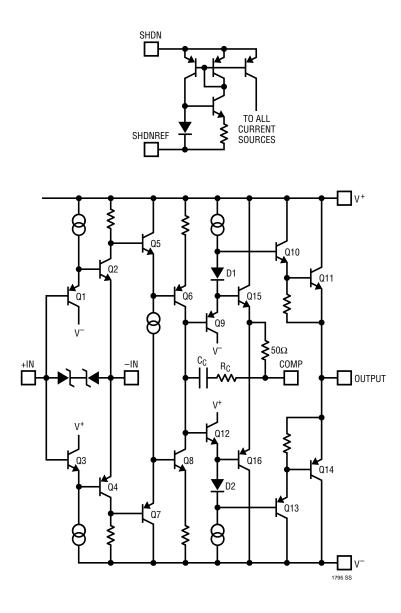

The LT1795 is a dual current feedback amplifier with high output current drive capability. The amplifier is designed to drive low impedance loads such as twisted-pair transmission lines with excellent linearity.

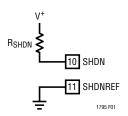

### SHUTDOWN/CURRENT SET

If the shutdown/current set feature is not used, connect SHDN to  $V^+$  and SHDNREF to ground.

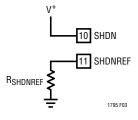

The SHDN and SHDNREF pins control the biasing of the two amplifiers. The pins can be used to either turn off the amplifiers completely, reducing the quiescent current to less then  $200\mu A$ , or to control the quiescent current in normal operation.

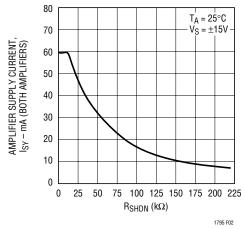

Figure 1.  $R_{SHDN}$  Connected Between V+ and SHDN (Pin 10); SHDNREF (Pin 11) = GND. See Figure 2

Figure 2. LT1795 Amplifier Supply Current vs  $R_{SHDN}$ .  $R_{SHDN}$  Connected Between V+ and SHDN, SHDNREF = GND (See Figure 1)

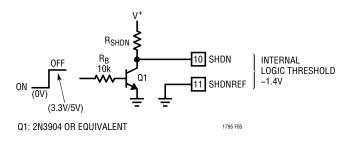

When  $V_{SHDN} = V_{SHDNREF}$ , the device is shut down. The device will interface directly with 3V or 5V CMOS logic when SHDNREF is grounded and the control signal is applied to the SHDN pin. Switching time between the active and shutdown states is about 1.5 $\mu$ s.

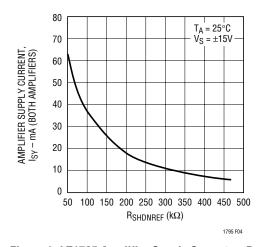

Figures 1 to 4 illustrate how the SHDN and SHDNREF pins can be used to reduce the amplifier quiescent current. In both cases, an external resistor is used to set the current. The two approaches are equivalent, however the required resistor values are different. The quiescent current will be approximately 115 times the current in the SHDN pin and 230 times the current in the SHDNREF pin. The voltage across the resistor in either condition is  $V^+ - 1.5V$ . For example, a 50k resistor between  $V^+$  and SHDN will set the

Figure 3.  $R_{SHDNREF}$  Connected Between SHDNREF (Pin 11) and GND; SHDN (Pin 10) = V<sup>+</sup>. See Figure 4

Figure 4. LT1795 Amplifier Supply Current vs  $R_{SHDNREF}$ .  $R_{SHDNREF}$  Connected Between SHDNREF and GND, SHDN = V<sup>+</sup> (See Figure 3)

quiescent current to 33mA with  $V_S = \pm 15V$ . If ON/OFF control is desired in addition to reduced quiescent current, then the circuits in Figures 5 to 7 can be employed.

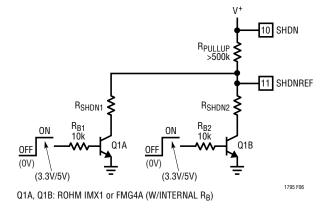

Figure 5. Setting Amplifier Supply Current Level with ON/OFF Control, Version 1

Figure 6. Setting Multiple Amplifier Supply Current Levels with ON/OFF Control, Version 2

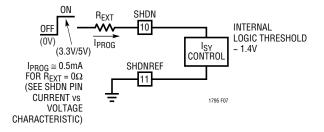

Figure 7. Setting Amplifier Supply Current Level with ON/OFF Control, Version 3

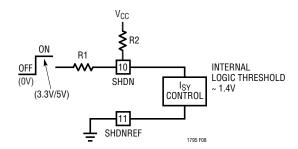

Figure 8 illustrates a partial shutdown with direct logic control. By keeping the output stage slightly biased on, the output impedance remains low, preserving the line termination. The design equations are:

$$R1 = \frac{115 \cdot V_H}{\left(I_S\right)_{ON} - \left(I_S\right)_{OFF}}$$

$$R2 = \frac{115 \cdot \left(V_{CC} - V_{SHDN}\right)}{\left(V_{SHDN} / V_{H}\right) \cdot \left[\left(I_{S}\right)_{ON} - \left(I_{S}\right)_{OFF}\right] + \left(I_{S}\right)_{OFF}}$$

where

V<sub>H</sub> = Logic High Level

$(I_S)_{ON} = Supply Current Fully On$

$(I_S)_{OFF}$  = Supply Current Partially On

V<sub>SHDN</sub> = Shutdown Pin Voltage ≈1.4V

V<sub>CC</sub> = Positive Supply Voltage

Figure 8. Partial Shutdown

#### THERMAL CONSIDERATIONS

The LT1795 contains a thermal shutdown feature that protects against excessive internal (junction) temperature. If the junction temperature of the device exceeds the protection threshold, the device will begin cycling between normal operation and an off state. The cycling is not harmful to the part. The thermal cycling occurs at a slow rate, typically 10ms to several seconds, which depends on the power dissipation and the thermal time constants of the package and heat sinking. Raising the ambient tempera-

LINEAR

ture until the device begins thermal shutdown gives a good indication of how much margin there is in the thermal design.

For surface mount devices, heat sinking is accomplished by using the heat spreading capabilities of the PC board and its copper traces. For the TSSOP package, power is dissipated through the exposed heatsink. For the SO package, power is dissipated from the package primarily through the  $V^-$  pins (4 to 7 and 14 to 17). These pins should have a good thermal connection to a copper plane, either by direct contact or by plated through holes. The copper plane may be an internal or external layer. The thermal resistance, junction-to-ambient will depend on the total copper area connected to the device. For example, the thermal resistance of the LT1795 connected to a  $2\times 2$  inch, double sided 2 oz copper plane is  $40^{\circ}$ C/W.

### **CALCULATING JUNCTION TEMPERATURE**

The junction temperature can be calculated from the equation:

$$T_J = (P_D)(\theta_{JA}) + T_A$$

where

$T_J$  = Junction Temperature

T<sub>A</sub> = Ambient Temperature

P<sub>D</sub> = Device Dissipation

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

### **Differential Input Signal Swing**

The differential input swing is limited to about  $\pm 5V$  by an ESD protection device connected between the inputs. In normal operation, the differential voltage between the input pins is small, so this clamp has no effect. However, in the shutdown mode, the differential swing can be the same as the input swing. The clamp voltage will then set the maximum allowable input voltage.

### **POWER SUPPLY BYPASSING**

To obtain the maximum output and the minimum distortion from the LT1795, the power supply rails should be well bypassed. For example, with the output stage supply-

ing 0.5A current peaks into the load, a  $1\Omega$  power supply impedance will cause a droop of 0.5V, reducing the available output swing by that amount. Surface mount tantalum and ceramic capacitors make excellent low ESR bypass elements when placed close to the chip. For frequencies above 100kHz, use  $1\mu F$  and 100nF ceramic capacitors. If significant power must be delivered below 100kHz, capacitive reactance becomes the limiting factor. Larger ceramic or tantalum capacitors, such as  $4.7\mu F$ , are recommended in place of the  $1\mu F$  unit mentioned above.

Inadequate bypassing is evidenced by reduced output swing and "distorted" clipping effects when the output is driven to the rails. If this is observed, check the supply pins of the device for ripple directly related to the output waveform. Significant supply modulation indicates poor bypassing.

### **Capacitance on the Inverting Input**

Current feedback amplifiers require resistive feedback from the output to the inverting input for stable operation. Take care to minimize the stray capacitance between the output and the inverting input. Capacitance on the inverting input to ground will cause peaking in the frequency response (and overshoot in the transient response), but it does not degrade the stability of the amplifier.

#### **Feedback Resistor Selection**

The optimum value for the feedback resistors is a function of the operating conditions of the device, the load impedance and the desired flatness of response. The Typical AC Performance tables give the values which result in less than 1dB of peaking for various resistive loads and operating conditions. If this level of flatness is not required, a higher bandwidth can be obtained by use of a lower feedback resistor.

For resistive loads, the COMP pin should be left open (see Capacitive Loads section).

### **Capacitive Loads**

The LT1795 includes an optional compensation network for driving capacitive loads. This network eliminates most of the output stage peaking associated with capacitive loads, allowing the frequency response to be flattened.

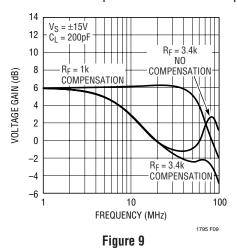

Figure 9 shows the effect of the network on a 200pF load. Without the optional compensation, there is a 6dB peak at 85MHz caused by the effect of the capacitance on the output stage. Adding a 0.01µF bypass capacitor between the output and the COMP pins connects the compensation

and greatly reduces the peaking. A lower value feedback resistor can now be used, resulting in a response which is flat to  $\pm 1$ dB to 45MHz. The network has the greatest effect for C<sub>1</sub> in the range of 0pF to 1000pF.

Although the optional compensation works well with capacitive loads, it simply reduces the bandwidth when it is connected with resistive loads. For instance, with a  $25\Omega$ load, the bandwidth drops from 48MHz to 32MHz when the compensation is connected. Hence, the compensation was made optional. To disconnect the optional compensation, leave the COMP pin open.

### **DEMO BOARD**

A demo board (DC261A) is available for evaluating the performence of the LT1795. The board is configured as a differential line driver/receiver suitable for xDSL applications. For details, consult your local sales representative.

# PACKAGE DESCRIPTION

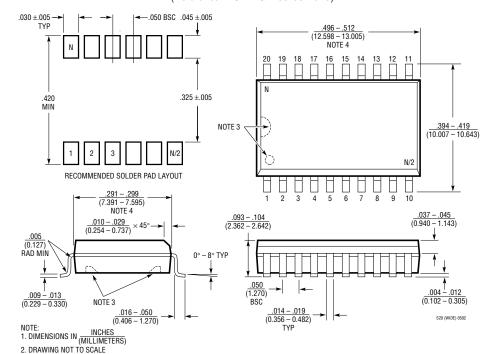

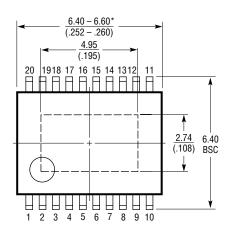

### SW Package 20-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

3. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS. THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

4. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

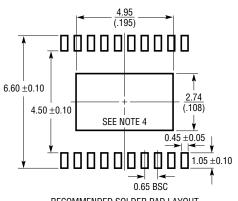

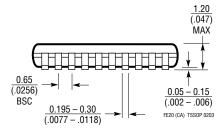

# PACKAGE DESCRIPTION

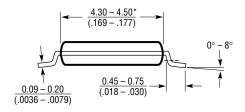

### FE Package 20-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663)

### **Exposed Pad Variation CA**

- 1. CONTROLLING DIMENSION: MILLIMETERS

- 2. DIMENSIONS ARE IN  $\frac{\text{MILLIMETERS}}{\text{(INCHES)}}$

- 3. DRAWING NOT TO SCALE

- 4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT

- \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE

# SIMPLIFIED SCHEMATIC

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                   | COMMENTS                         |

|-------------|-----------------------------------------------|----------------------------------|

| LT1497      | Dual 125mA, 50MHz Current Feedback Amplifier  | 900V/µs Slew Rate                |

| LT1207      | Dual 250mA, 60MHz Current Feedback Amplifier  | Shutdown/Current Set Function    |

| LT1886      | Dual 200mA, 700MHz Voltage Feedback Amplifier | Low Distortion: –72dBc at 200kHz |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **Analog Devices Inc.:**

<u>LT1795CSW#TRPBF</u> <u>LT1795IFE#TR</u> <u>LT1795CFE</u> <u>LT1795IFE#TRPBF</u> <u>LT1795ISW#TR</u> <u>LT1795ISW#TR</u> <u>LT1795CSW#TRPBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#PBF</u> <u>LT1795CSW#TR</u>