SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

# 16-Bit, Low-Power Stereo Audio CODEC With Microphone Bias, Headphone, and Digital Speaker Amplifier

#### **FEATURES**

- Analog Front End:

- Stereo Single-Ended Input With Multiplexer

- Mono Differential Input

- Stereo Programmable Gain Amplifier

- Microphone Boost Amplifier (20 dB) and Bias

- Analog BackEnd:

- Stereo/Mono Line Output With Volume

- Stereo/Mono Headphone Amplifier With Volume and Capless Mode

- Stereo/Mono Digital Speaker Amplifier (BTL) With Volume (PCM3793)

- Analog Performance:

- Dynamic Range: 93 dB (DAC)

- Dynamic Range: 90 dB (ADC)

- 40-mW + 40-mW Headphone Output at  $R_L = 16 \Omega$

- 700-mW + 700-mW Speaker Output at  $R_L = 8 \Omega$

- Power Supply Voltage

- 1.71 V to 3.6 V for Digital I/O Section

- 1.71 V to 3.6 V for Digital Core Section

- 2.4 V to 3.6 V for Analog Section

- 2.4 V to 3.6 V for Power Amplifier Section

- Low Power Dissipation:

- 7 mW in Playback, 1.8 V/2.4 V, 48 kHz

- 13 mW in Record, 1.8 V/2.4 V, 48 kHz

- 30 μW in Power Down

- Sampling Frequency: 5 kHz to 50 kHz

- Automatic Level Control for Recording

- Operation From a Single Clock Input Without PLL

- System Clock:

- Common-Audio Clock (256 f<sub>s</sub>/384 f<sub>s</sub>), 12/24, 13/26, 13.5/27, 19.2/38.4, 19.68/39.36 MHz

- Headphone Plug Insert Detection

- 2 (I<sup>2</sup>C) or 3 (SPI) Wire Serial Control

- Programmable Function by Register Control:

- Digital Attenuation of DAC: 0 dB to -62 dB

- Power Up/Down Control for Each Module

- 6-dB to -70-dB Gain for Analog Outputs

- 30-dB to -12-dB Gain for Analog Inputs

- 0/20 dB Boost Selectable for Microphone Input

- 0-dB to -21-dB Gain for Analog Mixing

- Parameter Settings for ALC

- Three-Band Tone Control and 3D Sound

- High-Pass Filter and Two-Stage Notch Filter

- Analog Mixing

- Pop-Noise Reduction Circuit

- Short and Thermal Protection Circuit

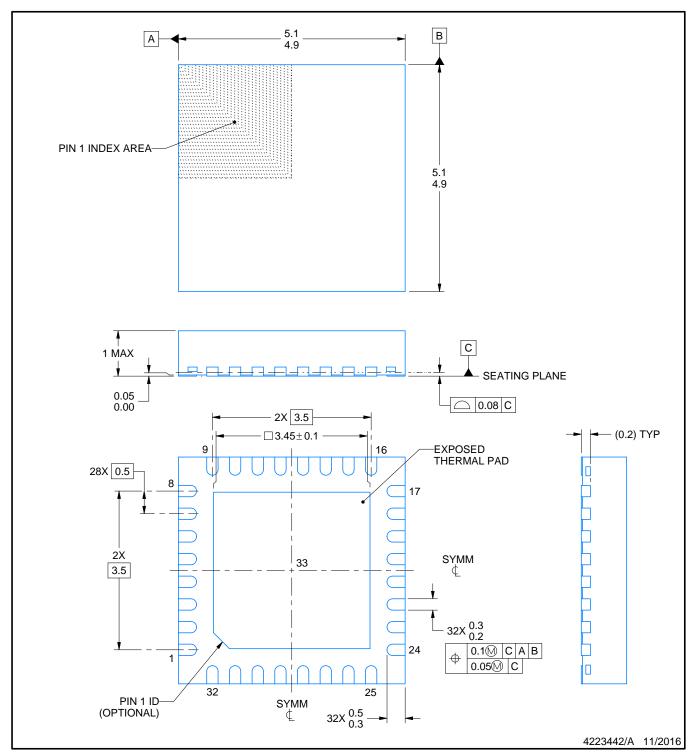

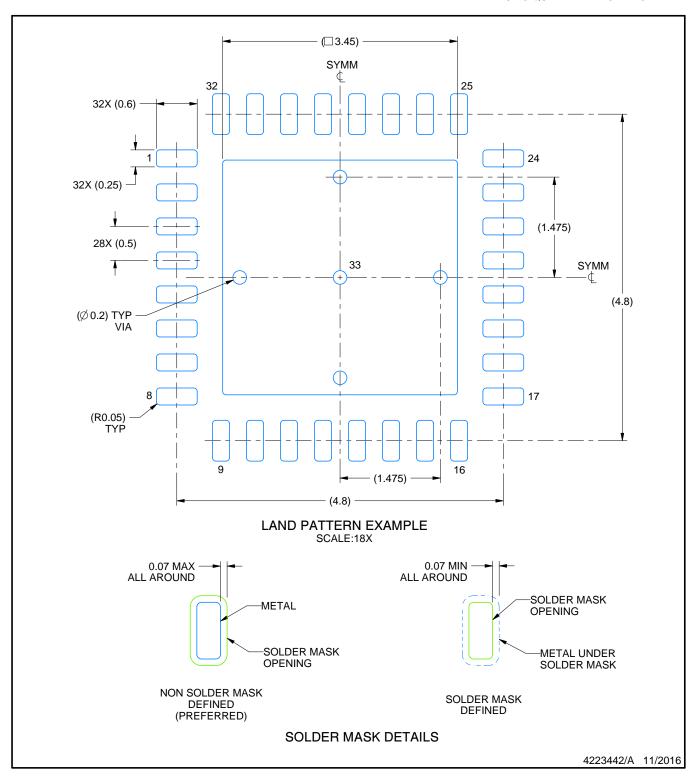

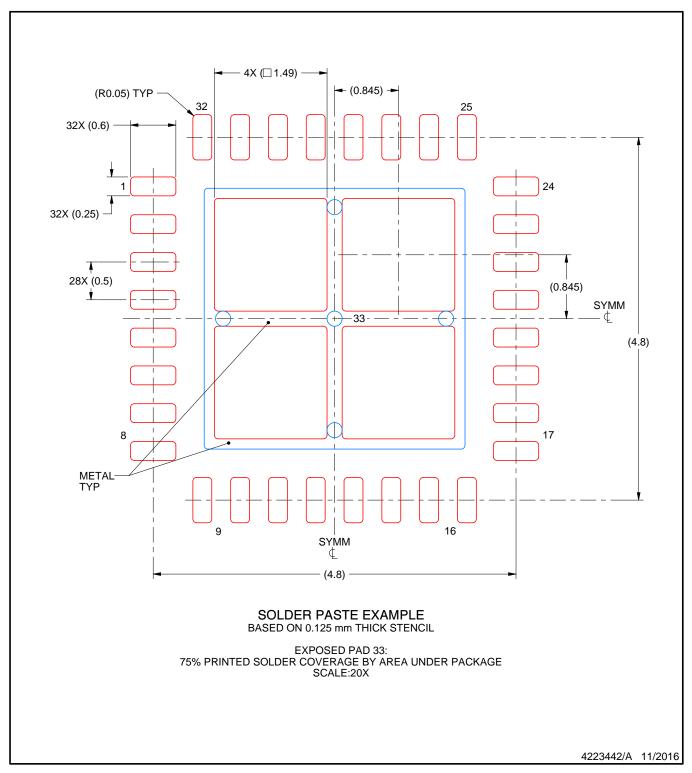

- Package: 5-mm × 5-mm QFN Pacakge

- Operation Temperature Range: –40°C to 85°C

#### **APPLICATIONS**

- Portable Audio Player, Cellular Phone

- Video Camcorder, Digital Still Camera

- PMP/DMB

#### DESCRIPTION

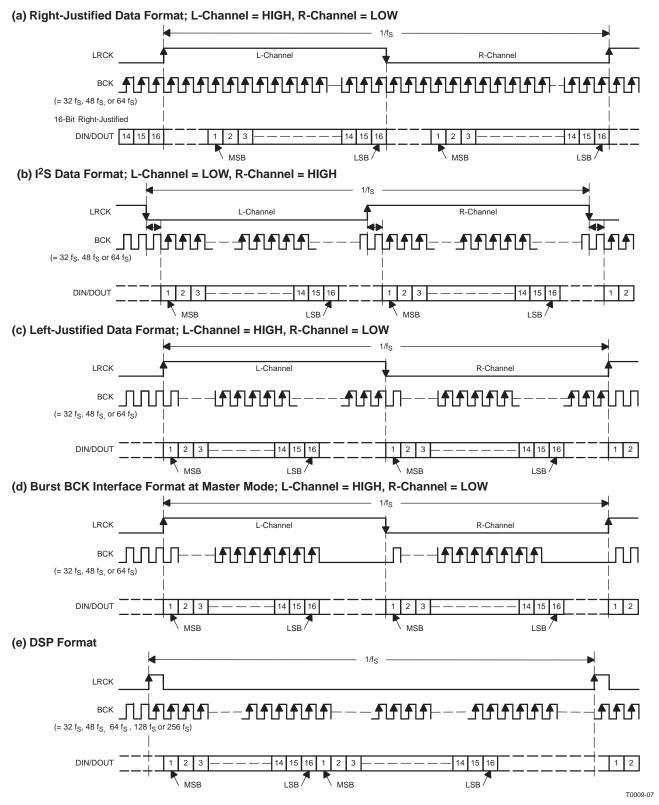

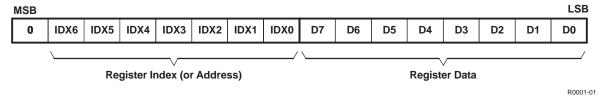

The PCM3793/94 is a low-power stereo CODEC designed for portable digital audio applications. The device integrates stereo digital speaker amplifier, headphone amplifier, line amplifier, line input, boost amplifier, microphone bias, programmable gain control, analog mixing, sound effects, and automatic level control (ALC). It is available in a small-footprint, 5-mm × 5-mm QFN package. The PCM3793/94 accepts right-justified, left-justified, l²S, and DSP formats, providing easy interfacing to audio DSP, decoder, and encoder chips. Sampling rates up to 50 kHz are supported. The user-programmable functions are accessible through a two- or three-wire serial control port.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### TEXAS INSTRUMENTS www.ti.com

#### SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION

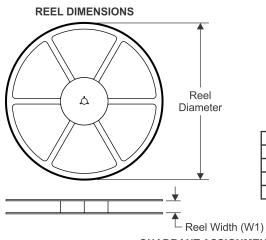

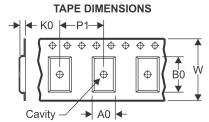

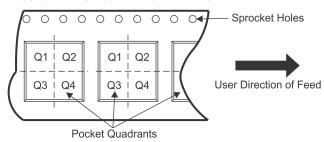

| PRODUCT      | PACKAGE | PACKAGE<br>CODE   | OPERATION<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT MEDIA     |             |                     |

|--------------|---------|-------------------|-----------------------------------|--------------------|-----------------------------------|---------------------|-------------|---------------------|

| PCM3793RHB   | 32 QFN  | RHB               | −40°C to 85°C                     | PCM3793            | PCM3793RHBT                       | Small tape and reel |             |                     |

| PCIVIS/93KHB | 32 QI N | SKIID 32 QFN KIID | KIID                              | -40°C 10 65°C      | -40 C to 65 C                     |                     | PCM3793RHBR | Large tape and reel |

| PCM3794RHB   | 32 QFN  | RHB               | 40°C to 95°C                      | PCM3794            | PCM3794RHBT                       | Small tape and reel |             |                     |

| PCIVI3/94RHB | 32 QFN  | KHD               | –40°C to 85°C                     | PCIVI3794          | PCM3794RHBR                       | Large tape and reel |             |                     |

<sup>(1)</sup> For the most current specification and package information, see the TI Web site at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)(1)

|                              |                                                      | PCM3793/94 | UNIT    |  |

|------------------------------|------------------------------------------------------|------------|---------|--|

| Supply voltage               | $V_{DD}$ , $V_{IO}$ , $V_{CC}$ , $V_{PA}$            | -0.3 to 4  | V       |  |

| Ground voltage differe       | nces: DGND, AGND, PGND                               | ±0.1       | V       |  |

| Input voltage                | nput voltage                                         |            |         |  |

| Input current (any pins      | Input current (any pins except supplies and SPK out) |            |         |  |

| Ambient temperature u        | under bias                                           | -40 to 110 | °C      |  |

| Storage temperature          |                                                      | -55 to 150 | °C      |  |

| Junction temperature         |                                                      | 150        | °C      |  |

| Lead temperature (soldering) |                                                      | 260        | °C, 5 s |  |

| Package temperature          | 260                                                  | °C         |         |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                   |                                                              |                               | MIN   | NOM  | MAX    | UNIT |

|-----------------------------------|--------------------------------------------------------------|-------------------------------|-------|------|--------|------|

| V <sub>CC</sub> , V <sub>PA</sub> | Analog supply voltage                                        |                               | 2.4   | 3.3  | 3.6    | V    |

| $V_{DD}$ , $V_{IO}$               | Digital supply voltage                                       | Digital supply voltage        |       | 3.3  | 3.6    | V    |

|                                   | Digital input logic family                                   |                               |       | CMOS |        |      |

|                                   | Digital input clock frequency  Analog output load resistance | SCKI system clock             | 3.072 |      | 18.432 | MHz  |

|                                   |                                                              | LRCK sampling clock           | 8     |      | 48     | kHz  |

|                                   |                                                              | LOL and LOR                   | 10    |      |        | kΩ   |

|                                   |                                                              | HPOL and HPOR                 | 16    |      |        | Ω    |

|                                   |                                                              | SPOLP, SPOLN, SPORP and SPORN | 8     |      |        | Ω    |

|                                   | Analog output load capacitance                               |                               |       |      | 30     | pF   |

|                                   | Digital output load capacitance                              |                               |       |      | 10     | pF   |

| T <sub>A</sub>                    | Operating free-air temperature                               |                               | -40   |      | 85     | °C   |

# **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = 25$ °C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data (unless otherwise noted).

|                 |                                          | TEST CONDITIONS                         | PCM3793RHB, PCM3794RHB                |                    |                     |      |  |

|-----------------|------------------------------------------|-----------------------------------------|---------------------------------------|--------------------|---------------------|------|--|

|                 | PARAMETER                                | TEST CONDITIONS                         | MIN                                   | TYP                | MAX                 | UNIT |  |

| Audio D         | Oata Characteristics                     |                                         |                                       |                    | ·                   |      |  |

| DATA F          | ORMAT                                    |                                         |                                       |                    |                     |      |  |

|                 | Resolution                               |                                         |                                       | 16                 |                     | Bits |  |

|                 | Audio data interface format              |                                         | I <sup>2</sup> S, left-, riç          | ght-justified, DSI | Р                   |      |  |

|                 | Audio data bit length                    |                                         |                                       | 16                 |                     | Bits |  |

|                 | Audio data format                        |                                         | MSB first,                            | 2s complement      |                     |      |  |

|                 | Sampling frequency (f <sub>S</sub> )     |                                         | 5                                     |                    | 50                  | kHz  |  |

|                 | 0                                        | V <sub>DD</sub> < 2 V                   |                                       |                    | 27                  | 27   |  |

|                 | System clock                             | V <sub>DD</sub> > 2 V                   |                                       |                    | 40                  | MHz  |  |

| Digital I       | nput/Output                              |                                         |                                       |                    | l .                 |      |  |

|                 | Logic family                             |                                         | CMOS                                  | S compatible       |                     |      |  |

| √ <sub>IH</sub> |                                          |                                         | 0.7 V <sub>IO</sub>                   |                    |                     | VDC  |  |

| V <sub>IL</sub> | Input logic level                        |                                         | · · · · · · · · · · · · · · · · · · · |                    | 0.3 V <sub>IO</sub> | VDC  |  |

| IH              |                                          | V <sub>IN</sub> = 3.3 V                 |                                       |                    | 10                  |      |  |

| IL              | Input logic current                      | V <sub>IN</sub> = 0 V                   |                                       |                    | -10                 | μΑ   |  |

| V <sub>OH</sub> |                                          | I <sub>OH</sub> = -2 mA                 | 0.75 V <sub>IO</sub>                  |                    |                     | VDC  |  |

| V <sub>OL</sub> | Output logic level                       | I <sub>OL</sub> = 2 mA                  | -                                     | 0                  | .25 V <sub>IO</sub> | VDC  |  |

|                 | nput to Line Output Through DAG          | C (LOL, LOR, and MONO)                  |                                       |                    |                     |      |  |

| $R_1 = 10$      | $k\Omega$ , ALC = OFF, volume = 0 dB, sp | eaker = powered down, analog mixing = d | isabled                               |                    |                     |      |  |

| DYNAM           | IC PERFORMANCE                           |                                         |                                       |                    |                     |      |  |

|                 |                                          | 0 dB                                    |                                       | 2.828              |                     | Vp-p |  |

|                 | Full-scale output voltage                |                                         |                                       | 1                  |                     | Vrms |  |

|                 | Dynamic range                            | EIAJ, A-weighted                        |                                       | 93                 |                     | dB   |  |

| SNR             | Signal-to-noise ratio                    | EIAJ, A-weighted                        | 86                                    | 93                 |                     | dB   |  |

|                 | Channel separation                       | -                                       |                                       | 91                 |                     | dB   |  |

| THD+N           | Total harmonic distortion + noise        | 0 dB                                    |                                       | 0.008%             |                     |      |  |

|                 | Load resistance                          |                                         | 10                                    |                    |                     | kΩ   |  |

| Line Inp        | out to Line Output Through Mixing        | g Path (LOL, LOR, and MONO)             |                                       |                    |                     |      |  |

| -               |                                          | eaker = powered down, analog mixing = e | nabled                                |                    |                     |      |  |

|                 | IC PERFORMANCE                           |                                         |                                       |                    |                     |      |  |

|                 | Full-scale input and output              |                                         |                                       | 2.828              |                     | Vp-p |  |

|                 | voltage                                  | 0 dB                                    |                                       | 1                  |                     | Vrms |  |

| SNR             | Signal-to-noise ratio                    | EIAJ, A-weighted                        | 84                                    | 93                 |                     | dB   |  |

TEXAS INSTRUMENTS www.ti.com

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = 25$ °C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data (unless otherwise noted).

|                                           | 2.2.4                                                                                                                                                                                               | TT0T 0011D1T10110                                                                                                                                                                               | PCM3793RHB, PCM3794RHB     |                                        | НВ  |                       |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|-----|-----------------------|

|                                           | PARAMETER                                                                                                                                                                                           | TEST CONDITIONS                                                                                                                                                                                 | MIN                        | TYP                                    | MAX | UNIT                  |

| Digital I                                 | nput to Headphone Output Throu                                                                                                                                                                      | igh DAC (HPOL and HPOR)                                                                                                                                                                         |                            |                                        |     |                       |

| R <sub>L</sub> = 16                       | $\Omega$ or 32 $\Omega$ , ALC = OFF, volume = 0                                                                                                                                                     | dB, speaker = powered down, analog mix                                                                                                                                                          | xing = disabled, no        | t capless mode                         | )   |                       |

| DYNAM                                     | IC PERFORMANCE                                                                                                                                                                                      |                                                                                                                                                                                                 |                            |                                        |     |                       |

|                                           | Full scale output voltage                                                                                                                                                                           | 0 dB                                                                                                                                                                                            |                            | 2.828                                  |     | Vp-p                  |

|                                           | Full-scale output voltage                                                                                                                                                                           | U UB                                                                                                                                                                                            |                            | 1                                      |     | Vrms                  |

| SNR                                       | Signal-to-noise ratio                                                                                                                                                                               | EIAJ, A-weighted                                                                                                                                                                                | 84                         | 93                                     |     | dB                    |

| TUD.N                                     | Total harmonic distortion I naise                                                                                                                                                                   | 30 mW, $R_L = 32 \Omega$ , volume = 0 dB                                                                                                                                                        |                            | 0.1%                                   |     |                       |

| THD+N                                     | Total harmonic distortion + noise                                                                                                                                                                   | 40 mW, $R_L$ = 16 Ω, volume = -1 dB                                                                                                                                                             |                            | 0.03%                                  |     |                       |

|                                           | Load resistance                                                                                                                                                                                     |                                                                                                                                                                                                 | 16                         |                                        |     | Ω                     |

|                                           |                                                                                                                                                                                                     | 200 Hz, 140 mVp-p                                                                                                                                                                               |                            | -40                                    |     |                       |

| PSRR                                      | Power-supply rejection ratio                                                                                                                                                                        | 1 kHz, 140 mVp-p                                                                                                                                                                                |                            | -45                                    |     | dB                    |

|                                           |                                                                                                                                                                                                     | 20 kHz, 140 mVp-p                                                                                                                                                                               |                            | -32                                    |     |                       |

| Line Inp                                  | out to Headphone Output Through                                                                                                                                                                     | h Mixing Path (HPOL and HPOR)                                                                                                                                                                   | •                          |                                        | '   |                       |

| R <sub>L</sub> = 16                       | $\Omega$ or 32 $\Omega$ , ALC = OFF, volume = 0                                                                                                                                                     | dB, speaker = powered down, analog mix                                                                                                                                                          | xing = enabled, no         | t capless mode                         |     |                       |

| DYNAM                                     | IC PERFORMANCE                                                                                                                                                                                      |                                                                                                                                                                                                 |                            |                                        |     |                       |

|                                           |                                                                                                                                                                                                     | 0.40                                                                                                                                                                                            |                            | 2.828                                  |     | Vp-p                  |

|                                           | Full-scale output voltage                                                                                                                                                                           | 0 dB                                                                                                                                                                                            |                            | 1                                      |     | Vrms                  |

| SNR                                       | Signal-to-noise ratio                                                                                                                                                                               | EIAJ, A-weighted                                                                                                                                                                                | 84                         | 93                                     |     | dB                    |

|                                           | Load resistance                                                                                                                                                                                     |                                                                                                                                                                                                 | 16                         |                                        |     | Ω                     |

| Digital I                                 | nput to Speaker Output Through                                                                                                                                                                      | DAC (SPOLP, SPOLN, SPORP, and SP                                                                                                                                                                | ORN): PCM3793              |                                        | I_  |                       |

| $R_1 = 8 \Omega$                          | Ω, ALC = OFF, volume = 0 dB, head                                                                                                                                                                   | dphone = powered down, analog mixing =                                                                                                                                                          | disabled                   |                                        |     |                       |

|                                           |                                                                                                                                                                                                     |                                                                                                                                                                                                 | uisabieu                   |                                        |     |                       |

| DYNAM                                     | IC PERFORMANCE                                                                                                                                                                                      |                                                                                                                                                                                                 | uisabieu                   |                                        |     |                       |

| DYNAM                                     |                                                                                                                                                                                                     |                                                                                                                                                                                                 | disabled                   | 2.52                                   |     | Vp-p                  |

| DYNAM                                     | Full-scale output voltage                                                                                                                                                                           | 0 dB                                                                                                                                                                                            | uisableu                   | 2.52                                   |     | Vp-p<br>Vrms          |

| DYNAM                                     | Full-scale output voltage                                                                                                                                                                           |                                                                                                                                                                                                 | uisableu 84                |                                        |     |                       |

|                                           |                                                                                                                                                                                                     | EIAJ, A-weighted                                                                                                                                                                                |                            | 0.9                                    |     | Vrms                  |

| SNR                                       | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise                                                                                                                 |                                                                                                                                                                                                 |                            | 0.9                                    |     | Vrms                  |

| SNR                                       | Full-scale output voltage Signal-to-noise ratio                                                                                                                                                     | EIAJ, A-weighted 400 mW, $R_L = 8\Omega$ , volume = 0 dB                                                                                                                                        | 84                         | 0.9                                    |     | Vrms<br>dB            |

| SNR<br>THD+N                              | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise  Load resistance                                                                                                | EIAJ, A-weighted 400 mW, $R_L = 8\Omega$ , volume = 0 dB 200 Hz, 140 mVp-p                                                                                                                      | 84                         | 0.9<br>93<br>0.3%                      |     | Vrms<br>dB            |

| SNR                                       | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise                                                                                                                 | EIAJ, A-weighted 400 mW, $R_L = 8\Omega$ , volume = 0 dB 200 Hz, 140 mVp-p 1 kHz, 140 mVp-p                                                                                                     | 84                         | 0.9<br>93<br>0.3%<br>-50<br>-45        |     | Vrms<br>dB            |

| SNR<br>THD+N<br>PSRR                      | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise  Load resistance  Power-supply rejection ratio                                                                  | EIAJ, A-weighted $400 \text{ mW, R}_{L} = 8\Omega, \text{ volume} = 0 \text{ dB}$ $200 \text{ Hz, } 140 \text{ mVp-p}$ $1 \text{ kHz, } 140 \text{ mVp-p}$ $20 \text{ kHz, } 140 \text{ mVp-p}$ | 84                         | 0.9<br>93<br>0.3%<br>-50<br>-45<br>-25 |     | Vrms<br>dB            |

| SNR THD+N PSRR                            | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise Load resistance  Power-supply rejection ratio  put to Speaker Output Through M                                  | EIAJ, A-weighted  400 mW, R <sub>L</sub> = 8Ω, volume = 0 dB  200 Hz, 140 mVp-p  1 kHz, 140 mVp-p  20 kHz, 140 mVp-p  ixing Path (SPOLP, SPOLN, SPORP, and                                      | 84<br>8<br>ad SPORN): PCM3 | 0.9<br>93<br>0.3%<br>-50<br>-45<br>-25 |     | Vrms<br>dB            |

| SNR THD+N  PSRR  Line Inp $R_L = 8\Omega$ | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise  Load resistance  Power-supply rejection ratio  out to Speaker Output Through M  ALC = OFF, volume = 0 dB, head | EIAJ, A-weighted $400 \text{ mW, R}_{L} = 8\Omega, \text{ volume} = 0 \text{ dB}$ $200 \text{ Hz, } 140 \text{ mVp-p}$ $1 \text{ kHz, } 140 \text{ mVp-p}$ $20 \text{ kHz, } 140 \text{ mVp-p}$ | 84<br>8<br>ad SPORN): PCM3 | 0.9<br>93<br>0.3%<br>-50<br>-45<br>-25 |     | Vrms<br>dB            |

| SNR THD+N  PSRR  Line Inp $R_L = 8\Omega$ | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise Load resistance  Power-supply rejection ratio  put to Speaker Output Through M                                  | EIAJ, A-weighted  400 mW, R <sub>L</sub> = 8Ω, volume = 0 dB  200 Hz, 140 mVp-p  1 kHz, 140 mVp-p  20 kHz, 140 mVp-p  ixing Path (SPOLP, SPOLN, SPORP, and                                      | 84<br>8<br>ad SPORN): PCM3 | 0.9<br>93<br>0.3%<br>-50<br>-45<br>-25 |     | Vrms<br>dB<br>Ω<br>dB |

| SNR THD+N  PSRR  Line Inp $R_L = 8\Omega$ | Full-scale output voltage  Signal-to-noise ratio  Total harmonic distortion + noise  Load resistance  Power-supply rejection ratio  out to Speaker Output Through M  ALC = OFF, volume = 0 dB, head | EIAJ, A-weighted  400 mW, R <sub>L</sub> = 8Ω, volume = 0 dB  200 Hz, 140 mVp-p  1 kHz, 140 mVp-p  20 kHz, 140 mVp-p  ixing Path (SPOLP, SPOLN, SPORP, and                                      | 84<br>8<br>ad SPORN): PCM3 | 0.9<br>93<br>0.3%<br>-50<br>-45<br>-25 |     | Vrms<br>dB            |

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data (unless otherwise noted).

|           | DADAMETER                         | PCI                                             | PCM3793RHB, PCM3794RHB |                      | UNIT |  |

|-----------|-----------------------------------|-------------------------------------------------|------------------------|----------------------|------|--|

|           | PARAMETER                         | TEST CONDITIONS                                 | MIN TYP                | MAX                  | UNIT |  |

| Line Inp  | out to Digital Output Through AD  | (AIN1L/R, AIN2L/R, AIN3L, and AIN3L/R)          |                        |                      |      |  |

| ALC = C   | DFF, microphone boost = 0 dB, PGA | a = 0 dB, speaker and headphone = powered down, | analog mixing = disab  | oled                 |      |  |

| DYNAM     | IIC PERFORMANCE                   |                                                 |                        |                      |      |  |

|           | Full cools input valtage          | 0.40                                            | 2.828                  |                      | Vp-p |  |

|           | Full-scale input voltage          | 0 dB                                            | 1                      |                      | Vrms |  |

|           | Dynamic range                     | EIAJ, A-weighted                                | 90                     |                      | dB   |  |

| SNR       | Signal-to-noise ratio             | EIAJ, A-weighted                                | 83 90                  |                      | dB   |  |

|           | Channel separation                |                                                 | 87                     |                      | dB   |  |

| THD+N     | Total harmonic distortion + noise | –1 dB                                           | 0.009%                 |                      |      |  |

| ANALO     | G INPUT                           | -                                               |                        | "                    |      |  |

|           | Center voltage                    |                                                 | 0.5 V <sub>CC</sub>    |                      | V    |  |

|           | Input impedance                   |                                                 | 10 20                  |                      | kΩ   |  |

| Microph   | none Bias                         |                                                 |                        |                      |      |  |

| ALC = C   | OFF, microphone boost = 0 dB, PGA | a = 0 dB, speaker and headphone = powered down, | analog mixing = disab  | oled                 |      |  |

|           | Bias voltage                      |                                                 | 0.75 V <sub>CC</sub>   |                      | V    |  |

|           | Bias source current               |                                                 | 2                      |                      | mA   |  |

|           | Output noise                      |                                                 | 14                     |                      | μV   |  |

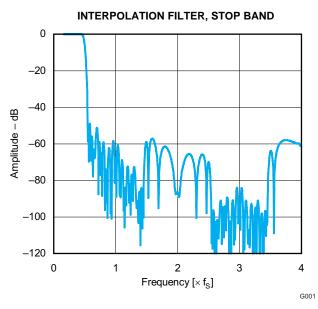

| Filter Cl | haracteristics                    |                                                 |                        |                      | ·    |  |

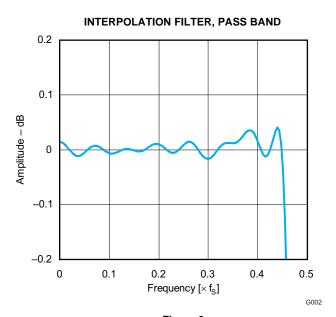

| INTERP    | OLATION FILTER FOR DAC            |                                                 |                        |                      |      |  |

|           | Pass band                         |                                                 |                        | 0.454 f <sub>S</sub> |      |  |

|           | Stop band                         | 0.54                                            | 6 f <sub>S</sub>       | -                    |      |  |

|           | Pass-band ripple                  |                                                 | <del></del>            | ±0.04                | dB   |  |

|           | Stop-band attenuation             |                                                 | -50                    |                      | dB   |  |

|           | Group delay                       |                                                 | 19/f <sub>s</sub>      |                      | S    |  |

|           | De-emphasis error                 |                                                 | ±0.1                   |                      | dB   |  |

| ANALO     | G FILTER FOR DAC                  | <u> </u>                                        |                        |                      |      |  |

|           | Frequency response                | f = 20 kHz                                      | ±0.2                   |                      | dB   |  |

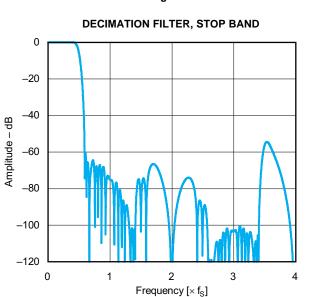

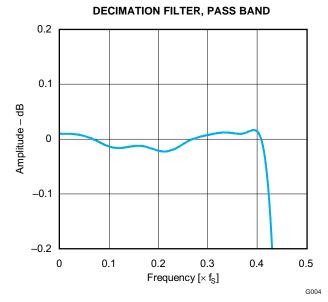

| DECIMA    | ATION FILTER FOR ADC              | <u> </u>                                        |                        |                      |      |  |

|           | Pass band                         |                                                 |                        | 0.408 f <sub>S</sub> |      |  |

|           | Stop band                         | 0.59                                            | 1 f <sub>S</sub>       | -                    |      |  |

|           | Pass-band ripple                  |                                                 | <del>-</del>           | ±0.02                | dB   |  |

|           | Stop-band attenuation             | f < 3.268 f <sub>S</sub>                        | -60                    |                      | dB   |  |

|           | Group delay                       |                                                 | 17/f <sub>S</sub>      |                      | s    |  |

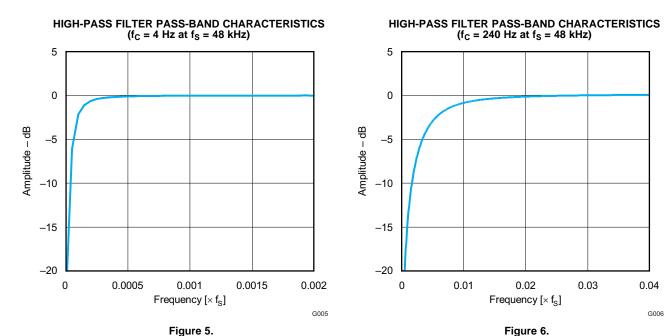

| HIGH-P    | ASS FILTER FOR ADC                |                                                 | . 3                    |                      | -    |  |

|           | <del>-</del>                      | $-3 \text{ dB, } f_c = 4 \text{ Hz}$            | 3.74                   |                      |      |  |

|           |                                   | $-0.5 \text{ dB, } f_c = 4 \text{ Hz}$          | 10.66                  |                      |      |  |

|           |                                   | $-0.1 \text{ dB}, f_c = 4 \text{ Hz}$           | 24.2                   |                      |      |  |

|           | Frequency response                | -3 dB, f <sub>c</sub> = 240 Hz                  | 235.68                 |                      | Hz   |  |

|           |                                   | $-0.5 \text{ dB}, t_c = 240 \text{ Hz}$         | 609.95                 |                      |      |  |

|           |                                   | 5.5 52, ic - 2 10 112                           | 505.50                 |                      |      |  |

TEXAS INSTRUMENTS www.ti.com

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = 25$ °C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data (unless otherwise noted).

|                 | DADAMETED                   | TEST COMPLIANCE                | PCM3793RI | HB, PCM3794 | IRHB  | LINUT |

|-----------------|-----------------------------|--------------------------------|-----------|-------------|-------|-------|

|                 | PARAMETER                   | TEST CONDITIONS                | MIN       | TYP         | MAX   | UNIT  |

| Powe            | r Supply and Supply Current |                                | ·         |             |       |       |

| V <sub>IO</sub> |                             | V <sub>IO</sub>                | 1.71      | 3.3         | 3.6   |       |

| $V_{DD}$        | Voltage range               | $V_{DD}$                       | 1.71      | 3.3         | 3.6   | VDC   |

| $V_{CC}$        |                             | V <sub>CC</sub>                | 2.4       | 3.3         | 3.6   | VDC   |

| $V_{PA}$        |                             | $V_{PA}$                       | 2.4       | 3.3         | 3.6   |       |

|                 | Complex accompant           | BPZ input, all active, no load |           | 24.3        | 35    | mA    |

|                 | Supply current              | All inputs are held static     |           | 9           | 50    | μΑ    |

|                 | Daniel Parkardan            | BPZ input                      |           | 80.2        | 115.5 | mW    |

|                 | Power dissipation           | All inputs are held static     |           | 30          | 165   | μW    |

| Temp            | erature Condition           |                                |           |             |       |       |

|                 | Operation temperature       |                                | -40       |             | 85    | °C    |

| $\theta_{JA}$   | Thermal resistance          |                                |           | 30          |       | °C/W  |

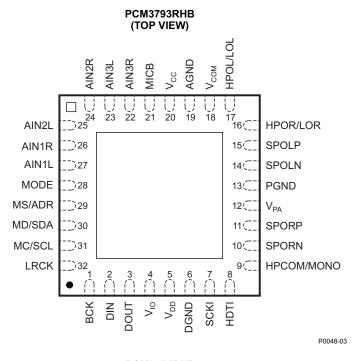

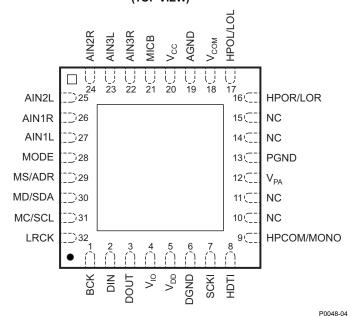

#### **PIN ASSIGNMENTS**

#### PCM3794RHB (TOP VIEW)

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

#### **Table 1. TERMINAL FUNCTIONS**

|                  | TERMINAL   |            |     | DEGODITECT                                                                |

|------------------|------------|------------|-----|---------------------------------------------------------------------------|

| NAME             | PCM3793RHB | PCM3794RHB | I/O | DESCRIPTION                                                               |

| AGND             | 19         | 19         | _   | Ground for analog                                                         |

| AIN1L            | 27         | 27         | ı   | Analog input 1 for L-channel                                              |

| AIN1R            | 26         | 26         | ı   | Analog input 1 for R-channel                                              |

| AIN2L            | 25         | 25         | I   | Analog input 2 for L-channel                                              |

| AIN2R            | 24         | 24         | ı   | Analog input 2 for R-channel                                              |

| AIN3L            | 23         | 23         | ı   | Analog input 3 for L-channel                                              |

| AIN3R            | 22         | 22         | ı   | Analog input 3 for R-channel                                              |

| BCK              | 1          | 1          | I/O | Serial bit clock                                                          |

| DGND             | 6          | 6          | -   | Digital ground                                                            |

| DIN              | 2          | 2          | I   | Serial audio data input                                                   |

| DOUT             | 3          | 3          | 0   | Serial audio data output                                                  |

| HDTI             | 8          | 8          | I   | Headphone plug insertion detection                                        |

| HPCOM/MONO       | 9          | 9          | 0   | Headphone common/mono line output                                         |

| HPOL/LOL         | 17         | 17         | 0   | Headphone/lineout for R-channel                                           |

| HPOR/LOR         | 16         | 16         | 0   | Headphone/lineout for L-channel                                           |

| LRCK             | 32         | 32         | I/O | Left and right channel clock                                              |

| MC/SCL           | 31         | 31         | ı   | Mode control clock for three-wire/two-wire interface                      |

| MD/SDA           | 30         | 30         | I/O | Mode control data for three-wire/two-wire interface                       |

| MICB             | 21         | 21         | 0   | Microphone bias source output                                             |

| MODE             | 28         | 28         | I   | Two- or three-wire interface selection (LOW: SPI, HIGH: I <sup>2</sup> C) |

| MS/ADR           | 29         | 29         | ı   | Mode control select for three-wire/two-wire interface                     |

| PGND             | 13         | 13         | _   | Ground for speaker power amplifier                                        |

| SCKI             | 7          | 7          | ı   | System clock                                                              |

| SPOLN            | 14         | _          | 0   | Speaker output L-channel for negative (PCM3793)                           |

| SPOLP            | 15         | _          | 0   | Speaker output L-channel for positive (PCM3793)                           |

| SPORN            | 10         | _          | 0   | Speaker output R-channel for negative (PCM3793)                           |

| SPORP            | 11         | _          | 0   | Speaker output R-channel for positive (PCM3793)                           |

| V <sub>CC</sub>  | 20         | 20         | -   | Analog power supply                                                       |

| V <sub>COM</sub> | 18         | 18         | _   | Analog common voltage                                                     |

| $V_{DD}$         | 5          | 5          | -   | Power supply for digital core                                             |

| V <sub>IO</sub>  | 4          | 4          | _   | Power supply for digital I/O                                              |

| $V_{PA}$         | 12         | 12         | -   | Power supply for power amplifier                                          |

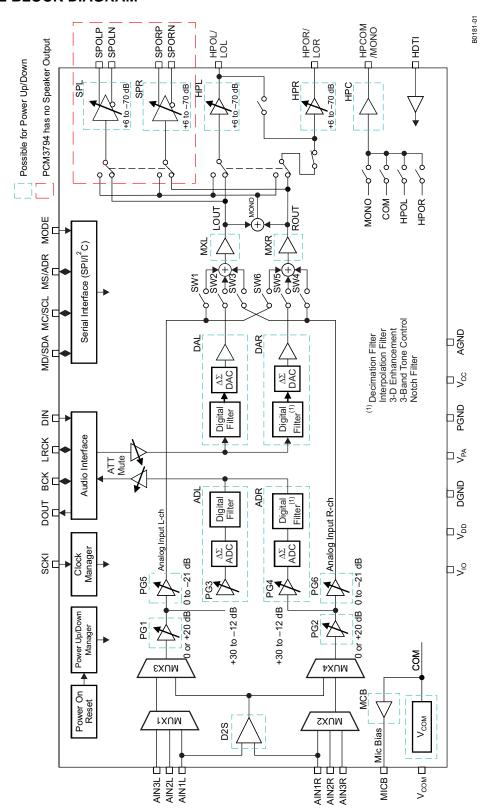

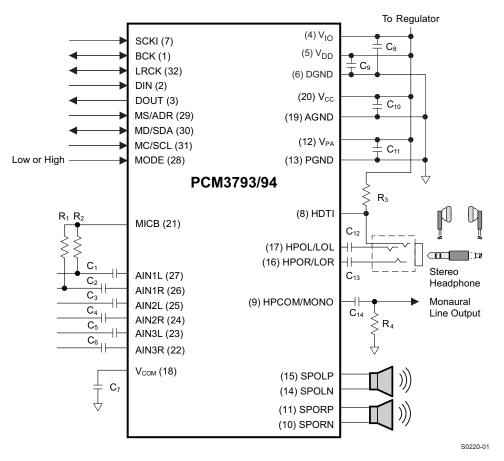

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **TYPICAL PERFORMANCE CURVES**

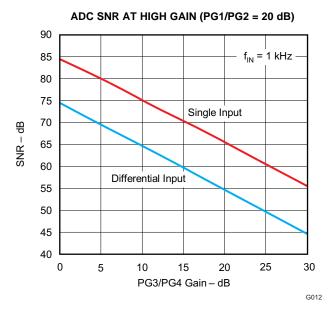

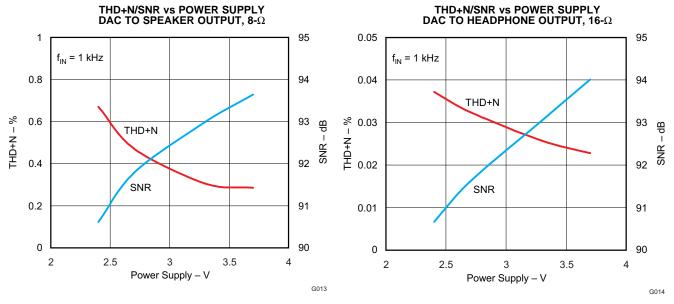

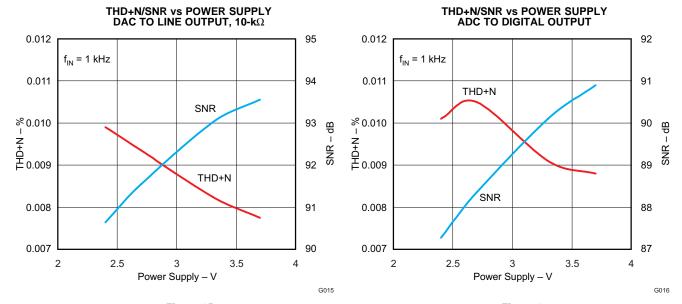

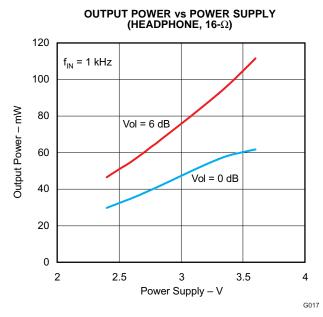

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 8 \text{ to } 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

Figure 3.

Figure 2.

Figure 4.

G003

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 8 \text{ to } 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

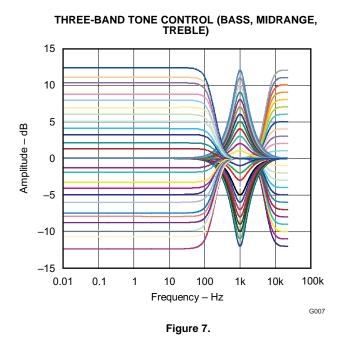

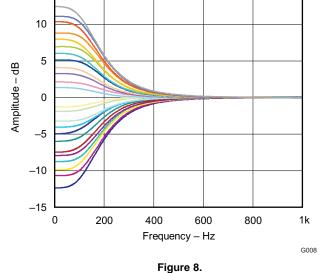

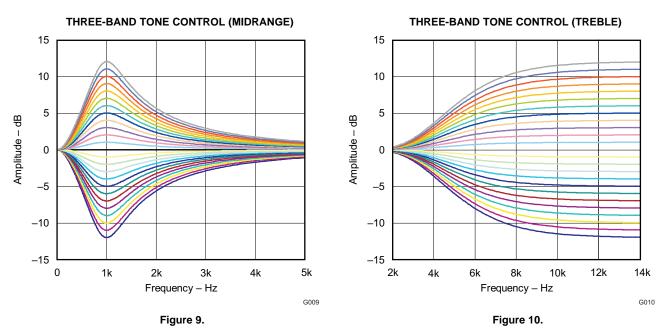

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 44.1 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

15

THREE-BAND TONE CONTROL (BASS)

All specifications at  $T_A = 25$ °C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 44.1$  kHz, system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

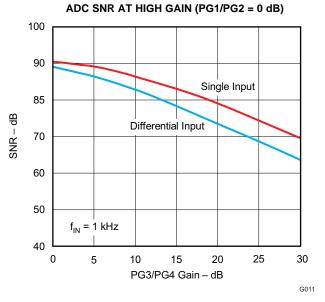

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

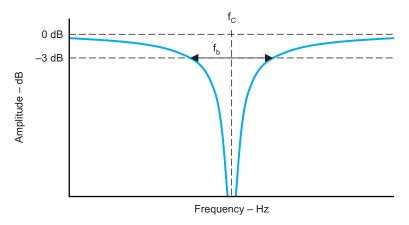

Figure 12.

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

Figure 13. Figure 14.

Figure 15. Figure 16.

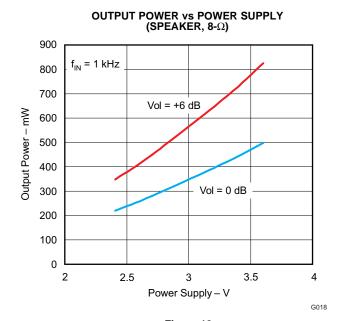

All specifications at  $T_A = 25$  °C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

Figure 17.

Figure 18.

Figure 19.

Figure 20.

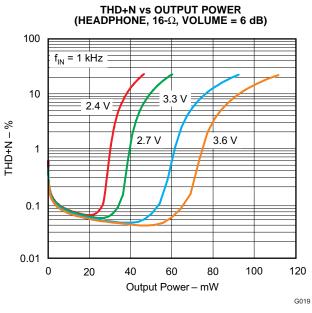

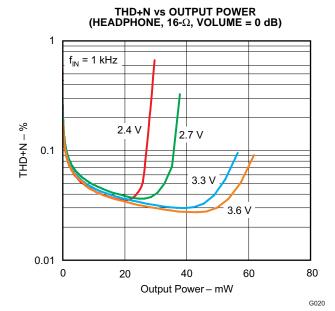

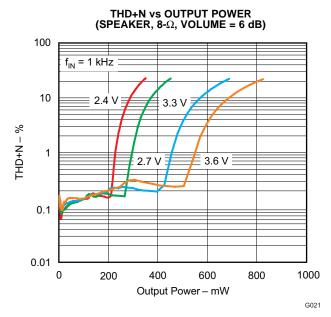

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted.

#### Figure 21.

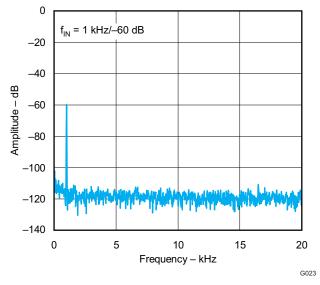

# OUTPUT SPECTRUM (DAC TO HEADPHONE OUTPUT, 16- $\Omega$ )

Figure 23.

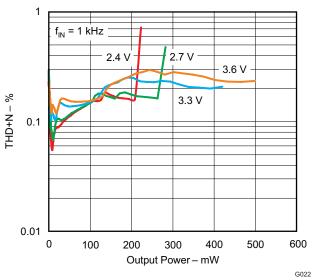

# THD+N vs OUTPUT POWER (SPEAKER, 8- $\Omega$ , VOLUME = 0 dB)

Figure 22.

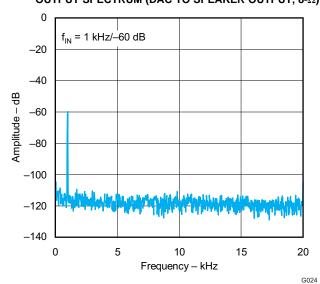

# OUTPUT SPECTRUM (DAC TO SPEAKER OUTPUT, $8-\Omega$ )

Figure 24.

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

#### PCM3793/94 DESCRIPTION

#### **Analog Input**

The AIN1L, AIN1R, AIN2L, AIN2R, AIN3L, and AIN3R pins can be used as microphone or line inputs with selectable 0- or 20-dB boost and 1-Vrms input. All analog inputs have high input impedance (20  $k\Omega$ ), which is not changed by gain settings. One pair of inputs is selected by register 87 (AIL[1:0], AIR[1:0]). AIN1L and AIN1R can be used as monaural differential inputs.

#### **Gain Settings for Analog Input**

Analog signals can be adjusted from 30 dB to -12 dB in 1-dB steps following the 0- or 20-dB boost amplifier. The gain level can be set for each channel by registers 79 and 80 (ALV[5:0], ARV[5:0]).

#### A/D Converter

The ADC includes a multilevel delta-sigma modulator, aliasing filter, decimation filter, high-pass filter, and notch filter and can accept a 1-Vrms full-scale voltage input. The decimation filter has a digital soft mute controlled by register 81 (RMUL, RMUR). The high-pass filter can be disabled by register 81 (HPF[1:0]) and the notch filter can be disabled by registers 96 to 104 if it is not necessary to cancel a dc offset or compensate for wind noise.

#### **D/A Converter**

The DAC includes a multilevel delta-sigma modulator and interpolation filter. These can be used to obtain high PSRR, low jitter sensitivity, and low out-of-band noise quickly and easily. The interpolation filter includes digital attenuator, digital soft mute, three-band tone control (bass, midrange and treble), and 3-D sound controlled by registers 92 to 95. The de-emphasis filter (32, 44.1 and 48 kHz) is controlled by registers 68 to 70 (ATL[5:0], ATR[5:0], PMUL, PMUR, DEM[1:0]). Oversampling rate control can reduce out-of-band noise when operating at low sampling rate by using register 70 (OVER).

#### **Common Voltage**

The  $V_{COM}$  pin is normally biased to 0.5  $V_{CC}$ , and it provides the common voltage to internal circuitry. It is recommended that a 10- $\mu$ F capacitor be connected between this pin and ground to provide clean voltage and avoid pop noise. The PCM3793/94 may have a little pop noise on each analog output if a capacitor smaller than 10  $\mu$ F is used.

#### **Line Output**

The HPOL/LOL and HPOR/LOR and HPCOM/MONO pins can be used as a monaural single-ended, monaural differential, or stereo single-line output with 1- $V_{rms}$  output by register 74 (HPS[1:0]). The line outputs can drive a 10- $k\Omega$  load. These outputs include an analog volume amplifier, except for the HPCOM/MONO pin that can be set from 6 dB to -70 dB and mute with 0.5-, 1-, 2- or 4-dB steps for each output, as controlled by registers 64 and 65 (HLV[5:0], HRV[5:0], HMUL, HMUR). A dc blocking capacitor is not required when connecting to an external speaker amplifier with monaural differential input. The center voltage is 0.5  $V_{CC}$  with zero data input.

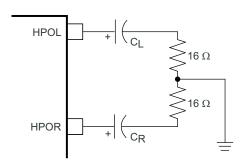

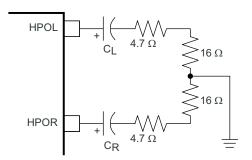

#### **Headphone Output**

The HPOL/LOL, HPOR/LOR, and HPCOM/MONO pins are stereo, monaural, or monaural differential headphone outputs with more than 30 or 40 mWrms output power into a 32- or 16- $\Omega$  load, either through a dc blocking capacitor or without a capacitor, as selected by register 74 (HPS[2:0]). These outputs include analog volume amplifiers, except for the HPCOM/MONO pin, which can be set from 6 dB to –70 dB with 0.5-, 1-, 2- or 4-dB steps for each output using registers 64 and 65 (HLV[5:0], HRV[5:0], HMUL, HMUR). The center voltage is 0.5  $V_{CC}$  with zero data input.

#### **Headphone Plug Insertion Detection**

The HDTI pin detects the insertion status of headphone plug and writes the status to register 77 (HPDS), which can be read by the I<sup>2</sup>C interface. The polarity of the status indication can be inverted by register 75 (HPDP). The headphone and speaker amplifiers are disabled or enabled automatically by headphone plug insertion/extractrion if register 75, HPDE = 1. They are controlled by register settings if register 75, HPDE = 0. HPCOM/MONO is not affected by the status when register 74, CMS[0] = 1.

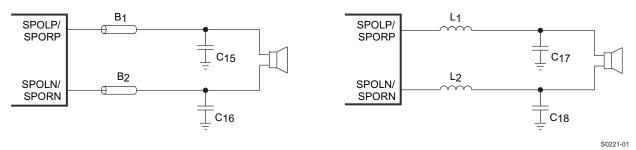

#### Speaker Output (Class-D, PCM3793)

The SPOLP, SPOLN and SPORP, SPORN pins are stereo or mono speaker differential outputs (BTL) with a maximum of 700 mWrms ( $V_{PA} = 3.6$  V, volume = 6 dB) into an 8- $\Omega$  load. The digital speaker amplifier offers maximum battery life and minimum heat, eliminates the LC low-pass filter, and includes analog volume amplification for each output from 6 dB to -70 dB with 0.5-, 1-, 2- or 4-dB steps, which can be set by register 66, 67 (SLV[5:0], SLR[5:0]). Spectrum spreading technology and selectable switching frequency to reduce EMI noise is controlled by register 71 (DFQ[2:0], SPS[1:0] and SPSE). The speaker amplifiers have a thermal shutdown circuit which detects when the device temperature reaches approximately 150°C; then the speaker amplifier is powered down.

#### **Analog Mixing and Bypass**

Mixing amplifiers (MXL, MXR) mix gain-controlled analog inputs from the AIN pins which have bypassed ADC and DAC and direct the mixed signal to the headphone or speaker outputs. Analog mixing is controlled by register 87 (AD2S, AIR[1:0], AIL[1:0]), register 88 (MXR[2:0], MXL[2:0]), and register 89 (GMR[2:0], GML[2:0]). The analog mixing functions are suitable for FM radio, headset, and another analog sources without an ADC.

#### Microphone Bias

The MICB pin is the microphone bias source for an external microphone and can provide 2 mA (typical) bias current.

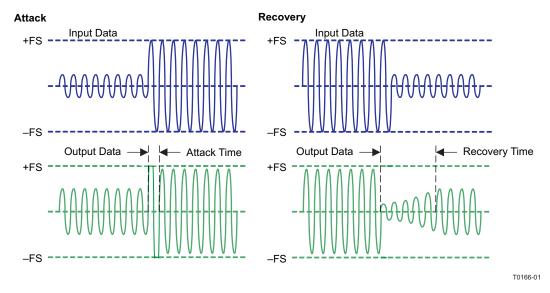

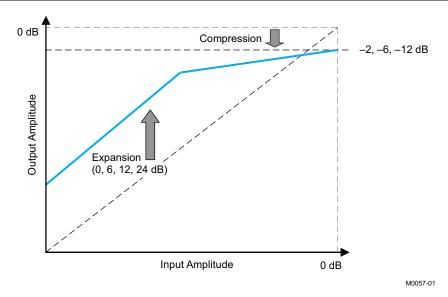

#### Automatic Level Control (ALC) for Recording

The sound for microphone recording should be expanded to a suitable level without saturation. The digitally controlled automatic level control (ALC) provides automatic expansion for small input signals and compression for large input signals while recording. The expansion level, compression level, attack time, and recovery time can be selected by register 83. The register 83 description explains the details of these settings.

#### 3-D Sound

A 3-D sound effect is provided by mixing L-channel and R-channel data with band pass filter that can be controlled two parameters, mixing ratio and band pass filter characteristic by register 95 (3DP[3:0], 3FLO). The 3-D sound effect can be applied to the DAC digital input or ADC digital output, as selected by register 95 (SDAS).

#### **Three-Band Tone Control**

Tone control has bass, midrange, and treble controls that can be adjusted from 12 dB to -12 dB in 1-dB steps by registers 92 to 94 (LGA[4:0], MGA[4:0] and HGA[4:0]). Register 92 (LPAE) attenuates the digital input signal automatically to prevent clipping of the output signal at settings above 0 dB for bass control. LPAE has no effect on midrange and treble controls.

#### **High-Pass Filter and Notch Filter**

The high-pass filter eliminates the dc offset of the ADC analog signal and can be set for a cutoff frequency of 4 Hz or 240 Hz at of 48-kHz sampling frequency by register 81 (HPF[1:0]). A register 95 (SDAS) selection applies the filter to either the DAC digital input or the ADC digital output.

Notch filters are provided to remove noise of a particular frequency, such as CCD noise, motor noise, or other mechanical noise in a particular application. The PCM3793/94 has two notch filters for which the center frequency and frequency bandwidth can be programmed by registers 96 to 104. A register 95 (SDAS) selection applies the filter to either the DAC digital input or the ADC digital output.

#### **Digital Monaural Mixing**

Register 96 (MXEN) enables or disables the internal mixing of stereo digital data to monaural digital data.

#### **Zero-Cross Detection**

Zero-cross detection minimizes audible zipper noise while changing analog volume and digital attenuation. This function can be applied to digital input or digital output by register 86 (ZCRS).

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

#### **Short Protection**

The short-circuit protection on each headphone output prevents damage to the device while an output is shorted to  $V_{PA}$ , an output is shorted to PGND, or any two outputs are shorted together. When the short circuit is detected on the outputs, the PCM3793/94 powers down the shorted amplifier at once. The short-protection status can be monitored by reading register 77 (STHC, STHL, SCHR) through the  $I^2C$  interface. Short-circuit protection operates in any enabled headphone amplifier.

#### **Thermal Protection**

The thermal protection on the speaker amplifier prevents damage to the device when the internal die temperature exceeds approximately 150°C. Once the die temperature exceeds the thermal set point, all analog outputs are powered down. This status can be reset by setting register 76 (RLSR, RLSL) and can be watched by reading register 77 (STSR, STSL) on the two-wire (I<sup>2</sup>C) interface. Thermal protection operates in any enabled speaker amplifier.

#### **Pop-Noise Reduction Circuit**

The pop-noise reduction circuit prevents audible noise when turning the power supply on/off and powering the device up/down in portable applications. It is recommended to establish the register settings in the sequence that is shown in Table 3 and Table 4. No particular external parts are required, and power-supply sequencing is not necessary.

#### Power Up/Down for Each Module

Using register 72 (PMXL, PMXR), register 73 (PBIS, PDAR, PDAL, PHPC, PHPR, PHPL, PSPR, PSPL), register 82 (PAIR, PAIL, PADS, PMCB, PADL), and register 90 (PCOM), unused modules can be powered down to minimize power consumption (7 mW during playback only and 13 mW when recording only).

#### **Digital Interface**

All digital I/O pins can interface at various power supply voltages. The  $V_{IO}$  pin can be connected to a 1.71-V to 3.6-V power supply.

#### **Power Supply**

The  $V_{CC}$  pin and the  $V_{PA}$  pin can be connected to 2.4 V to 3.6 V. The same voltage must be applied to both pins. The  $V_{DD}$  pin and the  $V_{IO}$  pin can be connected to 1.71 V to 3.6 V. A different voltage can be applied to each of these pins (for example,  $V_{DD} = 1.8$  V,  $V_{IO} = 3.3$  V).

#### **DESCRIPTION OF OPERATION**

#### **System Clock Input**

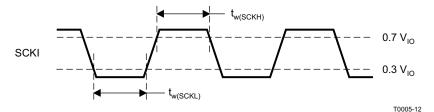

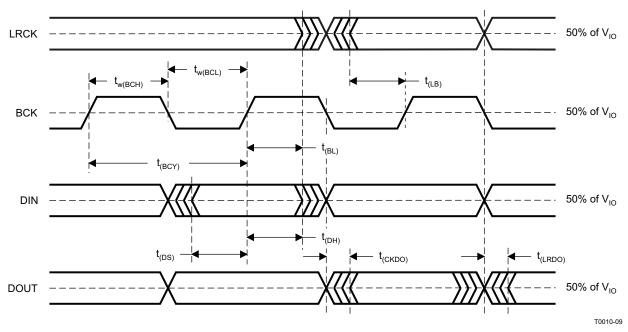

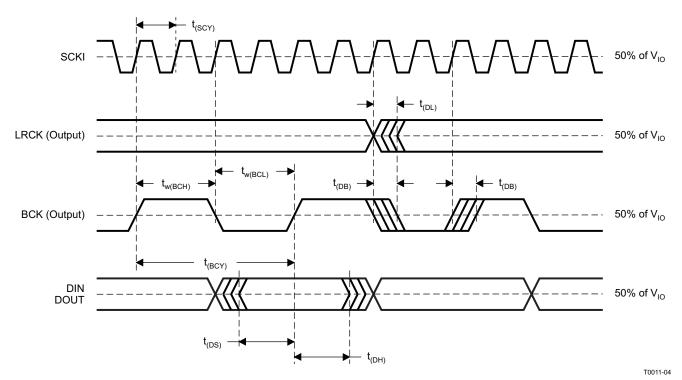

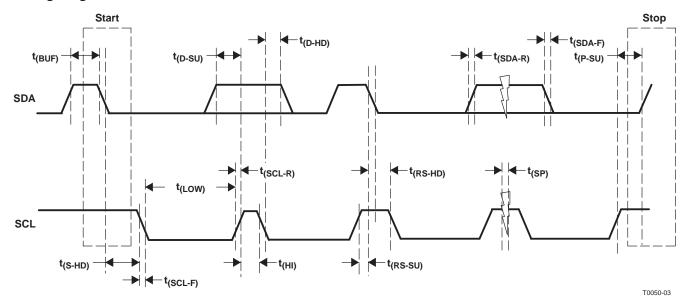

The PCM3793/94 can accept clocks of various frequencies without a PLL. They are used for clocking the digital filters and automatic level control and delta-sigma modulators and are classified as common-audio and application-specific clocks. Table 2 shows frequencies of the common-audio clock and application-specific clock. Figure 25 shows the timing requirements for system clock inputs. The sampling rate and frequency of the system clocks are determined by the settings of register 86 (MSR[2:0]) and register 85 (NPR[5:0]). Note that the sampling rate of the application-specific clock has a little sampling error.

Table 2. System Clock Frequencies

| CLOCK                      | FREQUENCIES                                            |

|----------------------------|--------------------------------------------------------|

| Common-audio clock         | 11.2896, 12.288, 16.9344, 18.432 MHz                   |

| Application-specific clock | 12, 13, 13.5, 24, 26, 27, 19.2, 19.68, 38.4, 39.36 MHz |

| PARAMETERS                        | SYMBOL               | MIN | UNITS |

|-----------------------------------|----------------------|-----|-------|

| System-clock pulse duration, high | t <sub>w(SCKH)</sub> | 7   | ns    |

| System-clock pulse duration, low  | t <sub>w(SCKL)</sub> | 7   | ns    |

Figure 25. System Clock Timing

#### **Power-On Reset and System Reset**

The power-on-reset circuit outputs a reset signal, typically at  $V_{DD} = 1.2 \text{ V}$ , and this circuit does not depend on the voltage of other power supplies (V<sub>CC</sub>, V<sub>PA</sub> and V<sub>IO</sub>). Internal circuits are cleared to default status, then signals are removed from all analog and digital outputs. The PCM3793/94 does not require any power supply sequencing. Register data must be written after turning all power supplies on.

System reset is enabled by setting register 85 (SRST), and all register are cleared automatically. All circuits are reset to their default status at once. Note that the PCM3793/94 has audible pop noise on the analog outputs when enabling SRST.

#### Power On/Off Sequence

To reduce audible pop noise, a sequence of register settings is required after turning all power supplies on when powering up, or before turning the power supplies off when powering down. If some modules are not required for a particular application or operation, they should be placed in the power-down state after performing the power-on sequence. The recommended power-on and power-off sequences are shown in Table 3 and Table 4, respectively.

**Table 3. Recommended Power-On Sequence**

| STEP | REGISTER<br>SETTINGS | NOTE                                                                                  |

|------|----------------------|---------------------------------------------------------------------------------------|

| 1    | _                    | Turn on all power supplies <sup>(1)</sup>                                             |

| 2    | 4027h                | Headphone amplifier L-ch volume (–6 dB) <sup>(2)</sup>                                |

| 3    | 4127h                | Headphone amplifier R-ch volume (–6 dB) <sup>(2)</sup>                                |

| 4    | 4227h                | Speaker amplifier L-ch volume (–6 dB) <sup>(2)</sup>                                  |

| 5    | 4327h                | Speaker amplifier R-ch volume (–6 dB) <sup>(2)</sup>                                  |

| 6    | 4427h                | Digital attenuator L-ch (–24 dB) <sup>(2)</sup>                                       |

| 7    | 4527h                | Digital attenuator R-ch (–24 dB) <sup>(2)</sup>                                       |

| 8    | 4620h                | DAC audio interface format (left-justified) <sup>(3)</sup>                            |

| 9    | 4BC0h                | Headphone detection enable and inverting polarity. Short and thermal detection enable |

| 10   | 5102h                | ADC audio interface format (left-justified) <sup>(3)</sup>                            |

| 11   | 5A10h                | V <sub>COM</sub> ramp up/down time control. PG1, PG2 gain control (0 dB)              |

| 12   | 49E0h                | DAC (DAL, DAR) and analog bias power up                                               |

| 13   | 5601h                | Zero-cross detection enable                                                           |

| 14   | 4803h                | Analog mixer (MXL, MXR) power up                                                      |

| 15   | 5811h                | Analog mixer input (SW2, SW5) select                                                  |

| 16   | 49FCh                | Headphone amplifier (HPL, HPR, HPC) power up                                          |

<sup>(1)</sup> Power supply sequencing is not required. It is recommended to set register data with system clock input after turning all power supplies

Any level is acceptable for volume or attenuation. Level should be resumed by register data recorded when system power off.

Audio interface format should be set to match the DSP or decoder being used. (3)

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

#### Table 3. Recommended Power-On Sequence (continued)

| STEP | REGISTER<br>SETTINGS                                          | NOTE                                                               |  |  |  |

|------|---------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| 17   | 4C03h                                                         | Speaker amplifier shut down release                                |  |  |  |

| 18   | 4A01h                                                         | V <sub>COM</sub> power up                                          |  |  |  |

| 19   | 523Fh                                                         | Analog front end (ADL, ADR, D2S, MCB, PG1, 2, 5, 6) power up       |  |  |  |

| 20   | 5711h                                                         | Analog input (MUX3, MUX4) select. Analog input (MUX1, MUX2) select |  |  |  |

| 21   | 4F0Ch                                                         | Analog input L-ch (PG3) volume (0 dB) <sup>(2)</sup>               |  |  |  |

| 22   | 22 500Ch Analog input R-ch (PG4) volume (0 dB) <sup>(2)</sup> |                                                                    |  |  |  |

| 23   | _                                                             | Any settings for other devices or wait time <sup>(4)(5)</sup>      |  |  |  |

| 24   | 49FFh                                                         | Speaker amplifier (SPL, SPR) power up (5)                          |  |  |  |

<sup>(4)</sup> The PCM3793 requires time for  $V_{COM}$  to reach the common level from GND level. The delay depends on the capacitor value for  $V_{COM}$  and the setting of register 90 CMT[1:0]. Wait time [s] =  $4 \times C_{VCOM} \times R_{CMT}$

#### **Table 4. Recommended Power-Off Sequence**

| STEP | REGISTER<br>SETTINGS | NOTE                                                                                           |

|------|----------------------|------------------------------------------------------------------------------------------------|

| 1    | 447Fh                | DAC L-ch digital soft-mute enable <sup>(1)</sup>                                               |

| 2    | 457Fh                | DAC R-ch digital soft-mute enable <sup>(1)</sup>                                               |

| 3    | 5132h                | ADC L-ch/R-ch digital soft-mute enable, ADC audio interface format (left-justified) (2)        |

| 4    | 5811h                | Analog mixer input (SW2, SW5) Select                                                           |

| 5    | 49FFh                | Headphone amplifier (HPL, HPR, HPC) power up (4), speaker amplifier (SPL, SPR) power up (3)(4) |

| 6    | 5200h                | Analog front end (ADL, ADR, D2S, MCB, PG1, 2, 5, 6) power down                                 |

| 7    | 5A10h                | V <sub>COM</sub> ramp up/down time control, PG1, PG2 gain control (0 dB)                       |

| 8    | 4A00h                | V <sub>COM</sub> power down                                                                    |

| 9    | _                    | Wait time (100 ms)                                                                             |

| 10   | 5A00h                | V <sub>COM</sub> ramp up/down time control                                                     |

| 11   | _                    | Wait time (100 ms)                                                                             |

| 12   | 5A20h                | V <sub>COM</sub> ramp up/down time control                                                     |

| 13   | _                    | Wait time (4000 ms)                                                                            |

| 14   | 5A30h                | V <sub>COM</sub> ramp up/down time control                                                     |

| 15   | 49E0h                | Headphone amplifier (HPL, HPR, HPC) power down, speaker amplifier (SPL, SPR) power down        |

| 16   | 4800h                | Analog mixer (MXL, MXR) power down                                                             |

| 17   | 4900h                | DAC (DAL, DAR) and analog bias power down                                                      |

| 18   | _                    | Turn off all power supplies (5)                                                                |

- (1) Any level is acceptable for volume or attenuation.

- (2) Audio interface format should be set according to DSP or decoder.

- (3) PCM3794 has no speaker amplifier.

- (4) These modules must be powered up during the power-down sequence.

- (5) Power supply sequencing is not required. It is recommended to turn off all power supply after register settings with system clock input.

#### **Power-Supply Current**

The current consumption of the PCM3793/94 depends on power up/down status of each circuit module. In order to reduce the power consumption, disabling each module is recommended when it is not used in an application or operation. Table 5 shows the current consumption in some states.

<sup>(5)</sup> The PCM3794 does not require this setting because it has no speaker output.

SLES193C-AUGUST 2006-REVISED FEBRUARY 2007

# **Table 5. Power Consumption Table**

| OPERATION MODE                                                                  | F                          | OWER SU                    | PPLY CURI                  | RENT [mA]                  |                         | PD [mW]                               | PD [mW]                            |

|---------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------------------------|---------------------------------------|------------------------------------|

|                                                                                 | V <sub>DD</sub><br>(1.8 V) | V <sub>DD</sub><br>(3.3 V) | V <sub>CC</sub><br>(3.3 V) | V <sub>PA</sub><br>(3.3 V) | V <sub>IO</sub> (3.3 V) | TOTAL<br>(V <sub>DD</sub> = 1.8<br>V) | TOTAL<br>(V <sub>DD</sub> = 3.3 V) |

| All Power Down                                                                  | 0                          | 0                          | 0.007                      | 0.002                      | 0                       | 0.03                                  | 0.03                               |

| All Active                                                                      | 2.5                        | 5.1                        | 7.5                        | 11.6                       | 0.1                     | 67.7                                  | 80.2                               |

| PLAYBACK WITH DIGITAL INPUT                                                     |                            |                            | •                          |                            |                         |                                       |                                    |

| Line output and headphone output                                                | 1.18                       | 2.51                       | 1.79                       | 0.54                       | 0.09                    | 10.1                                  | 16.3                               |

| Headphone output with sound effect                                              | 1.81                       | 3.84                       | 1.79                       | 0.54                       | 0.09                    | 11.2                                  | 20.7                               |

| Capless headphone output                                                        | 1.18                       | 2.51                       | 1.8                        | 0.75                       | 0.09                    | 10.8                                  | 17.0                               |

| Headphone output with line input (AIN2L/AIN2R)                                  | 1.18                       | 2.52                       | 2.09                       | 0.54                       | 0.09                    | 11.1                                  | 17.3                               |

| Headphone output with mono microphone input (AIN1L, 20 dB)                      | 1.18                       | 2.52                       | 2.5                        | 0.54                       | 0.09                    | 12.5                                  | 18.6                               |