## THIS SPEC IS OBSOLETE

Spec No: 002-08401

Spec Title: MB39C811 ULTRA LOW POWER BUCK PMIC

SOLAR/VIBRATIONS ENERGY HARVESTING

Replaced by: NONE

## Ultra Low Power Buck PMIC Solar/Vibrations Energy Harvesting

### Description

The MB39C811 is the high efficient buck (Power Management) DC/DC converter IC which adopts the all-wave bridge rectifier using the low-dissipation and the comparator system. It achieves the energy harvest solution for the energy source of the high output impedance such as the piezoelectric transducer.

It is possible to select from eight preset output voltages and supply up to 100 mA of the output current.

### Features

- Quiescent current (No load, Output in regulation): 1.5  $\mu$ A

- Quiescent current (VIN = 2.5 V UVLO): 550 nA

- Integrated Low Loss Full-Wave Bridge Rectifier

- VIN input voltage range: 2.6 V to 23 V

- Preset output voltage: 1.5 V, 1.8 V, 2.5 V, 3.3 V, 3.6 V, 4.1 V, 4.5 V, 5.0 V

- Output current: Up to 100 mA

- Protection functions

- Shunt for input protection: VIN  $\geq$  21 V, Up to 100 mA Pull-down

- Over current limit

- I/O power-good detection signal output

- Wireless HVAC sensor

- Stand-alone nano-power buck regulator

### Applications

- Light energy harvesting

- Piezoelectric energy harvesting

- Electro-Mechanical energy harvesting

### Online Design Simulation Easy DesignSim

This product supports the web-based design simulation tool.

It can easily select external components and can display useful information.

Please access from the following URL.

<http://cypress.transim.com/login.aspx>

## Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| <b>Description</b> .....                                          | 1  |

| <b>Features</b> .....                                             | 1  |

| <b>Applications</b> .....                                         | 1  |

| 1. Pin Assignments .....                                          | 3  |

| 2. Pin Descriptions.....                                          | 4  |

| 3. Block Diagram.....                                             | 5  |

| 4. Absolute Maximum Ratings .....                                 | 6  |

| 5. Recommended Operating Conditions .....                         | 7  |

| 6. Electrical Characteristics .....                               | 8  |

| 6.1 DC Characteristics.....                                       | 8  |

| 6.2 Characteristics of Built-in Bridge Rectification Circuit..... | 9  |

| 6.3 AC Characteristics (Input/Output Power-Good).....             | 9  |

| 7. Function.....                                                  | 10 |

| 7.1 Operational Summary.....                                      | 10 |

| 7.2 Start-Up/Shut-Down Sequences .....                            | 11 |

| 7.3 Function Descriptions .....                                   | 11 |

| 8. Typical Application Circuits .....                             | 14 |

| 9. Application Notes.....                                         | 16 |

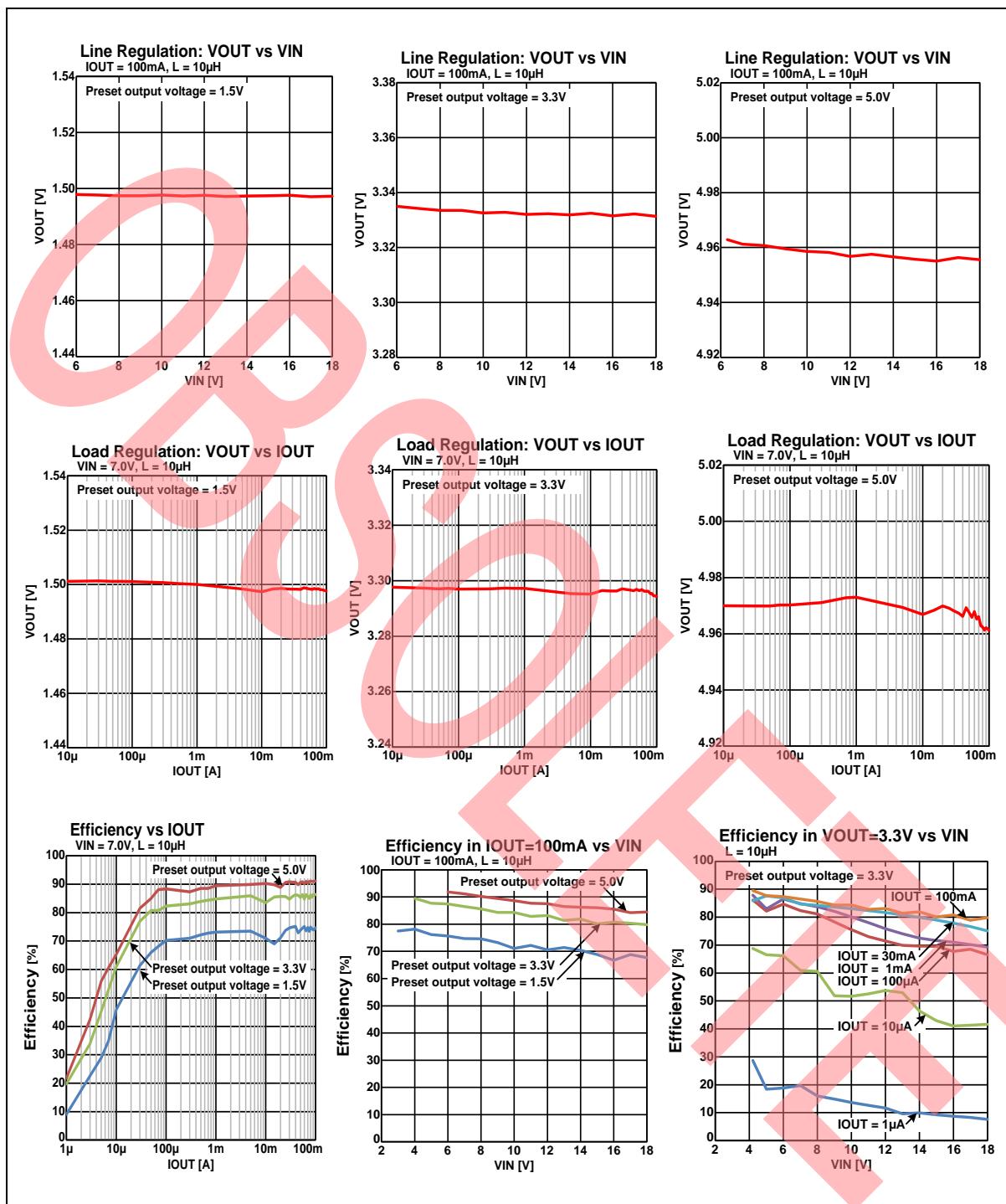

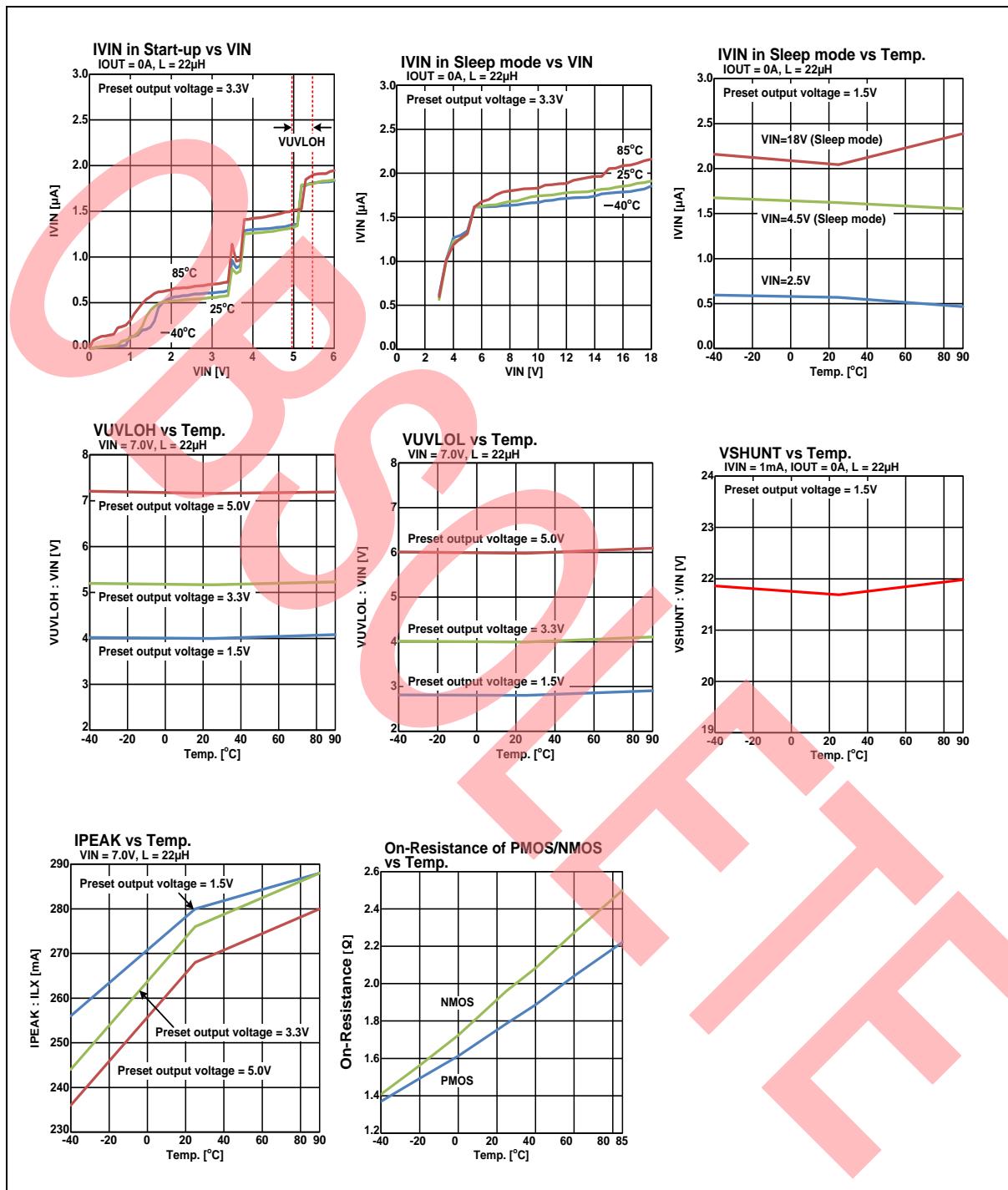

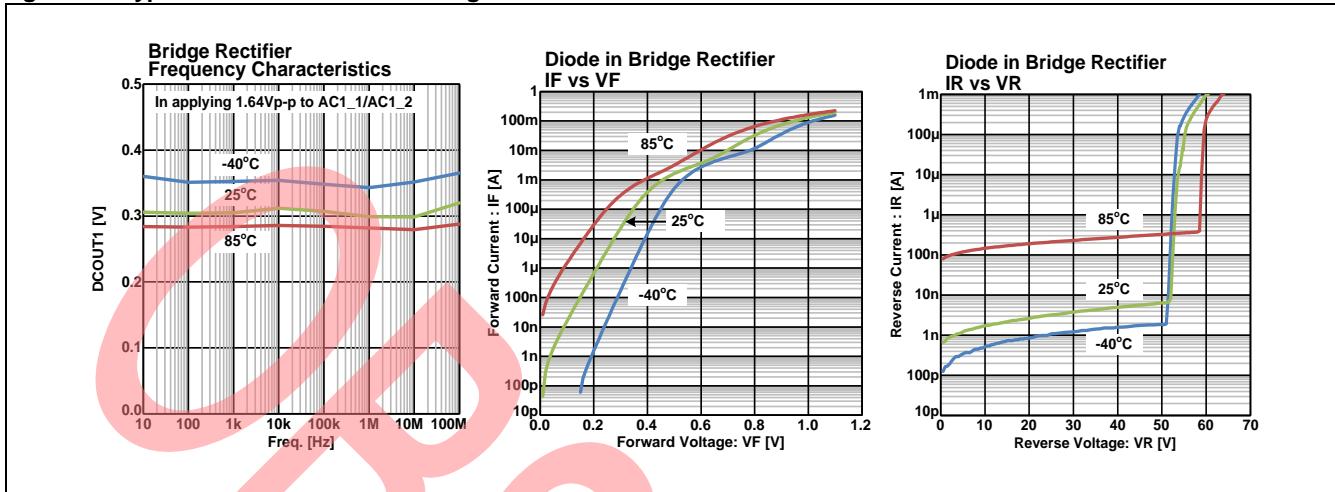

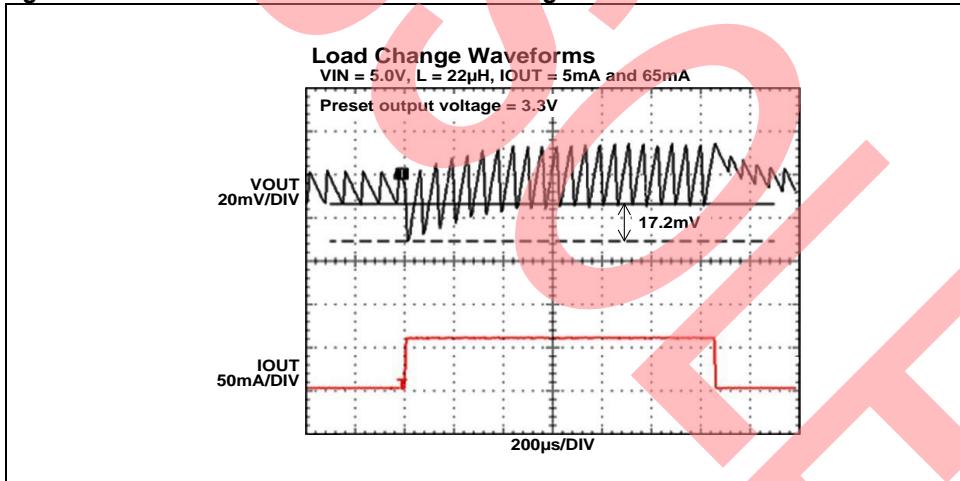

| 10. Typical Characteristics .....                                 | 20 |

| 11. Layout for Printed Circuit Board.....                         | 26 |

| 12. Usage Precaution .....                                        | 27 |

| 13. RoHS Compliance Information .....                             | 27 |

| 14. Ordering Information .....                                    | 27 |

| 15. Package Dimensions .....                                      | 28 |

| 16. Major Changes .....                                           | 29 |

| <b>Document History</b> .....                                     | 31 |

| <b>Sales, Solutions, and Legal Information</b> .....              | 32 |

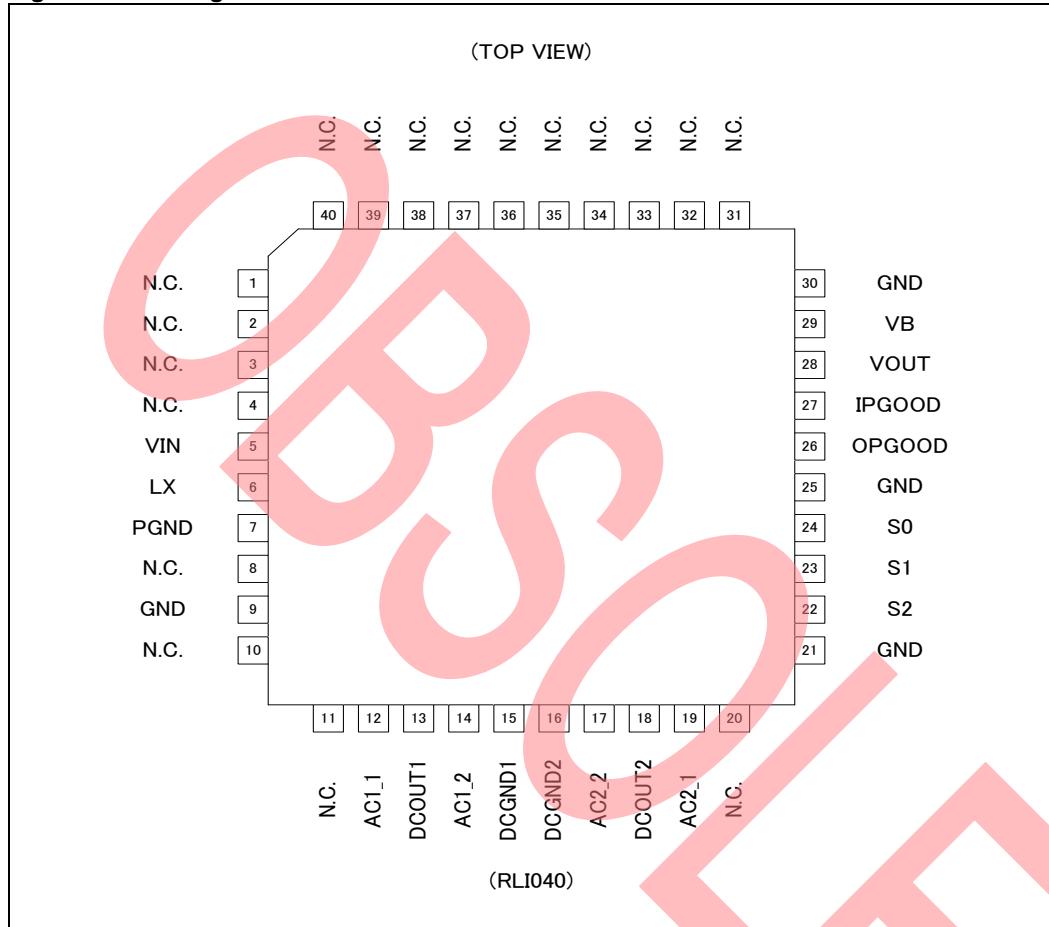

## 1. Pin Assignments

Figure 1. Pin Assignments

## 2. Pin Descriptions

**Table 1. Pin Descriptions.**

| Pin No.  | Pin Name | I/O | Description                                |

|----------|----------|-----|--------------------------------------------|

| 1 to 4   | N.C.     | -   | Non connection pins (Leavethese pins open) |

| 5        | VIN      | -   | DC power supply input pin                  |

| 6        | LX       | O   | DC/DC output pin                           |

| 7        | PGND     | -   | PGND pin                                   |

| 8        | N.C.     | -   | Non connection pin (Leavethis pin open)    |

| 9        | GND      | -   | GND pin                                    |

| 10,11    | N.C.     | -   | Non connection pins (Leavethese pins open) |

| 12       | AC1_1    | I   | Bridge Rectifier1 AC input pin 1           |

| 13       | DCOUT1   | O   | Bridge Rectifier1 DC output pin            |

| 14       | AC1_2    | I   | Bridge Rectifier1 AC input pin 2           |

| 15       | DCGND1   | -   | GND pin                                    |

| 16       | DCGND2   | -   | GND pin                                    |

| 17       | AC2_2    | I   | Bridge Rectifier2 AC input pin 2           |

| 18       | DCOUT2   | O   | Bridge Rectifier2 DC output pin            |

| 19       | AC2_1    | I   | Bridge Rectifier2 AC input pin 1           |

| 20       | N.C.     | -   | Non connection pin (Leavethis pin open)    |

| 21       | GND      | -   | GND pin                                    |

| 22       | S2       | I   | Output voltage select pin 2                |

| 23       | S1       | I   | Output voltage select pin 1                |

| 24       | S0       | I   | Output voltage select pin 0                |

| 25       | GND      | -   | GND pin                                    |

| 26       | OPGOOD   | O   | Output power-good output pin               |

| 27       | IPGOOD   | O   | Input power-good output pin                |

| 28       | VOUT     | I   | Output voltage feedback pin                |

| 29       | VB       | O   | Internal circuit power supply pin          |

| 30       | GND      | -   | GND pin                                    |

| 31 to 40 | N.C.     | -   | Non connection pins (Leavethese pins open) |

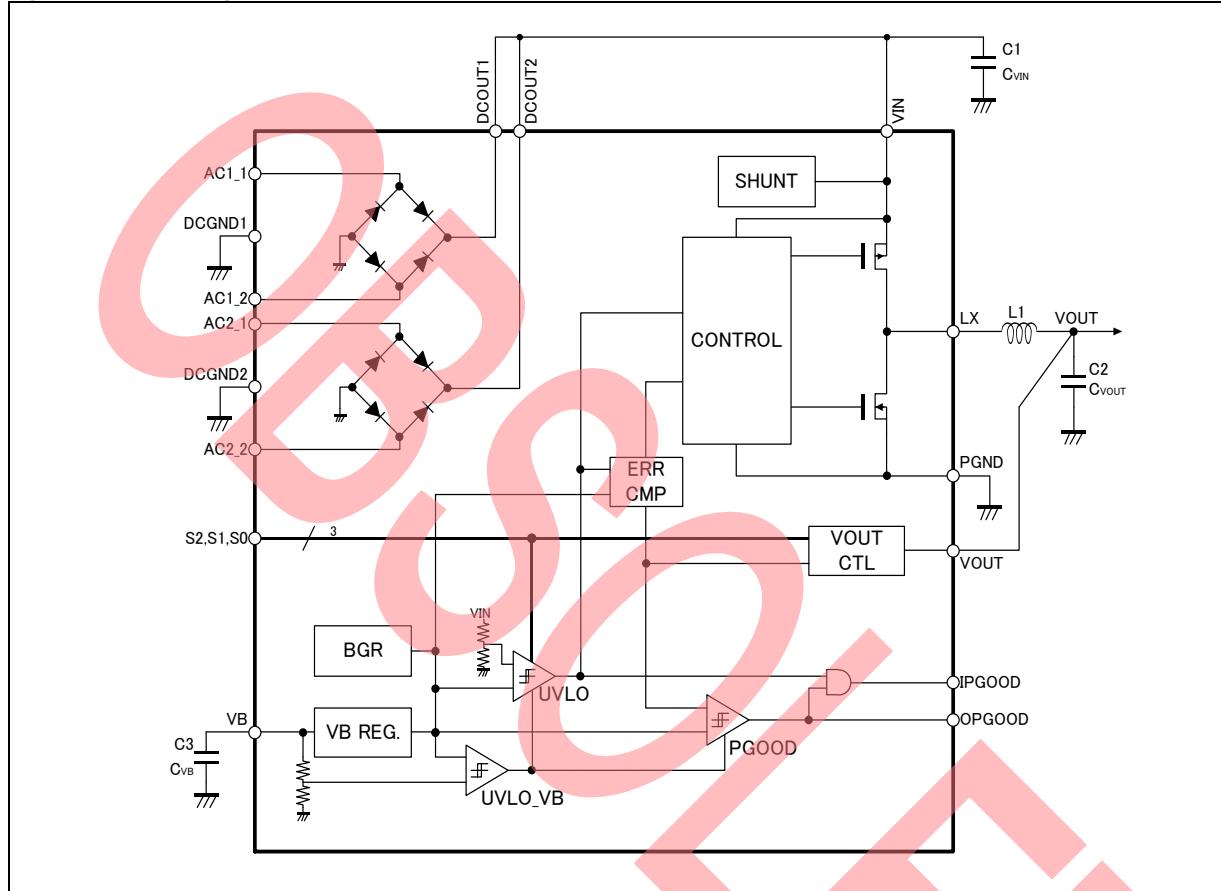

### 3. Block Diagram

Figure 2. Block Diagram

## 4. Absolute Maximum Ratings

**Table 2. Absolute Maximum Ratings**

| Parameter               | Symbol     | Condition                                  | Rating |                          | Unit |

|-------------------------|------------|--------------------------------------------|--------|--------------------------|------|

|                         |            |                                            | Min    | Max                      |      |

| VIN pin input voltage   | VVINMAX    | VIN pin                                    | -0.3   | +24                      | V    |

| VIN pin input slew rate | SRMAX      | VIN pin (VIN $\geq$ 7V)                    | -      | 0.25                     | V/ms |

| VIN pin input current   | IINMAX     | VIN pin                                    | -      | 100                      | mA   |

| AC pin input voltage    | VACMAX     | AC1_1 pin, AC1_2 pin, AC2_1 pin, AC2_2 pin | -0.3   | +24                      | V    |

| AC pin input current    | IPVMAX     | AC1_1 pin, AC1_2 pin, AC2_1 pin, AC2_2 pin | -      | 50                       | mA   |

| LX pin input voltage    | VLXMAX     | LX pin                                     | -0.3   | +24                      | V    |

| Input voltage           | VVINPUTMAX | S0 pin, S1 pin, S2 pin                     | -0.3   | VVB + 0.3 ( $\leq$ +7.0) | V    |

|                         |            | VOUT pin                                   | -0.3   | +7.0                     | V    |

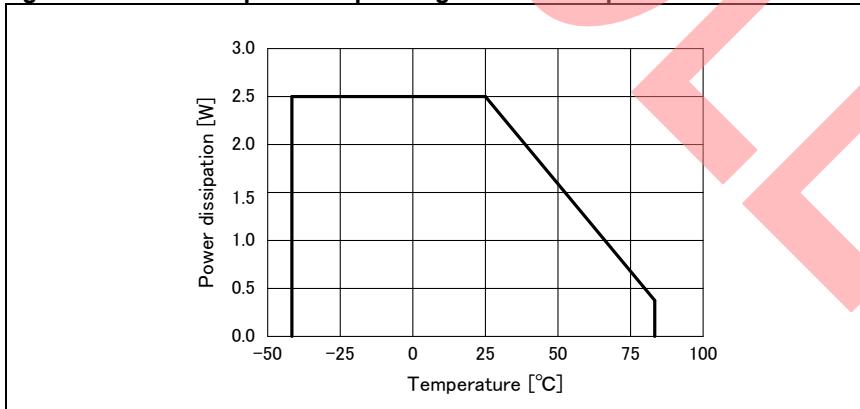

| Power dissipation       | PD         | Ta $\leq$ +25°C                            | -      | 2500                     | mW   |

| Storage temperature     | TSTG       | -                                          | -55    | +125                     | °C   |

| ESD voltage 1           | VESDH      | Human Body Model (100pF, 5k $\Omega$ )     | -900   | +2000                    | V    |

| ESD voltage 2           | VESDM      | Machine Model (200pF, 0 $\Omega$ )         | -150   | +150                     | V    |

| ESD voltage3            | VCDM       | Charged Device Model                       | -1000  | +1000                    | V    |

**Figure 3. Power Dissipation - Operating Ambient Temperature**

**WARNING:**

- Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

## 5. Recommended Operating Conditions

**Table 3. Recommended operating conditions**

| Parameter                     | Symbol | Condition                                     | Value |     |     | Unit |

|-------------------------------|--------|-----------------------------------------------|-------|-----|-----|------|

|                               |        |                                               | Min   | Typ | Max |      |

| VIN pin input voltage         | VVIN   | VIN pin                                       | 2.6   | -   | 23  | V    |

| AC pin input voltage          | VPV    | AC1_1 pin, AC1_2 pin,<br>AC2_1 pin, AC2_2 pin | -     | -   | 23  | V    |

| Input voltage                 | VSI    | S0 pin, S1 pin, S2 pin                        | 0     | -   | VVB | V    |

|                               | VFB    | VOUT pin                                      | 0     | -   | 5.5 | V    |

| Operating ambient temperature | Ta     | -                                             | -40   | -   | +85 | °C   |

**WARNING:**

- The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- Any use of semiconductor devices will be under their recommended operating condition.

- Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

## 6. Electrical Characteristics

### 6.1 DC Characteristics

**Table 4. DC Characteristics**

$(Ta = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, VVIN = 7.0\text{V}, L1 = 22\mu\text{H}, C2 = 47\mu\text{F})$

| Parameter                                                | Symbol  | Condition                                                   | Value |                    |       | Unit |

|----------------------------------------------------------|---------|-------------------------------------------------------------|-------|--------------------|-------|------|

|                                                          |         |                                                             | Min   | Typ                | Max   |      |

| Quiescent current                                        | IVIN    | VVIN = 2.5V (UVLO), Ta = +25°C                              | -     | 550                | 775   | nA   |

|                                                          |         | VVIN = 4.5V (sleep mode), Ta = +25°C                        | -     | 1.5                | 2.25  | µA   |

|                                                          |         | VVIN = 18V (sleep mode), Ta = +25°C                         | -     | 1.9                | 2.85  | µA   |

| Preset output voltage                                    | VVOUT   | S2 = L, S1 = L, S0 = L, IOUT = 1mA                          | 1.457 | 1.5                | 1.544 | V    |

|                                                          |         | S2 = L, S1 = L, S0 = H, IOUT = 1mA                          | 1.748 | 1.8                | 1.852 | V    |

|                                                          |         | S2 = L, S1 = H, S0 = L, IOUT = 1mA                          | 2.428 | 2.5                | 2.573 | V    |

|                                                          |         | S2 = L, S1 = H, S0 = H, IOUT = 1mA                          | 3.214 | 3.3                | 3.386 | V    |

|                                                          |         | S2 = H, S1 = L, S0 = L, IOUT = 1mA                          | 3.506 | 3.6                | 3.694 | V    |

|                                                          |         | S2 = H, S1 = L, S0 = H, IOUT = 1mA                          | 3.993 | 4.1                | 4.207 | V    |

|                                                          |         | S2 = H, S1 = H, S0 = L, IOUT = 1mA                          | 4.383 | 4.5                | 4.617 | V    |

|                                                          |         | S2 = H, S1 = H, S0 = H, IOUT = 1mA                          | 4.870 | 5.0                | 5.130 | V    |

| Peak switching current                                   | IPEAK   | -                                                           | 200   | 250                | 400   | mA   |

| Maximum Output current                                   | IOUTMAX | Ta = +25°C                                                  | 100*  | -                  | -     | mA   |

| UVLO release voltage (Input power-good detectionvoltage) | VUVLOH  | S2 = L, S1 = L, S0 = L                                      | 3.8   | 4.0                | 4.2   | V    |

|                                                          |         | S2 = L, S1 = L, S0 = H                                      |       |                    |       |      |

|                                                          |         | S2 = L, S1 = H, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = L, S1 = H, S0 = H                                      | 4.94  | 5.2                | 5.46  | V    |

|                                                          |         | S2 = H, S1 = L, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = H, S1 = L, S0 = H                                      | 6.84  | 7.2                | 7.56  | V    |

|                                                          |         | S2 = H, S1 = H, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = H, S1 = H, S0 = H                                      |       |                    |       |      |

| UVLO detection voltage (Input power-good resetvoltage)   | VUVLOL  | S2 = L, S1 = L, S0 = L                                      | 2.6   | 2.8                | 3.0   | V    |

|                                                          |         | S2 = L, S1 = L, S0 = H                                      |       |                    |       |      |

|                                                          |         | S2 = L, S1 = H, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = L, S1 = H, S0 = H                                      | 3.8   | 4.0                | 4.2   | V    |

|                                                          |         | S2 = H, S1 = L, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = H, S1 = L, S0 = H                                      | 5.7   | 6.0                | 6.3   | V    |

|                                                          |         | S2 = H, S1 = H, S0 = L                                      |       |                    |       |      |

|                                                          |         | S2 = H, S1 = H, S0 = H                                      |       |                    |       |      |

| VIN pin shunt voltage                                    | VSHUNT  | IVIN = 1mA                                                  | 19    | 21                 | 23    | V    |

| VIN pin shunt current                                    | ISHUNT  | -                                                           | 100   | -                  | -     | mA   |

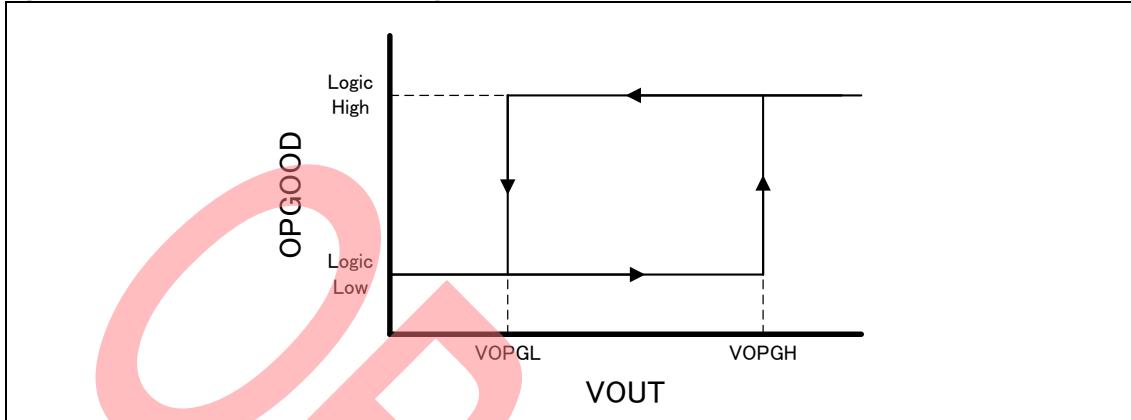

| Output power-good detectionvoltage (Rising)              | VOPGH   | To preset voltage ratio<br>VVOUT $\geq$ 3.3V <sup>[2]</sup> | 90    | 94                 | 98    | %    |

| Output power-good resetvoltage (Falling)                 | VOPGL   | To preset voltage ratio                                     | 65.5  | 70                 | 74.5  | %    |

| Power supply output voltage for internal circuit         | VVB     | VVIN = 6V to 20V                                            | -     | 5.0 <sup>[1]</sup> | -     | V    |

[1]: This parameter is not be specified. This should be used as a reference to support designing the circuits.

[2]: Please contact the department in charge if use this output power-good function under the conditions of VVOUT $\leq$ 2.5V.

## 6.2 Characteristics of Built-in Bridge Rectification Circuit

**Table 5. Characteristics of Built-in Bridge Rectification Circuit**

(Ta = +25 °C)

| Parameter                 | Symbol | Condition | Value  |     |     | Unit |

|---------------------------|--------|-----------|--------|-----|-----|------|

|                           |        |           | Min    | Typ | Max |      |

| Forward bias voltage      | VF     | IF = 10µA | 150    | 280 | 450 | mV   |

| Forward direction current | IF     | -         | -      | -   | 50  | mA   |

| Reverse bias leak current | IR     | VR = 18V  | -      | -   | 20  | nA   |

| Break down voltage        | VBREAK | IR = 1µA  | VSHUNT | 25  | -   | V    |

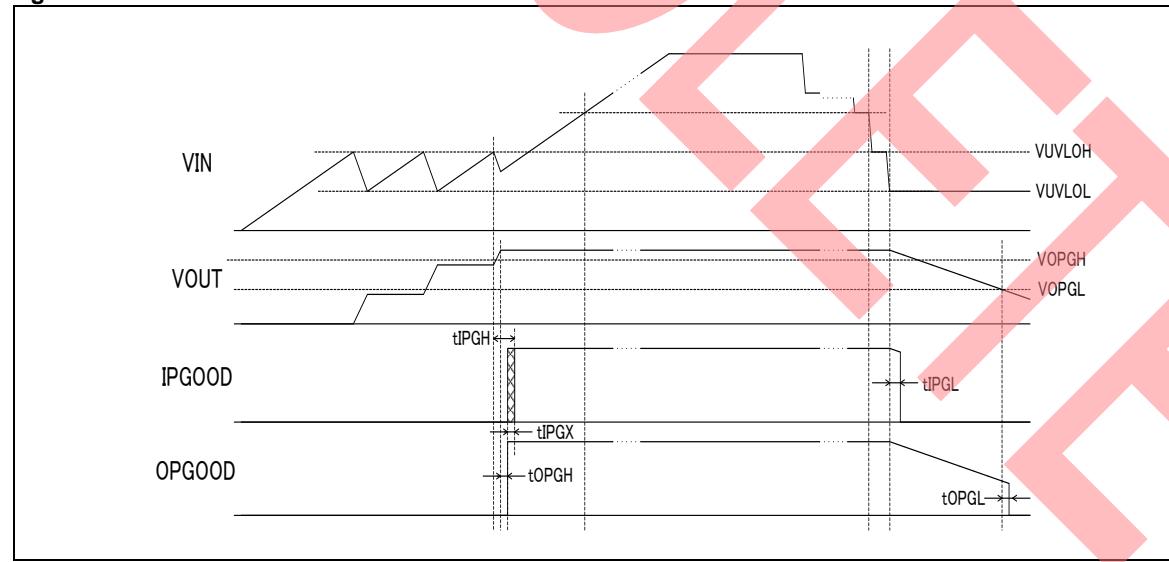

## 6.3 AC Characteristics (Input/Output Power-Good)

**Table 6. AC Characteristics**

(Ta = +25 °C, VOUT = 3.3 V)

| Parameter                                       | Symbol | Condition                         | Value |     |     | Unit |

|-------------------------------------------------|--------|-----------------------------------|-------|-----|-----|------|

|                                                 |        |                                   | Min   | Typ | Max |      |

| Input power-good detection delay time (Rising)  | tIPGH  | SRVIN = 0.1V/ms                   | -     | 1   | -   | ms   |

| Input power-good reset delay time (Falling)     | tIPGL  | SRVIN = 0.1V/ms                   | -     | 1   | -   | ms   |

| Input power-good undefined time                 | tIPGX  | OPGOOD rising                     | -     | 1   | 3   | ms   |

| Output power-good detection delay time (Rising) | tOPGH  | IOUT = 0mA, L1 = 22µH, C2 = 47µF, | -     | 1   | -   | ms   |

| Output power-good reset delay time (Falling)    | tOPGL  | IOUT = 1mA, C2 = 47µF             | -     | 1   | -   | ms   |

**Figure 4. AC Characteristics**

## 7. Function

### 7.1 Operational Summary

#### Bridge Rectifier

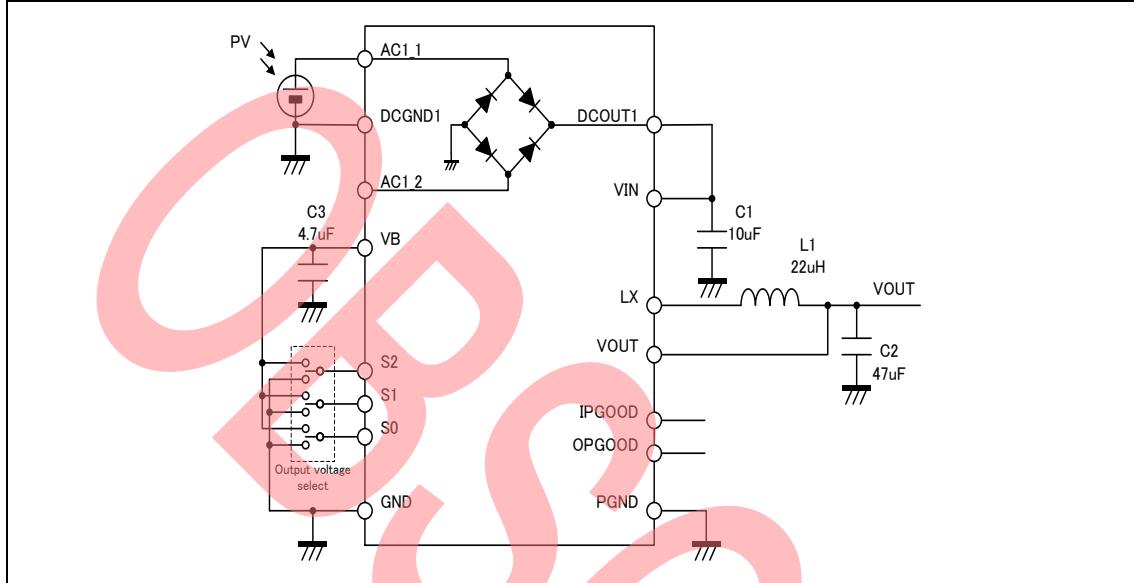

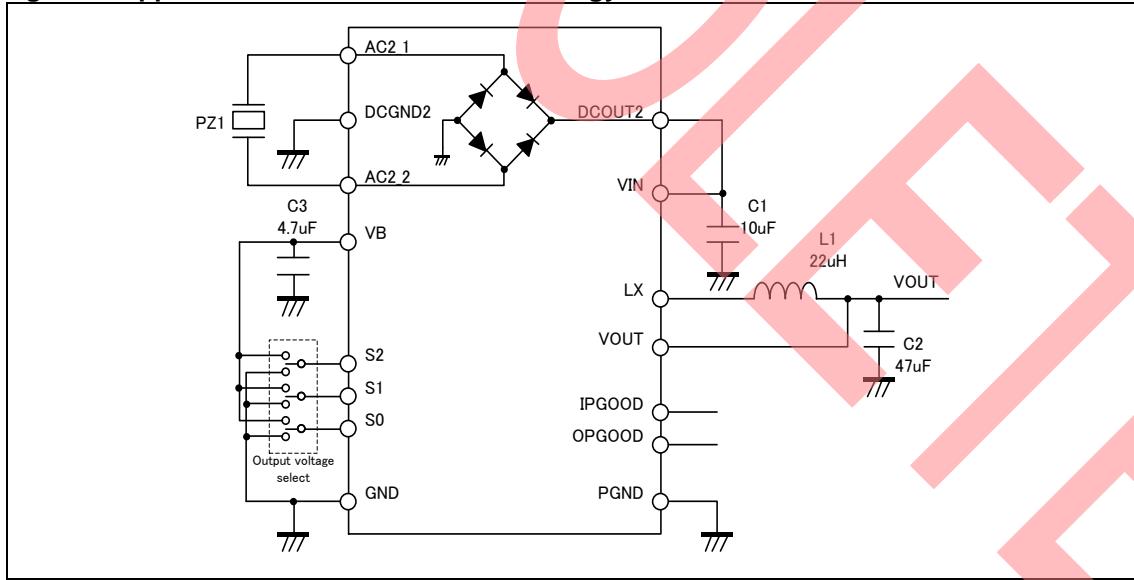

The A/C voltage which is input to the AC1\_1 and AC1\_2 pins or the AC2\_1 and AC2\_2 pins is all-wave rectified at the bridge rectifier of the low-dissipation diode. The bridge rectifier output is output from the DCOUT1 pin and the DCOUT2 pin. By connecting those outputs to the VIN pin, the electric charge is accumulated to the capacitor and it is used as the energy condenser of the buck converter.

#### Power Supply for Internal Circuit

When the VIN pin voltage is 3.5V or lower, the power supply is supplied from the VIN pin to the internal circuit directly. If the VIN pin is over 3.5V, the internal regulator is activated and the power supply is supplied from the internal regulator to the internal circuit. Therefore, the stable output voltage is maintained in the wide input voltage range 2.6 V to 23V.

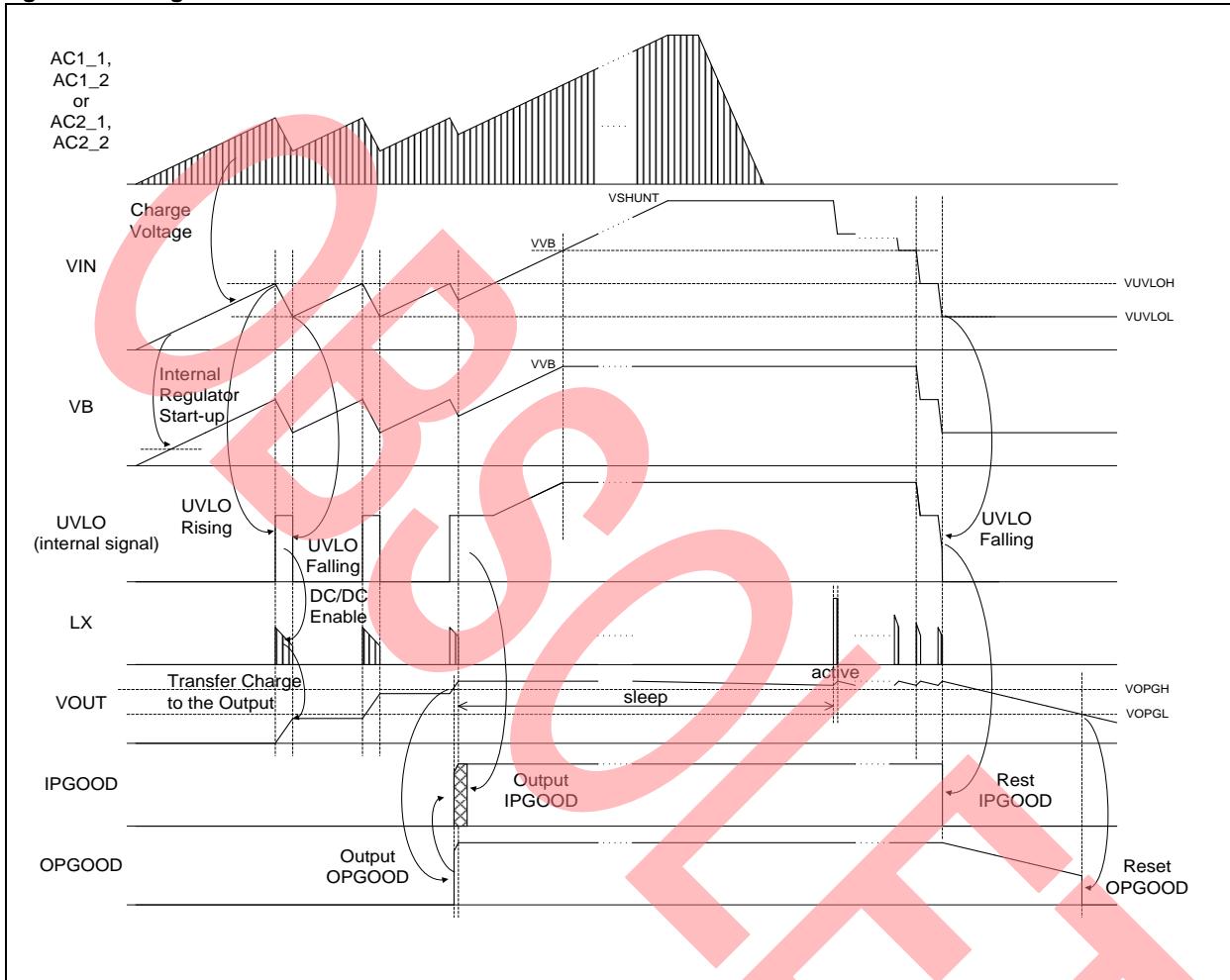

#### DC/DC Start-Up/Shut-Down

When the VIN pin voltage is over the release voltage VUVLOH for the under voltage lockout protection circuit (UVLO), the converter circuit is enabled and the electric charge is supplied from the input capacitor to the output capacitor. When the VIN pin voltage is below the UVLO detection voltage VUVLOL, the converter is disabled. The 1.2V hysteresis between the release voltage and the detection voltage for UVLO prevents the converter from noise or frequent ON/OFF which is caused by the VIN pin voltage-drop during start-up.

#### Sleep/Auto Active Control

When the feedback voltage VFB for the converter reaches the determinate voltage, the sleep state to stop the switching operation starts and that can reduce the consumption power from the internal circuit. When the VOUT voltage is below the threshold value, the VOUT voltage is maintained to the rated value by making the converter active again.

## 7.2 Start-Up/Shut-Down Sequences

Figure 5. Timing Chart

## 7.3 Function Descriptions

### Output Voltage Setting and Under Voltage Lockout Protection (UVLO) Function

It is possible to select the output voltage from eight kinds of presets using the S2, S1 and S0 pins.

Also, the under voltage lockout protection circuit is provided to prevent IC's malfunction by the transient state or the instant drop during the VIN pin voltage activation, system destroy and deterioration, and it is set as follows according to the preset voltage. When the VIN pin exceeds the release voltage for the UVLO circuit, the system is recovered.

**Table 7. Output Voltage Setting and Under Voltage Lockout Protection (UVLO) Function**

| S2 | S1 | S0 | VOUT[V] | Under Voltage Lockout Protection (UVLO) -Typ- |                                        |

|----|----|----|---------|-----------------------------------------------|----------------------------------------|

|    |    |    |         | Detection Voltage<br>(Falling) VUVLOL [V]     | Release Voltage<br>(Rising) VUVLOH [V] |

| L  | L  | L  | 1.5     |                                               |                                        |

| L  | L  | H  | 1.8     | 2.8                                           | 4.0                                    |

| L  | H  | L  | 2.5     |                                               |                                        |

| L  | H  | H  | 3.3     |                                               |                                        |

| H  | L  | L  | 3.6     | 4.0                                           | 5.2                                    |

| H  | L  | H  | 4.1     |                                               |                                        |

| H  | H  | L  | 4.5     | 6.0                                           | 7.2                                    |

| H  | H  | H  | 5.0     |                                               |                                        |

**Input/Output Power-good Signal Output**

When the VIN pin input voltage is equal to the release voltage VUVLOH for UVLO or more, the output for the IPGOOD pin is set to the "H" level as the input power-good. When the VIN pin input voltage is equal to the detection voltage VUVLOL for UVLO or less, the output for the IPGOOD pin is reset to the "L" level. The IPGOOD output is enabled only when the following output power-good signal output OPGOOD is "H" level.

The output power-good signal OPGOOD is set to the "H" level when the feedback voltage VFB for the VOUT pin is equal to the detection voltage VOPGH or more. When the feedback voltage VFB is equal to the reset voltage VOPGL or less, the output for the OPGOOD pin is reset to the "L" level.

**Table 8. Input Power-Good Signal Output (IPGOOD)**

| OPGOOD | UVLO       | IPGOOD |

|--------|------------|--------|

| L      | Don't care | L      |

| H      | L          | L      |

| H      | H          | H      |

**Table 9. Output Power-Good Signal Output (OPGOOD)**

| VFB                                                  | OPGOOD |

|------------------------------------------------------|--------|

| $\leq$ VOPGL                                         | L      |

| $\geq$ VOPGH<br>( $VVOUT \geq 3.3V$ ) <sup>[1]</sup> | H      |

[1]:Please contact the department in charge if use this output power-good function under the conditions of  $VVOUT \leq 2.5V$ .

**Figure 6. Input/Output Power-Good Signal Output**

### **Input Over Voltage Protection**

If the voltage exceeding  $V_{SHUNT}$  (Typ : 21V) is input to the VIN pin, the input level is clamped enabling the over voltage protection circuit. The flowing current is  $I_{SHUNT}$  (Min 100mA) during clamp.

### **Over Current Protection**

If the output current for the LX pin reaches the over current detection level  $I_{PEAK}$ , the circuit is protected by controlling the peak value for the inductor current setting the main side FET to the OFF state.

## 8. Typical Application Circuits

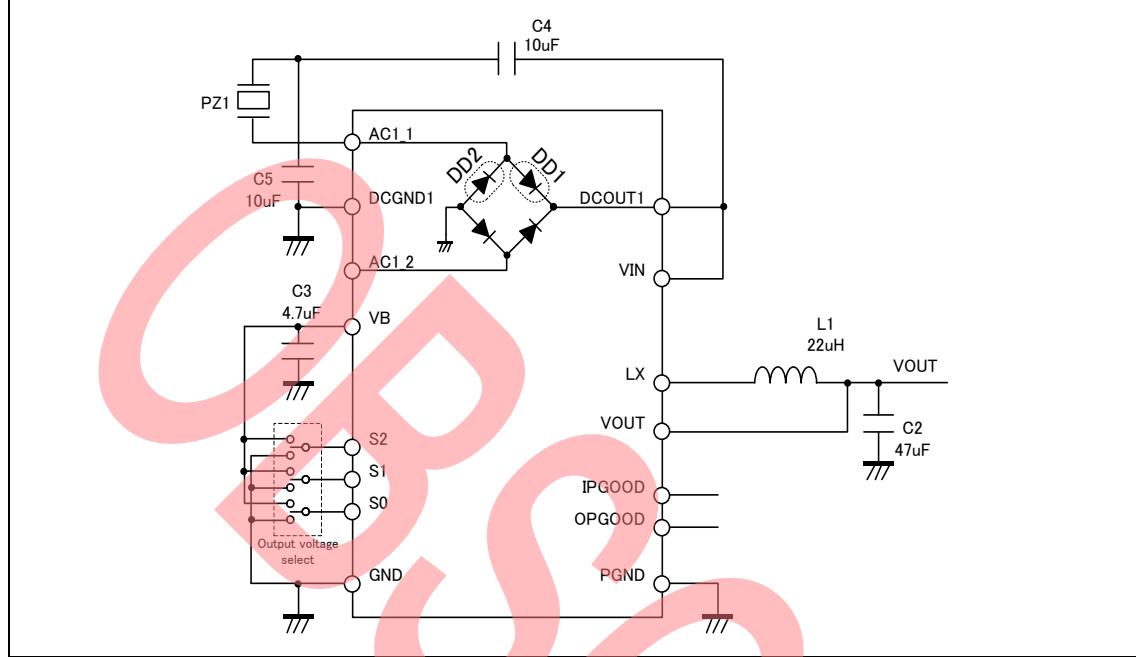

Figure 7. Application Circuit For Photovoltaic Energy Harvester

Figure 8. Application Circuit for Vibration Energy Harvester

**Figure 9. Voltage Doubler Rectification Circuit for Vibration Harvester**

**Operation of the Double Voltage Rectifier Circuit Rectifying an AC Input Voltage**

When the AC1\_1 input voltage is positive, the capacitor C4 charges up through the diode DD1, and when the AC1\_1 input voltage is negative, the capacitor C5 charges up through the diode DD2. Each capacitor takes on a charge of the positive peak of the AC input. The output voltage at the VIN pin is the series total of C4+C5.

**Table 10. Parts list**

| Part Number | Value                     | Description |

|-------------|---------------------------|-------------|

| C1          | 10 $\mu$ F <sup>[1]</sup> | Capacitor   |

| C2          | 47 $\mu$ F <sup>[1]</sup> | Capacitor   |

| C3          | 4.7 $\mu$ F               | Capacitor   |

| C4          | 10 $\mu$ F <sup>[1]</sup> | Capacitor   |

| C5          | 10 $\mu$ F <sup>[1]</sup> | Capacitor   |

| L1          | 10 $\mu$ H to 22 $\mu$ H  | Inductor    |

[1]: Adjust the values according to the source supply ability and the load power.

## 9. Application Notes

### Inductor

The MB39C811 is optimized to work with an inductor in the range of 10 $\mu$ H to 22 $\mu$ H. Also, since the peak switching current is up to 400mA, select an inductor with a DC current rating greater than 400mA.

**Table 11. Manufactures of Recommended Inductors**

| Part Number      | Value      | Manufacture     |

|------------------|------------|-----------------|

| LPS5030-223ML    | 22 $\mu$ H | Coilcraft, Inc. |

| VLF403215MT-220M | 22 $\mu$ H | TDK Corporation |

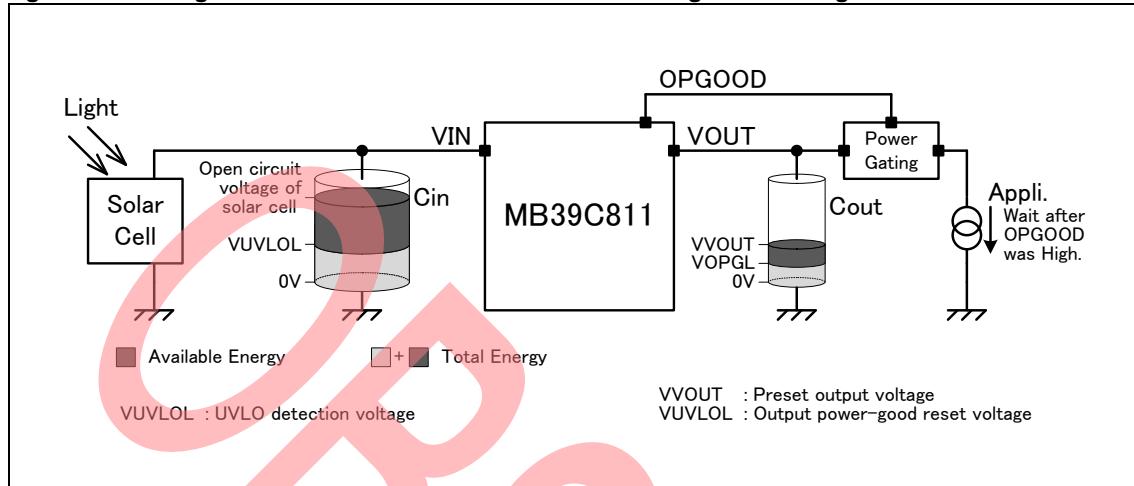

### Harvester (Photovoltaic Power Generator)

In case of photovoltaic energy harvesting, such as solar or light energy harvesting, use a solar cell with high open-circuit voltage which must be higher than the UVLO release voltage. Electric power obtained from light or solar is increased in proportion to the ambient illuminance.

There are silicone-based solar cells and organic-based solar cells about photovoltaic power generators. Silicone-based solar cells are single crystal silicon solar cell, polycrystalline silicon solar cell, and amorphous silicon solar cell. Organic-based solar cells are dye-sensitized solar cell (DSC), and organic thin film solar cell. Crystal silicon and polycrystalline silicon solar cells have high energy conversion efficiency. Amorphous silicon solar cells are lightweight, flexible, and produced at low cost. Dye-sensitized solar cells are composed by sensitizing dye and electrolytes, and are low-cost solar cell. Organic thin film solar cells are lightweight, flexible, and easily manufactured.

**Table 12. Manufactures of Photovoltaic Harvesters**

| Part Number/Series Name | Type                               | Manufacture           |

|-------------------------|------------------------------------|-----------------------|

| BCS4630B9               | Film amorphous silicon solar cells | TDK Corporation       |

| Amorton                 | Amorphous silicon solar cells      | Panasonic Corporation |

### Harvester (Vibration Power Generator, Piezoelectric Generator)

Vibration power generators produce AC power by vibration. For AC to DC rectification, the MB39C811 integrates two bridge rectifiers. Electric power obtained from a vibration power generator depends on frequency of vibration and usage of the generator. Although, vibration generators produce high voltage, the shunt circuit protects from higher voltage than 21V.

There are electromagnetic induction generators and piezoelectric generators about vibration harvesters. The electromagnetic induction generator consists of coil and magnet. The piezoelectric generators are made from plastics or ceramics. Plastic-based piezoelectric generators made from polyvinylidene fluoride are lightweight, flexible. Ceramic-based piezoelectric generators are made from barium titanate or lead zirconate titanate ceramics.

**Table 13. Manufactures of Vibration Harvesters**

| Part Number      | Type                      | Manufacture              |

|------------------|---------------------------|--------------------------|

| EH12, EH13, EH15 | Electromagnetic induction | Star Micronics Co., Ltd. |

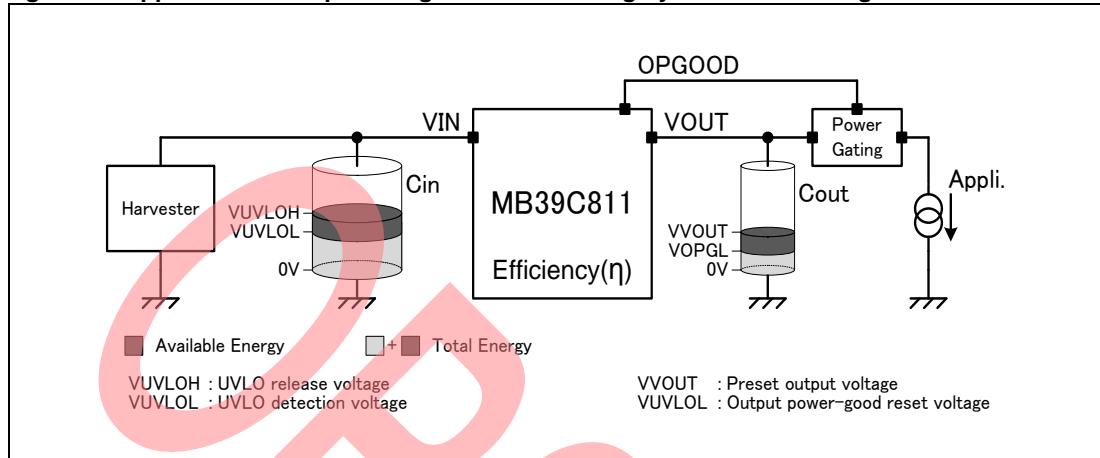

### Sizing of Input and Output Capacitors

Energy from harvester should be stored on the Cin and Cout to operate the application block. If the size of these capacitors were too big, it would take too much time to charge energy into these capacitors, and the system cannot be operated frequently. On the other hand, if these capacitors were too small, enough energy cannot be stored on these capacitors for the application block. The sizing of the Cin and Cout is important.

Common capacitors are layered ceramic capacitor, electrolytic capacitor, electric double layered capacitor, and so on. Electrostatic capacitance of layered ceramic capacitors is relatively small. However, layered ceramic capacitors are small and have high voltage resistance characteristic. Electrolytic capacitors have high electrostatic capacitance from  $\mu\text{F}$  order to  $\text{mF}$  order. The size of capacitor becomes large in proportion to the size of capacitance. Electric double layered capacitors have high electrostatic capacitance around  $0.5\text{F}$  to  $1\text{F}$ , but have low voltage resistance characteristics around  $3\text{V}$  to  $5\text{V}$ . Be very careful with a voltage resistance characteristic. Also, leak current, equivalent series resistance (ESR), and temperature characteristic are criteria for selecting,

**Table 14. Manufactures of Capacitors**

| Part Number/Series Name | Type, Capacitance | Manufacture           |

|-------------------------|-------------------|-----------------------|

| EDLC351420-501-2F-50    | EDLC, 500mF       | TDK Corporation       |

| EDLC082520-500-1F-81    | EDLC, 50mF        |                       |

| EDLC041720-050-2F-52    | EDLC, 5mF         |                       |

| Gold capacitor          | EDLC              | Panasonic Corporation |

First of all, apply the following equation and calculate energy consumption for an application from voltage, current, and time during an operation.

$$E_{\text{Appli.}}[\text{J}] = V_{\text{Appli.}} \times I_{\text{Appli.}} \times t_{\text{Appli.}}$$

The energy stored on a capacitor is calculated by the following equation.

$$E_c[\text{J}] = \frac{1}{2} CV^2$$

Since the energy in a capacitor is proportional to the square of the voltage, it is energetically advantageous for the buck DC/DC converter to make the Cin larger.

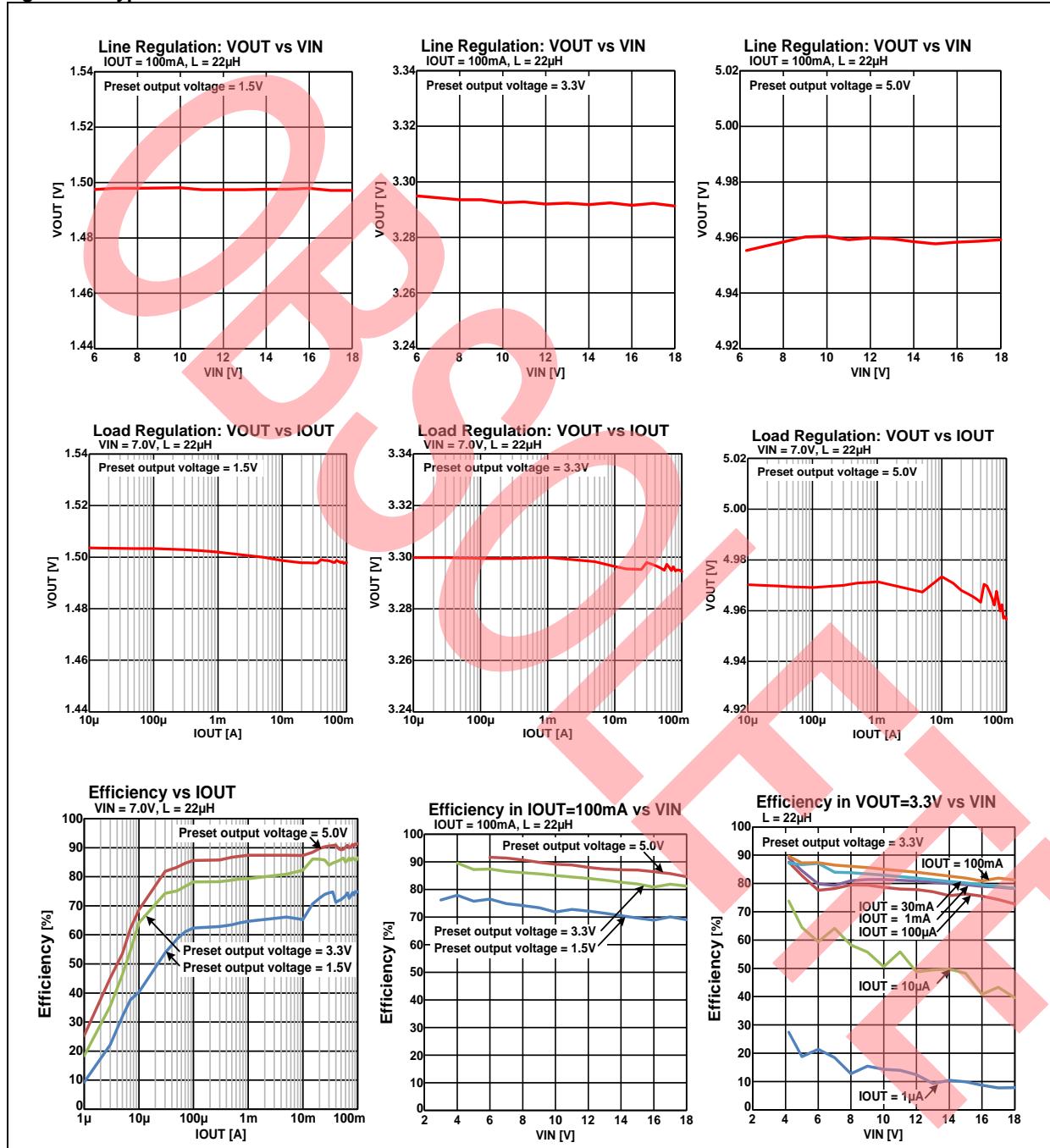

An example of an application using the power gating by the OPGOOD signal is shown in the Figure 10. The Cin and the Cout are sized so as to satisfy the following equation. The  $\eta$ , the efficiency of the MB39C811, is determined from the current of application and the graph shown in Figure 12, Efficiency vs IOUT.

$$E_{\text{Appli.}} \leq dE_{\text{Cin}} \times \eta + dE_{\text{Cout}}$$

$dE_{\text{Cin}}$  and  $dE_{\text{Cout}}$  are the available energies for the application.

$$dE_{\text{Cin}}[\text{J}] = \frac{1}{2} \text{Cin}(\text{VUVLOH}^2 - \text{VUVLOL}^2)$$

$$dE_{\text{Cout}}[\text{J}] = \frac{1}{2} \text{Cout}(\text{VVOUT}^2 - \text{VOPGL}^2)$$

**Figure 10. Application Example Using the Power Gating by the OPGOOD Signal**

Before calculating the initial charging time ( $T_{Initial}[s]$ ), calculate the total energy ( $E_{Cin}$  and  $E_{Cout}$ ) stored on both  $C_{in}$  and  $C_{out}$ .

$$E_{Cout}[J] = \frac{1}{2} C_{in} \times V_{UVLOH}^2$$

$$E_{Cout}[J] = \frac{1}{2} C_{out} \times V_{VOUT}^2$$

A  $P_{Harvester}[W]$  is a power generation capability of a harvester. An initial charging time ( $T_{Initial}[s]$ ) is calculated by the following equation.

$$T_{Initial} = \frac{E_{Cin}}{P_{Harvester}} + \frac{E_{Cout}}{P_{Harvester} \times \eta}$$

A repeat charging time ( $T_{Repeat}[s]$ ) is calculated by the following equation. The  $T_{Repeat}[s]$  become shorter than the  $T_{Initial}[s]$ .

$$T_{Repeat} = \frac{dE_{Cin}}{P_{Harvester}} + \frac{dE_{Cout}}{P_{Harvester} \times \eta}$$

Additionally, waiting for a period of time after the OPGOOD signal goes high can store more energy on the capacitor  $C_{in}$  Figure 11.

$$dE_{Cout}[J] = \frac{1}{2} C_{in} (V_{OpenCircuitVoltage}^2 - V_{UVLOL}^2)$$

**Figure 11. Waiting for a Period of Time After the OPGOOD Signal Goes High**

For more information about the energy calculation, refer to the application note: [Energy Calculation for Energy Harvesting](#).

## 10. Typical Characteristics

Figure 12. Typical Characteristics of DC/DC Converter

**Figure 13. Typical Characteristics of Bridge Rectifier**

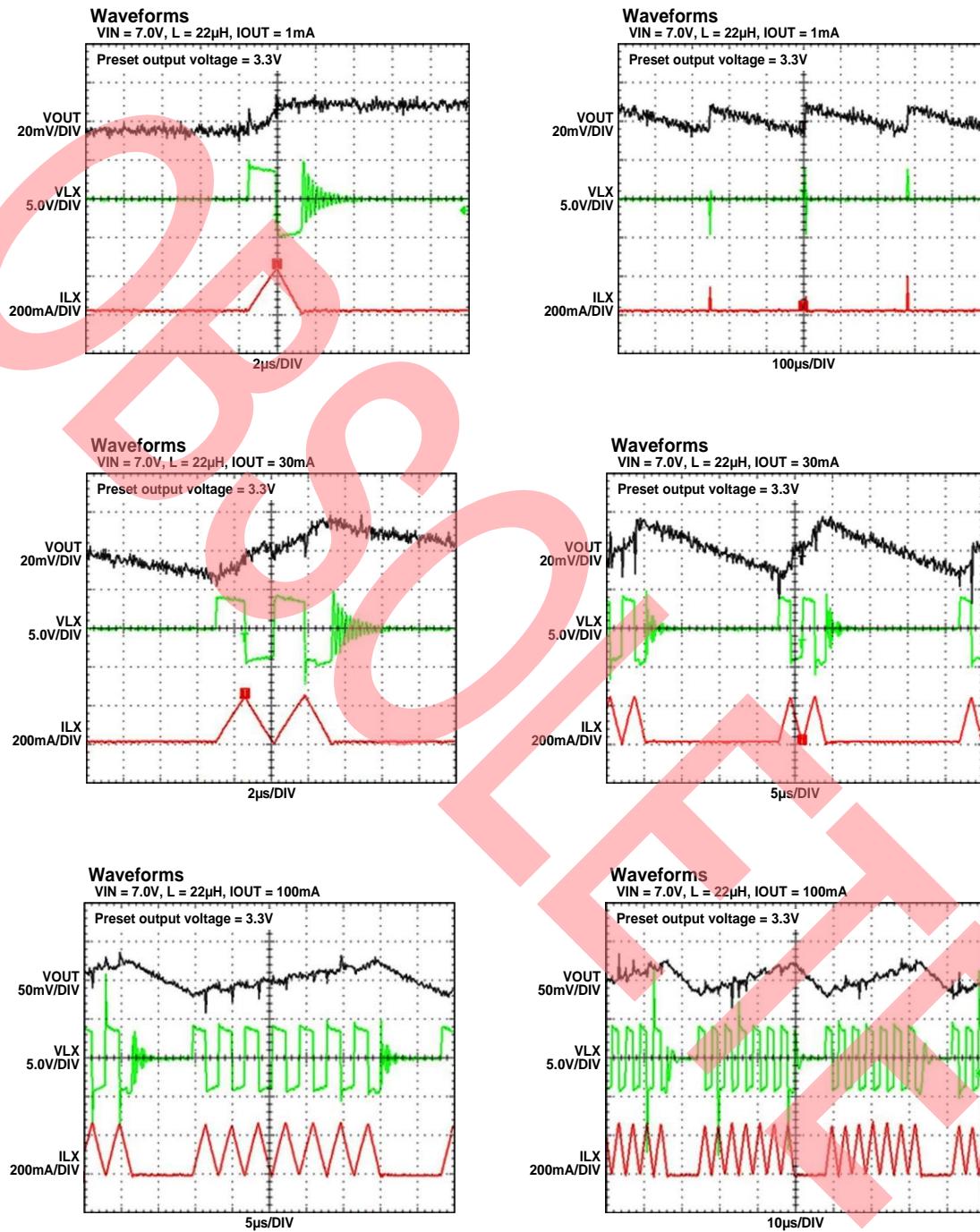

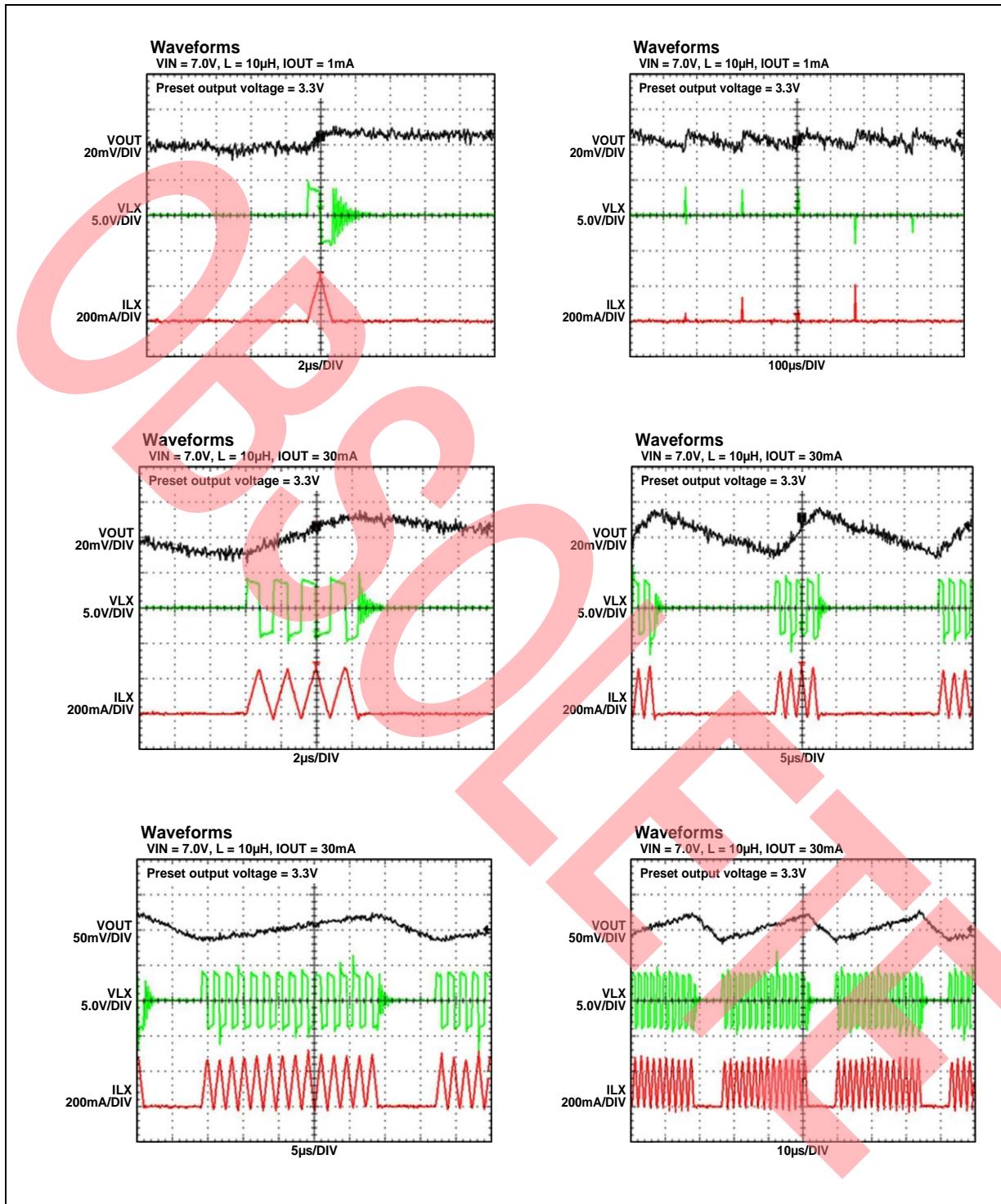

**Figure 14. DC/DC Converter Sudden Load Change**

**Figure 15. Switching Waveforms of DC/DC Converter**

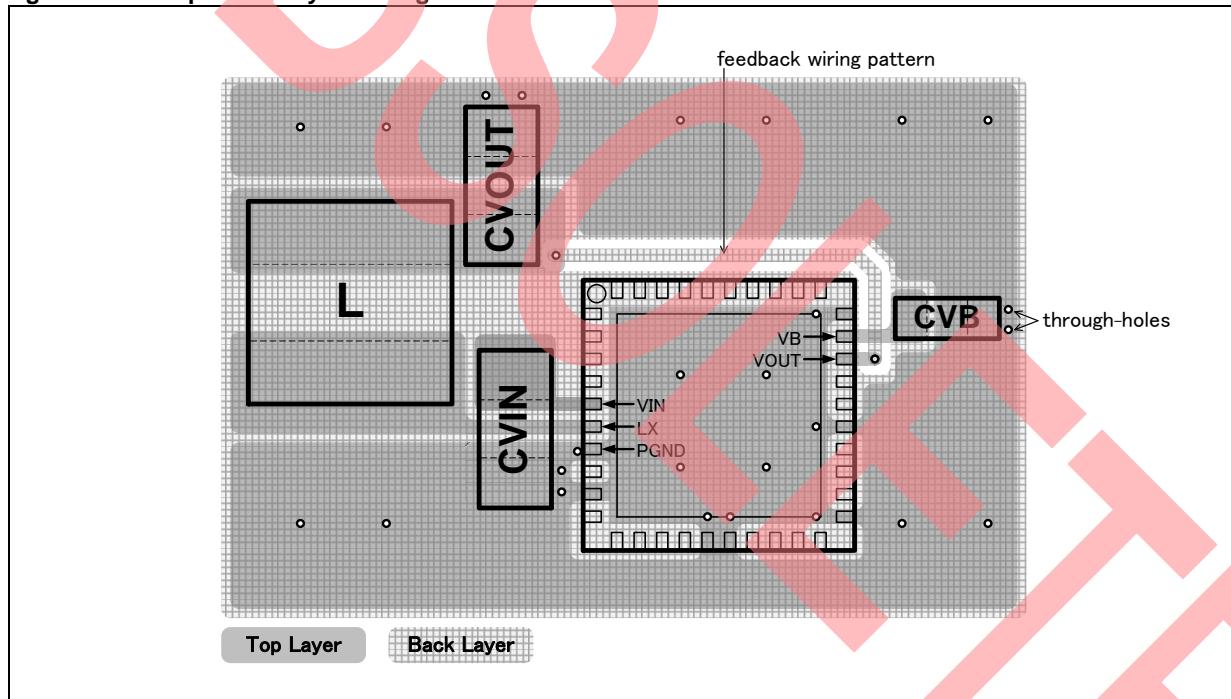

## 11. Layout for Printed Circuit Board

### Note the Points Listed Below in Layout Design

- Place the switching parts<sup>[1]</sup> on top layer, and avoid connecting each other through through-holes.

- Make the through-holes connecting the ground plane close to the GND pins of the switching parts<sup>[1]</sup>

- Be very careful about the current loop consisting of the input capacitor CVIN, the VIN pin of IC, and the PGND pin. Place and connect these parts as close as possible to make the current loop small.

- The output capacitor CVOUT and the inductor L are placed adjacent to each other.

- Place the bypass capacitor CVB close to VB pin, and make the through-holes connecting the ground plane close to the GND pin of the bypass capacitor CVB.

- Draw the feedback wiring pattern from the VOUT pin to the output capacitor pin. The wiring connected to the VOUT pin is very sensitive to noise so that the wiring should keep away from the switching parts<sup>[1]</sup>. Especially, be very careful about the leaked magnetic flux from the inductor L, even the back side of the inductor L.

[1]: Switching parts: IC (MB39C811), Input capacitor (CVIN), Inductor (L), Output capacitor (CVOUT).

Refer to [Figure 2](#).

**Figure 16. Example of a Layout Design**

## 12. Usage Precaution

### Do Not Configure the IC Over the Maximum Ratings

If the IC is used over the maximum ratings, the LSI may be permanently damaged.

It is preferable for the device to be normally operated within the recommended usage conditions. Usage outside of these conditions can have a bad effect on the reliability of the LSI.

### Use the Devices within Recommended Operating Conditions

The recommended operating conditions are the recommended values that guarantee the normal operations of LSI.

The electrical ratings are guaranteed when the device is used within the recommended operating conditions and under the conditions stated for each item.

### Printed Circuit Board Ground Lines should be set up with Consideration for Common Impedance

### Take Appropriate Measures against Static Electricity

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 kΩ to 1MΩ in series between body and ground.

### Do not apply Negative Voltages

The use of negative voltages below -0.3V may cause the parasitic transistor to be activated on LSI lines, which can cause malfunctions.

## 13. RoHS Compliance Information

This product has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

## 14. Ordering Information

**Table 15. Ordering Information**

| Part Number | Package                     |

|-------------|-----------------------------|

| MB39C811QN  | 40-pin plastic QFN (RLI040) |

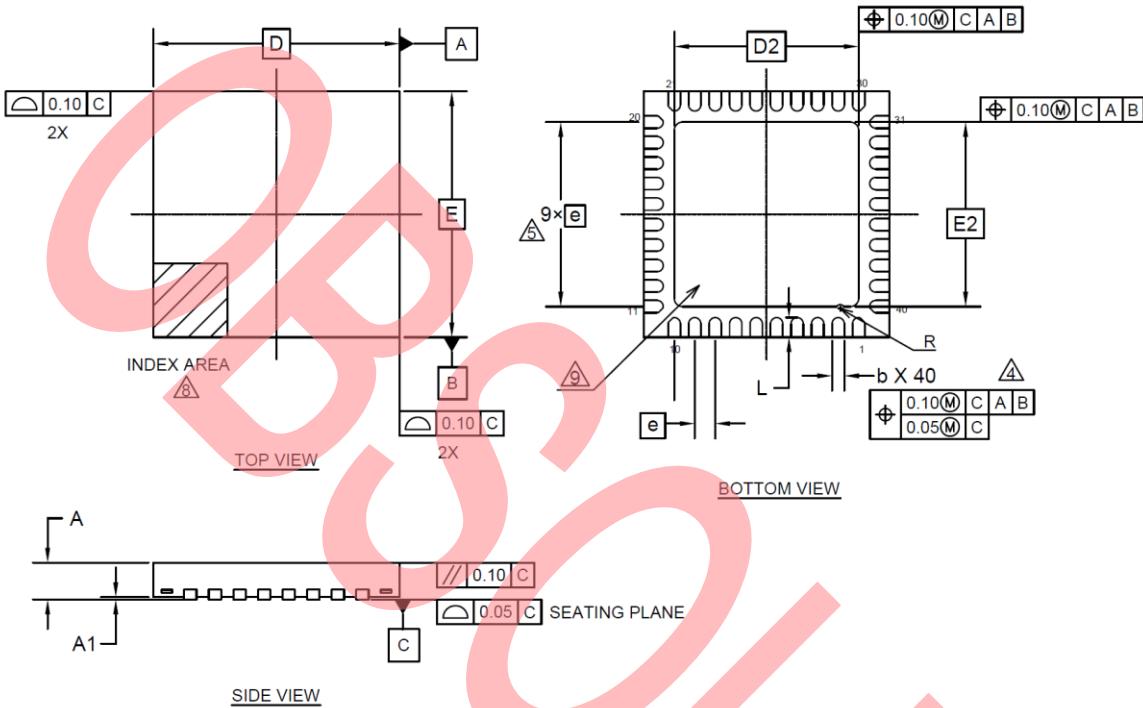

## 15. Package Dimensions

Package Code: RLI040

| SYMBOL | DIMENSIONS |      |          |

|--------|------------|------|----------|

|        | MIN.       | NOM. | MAX.     |

| A      | —          | —    | 0.90     |

| A1     | 0.00       | —    | 0.05     |

| D      |            |      | 6.00 BSC |

| E      |            |      | 6.00 BSC |

| b      | 0.20       | 0.25 | 0.30     |

| D2     | 4.50 BSC   |      |          |

| E2     | 4.50 BSC   |      |          |

| e      | 0.50 BSC   |      |          |

| R      | 0.20       |      |          |

| L      | 0.35       | 0.40 | 0.45     |

| N      | 40         |      |          |

| ND     | 10         |      |          |

| NE     | 10         |      |          |

### NOTES

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING CONFORMS TO ASME Y14.5M-1994.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL TIP. IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION "b" SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

5. ND REFERS TO THE NUMBER OF TERMINALS ON D SIDE OR E SIDE.

6. MAX. PACKAGE WARPAGE IS 0.05mm.

7. MAXIMUM ALLOWABLE BURR IS 0.076mm IN ALL DIRECTIONS.

8. PIN #1 ID ON TOP WILL BE LOCATED WITHIN THE INDICATED ZONE.

9. BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

002-19408 Rev. \*\*

## 16. Major Changes

Spansion Publication Number: MB39C811\_DS405-00013....

| Page                             | Section                                                                                                       | Change Results                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary 0.1 [June 14, 2013]  |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                                | -                                                                                                             | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Revision 1.0 [November 18, 2013] |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6                                | 4. Pin Assignments                                                                                            | Changed Pin8 PGND to N.C.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7                                | 5. Pin Descriptions                                                                                           | Changed Pin8 PGND to N.C.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9                                | 7. Absolute Maximum Rating                                                                                    | Added Max in Power dissipation<br>Added Figure [Power dissipation]<br>Changed VIN pin input slew rate<br>Added VIN pin , Input current<br>Added AC pin input current                                                                                                                                                                                                                                                                                   |

| 10                               | 8. Recommended Operating Conditions                                                                           | Deleted Added VIN pin , Input current<br>Deleted AC pin input current<br>Changed values in "Input voltage range"<br>Deleted Input slew rate<br>Added "IOUT=1mA" in "Preset output voltage" and changed values<br>Changed "over current protection" to "peak switching current" and values<br>Changed "Output current" to "Maximum output current" and values<br>Changed values in "UVLO release voltage"<br>Changed values in "UVLO detection voltage" |

| 11                               | 9.1. DC Characteristics                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18                               | 11. Example                                                                                                   | Added new                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                               | 14. Ordering Information                                                                                      | Added "Table 14-2 EVB Ordering Information"                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23                               | 15. Marking                                                                                                   | Added new                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24                               | 16. Product Label                                                                                             | Added new                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25                               | 17. Recommended Mounting Conditions                                                                           | Added new                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Revision 2.0 [August 29, 2014]   |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11                               | 9. Electrical Characteristics<br>Table 9-1 DC characteristics                                                 | Deleted Input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18                               | 11. Typical Application Circuits<br>Figure 11-3 Voltage doubler rectification circuit for vibration harvester | Added the explanation of the voltage doubler rectification circuit                                                                                                                                                                                                                                                                                                                                                                                     |

| 19 to 21                         | 12. Application Notes                                                                                         | Added the "12. Application Notes"                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22 to 26                         | 13. Typical Characteristics                                                                                   | Updated the "13. Typical Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27                               | 14. Layout for Printed Circuit Board                                                                          | Added the "14. Layout for Printed Circuit Board"                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30 to 32                         | 18. Product Label                                                                                             | Changed the "18. Product Label"                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Revision 3.0                     |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7                                | 5. Pin Descriptions                                                                                           | Added descriptions for all N.C. pins in "Table 5-1 Pin descriptions"<br>"Non connection pin" → "Non connection pin (Leave this pin open)"                                                                                                                                                                                                                                                                                                              |

| 8                                | 6. Block Diagram                                                                                              | Wiring correction in "Figure 6-1 Block diagram"<br>Deleted the wire connections between DCGND1, DCGND2 pins and each bridge rectifier, then added the internal GNDs.                                                                                                                                                                                                                                                                                   |

| 11                               | 9. Electrical Characteristics<br>9.1 DC characteristics                                                       | Added conditions and notes for output power-good detection voltage in "Table 9-1 DC characteristics"<br>"To preset voltage ratio" → "To preset voltage ratio $V_{VOUT} \geq 3.3V$ (*2)"                                                                                                                                                                                                                                                                |

| 15                               | 10. Function<br>10.3 Function descriptions                                                                    | Added conditions and notes in "Table 10-3 Output power-good signal output (OPGOOD)"<br>"≥ VOPGH" → "≥ VOPGH ( $V_{VOUT} \geq 3.3V$ ) (*1)"                                                                                                                                                                                                                                                                                                             |

| Page     | Section                          | Change Results                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17       | 11. Typical Application Circuits | <p>Wiring correction in "Figure 11-1 Application circuit for photovoltaic energy harvester"</p> <p>Deleted the wire connections between DCGND1 pin and the bridge rectifier, then added the internal GND.</p>                                                                                          |

| 17       | 11. Typical Application Circuits | <p>Wiring correction in "Figure 11-2 Application circuit for vibration energy harvester"</p> <p>Deleted the wire connections between DCGND2 pin and the bridge rectifier, then added the internal GND.</p>                                                                                             |

| 18       | 11. Typical Application Circuits | <p>Wiring correction in "Figure 11-3 Voltage doubler rectification circuit for vibration harvester"</p> <p>Deleted the wire connections between DCGND1 pin and the bridge rectifier, then added the internal GND.</p>                                                                                  |

| 19, 20   | 12. Application Notes            | <p>Added the "Table 12-1 Manufactures of recommended inductors"</p> <p>Added the "Table 12-2 Manufactures of photovoltaic harvesters"</p> <p>Added the "Table 12-3 Manufactures of vibration harvesters"</p> <p>Added the "Table 12-4 Manufactures of capacitors"</p>                                  |

| 23 to 28 | 13. Typical Characteristics      | <p>Inserted the data of 22<math>\mu</math>H and 10<math>\mu</math>H together into "Figure 13-1 Typical characteristics of DC/DC converter".</p> <p>Inserted the data of 22<math>\mu</math>H and 10<math>\mu</math>H together into "Figure 13-4 Switching waveforms of DC/DC converter".</p>            |

| 23, 24   | 13. Typical Characteristics      | <p>Replaced the line regulation datas of 22<math>\mu</math>H in "Figure 13-1 Typical characteristics of DC/DC converter"</p> <p>Replaced the load regulation datas of 22<math>\mu</math>H in "Figure 13-1"</p> <p>Added the line and load regulation data of 10<math>\mu</math>H in "Figure 13-1".</p> |

| 31       | 16. Ordering Information         | Deleted "Table 16-2 EVB Ordering information"                                                                                                                                                                                                                                                          |

**NOTE: Please see "Document History" about later revised information.**

## Document History

**Document Title:** MB39C811 Ultra Low Power Buck PMIC Solar/Vibrations Energy Harvesting

**Document Number:** 002-08401

| Revision | ECN     | Orig. of Change | Submission Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | —       | TAOA            | 12/05/2014      | Migrated to Cypress and assigned document number 002-08401.<br>No change to document contents or format.                                                                                                                                                                                                                                                                                                                           |

| *A       | 5124887 | TAOA            | 02/22/2016      | Updated to Cypress template                                                                                                                                                                                                                                                                                                                                                                                                        |

| *B       | 5738429 | HIXT            | 05/17/2017      | Updated <a href="#">Pin Assignments</a> :<br>Change the package name from QFN_40PIN to RLI040<br>Added <a href="#">RoHS Compliance Information</a><br>Updated <a href="#">Ordering Information</a> :<br>Change the package name from LCC-40P-M63 to RLI040<br>Deleted "Marking"<br>Deleted "Product Labels"<br>Deleted "Recommended Mounting Conditions"<br>Updated <a href="#">Package Dimensions</a> : Updated to Cypress format |

| *C       | 6369000 | YOST            | 10/29/2018      | Obsoleted.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at [Cypress Locations](#).

#### Products

Arm® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

Memory

Microcontrollers

PSoC

Power Management ICs

Touch Sensing

USB Controllers

Wireless Connectivity

[cypress.com/arm](http://cypress.com/arm)

[cypress.com/automotive](http://cypress.com/automotive)

[cypress.com/clocks](http://cypress.com/clocks)

[cypress.com/interface](http://cypress.com/interface)

[cypress.com/iot](http://cypress.com/iot)

[cypress.com/memory](http://cypress.com/memory)

[cypress.com/mcu](http://cypress.com/mcu)

[cypress.com/psoc](http://cypress.com/psoc)

[cypress.com/pmic](http://cypress.com/pmic)

[cypress.com/touch](http://cypress.com/touch)

[cypress.com/usb](http://cypress.com/usb)

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® Solutions

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### Cypress Developer Community

[Community](#) | [Projects](#) | [Videos](#) | [Blogs](#) | [Training](#)

| [Components](#)

#### Technical Support

[cypress.com/support](http://cypress.com/support)

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

© Cypress Semiconductor Corporation, 2014-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit [cypress.com](http://cypress.com). Other names and brands may be claimed as property of their respective owners.