# Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

# FAN5903 Buck Converter with Bypass Mode for 3G / 3.5G / 4G PAs

#### **Features**

- 2.7 V to 5.5 V Input Voltage Range

- V<sub>OUT</sub> Range from 0.4 V to 3.5 V (or V<sub>IN</sub>)

- Small Form Factor Inductor

- o 2012 470 nH or 540 nH for Minimal PCB Area

- o 2520 1.0 µH for Higher Efficiency

- Bypass Dropout at 500 mA, 60 mV Typical

- 100% Duty Cycle for Low Dropout Operation

- Input Under-Voltage Lockout / Thermal Shutdown

- 1.34 mm x 1.29 mm, 9-Bump, 0.4 mm-Pitch, Wafer-Level Chip-Scale Package (WLCSP)

- 3 MHz / 6 MHz Selectable Switching Frequency to Facilitate System Optimization

- High-Efficiency PFM Operation at Low Power

- Sleep Mode for Very Low IQ Operation

- Up to 96% Efficient Synchronous Operation at High-Power Conditions

- 10 µs Output Voltage Step Response for Early Power Loop Settling

# **Applications**

- Dynamic Supply Bias for 3G/3.5G and 4G PAs

- Power Supply for WCDMA/LTE PAs

#### Resources

For more information or a full copy of this datasheet, please contact a Fairchild representative.

# Description

FAN5903 is a high-efficiency, low-noise, synchronous, step-down, DC-DC converter designed for powering 3G / 3.5G / 4G RF Power Amplifiers (PAs) in handsets and other mobile applications.

The output voltage may be dynamically varied from 0.40~V to 3.50~V, proportional to an analog input  $V_{\rm CON}$ , ranging from 0.16~V to 1.40~V provided by an external DAC. This allows the PA to be supplied with the voltage that enables maximum power-added efficiency.

An integrated bypass FET automatically switches on when battery voltage drops close to the desired output voltage ( $V_{OUT} = V_{BAT}$  - 200 mV). The DC-DC switches back to Synchronous Mode when the voltage dropout exceeds 375 mV. The integrated bypass FET is also enabled when  $V_{CON}$  is nominally greater than to 1.5 V.

The FAN5903 offers fast transition times, enabling changes to the output voltage in less than 10  $\mu$ s for power transitions. Moreover, a Current-Mode control loop with fast transient response ensures excellent line and load regulation.

Light-load efficiency is optimized by operating in PFM Mode for load currents typically less than 100 mA.

The switching frequency may be set to 3 MHz or 6 MHz, enabling further optimization of system performance. The FAN5903 typically uses a single, small-form-factor inductor of 470 nH or 540 nH. Efficiency may be further optimized using a 1.0  $\mu$ H inductor when running at 3 MHz.

When output regulation is not required, the FAN5903 may be placed in Sleep Mode by setting  $V_{CON}$  nominally to 50 mV. This ensures a very low  $I_Q$  (<70  $\mu$ A) while enabling a fast return to output regulation. The FAN5903 enables significant current reduction and increased talk time and is available in a 1.34 mm x 1.29 mm, 9-bump, 0.40 mm-pitch, WLCSP package.

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                                                                         | Packing Method |

|-------------|--------------------------------|---------------------------------------------------------------------------------|----------------|

| FAN5903UCX  |                                | 1.34 mm x 1.29 mm, 9-bump, 0.4 mm Pitch, Wafer-Level Chip-Scale Package (WLCSP) | Tape and Reel  |

# **Application Diagrams**

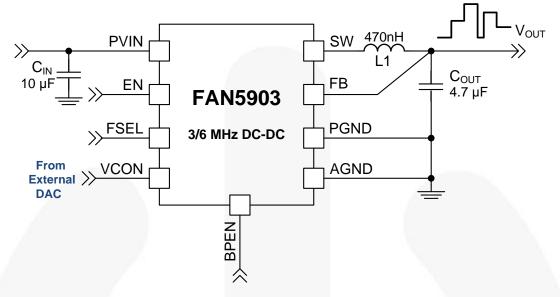

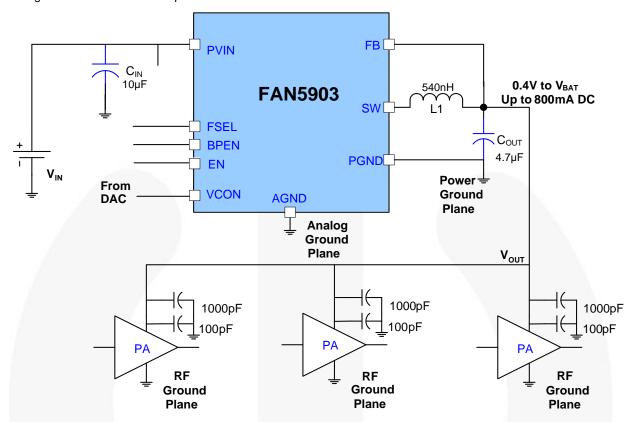

Figure 1. Application Circuit

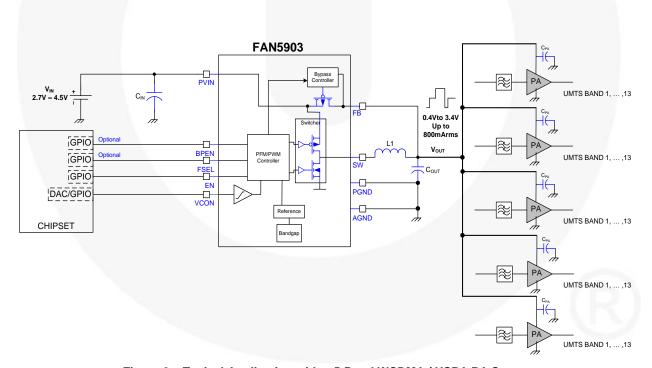

Figure 2. Typical Application with a 5-Band WCDMA / HSPA PA System

# **Pin Configuration**

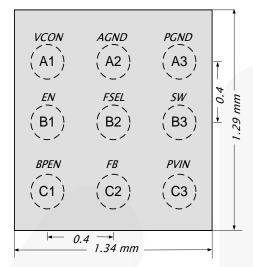

Figure 3. Top-Through View, Bumps Face Down

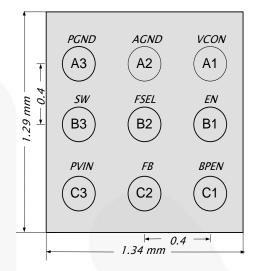

Figure 4. Top-Through View, Bumps Face Up

# **Pin Definitions**

| Pin# | Name | Description                                                                                                                                                      |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | VCON | Analog control pin. Shield signal routing against noise.                                                                                                         |

| A2   | AGND | Analog ground, reference ground for the IC. Follow PCB routing notes for connecting this pin.                                                                    |

| А3   | PGND | Power ground of the internal MOSFET switches. Follow routing notes for connections between PGND and AGND.                                                        |

| B1   | EN   | Enables switching when HIGH, Shutdown Mode when LOW. This pin should not be left floating.                                                                       |

| B2   | FSEL | Switching frequency select. When FSEL is LOW, the DC-DC operates at 6 MHz. When FSEL is HIGH, the DC-DC operates at 3 MHz. This pin should not be left floating. |

| В3   | SW   | Switching node of the internal MOSFET switches. Connect to output inductor.                                                                                      |

| C1   | BPEN | Force bypass transistor when HIGH; auto-bypass when LOW. This pin should not be left floating.                                                                   |

| C2   | FB   | Output voltage-sense pin. Connect to VOUT to establish feedback path for regulation point.                                                                       |

| C3   | PVIN | Supply voltage input to the internal MOSFET switches; connect to input power source.                                                                             |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           |                                         | Parameter                         | Min.                   | Max. | Unit  |

|------------------|-----------------------------------------|-----------------------------------|------------------------|------|-------|

| V                | PVIN                                    | /IN                               |                        |      | V     |

| V <sub>IN</sub>  | Voltage On Any Other Pi                 | -0.3                              | PV <sub>IN</sub> + 0.3 | V    |       |

| TJ               | Junction Temperature                    | -40                               | +125                   | °C   |       |

| T <sub>STG</sub> | Storage Temperature                     |                                   | -65                    | +150 | °C    |

| TL               | Lead Soldering Temperature (10 Seconds) |                                   |                        | +260 | °C    |

| ESD              | Electrostatic Discharge                 | Human Body Model, JESD22-A114     | 2.0                    |      | IA) / |

| ESD              | Protection                              | Charged Device Model, JESD22-C101 | 1.5                    |      | kV    |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                |                                     | Parameter                | Min. | Тур. | Max.              | Unit |

|-----------------------|-------------------------------------|--------------------------|------|------|-------------------|------|

| V <sub>IN</sub>       | Supply Voltage Ra                   | Voltage Range            |      |      | 5.5               | V    |

| V <sub>OUT</sub>      | Output Voltage Range                |                          | 0.35 |      | <v<sub>IN</v<sub> | V    |

| I <sub>OUT_BYP</sub>  | Output Current (Bypass Mode)        |                          |      |      | 2.4               | Α    |

| I <sub>OUT_DCDC</sub> | Output Current (DCDC Mode)          |                          |      |      | 1.0               | Α    |

| L1 Inductor           |                                     | 6 0 1411-                |      | 470  |                   |      |

|                       | $f_{SW} = 6 \text{ MHz}$            |                          | 540  |      | nH                |      |

|                       |                                     | $f_{SW} = 3 \text{ MHz}$ |      | 1.00 |                   | μΗ   |

| C <sub>IN</sub>       | Input Capacitor <sup>(1)</sup>      |                          |      | 10   |                   | μF   |

| C <sub>OUT</sub>      | Output Capacitor                    |                          | 2.2  | 4.7  |                   | μF   |

| T <sub>A</sub>        | Operating Ambient Temperature Range |                          | -40  | 1    | +85               | °C   |

| TJ                    | Operating Junction                  | n Temperature Range      | -40  |      | +125              | °C   |

#### Note:

1. A large enough input capacitor value is required for limiting the input voltage drop during bursts, bypass transitions, or during large output voltage transitions. Ensure the input capacitor value is greater than the output capacitor's. See the inrush current specifications below.

# **Dissipation Ratings**

| Symbol        | Parameter                                             | Min. | Тур. | Max. | Unit |

|---------------|-------------------------------------------------------|------|------|------|------|

| $\Theta_{JA}$ | Junction-to-Ambient Thermal Resistance <sup>(2)</sup> |      | 110  |      | °C/W |

#### Note:

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JESD51- JEDEC standard. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperate T<sub>A</sub>.

# **Electrical Characteristics**

$V_{IN}$  =  $V_{OUT}$  + 0.6 V,  $I_{OUT}$  = 200 mA, EN =  $V_{IN}$ ,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C,  $V_{IN}$  = 3.7 V.

| Symbol                 | Parameter                                 | Condition                                                                                   | Min.  | Тур.        | Max. | Unit |

|------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------------|------|------|

| Power Supp             | olies                                     |                                                                                             |       |             |      |      |

| $V_{IN}$               | Input Voltage Range                       | I <sub>OUT</sub> ≤ 800 mA                                                                   | 2.7   |             | 5.5  | V    |

| I <sub>SD</sub>        | Shutdown Supply Current                   | EN = 0 V                                                                                    |       | 1           | 3    | μΑ   |

| IQ                     | Quiescent Current                         | Sleep Enabled                                                                               |       | 70          |      | μΑ   |

|                        |                                           | V <sub>IN</sub> Rising                                                                      | 2.30  | 2.45        | 2.60 | V    |

| $V_{UVLO}$             | Under Voltage Lockout Threshold           | Hysteresis                                                                                  |       | 175         |      | mV   |

| V <sub>IH</sub>        | Logic Threshold Voltage: EN,              | Input HIGH Threshold                                                                        | 1.2   |             |      | V    |

| V <sub>IL</sub>        | FSEL and BPEN                             | Input LOW Threshold                                                                         | ,4    |             | 0.5  | V    |

| I <sub>EN</sub>        | EN Input Bias Current                     | EN = V <sub>IN</sub> or GND                                                                 |       | 0.01        | 1.00 | μΑ   |

| Oscillator             |                                           |                                                                                             |       |             |      |      |

| f <sub>SW</sub>        | Average Oscillator Frequency              | FSEL = 0                                                                                    | 5.4   | 6.0         | 6.6  | MHz  |

| f <sub>SW</sub>        | Average Oscillator Frequency              | FSEL = 1                                                                                    | 2.7   | 3.0         | 3.3  | MHz  |

| DC-DC Mod              |                                           |                                                                                             |       |             |      |      |

|                        | PMOS On Resistance <sup>(3)</sup>         | $V_{IN} = V_{GS} = 3.7 \text{ V}$                                                           |       | 230         |      | mΩ   |

| R <sub>DSON</sub>      | NMOS On Resistance <sup>(3)</sup>         | $V_{IN} = V_{GS} = 3.7 \text{ V}$                                                           |       | 150         |      | mΩ   |

| I <sub>LIMp</sub>      | P-Channel Current Limit                   |                                                                                             | 1.2   | 1.5         | 1.8  | Α    |

| I <sub>LIMn</sub>      | N-Channel Current Limit                   |                                                                                             | 0.8   | 1.1         | 1.4  | Α    |

| V <sub>OUT_MIN</sub>   | Minimum Output Voltage                    | V <sub>CON</sub> = 0.16 V                                                                   | 0.35  | 0.40        | 0.45 | V    |

| V <sub>OUT MAX</sub>   | Maximum Output Voltage                    | V <sub>CON</sub> = 1.40 V                                                                   | 3.45  | 3.50        | 3.55 | V    |

| Gain                   | Gain in Control Range 0.16V to 1.40V      |                                                                                             |       | 2.5         |      |      |

| V <sub>OUT_ACC</sub>   | V <sub>OUT</sub> Accuracy                 | Ideal = 2.5 x V <sub>CON</sub>                                                              | -50   |             | +50  | mV   |

| Bypass Mod             | -                                         |                                                                                             |       |             | 1    |      |

| R <sub>FET</sub>       | Bypass FET Resistance <sup>(4)</sup>      | $V_{IN} = V_{GS} = 3.7 \text{ V}$                                                           |       | 210         |      | mΩ   |

| $\Delta V_{OUT\_BP}$   | Bypass Mode Output Voltage Drop           | I <sub>OUT</sub> = 500 mA                                                                   | - 1/1 | 60          |      | mV   |

| Output Reg             | <u> </u>                                  |                                                                                             |       | 1           | 1    |      |

| V <sub>OUT_RLine</sub> | V <sub>OUT</sub> Line Regulation          |                                                                                             | 7     | <u>+</u> 5  | 1    | mV   |

| V <sub>OUT_RL</sub>    | V <sub>OUT</sub> Load Regulation          | I <sub>OUT</sub> ≤ 800 mA                                                                   |       | <u>+</u> 25 |      | mV   |

| V <sub>CON_SL_EN</sub> | V <sub>CON</sub> Sleep Mode Enter         | V <sub>CON</sub> Voltage that Forces Very<br>Low I <sub>Q</sub> Sleep Mode                  | 50    |             |      | mV   |

| V <sub>CON_SL_EX</sub> | V <sub>CON</sub> Sleep Mode Exit          | V <sub>CON</sub> Voltage that Exits Sleep<br>Mode                                           |       | 1/2         | 135  | mV   |

| V <sub>CON_BP_EN</sub> | V <sub>CON</sub> Forced Bypass Mode Enter | V <sub>CON</sub> Voltage that Forces<br>Bypass, V <sub>IN</sub> = 2.70 V - 4.75 V           | 1.6   |             | (1   | V    |

| V <sub>CON_BP_EX</sub> | V <sub>CON</sub> Forced Bypass Mode Exit  | V <sub>CON</sub> Voltage that Exits<br>Forced; Bypass,<br>V <sub>IN</sub> = 2.70 V - 4.75 V |       |             | 1.4  | V    |

| $V_{BP\_ThH}$          | Voltage Threshold to Enter Bypass Mode    | V <sub>IN</sub> – V <sub>OUT</sub>                                                          | 160   | 200         | 240  | mV   |

| $V_{BP\_ThL}$          | Voltage Threshold to Exit Bypass Mode     | V <sub>IN</sub> – V <sub>OUT</sub>                                                          | 320   | 375         | 440  | mV   |

| т.                     | Over Temperature Protection               | Rising Temperature                                                                          |       | +150        |      | ۰.   |

| $T_{OTP}$              | Over-Temperature Protection               | Hysteresis                                                                                  |       | +20         |      | °C   |

#### **Electrical Characteristics**

$V_{IN}$  =  $V_{OUT}$  + 0.6 V,  $I_{OUT}$  = 200 mA, EN =  $V_{IN}$ ,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C,  $V_{IN}$  = 3.7 V.

| Symbol                | Parameter                                                          | Condition                                                                                                                | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Timings               |                                                                    |                                                                                                                          | •    | •    |      |      |

| t <sub>SS</sub>       | Startup Time                                                       | $V_{\text{IN}} = 3.7$ V, $V_{\text{OUT}}$ from 0 V to 3.1 V, $C_{\text{OUT}} = 4.7~\mu\text{F},~10~\text{V},$ X5R        |      | 30   | 40   | μs   |

| t <sub>SP_en</sub>    | Sleep Mode Enter Time                                              | V <sub>CON</sub> < 50 mV                                                                                                 |      | 40   |      | μs   |

| t <sub>SP_ex</sub>    | Sleep Mode Exit Time                                               | V <sub>CON</sub> ≥ 135 mV                                                                                                |      | 11   |      | μs   |

| t <sub>DC-DC_TR</sub> | V <sub>OUT</sub> Step Response Rise Time <sup>(3)</sup>            | $V_{OUT}$ from 5% to 95%,<br>$\Delta V_{OUT} < 2 \text{ V (1.4 V} - 3.4 \text{ V)}$ ,<br>$R_{LOAD} \le 7 \Omega$         |      |      | 10   | μs   |

| t <sub>DC-DC_TF</sub> | V <sub>OUT</sub> Step Response Fall Time <sup>(3)</sup>            | $V_{OUT}$ from 95% to 5%,<br>$\Delta V_{OUT} < 2 \text{ V } (3.4 \text{ V} - 1.4 \text{ V}),$<br>$R_{LOAD} \le 7 \Omega$ |      |      | 12   | μs   |

| t <sub>DC-DC_CL</sub> | Maximum Allowed Time for Consecutive Current Limits <sup>(5)</sup> |                                                                                                                          |      | 40   |      | μs   |

| t <sub>DCDC_CLR</sub> | Consecutive Current Limit<br>Recovery Time <sup>(3)</sup>          |                                                                                                                          |      | 180  |      | μs   |

#### Notes:

- 3. Guaranteed by design; not tested in production.

- 4. Bypass FET resistance does not include the PFET R<sub>DSON</sub> and inductor DCR in parallel with the bypass FET in Bypass Mode.

- 5. Protects part under short circuit conditions. After 40 μs, operation halts and restarts after 180 μs. Under heavy capacitive loads, V<sub>CON</sub> slew rate may be reduced to avoid consecutive current limits. Under typical conditions for a 3 V change at the output, a capacitive only load of up to 40 μF is supported, assuming a step at the V<sub>CON</sub> input.

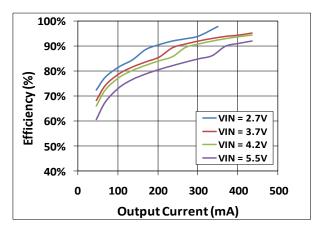

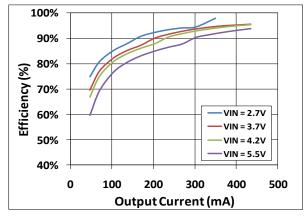

Figure 5. Efficiency vs. Output Current vs. Input Voltage,  $f_{SW} = 6$  MHz,  $R_{PA} = 7$   $\Omega$

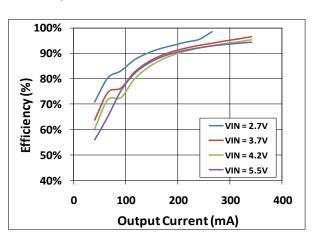

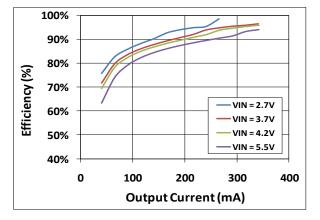

Figure 6. Efficiency vs. Output Current vs. Input Voltage,  $f_{SW}$  = 6 MHz,  $R_{PA}$  = 10  $\Omega$

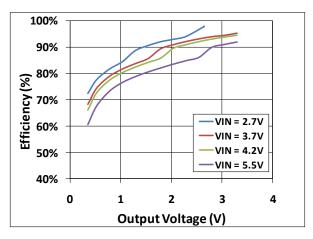

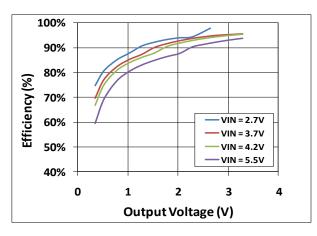

Figure 7. Efficiency vs. Output Voltage vs. Input Voltage,  $f_{SW} = 6$  MHz,  $R_{PA} = 7$   $\Omega$

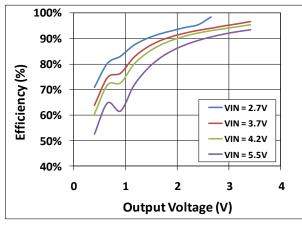

Figure 8. Efficiency vs. Output Voltage vs. Input Voltage,  $f_{SW} = 6$  MHz,  $R_{PA} = 10 \Omega$

Figure 9. Efficiency vs. Output Current vs. Input Voltage,  $f_{SW} = 3$  MHz,  $R_{PA} = 7$   $\Omega$

Figure 10. Efficiency vs. Output Current vs. Input Voltage,  $f_{SW}$  = 3 MHz,  $R_{PA}$  = 10  $\Omega$

100% 90% 80% Efficiency (%) 70% VIN = 2.7V 60% VIN = 3.7V VIN = 4.2V 50% VIN = 5.5V 40% 0 1 2 3 4 Output Voltage (V)

Figure 11. Efficiency vs. Output Voltage vs. Input Voltage,  $f_{SW}$  = 3 MHz,  $R_{PA}$  = 7  $\Omega$

Figure 12. Efficiency vs. Output Voltage vs. Input Voltage,  $f_{SW}$  = 3 MHz,  $R_{PA}$  = 10  $\Omega$

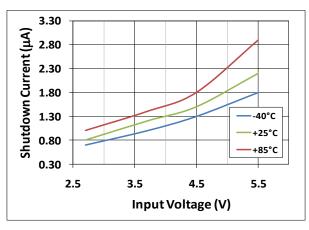

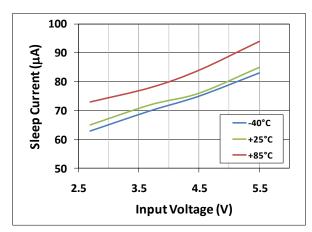

Figure 13. Shutdown Current vs. Input Voltage vs. Temperature

Figure 14. Sleep Mode Current vs. Input Voltage vs. Temperature

Figure 15. Rise Times for 300 mV, 500 mV, and 2 V  $\Delta V_{OUT}$  (V<sub>IN</sub> = 3.7 V)

Figure 16. Rise Times for 300 mV, 500 mV, and 2 V  $\Delta V_{OUT}$  (V<sub>IN</sub> = 3.7 V)

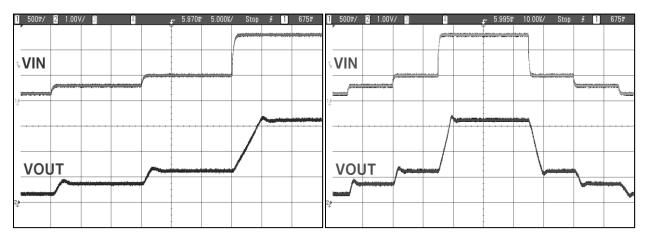

Figure 17. Line Transient  $V_{IN}$  = 3.7 V to 4.2 V,  $V_{OUT}$  = 2.5 V, 10  $\Omega$  Load, 50  $\mu$ s/div.

Figure 18. Line Transient  $V_{IN}$  = 3.7 V to 4.2 V,  $V_{OUT}$  = 1.0 V, 10  $\Omega$  Load, 50  $\mu$ s/div.

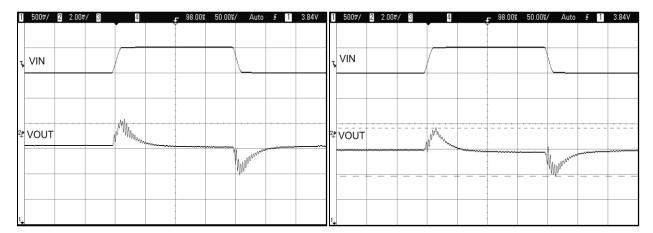

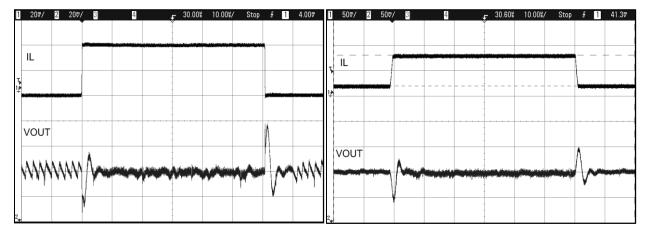

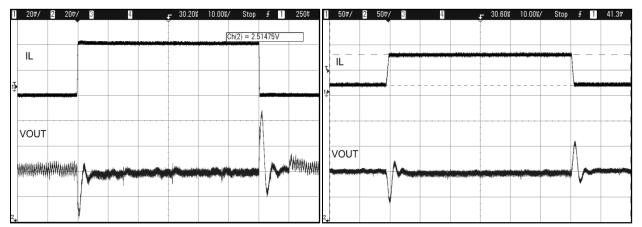

Figure 19. Load Transient, 0 mA to 400 mA,  $V_{OUT}$  = 1.0 V

Figure 20. Load Transient, 200 mA to 800 mA,  $V_{OUT}$  = 1.0 V

Figure 21. Load Transient, 0 mA to 400 mA,  $V_{OUT} = 2.5 \text{ V}$

Figure 22. Load Transient, 200 mA to 800 mA, V<sub>OUT</sub> = 2.5 V

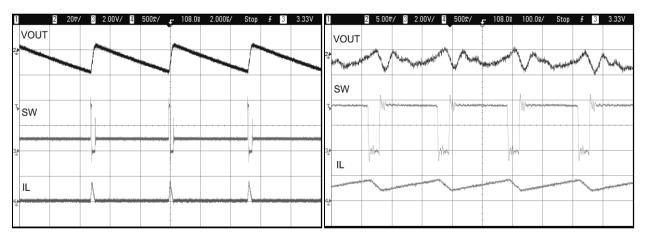

Figure 23. Switching Waveforms, PFM Mode,  $I_{LOAD} = 10$  mA (Light Load)

Figure 24. Switching Waveforms, PWM Mode, f<sub>SW</sub> = 6 MHz, I<sub>LOAD</sub> = 300 mA (Heavy Load)

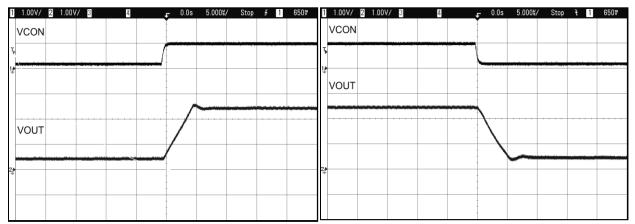

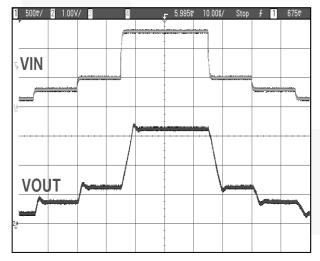

Figure 25.  $V_{\text{OUT}}$  Rising Transition 0.5 V to 2.5 V,  $V_{\text{IN}} = 3.7 \text{ V}$

Figure 26.  $V_{OUT}$  Falling Transition 2.5 V to 0.5 V,  $V_{IN} = 3.7 \text{ V}$

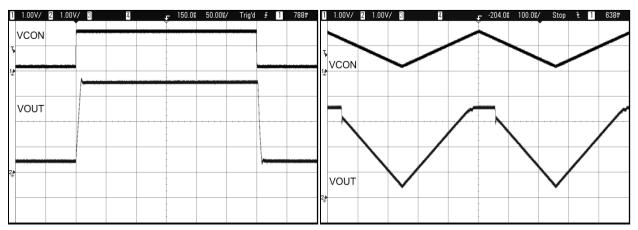

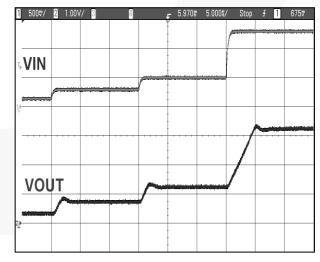

Figure 27.  $V_{OUT}$  Transient Response  $\Delta V_{OUT} = 3 \text{ V}$

Figure 28.  $V_{OUT}$  Transient and Bypass Response  $\Delta V_{OUT}$  > 3 V,  $V_{CON}$  Stepped Above 1.5 V

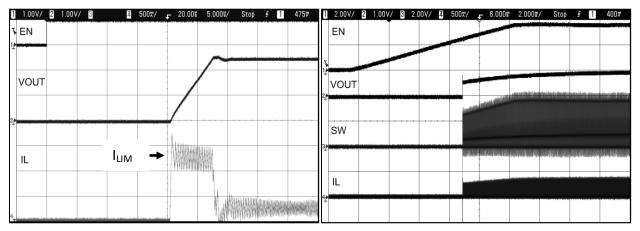

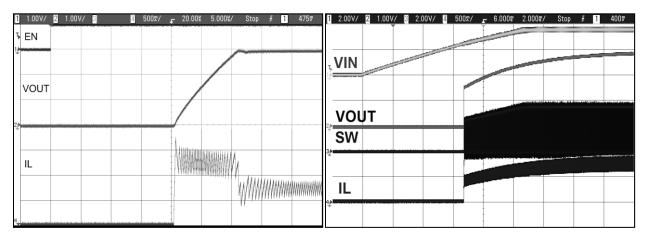

Figure 29. Soft-Start Transient Response from 0 mA to 100 mA

Figure 30. Cold-Start Transient Response from 0 mA to 100 mA

Figure 31. Soft-Start Transient Response from 0 mA to 800 mA

Figure 32. Cold-Start Transient Response from 0 mA to 800 mA

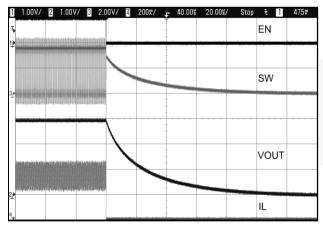

Figure 33. Shutdown Transient Response

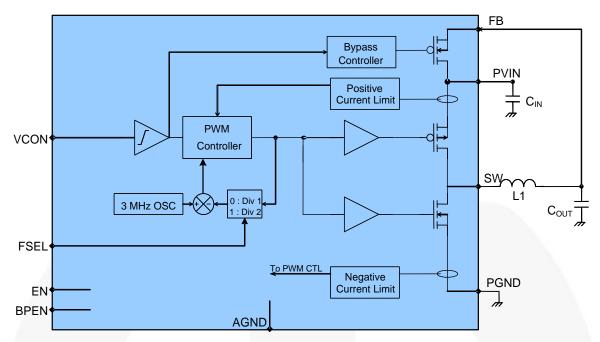

# **Block Diagram**

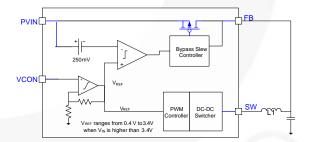

Figure 34. Block Diagram

# **Operating Mode Description**

The FAN5903 is a high-efficiency synchronous step-down DC-DC converter operating with a Current-Mode control. It adjusts the output voltage,  $V_{\text{OUT}}$ , depending on the set voltage  $V_{\text{CON}}$  provided by an external DAC. Regulated  $V_{\text{OUT}}$  is set to 2.5 times input voltage  $V_{\text{CON}}$ .

The DC-DC operates in PWM Mode or PFM Mode, depending on the output voltage and load current. Bypass Mode is supported where the output voltage is shorted to the input voltage via a low on-state resistance bypass FET.

The FAN5903 supports a wide range of load currents. High-current applications, up to a DC output of 800 mA, mandated by 3G / 3.5G and 4G applications, for example, are supported. System performance may be optimized by enabling the DC-DC to run at either a 3 MHz or 6 MHz switching rate.

#### **Auto Mode**

In Pulse Width Modulation (PWM) Mode, regulation starts with an on-state where a P-channel transistor is turned on and the inductor current is ramped up until the off state begins. In the off state, the P-channel is switched off and an N-channel transistor is turned on. The inductor current decreases to maintain an average value equal to the DC load current. The inductor current is continuously

monitored. A current sense flags when the P-channel transistor current exceeds the current limit and the switcher is turned off to decrease the inductor current and prevent magnetic saturation. Similarly, the current sense flags when the N-channel transistor current exceeds the current limit and re-directs discharging current through the inductor back to the battery.

In Pulse Frequency Modulation (PFM) Mode, at low output voltages and load currents, typically less than 100 mA; the DC-DC operates in a constant On-Time Mode. In the on-state, the P-channel is turned on during a well-defined on-time before switching to the off state, whereby the N-channel switch is turned on and the inductor current is decreased to 0 A. The switcher output is put into high-resistance state until the new regulation cycle starts.

PFM Mode realizes high efficiency while maintaining RF system performance down to low load currents.

## **Bypass Mode**

**In Bypass Mode**, the FAN5903 operates at 100% duty cycle with the bypass FET turned on. This enables a very low voltage dropout with up to 2.4 A DC load current. In applications with 3G / 3.5G and 4G PAs, the Bypass Mode typically handles 800 mA.

**Table 1. Mode Descriptions**

|   | Mode            | Mode Mode Description -                                             |      | Conditions |    |      |  |

|---|-----------------|---------------------------------------------------------------------|------|------------|----|------|--|

| # | Wiode           | Mode Description                                                    | FSEL | BPEN       | EN | VCON |  |

| 1 | Shutdown Mode   | ne whole IC is disabled.                                            |      | Х          | 0  | 0    |  |

| 2 | Sleep Mode      | The DC-DC is in Sleep Mode and consumes less than 70 µA of current. | Х    | Х          | 1  | 0    |  |

| 3 | 6 MHz Auto Mode | The DC-DC is in Auto Mode and switches at 6 MHz. (6,7)              | 0    | 0          | 1  | 1    |  |

| 4 | 3 MHz Auto Mode | The DC-DC is in Auto Mode and switches at 3 MHz.                    | 1    | 0          | 1  | 1    |  |

| 5 | Bypass Mode     | The bypass FET is forced ON. The DC-DC is set to 100% duty cycle.   | Х    | 1          | 1  | 1    |  |

#### Notes:

- 6. When  $V_{OUT}$  exceeds  $V_{IN}$  200 mV, the bypass FET is enabled and the DC-DC goes to 100% duty cycle. When  $V_{OUT} \le V_{IN}$  375 mV, the bypass FET is disabled and the DC-DC goes to Auto Mode.

- When the load current is smaller than PFM current threshold, the DC-DC changes to PFM Mode.

# **DC Output Voltage**

The output voltage of the DC-DC is determined by  $V_{CON}$ , provided by an external DAC or voltage reference:

$$V_{OUT} = 2.5 \times V_{CON} \tag{1}$$

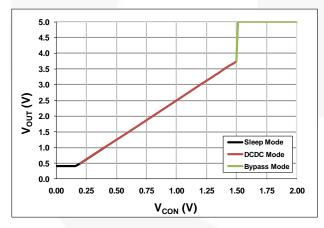

Figure 35. Output Voltage vs. Control Voltage

The DC-DC is able to provide a regulated  $V_{\text{OUT}}$  only if  $V_{\text{CON}}$  is between 0.16 V to 1.40 V. This allows  $V_{\text{OUT}}$  to be adjusted between 0.40 V and 3.50 V. If  $V_{\text{CON}}$  is below this range,  $V_{\text{OUT}}$  is clamped to 0.40 V as minimum and enters bypass for  $V_{\text{CON}} > 1.50$  V. If  $V_{\text{CON}}$  is less than 50 mV, FAN5903 enters a non-regulated Sleep Mode. This reduces current consumption to less than 70  $\mu$ A while allowing for a rapid return to regulation.

FAN5903 automatically switches between PFM, PWM, and Bypass Modes.

The DC-DC is able to provide a regulated  $V_{OUT}$  only if the battery voltage is 200 mV greater than  $V_{OUT}$ .

# **Bypass Mode**

The trigger to enter Bypass Mode is based on the voltage difference between the battery voltage (sensed through the PVIN pin) and the internally generated reference voltage,  $V_{REF},$  as depicted in Figure 36. The DC-DC enters Bypass Mode when  $V_{\text{IN}} = V_{\text{OUT}} + 200 \text{ mV}.$  It then turns into 100% duty cycle and the low-R\_DSON bypass FET is turned on. As  $V_{\text{OUT}}$  approaches  $V_{\text{IN}};$  the DC-DC operates in a constant off-time mode, the frequency is decreased to achieve a high duty cycle, and the system continues to run in a regulated mode until the bypass condition is satisfied.

As noted above, Bypass Mode is also entered when  $V_{\text{CON}}\,\text{exceeds}\,\,1.5\,\,\text{V}.$

Figure 36. Enabling Bypass Transistor Circuit

The bypass FET is turned on progressively using a slew rate controller to limit the inrush current. The inrush current is expressed as a function of the specified slew rate as follows:

$$I_{INRUSH} \approx C_{OUT} \frac{\Delta V_{OUT}}{\Delta t} = C_{OUT} \bullet V_{BP\_SLEW}$$

(2)

The slew rate controller is not used when releasing the Bypass Mode.

# **Switching Frequency Selection (FSEL)**

In some cases, it may be desirable to change the DC-DC's switching frequency from 6 MHz (FSEL = 0) to 3 MHz (FSEL = 1). At 3 MHz operation the DC-DC's efficiency is generally higher than that at 6 MHz. The primary tradeoff with this is increased voltage ripple at the lower frequency. A 1.0  $\mu$ H inductor may be used in 3 MHz operation to optimize efficiency and ripple.

The FAN5903 is designed to have minimal impact on the RF output spectrum at either switching frequency.

# **Dynamic Output Voltage Transitions**

The FAN5903 has a complex voltage transition controller that realizes less than 10 µs transition times with a large output capacitor and output voltage ranges.

The transition controller manages five transitions:

- ∆V<sub>OUT</sub> positive step

- ∆V<sub>OUT</sub> negative step

- ∆V<sub>OUT</sub> transition to or from Bypass Mode

- ∆V<sub>OUT</sub> transition at startup

- ∆V<sub>OUT</sub> transition after BPEN

In most cases, sharp  $V_{\text{CON}}$  transitions and letting the transition controller optimize the output voltage slew rate are recommended.

#### ΔV<sub>OUT</sub> Positive Step

After a  $V_{CON}$  positive step, the DC-DC enters a Current-Limit Mode, where  $V_{OUT}$  ramps with a constant slew rate dictated by the output capacitor and the current limit.

## $\Delta V_{OUT}$ Negative Step

After a V<sub>CON</sub> negative step, the DC-DC enters Current-Limit Mode, where V<sub>OUT</sub> is reduced with a constant slew rate dictated by the output capacitor and the current limit.

#### **VOUT** Transition to or from Bypass Mode

The transition to or from Bypass Mode requires the bypass conditions be met. The FAN5903 performs detection of the bypass conditions 2  $\mu$ s after V<sub>CON</sub> transition and enables the required charging / discharging circuit to realize a transition time of 10  $\mu$ s.

#### **VOUT Transition at Startup**

At startup, after EN rising edge is detected, the system requires 40 µs to enable all internal voltage references and amplifiers before enabling the DC-DC function.

#### **VOUT Transition After BPEN**

When BPEN goes HIGH, the controller dismisses the internal bypass flags and sensors and enables Bypass Mode. However, the transition is managed with the same current limit and slew rate used during regular transitions.

#### **Thermal Protection**

If the junction temperature exceeds the maximum specified junction temperature, the FAN5903 enters Power-Down Mode (except the thermal detection circuit).

## Sleep Mode

The FAN5903 offers a Sleep mode to minimize current, while also enabling a rapid return to regulation. Sleep Mode is entered when  $V_{\rm CON}$  is held below 50 mV for at least 40  $\mu$ s. In this mode, current consumption is reduced to under 70  $\mu$ A. Sleep Mode is exited after approximately 12  $\mu$ s when  $V_{\rm CON}$  is set above 135 mV.

# **Typical Voltage Transitions**

Figure 37. Rise and Fall Times for 300 mV, 500 mV, and 2 V  $\Delta V_{OUT}$  ( $V_{IN}$  = 3.7 V)

Figure 38. Rise Times for 300 mV, 500 mV, and 2 V  $\Delta V_{OUT}$  (V<sub>IN</sub> = 3.7 V)

# **Application Information**

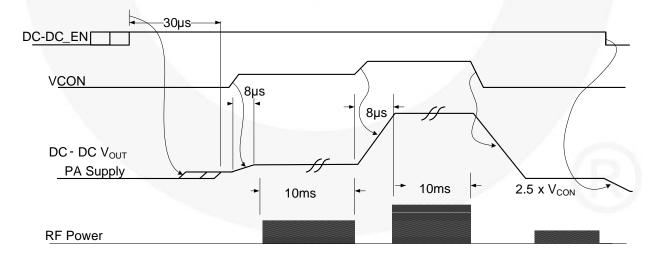

Figure 39 illustrates an application of the FAN5903 in a 3G / 4G transmitter. The FAN5903 is designed for driving multiple PAs. Figure 40 presents a timing diagram designed to meet WCDMA specifications. The FAN5903 supports voltage transients less than 10  $\mu$ s.

Figure 39. Typical Application Diagram of FAN5903 Supplying Power to Three 3G or 4G PAs

Figure 40. Timing Diagram for 3G/4G Transmitters

# **Application Information**

#### Inductor Selection

The FAN5903 is able to operate at 3 MHz or 6 MHz switching frequency, so 470 nH (or 540 nH) or 1.0  $\mu$ H inductors can be used, respectively. To achieve optimum efficiency, it is recommended that the FAN5903 switch at 3 MHz (FSEL = HIGH), using a 1.0  $\mu$ H inductor. For applications that require the smallest possible PCB area, the FAN5903 should be configured for 6 MHz operation (FSEL = LOW) to allow use of a 470 nH or 540 nH 2012 inductor.

**Table 2. Recommended Inductors**

| Inductor | f <sub>SW</sub> | Description                                                         |

|----------|-----------------|---------------------------------------------------------------------|

|          | A               | 470 nH, ±20%, 1100 mA, 2012<br>(metric)<br>Murata: LQM21PNR47MC0    |

| 11       | 6 MHz           | 470 nH, ±30%, 1200 mA, 2012<br>(metric)<br>Panasonic: ELGTEAR47NA   |

| _1       |                 | 540 nH, ±20%, 1300 mA, 2012<br>(metric)<br>Murata: LQM21PNR54MG0    |

|          | 3 MHz           | 1.0 µH, ±20%, 2500 mA, 3030<br>(metric)<br>Coilcraft: XFL3010-102ME |

#### **Capacitor Selection**

The minimum required output capacitor  $C_{OUT}$  is 4.7  $\mu$ F, 6.3 V, X5R with an ESR of 10 m $\Omega$  or lower and an ESL of 0.3 nH or lower. Larger case sizes result in increased loop parasitic inductance and higher noise.

A 0.1  $\mu$ F capacitor may be added in parallel with C<sub>OUT</sub> to reduce the effect of the capacitor's parasitic inductance.

**Table 3. Recommended Capacitor Values**

| Capacitor             | Description              |

|-----------------------|--------------------------|

| C <sub>IN</sub>       | 10 μF, ±20%, X5R, 10 V   |

| C <sub>OUT</sub>      | 4.7 μF, ±20%, X5R, 6.3 V |

| C on V <sub>CON</sub> | 470 pF, ±20%, X5R        |

#### **Filter VCON**

VCON is the analog control pin of the DC-DC and should be connected to an external Digital-to-Analog Converter (DAC). It is recommended to place up to 470 pF decoupling capacitance between VCON and AGND to filter the DAC noise. This capacitor also helps protect the DAC from the DC-DC high-frequency switching noise coupled through the VCON pin.

Any noise on the  $V_{\text{CON}}$  input is transferred to  $V_{\text{OUT}}$  with a gain of two and a half (2.5). If the DAC output is noisy, a series resistor may be inserted between the DAC output and the capacitor to form an RC filter.

Follow these guidelines:

- Use a low noise source or a driver with good PSRR to generate V<sub>CON</sub>.

- The V<sub>CON</sub> driver must be referenced to AGND.

- V<sub>CON</sub> routing must be protected against PVIN, SW, PGND signals, and other noisy signals. Use AGND shielding for better isolation.

- Be sure the DAC output can drive the 470 pF capacitor on VCON. It may be necessary to insert a low value resistor to ensure DAC stability without slowing V<sub>CON</sub> fast transition times.

#### No Floating Inputs

The FAN5903 does not have internal pull-down resistors on its inputs. Therefore, unused inputs should not be left floating and should be pulled HIGH or LOW.

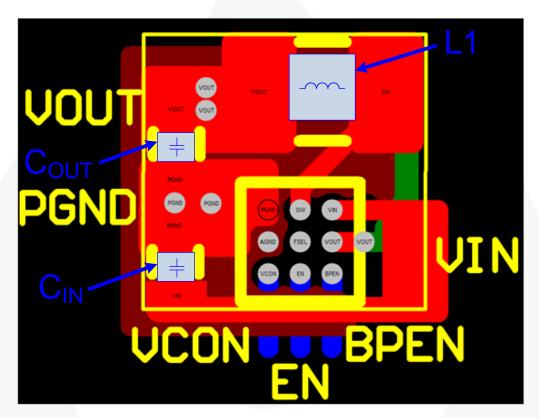

# **PCB Layout & Component Placement**

- Make sure the FAN5903, C<sub>IN</sub>, and C<sub>OUT</sub> are all tied to the same power ground (PGND). This minimizes the parasitic inductance of the switching loop paths.

- Place PGND on the top layer and connect it to the AGND ground plane next to C<sub>OUT</sub> using several vias.

- Ensure that the routing loop, PVIN PGND -VOUT is the shortest possible.

- Place the inductor away from the FB connection to prevent unpredictable loop behavior.

- Use the application circuit layout in Figure 41 whenever possible. The performance of this layout has been verified.

- Review the layout guidelines for the IC package. This is especially important for the WLCSP package. Refer to "Surface Mount Assembly of Amkor's Eutectic and Lead-Free CSPnI™ Wafer-Level Chip-Scale Package" available from the Amkor website.

- PVIN and PGND must be routed with the widest and shortest traces possible. It is acceptable for the traces connecting the inductor to be long rather than having long PVIN or PGND traces. The SW node is a source of electrical switching noise. Do not route it near sensitive analog signals.

- Two small vias are used to connect the SW node to the inductor L1. Use solder-filled vias if available.

- The connection from C<sub>OUT</sub> to FB should be wide to minimize the Bypass mode voltage drop and the series inductance. Even if the current in Bypass Mode is small, keep this trace short and at least 5mm wide.

- The ground plane should be not be broken into pieces. Ground currents must have a direct, wide path from input to output.

- Each capacitor should have at least two dedicated ground vias. Place vias within 0.1 mm of the capacitors.

- Ensure the traces are wide enough to handle the maximum current value, especially in Bypass Mode.

- Ensure the vias are able to handle the current density. Use metal-filled vias if available.

# **Assembly**

- Use metal-filled or solder-filled vias if available.

- Poor soldering can cause low DC-DC conversion efficiency. If the efficiency is low, X-ray the solder connections to verify their integrity.

Figure 41. Recommended PCB Layout

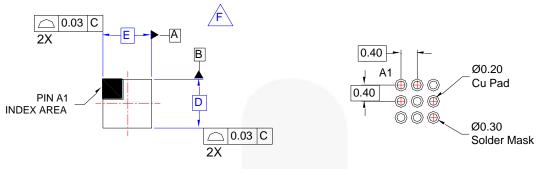

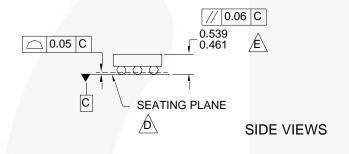

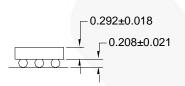

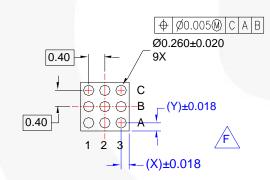

# **Physical Dimensions**

# LAND PATTERN RECOMMENDATION (NSMD PAD TYPE)

**BOTTOM VIEW**

## NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASMEY14.5M, 1994.

- D. DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE NOMINAL HEIGHT IS 500 MICRONS ±39 MICRONS (461-539 MICRONS).

- F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

- G. DRAWING FILNAME: MKT-UC009AErev1

| Product    | D             | Е             | X     | Y     | Unit |

|------------|---------------|---------------|-------|-------|------|

| FAN5903UCX | 1.292 ± 0.030 | 1.342 ± 0.030 | 0.271 | 0.246 | mm   |

Figure 42. 1.34 x 1.29 mm, 9-Bump, 0.4 mm-Pitch WLCSP

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™ FPS™ AccuPower™ F-PFS™ FRFET® AX-CAP® BitSiC™ Global Power Resource GreenBridge™ Build it Now™ Green FPS™ CorePLUS™ Green FPS™ e-Series™ CorePOWER™ CROSSVOLT™ Gmax<sup>⊤</sup> GTO™ CTL™ IntelliMAX™ Current Transfer Logic™ DEUXPEED<sup>®</sup> ISOPLANAR\*\*

Dual Cool™ Making Small Speakers Sound Louder EcoSPARK<sup>®</sup> and Better™

EfficientMax™

ESBC™

MicroCOUPLER™

MicroFET™

MicroPak™

Fairchild®

Fairchild Semiconductor®

FACT®

FACT®

MicroPak™

MillerDrive™

MotionMax™

mWSaver™

FACT® Motioninax™

FAST® mWSaver™

FastvCore™ OptoHiT™

FETBench™ OPTOLOGIC®

OPTOPLANAR®

PowerTrench®

PowerXS™

Programmable Active Droop™

QFET®

QS™

Quiet Series™

RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM®

STEALTH™

SuperFET®

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

SupreMOS®

SyncFET™

Sync-Lock™ SYSTEM GENERAL®

VERTORS UHC®

UItra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.  The datasheet is for reference information only.                                                   |

Rev. 164

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

FAN5903UCX FAN5903BUCX