## **LV5609LP**

# Bi-CMOS LSI Vertical Clock Driver for CCD

http://onsemi.com

#### Overview

The LV5609LP is vertical clock driver for CCD.

#### **Functions**

- Ternary output ×2ch

- Binary output ×2ch

- SHT output ×1ch

- Output ON resistance :  $30\Omega$  typ

#### **Specifications**

Absolute Maximum Ratings at Ta = 25°C,  $V_{SS} = VM = 0V$

| Parameter                   | Symbol              | Conditions                 | Ratings     | Unit |

|-----------------------------|---------------------|----------------------------|-------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |                            | 6           | V    |

|                             | VH max              |                            | 20          | V    |

|                             | VL max              |                            | -10         | V    |

|                             | VH-VL max           |                            | 24          | V    |

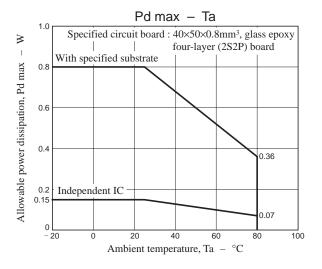

| Allowable power dissipation | Pd max              | with specified substrate * | 0.8         | W    |

| Operating temperature       | Topr                |                            | -20 to +80  | °C   |

| Storage temperature         | Tstg                |                            | -40 to +125 | °C   |

<sup>\* :</sup> Specified substrate : 40×50×0.8mm³, glass epoxy four-layer (2S2P) board

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Allowable Operating Ratings at Ta = 25°C, $V_{SS} = VM = 0V$

| Parameter               | O. made al        | Condition - |                    | Ratings |          | Unit |

|-------------------------|-------------------|-------------|--------------------|---------|----------|------|

|                         | Symbol            | Conditions  | min                | typ     | max      | Onit |

| Supply voltage          | $V_{DD}$          |             | 2.0                | 3.3     | 5.5      | V    |

|                         | VH                |             |                    | 15      | 17       | V    |

|                         | VL                |             | -8.5               | -7.5    | -4       | V    |

|                         | VH-VL             |             |                    |         | 23.5     | V    |

| CMOS input High voltage | V <sub>IN</sub> H |             | 0.8V <sub>DD</sub> |         | $V_{DD}$ | V    |

| CMOS input Low voltage  | V <sub>IN</sub> L |             | -0.1               |         | 0.4      | V    |

#### **LV5609LP**

$\textbf{Electrical Characteristics} \ at \ Ta=25^{\circ}C, \ V_{DD}=3.3V, \ V_{SS}=0V, \ VH=15V, \ VL=-7.5V, \ VM=0V, \ VM=15V, \ VM=1$

Unless otherwise specified

| Parameter              | Symbol          | Conditions                         |     | 11-3 |     |      |

|------------------------|-----------------|------------------------------------|-----|------|-----|------|

| Parameter              | Symbol          | Conditions                         | min | typ  | max | Unit |

| Static current drain   | I <sub>DD</sub> | V <sub>DD</sub> pin                |     |      | 1   | μΑ   |

|                        | IH              | VH pin                             |     |      | 10  | μΑ   |

|                        | IL              | VL pin                             |     |      | 1   | μΑ   |

| Dynamic current drain  | I <sub>DD</sub> | V <sub>DD</sub> pin See *1 and *2. |     |      | 1   | mA   |

|                        | IH              | VH pin See *1 and *2.              |     | 2.4  | 4.5 | mA   |

|                        | IL              | VL pin See *1 and *2.              |     | 3    | 5   | mA   |

| Output ON resistance   | RL              | I <sub>O</sub> = +10mA             |     | 20   | 30  | Ω    |

|                        | RM              | $I_O = \pm 10 \text{mA}$           |     | 30   | 45  | Ω    |

|                        | RH              | I <sub>O</sub> = -10mA             |     | 30   | 40  | Ω    |

|                        | RSHT            | I <sub>O</sub> = -10mA             |     | 30   | 40  | Ω    |

| Propagation delay time | TPLM            | No load                            |     |      | 200 | ns   |

|                        | TPMH            | No load                            |     |      | 200 | ns   |

|                        | TPLH            | No load                            |     |      | 200 | ns   |

|                        | TPML            | No load                            |     |      | 200 | ns   |

|                        | TPHM            | No load                            |     |      | 200 | ns   |

|                        | TPHL            | No load                            |     |      | 200 | ns   |

| Rise time              | TTLM            | VL → VM V1, V3 See *1.             |     |      | 800 | ns   |

|                        |                 | VL → VM V2, V4 See *1.             |     |      | 800 | ns   |

|                        | TTMH            | VM → VL V1, V3 See *1.             |     |      | 800 | ns   |

|                        | TTLH            | VL → VH SHT See *1.                |     |      | 200 | ns   |

| Fall time              | TTML            | VM → VL V1, V3 See *1.             |     |      | 800 | ns   |

|                        |                 | VM → VL V2, V4 See *1.             |     |      | 800 | ns   |

|                        | TTHM            | VH → VM V1, V3 See *1.             |     |      | 800 | ns   |

|                        | TTHL            | VH → VL SHT See *1.                |     |      | 200 | ns   |

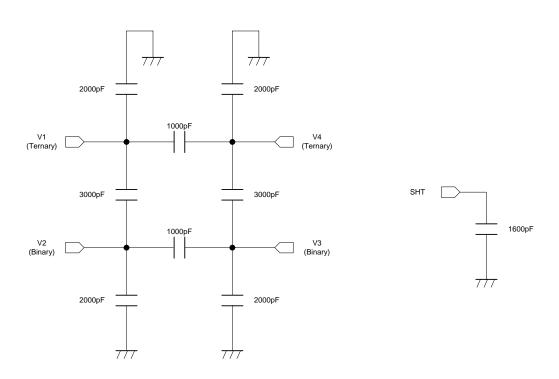

<sup>\*1 :</sup> Refer to the CCD equivalent load shown below.

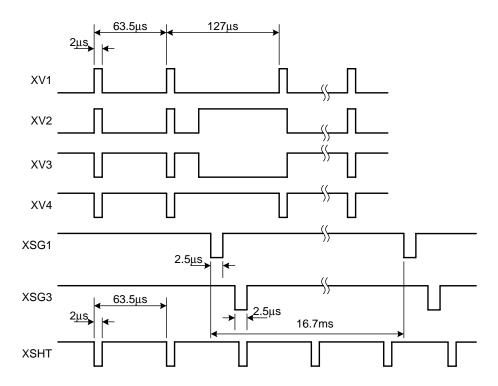

$<sup>^{\</sup>star}2$ : Refer to the timing waveform on Page 7.

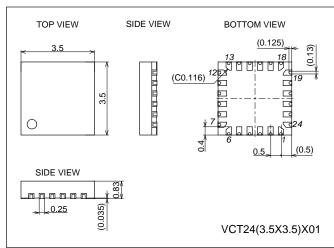

#### **Package Dimensions**

unit: mm (typ)

3322

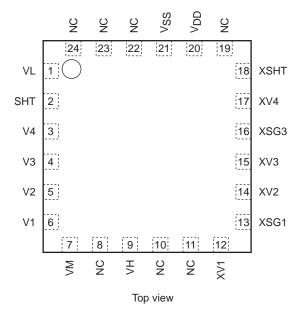

### **Pin Assignment**

#### **Pin Function**

| Pin No. | Name            | Mode                                        |  |  |  |  |

|---------|-----------------|---------------------------------------------|--|--|--|--|

| 1       | VL              | Lo power for output (-7.5V system)          |  |  |  |  |

| 2       | SHT             | Level shift output (binary VH, VL)          |  |  |  |  |

| 3       | V4              | Level shift output (binary VM, VL)          |  |  |  |  |

| 4       | V3              | Level shift output (ternary VH, VM, VL)     |  |  |  |  |

| 5       | V2              | Level shift output (binary VM, VL)          |  |  |  |  |

| 6       | V1              | Level shift output (ternary VH, VM, VL)     |  |  |  |  |

| 7       | VM              | GND for output                              |  |  |  |  |

| 8       | NC              |                                             |  |  |  |  |

| 9       | VH              | Hi power supply for output (15V system)     |  |  |  |  |

| 10      | NC              |                                             |  |  |  |  |

| 11      | NC              |                                             |  |  |  |  |

| 12      | XV1             | V1 transfer pulse input                     |  |  |  |  |

| 13      | XSG1            | V1 read pulse input                         |  |  |  |  |

| 14      | XV2             | V2 transfer pulse input                     |  |  |  |  |

| 15      | XV3             | V3 transfer pulse input                     |  |  |  |  |

| 16      | XSG3            | V3 read pulse input                         |  |  |  |  |

| 17      | XV4             | V4 transfer pulse input                     |  |  |  |  |

| 18      | XSHT            | SHT pulse input                             |  |  |  |  |

| 19      | NC              |                                             |  |  |  |  |

| 20      | $v_{DD}$        | Power supply for input buffer (3.3V system) |  |  |  |  |

| 21      | V <sub>SS</sub> | GND for input buffer                        |  |  |  |  |

| 22      | NC              |                                             |  |  |  |  |

| 23      | NC              |                                             |  |  |  |  |

| 24      | NC              |                                             |  |  |  |  |

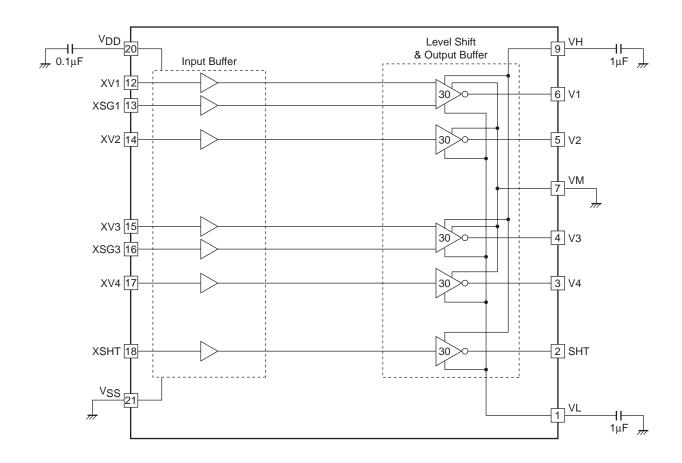

#### **Block Diagram**

#### **Logical Function Table**

|            | Inp          | out        |      |          | Output   |     |

|------------|--------------|------------|------|----------|----------|-----|

| XV1<br>XV3 | XSG1<br>XSG3 | XV2<br>XV4 | XSHT | V1<br>V3 | V2<br>V4 | SHT |

| L          | L            | Х          | Х    | VH       | Х        | Х   |

| L          | Н            | Х          | Х    | VM       | Х        | Х   |

| Н          | L            | Х          | Х    | VL       | Х        | Х   |

| Н          | Н            | Х          | Х    | VL       | Х        | Х   |

| Х          | Х            | L          | Х    | Х        | VM       | Х   |

| Х          | Х            | Н          | Х    | Х        | VL       | Х   |

| Х          | Х            | Х          | L    | Х        | Х        | VH  |

| Х          | Х            | Х          | Н    | Х        | Х        | VL  |

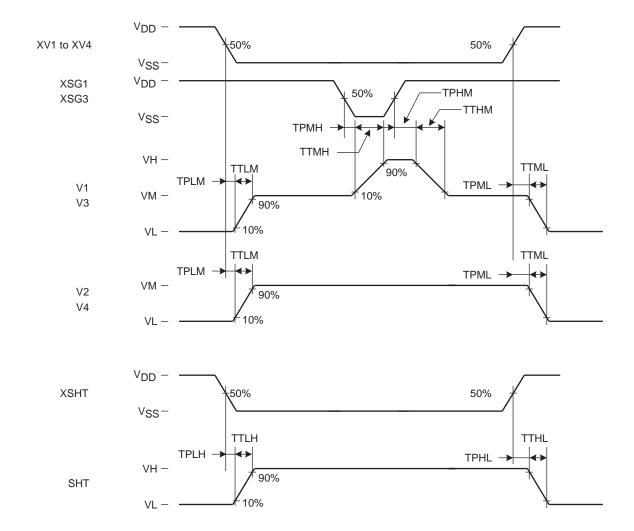

#### **Timing Chart**

#### **CCD Equivalent Load Measurement Timing Waveform**

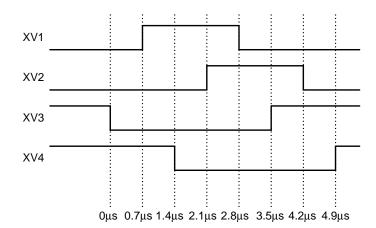

#### **Enlarged View of overlapped portion**

#### **LV5609LP**

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: