### **Multiformat SDTV Video Decoder**

**ADV7189B**

#### **FEATURES**

Multiformat video decoder supports NTSC-(J, M, 4.43), PAL-(B/D/G/H/I/M/N), SECAM

Integrates three 54 MHz, Noise Shaped Video<sup>®</sup>, 12-bit ADCs

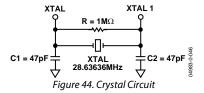

Clocked from a single 28 MHz crystal

Line-locked clock-compatible (LLC)

Adaptive-Digital-Line-Length-Tracking (ADLLT™), signal processing, and enhanced FIFO management gives mini-**TBC functionality**

5-line adaptive comb filters

Proprietary architecture for locking to weak, noisy, and unstable video sources such as VCRs and tuners

Subcarrier frequency lock and status information output

Integrated AGC with adaptive peak white mode

Macrovision® copy protection detection

CTI (chroma transient improvement)

DNR (digital noise reduction)

Multiple programmable analog input formats

CVBS (composite video)

S-Video (Y/C)

YPrPb component (VESA, MII, SMPTE, and BetaCam)

12 analog video input channels

**Automatic NTSC/PAL/SECAM identification**

Digital output formats (8-bit/10-bit/16-bit/20-bit)

ITU-R BT.656 YCrCb 4:2:2 output + HS, VS, and FIELD

0.5 V to 1.6 V analog signal input range

Differential gain: 0.4% typ

Differential phase: 0.4° typ

**Programmable video controls**

Peak white/hue/brightness/saturation/contrast

Integrated on-chip video timing generator

Free-run mode (generates stable video output with no I/P)

VBI decode support for close captioning, WSS, CGMS, EDTV,

Gemstar® 1×/2×

Power-down mode

2-wire serial MPU interface (I<sup>2</sup>C®-compatible)

3.3 V analog, 1.8 V digital core; 3.3 V IO supply

2 temperature grades: 0°C to +70°C and -40°C to +85°C

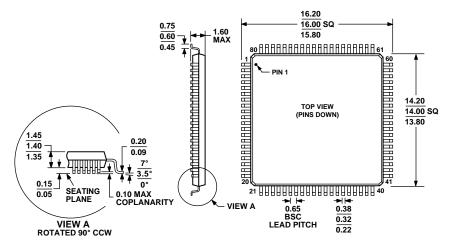

80-lead LQFP Pb-free package

#### **APPLICATIONS**

**High-end DVD recorders**

Video projectors

**HDD-based PVRs/DVDRs**

LCD TVs

**Set-top boxes**

**Professional video products**

**AVR** receivers

### **GENERAL DESCRIPTION**

The ADV7189B integrated video decoder automatically detects and converts a standard analog baseband television signal, compatible with worldwide standards NTSC, PAL, and SECAM into 4:2:2 component video data-compatible with 20-, 16-, 10-, and 8-bit CCIR601/CCIR656.

The advanced and highly flexible digital output interface enables performance video decoding and conversion in linelocked, clock-based systems. This makes the device ideally suited for a broad range of applications with diverse analog video characteristics, including tape-based sources, broadcast sources, security/surveillance cameras, and professional systems.

The 12-bit accurate A/D conversion provides professional quality video performance and is unmatched. This allows

## true 10-bit resolution in the 10-bit output mode.

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

The 12 analog input channels accept standard composite, S-Video, YPrPb video signals in an extensive number of combinations. AGC and clamp restore circuitry allow an input video signal peak-to-peak range of 0.5 V to 1.6 V. Alternatively, these can be bypassed for manual settings.

The fixed 54 MHz clocking of the ADCs and datapath for all modes allows very precise, accurate sampling and digital filtering. The line-locked clock output allows the output data rate, timing signals, and output clock signals to be synchronous, asynchronous, or line locked even with  $\pm 5\%$  line length variation. The output control signals allow glueless interface connections in almost any application. The ADV7189B modes are set up over a 2-wire, serial, bidirectional port (I<sup>2</sup>C-compatible).

The ADV7189B is fabricated in a 3.3 V CMOS process. Its monolithic CMOS construction ensures greater functionality with lower power dissipation. The ADV7189B is packaged in a small, 80-lead LQFP Pb-free package.

### **TABLE OF CONTENTS**

| Introduction4                                 | General Setup                           | 21 |

|-----------------------------------------------|-----------------------------------------|----|

| Analog Front End 4                            | SD Color Controls                       | 23 |

| Standard Definition Processor 4               | Clamp Operation                         | 25 |

| Functional Block Diagram5                     | Luma Filter                             | 26 |

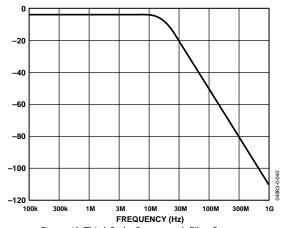

| Specifications6                               | Chroma Filter                           | 29 |

| Electrical Characteristics                    | Gain Operation                          | 30 |

| Video Specifications7                         | Chroma Transient Improvement (CTI)      | 34 |

| Timing Specifications                         | Digital Noise Reduction (DNR)           | 34 |

| Analog Specifications                         | Comb Filters                            | 35 |

| Thermal Specifications                        | AV Code Insertion and Controls          | 38 |

| Timing Diagrams9                              | Synchronization Output Signals          | 40 |

| Absolute Maximum Ratings10                    | Sync Processing                         | 48 |

| ESD Caution                                   | VBI Data Decode                         | 48 |

| Pin Configuration and Function Descriptions11 | Pixel Port Configuration                | 60 |

| Analog Front End13                            | MPU Port Description                    | 61 |

| Analog Input Muxing13                         | Register Accesses                       | 62 |

| Global Control Registers16                    | Register Programming                    | 62 |

| Power-Save Modes                              | I <sup>2</sup> C Sequencer              | 62 |

| Reset Control                                 | I <sup>2</sup> C Register Maps          | 63 |

| Global Pin Control                            | I <sup>2</sup> C Register Map Details   | 67 |

| Global Status Registers                       | I <sup>2</sup> C Interrupt Register Map | 68 |

| Identification                                | I <sup>2</sup> C Programming Examples   | 90 |

| Status 1                                      | Examples Using 28 MHz Clock             | 90 |

| SD Autodetection Result                       | Examples Using 27 MHz Clock             | 94 |

| Status 2                                      | PCB Layout Recommendations              | 97 |

| Status 3                                      | Analog Interface Inputs                 | 97 |

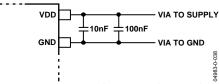

| Standard Definition Processor (SDP)20         | Power Supply Decoupling                 | 97 |

| SD Luma Path                                  | PLL                                     | 97 |

| SD Chroma Path                                | Digital Outputs (Both Data and Clocks)  | 97 |

| Sync Processing21                             | Digital Inputs                          | 98 |

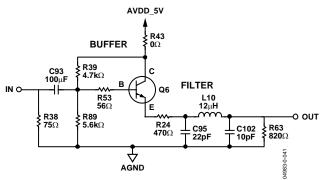

| VBI Data Recovery21                           | Antialiasing Filters                    | 98 |

| Crystal Load Capacitor Value Selection98 | Outline Dimensions                                          |

|------------------------------------------|-------------------------------------------------------------|

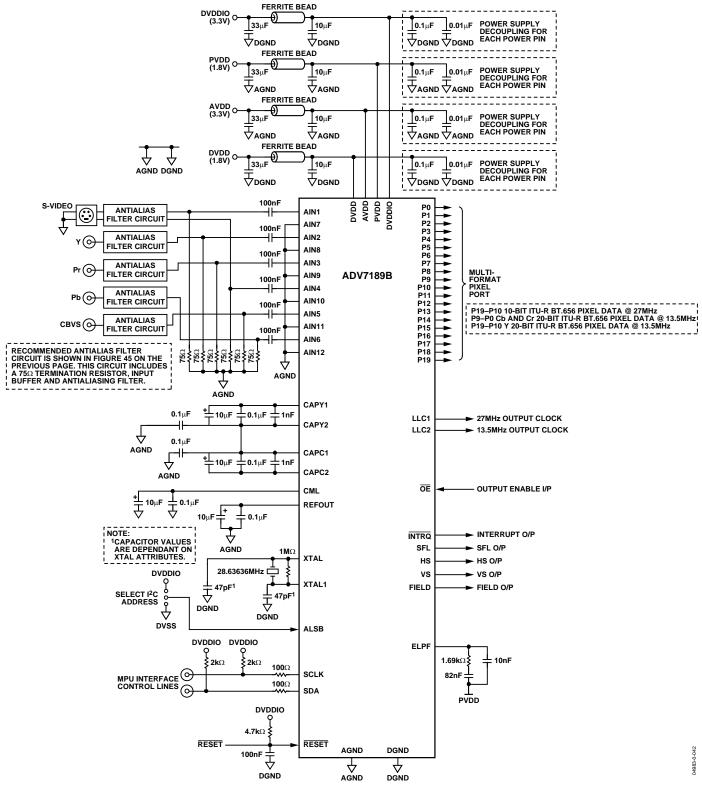

| Typical Circuit Connection99             | Ordering Guide101                                           |

| REVISION HISTORY                         |                                                             |

| 9/05—Rev. A to Rev. B                    | 7/05—Rev. 0 to Rev. A                                       |

| Changes to Table 16                      | Updated Format                                              |

| Changes to Table 27                      | Changes to Features                                         |

| Changes to Table 3 and Table 48          | Changes to Analog Specifications6                           |

| Changes to Table 59                      | Changes to Table 711                                        |

| Changes to Figure 613                    | Changes to Clamp Operation Section26                        |

| Changes to Table 814                     | Changes to Table 3029                                       |

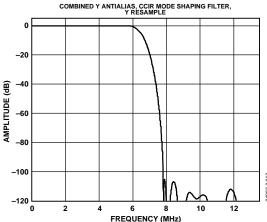

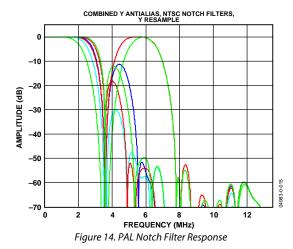

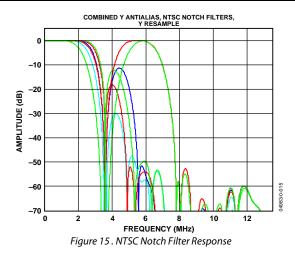

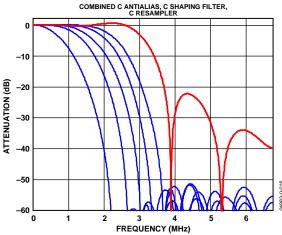

| Update Table Formatting19                | Changes to Figure 12, Figure 13, Figure 14, and Figure 1530 |

| Update Page Layout29                     | Added CSFM[2:0] C-Shaping Filter Mode, Address 0x17[7]      |

| Change to Table 3431                     | Section and Changes to Figure 1631                          |

| Update Table Formatting39                | Changes to Luma Gain Section32                              |

| Change to Table 5540                     | Changes to Table 5441                                       |

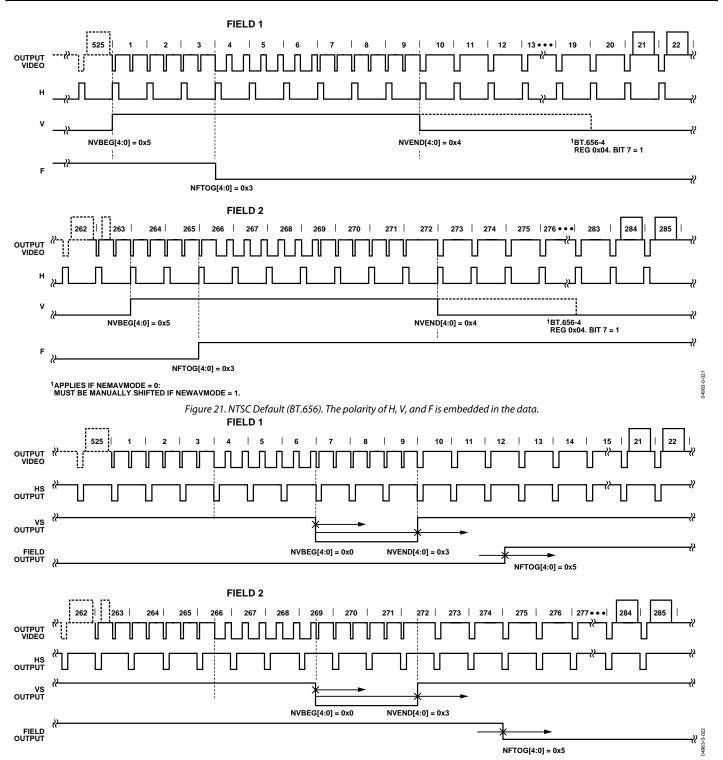

| Changes to Figure 2142                   | Changes to VSEHO VS End Horizontal Position Odd,            |

| Update Page Formatting49                 | Address 0x33[7] Section42                                   |

| Change Footnote Numbering in Table 8467  | Changes to Table 5544                                       |

| Change to Table 8568                     | Changes to Table 8469                                       |

| Change to Table 8790                     | Changes to Table 8573                                       |

| Change to Table 8891                     | Changes to Table 8691                                       |

| Change to Table Numbering94              | Changes to Table 8792                                       |

|                                          | Changes to Table 8893                                       |

|                                          | Changes to Table 8994                                       |

|                                          | Added XTAL Load Capacitor Value Section99                   |

|                                          | Inserted Figure 44; Renumbered Sequentially99               |

|                                          | Changes to Figure 46101                                     |

|                                          | Updated Outline Dimensions102                               |

|                                          | Changes to Ordering Guide102                                |

9/04—Revision 0: Initial Version

### INTRODUCTION

The ADV7189B is a high quality, single chip, multiformat video decoder that automatically detects and converts PAL, NTSC, and SECAM standards in the form of composite, S-Video, and component video into a digital ITU-R BT.656 format.

The advanced and highly flexible digital output interface enables performance video decoding and conversion in line-locked, clock-based systems. This makes the device ideally suited for a broad range of applications with diverse analog video characteristics, including tape-based sources, broadcast sources, security/ surveillance cameras, and professional systems.

### **ANALOG FRONT END**

The ADV7189B analog front end comprises three 12-bit noise shaped video ADCs that digitize the analog video signal before applying it to the standard definition processor. The analog front end employs differential channels to each ADC to ensure high performance in mixed-signal applications.

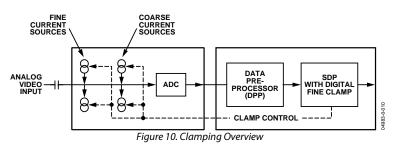

The front end also includes a 12-channel input mux that enables multiple video signals to be applied to the ADV7189B. Current and voltage clamps are positioned in front of each ADC to ensure the video signal remains within the range of the converter. Fine clamping of the video signals is performed downstream by digital fine clamping within the ADV7189B. The ADCs are configured to run in 4× oversampling mode.

#### STANDARD DEFINITION PROCESSOR

The ADV7189B is capable of decoding a large selection of baseband video signals in composite, S-Video, and component formats. The video standards supported by the ADV7189B include PAL B/D/I/G/H, PAL60, PAL M, PAL N, PAL Nc, NTSC M/J, NTSC 4.43, and SECAM B/D/G/K/L. The ADV7189B can automatically detect the video standard and process it accordingly. The ADV7189B has a 5-line, super-adaptive, 2D comb filter that gives superior chrominance and luminance separation when decoding a composite video signal. This highly adaptive filter automatically adjusts its processing mode according to video standard and signal quality with no user intervention required. Video user controls such as brightness, contrast, saturation, and hue are also available within the ADV7189B.

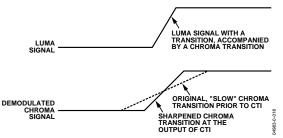

The ADV7189B implements a patented adaptive-digital-line-length-tracking (ADLLT) algorithm to track varying video line lengths from sources such as a VCR. ADLLT enables the ADV7189B to track and decode poor quality video sources such as VCRs, noisy sources from tuner outputs, VCD players, and camcorders. The ADV7189B contains a chroma transient improvement (CTI) processor that sharpens the edge rate of chroma transitions, resulting in sharper vertical transitions.

The ADV7189B can process a variety of VBI data services, such as closed captioning (CC), wide screen signaling (WSS), copy generation management system (CGMS), EDTV, Gemstar  $1\times/2\times$ , and extended data service (XDS). The ADV7189B is fully Macrovision certified; detection circuitry enables Type I, Type II, and Type III protection levels to be identified and reported to the user. The decoder is also fully robust to all Macrovision signal inputs.

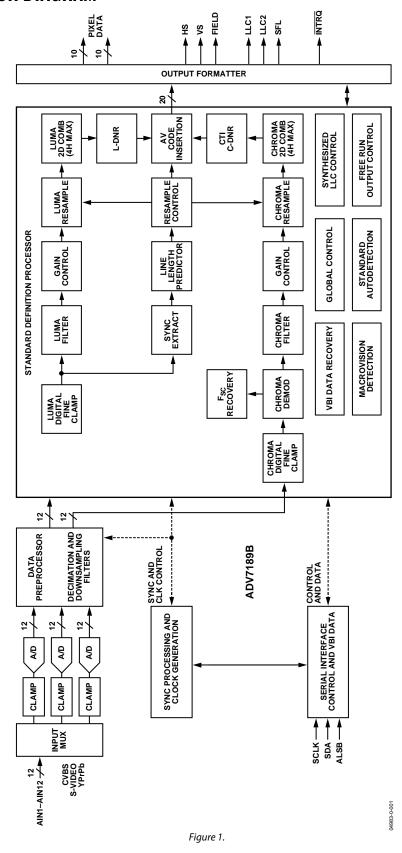

### **FUNCTIONAL BLOCK DIAGRAM**

### **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

At  $A_{VDD}$  = 3.15 V to 3.45 V,  $D_{VDD}$  = 1.65 V to 2.0 V,  $D_{VDDIO}$  = 3.0 V to 3.6 V,  $P_{VDD}$  = 1.65 V to 2.0 V, operating temperature range, unless otherwise specified.

Table 1.

| Parameter <sup>1, 2</sup>       | Symbol              | Test Conditions               | Min  | Тур       | Max      | Unit |

|---------------------------------|---------------------|-------------------------------|------|-----------|----------|------|

| STATIC PERFORMANCE              |                     |                               |      |           |          |      |

| Resolution (Each ADC)           | N                   |                               |      |           | 12       | Bits |

| Integral Nonlinearity           | INL                 | BSL at 54 MHz                 |      | -1.5/+2.5 | ±8       | LSB  |

| Differential Nonlinearity       | DNL                 | BSL at 54 MHz                 |      | -0.7/+0.7 | -0.95/+2 | LSB  |

| DIGITAL INPUTS                  |                     |                               |      |           |          |      |

| Input High Voltage              | V <sub>IH</sub>     |                               | 2    |           |          | V    |

| Input Low Voltage               | VIL                 |                               |      |           | 0.8      | V    |

| Input Current <sup>3</sup>      | I <sub>IN</sub>     |                               | -50  |           | +50      | μΑ   |

|                                 |                     | All other pins                | -10  |           | +10      | μΑ   |

| Input Capacitance               | C <sub>IN</sub>     |                               |      |           | 10       | pF   |

| DIGITAL OUTPUTS                 |                     |                               |      |           |          |      |

| Output High Voltage             | V <sub>OH</sub>     | $I_{SOURCE} = 0.4 \text{ mA}$ | 2.4  |           |          | V    |

| Output Low Voltage              | $V_{OL}$            | $I_{SINK} = 3.2 \text{ mA}$   |      |           | 0.4      | V    |

| High Impedance Leakage Current⁴ | I <sub>LEAK</sub>   |                               |      |           | 50       | μΑ   |

|                                 |                     | All other pins                |      |           | 10       | μΑ   |

| Output Capacitance              | Соит                |                               |      |           | 20       | рF   |

| POWER REQUIREMENTS <sup>5</sup> |                     |                               |      |           |          |      |

| Digital Core Power Supply       | D <sub>VDD</sub>    |                               | 1.65 | 1.8       | 2        | V    |

| Digital I/O Power Supply        | D <sub>VDDIO</sub>  |                               | 3.0  | 3.3       | 3.6      | V    |

| PLL Power Supply                | P <sub>VDD</sub>    |                               | 1.65 | 1.8       | 2.0      | V    |

| Analog Power Supply             | A <sub>VDD</sub>    |                               | 3.15 | 3.3       | 3.45     | V    |

| Digital Core Supply Current     | I <sub>DVDD</sub>   |                               |      | 82        |          | mA   |

| Digital I/O Supply Current      | I <sub>DVDDIO</sub> |                               |      | 2         |          | mA   |

| PLL Supply Current              | I <sub>PVDD</sub>   |                               |      | 10.5      |          | mA   |

| Analog Supply Current           | l <sub>AVDD</sub>   | CVBS input <sup>6</sup>       |      | 85        |          | mA   |

|                                 |                     | YPrPb input <sup>7</sup>      |      | 180       |          | mA   |

| Power-Down Current              | I <sub>PWRDN</sub>  |                               |      | 1.5       |          | mA   |

| Power-Up Time                   | t <sub>PWRUP</sub>  |                               |      | 20        |          | ms   |

$<sup>^1</sup>$  Temperature range:  $T_{MIN}$  to  $T_{MAX},$   $-40^{\circ}C$  to  $+85^{\circ}C.$  (0°C to 70°C for ADV7189BKSTZ)

<sup>&</sup>lt;sup>2</sup> The min/max specifications are guaranteed over this range.

<sup>&</sup>lt;sup>3</sup> Pin 36 and Pin 79.

$<sup>^{\</sup>rm 4}$  Pin 1, Pin 2, Pin 5 to Pin 8, Pin 12, Pin 17 to Pin 24, Pin 32 to Pin 35, Pin 73 to Pin 76, and Pin 80.

$<sup>^{\</sup>scriptscriptstyle 5}$  Guaranteed by characterization.

<sup>&</sup>lt;sup>6</sup> ADC1 powered on.

<sup>&</sup>lt;sup>7</sup> All three ADCs powered on.

### **VIDEO SPECIFICATIONS**

Guaranteed by characterization. At  $A_{\text{VDD}} = 3.15 \text{ V}$  to 3.45 V,  $D_{\text{VDD}} = 1.65 \text{ V}$  to 2.0 V,  $D_{\text{VDDIO}} = 3.0 \text{ V}$  to 3.6 V,  $P_{\text{VDD}} = 1.65 \text{ V}$  to 2.0 V; operating temperature range, unless otherwise specified.

Table 2.

| Parameter <sup>1, 2</sup>             | Symbol | Test Conditions           | Min | Тур  | Max | Unit    |

|---------------------------------------|--------|---------------------------|-----|------|-----|---------|

| NONLINEAR SPECIFICATIONS              |        |                           |     |      |     |         |

| Differential Phase                    | DP     | CVBS I/P, modulate 5-step |     | 0.4  | 0.6 | Degrees |

| Differential Gain                     | DG     | CVBS I/P, modulate 5-step |     | 0.4  | 0.6 | %       |

| Luma Nonlinearity                     | LNL    | CVBS I/P, 5-step          |     | 0.4  | 0.7 | %       |

| NOISE SPECIFICATIONS                  |        |                           |     |      |     |         |

| SNR Unweighted                        |        | Luma ramp                 | 61  | 63   |     | dB      |

|                                       |        | Luma flat field           | 63  | 65   |     | dB      |

| Analog Front End Crosstalk            |        |                           |     | 60   |     | dB      |

| LOCK TIME SPECIFICATIONS              |        |                           |     |      |     |         |

| Horizontal Lock Range                 |        |                           | -5  |      | +5  | %       |

| Vertical Lock Range                   |        |                           | 40  |      | 70  | Hz      |

| F <sub>SC</sub> Subcarrier Lock Range |        |                           |     | ±1.3 |     | Hz      |

| Color Lock In Time                    |        |                           |     | 60   |     | Lines   |

| Sync Depth Range                      |        |                           | 20  |      | 200 | %       |

| Color Burst Range                     |        |                           | 5   |      | 200 | %       |

| Vertical Lock Time                    |        |                           |     | 2    |     | Fields  |

| Autodetection Switch Speed            |        |                           |     | 100  |     | Lines   |

| CHROMA SPECIFICATIONS                 |        |                           |     |      |     |         |

| Hue Accuracy                          | HUE    |                           |     | 1    |     | Degrees |

| Color Saturation Accuracy             | CL_AC  |                           |     | 1    |     | %       |

| Color AGC Range                       |        |                           | 5   |      | 400 | %       |

| Chroma Amplitude Error                |        |                           |     | 0.4  |     | %       |

| Chroma Phase Error                    |        |                           |     | 0.3  |     | Degrees |

| Chroma Luma Intermodulation           |        |                           |     | 0.1  |     | %       |

| LUMA SPECIFICATIONS                   |        |                           |     |      |     |         |

| Luma Brightness Accuracy              |        | CVBS, 1 V I/P             |     | 1    |     | %       |

| Luma Contrast Accuracy                |        | CVBS, 1 V I/P             |     | 1    |     | %       |

$<sup>^1</sup>$  Temperature range: Tmin to Tmax, –40°C to +85°C. (0°C to 70°C for ADV7189BKSTZ).  $^2$  The min/max specifications are guaranteed over this range.

### **TIMING SPECIFICATIONS**

Guaranteed by characterization.  $A_{\rm VDD}$  = 3.15 V to 3.45 V,  $D_{\rm VDD}$  = 1.65 V to 2.0 V,  $D_{\rm VDDIO}$  = 3.0 V to 3.6 V,  $P_{\rm VDD}$  = 1.65 V to 2.0 V; operating temperature range, unless otherwise specified.

Table 3.

| Parameter <sup>1, 2</sup>     | Symbol                          | Test Conditions                                                               | Min   | Тур     | Max   | Unit   |

|-------------------------------|---------------------------------|-------------------------------------------------------------------------------|-------|---------|-------|--------|

| SYSTEM CLOCK AND CRYSTAL      |                                 |                                                                               |       |         |       |        |

| Nominal Frequency             |                                 |                                                                               |       | 28.6363 |       | MHz    |

| Frequency Stability           |                                 |                                                                               |       |         | ±50   | ppm    |

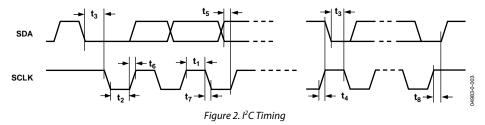

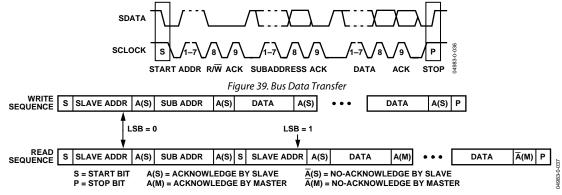

| I <sup>2</sup> C PORT         |                                 |                                                                               |       |         |       |        |

| SCLK Frequency                |                                 |                                                                               |       |         | 400   | kHz    |

| SCLK Min Pulse Width High     | t <sub>1</sub>                  |                                                                               | 0.6   |         |       | μs     |

| SCLK Min Pulse Width Low      | t <sub>2</sub>                  |                                                                               | 1.3   |         |       | μs     |

| Hold Time (Start Condition)   | t <sub>3</sub>                  |                                                                               | 0.6   |         |       | μs     |

| Setup Time (Start Condition)  | t <sub>4</sub>                  |                                                                               | 0.6   |         |       | μs     |

| SDA Setup Time                | <b>t</b> <sub>5</sub>           |                                                                               | 100   |         |       | ns     |

| SCLK and SDA Rise Time        | t <sub>6</sub>                  |                                                                               |       |         | 300   | ns     |

| SCLK and SDA Fall Time        | t <sub>7</sub>                  |                                                                               |       |         | 300   | ns     |

| Setup Time for Stop Condition | t <sub>8</sub>                  |                                                                               |       | 0.6     |       | μs     |

| RESET FEATURE                 |                                 |                                                                               |       |         |       |        |

| Reset Pulse Width             |                                 |                                                                               | 5     |         |       | ms     |

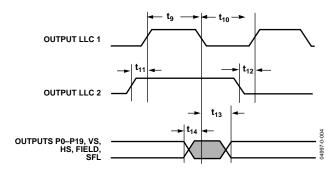

| CLOCK OUTPUTS                 |                                 |                                                                               |       |         |       |        |

| LLC1 Mark Space Ratio         | t <sub>9</sub> :t <sub>10</sub> |                                                                               | 45:55 |         | 55:45 | % duty |

|                               |                                 |                                                                               |       |         |       | cycle  |

| LLC1 Rising to LLC2 Rising    | t <sub>11</sub>                 |                                                                               |       | 0.5     |       | ns     |

| LLC1 Rising to LLC2 Falling   | t <sub>12</sub>                 |                                                                               |       | 0.5     |       | ns     |

| DATA AND CONTROL OUTPUTS      |                                 |                                                                               |       |         |       |        |

| Data Output Transitional Time | t <sub>13</sub>                 | Negative clock edge to start of valid data ( $t_{ACCESS} = t_{10} - t_{13}$ ) |       |         | 3.4   | ns     |

| Data Output Transitional Time | t <sub>14</sub>                 | End of valid data to negative clock edge ( $t_{HOLD} = t_9 + t_{14}$ )        |       |         | 2.4   | ns     |

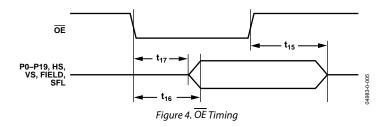

| Propagation Delay to Hi Z     | t <sub>15</sub>                 |                                                                               |       | 6       |       | ns     |

| Max Output Enable Access Time | t <sub>16</sub>                 |                                                                               |       | 7       |       | ns     |

| Min Output Enable Access Time | t <sub>17</sub>                 |                                                                               |       | 4       |       | ns     |

$<sup>^1</sup>$  Temperature range:  $T_{MIN}$  to  $T_{MAX_r}$  –40°C to +85°C. (0°C to 70°C for ADV7189BKSTZ).

### **ANALOG SPECIFICATIONS**

Guaranteed by characterization.  $A_{\rm VDD}$  = 3.15 V to 3.45 V,  $D_{\rm VDD}$  = 1.65 V to 2.0 V,  $D_{\rm VDDIO}$  = 3.0 V to 3.6 V,  $P_{\rm VDD}$  = 1.65 V to 2.0 V; operating temperature range, unless otherwise specified. Recommended Analog input video signal range 0.5 V to 1.5 V, typically 1 V p-p.

Table 4.

| Parameter <sup>1, 2</sup>  | Symbol | Test Condition      | Min | Тур  | Max | Unit |

|----------------------------|--------|---------------------|-----|------|-----|------|

| CLAMP CIRCUITRY            |        |                     |     |      |     |      |

| External Clamp Capacitor   |        |                     |     | 0.1  |     | μF   |

| Input Impedance            |        | Clamps switched off |     | 10   |     | ΜΩ   |

| Large Clamp Source Current |        |                     |     | 0.75 |     | mA   |

| Large Clamp Sink Current   |        |                     |     | 0.75 |     | mA   |

| Fine Clamp Source Current  |        |                     |     | 60   |     | μΑ   |

| Fine Clamp Sink Current    |        |                     |     | 60   |     | μΑ   |

$<sup>^1</sup>$  Temperature range:  $T_{MIN}$  to  $T_{MAX},$   $-40^{\circ}C$  to  $+85^{\circ}C.$  (0°C to 70°C for ADV7189BKSTZ).

<sup>&</sup>lt;sup>2</sup> The min/max specifications are guaranteed over this range.

<sup>&</sup>lt;sup>2</sup> The min/max specifications are guaranteed over this range.

### **THERMAL SPECIFICATIONS**

Table 5.

| Parameter <sup>1, 2</sup>                          | Symbol        | Test Conditions                     | Min | Тур  | Max | Unit |

|----------------------------------------------------|---------------|-------------------------------------|-----|------|-----|------|

| THERMAL CHARACTERISTICS                            |               |                                     |     |      |     |      |

| Junction-to-Case Thermal Resistance                | θις           | 4-layer PCB with solid ground plane |     | 7.6  |     | °C/W |

| Junction-to-Ambient Thermal Resistance (Still Air) | $\Theta_{JA}$ | 4-layer PCB with solid ground plane |     | 38.1 |     | °C/W |

$<sup>^1</sup>$  Temperature range:  $T_{MIN}$  to  $T_{MAX}$ ,  $-40^{\circ}C$  to  $+85^{\circ}C$ . (0°C to  $70^{\circ}C$  for ADV7189BKSTZ)  $^2$  The min/max specifications are guaranteed over this range.

### **TIMING DIAGRAMS**

Figure 3. Pixel Port and Control Output Timing

### **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Table 0.                                             |                                          |

|------------------------------------------------------|------------------------------------------|

| Parameter                                            | Rating                                   |

| A <sub>VDD</sub> to GND                              | 4 V                                      |

| A <sub>VDD</sub> to AGND                             | 4 V                                      |

| D <sub>VDD</sub> to DGND                             | 2.2 V                                    |

| P <sub>VDD</sub> to AGND                             | 2.2 V                                    |

| D <sub>VDDIO</sub> to DGND                           | 4 V                                      |

| D <sub>VDDIO</sub> to AVDD                           | -0.3 V to +0.3 V                         |

| P <sub>VDD</sub> to D <sub>VDD</sub>                 | -0.3 V to +0.3 V                         |

| D <sub>VDDIO</sub> – P <sub>VDD</sub>                | −0.3 V to +2 V                           |

| Dvddio - Dvdd                                        | −0.3 V to +2 V                           |

| $A_{VDD} - P_{VDD}$                                  | −0.3 V to +2 V                           |

| $A_{VDD} - D_{VDD}$                                  | −0.3 V to +2 V                           |

| Digital Inputs Voltage to DGND                       | -0.3 V to D <sub>VDDIO</sub> + 0.3 V     |

| Digital Output Voltage to DGND                       | -0.3 V to D <sub>VDDIO</sub> + 0.3 V     |

| Analog Inputs to AGND                                | AGND – 0.3 V to A <sub>VDD</sub> + 0.3 V |

| Maximum Junction Temperature<br>(T <sub>J</sub> Max) | 150°C                                    |

| Storage Temperature Range                            | _65°C to +150°C                          |

| Infrared Reflow Soldering (20 sec)                   | 260°C                                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

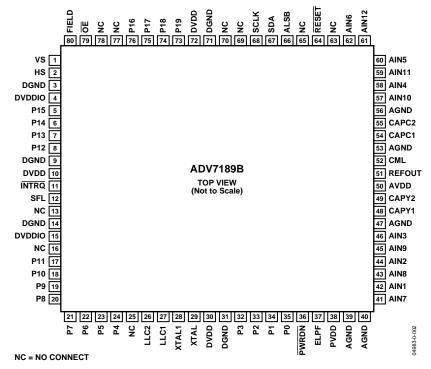

Figure 5. 80-Lead LQFP Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin No.                                              | Mnemonic     | Type | Function                                                                                                                                                                                                                        |

|------------------------------------------------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 9, 14, 31, 71                                     | DGND         | G    | Digital Ground.                                                                                                                                                                                                                 |

| 39, 40, 47, 53,<br>56                                | AGND         | G    | Analog Ground.                                                                                                                                                                                                                  |

| 4, 15                                                | DVDDIO       | Р    | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                                                             |

| 10, 30, 72                                           | DVDD         | Р    | Digital Core Supply Voltage (1.8 V).                                                                                                                                                                                            |

| 50                                                   | AVDD         | Р    | Analog Supply Voltage (3.3 V).                                                                                                                                                                                                  |

| 38                                                   | PVDD         | Р    | PLL Supply Voltage (1.8 V).                                                                                                                                                                                                     |

| 42, 44, 46, 58,<br>60, 62, 41, 43,<br>45, 57, 59, 61 | AIN1toAIN12  | 1    | Analog Video Input Channels.                                                                                                                                                                                                    |

| 11                                                   | ĪNTRQ        | 0    | Interrupt Request Output. Interrupt occurs when certain signals are detected on the input video. See the interrupt register map in Table 86.                                                                                    |

| 13, 16, 25, 63,<br>65, 69, 70, 77,<br>78             | NC           |      | No Connect Pins.                                                                                                                                                                                                                |

| 35 to 32, 24 to<br>17, 8 to 5,<br>76 to 73           | P0-P19       | 0    | Video Pixel Output Port.                                                                                                                                                                                                        |

| 2                                                    | HS           | 0    | Horizontal Synchronization Output Signal.                                                                                                                                                                                       |

| 1                                                    | VS           | 0    | Vertical Synchronization Output Signal.                                                                                                                                                                                         |

| 80                                                   | FIELD        | 0    | Field Synchronization Output Signal.                                                                                                                                                                                            |

| 67                                                   | SDA          | I/O  | I <sup>2</sup> C Port Serial Data Input/Output Pin.                                                                                                                                                                             |

| 68                                                   | SCLK         | 1    | I <sup>2</sup> C Port Serial Clock Input (Max Clock Rate of 400 kHz).                                                                                                                                                           |

| 66                                                   | ALSB         | 1    | This pin selects the I <sup>2</sup> C address for the ADV7189B. ALSB set to a Logic 0 sets the address for a write as 0x40; for ALSB set to a logic high, the address selected is 0x42.                                         |

| 64                                                   | RESET        | 1    | System Reset Input, Active Low. A minimum low reset pulse width of 5 ms is required to reset the ADV7189B circuitry.                                                                                                            |

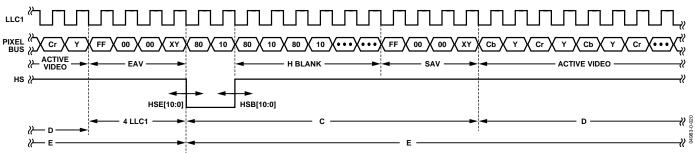

| 27                                                   | LLC1         | 0    | This is a line-locked output clock for the pixel data output by the ADV7189B. Nominally 27 MHz, but varies up or down according to video line length.                                                                           |

| 26                                                   | LLC2         | 0    | This is a divide-by-2 version of the LLC1 output clock for the pixel data output by the ADV7189B. Nominally 13.5 MHz, but varies up or down according to video line length.                                                     |

| 29                                                   | XTAL         | I    | This is the input pin for the 28.6363 MHz crystal, or can be overdriven by an external 3.3 V, 27 MHz clock oscillator source. In crystal mode, the crystal must be a fundamental crystal.                                       |

| 28                                                   | XTAL1        | 0    | This pin should be connected to the 28.6363 MHz crystal or left as a no connect if an external 3.3 V, 27 MHz clock oscillator source is used to clock the ADV7189B. In crystal mode, the crystal must be a fundamental crystal. |

| 36                                                   | PWRDN        | ı    | A logic low on this pin places the ADV7189B in a power-down mode. Refer to Power Management Register in the I2C Register Maps section for more options on power-down modes for the ADV7189B.                                    |

| 79                                                   | ŌĒ           | I    | When set to a logic low, $\overline{OE}$ enables the pixel output bus, P19 toP0 of the ADV7189B. A logic high on the $\overline{OE}$ pin places Pins P19 to P0, HS, VS, SFL into a high impedance state.                        |

| 37                                                   | ELPF         | 1    | The recommended external loop filter must be connected to this ELPF pin, as shown in Figure 46.                                                                                                                                 |

| 12                                                   | SFL          | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices, Inc. digital video encoder.                         |

| 51                                                   | REFOUT       | 0    | Internal Voltage Reference Output. Refer to Figure 46 for a recommended capacitor network for this pin.                                                                                                                         |

| 52                                                   | CML          | 0    | The CML pin is a common-mode level for the internal ADCs. Refer to Figure 46 for a recommended capacitor network for this pin.                                                                                                  |

| 48, 49                                               | CAPY1, CAPY2 | 1    | ADC's Capacitor Network. Refer to Figure 46 for a recommended capacitor network for this pin.                                                                                                                                   |

| 54, 55                                               | CAPC1, CAPC2 | 1    | ADC's Capacitor Network. Refer to Figure 46 for a recommended capacitor network for this pin.                                                                                                                                   |

### ANALOG FRONT END

### **ANALOG INPUT MUXING**

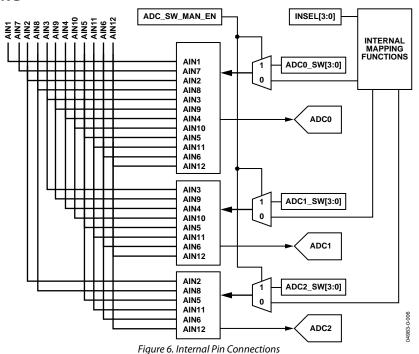

The ADV7189B has an integrated analog muxing section that allows more than one source of video signal to be connected to the decoder. Figure 6 outlines the overall structure of the input muxing provided in the ADV7189B.

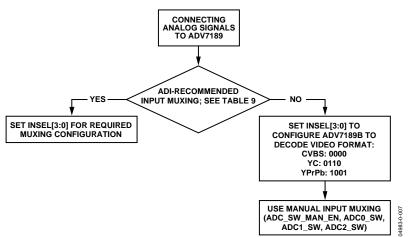

As can be seen in Figure 6, there are two different ways in which the analog input muxes can be controlled:

- Control via functional registers (INSEL). Using INSEL[3:0] simplifies the setup of the muxes, and minimizes crosstalk between channels by pre-assigning the input channels.

This is referred to as ADI recommended input muxing.

- Control via an I<sup>2</sup>C manual override (ADC\_sw\_man\_en, ADC0\_sw, ADC1\_sw, ADC2\_sw). This is provided for applications with special requirements, for example, number/combinations of signals that would not be served by the pre-assigned input connections. This is referred to as manual input muxing.

Refer to Figure 7 for an overview of the two methods of controlling the ADV7189B's input muxing.

### **ADI Recommended Input Muxing**

A maximum of 12 CVBS inputs can be connected and decoded by the ADV7189B. As seen in Figure 5, this means the sources have to be connected to adjacent pins on the IC. This calls for a careful design of the PCB layout, for example, ground shielding between all signals routed through tracks that are physically close together.

### INSEL[3:0] Input Selection, Address 0x00[3:0]

The INSEL bits allow the user to select an input channel as well as the input format. Depending on the PCB connections, only a subset of the INSEL modes are valid. The INSEL[3:0] does not only switch the analog input muxing, it also configures the standard definition processor core to process CVBS (Comp), S-Video (Y/C), or component (YPbPr) format.

Figure 7. Input Muxing Overview

Table 8. Input Channel Switching Using INSEL[3:0]

|            | Description            |              |  |  |  |

|------------|------------------------|--------------|--|--|--|

| INSEL[3:0] | Analog Input Pins      | Video Format |  |  |  |

| 0000       | CVBS1 = AIN1 (default) | Composite    |  |  |  |

| 0001       | CVBS2 = AIN2           | Composite    |  |  |  |

| 0010       | CVBS3 = AIN3           | Composite    |  |  |  |

| 0011       | CVBS4 = AIN4           | Composite    |  |  |  |

| 0100       | CVBS5 = AIN5           | Composite    |  |  |  |

| 0101       | CVBS6 = AIN6           | Composite    |  |  |  |

| 0110       | Y1 = AIN1              | YC           |  |  |  |

|            | C1 = AIN4              | YC           |  |  |  |

| 0111       | Y2 = AIN2              | YC           |  |  |  |

|            | C2 = AIN5              | YC           |  |  |  |

| 1000       | Y3 = AIN3              | YC           |  |  |  |

|            | C3 = AIN6              | YC           |  |  |  |

| 1001       | Y1 = AIN1              | YPrPb        |  |  |  |

|            | PB1 = AIN4             | YPrPb        |  |  |  |

|            | PR1 = AIN5             | YPrPb        |  |  |  |

| 1010       | Y2 = AIN2              | YPrPb        |  |  |  |

|            | PB2 = AIN3             | YPrPb        |  |  |  |

|            | PR2 = AIN6             | YPrPb        |  |  |  |

| 1011       | CVBS7 = AIN7           | Composite    |  |  |  |

| 1100       | CVBS8 = AIN8           | Composite    |  |  |  |

| 1101       | CVBS9 = AIN9           | Composite    |  |  |  |

| 1110       | CVBS10 = AIN10         | Composite    |  |  |  |

| 1111       | CVBS11 = AIN11         | Composite    |  |  |  |

**Table 9. Input Channel Assignments**

|                  | I          | 8             |                                                 |           |  |  |  |

|------------------|------------|---------------|-------------------------------------------------|-----------|--|--|--|

| Input<br>Channel | Pin<br>No. |               | ADI Recommended Input Muxing Control INSEL[3:0] |           |  |  |  |

| AIN7             | 41         | CVBS7         |                                                 |           |  |  |  |

| AIN1             | 42         | CVBS1         | YC1-Y                                           | YPrPb1-Y  |  |  |  |

| AIN8             | 43         | CVBS8         |                                                 |           |  |  |  |

| AIN2             | 44         | CVBS2         | YC2-Y                                           | YPrPb2-Y  |  |  |  |

| AIN9             | 45         | CVBS9         |                                                 |           |  |  |  |

| AIN3             | 46         | CVBS3         | YC3-Y                                           | YPrPb2-Pb |  |  |  |

| AIN10            | 57         | CVBS10        |                                                 |           |  |  |  |

| AIN4             | 58         | CVBS4         | YC1-C                                           | YPrPb1-Pb |  |  |  |

| AIN11            | 59         | CVBS11        |                                                 |           |  |  |  |

| AIN5             | 60         | CVBS5         | YC2-C                                           | YPrPb1-Pr |  |  |  |

| AIN12            | 61         | Not Available |                                                 |           |  |  |  |

| AIN6             | 62         | CVBS6         | YC3-C                                           | YPrPb2-Pr |  |  |  |

ADI-recommended input muxing is designed to minimize crosstalk between signal channels and to obtain the highest level of signal integrity. Table 9 summarizes how the PCB layout should connect analog video signals to the ADV7189B.

It is strongly recommended to connect any unused analog input pins to AGND to act as a shield.

Inputs AIN7 to AIN11 should be connected to AGND when only six input channels are used. This improves the quality of the sampling due to better isolation between channels.

AIN12 is not under the control of INSEL[3:0]. It can only be routed to ADC0/ADC1/ADC2 by manual muxing. See Table 10 for further details.

### **Manual Input Muxing**

By accessing a set of manual override muxing registers, the analog input muxes of the ADV7189B can be controlled directly. This is referred to as manual input muxing.

Manual input muxing overrides other input muxing control bits, for example, INSEL. The manual muxing is activated by setting the ADC\_SW\_MAN\_EN bit. It only affects the analog switches in front of the ADCs.

This means if the settings of INSEL and the manual input muxing registers (ADC0/1/2\_sw) contradict each other, the ADC0/ADC1/ADC2\_sw settings apply and INSEL is ignored.

Manual input muxing controls only the analog input muxes. INSEL[3:0] still has to be set so the follow-on blocks process the video data in the correct format.

This means INSEL must be used to tell the ADV7189B whether the input signal is of component, YC, or CVBS format.

Restrictions in the channel routing are imposed by the analog signal routing inside the IC; every input pin cannot be routed to each ADC. Refer to Figure 6 for an overview on the routing capabilities inside the chip. The three mux sections can be controlled by the reserved control signal buses ADC0/ADC1/ADC2\_sw[3:0]. Table 10 explains the control words used.

## SETADC\_sw\_man\_en, Manual Input Muxing Enable, Address C4[7]

ADC0\_sw[3:0], ADC0 Mux Configuration, Address 0xC3[3:0] ADC1\_sw[3:0], ADC1 Mux Configuration, Address 0xC3[7:4] ADC2\_sw[3:0], ADC2 Mux Configuration, Address 0xC4[3:0]

Table 10. Manual Mux Settings for All ADCs (SETADC\_sw\_man\_en = 1)

| ADC0_sw[3:0] | ADC0 Connected To: | ADC1_sw[3:0] | ADC1 Connected To: | ADC2_sw[3:0] | ADC2 Connected To: |

|--------------|--------------------|--------------|--------------------|--------------|--------------------|

| 0000         | No Connection      | 0000         | No Connection      | 0000         | No Connection      |

| 0001         | AIN1               | 0001         | No Connection      | 0001         | No Connection      |

| 0010         | AIN2               | 0010         | No Connection      | 0010         | AIN2               |

| 0011         | AIN3               | 0011         | AIN3               | 0011         | No Connection      |

| 0100         | AIN4               | 0100         | AIN4               | 0100         | No Connection      |

| 0101         | AIN5               | 0101         | AIN5               | 0101         | AIN5               |

| 0110         | AIN6               | 0110         | AIN6               | 0110         | AIN6               |

| 0111         | No Connection      | 0111         | No Connection      | 0111         | No Connection      |

| 1000         | No Connection      | 1000         | No Connection      | 1000         | No Connection      |

| 1001         | AIN7               | 1001         | No Connection      | 1001         | No Connection      |

| 1010         | AIN8               | 1010         | No Connection      | 1010         | AIN8               |

| 1011         | AIN9               | 1011         | AIN9               | 1011         | No Connection      |

| 1100         | AIN10              | 1100         | AIN10              | 1100         | No Connection      |

| 1101         | AIN11              | 1101         | AIN11              | 1101         | AIN11              |

| 1110         | AIN12              | 1110         | AIN12              | 1110         | AIN12              |

| 1111         | No Connection      | 1111         | No Connection      | 1111         | No Connection      |

### **GLOBAL CONTROL REGISTERS**

Register control bits listed in this section affect the whole chip.

#### **POWER-SAVE MODES**

#### Power-Down

#### PDBP, Address 0x0F[2]

The digital core of the ADV7189B can be shut down by using a pin  $(\overline{PWRDN})$  and a bit  $(\overline{PWRDN})$ , see below). The PDBP controls which of the two has the higher priority. The default is to give the pin  $(\overline{PWRDN})$  priority. This allows the user to have the ADV7189B powered down by default.

When  $\underline{PDBD}$  is 0 (default), the digital core power is controlled by the  $\underline{PWRDN}$  pin (the bit is disregarded).

When PDBD is 1, the bit has priority (the pin is disregarded).

### PWRDN, Address 0x0F[5]

Setting the PWRDN bit switches the ADV7189B into a chipwide power-down mode. The power down stops the clock from entering the digital section of the chip, thereby freezing its operation. No I<sup>2</sup>C bits are lost during power down. The PWRDN bit also affects the analog blocks and switches them into low current modes. The I<sup>2</sup>C interface itself is unaffected, and remains operational in power-down mode.

The ADV7189B leaves the power-down state if the PWRDN bit is set to 0 (via  $I^2C$ ), or if the overall part is reset using the RESET pin.

Note: PDBP must be set to 1 for the PWRDN bit to power down the ADV7189B.

When PWRDN is 0 (default), the chip is operational.

When PWRDN is 1, the ADV7189B is in chip-wide power down.

### **ADC Power-Down Control**

The ADV7189B contains three 12-bit ADCs (ADC 0, ADC 1, and ADC 2). If required, it is possible to power down each ADC individually.

The ADCs should be powered down when in:

- CVBS mode. ADC 1 and ADC 2 should be powered down to save on power consumption.

- S-Video mode. ADC 2 should be powered down to save on power consumption.

#### PWRDN\_ADC\_0, Address 0x3A[3]

When PWRDN\_ADC\_0 is 0 (default), the ADC is in normal operation.

When PWRDN\_ADC\_0 is 1, ADC 0 is powered down.

### PWRDN\_ADC\_1, Address 0x3A[2]

When PWRDN\_ADC\_1 is 0 (default), the ADC is in normal operation.

When PWRDN\_ADC\_1 is 1, ADC 1 is powered down.

### PWRDN\_ADC\_2, Address 0x3A[1]

When PWRDN\_ADC\_2 is 0 (default), the ADC is in normal operation.

When PWRDN\_ADC\_2 is 1, ADC 2 is powered down.

#### RESET CONTROL

#### Chip Reset (RES), Address 0x0F[7]

Setting this bit, equivalent to controlling the RESET pin on the ADV7189B, issues a full chip reset. All I<sup>2</sup>C registers get reset to their default values. Note: Some register bits do not have a reset value specified. They keep their last written value. These bits are marked as having a reset value of x in the register table. After the reset sequence, the part immediately starts to acquire the incoming video signal.

After setting the RES bit, or initiating a reset via the pin, the part returns to the default mode of operation with respect to its primary mode of operation. All I<sup>2</sup>C bits are loaded with their default values, making this bit self-clearing.

Executing a software reset takes approximately 2 ms. However, it is recommended to wait 5 ms before any further I<sup>2</sup>C writes are performed.

The I<sup>2</sup>C master controller receives a no-acknowledge condition on the ninth clock cycle when chip reset is implemented. See the MPU Port Description section for a full description.

When RES is 0 (default), operation is normal.

When RES is 1, the reset sequence starts.

### **GLOBAL PIN CONTROL**

### **Three-State Output Drivers**

### TOD, Address 0x03[6]

This bit allows the user to three-state the output drivers of the ADV7189B.

Upon setting the TOD bit, the P[19:0], HS, VS, FIELD, and SFL pins are three-stated.

The timing pins (HS/VS/FIELD) can be forced active via the TIM\_OE bit. For more information on three-state control, refer to the Three-State LLC Drivers and the Timing Signals Output Enable sections.

Individual drive strength controls are provided via the DR\_STR\_XX bits.

The ADV7189B supports three-stating via a dedicated pin. When set high, the  $\overline{OE}$  pin three-states the output drivers for P[19:0], HS, VS, FIELD, and SFL. The output drivers are three-stated if the TOD bit or the  $\overline{OE}$  pin is set high.

When TOD is 0 (default), the output drivers are enabled.

When TOD is 1, the output drivers are three-stated.

#### **Three-State LLC Drivers**

### TRI\_LLC, Address 0x1D[7]

This bit allows the output drivers for the LLC1 pin and LLC2 pin of the ADV7189B to be three-stated. For more information on three-state control, refer to the Three-State Output Drivers and the Timing Signals Output Enable sections.

Individual drive strength controls are provided via the DR STR XX bits.

When TRI\_LLC is 0 (default), the LLC pin drivers work according to the DR\_STR\_C[1:0] setting (pin enabled).

When TRI\_LLC is 1, the LLC pin drivers are three-stated.

### **Timing Signals Output Enable**

### TIM\_OE, Address 0x04[3]

The TIM\_OE bit should be regarded as an addition to the TOD bit. Setting it high forces the output drivers for HS, VS, and FIELD into the active (that is, driving) state even if the TOD bit is set. If set to low, the HS, VS, and FIELD pins are three-stated dependent on the TOD bit. This functionality is useful if the decoder is to be used as a timing generator only. This may be the case if only the timing signals are to be extracted from an incoming signal, or if the part is in freerun mode where a separate chip can output, for instance, a company logo.

For more information on three-state control, refer to the Three-State Output Drivers and the Three-State LLC Drivers sections.

Individual drive strength controls are provided via the DR\_STR\_XX bits.

When TIM\_OE is 0 (default), HS, VS, and FIELD are three-stated according to the TOD bit.

When TIM\_OE is 1, HS, VS, and FIELD are forced active all the time.

### **Drive Strength Selection (Data)**

### DR\_STR[1:0] Address 0xF4[5:4]

For EMC and crosstalk reasons, it can be desirable to strengthen or weaken the drive strength of the output drivers. The DR\_STR[1:0] bits affect the P[19:0] output drivers.

For more information on three-state control, refer to the Drive Strength Selection (Clock) and the Drive Strength Selection (Sync) sections.

Table 11. DR\_STR\_C Function

| DR_STR_C[1:0] | Description                        |

|---------------|------------------------------------|

| 00            | Low drive strength (1 $\times$ ).  |

| 01 (default)  | Medium low drive strength (2×).    |

| 10            | Medium high drive strength (3×).   |

| 11            | High drive strength ( $4\times$ ). |

### **Drive Strength Selection (Clock)**

### DR\_STR\_C[1:0] Address 0xF4[3:2]

The DR\_STR\_C[1:0] bits can be used to select the strength of the clock signal output driver (LLC pin). For more information, refer to the Drive Strength Selection (Sync) and the Drive Strength Selection (Data) sections.

Table 12. DR\_STR\_C Function

| DR_STR_C[1:0] | Description                             |

|---------------|-----------------------------------------|

| 00            | Low drive strength (1×).                |

| 01 (default)  | Medium low drive strength $(2\times)$ . |

| 10            | Medium high drive strength (3×).        |

| 11            | High drive strength (4×).               |

### Drive Strength Selection (Sync)

### DR\_STR\_S[1:0] Address 0xF4[1:0]

The DR\_STR\_S[1:0] bits allow the user to select the strength of the synchronization signals with which HS, VS, and F are driven. For more information, refer to the Drive Strength Selection (Clock) and the Drive Strength Selection (Data) sections.

Table 13. DR\_STR\_S Function

| DR_STR_S[1:0] | Description                      |

|---------------|----------------------------------|

| 00            | Low drive strength (1×).         |

| 01 (default)  | Medium low drive strength (2×).  |

| 10            | Medium high drive strength (3×). |

| 11            | High drive strength (4×).        |

## Enable Subcarrier Frequency Lock Pin EN\_SFL\_PIN Address 0x04[1]

The EN\_SFL\_PIN bit enables the output of subcarrier lock information (also known as GenLock) from the ADV7189B core to an encoder in a decoder-encoder back-to-back arrangement.

When EN\_SFL\_PIN is 0 (default), the subcarrier frequency lock output is disabled.

When EN\_SFL\_PIN is 1, the subcarrier frequency lock information is presented on the SFL pin.

### **Polarity LLC Pin**

### PCLK Address 0x37[0]

The polarity of the clock that leaves the ADV7189B via the LLC1 and LLC2 pins can be inverted using the PCLK bit.

Changing the polarity of the LLC clock output can be necessary to meet the setup-and-hold time expectations of follow-on chips.

Note: This bit also inverts the polarity of the LLC2 clock.

When PCLK is 0, the LLC output polarity is inverted.

When PCLK is 1 (default), the LLC output polarity is normal (as per the Timing Diagrams).

### **GLOBAL STATUS REGISTERS**

Four registers provide summary information about the video decoder. The IDENT register allows the user to identify the revision code of the ADV7189B. The other three registers contain status bits from the ADV7189B.

### **IDENTIFICATION**

### IDENT[7:0] Address 0x11[7:0]

This register provides identification of the revision of the ADV7189B.

An identification value of 0x11 indicates the ADV7189, released silicon.

An identification value of 0x13 indicates the ADV7189B silicon.

### **STATUS 1**

### STATUS\_1[7:0] Address 0x10[7:0]

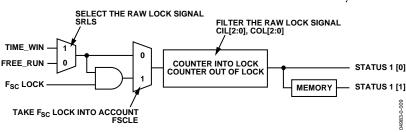

This read-only register provides information about the internal status of the ADV7189B. These bits are used to set VS free run (coast) frequency. See the VS\_Coast[1:0], Address 0xF9[3:2]section and COL[2:0] Count Out-of-Lock, Address 0x51[5:3] for information on the timing.

Depending on the setting of the FSCLE bit, the Status[0] and Status[1] are based solely on horizontal timing information or on the horizontal timing and lock status of the color subcarrier. See the FSCLE FSC Lock Enable, Address 0x51[7] section.

### **SD AUTODETECTION RESULT**

### AD\_RESULT[2:0] Address 0x10[6:4]

The AD\_RESULT[2:0] bits report back on the findings from the autodetection block. For more information on enabling the autodetection block, see the General Setup section. For information on configuring it, see the Autodetection of SD Modes section.

Table 14. AD\_RESULT Function

| AD_RESULT[2:0] | Description       |

|----------------|-------------------|

| 000            | NTSM-MJ           |

| 001            | NTSC-443          |

| 010            | PAL-M             |

| 011            | PAL-60            |

| 100            | PAL-BGHID         |

| 101            | SECAM             |

| 110            | PAL-Combination N |

| 111            | SECAM 525         |

**Table 15. STATUS 1 Function**

| STATUS 1[7:0] | Bit Name    | Description                                   |

|---------------|-------------|-----------------------------------------------|

| 0             | IN_LOCK     | In lock (right now).                          |

| 1             | LOST_LOCK   | Lost lock (since last read of this register). |

| 2             | FSC_LOCK    | F <sub>SC</sub> locked (right now).           |

| 3             | FOLLOW_PW   | AGC follows peak white algorithm.             |

| 4             | AD_RESULT.0 | Result of autodetection.                      |

| 5             | AD_RESULT.1 | Result of autodetection.                      |

| 6             | AD_RESULT.2 | Result of autodetection.                      |

| 7             | COL_KILL    | Color kill active.                            |

### **STATUS 2**

STATUS\_2[7:0], Address 0x12[7:0] Table 16. STATUS 2 Function

| STATUS 2[7:0] | Bit Name   | Description                                                                          |

|---------------|------------|--------------------------------------------------------------------------------------|

| 0             | MVCS DET   | Detected Macrovision color striping.                                                 |

| 1             | MVCS T3    | Macrovision color striping protection. Conforms to Type 3 if high, to Type 2 if low. |

| 2             | MV_PS DET  | Detected Macrovision pseudo sync pulses.                                             |

| 3             | MV_AGC DET | Detected Macrovision AGC pulses.                                                     |

| 4             | LL_NSTD    | Line length is nonstandard.                                                          |

| 5             | FSC_NSTD   | F <sub>sc</sub> frequency is nonstandard.                                            |

| 6             | Reserved   |                                                                                      |

| 7             | Reserved   |                                                                                      |

#### **STATUS 3**

STATUS\_3[7:0], Address 0x13[7:0] Table 17. STATUS 3 Function

| STATUS 3[7:0] | Bit Name     | Description                                                                                        |

|---------------|--------------|----------------------------------------------------------------------------------------------------|

| 0             | INST_HLOCK   | Horizontal lock indicator (instantaneous).                                                         |

| 1             | GEMD         | Gemstar Detect.                                                                                    |

| 2             | SD_OP_50HZ   | Flags whether 50 Hz or<br>60 Hz is present at output.                                              |

| 3             |              | Reserved for future use.                                                                           |

| 4             | FREE_RUN_ACT | ADV7189B outputs a blue screen (see the DEF_VAL_EN Default Value Enable, Address 0x0C[0] section). |

| 5             | STD_FLD_LEN  | Field length is correct for<br>currently selected video<br>standard.                               |

| 6             | INTERLACED   | Interlaced video detected (field sequence found).                                                  |

| 7             | PAL_SW_LOCK  | Reliable sequence of swinging bursts detected.                                                     |

### STANDARD DEFINITION PROCESSOR (SDP)

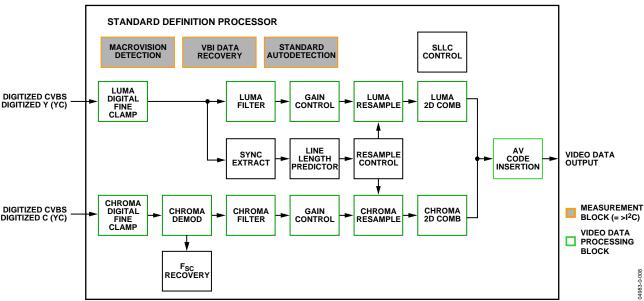

Figure 8. Block Diagram of the Standard Definition Processor

A block diagram of the ADV7189B's standard definition processor (SDP) is shown in Figure 8.

The ADV7189B block can handle standard definition video in CVBS, YC, and YPrPb formats. It can be divided into a luminance and chrominance path. If the input video is of a composite type (CVBS), both processing paths are fed with the CVBS input.

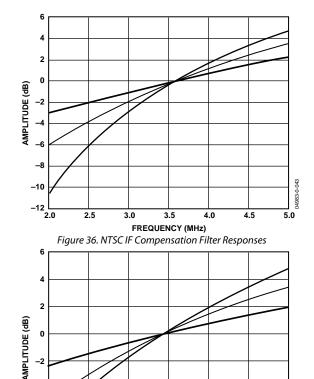

#### **SD LUMA PATH**

The input signal is processed by the following blocks:

- Digital Fine Clamp. This block uses a high precision algorithm to clamp the video signal.

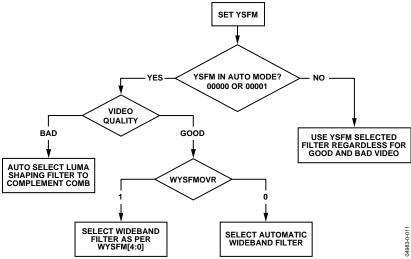

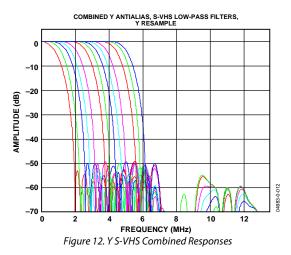

- Luma Filter Block. This block contains a luma decimation filter (YAA) with a fixed response, and some shaping filters (YSH) that have selectable responses.

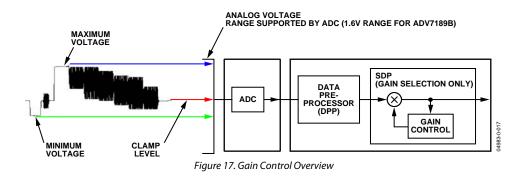

- Luma Gain Control. The automatic gain control (AGC)

can operate on a variety of different modes, including gain

based on the depth of the horizontal sync pulse, peak white

mode, and fixed manual gain.

- Luma Resample. To correct for line-length errors and dynamic line-length changes, the data is digitally resampled.

- Luma 2D Comb. The two-dimensional comb filter provides YC separation.

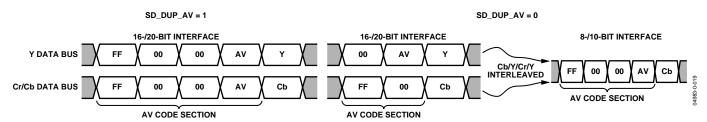

- AV Code Insertion. At this point, the decoded luma (Y) signal is merged with the retrieved chroma values. AV codes (as per ITU-R. BT-656) can be inserted.

#### **SD CHROMA PATH**

The input signal is processed by the following blocks:

- Digital Fine Clamp. This block uses a high precision algorithm to clamp the video signal.

- Chroma Demodulation. This block employs a color subcarrier (F<sub>SC</sub>) recovery unit to regenerate the color subcarrier for any modulated chroma scheme. The demodulation block then performs an AM demodulation for PAL and NTSC and an FM demodulation for SECAM.

- Chroma Filter Block. This block contains a chroma decimation filter (CAA) with a fixed response, and some shaping filters (CSH) that have selectable responses.

- Gain Control. Automatic gain control (AGC) can operate

on several different modes, including gain based on the

color subcarrier's amplitude, gain based on the depth of

the horizontal sync pulse on the luma channel, or fixed

manual gain.

- Chroma Resample. The chroma data is digitally resampled to keep it perfectly aligned with the luma data. The resampling is done to correct for static and dynamic linelength errors of the incoming video signal.

- Chroma 2D Comb. The two-dimensional, 5-line, superadaptive comb filter provides high quality YC separation in case the input signal is CVBS.

- AV Code Insertion. At this point, the demodulated chroma (Cr and Cb) signal is merged with the retrieved luma values. AV codes (as per ITU-R. BT-656) can be inserted.

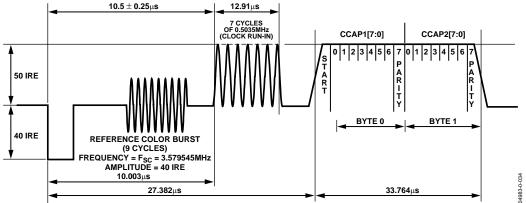

#### SYNC PROCESSING

The ADV7189B extracts syncs embedded in the video data stream. There is currently no support for external HS/VS inputs. The sync extraction has been optimized to support imperfect video sources such as VCRs with head switches. The actual algorithm used employs a coarse detection based on a threshold crossing followed by a more detailed detection using an adaptive interpolation algorithm. The raw sync information is sent to a line-length measurement and prediction block. The output of this is then used to drive the digital resampling section to ensure that the ADV7189B outputs 720 active pixels per line.

The sync processing on the ADV7189B also includes the following specialized postprocessing blocks that filter and condition the raw sync information retrieved from the digitized analog video.

- Vsync Processor. This block provides extra filtering of the detected Vsyncs to give improved vertical lock.

- Hsync Processor. The Hsync processor is designed to filter incoming Hsyncs that are corrupted by noise, providing much improved performance for video signals with stable time base but poor SNR.

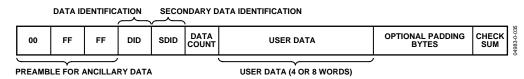

#### **VBI DATA RECOVERY**

The ADV7189B can retrieve the following information from the input video:

- Wide-screen signaling (WSS)

- Copy generation management system (CGMS)

- Closed captioning (CC)

- Macrovision protection presence

- EDTV data

- Gemstar-compatible data slicing

The ADV7189B is also capable of automatically detecting the incoming video standard with respect to

- Color subcarrier frequency

- Field rate

- Line rate

The ADV7189B can configure itself to support PAL-BGHID, PAL-M/N, PAL-combination N, NTSC-M, NTSC-J, SECAM 50 Hz/60 Hz, NTSC4.43, and PAL60.

#### **GENERAL SETUP**

### **Video Standard Selection**

The VID\_SEL[3:0] register allows the user to force the digital core into a specific video standard. Under normal circumstances, this should not be necessary. The VID\_SEL[3:0] bits default to an autodetection mode that supports PAL, NTSC, SECAM, and variants thereof. The following section provides more information on the autodetection system.

#### **Autodetection of SD Modes**

To guide the autodetect system of the ADV7189B, individual enable bits are provided for each of the supported video standards. Setting the relevant bit to 0 inhibits the standard from being detected automatically. Instead, the system picks the closest of the remaining enabled standards. The results of the autodetection can be read back via the status registers. See the Global Status Registers section for more information.

### VID\_SEL[3:0] Address 0x00[7:4] Table 18. VID SEL Function

| Tuble 10. VID_ULE I unetion |                                                                |  |

|-----------------------------|----------------------------------------------------------------|--|

| VID_SEL[3:0]                | Description                                                    |  |

| 0000 (default)              | Autodetect (PAL BGHID) <-> NTSC J (no pedestal), SECAM.        |  |

| 0001                        | Autodetect (PAL BGHID) <-> NTSC M (pedestal), SECAM.           |  |

| 0010                        | Autodetect (PAL N) (pedestal) <-> NTSC J (no pedestal), SECAM. |  |

| 0011                        | Autodetect (PAL N) (pedestal) <-> NTSC M (pedestal), SECAM.    |  |

| 0100                        | NTSC J (1).                                                    |  |

| 0101                        | NTSC M (1).                                                    |  |

| 0110                        | PAL 60.                                                        |  |

| 0111                        | NTSC 4.43 (1).                                                 |  |

| 1000                        | PAL BGHID.                                                     |  |

| 1001                        | PAL N[= PAL BGHID (with pedestal)].                            |  |

| 1010                        | PAL M (without pedestal).                                      |  |

| 1011                        | PAL M.                                                         |  |

| 1100                        | PAL Combination N.                                             |  |

| 1101                        | PAL Combination N (with pedestal).                             |  |

| 1110                        | SECAM.                                                         |  |

| 1111                        | SECAM (with pedestal).                                         |  |

### AD\_SEC525\_EN Enable Autodetection of SECAM 525 Line Video, Address 0x07[7]

Setting AD\_SEC525\_EN to 0 (default), disables the autodetection of a 525-line system with a SECAM style, FM-modulated color component.

Setting AD\_SEC525\_EN to 1 enables the detection.

## AD\_SECAM\_EN Enable Autodetection of SECAM, Address 0x07[6]

Setting AD\_SECAM\_EN to 0 disables the autodetection of SECAM.

Setting AD\_SECAM\_EN to 1 (default) enables the detection.

## AD\_N443\_EN Enable Autodetection of NTSC 443, Address 0x07[5]

Setting AD\_N443\_EN to 0 disables the autodetection of NTSC style systems with a 4.43 MHz color subcarrier.

Setting AD\_N443\_EN to 1 (default) enables the detection.

## AD\_P60\_EN Enable Autodetection of PAL60, Address 0x07[4]

Setting AD\_P60\_EN to 0 disables the autodetection of PAL systems with a 60 Hz field rate.

Setting AD\_P60\_EN to 1 (default) enables the detection.

## AD\_PALN\_EN Enable Autodetection of PAL N, Address 0x07[3]

Setting AD\_PALN\_EN to 0 disables the detection of the PAL N standard.

Setting AD\_PALN\_EN to 1 (default) enables the detection.

## AD\_PALM\_EN Enable Autodetection of PAL M, Address 0x07[2]

Setting AD\_PALM\_EN to 0 disables the autodetection of PAL M. Setting AD\_PALM\_EN to 1 (default), enables the detection.

## AD\_NTSC\_EN Enable Autodetection of NTSC, Address 0x07[1]

Setting AD\_NTSC\_EN to 0 disables the detection of standard NTSC.

Setting AD\_NTSC\_EN to 1 (default) enables the detection.

## AD\_PAL\_EN Enable Autodetection of PAL, Address 0x07[0]

Setting AD\_PAL\_EN to 0 disables the detection of standard PAL.

Setting AD\_PAL\_EN to 1 (default) enables the detection.

### SFL\_INV Subcarrier Frequency Lock Inversion

This bit controls the behavior of the PAL switch bit in the SFL (GenLock Telegram) data stream. It was implemented to solve some compatibility issues with video encoders. It solves two problems as follows:

First, the PAL switch bit is only meaningful in PAL. Some encoders (including Analog Devices encoders) also look at the state of this bit in NTSC.

Second, there was a design change in Analog Devices encoders from ADV717x to ADV719x. The older versions used the SFL (GenLock Telegram) bit directly, while the later ones invert the bit prior to using it. The reason for this is the inversion compensated for the 1-line delay of an SFL (GenLock Telegram) transmission.

As a result, ADV717x encoders need the PAL switch bit in the SFL (GenLock Telegram) to be 1 for NTSC to work. Also, ADV7190/ADV7191/ADV7194 encoders need the PAL switch bit in the SFL to be 0 to work in NTSC. If the state of the PAL switch bit is wrong, a 180° phase shift occurs.

In a decoder/encoder back-to-back system in which SFL is used, this bit must be set up properly for the specific encoder used.

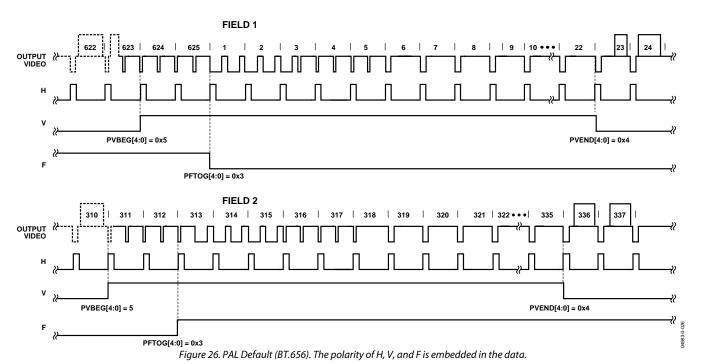

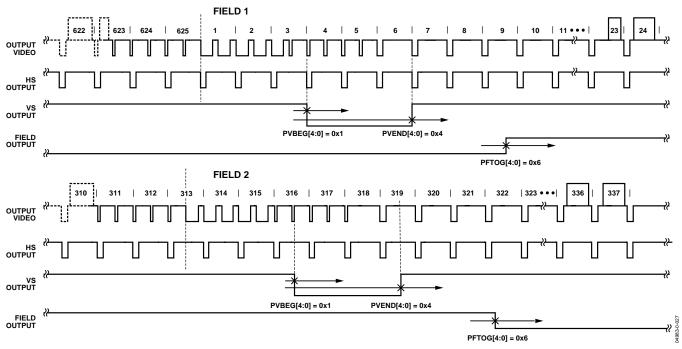

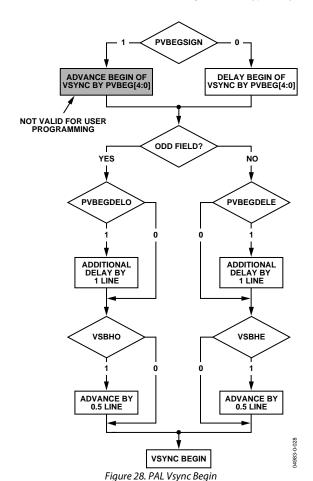

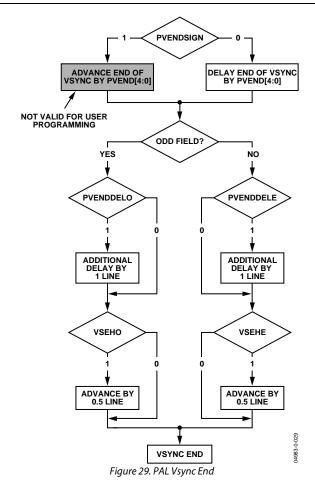

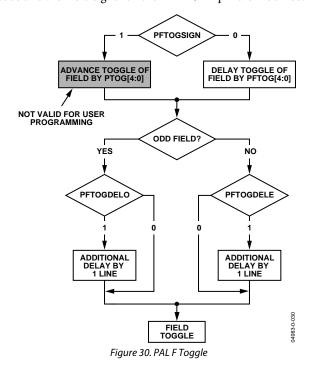

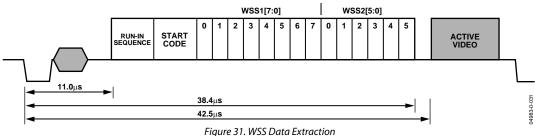

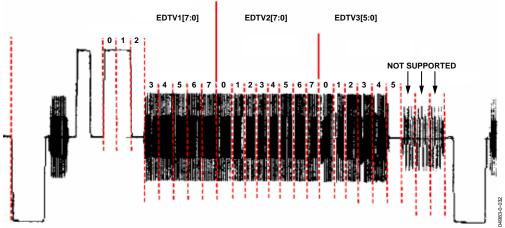

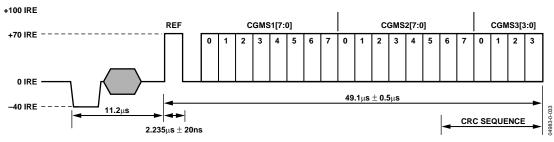

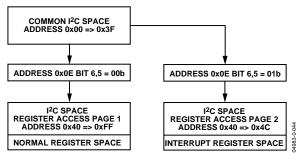

#### SFL\_INV Address 0x41[6]