## LatticeXP2™ Family Data Sheet

DS1009 Version 2.2, September 2014

# LatticeXP2 Family Data Sheet Introduction

February 2012 Data Sheet DS1009

#### **Features**

#### ■ flexiFLASH<sup>™</sup> Architecture

- Instant-on

- Infinitely reconfigurable

- · Single chip

- FlashBAK™ technology

- Serial TAG memory

- · Design security

#### ■ Live Update Technology

- TransFR™ technology

- Secure updates with 128 bit AES encryption

- Dual-boot with external SPI

#### ■ sysDSP<sup>™</sup> Block

- Three to eight blocks for high performance Multiply and Accumulate

- 12 to 32 18x18 multipliers

- Each block supports one 36x36 multiplier or four 18x18 or eight 9x9 multipliers

#### **■** Embedded and Distributed Memory

- Up to 885 Kbits sysMEM™ EBR

- Up to 83 Kbits Distributed RAM

#### ■ sysCLOCK<sup>™</sup> PLLs

- Up to four analog PLLs per device

- · Clock multiply, divide and phase shifting

#### ■ Flexible I/O Buffer

- syslO™ buffer supports:

- LVCMOS 33/25/18/15/12; LVTTL

- SSTL 33/25/18 class I, II

- HSTL15 class I; HSTL18 class I, II

- PCI

- LVDS, Bus-LVDS, MLVDS, LVPECL, RSDS

#### Pre-engineered Source Synchronous Interfaces

- DDR / DDR2 interfaces up to 200 MHz

- 7:1 LVDS interfaces support display applications

- XGMII

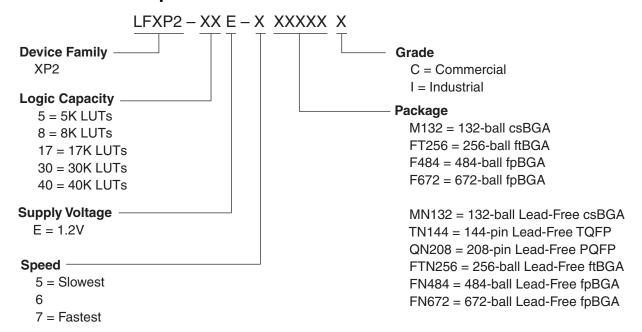

#### ■ Density And Package Options

- 5k to 40k LUT4s, 86 to 540 I/Os

- csBGA, TQFP, PQFP, ftBGA and fpBGA packages

- · Density migration supported

#### ■ Flexible Device Configuration

- SPI (master and slave) Boot Flash Interface

- Dual Boot Image supported

- · Soft Error Detect (SED) macro embedded

#### ■ System Level Support

- IEEE 1149.1 and IEEE 1532 Compliant

- · On-chip oscillator for initialization & general use

- Devices operate with 1.2V power supply

Table 1-1. LatticeXP2 Family Selection Guide

| Device                        | XP2-5 | XP2-8 | XP2-17 | XP2-30 | XP2-40 |

|-------------------------------|-------|-------|--------|--------|--------|

| LUTs (K)                      | 5     | 8     | 17     | 29     | 40     |

| Distributed RAM (KBits)       | 10    | 18    | 35     | 56     | 83     |

| EBR SRAM (KBits)              | 166   | 221   | 276    | 387    | 885    |

| EBR SRAM Blocks               | 9     | 12    | 15     | 21     | 48     |

| sysDSP Blocks                 | 3     | 4     | 5      | 7      | 8      |

| 18 x 18 Multipliers           | 12    | 16    | 20     | 28     | 32     |

| V <sub>CC</sub> Voltage       | 1.2   | 1.2   | 1.2    | 1.2    | 1.2    |

| GPLL                          | 2     | 2     | 4      | 4      | 4      |

| Max Available I/O             | 172   | 201   | 358    | 472    | 540    |

| Packages and I/O Combinations |       |       |        | •      |        |

| 132-Ball csBGA (8 x 8 mm)     | 86    | 86    |        |        |        |

| 144-Pin TQFP (20 x 20 mm)     | 100   | 100   |        |        |        |

| 208-Pin PQFP (28 x 28 mm)     | 146   | 146   | 146    |        |        |

| 256-Ball ftBGA (17 x17 mm)    | 172   | 201   | 201    | 201    |        |

| 484-Ball fpBGA (23 x 23 mm)   |       |       | 358    | 363    | 363    |

| 672-Ball fpBGA (27 x 27 mm)   |       |       |        | 472    | 540    |

#### Introduction

LatticeXP2 devices combine a Look-up Table (LUT) based FPGA fabric with non-volatile Flash cells in an architecture referred to as flexiFLASH.

The flexiFLASH approach provides benefits including instant-on, infinite reconfigurability, on chip storage with FlashBAK embedded block memory and Serial TAG memory and design security. The parts also support Live Update technology with TransFR, 128-bit AES Encryption and Dual-boot technologies.

The LatticeXP2 FPGA fabric was optimized for the new technology from the outset with high performance and low cost in mind. LatticeXP2 devices include LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support and enhanced sysDSP blocks.

Lattice Diamond® design software allows large and complex designs to be efficiently implemented using the LatticeXP2 family of FPGA devices. Synthesis library support for LatticeXP2 is available for popular logic synthesis tools. The Diamond software uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeXP2 device. The Diamond tool extracts the timing from the routing and back-annotates it into the design for timing verification.

Lattice provides many pre-designed Intellectual Property (IP) LatticeCORE™ modules for the LatticeXP2 family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

## LatticeXP2 Family Data Sheet Architecture

August 2014 Data Sheet DS1009

#### **Architecture Overview**

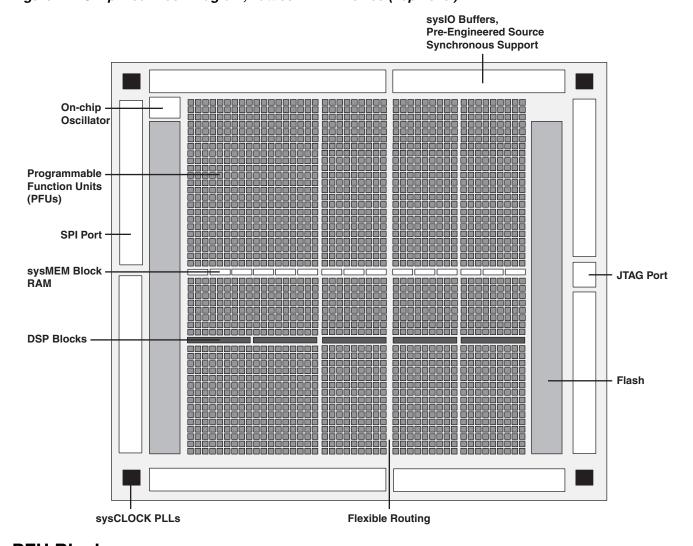

Each LatticeXP2 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM™ Embedded Block RAM (EBR) and a row of sysDSP™ Digital Signal Processing blocks as shown in Figure 2-1.

On the left and right sides of the Programmable Functional Unit (PFU) array, there are Non-volatile Memory Blocks. In configuration mode the nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG™ peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memory is not required, and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications. LatticeXP2 devices can also transfer data from the sysMEM EBR blocks to the Non-volatile Memory Blocks at user request.

There are two kinds of logic blocks, the PFU and the PFU without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

LatticeXP2 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large dedicated 18Kbit memory blocks. Each sysMEM block can be configured in a variety of depths and widths of RAM or ROM. In addition, LatticeXP2 devices contain up to two rows of DSP Blocks. Each DSP block has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO buffers. The sysIO buffers of the LatticeXP2 devices are arranged into eight banks, allowing the implementation of a wide variety of I/O standards. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as 7:1 LVDS interfaces, found in many display applications, and memory interfaces including DDR and DDR2.

The LatticeXP2 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

Other blocks provided include PLLs and configuration functions. The LatticeXP2 architecture provides up to four General Purpose PLLs (GPLL) per device. The GPLL blocks are located in the corners of the device.

The configuration block that supports features such as configuration bit-stream de-encryption, transparent updates and dual boot support is located between banks two and three. Every device in the LatticeXP2 family supports a sysCONFIG port, muxed with bank seven I/Os, which supports serial device configuration. A JTAG port is provided between banks two and three.

This family also provides an on-chip oscillator. LatticeXP2 devices use 1.2V as their core voltage.

Figure 2-1. Simplified Block Diagram, LatticeXP2-17 Device (Top Level)

#### **PFU Blocks**

The core of the LatticeXP2 device is made up of logic blocks in two forms, PFUs and PFFs. PFUs can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. PFF blocks can be programmed to perform logic, arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

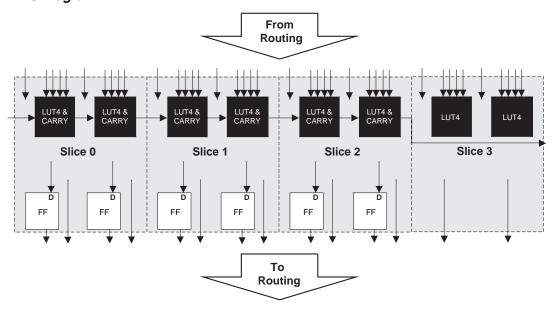

Each PFU block consists of four interconnected slices, numbered Slice 0 through Slice 3, as shown in Figure 2-2. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

Figure 2-2. PFU Diagram

#### Slice

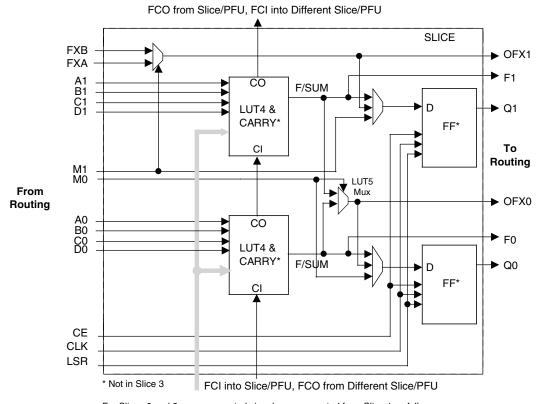

Slice 0 through Slice 2 contain two 4-input combinatorial Look-Up Tables (LUT4), which feed two registers. Slice 3 contains two LUT4s and no registers. For PFUs, Slice 0 and Slice 2 can also be configured as distributed memory, a capability not available in PFF blocks. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured as positive/negative edge triggered or level sensitive clocks.

Table 2-1. Resources and Modes Available per Slice

|         | PFU E                   | BLock                   | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM      | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Slice 0 through Slice 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 13 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

Figure 2-3. Slice Diagram

For Slices 0 and 2, memory control signals are generated from Slice 1 as follows: WCK is CLK WRE is from LSR

DI[3:2] for Slice 2 and DI[1:0] for Slice 0 data WAD [A:D] is a 4bit address from slice 1 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-In <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

- 1. See Figure 2-3 for connection details.

- 2. Requires two PFUs.

#### **Modes of Operation**

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### **Logic Mode**

In this mode, the LUTs in each slice are configured as LUT4s. A LUT4 has 16 possible input combinations. Four-input logic functions are generated by programming the LUT4. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger LUTs such as LUT6, LUT7 and LUT8, can be constructed by concatenating two or more slices. Note that a LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode allows efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- · Addition 2-bit

- · Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- · Down counter 2-bit

- Up/Down counter with async clear

- Up/Down counter with preload (sync)

- · Ripple mode multiplier building block

- · Multiplier support

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two carry signals, FCI and FCO, are generated per slice in this mode, allowing fast arithmetic functions to be constructed by concatenating slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed Single Port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 2 as a 16x1-bit memory. Slice 1 is used to provide memory address and control signals. A 16x2-bit Pseudo Dual Port RAM (PDPR) memory is created by using one slice as the read-write port and the other companion slice as the read-only port.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information on using RAM in LatticeXP2 devices, please see TN1137, <u>LatticeXP2 Memory Usage Guide</u>.

Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in the ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

## **Routing**

There are many resources provided in the LatticeXP2 devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) or x6 (spans seven PFU) connections. The x1 and x2 connections provide fast and efficient connections in horizontal and vertical directions. The x2 and x6 resources are buffered to allow both short and long connections routing between PFUs.

The LatticeXP2 family has an enhanced routing architecture to produce a compact design. The Diamond design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## sysCLOCK Phase Locked Loops (PLL)

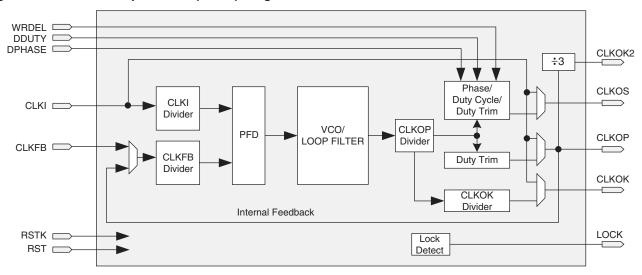

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The LatticeXP2 family supports between two and four full featured General Purpose PLLs (GPLL). The architecture of the GPLL is shown in Figure 2-4.

CLKI, the PLL reference frequency, is provided either from the pin or from routing; it feeds into the Input Clock Divider block. CLKFB, the feedback signal, is generated from CLKOP (the primary clock output) or from a user clock pin/logic. CLKFB feeds into the Feedback Divider and is used to multiply the reference frequency.

Both the input path and feedback signals enter the Voltage Controlled Oscillator (VCO) block. The phase and frequency of the VCO are determined from the input path and feedback signals. A LOCK signal is generated by the VCO to indicate that the VCO is locked with the input clock signal.

The output of the VCO feeds into the CLKOP Divider, a post-scalar divider. The duty cycle of the CLKOP Divider output can be fine tuned using the Duty Trim block, which creates the CLKOP signal. By allowing the VCO to operate at higher frequencies than CLKOP, the frequency range of the GPLL is expanded. The output of the CLKOP Divider is passed through the CLKOK Divider, a secondary clock divider, to generate lower frequencies for the CLKOK output. For applications that require even lower frequencies, the CLKOP signal is passed through a divide-by-three divider to produce the CLKOK2 output. The CLKOK2 output is provided for applications that use source synchronous logic. The Phase/Duty Cycle/Duty Trim block is used to adjust the phase and duty cycle of the CLKOP Divider output to generate the CLKOS signal. The phase/duty cycle setting can be pre-programmed or dynamically adjusted.

The clock outputs from the GPLL; CLKOP, CLKOK, CLKOK2 and CLKOS, are fed to the clock distribution network.

For further information on the GPLL please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and Usage Guide</u>.

Figure 2-4. General Purpose PLL (GPLL) Diagram

Table 2-4 provides a description of the signals in the GPLL blocks.

Table 2-4. GPLL Block Signal Descriptions

| Signal       | I/O | Description                                                                                              |  |

|--------------|-----|----------------------------------------------------------------------------------------------------------|--|

| CLKI         | I   | Clock input from external pin or routing                                                                 |  |

| CLKFB        | I   | PLL feedback input from CLKOP (PLL internal), from clock net (CLKOP) or from a user clock (PIN or logic) |  |

| RST          | ı   | "1" to reset PLL counters, VCO, charge pumps and M-dividers                                              |  |

| RSTK         | I   | "1" to reset K-divider                                                                                   |  |

| DPHASE [3:0] | I   | DPA Phase Adjust input                                                                                   |  |

| DDDUTY [3:0] | I   | DPA Duty Cycle Select input                                                                              |  |

| WRDEL        | I   | DPA Fine Delay Adjust input                                                                              |  |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                        |  |

| CLKOP        | 0   | PLL output clock to clock tree (no phase shift)                                                          |  |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                 |  |

| CLKOK2       | 0   | PLL output to clock tree (CLKOP divided by 3)                                                            |  |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                           |  |

#### **Clock Dividers**

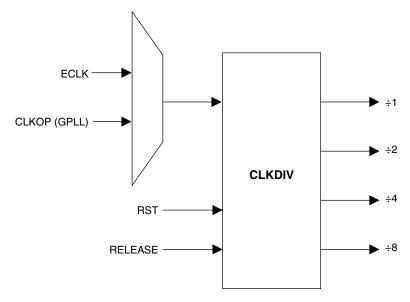

LatticeXP2 devices have two clock dividers, one on the left side and one on the right side of the device. These are intended to generate a slower-speed system clock from a high-speed edge clock. The block operates in a ÷2, ÷4 or ÷8 mode and maintains a known phase relationship between the divided down clock and the high-speed clock based on the release of its reset signal. The clock dividers can be fed from the CLKOP output from the GPLLs or from the Edge Clocks (ECLK). The clock divider outputs serve as primary clock sources and feed into the clock distribution network. The Reset (RST) control signal resets the input and forces all outputs to low. The RELEASE signal releases outputs to the input clock. For further information on clock dividers, please see TN1126, LatticeXP2 sysCLOCK PLL Design and Usage Guide. Figure 2-5 shows the clock divider connections.

Figure 2-5. Clock Divider Connections

#### **Clock Distribution Network**

LatticeXP2 devices have eight quadrant-based primary clocks and between six and eight flexible region-based secondary clocks/control signals. Two high performance edge clocks are available on each edge of the device to support high speed interfaces. The clock inputs are selected from external I/Os, the sysCLOCK PLLs, or routing. Clock inputs are fed throughout the chip via the primary, secondary and edge clock networks.

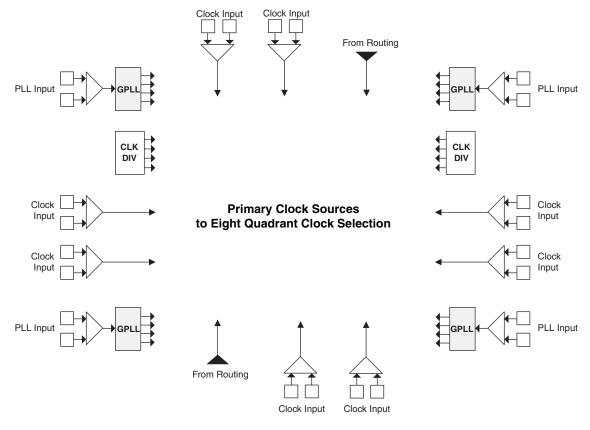

#### **Primary Clock Sources**

LatticeXP2 devices derive primary clocks from four sources: PLL outputs, CLKDIV outputs, dedicated clock inputs and routing. LatticeXP2 devices have two to four sysCLOCK PLLs, located in the four corners of the device. There are eight dedicated clock inputs, two on each side of the device. Figure 2-6 shows the primary clock sources.

Figure 2-6. Primary Clock Sources for XP2-17

$Note: This \ diagram \ shows \ sources \ for \ the \ XP2-17 \ device. \ Smaller \ Lattice XP2 \ devices \ have \ two \ GPLLs.$

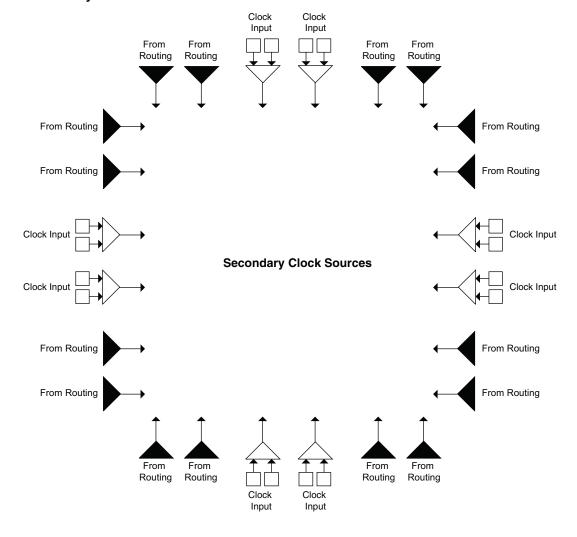

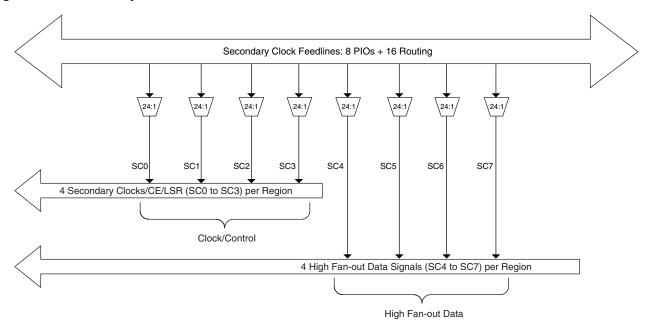

### **Secondary Clock/Control Sources**

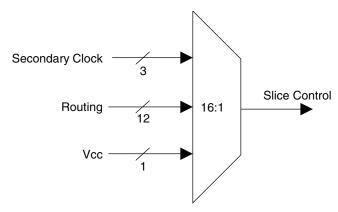

LatticeXP2 devices derive secondary clocks (SC0 through SC7) from eight dedicated clock input pads and the rest from routing. Figure 2-7 shows the secondary clock sources.

Figure 2-7. Secondary Clock Sources

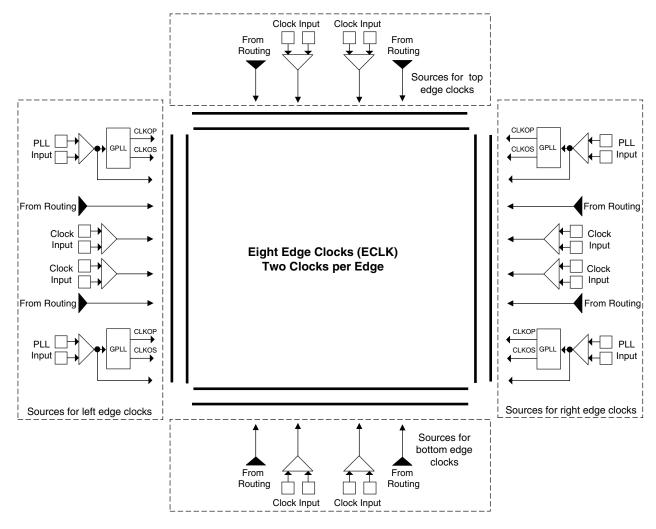

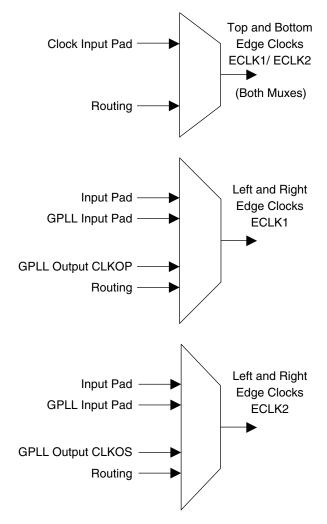

## **Edge Clock Sources**

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs and clock dividers as shown in Figure 2-8.

Figure 2-8. Edge Clock Sources

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

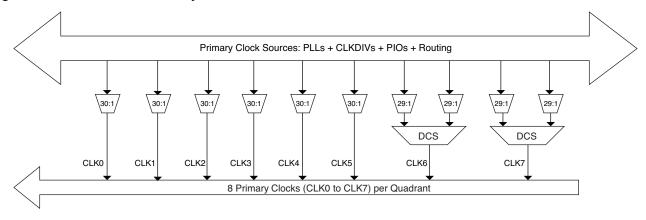

#### **Primary Clock Routing**

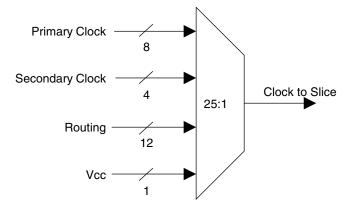

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

Figure 2-9. Per Quadrant Primary Clock Selection

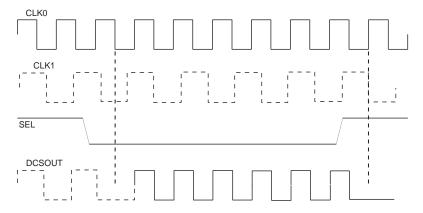

## **Dynamic Clock Select (DCS)**

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-9).

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and Usage Guide</u>.

Figure 2-10. DCS Waveforms

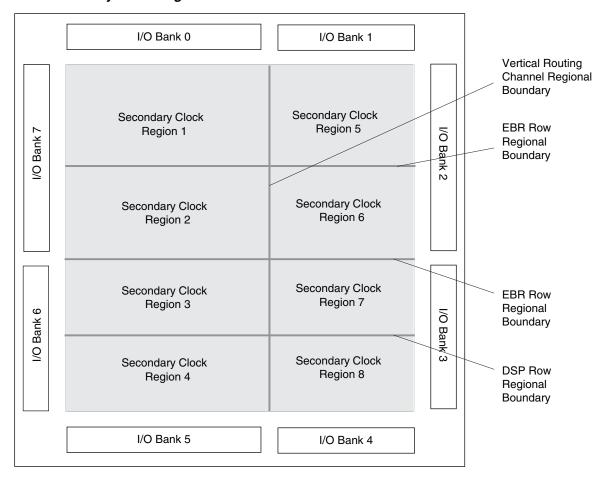

#### Secondary Clock/Control Routing

Secondary clocks in the LatticeXP2 devices are region-based resources. The benefit of region-based resources is the relatively low injection delay and skew within the region, as compared to primary clocks. EBR rows, DSP rows and a special vertical routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special vertical routing channel and the eight secondary clock regions for the LatticeXP2-40.

LatticeXP2-30 and smaller devices have six secondary clock regions. All devices in the LatticeXP2 family have four secondary clocks (SC0 to SC3) which are distributed to every region.

The secondary clock muxes are located in the center of the device. Figure 2-12 shows the mux structure of the secondary clock routing. Secondary clocks SC0 to SC3 are used for clock and control and SC4 to SC7 are used for high fan-out signals.

Figure 2-11. Secondary Clock Regions XP2-40

Figure 2-12. Secondary Clock Selection

#### Slice Clock Selection

Figure 2-13 shows the clock selections and Figure 2-14 shows the control selections for Slice0 through Slice2. All the primary clocks and the four secondary clocks are routed to this clock selection mux. Other signals, via routing, can be used as clock inputs to the slices. Slice controls are generated from the secondary clocks or other signals connected via routing.

If none of the signals are selected for both clock and control, then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

Figure 2-13. Slice0 through Slice2 Clock Selection

Figure 2-14. Slice0 through Slice2 Control Selection

## **Edge Clock Routing**

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

Figure 2-15. Edge Clock Mux Connections

## sysMEM Memory

LatticeXP2 devices contains a number of sysMEM Embedded Block RAM (EBR). The EBR consists of 18 Kbit RAM with dedicated input and output registers.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-5. FIFOs can be implemented in sysMEM EBR blocks by using support logic with PFUs. The EBR block supports an optional parity bit for each data byte to facilitate parity checking. EBR blocks provide byte-enable support for configurations with 18-bit and 36-bit data widths.

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                                              |

|------------------|-----------------------------------------------------------------------------|

| Single Port      | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| True Dual Port   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| Pseudo Dual Port | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

#### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

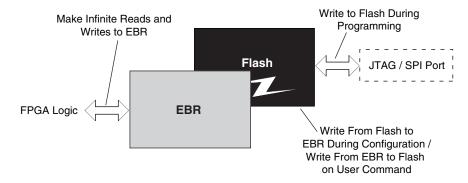

#### FlashBAK EBR Content Storage

All the EBR memory in the LatticeXP2 is shadowed by Flash memory. Optionally, initialization values for the memory blocks can be defined using the Lattice Diamond design tools. The initialization values are loaded into the Flash memory during device programming and into the SRAM at power up or whenever the device is reconfigured. This feature is ideal for the storage of a variety of information such as look-up tables and microprocessor code. It is also possible to write the current contents of the EBR memory back to Flash memory. This capability is useful for the storage of data such as error codes and calibration information. For additional information on the FlashBAK capability see TN1137, LatticeXP2 Memory Usage Guide.

Figure 2-16. FlashBAK Technology

#### **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual and Pseudo-Dual Port Modes

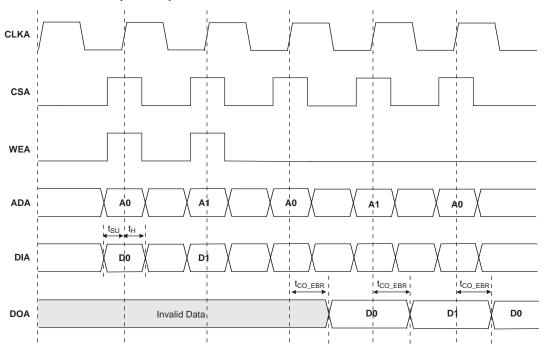

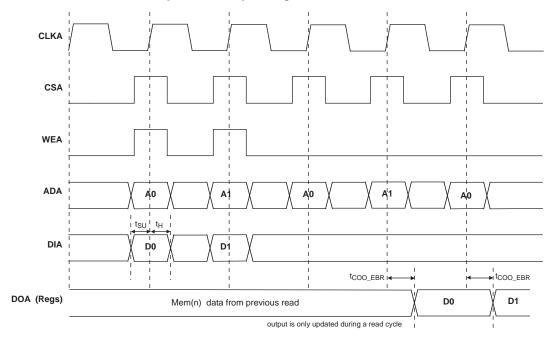

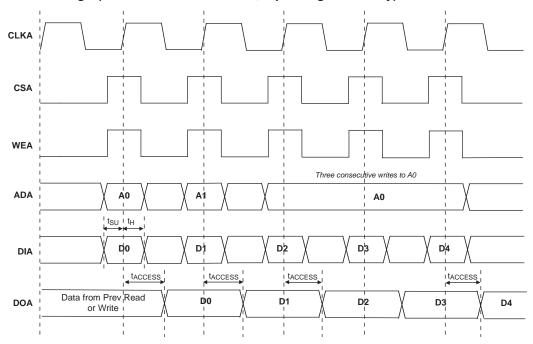

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports two forms of write behavior for single port or dual port operation:

- 1. Normal Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

## **Memory Core Reset**

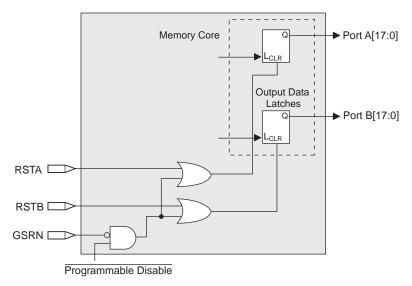

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. GSRN, the global reset signal, resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-17.

Figure 2-17. Memory Core Reset

For further information on the sysMEM EBR block, please see TN1137, LatticeXP2 Memory Usage Guide.

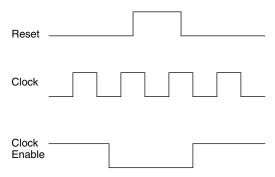

#### **EBR Asynchronous Reset**

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the low-to-high transition of the reset signal, as shown in Figure 2-18. The GSR input to the EBR is always asynchronous.

Figure 2-18. EBR Asynchronous Reset (Including GSR) Timing Diagram

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM and ROM implementations.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## sysDSP™ Block

The LatticeXP2 family provides a sysDSP block making it ideally suited for low cost, high performance Digital Signal Processing (DSP) applications. Typical functions used in these applications include Bit Correlators, Fast Fourier Transform (FFT) functions, Finite Impulse Response (FIR) Filter, Reed-Solomon Encoder/Decoder, Turbo Encoder/Decoder and Convolutional Encoder/Decoder. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

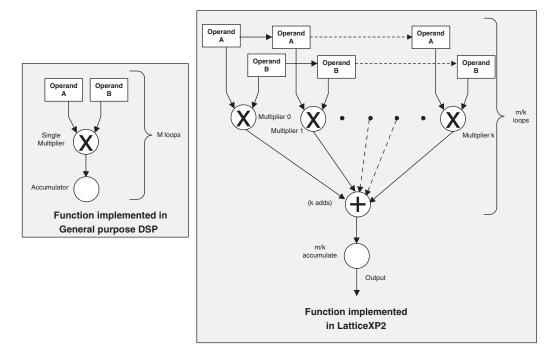

### sysDSP Block Approach Compare to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeXP2 family, on the other hand, has many DSP blocks that support different data-widths. This allows the designer to use highly parallel implementations of DSP functions. The designer can optimize the DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-19 compares the fully serial and the mixed parallel and serial implementations.

Figure 2-19. Comparison of General DSP and LatticeXP2 Approaches

#### sysDSP Block Capabilities

The sysDSP block in the LatticeXP2 family supports four functional elements in three 9, 18 and 36 data path widths. The user selects a function element for a DSP block and then selects the width and type (signed/unsigned) of its operands. The operands in the LatticeXP2 family sysDSP Blocks can be either signed or unsigned but not mixed within a function element. Similarly, the operand widths cannot be mixed within a block. DSP elements can be concatenated.

The resources in each sysDSP block can be configured to support the following four elements:

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Accumulate)

The number of elements available in each block depends on the width selected from the three available options: x9, x18, and x36. A number of these elements are concatenated for highly parallel implementations of DSP functions. Table 2-6 shows the capabilities of the block.

Table 2-6. Maximum Number of Elements in a Block

| Width of Multiply | х9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 8  | 4   | 1   |

| MAC               | 2  | 2   | _   |

| MULTADDSUB        | 4  | 2   | _   |

| MULTADDSUBSUM     | 2  | 1   | _   |

Some options are available in four elements. The input register in all the elements can be directly loaded or can be loaded as shift register from previous operand registers. By selecting 'dynamic operation' the following operations are possible:

- In the 'Signed/Unsigned' options the operands can be switched between signed and unsigned on every cycle.

- In the 'Add/Sub' option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

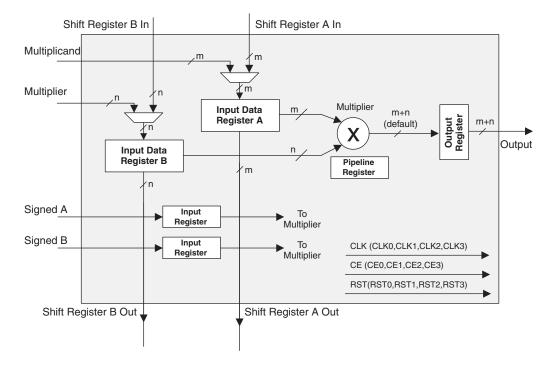

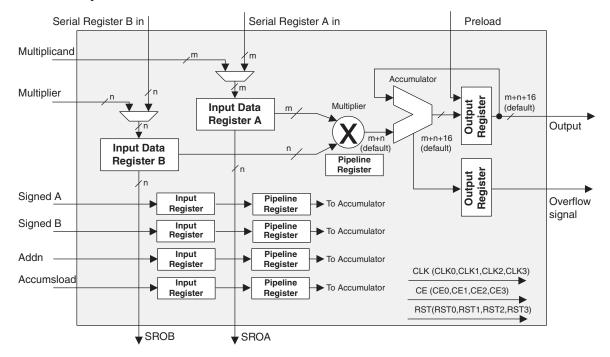

### **MULT sysDSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, A and B, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-20 shows the MULT sysDSP element.

Figure 2-20. MULT sysDSP Element

#### **MAC sysDSP Element**

In this case, the two operands, A and B, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers but the output register is always enabled. The output register is used to store the accumulated value. The Accumulators in the DSP blocks in LatticeXP2 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-21 shows the MAC sysDSP element.

Figure 2-21. MAC sysDSP

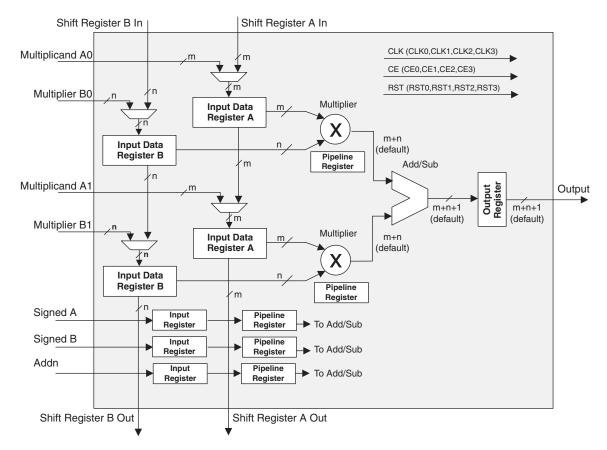

## **MULTADDSUB sysDSP Element**

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and B1. The user can enable the input, output and pipeline registers. Figure 2-22 shows the MULTADDSUB sysDSP element.

Figure 2-22. MULTADDSUB

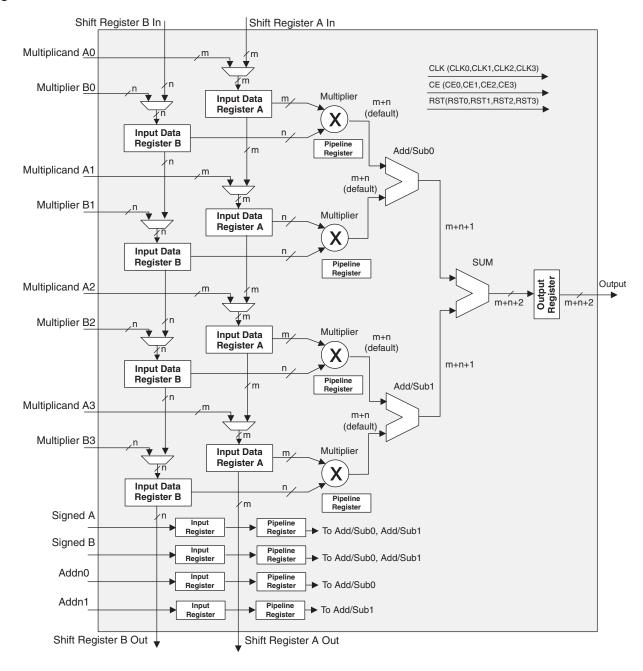

#### **MULTADDSUBSUM sysDSP Element**

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and B1. Additionally the operands A2 and B2 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A3 and B3. The result of both addition/subtraction are added in a summation block. The user can enable the input, output and pipeline registers. Figure 2-23 shows the MULTADDSUBSUM sysDSP element.

Figure 2-23. MULTADDSUBSUM

#### Clock, Clock Enable and Reset Resources

Global Clock, Clock Enable (CE) and Reset (RST) signals from routing are available to every DSP block. From four clock sources (CLK0, CLK1, CLK2, CLK3) one clock is selected for each input register, pipeline register and output

register. Similarly, CE and RST are selected from their four respective sources (CE0, CE1, CE2, CE3 and RST0, RST1, RST2, RST3) at each input register, pipeline register and output register.

### Signed and Unsigned with Different Widths

The DSP block supports other widths, in addition to x9, x18 and x36 widths, of signed and unsigned multipliers. For unsigned operands, unused upper data bits should be filled to create a valid x9, x18 or x36 operand. For signed two's complement operands, sign extension of the most significant bit should be performed until x9, x18 or x36 width is reached. Table 2-7 provides an example of this.

Table 2-7. Sign Extension Example

|   | Number | Unsigned | Unsigned<br>9-bit | Unsigned<br>18-bit | Signed | Two's Complement<br>Signed 9 Bits | Two's Complement<br>Signed 18 Bits |

|---|--------|----------|-------------------|--------------------|--------|-----------------------------------|------------------------------------|

| Ī | +5     | 0101     | 00000101          | 00000000000000101  | 0101   | 00000101                          | 00000000000000101                  |

| Ī | -6     | N/A      | N/A               | N/A                | 1010   | 111111010                         | 1111111111111111010                |

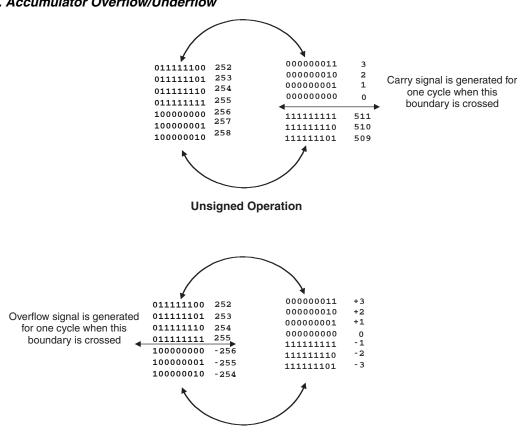

#### **OVERFLOW Flag from MAC**

The sysDSP block provides an overflow output to indicate that the accumulator has overflowed. "Roll-over" occurs and an overflow signal is indicated when any of the following is true: two unsigned numbers are added and the result is a smaller number than the accumulator, two positive numbers are added with a negative sum or two negative numbers are added with a positive sum. Note that when overflow occurs the overflow flag is present for only one cycle. By counting these overflow pulses in FPGA logic, larger accumulators can be constructed. The conditions for the overflow signal for signed and unsigned operands are listed in Figure 2-24.

Figure 2-24. Accumulator Overflow/Underflow

**Signed Operation**

#### IPexpress<sup>™</sup>

The user can access the sysDSP block via the Lattice IPexpress tool, which provides the option to configure each DSP module (or group of modules), or by direct HDL instantiation. In addition, Lattice has partnered with The Math-Works® to support instantiation in the Simulink® tool, a graphical simulation environment. Simulink works with Diamond to dramatically shorten the DSP design cycle in Lattice FPGAs.

## **Optimized DSP Functions**

Lattice provides a library of optimized DSP IP functions. Some of the IP cores planned for the LatticeXP2 DSP include the Bit Correlator, FFT functions, FIR Filter, Reed-Solomon Encoder/Decoder, Turbo Encoder/Decoder and Convolutional Encoder/Decoder. Please contact Lattice to obtain the latest list of available DSP IP cores.

#### **Resources Available in the LatticeXP2 Family**

Table 2-8 shows the maximum number of multipliers for each member of the LatticeXP2 family. Table 2-9 shows the maximum available EBR RAM Blocks and Serial TAG Memory bits in each LatticeXP2 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

Table 2-8. Maximum Number of DSP Blocks in the LatticeXP2 Family

| Device | DSP Block | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|--------|-----------|----------------|------------------|------------------|

| XP2-5  | 3         | 24             | 12               | 3                |

| XP2-8  | 4         | 32             | 16               | 4                |

| XP2-17 | 5         | 40             | 20               | 5                |

| XP2-30 | 7         | 56             | 28               | 7                |

| XP2-40 | 8         | 64             | 32               | 8                |

Table 2-9. Embedded SRAM/TAG Memory in the LatticeXP2 Family

| Device | EBR SRAM Block | Total EBR SRAM<br>(Kbits) | TAG Memory<br>(Bits) |

|--------|----------------|---------------------------|----------------------|

| XP2-5  | 9              | 166                       | 632                  |

| XP2-8  | 12             | 221                       | 768                  |

| XP2-17 | 15             | 276                       | 2184                 |

| XP2-30 | 21             | 387                       | 2640                 |

| XP2-40 | 48             | 885                       | 3384                 |

#### LatticeXP2 DSP Performance

Table 2-10 lists the maximum performance in Millions of MAC (MMAC) operations per second for each member of the LatticeXP2 family.

Table 2-10. DSP Performance

| Device | DSP Block | DSP Performance<br>MMAC |

|--------|-----------|-------------------------|

| XP2-5  | 3         | 3,900                   |

| XP2-8  | 4         | 5,200                   |

| XP2-17 | 5         | 6,500                   |

| XP2-30 | 7         | 9,100                   |

| XP2-40 | 8         | 10,400                  |

For further information on the sysDSP block, please see TN1140, LatticeXP2 sysDSP Usage Guide.

## **Programmable I/O Cells (PIC)**

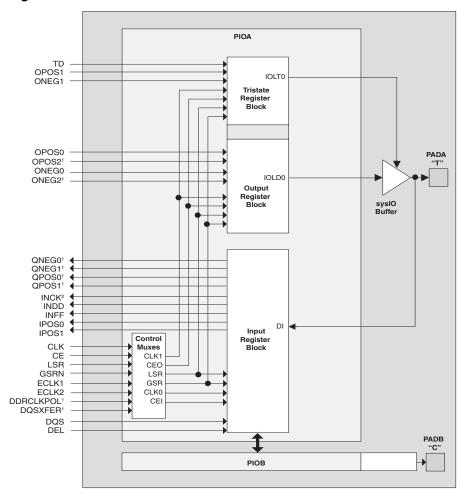

Each PIC contains two PIOs connected to their respective sysIO buffers as shown in Figure 2-25. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysIO buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

Figure 2-25. PIC Diagram

<sup>1.</sup> Signals are available on left/right/bottom edges only. 2. Selected blocks.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-25. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as inputs.

#### Table 2-11. PIO Signal List

| Name                                    | Туре                            | Description                                                             |

|-----------------------------------------|---------------------------------|-------------------------------------------------------------------------|

| CE                                      | Control from the core           | Clock enables for input and output block flip-flops                     |

| CLK                                     | Control from the core           | System clocks for input and output blocks                               |

| ECLK1, ECLK2                            | Control from the core           | Fast edge clocks                                                        |

| LSR                                     | Control from the core           | Local Set/Reset                                                         |

| GSRN                                    | Control from routing            | Global Set/Reset (active low)                                           |

| INCK <sup>2</sup>                       | Input to the core               | Input to Primary Clock Network or PLL reference inputs                  |

| DQS                                     | Input to PIO                    | DQS signal from logic (routing) to PIO                                  |

| INDD                                    | Input to the core               | Unregistered data input to core                                         |

| INFF                                    | Input to the core               | Registered input on positive edge of the clock (CLK0)                   |

| IPOS0, IPOS1                            | Input to the core               | Double data rate registered inputs to the core                          |

| QPOS0 <sup>1</sup> , QPOS1 <sup>1</sup> | Input to the core               | Gearbox pipelined inputs to the core                                    |

| QNEG0 <sup>1</sup> , QNEG1 <sup>1</sup> | Input to the core               | Gearbox pipelined inputs to the core                                    |

| OPOS0, ONEG0,<br>OPOS2, ONEG2           | Output data from the core       | Output signals from the core for SDR and DDR operation                  |

| OPOS1 ONEG1                             | Tristate control from the core  | Signals to Tristate Register block for DDR operation                    |

| DEL[3:0]                                | Control from the core           | Dynamic input delay control bits                                        |

| TD                                      | Tristate control from the core  | Tristate signal from the core used in SDR operation                     |

| DDRCLKPOL                               | Control from clock polarity bus | Controls the polarity of the clock (CLK0) that feed the DDR input block |

| DQSXFER                                 | Control from core               | Controls signal to the Output block                                     |

<sup>1.</sup> Signals available on left/right/bottom only.

#### PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with necessary clock and selection logic.

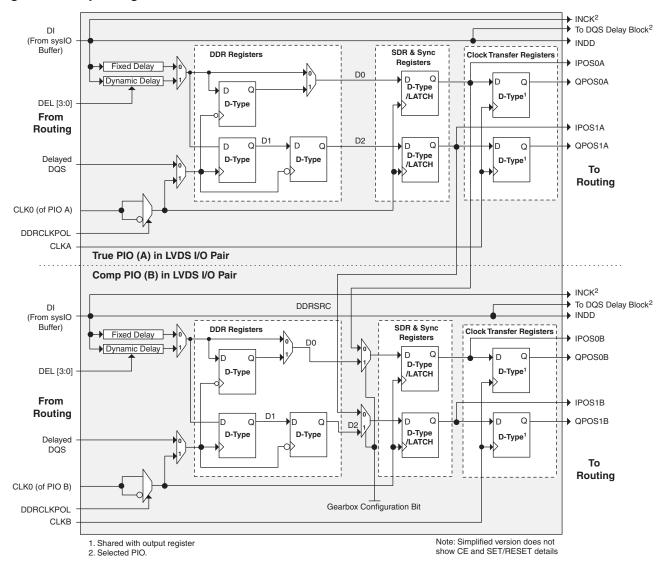

#### **Input Register Block**

The input register blocks for PIOs contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-26 shows the diagram of the input register block.

Input signals are fed from the sysIO buffer to the input register block (as signal DI). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), a clock (INCK) and, in selected blocks, the input to the DQS delay block. If an input delay is desired, designers can select either a fixed delay or a dynamic delay DEL[3:0]. The delay, if selected, reduces input register hold time requirements when using a global clock.

The input block allows three modes of operation. In the Single Data Rate (SDR) mode, the data is registered, by one of the registers in the SDR Sync register block, with the system clock. In DDR mode two registers are used to sample the data on the positive and negative edges of the DQS signal which creates two data streams, D0 and D2. D0 and D2 are synchronized with the system clock before entering the core. Further information on this topic can be found in the DDR Memory Support section of this data sheet.

By combining input blocks of the complementary PIOs and sharing registers from output blocks, a gearbox function can be implemented, that takes a double data rate signal applied to PIOA and converts it as four data streams, IPOS0A, IPOS0B and IPOS1B. Figure 2-26 shows the diagram using this gearbox function. For more information on this topic, please see TN1138, <u>LatticeXP2 High Speed I/O Interface</u>.

<sup>2.</sup> Selected I/O.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred from the DQS to system clock domain. For further discussion on this topic, see the DDR Memory section of this data sheet.

Figure 2-26. Input Register Block

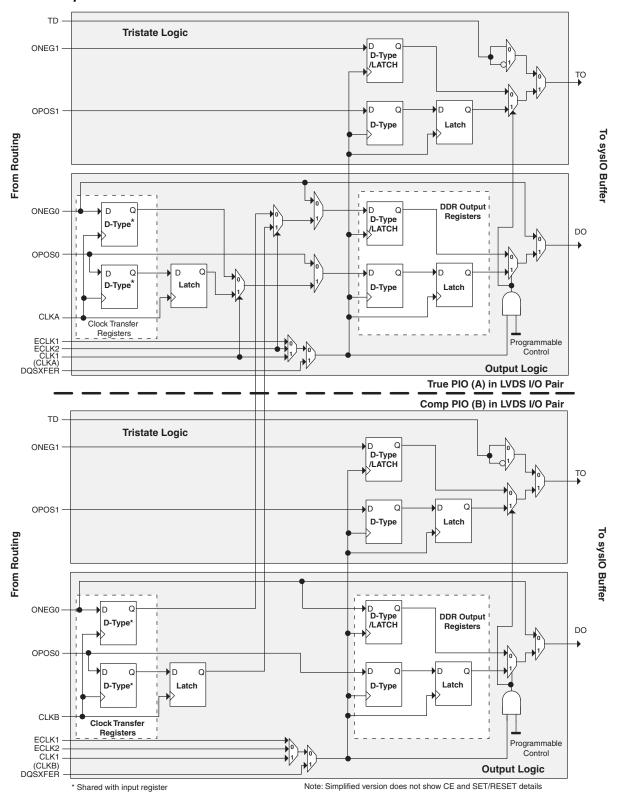

#### **Output Register Block**

The output register block provides the ability to register signals from the core of the device before they are passed to the sysIO buffers. The blocks on the PIOs on the left, right and bottom contain registers for SDR operation that are combined with an additional latch for DDR operation. Figure 2-27 shows the diagram of the Output Register Block for PIOs.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a D-type or latch. In DDR mode, ONEG0 and OPOS0 are fed into registers on the positive edge of the clock. At the next clock cycle the registered OPOS0 is latched. A multiplexer running off the same clock cycle selects the correct register to feed the output (D0).

By combining output blocks of the complementary PIOs and sharing some registers from input blocks, a gearbox function can be implemented, to take four data streams ONEG0A, ONEG1A, ONEG1B and ONEG1B. Figure 2-27

shows the diagram using this gearbox function. For more information on this topic, see TN1138, <u>LatticeXP2 High Speed I/O Interface</u>.

Figure 2-27. Output and Tristate Block

#### **Tristate Register Block**

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the syslO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-27 shows the Tristate Register Block with the Output Block

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as D-type or latch. In DDR mode, ONEG1 and OPOS1 are fed into registers on the positive edge of the clock. Then in the next clock the registered OPOS1 is latched. A multiplexer running off the same clock cycle selects the correct register for feeding to the output (D0).

#### **Control Logic Block**

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock signal is selected from general purpose routing, ECLK1, ECLK2 or a DQS signal (from the programmable DQS pin) and is provided to the input register block. The clock can optionally be inverted.

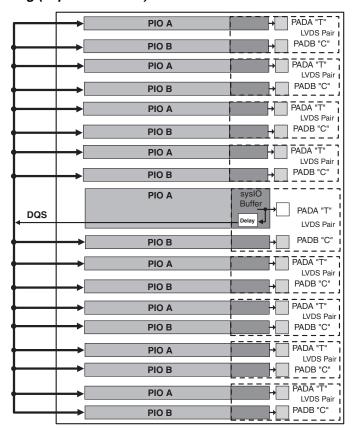

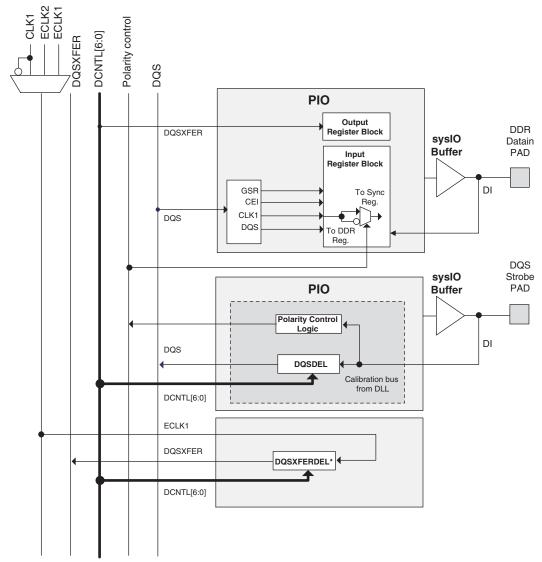

## **DDR Memory Support**

PICs have additional circuitry to allow implementation of high speed source synchronous and DDR memory interfaces.

PICs have registered elements that support DDR memory interfaces. Interfaces on the left and right edges are designed for DDR memories that support 16 bits of data, whereas interfaces on the top and bottom are designed for memories that support 18 bits of data. One of every 16 PIOs on the left and right and one of every 18 PIOs on the top and bottom contain delay elements to facilitate the generation of DQS signals. The DQS signals feed the DQS buses which span the set of 16 or 18 PIOs. Figure 2-28 and Figure 2-29 show the DQS pin assignments in each set of PIOs.

The exact DQS pins are shown in a dual function in the Logic Signal Connections table in this data sheet. Additional detail is provided in the Signal Descriptions table. The DQS signal from the bus is used to strobe the DDR data from the memory into input register blocks. For additional information on using DDR memory support please see TN1138, LatticeXP2 High Speed I/O Interface.

Figure 2-28. DQS Input Routing (Left and Right)

Figure 2-29. DQS Input Routing (Top and Bottom)

#### **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment. However, in DDR memories the clock, referred to as DQS, is not free-running, and this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only, as shown in Figure 2-30) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figure 2-30 and Figure 2-31 show how the DQS transition signals are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of 6-bit bus calibration signals from two dedicated DLLs (DDR\_DLL) on opposite sides of the device. Each DLL compensates DQS delays in its half of the device as shown in Figure 2-30. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

I/O Bank 0 I/O Bank 1 Spans 16 PIOs Left & Right Sides ECLK1 ECLK2 ੋਂ /O Bank 7 Bank 2 **DQS Input** Delayed DDR\_DLL DDR\_DLL DQS (Right) **Polarity Control** DQSXFER 5 Bank Bank 3 **DQS Delay** 0 Control Bus Spans 18 PIOs Top & Bottom Sides I/O Bank 5 I/O Bank 4

Figure 2-30. Edge Clock, DLL Calibration and DQS Local Bus Distribution

Figure 2-31. DQS Local Bus

\*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

## **Polarity Control Logic**

In a typical DDR memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeXP2 family contains dedicated circuits to transfer data between these domains. To prevent set-up and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block and requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

#### **DQSXFER**

LatticeXP2 devices provide a DQSXFER signal to the output buffer to assist it in data transfer to DDR memories that require DQS strobe be shifted 90°. This shifted DQS strobe is generated by the DQSDEL block. The DQSXFER signal runs the span of the data bus.

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, SSTL, HSTL, LVDS and LVPECL.

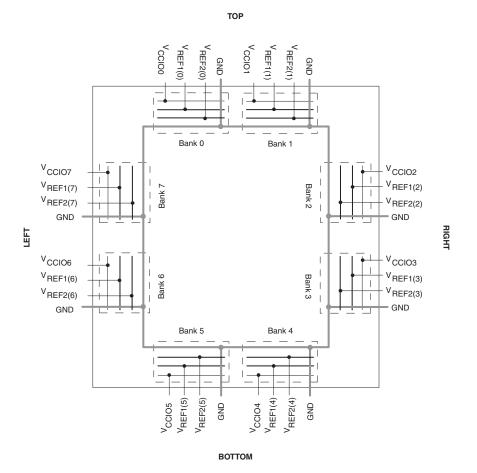

#### sysIO Buffer Banks

LatticeXP2 devices have eight sysIO buffer banks for user I/Os arranged two per side. Each bank is capable of supporting multiple I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , that allow it to be completely independent from the others. Figure 2-32 shows the eight banks and their associated supplies.

In LatticeXP2 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{\text{CCIO}}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{\text{CCIO}}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

Figure 2-32. LatticeXP2 Banks

LatticeXP2 devices contain two types of sysIO buffer pairs.

Top and Bottom (Banks 0, 1, 4 and 5) syslO Buffer Pairs (Single-Ended Outputs Only)

The syslO buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have programmable PCI clamps.

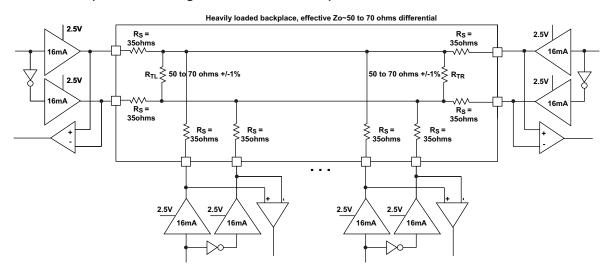

2. Left and Right (Banks 2, 3, 6 and 7) sysIO Buffer Pairs (50% Differential and 100% Single-Ended Outputs) The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp pad is associated with the negative side of the differential I/O.

LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

### Typical sysIO I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC, V_{CCCONFIG}}(V_{CCIO7})$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. During power up and before the FPGA core logic becomes active, all user I/Os will be high-impedance with weak pull-up. Please refer to TN1136, <u>LatticeXP2 sysIO Usage Guide</u> for additional information.

The  $V_{CC}$  and  $V_{CCAUX}$  supply the power to the FPGA core fabric, whereas the  $V_{CCIO}$  supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric.  $V_{CCIO}$  supplies should be powered-up before or together with the  $V_{CC}$  and  $V_{CCAUX}$  supplies.

#### Supported sysIO Standards

The LatticeXP2 sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2V, 1.5V, 1.8V, 2.5V and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, MLVDS, BLVDS, LVPECL, RSDS, differential SSTL and differential HSTL. Tables 2-12 and 2-13 show the I/O standards (together with their supply and reference voltages) supported by LatticeXP2 devices. For further information on utilizing the sysIO buffer to support a variety of standards please see TN1136, LatticeXP2 sysIO Usage Guide.

Table 2-12. Supported Input Standards

| Input Standard                   | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> ¹ (Nom.) |

|----------------------------------|-------------------------|----------------------------|

| Single Ended Interfaces          |                         |                            |

| LVTTL                            | _                       | _                          |

| LVCMOS33                         | _                       | _                          |

| LVCMOS25                         | <del>-</del>            | _                          |

| LVCMOS18                         | <del>-</del>            | 1.8                        |

| LVCMOS15                         | _                       | 1.5                        |

| LVCMOS12                         | <del>-</del>            | _                          |

| PCI33                            | _                       | _                          |

| HSTL18 Class I, II               | 0.9                     | _                          |

| HSTL15 Class I                   | 0.75                    | _                          |

| SSTL33 Class I, II               | 1.5                     | _                          |

| SSTL25 Class I, II               | 1.25                    | _                          |

| SSTL18 Class I, II               | 0.9                     | _                          |

| Differential Interfaces          |                         |                            |

| Differential SSTL18 Class I, II  | _                       | _                          |

| Differential SSTL25 Class I, II  | <del>-</del>            | _                          |

| Differential SSTL33 Class I, II  | <del>-</del>            | _                          |

| Differential HSTL15 Class I      | _                       | _                          |

| Differential HSTL18 Class I, II  | <del>-</del>            | _                          |

| LVDS, MLVDS, LVPECL, BLVDS, RSDS | _                       | _                          |

<sup>1.</sup> When not specified, V<sub>CCIO</sub> can be set anywhere in the valid operating range (page 3-1).

Table 2-13. Supported Output Standards

| Output Standard                  | Drive                      | V <sub>CCIO</sub> (Nom.) |

|----------------------------------|----------------------------|--------------------------|

| Single-ended Interfaces          |                            |                          |

| LVTTL                            | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

| LVCMOS33                         | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                      |

| LVCMOS25                         | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                      |

| LVCMOS18                         | 4mA, 8mA, 12mA, 16mA       | 1.8                      |

| LVCMOS15                         | 4mA, 8mA                   | 1.5                      |

| LVCMOS12                         | 2mA, 6mA                   | 1.2                      |

| LVCMOS33, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  | _                        |

| LVCMOS25, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  | _                        |

| LVCMOS18, Open Drain             | 4mA, 8mA, 12mA 16mA        | _                        |

| LVCMOS15, Open Drain             | 4mA, 8mA                   | _                        |

| LVCMOS12, Open Drain             | 2mA, 6mA                   | _                        |

| PCI33                            | N/A                        | 3.3                      |

| HSTL18 Class I, II               | N/A                        | 1.8                      |

| HSTL15 Class I                   | N/A                        | 1.5                      |

| SSTL33 Class I, II               | N/A                        | 3.3                      |

| SSTL25 Class I, II               | N/A                        | 2.5                      |

| SSTL18 Class I, II               | N/A                        | 1.8                      |

| Differential Interfaces          |                            |                          |

| Differential SSTL33, Class I, II | N/A                        | 3.3                      |

| Differential SSTL25, Class I, II | N/A                        | 2.5                      |

| Differential SSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL15, Class I     | N/A                        | 1.5                      |

| LVDS <sup>1, 2</sup>             | N/A                        | 2.5                      |

| MLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| BLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| LVPECL1                          | N/A                        | 3.3                      |

| RSDS <sup>1</sup>                | N/A                        | 2.5                      |

| LVCMOS33D1                       | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

<sup>1.</sup> Emulated with external resistors.

### Hot Socketing

LatticeXP2 devices have been carefully designed to ensure predictable behavior during power-up and power-down. Power supplies can be sequenced in any order. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the LatticeXP2 ideal for many multiple power supply and hot-swap applications.

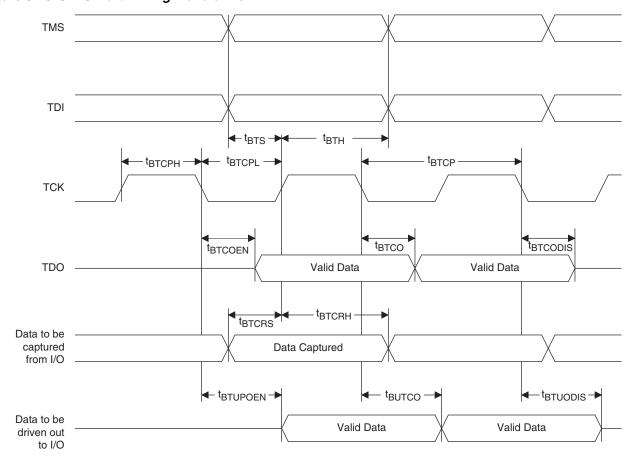

# **IEEE 1149.1-Compliant Boundary Scan Testability**

All LatticeXP2 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in

<sup>2.</sup> On the left and right edges, LVDS outputs are supported with a dedicated differential output driver on 50% of the I/Os. This solution does not require external resistors at the driver.

and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage V<sub>CCJ</sub> and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards. For more information, please see TN1141, <u>LatticeXP2 sysCONFIG Usage Guide</u>.

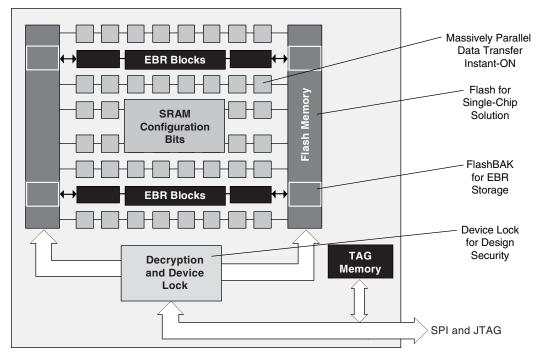

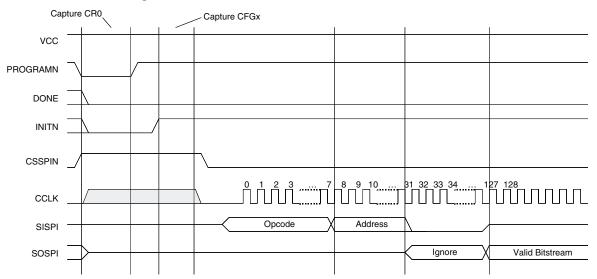

### flexiFLASH Device Configuration

The LatticeXP2 devices combine Flash and SRAM on a single chip to provide users with flexibility in device programming and configuration. Figure 2-33 provides an overview of the arrangement of Flash and SRAM configuration cells within the device. The remainder of this section provides an overview of these capabilities. See TN1141, <a href="LatticeXP2 sysCONFIG Usage Guide">LatticeXP2 sysCONFIG Usage Guide</a> for a more detailed description.

Figure 2-33. Overview of Flash and SRAM Configuration Cells Within LatticeXP2 Devices

At power-up, or on user command, data is transferred from the on-chip Flash memory to the SRAM configuration cells that control the operation of the device. This is done with massively parallel buses enabling the parts to operate within microseconds of the power supplies reaching valid levels; this capability is referred to as Instant-On.

The on-chip Flash enables a single-chip solution eliminating the need for external boot memory. This Flash can be programmed through either the JTAG or Slave SPI ports of the device. The SRAM configuration space can also be infinitely reconfigured through the JTAG and Master SPI ports. The JTAG port is IEEE 1149.1 and IEEE 1532 compliant.

As described in the EBR section of the data sheet, the FlashBAK capability of the parts enables the contents of the EBR blocks to be written back into the Flash storage area without erasing or reprogramming other aspects of the device configuration. Serial TAG memory is also available to allow the storage of small amounts of data such as calibration coefficients and error codes.

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM only FPGAs. This is further enhanced by device locking. The device can be in one of three modes:

- Unlocked

- Key Locked Presenting the key through the programming interface allows the device to be unlocked.

- 3. Permanently Locked The device is permanently locked.

To further complement the security of the device a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash portion of the device.

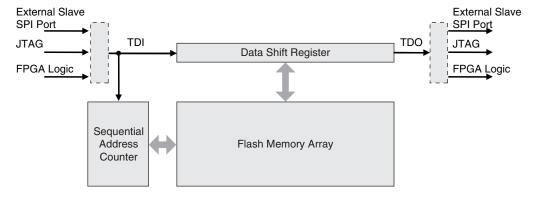

### **Serial TAG Memory**

LatticeXP2 devices offer 0.6 to 3.3kbits of Flash memory in the form of Serial TAG memory. The TAG memory is an area of the on-chip Flash that can be used for non-volatile storage including electronic ID codes, version codes, date stamps, asset IDs and calibration settings. A block diagram of the TAG memory is shown in Figure 2-34. The TAG memory is accessed in the same way as external SPI Flash and it can be read or programmed either through JTAG, an external Slave SPI Port, or directly from FPGA logic. To read the TAG memory, a start address is specified and the entire TAG memory contents are read sequentially in a first-in-first-out manner. The TAG memory is independent of the Flash used for device configuration and given its use for general-purpose storage functions is always accessible regardless of the device security settings. For more information, see TN1137, LatticeXP2 Memory Usage Guide and TN1141, LatticeXP2 sysCONFIG Usage Guide.

Figure 2-34. Serial TAG Memory Diagram

#### **Live Update Technology**

Many applications require field updates of the FPGA. LatticeXP2 devices provide three features that enable this configuration to be done in a secure and failsafe manner while minimizing impact on system operation.

#### 1. Decryption Support

LatticeXP2 devices provide on-chip, non-volatile key storage to support decryption of a 128-bit AES encrypted bitstream, securing designs and deterring design piracy.

#### 2. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. For more information please see TN1087, Minimizing System Interruption During Configuration Using TransFR Technology.

#### 3. **Dual Boot Image Support**

Dual boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeXP2 can be re-booted from this new configuration file. If there is a problem such as corrupt data during download or incorrect version number with this new boot image, the LatticeXP2 device can revert back to the

original backup configuration and try again. This all can be done without power cycling the system. For more information please see TN1220, <u>LatticeXP2 Dual Boot Feature</u>.

For more information on device configuration, please see TN1141, <u>LatticeXP2 sysCONFIG Usage Guide</u>.

### **Soft Error Detect (SED) Support**

LatticeXP2 devices have dedicated logic to perform Cyclic Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, LatticeXP2 devices can be programmed for checking soft errors in SRAM. SED can be run on a programmed device when the user logic is not active. In the event a soft error occurs, the device can be programmed to either reload from a known good boot image (from internal Flash or external SPI memory) or generate an error signal.

For further information on SED support, please see TN1130, LatticeXP2 Soft Error Detection (SED) Usage Guide.

#### **On-Chip Oscillator**

Every LatticeXP2 device has an internal CMOS oscillator that is used to derive a Master Clock (CCLK) for configuration. The oscillator and CCLK run continuously and are available to user logic after configuration is complete. The available CCLK frequencies are listed in Table 2-14. When a different CCLK frequency is selected during the design process, the following sequence takes place:

- 1. Device powers up with the default CCLK frequency.

- 2. During configuration, users select a different CCLK frequency.

- 3. CCLK frequency changes to the selected frequency after clock configuration bits are received.

This internal CMOS oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, please see TN1141, <u>LatticeXP2 sysCON-FIG Usage Guide</u>.

Table 2-14. Selectable CCLKs and Oscillator Frequencies During Configuration and User Mode

| CCLK/Oscillator (MHz) |

|-----------------------|

| 2.5 <sup>1</sup>      |

| 3.1 <sup>2</sup>      |

| 4.3                   |

| 5.4                   |

| 6.9                   |

| 8.1                   |

| 9.2                   |

| 10                    |

| 13                    |

| 15                    |

| 20                    |

| 26                    |

| 32                    |

| 40                    |

| 54                    |

| 80 <sup>3</sup>       |

| 163³                  |

- 1. Software default oscillator frequency.

- 2. Software default CCLK frequency.

- 3. Frequency not valid for CCLK.

# **Density Shifting**

The LatticeXP2 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# LatticeXP2 Family Data Sheet DC and Switching Characteristics

September 2014 Data Sheet DS1009

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage $V_{CC}$ 0.5 to 1.32V                              |

|-------------------------------------------------------------------|

| Supply Voltage $V_{CCAUX}$ 0.5 to 3.75V                           |

| Supply Voltage $V_{CCJ}$ 0.5 to 3.75V                             |

| Supply Voltage $V_{\mbox{CCPLL}^4}00.5$ to 3.75V                  |

| Output Supply Voltage $V_{CCIO}$ 0.5 to 3.75V                     |

| Input or I/O Tristate Voltage Applied $^5,\ldots,-0.5$ to $3.75V$ |

| Storage Temperature (Ambient)65 to 150 $^{\circ}\text{C}$         |

| Junction Temperature Under Bias (Tj)+125°C                        |

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4.  $V_{CCPLL}$  only available on csBGA, PQFP and TQFP packages.

- 5. Overshoot and undershoot of -2V to  $(V_{IHMAX} + 2)$  volts is permitted for a duration of <20 ns.

# **Recommended Operating Conditions**

| Symbol                               | Parameter                                       | Min.  | Max.  | Units |

|--------------------------------------|-------------------------------------------------|-------|-------|-------|

| V <sub>CC</sub>                      | Core Supply Voltage                             | 1.14  | 1.26  | V     |

| V <sub>CCAUX</sub> <sup>4, 5</sup>   | Auxiliary Supply Voltage                        | 3.135 | 3.465 | V     |

| V <sub>CCPLL</sub> <sup>1</sup>      | PLL Supply Voltage                              | 3.135 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>2, 3, 4</sup> | I/O Driver Supply Voltage                       | 1.14  | 3.465 | V     |

| V <sub>CCJ</sub> <sup>2</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature, Commercial Operation      | 0     | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature, Industrial Operation      | -40   | 100   | °C    |

- 1.  $V_{CCPLL}$  only available on csBGA, PQFP and TQFP packages.

- If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC</sub>. If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

- 3. See recommended voltages by I/O standard in subsequent table.

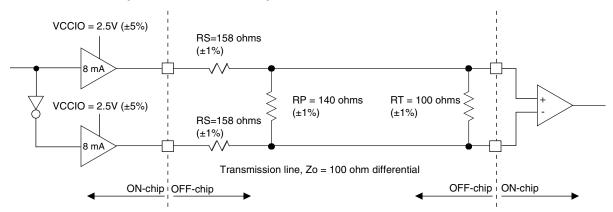

- 4. To ensure proper I/O behavior,  $V_{CCIO}$  must be turned off at the same time or earlier than  $V_{CCAUX}$ .