www.ti.com

SNLS171G - JANUARY 2005 - REVISED APRIL 2013

# SCANSTA476 Eight Input IEEE 1149.1 Analog Voltage Monitor

Check for Samples: SCANSTA476

## FEATURES

- Eight Selectable Analog Input Channels

- Analog Full-Scale Input Range 0V to V<sub>DD</sub>

- Typical Accuracy of 2 mV at Maximum V<sub>DD</sub>

- Very Low Power Operation

- Small Package Footprint in 16-Lead, 5 x 5 x 0.8 mm WSON

- Single +2.7V to +5.5V Supply Operation

- IEEE 1149.1 (JTAG) Compliant Interface

# **APPLICATIONS**

- Measurement of Point Voltages

- Real-time Signal Monitoring

- System Health Monitoring and Prognostics

- Debug, Environmental Test, Production Test, Field Service

- Supplement In-Circuit Tester (ICT) Access

- Vital in Servers, Computing, Telecommunication and Industrial Equipment

- Essential in Medical, Data Storage, and Networking Equipment

# DESCRIPTION

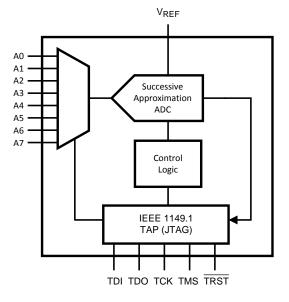

The SCANSTA476 is a low power, Analog Voltage Monitor used for sampling or monitoring up to 8 analog/mixed-signal input channels. Analog Voltage Monitors are valuable during product development, environmental test, production, and field service for verifying and monitoring power supply and reference voltages. In a supervisory role, the 'STA476 is useful for card or system-level health monitoring and prognostics applications.

Instead of requiring an external microcontroller with a GPIO interface, the 'STA476 features a common IEEE 1149.1 (JTAG) interface to select the analog input, initiate a measurement, and access the results - further extending the capabilities of an existing JTAG infrastructure.

The SCANSTA476 uses the V<sub>REF</sub> input as a reference. This enables the SCANSTA476 to operate with a full-scale input range of 0 to V<sub>DD</sub>, which can range from +2.7V to +5.5V.

The SCANSTA476 is packaged in a 16-lead nonpullback WSON package that provides an extremely small footprint for applications where space is a critical consideration. This product operates over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

## **Block Diagram**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners. SNLS171G - JANUARY 2005 - REVISED APRIL 2013

www.ti.com

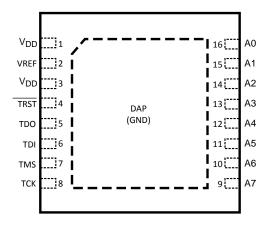

### **Connection Diagram**

Figure 1. DAP = GND (Top View)

### **Pin Descriptions**

| Pin No.                                                                                                                                                                                                                                                         | Symbol          | Description                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| ANALOG I/O                                                                                                                                                                                                                                                      | •               |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 16                                                                                                                                                                                                                                                              | A0              | Analog input 0. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 15                                                                                                                                                                                                                                                              | A1              | Analog input 1. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 14                                                                                                                                                                                                                                                              | A2              | Analog input 2. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 13                                                                                                                                                                                                                                                              | A3              | Analog input 3. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 12                                                                                                                                                                                                                                                              | A4              | Analog input 4. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 11                                                                                                                                                                                                                                                              | A5              | Analog input 5. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 10                                                                                                                                                                                                                                                              | A6              | Analog input 6. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 9                                                                                                                                                                                                                                                               | A7              | Analog input 7. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 2 $V_{REF}$ Analog reference voltage input. $V_{REF}$ must be $\leq V_{DD}$ . This pin should be connected to a quiet source (not directly to $V_{DD}$ ) and bypassed to GND with 0.1 µF and 1 µF monolithic capacitors located within cm of the $V_{REF}$ pin. |                 |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| DIGITAL I/O                                                                                                                                                                                                                                                     |                 |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 6                                                                                                                                                                                                                                                               | TDI             | Test Data Input to support IEEE 1149.1 features                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 5                                                                                                                                                                                                                                                               | TDO             | Test Data Ouput to support IEEE 1149.1 features                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 7                                                                                                                                                                                                                                                               | TMS             | Test Mode Select to support IEEE 1149.1 features                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 8                                                                                                                                                                                                                                                               | ТСК             | Test Clock to support IEEE 1149.1 features                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 4                                                                                                                                                                                                                                                               | TRST            | Test Reset to support IEEE 1149.1 features                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| POWER SUP                                                                                                                                                                                                                                                       | PLY             |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 1,3                                                                                                                                                                                                                                                             | V <sub>DD</sub> | Positive supply pin. These pins should be connected to a quiet +2.7V to +5.5V source and bypassed to GND with 0.1 $\mu$ F and 1 $\mu$ F monolithic capacitors located within 1 cm of the power pin.                                                                                  |  |  |  |  |  |  |  |

| See <sup>(1)</sup>                                                                                                                                                                                                                                              | GND             | Ground reference for CMOS circuitry. DAP is the exposed metal contact at the bottom of the WSON package. The DAP is used as the primary GND connection to the device. It should be connected to the ground plane with at least 4 vias for optimal low-noise and thermal performance. |  |  |  |  |  |  |  |

(1) Note that GND is not an actual pin on the package, the GND is connected thru the DAP on the back side of the WSON package.

www.ti.com

SNLS171G – JANUARY 2005 – REVISED APRIL 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings (1)(2)

| Supply Voltage V <sub>DD</sub>          |                  | -0.3V to +6.5V                 |

|-----------------------------------------|------------------|--------------------------------|

| Voltage on Any Analog Pin to C          | GND              | -0.3V to V <sub>DD</sub> +0.3V |

| /oltage on Any Digital Pin to GND -0.   |                  |                                |

| Input Current at Any Pin <sup>(3)</sup> |                  | ±10 mA                         |

| ESD Susceptibility                      | Human Body Model | 8000V                          |

|                                         | Machine Model    | >250V                          |

| Soldering Temperature                   |                  | Refer to AN-1187 (SNOA401)     |

| Junction Temperature                    |                  | +150°C                         |

| Storage Temperature                     |                  | -65°C to +150°C                |

| Thermal Resistance, $\theta_{JA}$       |                  | 42°C/W                         |

| Thermal Resistance, $\theta_{JC}$       |                  | 14.3°C/W                       |

(1) Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not implied. Exposure to maximum ratings for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

(3) Except power supply pins.

## **Recommended Operating Conditions**

| Operating Temperature Range                    | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ |

|------------------------------------------------|-------------------------------------------|

| V <sub>DD</sub> Supply Voltage                 | +2.7V to +5.5V                            |

| Digital Input Pins Voltage Range               | +0V to V <sub>DD</sub>                    |

| Analog Input Pins Voltage Range <sup>(1)</sup> | +0V to V <sub>REF</sub>                   |

(1) For valid measurements, the analog  $V_{IN} < V_{REF} \le V_{DD}$ .

## **SCANSTA476 Electrical Characteristics**

The following specifications apply for  $V_{DD}$  = +2.7V to 5.5V,  $f_{TCK}$  = 20 MHz, unless otherwise noted.

| Symbol            | Parameter                                       | Conditions                                              | Typical | Limits                | Units    |  |

|-------------------|-------------------------------------------------|---------------------------------------------------------|---------|-----------------------|----------|--|

| POWER             | SUPPLY CHARACTERISTICS                          |                                                         | I       |                       |          |  |

| N/                | Cummbe Malta an                                 | 10°0 < T < 05°0                                         |         | 2.7                   | V (min)  |  |

| V <sub>DD</sub>   | Supply Voltage                                  | $-40^{\circ}C \le T_A \le 85^{\circ}C$                  |         | 5.5                   | V (max)  |  |

|                   | Normal Mode (Static)                            | $V_{DD} = +2.7V$ to +5.5V,                              | 3.5     | 5.0                   | mA       |  |

| I <sub>DD</sub>   | Normal Mode (Operational)                       | $V_{DD}$ = +2.7V to +5.5V,<br>f <sub>TCK</sub> = 1 MSPS |         | 5.0                   | mA (max) |  |

| P <sub>D</sub>    | Power Consumption, Normal Mode<br>(Operational) | V <sub>DD</sub> = +5.5V, f <sub>TCK</sub> = 1 MSPS      |         | 27.5                  | mW (max) |  |

| ANALOG            | INPUT CHARACTERISTICS (A0-A7)                   |                                                         |         |                       |          |  |

| V <sub>IN</sub>   | Analog Input Range                              | $V_{REF} \le V_{DD}$                                    |         | 0 to V <sub>REF</sub> | V        |  |

| V <sub>REF</sub>  | Reference Voltage Range                         |                                                         |         | V <sub>DD</sub>       | V        |  |

| I <sub>DCL</sub>  | DC Leakage Current                              |                                                         | 0.1     | ±10                   | µA (max) |  |

| V                 | Appleg Input Measurement Assures                | V <sub>DD</sub> = +2.7V                                 | 1       | 7.5                   | mV       |  |

| V <sub>MEAS</sub> | Analog Input Measurement Accuracy               | V <sub>DD</sub> = +5.5V                                 | 2       | 15                    | INV      |  |

| DIGITAL           | INPUT CHARACTERISTICS (TDI, TMS, T              | ICK, TRST)                                              |         |                       |          |  |

| V                 | Input High Voltage                              | $V_{DD} = +2.7V$ to $+3.6V$                             |         | 2.0                   | V (min)  |  |

| V <sub>IH</sub>   | Input Figh Voltage                              | V <sub>DD</sub> = +5.5V                                 |         | 2.1                   | v (mm)   |  |

| V <sub>IL</sub>   | Input Low Voltage                               | $V_{DD} = +5V$                                          |         | 0.8                   | V (max)  |  |

| V <sub>CL</sub>   | Input Clamp Voltage                             | I <sub>CL</sub> = -18mA                                 | -0.8    | -1.5                  | V (max)  |  |

| I <sub>IN</sub>   | Input Current                                   | $V_{IN} = 0V \text{ or } V_{DD}$                        | 0.2     | ±10                   | µA (max) |  |

Copyright © 2005–2013, Texas Instruments Incorporated

SNLS171G - JANUARY 2005 - REVISED APRIL 2013

www.ti.com

**NSTRUMENTS**

**EXAS**

## SCANSTA476 Electrical Characteristics (continued)

The following specifications apply for  $V_{DD}$  = +2.7V to 5.5V,  $f_{TCK}$  = 20 MHz, unless otherwise noted.

| Symbol            | Parameter                    | Conditions                                                                                | Typical | Limits               | Units      |

|-------------------|------------------------------|-------------------------------------------------------------------------------------------|---------|----------------------|------------|

| I <sub>ILR</sub>  | Input Current                | TRST, TDI, TMS only                                                                       |         | -300                 | µA (max)   |

| DIGITAL           | OUTPUT CHARACTERISTICS (TDO) |                                                                                           |         |                      |            |

|                   |                              | $I_{OH} = -100 \ \mu\text{A}, \ 2.7 \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{V}$ |         | V <sub>DD</sub> -0.2 | V (min)    |

| V <sub>OH</sub>   | Output High Voltage          | $I_{OH} = -4 \text{ mA}, 3.0 \text{V} \le \text{V}_{DD} \le 5.5 \text{V}$                 |         | 2.4                  | V (min)    |

|                   |                              | $I_{OH} = -4 \text{ mA}, V_{DD} = 2.7 \text{V}$                                           |         | 2.2                  | V (min)    |

| V                 | Output Low Voltage           | $I_{OL} = 100 \ \mu\text{A}, \ 2.7\text{V} \leq \text{V}_{\text{DD}} \leq 5.5\text{V}$    |         | 0.2                  | V (max)    |

| V <sub>OL</sub>   | Output Low Voltage           | $I_{OL} = 4 \text{ mA}, 2.7 \text{V} \le \text{V}_{DD} \le 5.5 \text{V}$                  |         | 0.4                  | V (max)    |

| l <sub>os</sub>   | Output Short Circuit Current | $V_{OUT} = 0V, V_{DD} = 5.5V$                                                             |         | -85                  | mA (max)   |

| l <sub>oz</sub>   | TRI-STATE Leakage Current    |                                                                                           |         | ±10                  | μA (max)   |

|                   | Output Coding                |                                                                                           | Stra    | aight (Natural)      | ) Binary   |

| AC ELEC           | TRICAL CHARACTERISTICS       |                                                                                           |         |                      |            |

| F <sub>MAX</sub>  | Throughput Rate              | TCK = 20MHz                                                                               |         | 1                    | MSPS (max) |

| INPUT TI          | MING CHARACTERISTICS         |                                                                                           |         |                      |            |

| t <sub>SET</sub>  | TDI to TCK (H/L)             | See <sup>(1)</sup>                                                                        |         | 2.0                  | ns (min)   |

| t <sub>HOLD</sub> | TDI to TCK (H/L)             | See <sup>(1)</sup>                                                                        |         | 1.5                  | ns (min)   |

| t <sub>SET</sub>  | TMS to TCK (H/L)             | See <sup>(1)</sup>                                                                        |         | 2.0                  | ns (min)   |

| t <sub>HOLD</sub> | TMS to TCK (H/L)             | See <sup>(1)</sup>                                                                        |         | 2.0                  | ns (min)   |

| t <sub>W</sub>    | TCK Pulse Width (H/L)        | See <sup>(1)</sup>                                                                        |         | 10.0                 | ns (min)   |

| t <sub>REC</sub>  | Recovery Time TRST to TCK    | See <sup>(1)</sup>                                                                        |         | 2.0                  | ns (min)   |

| t <sub>W</sub>    | TRST Pulse Width (L)         | See <sup>(1)</sup>                                                                        |         | 2.5                  | ns (min)   |

| F <sub>MAX</sub>  | тск                          |                                                                                           |         | 20                   | MHz (min)  |

(1) Data sheet min/max specification limits are specified by design or statistical analysis.

# **APPLICATIONS INFORMATION**

## **POWER-UP TIMING**

The SCANSTA476 typically requires 1  $\mu$ s to power up, either after first applying V<sub>DD</sub>, or after an incomplete conversion shift. To return to normal, one "dummy" conversion must be fully completed. After this first dummy conversion, the SCANSTA476 will perform conversions properly.

## STARTUP MODE

When the V<sub>DD</sub> supply is first applied, the SCANSTA476 requires one dummy conversion after start-up.

#### www.ti.com

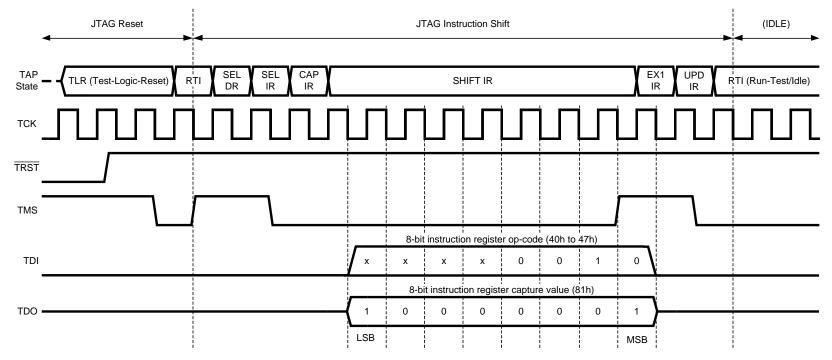

## **Timing Diagrams**

Op-codes 40h to 47h select pins A0 to A7 respectively.

Note the JTAG reset preamble places the JTAG TAP controller in a stable state (RTI). Both the instruction and data shifts start in - and return to - the RTI state

Figure 2. Instruction Shift (Channel Select)

# SCANSTA476

www.ti.com

#### SNLS171G - JANUARY 2005 - REVISED APRIL 2013

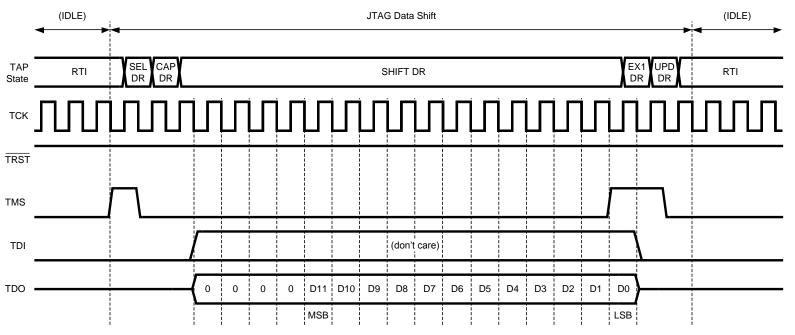

D11 through D0 correspond to the 12-bit sample from the ADC Core.

Note that Data shifts can be run back-to-back for continous sampling of a single channel, or can be interleaved with instruction shifts for rippling through all 8 channels.

Figure 3. Data Shift (A/D Sample)

Page

www.ti.com

SNLS171G - JANUARY 2005 - REVISED APRIL 2013

| • | Changed layout of National Data Sheet to TI format | 6 |

|---|----------------------------------------------------|---|

6-Feb-2020

# PACKAGING INFORMATION

| Orderable Device   | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|--------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                    | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| SCANSTA476TSD/NOPB | ACTIVE | WSON         | NHQ     | 16   | 1000    | Green (RoHS<br>& no Sb/Br) | SN               | Level-3-260C-168 HR | -40 to 85    | STA476T        | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

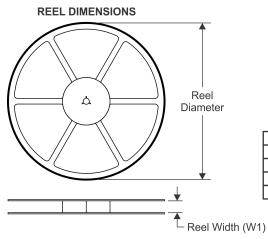

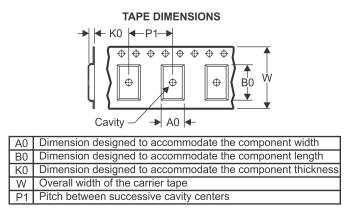

# TAPE AND REEL INFORMATION

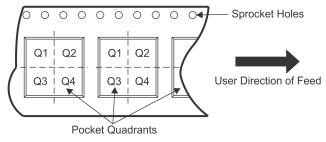

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| SCANSTA476TSD/NOPB          | WSON | NHQ                | 16 | 1000 | 178.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

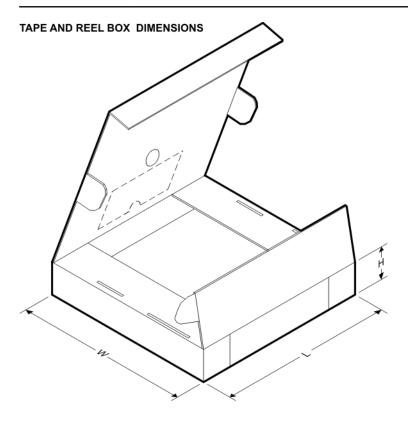

# PACKAGE MATERIALS INFORMATION

20-Sep-2016

\*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SCANSTA476TSD/NOPB | WSON         | NHQ             | 16   | 1000 | 210.0       | 185.0      | 35.0        |

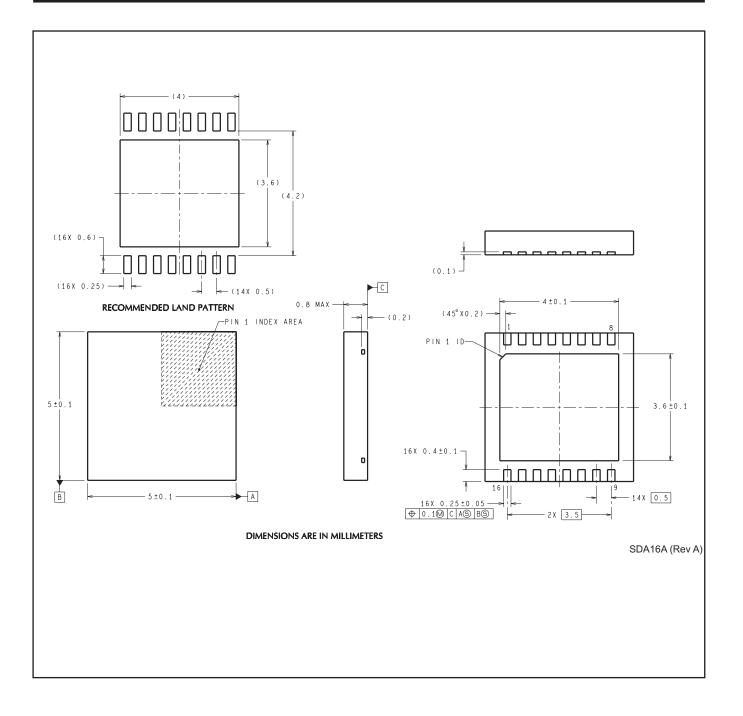

# **MECHANICAL DATA**

# NHQ0016A

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated