SBAS551 - JUNE 2011

# 24-Bit, 192-kHz Sampling, Enhanced Multi-Level $\Delta \Sigma$ , **Eight-Channel Audio Digital-to-Analog Converter**

Check for Samples: PCM1690-Q1

### FEATURES

- **Qualified for Automotive Applications**

- 24-Bit Delta-Sigma DAC

- 8-Channel DAC:

- High Performance: Differential, f<sub>S</sub> = 48 kHz

- THD+N: -94 dB

- SNR: 113 dB

- Dynamic Range: 113 dB

- Sampling Rate: 8 kHz to 192 kHz

- System Clock: 128 f<sub>S</sub>, 192 f<sub>S</sub>, 256 f<sub>S</sub>, 384 f<sub>S</sub>, 512 f<sub>S</sub>, 768 f<sub>S</sub>, 1152 f<sub>S</sub>

- Differential Voltage Output: 8 V<sub>PP</sub>

- Analog Low-Pass Filter Included

- 4x/8x Oversampling Digital Filter:

- Passband Ripple: ±0.0018 dB

- Stop Band Attenuation: –75 dB

- Zero Flag

- Flexible Audio Interface:

- I/F Format: I<sup>2</sup>S<sup>™</sup>, Left-/Right-Justified, DSP, TDM

- Data Length: 16, 20, 24, 32 Bits

- **Flexible Mode Control:**

- 3-Wire SPI<sup>™</sup>, 2-Wire I<sup>2</sup>C<sup>™</sup>-Compatible Serial Control Interface, or Hardware Control

- Multi Functions via SPI or I<sup>2</sup>C I/F:

- Audio I/F Format Select: I<sup>2</sup>S, Left-Justified, **Right-Justified, DSP, TDM**

- Digital Attenuation and Soft Mute

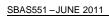

- Digital De-Emphasis: 32 kHz, 44.1 kHz, 48 kHz

- Data Polarity Control

- Power Down

- Multi Functions via H/W Control:

- Audio I/F Format Select: I<sup>2</sup>S, TDM

- Digital De-Emphasis Filter: 44.1 kHz

- Analog Mute by Clock Halt Detection

- **External RESET Pin**

- **Power Supplies:**

- 5 V for Analog and 3.3 V for Digital

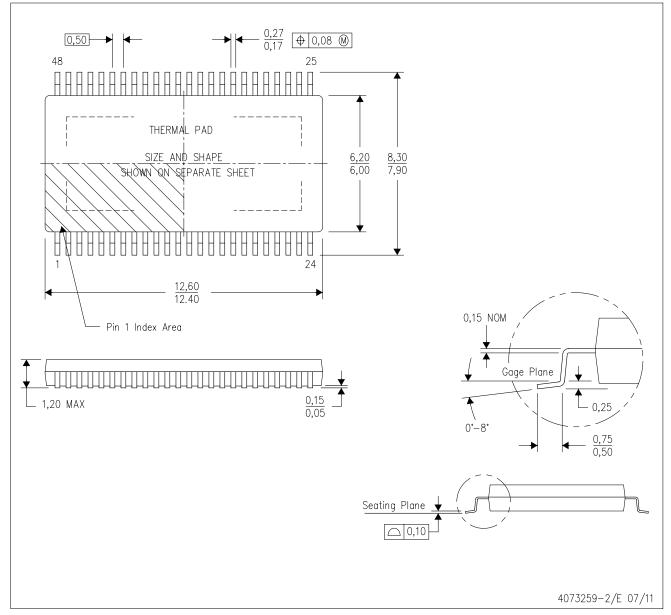

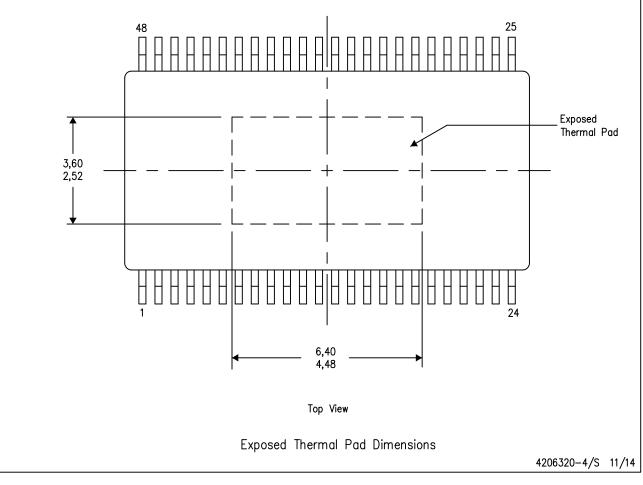

- Package: HTSSOP-48

- **Operating Temperature Range:**

- –40°C to +85°C

### APPLICATIONS

- Blu-ray<sup>™</sup> DVD Players

- **HD DVD Players**

- **AV Receivers**

- Home Theaters

- **Car Audio External Amplifiers**

- **Car Audio AVN Applications**

### DESCRIPTION

The PCM1690-Q1 is a high-performance, single-chip, 24-bit, eight-channel, audio digital-to-analog converter (DAC) with differential outputs. The eight-channel, 24-bit DAC employs an enhanced, multi-level delta-sigma ( $\Delta\Sigma$ ) modulator and supports 8-kHz to 192-kHz sampling rates and a 16-/20-/24-/32-bit width digital audio input word on the audio interface. The audio interface of the PCM1690-Q1 supports the time-division-multiplexed (TDM) format in addition to the standard I<sup>2</sup>S, left-justified, right-justified, and DSP formats.

The PCM1690-Q1 can be controlled through a three-wire, SPI-compatible interface, or two-wire, I<sup>2</sup>C-compatible serial interface in software, which provides access to all functions including digital attenuation, soft mute, de-emphasis, and so forth. Also, hardware control mode provides a subset of user-programmable functions through two control pins. The PCM1690-Q1 is available in a 12-mm × 8-mm (12-mm × 6-mm body) HTSSOP-48 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Blu-ray is a trademark of Blu-ray Disk Association.

SPI is a trademark of Motorola.

I<sup>2</sup>S, I<sup>2</sup>C are trademarks of NXP Semiconductors.

All other trademarks are the property of their respective owners.

# PCM1690-Q1

SBAS551 - JUNE 2011

#### www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

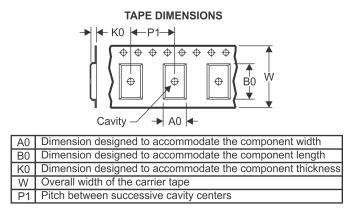

|            | ORDERING INFORMATION'' |                       |                                   |                    |                    |                              |  |  |  |  |  |  |

|------------|------------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|--|--|--|--|--|--|

| PRODUCT    | PACKAGE-<br>LEAD       | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |  |  |  |  |  |  |

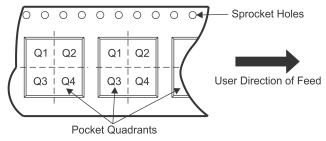

| PCM1690-Q1 | HTSSOP-48              | DCA                   | –40°C to +85°C                    | PCM1690Q           | PCM1690IDCARQ<br>1 | Tape and Reel, 2000          |  |  |  |  |  |  |

### ODDEDING INFORMATION(1)

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

| PARAMETER                                                           | PCM1690-Q1                 | UNIT |

|---------------------------------------------------------------------|----------------------------|------|

| Supply voltage: VCC1, VCC2                                          | -0.3 to +6.5               | V    |

| Supply voltage: VDD                                                 | -0.3 to +4.0               | V    |

| Ground voltage differences: AGND1, AGND2, DGND                      | ±0.1                       | V    |

| Supply voltage differences: VCC1, VCC2                              | ±0.1                       | V    |

| Digital input voltage: RST, TEST, MS, MC, MD, SCKI, AMUTEI, AMUTEO  | –0.3 to +6.5               | V    |

| Digital input voltage:<br>BCK, LRCK, DIN1/2/3/4, MODE, ZERO1, ZERO2 | -0.3 to (VDD + 0.3) < +4.0 | V    |

| Analog input voltage: VCOM, VOUT1-8±                                | -0.3 to (VCC + 0.3) < +6.5 | V    |

| Input current (all pins except supplies)                            | ±10                        | mA   |

| Ambient temperature under bias                                      | -40 to +125                | °C   |

| Storage temperature                                                 | -55 to +150                | °C   |

| Junction temperature                                                | +150                       | °C   |

| Lead temperature (soldering, 5s)                                    | +260                       | °C   |

| Package temperature (IR reflow, peak)                               | +260                       | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings (1) only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted).

|                                 |                              |       | PCM1690-Q1    |        |                 |

|---------------------------------|------------------------------|-------|---------------|--------|-----------------|

| Р                               | ARAMETER                     | MIN   | TYP           | MAX    | UNIT            |

| Analog supply voltage, VCC      |                              | 4.5   | 5.0           | 5.5    | V               |

| Digital supply voltage, VDD     |                              | 3.0   | 3.3           | 3.6    | V               |

| Digital Interface               |                              | L     | VTTL compatil | ble    |                 |

|                                 | Sampling frequency, LRCK     | 8     |               | 192    | kHz             |

| Digital input clock frequency   | System clock frequency, SCKI | 2.048 |               | 36.864 | MHz             |

| Analog output voltage           | Differential                 |       | 8             |        | V <sub>PP</sub> |

| Analog output load registeres   | To ac-coupled GND            | 5     |               |        | kΩ              |

| Analog output load resistance   | To dc-coupled GND            | 15    |               |        | kΩ              |

| Analog output load capacitance  |                              |       |               | 50     | pF              |

| Digital output load capacitance |                              |       |               | 20     | pF              |

| Operating free-air temperature  | PCM1690-Q1 consumer grade    | -40   | +25           | +85    | °C              |

www.ti.com

#### **ELECTRICAL CHARACTERISTICS: Digital Input/Output**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

|                                |                                               |                                                                                                                                                      | PCM1690-Q1<br>MIN TYP MAX          |                   |         |      |

|--------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|---------|------|

| PARAMETER                      |                                               | TEST CONDITIONS                                                                                                                                      |                                    |                   | MAX     | UNIT |

| DATA FORMAT                    |                                               |                                                                                                                                                      |                                    |                   |         |      |

| Audio data interface format    |                                               |                                                                                                                                                      | I <sup>2</sup> S, LJ, RJ, DSP, TDM |                   |         |      |

| Audio data word length         |                                               |                                                                                                                                                      |                                    | 16, 20, 24,<br>32 |         | Bits |

| Audio data format              |                                               |                                                                                                                                                      | MSB f                              | irst, twos comp   | olement |      |

| Sampling frequency             | f <sub>S</sub>                                |                                                                                                                                                      | 8                                  | 48                | 192     | kHz  |

| System clock frequency         |                                               | 128 f <sub>S</sub> , 192 f <sub>S</sub> , 256 f <sub>S</sub> ,<br>384 f <sub>S</sub> , 512 f <sub>S</sub> , 768 f <sub>S</sub> , 1152 f <sub>S</sub> | 2.048                              |                   | 36.864  | MHz  |

| INPUT LOGIC                    |                                               |                                                                                                                                                      |                                    |                   |         |      |

| Innut logic lovel              | V <sub>IH</sub> <sup>(1)</sup> <sup>(2)</sup> |                                                                                                                                                      | 2.0                                |                   | VDD     | VDC  |

| Input logic level              | V <sub>IL</sub> <sup>(1)</sup> <sup>(2)</sup> |                                                                                                                                                      |                                    |                   | 0.8     | VDC  |

|                                | V <sub>IH</sub> <sup>(3) (4)</sup>            |                                                                                                                                                      | 2.0                                |                   | 5.5     | VDC  |

| Input logic level              | V <sub>IL</sub> <sup>(3)</sup> <sup>(4)</sup> |                                                                                                                                                      |                                    |                   | 0.8     | VDC  |

|                                | I <sub>IH</sub> <sup>(2)</sup> <sup>(3)</sup> | V <sub>IN</sub> = VDD                                                                                                                                |                                    |                   | ±10     | μA   |

| Input logic current            | I <sub>IL</sub> <sup>(2)</sup> <sup>(3)</sup> | V <sub>IN</sub> = 0 V                                                                                                                                |                                    |                   | ±10     | μA   |

| Input logic ourrent            | I <sub>IH</sub> <sup>(1) (4)</sup>            | $V_{IN} = VDD$                                                                                                                                       |                                    | +65               | +100    | μA   |

| Input logic current            | I <sub>IL</sub> <sup>(1)</sup> <sup>(4)</sup> | $V_{IN} = 0 V$                                                                                                                                       |                                    |                   | ±10     | μA   |

| OUTPUT LOGIC                   |                                               |                                                                                                                                                      |                                    |                   |         |      |

|                                | V <sub>OH</sub> <sup>(5)</sup>                | $I_{OUT} = -4 \text{ mA}$                                                                                                                            | 2.4                                |                   |         | VDC  |

| Output logic level             | V <sub>OL</sub> <sup>(5)</sup> <sup>(6)</sup> | $I_{OUT} = +4 \text{ mA}$                                                                                                                            |                                    |                   | 0.4     | VDC  |

| REFERENCE OUTPUT               |                                               |                                                                                                                                                      |                                    |                   |         |      |

| VCOM output voltage            |                                               |                                                                                                                                                      |                                    | 0.5 ×<br>VCC1     |         | V    |

| VCOM output impedance          |                                               |                                                                                                                                                      |                                    | 7.5               |         | kΩ   |

| Allowable VCOM output source/s | ink current                                   |                                                                                                                                                      |                                    |                   | 1       | μA   |

BCK and LRCK (Schmitt trigger input with 50-kΩ typical internal pull-down resistor).

DIN1/2/3/4 (Schmitt trigger input).

(2) (3)

SCKI, TEST/ADR1/RSV, MC/SCL/FMT, MD/SDA/DEMP, and AMUTEI (Schmitt trigger input, 5-V tolerant). RST and MS/ADR0/RSV (Schmitt trigger input with 50-k $\Omega$  typical internal pull-down resistor, 5-V tolerant). (4)

(5) (6) ZERO1 and ZERO2. SDA (I<sup>2</sup>C mode, open-drain low output) and AMUTEO (open-drain low output).

#### SBAS551 - JUNE 2011

#### **ELECTRICAL CHARACTERISTICS: DAC**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

|                                                        |            |                                                            | F                      | PCM1690-Q                                                                                                                                                                     | 1                      |                 |

|--------------------------------------------------------|------------|------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|

| PARAMETER                                              |            | TEST CONDITIONS                                            | MIN                    | TYP                                                                                                                                                                           | MAX                    | UNIT            |

| DAC CHARACTERISTICS                                    |            |                                                            |                        |                                                                                                                                                                               |                        |                 |

| Resolution                                             |            |                                                            | 16                     | 24                                                                                                                                                                            |                        | Bits            |

| DC ACCURACY                                            |            |                                                            |                        |                                                                                                                                                                               |                        |                 |

| Gain mismatch channel-to-channel                       |            |                                                            |                        | ±2.0                                                                                                                                                                          | ±6                     | % of FSR        |

| Gain error                                             |            |                                                            |                        | ±2.0                                                                                                                                                                          | ±6                     | % of FSR        |

| Bipolar zero error                                     |            |                                                            |                        | ±1.0                                                                                                                                                                          |                        | % of FSR        |

| DYNAMIC PERFORMANCE <sup>(1)</sup> <sup>(2)</sup>      |            |                                                            |                        |                                                                                                                                                                               |                        |                 |

|                                                        |            | $f_S = 48 \text{ kHz}, V_{OUT} = 0 \text{ dB}$             |                        | -94                                                                                                                                                                           | -88                    | dB              |

| Total harmonic distortion + noise                      | THD+N      | $f_S = 96 \text{ kHz}, V_{OUT} = 0 \text{ dB}$             |                        | -94                                                                                                                                                                           |                        | dB              |

|                                                        |            | $f_S = 192 \text{ kHz}, V_{OUT} = 0 \text{ dB}$            |                        | -94                                                                                                                                                                           |                        | dB              |

|                                                        |            | $f_S = 48 \text{ kHz}, \text{ EIAJ}, \text{ A-weighted}$   | 106                    | 113                                                                                                                                                                           |                        | dB              |

| Dynamic range                                          |            | $f_{S} = 96 \text{ kHz}, \text{ EIAJ}, \text{ A-weighted}$ |                        | 113                                                                                                                                                                           |                        | dB              |

|                                                        |            | $f_{S}$ = 192 kHz, EIAJ, A-weighted                        |                        | 113                                                                                                                                                                           |                        | dB              |

| Sighnal-to-noise ratio                                 |            | $f_{S} = 48 \text{ kHz}, \text{ EIAJ}, \text{ A-weighted}$ | 106                    | 113                                                                                                                                                                           |                        | dB              |

|                                                        | SNR        | $f_{S} = 96 \text{ kHz}, \text{ EIAJ}, \text{ A-weighted}$ |                        | 113                                                                                                                                                                           |                        | dB              |

|                                                        |            | $f_{S}$ = 192 kHz, EIAJ, A-weighted                        |                        | 113                                                                                                                                                                           |                        | dB              |

| Channel separation<br>(between one channel and others) |            | f <sub>S</sub> = 48 kHz                                    | 103                    | 109                                                                                                                                                                           |                        | dB              |

|                                                        |            | f <sub>S</sub> = 96 kHz                                    |                        | 109                                                                                                                                                                           |                        | dB              |

|                                                        |            | f <sub>S</sub> = 192 kHz                                   |                        | 108                                                                                                                                                                           |                        | dB              |

| ANALOG OUTPUT                                          |            |                                                            |                        |                                                                                                                                                                               |                        |                 |

| Output voltage                                         |            | Differential                                               |                        | 1.6 ×<br>VCC1                                                                                                                                                                 |                        | V <sub>PP</sub> |

| Center voltage                                         |            |                                                            |                        | 0.5 ×<br>VCC1                                                                                                                                                                 |                        | V               |

| Load impedance                                         |            | To ac-coupled GND <sup>(3)</sup>                           | 5                      | -94     -88       -94     -94       113     113       113     113       113     113       113     113       113     113       113     113       109     109       108     108 | kΩ                     |                 |

|                                                        |            | To dc-coupled GND <sup>(3)</sup>                           | 15                     |                                                                                                                                                                               |                        | kΩ              |

| LPF frequency response                                 |            | f = 20 kHz                                                 |                        | -0.04                                                                                                                                                                         |                        | dB              |

|                                                        |            | f = 44 kHz                                                 |                        | -0.18                                                                                                                                                                         |                        | dB              |

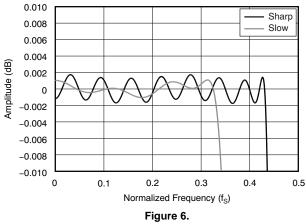

| DIGITAL FILTER PERFORMANCE                             | WITH SHARP | ROLL-OFF                                                   |                        |                                                                                                                                                                               | -                      |                 |

| Passhand (single, dual)                                |            | Except SCKI = 128 $f_S$ and 192 $f_S$                      |                        |                                                                                                                                                                               | 0.454 × f <sub>S</sub> | Hz              |

| Passband (single, dual)                                |            | SCKI = 128 $f_S$ and 192 $f_S$                             |                        |                                                                                                                                                                               | 0.432 × f <sub>S</sub> | Hz              |

| Passband (quad)                                        |            |                                                            |                        |                                                                                                                                                                               | 0.432 × f <sub>S</sub> | Hz              |

| Stop band (single, dual)                               |            | Except SCKI = 128 $f_S$ and 192 $f_S$                      | 0.546 × f <sub>S</sub> |                                                                                                                                                                               |                        | Hz              |

|                                                        |            | SCKI = 128 $f_S$ and 192 $f_S$                             | 0.569 × f <sub>S</sub> |                                                                                                                                                                               |                        | Hz              |

| Stop band (quad)                                       |            |                                                            | 0.569 × f <sub>S</sub> |                                                                                                                                                                               |                        | Hz              |

| Passband ripple                                        |            | $< 0.454 \times f_{S}, 0.432 \times f_{S}$                 |                        |                                                                                                                                                                               | ±0.0018                | dB              |

| Stop band attenuation                                  |            | > 0.546 × f <sub>S</sub> , 0.569 × f <sub>S</sub>          | -75                    |                                                                                                                                                                               |                        | dB              |

In differential mode at VOUTx± pin,  $f_{OUT}$  = 1 kHz, using Audio Precision System II, Average mode with 20-kHz LPF and 400-Hz HPF.  $f_S$  = 48 kHz: SCKI = 512  $f_S$  (single),  $f_S$  = 96 kHz : SCKI = 256  $f_S$  (dual),  $f_S$  = 192 kHz : SCKI = 128  $f_S$  (quad). (1)

(2)

(3) Allowable minimum input resistance of differential to single-ended converter with D to S Gain = G is calculated as  $(1 + 2G)/(1 + G) \times 5k$ for ac-coupled and (1+ 0.9G)/(1 + G) × 15k for dc-coupled connection; refer to Figure 41 and Figure 42 of the Application Information section.

www.ti.com

### ELECTRICAL CHARACTERISTICS: DAC (continued)

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

|                                 |                                       | P                      |                   |                        |      |

|---------------------------------|---------------------------------------|------------------------|-------------------|------------------------|------|

| PARAMETER                       | TEST CONDITIONS                       | MIN                    | TYP               | MAX                    | UNIT |

| DIGITAL FILTER PERFORMANCE WITH | SLOW ROLL-OFF                         |                        |                   |                        |      |

| Passband                        |                                       |                        |                   | 0.328 × f <sub>S</sub> | Hz   |

| Stop band                       |                                       | 0.673 × f <sub>S</sub> |                   |                        | Hz   |

| Passband ripple                 | < 0.328 × f <sub>S</sub>              |                        |                   | ±0.0013                | dB   |

| Stop band attenuation           | > 0.673 × f <sub>S</sub>              | -75                    |                   |                        | dB   |

| DIGITAL FILTER PERFORMANCE      |                                       |                        |                   |                        |      |

|                                 | Except SCKI = 128 $f_S$ and 192 $f_S$ |                        | 28/f <sub>S</sub> |                        | sec  |

| Group delay time (single, dual) | SCKI = 128 $f_S$ and 192 $f_S$        |                        | 19/f <sub>S</sub> |                        | sec  |

| Group delay time (quad)         |                                       |                        | 19/f <sub>S</sub> |                        | sec  |

| De-emphasis error               |                                       |                        | ±0.1              |                        | dB   |

#### **ELECTRICAL CHARACTERISTICS: Power-Supply Requirements**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

| PARAMETER               |                 | TEST CONDITIONS                | MIN TYP M                                                                                                                                                                                                                                                                                                                                                         |                                                                    | MAX | X UNIT |  |

|-------------------------|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|--------|--|

| POWER-SUPPLY REQUIREMEN | тѕ              |                                |                                                                                                                                                                                                                                                                                                                                                                   | •                                                                  |     |        |  |

|                         | VCC1/2          |                                | 4.5                                                                                                                                                                                                                                                                                                                                                               | 5.0                                                                | 5.5 | VDC    |  |

| voltage range           | VDD             |                                | 3.0                                                                                                                                                                                                                                                                                                                                                               | 3.3                                                                | 3.6 | VDC    |  |

|                         |                 | f <sub>S</sub> = 48 kHz        |                                                                                                                                                                                                                                                                                                                                                                   | 74                                                                 | 110 | mA     |  |

|                         | I <sub>CC</sub> | f <sub>S</sub> = 192 kHz       |                                                                                                                                                                                                                                                                                                                                                                   | 74                                                                 |     | mA     |  |

| Current comment         |                 | Full power-down <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                                   | 5.0         5.5           3.3         3.6           74         110 |     | μA     |  |

| Supply current          |                 | f <sub>S</sub> = 48 kHz        |                                                                                                                                                                                                                                                                                                                                                                   |                                                                    | mA  |        |  |

|                         | I <sub>DD</sub> | f <sub>S</sub> = 192 kHz       |                                                                                                                                                                                                                                                                                                                                                                   | 76                                                                 |     | mA     |  |

|                         |                 | Full power-down <sup>(1)</sup> | 4.5       5.0       5.5         3.0       3.3       3.6         Iz       74       110         Hz       74       10         wn <sup>(1)</sup> 170       170         Iz       57       90         Hz       76       10         wn <sup>(1)</sup> 60       10         Iz       558       847         Hz       621       105         wm <sup>(1)</sup> 1.05       105 | μA                                                                 |     |        |  |

|                         |                 | f <sub>S</sub> = 48 kHz        |                                                                                                                                                                                                                                                                                                                                                                   | 558                                                                | 847 | mW     |  |

| Operating temperature   |                 | f <sub>S</sub> = 192 kHz       |                                                                                                                                                                                                                                                                                                                                                                   | 621                                                                |     | mW     |  |

|                         |                 | Full power-down <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                                   | 1.05                                                               |     | mW     |  |

| TEMPERATURE RANGE       | <u>I</u>        |                                |                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |     |        |  |

| Operating temperature   |                 | PCM1690-Q1 Consumer grade      | -40                                                                                                                                                                                                                                                                                                                                                               |                                                                    | +85 | °C     |  |

| Thermal resistance      | θ <sub>JA</sub> | HTSSOP-48                      |                                                                                                                                                                                                                                                                                                                                                                   | +23                                                                |     | °C/W   |  |

(1) SCKI, BCK, and LRCK stopped.

TEXAS INSTRUMENTS

www.ti.com

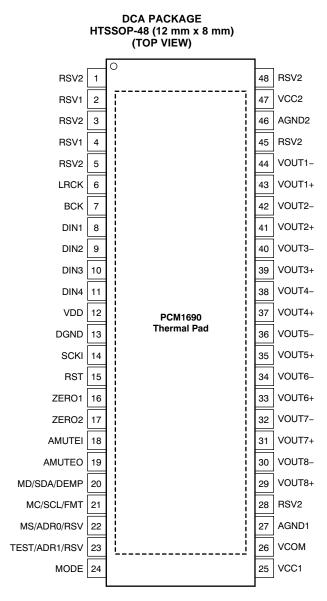

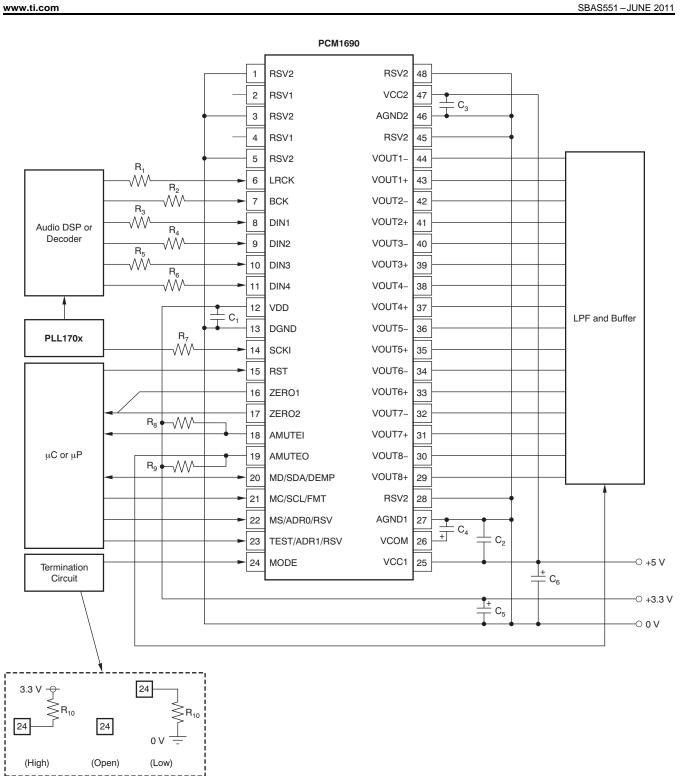

#### **PIN CONFIGURATION**

#### **TERMINAL FUNCTIONS**

| TERMINAL |     |     | PULL- | 5-V      |                                    |  |

|----------|-----|-----|-------|----------|------------------------------------|--|

| NAME     | PIN | I/O | DOWN  | TOLERANT | DESCRIPTION                        |  |

| RSV2     | 1   | _   | _     | _        | Reserved, tied to analog ground    |  |

| RSV1     | 2   | _   | _     | _        | Reserved, left open                |  |

| RSV2     | 3   | _   | _     | —        | Reserved, tied to analog ground    |  |

| RSV1     | 4   | _   | _     | —        | Reserved, left open                |  |

| RSV2     | 5   | _   | _     | _        | Reserved, tied to analog ground    |  |

| LRCK     | 6   | I   | Yes   | No       | Audio data word clock input        |  |

| BCK      | 7   | I   | Yes   | No       | Audio data bit clock input         |  |

| DIN1     | 8   | I   | No    | No       | Audio data input for DAC1 and DAC2 |  |

| DIN2     | 9   | I   | No    | No       | Audio data input for DAC3 and DAC4 |  |

| DIN3     | 10  | I   | No    | No       | Audio data input for DAC5 and DAC6 |  |

| DIN4     | 11  | I   | No    | No       | Audio data input for DAC7 and DAC8 |  |

www.ti.com

### **TERMINAL FUNCTIONS (continued)**

| TERMINAL      |    |     |               |                 |                                                                                                                           |  |  |

|---------------|----|-----|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME PIN I/   |    |     | PULL-<br>DOWN | 5-V<br>TOLERANT | DESCRIPTION                                                                                                               |  |  |

| VDD           | 12 |     |               |                 | Digital power supply, +3.3 V                                                                                              |  |  |

| DGND          | 12 |     |               |                 | Digital ground                                                                                                            |  |  |

| SCKI          | 13 | 1   | No            | Yes             | System clock input                                                                                                        |  |  |

| RST           | 14 | 1   | Yes           | Yes             | Reset and power-down control input with active low                                                                        |  |  |

| ZERO1         | 16 | 0   | No            | No              | Zero detect flag output 1                                                                                                 |  |  |

| ZERO2         | 10 | 0   | No            | No              | Zero detect flag output 2                                                                                                 |  |  |

| AMUTEI        | 18 | 1   | No            | Yes             | Analog mute control input with active low                                                                                 |  |  |

|               |    | 0   |               | Yes             | Analog mute status output <sup>(1)</sup> with active low                                                                  |  |  |

| AMUTEO        | 19 | 0   | No            | res             | Input data for SPI, data for $I^2C^{(1)}$ , de-emphasis control for hardware                                              |  |  |

| MD/SDA/DEMP   | 20 | I/O | No            | Yes             | control mode                                                                                                              |  |  |

| MC/SCL/FMT    | 21 | I   | No            | Yes             | Clock for SPI, clock for I <sup>2</sup> C, format select for hardware control mode                                        |  |  |

| MS/ADR0/RSV   | 22 | I   | Yes           | Yes             | Chip Select for SPI, address select 0 for I <sup>2</sup> C, reserve (set low) for hardware control mode                   |  |  |

| TEST/ADR1/RSV | 23 | I/O | No            | Yes             | Test (factory use, left open) for SPI, address select 1 for I <sup>2</sup> C, reserve (set low) for hardware control mode |  |  |

| MODE          | 24 | I   | No            | No              | Control port mode selection. Tied to VDD: SPI, left open: H/W mode, tied to DGND: $I^2C$                                  |  |  |

| VCC1          | 25 | _   | _             | _               | Analog power supply 1, +5 V                                                                                               |  |  |

| VCOM          | 26 | _   | —             | _               | Voltage common decoupling                                                                                                 |  |  |

| AGND1         | 27 | _   | —             | _               | Analog ground 1                                                                                                           |  |  |

| RSV2          | 28 | _   | _             | _               | Reserved, tied to analog ground                                                                                           |  |  |

| VOUT8+        | 29 | 0   | No            | No              | Positive analog output from DAC8                                                                                          |  |  |

| VOUT8-        | 30 | 0   | No            | No              | Negative analog output from DAC8                                                                                          |  |  |

| VOUT7+        | 31 | 0   | No            | No              | Positive analog output from DAC7                                                                                          |  |  |

| VOUT7-        | 32 | 0   | No            | No              | Negative analog output from DAC7                                                                                          |  |  |

| VOUT6+        | 33 | 0   | No            | No              | Positive analog output from DAC6                                                                                          |  |  |

| VOUT6-        | 34 | 0   | No            | No              | Negative analog output from DAC6                                                                                          |  |  |

| VOUT5+        | 35 | 0   | No            | No              | Positive analog output from DAC5                                                                                          |  |  |

| VOUT5-        | 36 | 0   | No            | No              | Negative analog output from DAC5                                                                                          |  |  |

| VOUT4+        | 37 | 0   | No            | No              | Positive analog output from DAC4                                                                                          |  |  |

| VOUT4-        | 38 | 0   | No            | No              | Negative analog output from DAC4                                                                                          |  |  |

| VOUT3+        | 39 | 0   | No            | No              | Positive analog output from DAC3                                                                                          |  |  |

| VOUT3-        | 40 | 0   | No            | No              | Negative analog output from DAC3                                                                                          |  |  |

| VOUT2+        | 41 | 0   | No            | No              | Positive analog output from DAC2                                                                                          |  |  |

| VOUT2-        | 42 | 0   | No            | No              | Negative analog output from DAC2                                                                                          |  |  |

| VOUT1+        | 43 | 0   | No            | No              | Positive analog output from DAC1                                                                                          |  |  |

| VOUT1-        | 44 | 0   | No            | No              | Negative analog output from DAC1                                                                                          |  |  |

| RSV2          | 45 | —   | —             | _               | Reserved, tied to analog ground                                                                                           |  |  |

| AGND2         | 46 | _   | _             | _               | Analog ground 2                                                                                                           |  |  |

| VCC2          | 47 | _   | _             | _               | Analog power supply 2, +5 V                                                                                               |  |  |

| RSV2          | 48 | _   | _             | _               | Reserved, tied to analog ground                                                                                           |  |  |

|               |    |     |               |                 |                                                                                                                           |  |  |

(1) Open-drain configuration in out mode.

# PCM1690-Q1

SBAS551 - JUNE 2011

www.ti.com

8

Sharp

0.5

Slow

#### www.ti.com

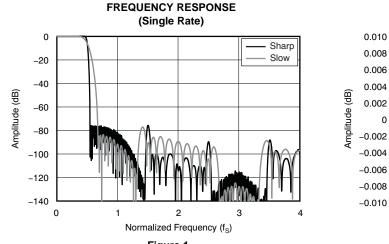

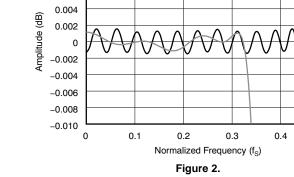

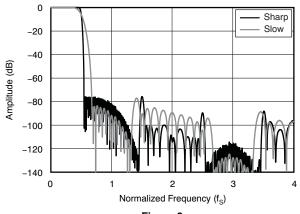

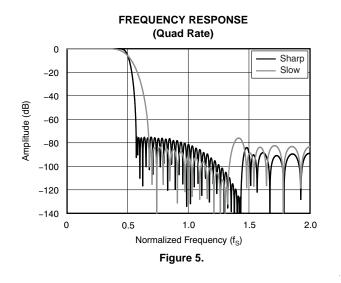

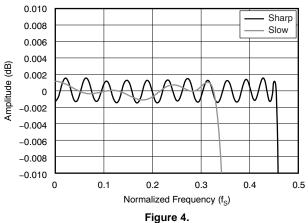

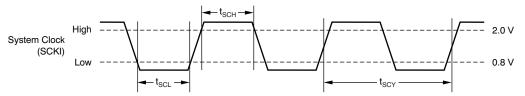

#### **TYPICAL CHARACTERISTICS: Digital Filter**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

FREQUENCY RESPONSE PASSBAND

(Single Rate)

Figure 10.

10

### **TYPICAL CHARACTERISTICS: Digital De-Emphasis Filter**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

www.ti.com

# PCM1690-Q1

SBAS551 - JUNE 2011

www.ti.com

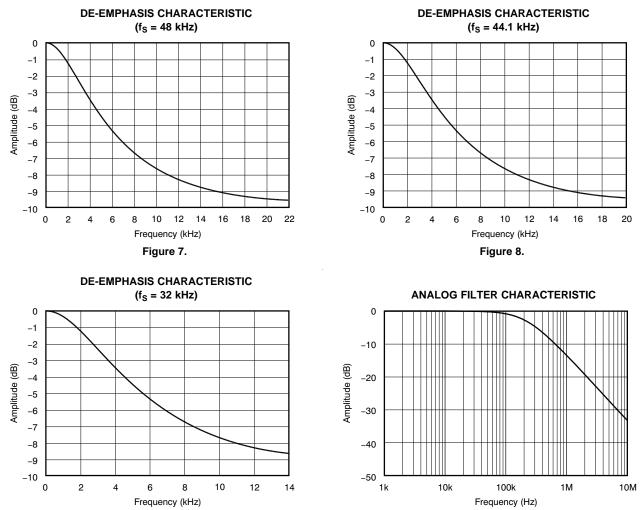

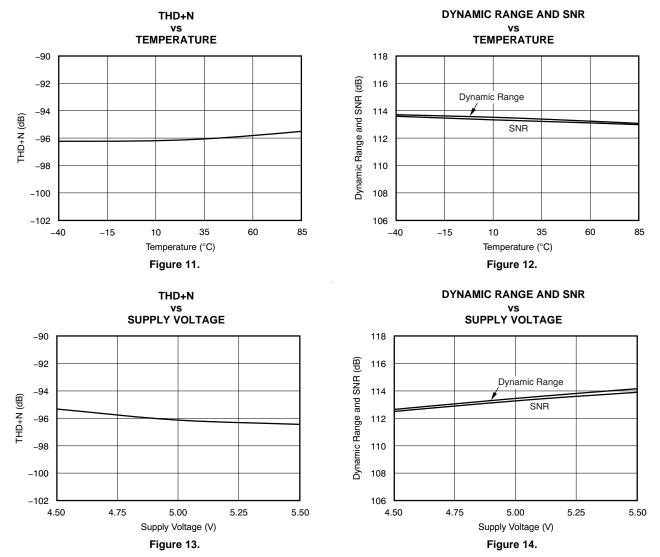

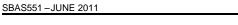

#### **TYPICAL CHARACTERISTICS: Dynamic Performance**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto, unless otherwise noted.

# PCM1690-Q1

Figure 17.

#### **TYPICAL CHARACTERISTICS: Output Spectrum**

All specifications at  $T_A = +25^{\circ}$ C, VCC1 = VCC2 = 5 V, VDD = 3.3 V,  $f_S = 48$  kHz, SCKI = 512  $f_S$ , 24-bit data, and Sampling Mode = Auto\_unless otherwise noted

www.ti.com

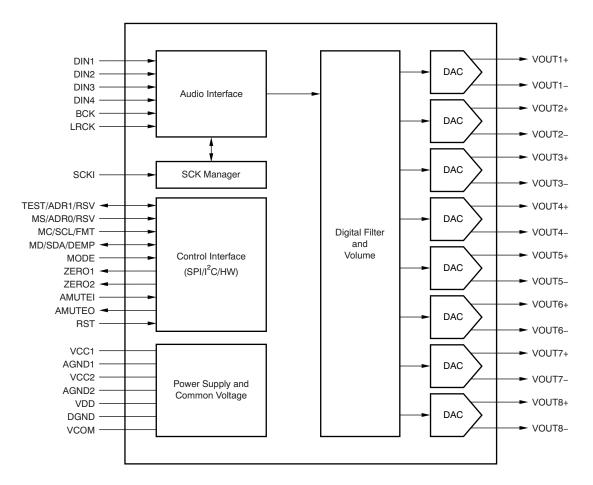

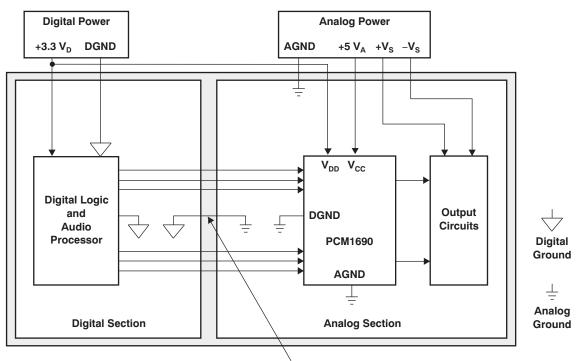

#### PRODUCT OVERVIEW

The PCM1690-Q1 is a high-performance, multi-channel DAC targeted for consumer audio applications such as Blu-ray DVD players and HD DVD players, as well as home multi-channel audio applications (such as home theaters and A/V receivers). The PCM1690-Q1 consists of an eight-channel DAC. The DAC output type is fixed with a differential configuration. The PCM1690-Q1 supports 16-/20-/24-/32-bit linear PCM input data in I<sup>2</sup>S- and left-justified audio formats, and 24-bit linear PCM input data in right-justified, DSP, and TDM formats for various sampling frequencies from 8 kHz to 192 kHz. The TDM format is useful for saving bus line interface numbers for multi-channel audio data communication between the DAC and a digital audio processor. The PCM1690-Q1 offers three modes for device control: two-wire I<sup>2</sup>C software, three-wire SPI software, and hardware modes.

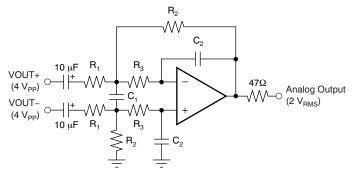

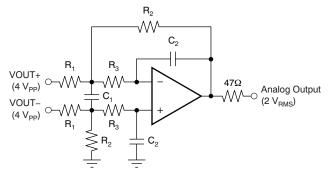

#### ANALOG OUTPUTS

The PCM1690-Q1 includes eight DACs, each with individual pairs of differential voltage outputs pins. The full-scale output voltage is (1.6 × VCC1) V<sub>PP</sub> at the differential output mode. A dc-coupled load is allowed in addition to an ac-coupled load if the load resistance conforms to the specification. These balanced outputs are each capable of driving 0.8 VCC1 (4 V<sub>PP</sub>) typical into a 5-k $\Omega$ , ac-coupled or 15-k $\Omega$ , dc-coupled load with VCC1 = +5 V. The internal output amplifiers for VOUT1 through VOUT8 are biased to the dc common voltage, equal to (0.5 × VCC1).

The output amplifiers include an RC continuous-time filter that helps to reduce the out-of-band noise energy present at the DAC outputs as a result of the noise shaping characteristics of the PCM1690-Q1 delta-sigma ( $\Delta\Sigma$ ) DACs. The frequency response of this filter is shown in the *Analog Filter Characteristic* (Figure 10) of the Typical Characteristics. By itself, this filter is not enough to attenuate the out-of-band noise to an acceptable level for most applications. An external low-pass filter is required to provide sufficient out-of-band noise rejection. Further discussion of DAC post-filter circuits is provided in the *Application Information* section.

| 5             |          |                     |  |  |  |  |  |

|---------------|----------|---------------------|--|--|--|--|--|

| DIGITAL INPUT | CHANNEL  | DIFFERENTIAL OUTPUT |  |  |  |  |  |

| DINI          | 1 (DAC1) | VOUT1+, VOUT1–      |  |  |  |  |  |

| DIN1          | 2 (DAC2) | VOUT2+, VOUT2–      |  |  |  |  |  |

|               | 3 (DAC3) | VOUT3+, VOUT3–      |  |  |  |  |  |

| DIN2          | 4 (DAC4) | VOUT4+, VOUT4–      |  |  |  |  |  |

|               | 5 (DAC5) | VOUT5+, VOUT5–      |  |  |  |  |  |

| DIN3          | 6 (DAC6) | VOUT6+, VOUT6–      |  |  |  |  |  |

| DINIA         | 7 (DAC7) | VOUT7+, VOUT7–      |  |  |  |  |  |

| DIN4          | 8 (DAC8) | VOUT8+, VOUT8–      |  |  |  |  |  |

#### Table 1. Pin Assignments in Differential Output Mode

#### VOLTAGE REFERENCE VCOM

The PCM1690-Q1 includes a pin for the common-mode voltage output, VCOM. This pin should be connected to the analog ground via a decoupling capacitor. This pin can also be used to bias external high-impedance circuits, if they are required.

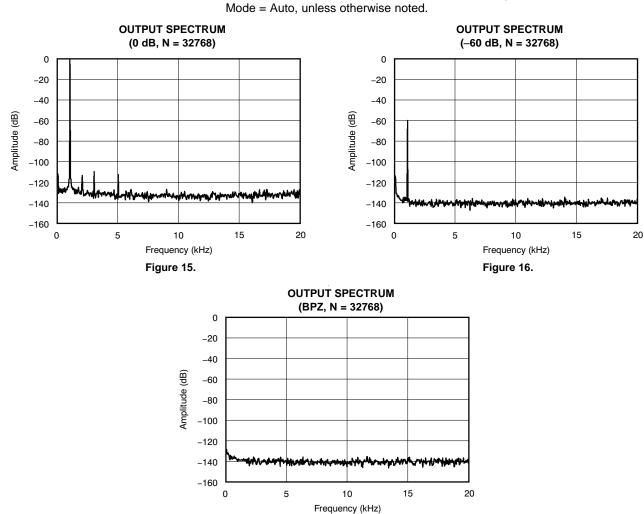

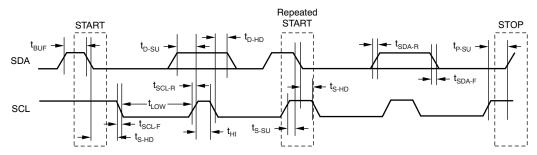

#### SYSTEM CLOCK INPUT

The PCM1690-Q1 requires an external system clock input applied at the SCKI input for DAC operation. The system clock operates at an integer multiple of the sampling frequency, or  $f_S$ . The multiples supported in DAC operation include 128  $f_S$ , 192  $f_S$ , 256  $f_S$ , 384  $f_S$ , 512  $f_S$ , 768  $f_S$ , and 1152  $f_S$ . Details for these system clock multiples are shown in Table 2. Figure 18 and Table 3 show the SCKI timing requirements.

| DEFAULT<br>SAMPLING | SAMPLING<br>FREQUENCY |                    | :                  | JENCY (MHz         | (MHz)              |                    |                    |                     |

|---------------------|-----------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|

| MODE                | f <sub>S</sub> (kHz)  | 128 f <sub>S</sub> | 192 f <sub>S</sub> | 256 f <sub>S</sub> | 384 f <sub>S</sub> | 512 f <sub>S</sub> | 768 f <sub>S</sub> | 1152 f <sub>S</sub> |

|                     | 8                     | N/A                | N/A                | 2.0480             | 3.0720             | 4.0960             | 6.1440             | 9.2160              |

|                     | 16                    | 2.0480             | 3.0720             | 4.0960             | 6.1440             | 8.1920             | 12.2880            | 18.4320             |

| Single rate         | 32                    | 4.0960             | 6.1440             | 8.1920             | 12.2880            | 16.3840            | 24.5760            | 36.8640             |

|                     | 44.1                  | 5.6448             | 8.4672             | 11.2896            | 16.9344            | 22.5792            | 33.8688            | N/A                 |

|                     | 48                    | 6.1440             | 9.2160             | 12.2880            | 18.4320            | 24.5760            | 36.8640            | N/A                 |

| Dual rate           | 88.2                  | 11.2896            | 16.9344            | 22.5792            | 33.8688            | N/A                | N/A                | N/A                 |

| Dual rate           | 96                    | 12.2880            | 18.4320            | 24.5760            | 36.8640            | N/A                | N/A                | N/A                 |

| Qued rete           | 176.4                 | 22.5792            | 33.8688            | N/A                | N/A                | N/A                | N/A                | N/A                 |

| Quad rate           | 192                   | 24.5760            | 36.8640            | N/A                | N/A                | N/A                | N/A                | N/A                 |

#### Table 2. System Clock Frequencies for Common Audio Sampling Rates

Figure 18. System Clock Timing Requirements

| SYMBOL           | PARAMETER               | MIN | MAX | UNIT |

|------------------|-------------------------|-----|-----|------|

| t <sub>SCY</sub> | System clock cycle time | 27  |     | ns   |

| t <sub>SCH</sub> | System clock width high | 10  |     | ns   |

| t <sub>SCL</sub> | System clock width low  | 10  |     | ns   |

| —                | System clock duty cycle | 40  | 60  | %    |

#### Table 3. Timing Requirements for Figure 18

#### SAMPLING MODE

The PCM1690-Q1 supports three sampling modes (single rate, dual rate, and quad rate) in DAC operation. In single rate mode, the DAC operates at an oversampling frequency of x128 (except when SCKI = 128  $f_S$  and 192  $f_S$ ). This mode is supported for sampling frequencies less than 50 kHz. In dual rate mode, the DAC operates at an oversampling frequency of x64; this mode is supported for sampling frequencies less than 100 kHz. In quad rate mode, the DAC operates at an oversampling frequency of x32. The sampling mode is automatically selected according to the ratio of system clock frequency and sampling frequency by default (that is, single rate for 512  $f_S$ , 768  $f_S$ , and 1152  $f_S$ ; dual rate for 256  $f_S$  and 384  $f_S$ ; and quad rate for 128  $f_S$  and 192  $f_S$ ), but manual selection is also possible for specified combinations through the serial mode control register.

Table 4 and Figure 19 show the relation among the oversampling rate (OSR) of the digital filter and  $\Delta\Sigma$  modulator, the noise-free shaped bandwidth, and each sampling mode setting.

| SAMPLING                    |                                                 | NOISE-FREI              | E SHAPED BANDW          |                          |                       |                  |  |

|-----------------------------|-------------------------------------------------|-------------------------|-------------------------|--------------------------|-----------------------|------------------|--|

| MODE<br>REGISTER<br>SETTING | SYSTEM CLOCK<br>FREQUENCY<br>(xf <sub>S</sub> ) | f <sub>S</sub> = 48 kHz | f <sub>S</sub> = 96 kHz | f <sub>S</sub> = 192 kHz | DIGITAL FILTER<br>OSR | MODULATOR<br>OSR |  |

|                             | 512, 768, 1152                                  | 40                      | N/A                     | N/A                      | ×8                    | x128             |  |

| Auto                        | 256, 384                                        | 20                      | 40                      | N/A                      | x8                    | x64              |  |

|                             | 128, 192 <sup>(2)</sup>                         | 10                      | 20                      | 40                       | x4                    | x32              |  |

|                             | 512, 768, 1152                                  | 40                      | N/A                     | N/A                      | x8                    | x128             |  |

| Single                      | 256, 384                                        | 40                      | N/A                     | N/A                      | x8                    | x128             |  |

|                             | 128, 192 <sup>(2)</sup>                         | 20                      | N/A                     | N/A                      | x4                    | x64              |  |

| Dual                        | 256, 384                                        | 20                      | 40                      | N/A                      | x8                    | x64              |  |

| Dual                        | 128, 192 <sup>(2)</sup>                         | 20                      | 40                      | N/A                      | x4                    | x64              |  |

| Quad                        | 128, 192 <sup>(2)</sup>                         | 10                      | 20                      | 40                       | x4                    | x32              |  |

| Table 4. DAC Filter OSR | R. Modulator OSR. | and Noise-Free | Shaped Bandwidth for | or Each Sampling Mode |

|-------------------------|-------------------|----------------|----------------------|-----------------------|

|                         | ,                 | ,              |                      |                       |

(1) Bandwidth in which noise is shaped out.

(2) Quad mode filter characteristic is applied.

Figure 19.  $\Delta\Sigma$  Modulator and Digital Filter Characteristic

#### **RESET OPERATION**

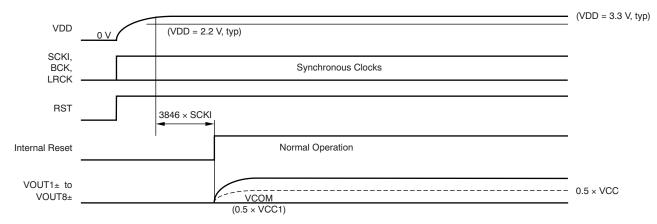

The PCM1690-Q1 has both an internal power-on reset circuit and an external reset circuit. The sequences for both reset circuits are illustrated in Figure 20 and Figure 21. Figure 20 describes the timing at the internal power-on reset. Initialization is triggered automatically at the point where VDD exceeds 2.2 V typical, and the internal reset is released after 3846 SCKI clock cycles from power-on if RST is held high and SCKI is provided. VOUT from the DACs are forced to the VCOM level initially (that is, 0.5 × VCC1) and settle at a specified level according to the rising VCC. If synchronization among SCKI, BCK, and LRCK is maintained, VOUT provides an output that corresponds to DIN after 3846 SCKI clocks from power-on. If the synchronization is not held, the internal reset is not released, and both operating modes are maintained at reset and power-down states; after synchronization forms again, the DAC returns to normal operation with the previous sequences.

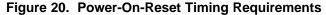

Figure 21 illustrates a timing diagram at the external reset. RST accepts an externally-forced reset with RST low, and provides a device reset and power-down state that achieves the lowest power dissipation state available in the PCM1690-Q1. If RST goes from high to low under synchronization among SCKI, BCK, and LRCK, the internal reset is asserted, all registers and memory are reset, and finally the PCM1690-Q1 enters into all power-down states. At the same time, VOUT is immediately forced into the AGND1 level. To begin normal operation again, toggle RST high; the same power-up sequence is performed as the power-on reset shown in Figure 20.

The PCM1690-Q1 does not require particular power-on sequences for VCC and VDD; it allows VDD on and then VCC on, or VCC on and then VDD on. From the viewpoint of the Absolute Maximum Ratings, however, simultaneous power-on is recommended for avoiding unexpected responses on VOUTx. Figure 20 illustrates the response for VCC on with VDD on.

PCM1690-Q1

The PCM1690-Q1 audio serial port consists of six signals: BCK, LRCK, DIN1, DIN2, DIN3, and DIN4. BCK is a bit clock input. LRCK is a left/right word clock input or frame synchronization clock input. DIN1/2/3/4 are the audio data inputs for VOUT1–8.

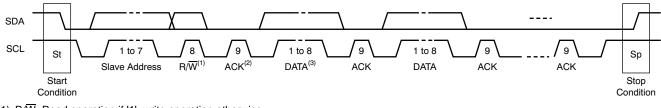

#### AUDIO DATA INTERFACE FORMATS AND TIMING

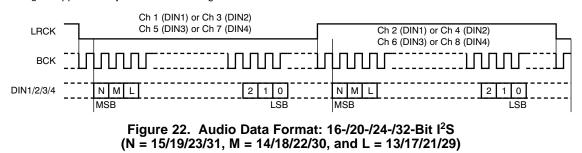

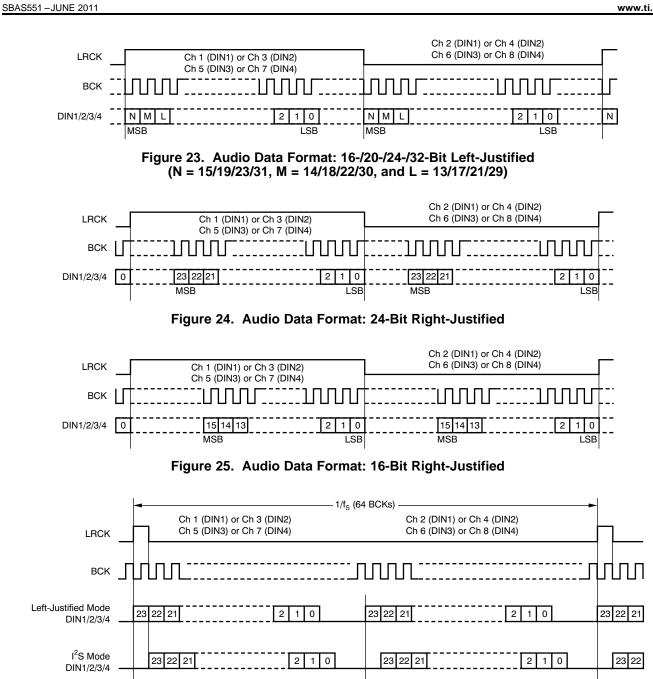

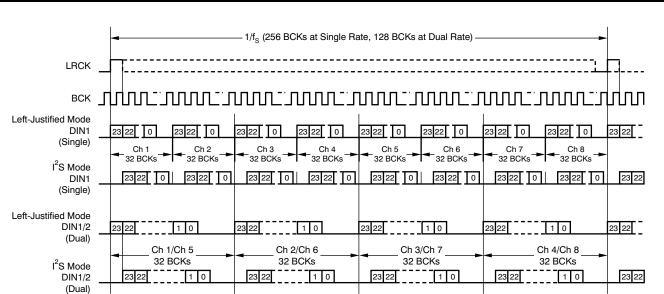

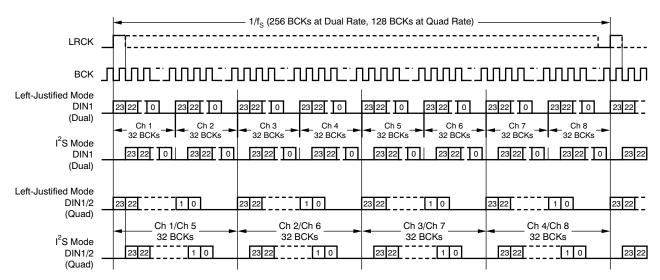

The PCM1690-Q1 supports 10 audio data interface formats: 16-/20-/24-/32-bit I<sup>2</sup>S, 16-/20-/24-/32-bit left-justified, 24-bit right-justified, 16-bit right-justified, 24-bit left-justified mode DSP, 24-bit I<sup>2</sup>S mode DSP, 24-bit left-justified mode TDM, 24-bit I<sup>2</sup>S mode TDM, 24-bit left-justified, and right-justified data formats, 64 BCKs, 48 BCKs, and 32 BCKs per LRCK period are supported; but 48 BCKs are limited in 192/384/768 f<sub>S</sub> SCKI, and 32 BCKs are limited in 16-bit right-justified only. In the case of TDM data format in single rate, BCK, LRCK, and DIN1 are used. In the case of TDM data format in single rate, BCK, LRCK, and DIN1 are used. In the case of TDM format in dual rate, BCK, LRCK, and DIN1/2 are used. In the case of high-speed TDM format in quad rate, BCK, LRCK, and DIN1/2 are used. TDM format and high-speed TDM format are supported only at SCKI = 512 f<sub>S</sub>, 256 f<sub>S</sub>, 128 f<sub>S</sub>, and f<sub>BCK</sub> ≤ f<sub>SCKI</sub>. The audio data formats are selected by MC/SCL/FMT in hardware control mode and by control register settings in software control mode. All data must be in binary twos complement and MSB first.

Table 5 summarizes the applicable formats and describes the relationships among them and the respective restrictions with mode control. Figure 22 through Figure 28 show 10 audio interface data formats.

| CONTROL<br>MODE     | FORMAT                               | DATA BITS      | MAX LRCK<br>FREQUENCY (f <sub>s</sub> ) | SCKI RATE (xf <sub>s</sub> ) | BCK RATE (xf <sub>s</sub> )        | APPLICABLE PINS |

|---------------------|--------------------------------------|----------------|-----------------------------------------|------------------------------|------------------------------------|-----------------|

|                     | I <sup>2</sup> S/Left-Justified      | 16/20/24/32(1) | 192 kHz                                 | 128 to 1152 <sup>(2)</sup>   | 64, 48                             | DIN1/2/3/4      |

|                     | Right-Justified                      | 24, 16         | 192 kHz                                 | 128 to 1152 <sup>(2)</sup>   | 64, 48, 32 (16 bit) <sup>(3)</sup> | DIN1/2/3/4      |

|                     | I <sup>2</sup> S/Left-Justified DSP  | 24             | 192 kHz                                 | 128 to 768                   | 64                                 | DIN1/2/3/4      |

| Software<br>control |                                      | 24             | 48 kHz                                  | 256, 512                     | 256                                | DIN1            |

|                     | I <sup>2</sup> S/ Left-Justified TDM | 24             | 96 kHz                                  | 128, 256                     | 128                                | DIN1/2          |

|                     | High-Speed                           | 24             | 96 kHz                                  | 256                          | 256                                | DIN1            |

|                     | I <sup>2</sup> S/Left-Justified TDM  | 24             | 192 kHz                                 | 128                          | 128                                | DIN1/2          |

|                     | l <sup>2</sup> S                     | 16/20/24/32(1) | 192 kHz                                 | 128 to 1152 <sup>(2)</sup>   | 64, 48                             | DIN1/2/3/4      |

| Hardware<br>control | 20 701                               | 24             | 48 kHz                                  | 512                          | 256                                | DIN1            |

|                     | I <sup>2</sup> S TDM                 | 24             | 96 kHz                                  | 256                          | 128                                | DIN1/2          |

Table 5. Audio Data Interface Formats and Sampling Rate, Bit Clock, and System Clock Restrictions

(1) 32-bit data length is acceptable only for BCK = 64  $f_S$  and when using  $I^2S$  and Left-Justified format.

(2) 1152 f<sub>S</sub> is acceptable only for f<sub>S</sub> = 32 kHz, BCK = 64 f<sub>S</sub>, and when using  $I^2S$ , Left-Justified, and 24-bit Right-Justified format.

(3) BCK = 32  $f_S$  is supported only for 16-bit data length.

Texas **NSTRUMENTS**

www.ti.com

# PCM1690-Q1

SBAS551 - JUNE 2011

#### www.ti.com

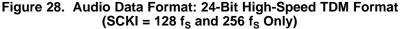

Figure 27. Audio Data Format: 24-Bit TDM Format (SCKI = 128 f<sub>S</sub>, 256 f<sub>S</sub>, and 512 f<sub>S</sub> Only)

www.ti.com

# AUDIO INTERFACE TIMING

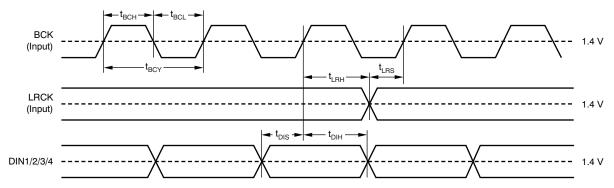

Figure 29 and Figure 30 describe the detailed interface timing specifications.

Figure 29. Audio Interface Timing Requirements for Left-Justified, Right-Justified, and I<sup>2</sup>S Data Formats

| SYMBOL           | DESCRIPTION                              | MIN | ТҮР | MAX | UNIT |

|------------------|------------------------------------------|-----|-----|-----|------|

| t <sub>BCY</sub> | BCK cycle time                           | 75  |     |     | ns   |

| t <sub>BCH</sub> | BCK pulse width high                     | 35  |     |     | ns   |

| t <sub>BCL</sub> | BCK pulse width low                      | 35  |     |     | ns   |

| t <sub>LRS</sub> | LRCK setup time to BCK rising edge       | 10  |     |     | ns   |

| t <sub>LRH</sub> | LRCK hold time to BCK rising edge        | 10  |     |     | ns   |

| t <sub>DIS</sub> | DIN1/2/3/4 setup time to BCK rising edge | 10  |     |     | ns   |

| t <sub>DIH</sub> | DIN1/2/3/4 hold time to BCK rising edge  | 10  |     |     | ns   |

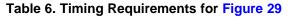

Figure 30. Audio Interface Timing Requirements for DSP and TDM Data Formats

| SYMBOL           | DESCRIPTION                              | MIN              | TYP | MAX                 | UNIT |

|------------------|------------------------------------------|------------------|-----|---------------------|------|

| t <sub>BCY</sub> | BCK cycle time                           | 40               |     |                     | ns   |

| t <sub>BCH</sub> | BCK pulse width high                     | 15               |     |                     | ns   |

| t <sub>BCL</sub> | BCK pulse width low                      | 15               |     |                     | ns   |

|                  | LRCK pulse width high (DSP format)       | t <sub>BCY</sub> |     | t <sub>BCY</sub>    |      |

| t <sub>LRW</sub> | LRCK pulse width high (TDM format)       | t <sub>BCY</sub> |     | $1/f_{S} - t_{BCY}$ |      |

| t <sub>LRS</sub> | LRCK setup time to BCK rising edge       | 10               |     |                     | ns   |

| t <sub>LRH</sub> | LRCK hold time to BCK rising edge        | 10               |     |                     | ns   |

| t <sub>DIS</sub> | DIN1/2/3/4 setup time to BCK rising edge | 10               |     |                     | ns   |

| t <sub>DIH</sub> | DIN1/2/3/4 hold time to BCK rising edge  | 10               |     |                     | ns   |

#### Table 7. Timing Requirements for Figure 30

#### SYNCHRONIZATION WITH THE DIGITAL AUDIO SYSTEM

The PCM1690-Q1 operates under the system clock (SCKI) and the audio sampling rate (LRCK). Therefore, SCKI and LRCK must have a specific relationship. The PCM1690-Q1 does not need a specific phase relationship between the audio interface clocks (LRCK, BCK) and the system clock (SCKI), but does require a specific frequency relationship (ratiometric) between LRCK, BCK, and SCKI.

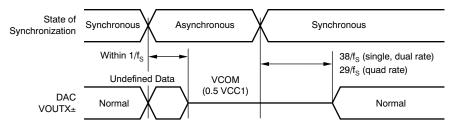

If the relationship between SCKI and LRCK changes more than  $\pm 2$  BCK clocks because of jitter, sampling frequency change, etc., the DAC internal operation stops within 1/f<sub>s</sub>, and the analog output is forced into VCOM (0.5 VCC1) until re-synchronization between SCKI, LRCK, and BCK completes and then 38/f<sub>s</sub> (single, dual rate) or 29/f<sub>s</sub> (quad rate) passes. In the event the change is less than  $\pm 2$  BCKs, re-synchronization does not occur, and this analog output control and discontinuity does not occur.

Figure 31 shows the DAC analog output during loss of synchronization. During undefined data periods, some noise may be generated in the audio signal. Also, the transition of normal to undefined data and undefined (or zero) data to normal data creates a discontinuity of data on the analog outputs, which then may generate some noise in the audio signal.

DAC outputs (VOUTx) hold the previous state if the system clock halts, but the asynchronous and re-synchronization processes will occur after the system clock resumes.

Figure 31. DAC Outputs During Loss of Synchronization

#### ZERO FLAG

The PCM1690-Q1 has two ZERO flag pins (ZERO1 and ZERO2) that can be assigned to the combinations shown in Table 8. Zero flag combinations are selected through control register settings. If the input data of the left and right channel of all assigned channels remain at '0' for 1024 sampling periods (LRCK clock periods), the ZERO1/2 bits are set to a high level, logic '1' state. Furthermore, if the input data of any channels of assigned channels read '1', the ZERO1/2 are set to a low level, logic '0' state, immediately. Zero data detection is supported for 16-/20-/24-bit data width, but is not supported for 32-bit data width.

The active polarity of the zero flag output can be inverted through control register settings. The reset default is active high for zero detection. In parallel hardware control mode, ZERO1 and ZERO2 are fixed with combination *A* shown in Table 8.

| ZERO FLAG COMBINATION | ZERO1               | ZERO2                |

|-----------------------|---------------------|----------------------|

| Α                     | DATA1, left channel | DATA1, right channel |

| В                     | DATA1–4             | DATA1–4              |

| С                     | DATA4               | DATA1–3              |

| D                     | DATA1               | DATA2–4              |

| Table 8 | . Zero Flag | Outputs | Combination |

|---------|-------------|---------|-------------|

|---------|-------------|---------|-------------|

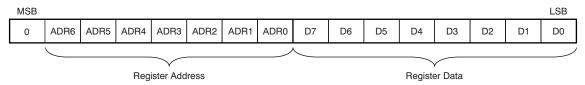

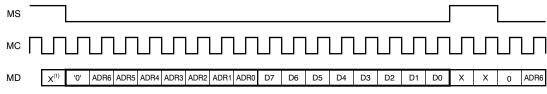

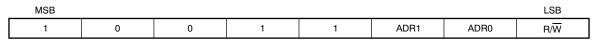

#### AMUTE CONTROL