# Propeller Manual

---

Version 1.1

IMPROVED

NEW

## **WARRANTY**

Parallax Inc. warrants its products against defects in materials and workmanship for a period of 90 days from receipt of product. If you discover a defect, Parallax Inc. will, at its option, repair or replace the merchandise, or refund the purchase price. Before returning the product to Parallax, call for a Return Merchandise Authorization (RMA) number. Write the RMA number on the outside of the box used to return the merchandise to Parallax. Please enclose the following along with the returned merchandise: your name, telephone number, shipping address, and a description of the problem. Parallax will return your product or its replacement using the same shipping method used to ship the product to Parallax.

## **14-DAY MONEY BACK GUARANTEE**

If, within 14 days of having received your product, you find that it does not suit your needs, you may return it for a full refund. Parallax Inc. will refund the purchase price of the product, excluding shipping/handling costs. This guarantee is void if the product has been altered or damaged. See the Warranty section above for instructions on returning a product to Parallax.

## **COPYRIGHTS AND TRADEMARKS**

This documentation is copyright © 2006-2009 by Parallax Inc. By downloading or obtaining a printed copy of this documentation or software you agree that it is to be used exclusively with Parallax products. Any other uses are not permitted and may represent a violation of Parallax copyrights, legally punishable according to Federal copyright or intellectual property laws. Any duplication of this documentation for commercial uses is expressly prohibited by Parallax Inc. Duplication for educational use is permitted, subject to the following Conditions of Duplication: Parallax Inc. grants the user a conditional right to download, duplicate, and distribute this text without Parallax's permission. This right is based on the following conditions: the text, or any portion thereof, may not be duplicated for commercial use; it may be duplicated only for educational purposes when used solely in conjunction with Parallax products, and the user may recover from the student only the cost of duplication.

This text is available in printed format from Parallax Inc. Because we print the text in volume, the consumer price is often less than typical retail duplication charges.

Parallax, Propeller Spin, and the Parallax and Propeller Hat logos are trademarks of Parallax Inc. BASIC Stamp, Stamps in Class, Boe-Bot, SumoBot, Toddler, and SX-Key are registered trademarks of Parallax, Inc. If you decide to use any trademarks of Parallax Inc. on your web page or in printed material, you must state that (trademark) is a (registered) trademark of Parallax Inc." upon the first appearance of the trademark name in each printed document or web page. Other brand and product names herein are trademarks or registered trademarks of their respective holders.

**ISBN 9-781928-982470**

**1.1.0-09.03.05-HKTP**

## DISCLAIMER OF LIABILITY

Parallax Inc. is not responsible for special, incidental, or consequential damages resulting from any breach of warranty, or under any legal theory, including lost profits, downtime, goodwill, damage to or replacement of equipment or property, or any costs of recovering, reprogramming, or reproducing any data stored in or used with Parallax products. Parallax Inc. is also not responsible for any personal damage, including that to life and health, resulting from use of any of our products. You take full responsibility for your Propeller microcontroller application, no matter how life-threatening it may be.

## INTERNET DISCUSSION LISTS

We maintain active web-based discussion forums for people interested in Parallax products. These forums are accessible at [forums.parallax.com](http://forums.parallax.com):

- [Propeller chip](#) – This list is specifically for our customers using Propeller chips and products.

- [BASIC Stamp](#) – This list is widely utilized by engineers, hobbyists and students who share their BASIC Stamp projects and ask questions.

- [Stamps in Class®](#) – Created for educators and students, subscribers discuss the use of the Stamps in Class series of tutorials in their courses. The list provides an opportunity for both students and educators to ask questions and get answers.

- [HYDRA](#) – for enthusiasts of the Propeller-powered HYDRA videogame development system.

- [Parallax Educators](#) – A private forum exclusively for educators and those who contribute to the development of Stamps in Class. Parallax created this group to obtain feedback on our curricula and to provide a place for educators to develop and obtain Teacher's Guides.

- [Robotics](#) – Designed for Parallax robots, this forum is intended to be an open dialogue for robotics enthusiasts. Topics include assembly, source code, expansion, and manual updates. The Boe-Bot®, Toddler®, SumoBot®, HexCrawler and QuadCrawler robots are discussed here.

- [SX Microcontrollers and SX-Key](#) – Discussion of programming the SX microcontroller with Parallax assembly language SX – Key® tools and 3rd party BASIC and C compilers.

- [Javelin Stamp](#) – Discussion of application and design using the Javelin Stamp, a Parallax module that is programmed using a subset of Sun Microsystems' Java® programming language.

## ERRATA

While great effort is made to assure the accuracy of our texts, errors may still exist. If you find an error, please let us know by sending an email to [editor@parallax.com](mailto:editor@parallax.com). We continually strive to improve all of our educational materials and documentation, and frequently revise our texts. Occasionally, an errata sheet with a list of known errors and corrections for a given text will be posted to our web site, [www.parallax.com](http://www.parallax.com). Please check the individual product page's free downloads for an errata file.

## SUPPORTED HARDWARE AND FIRMWARE

This manual is valid with the following hardware and firmware versions:

| Hardware   | Firmware    |

|------------|-------------|

| P8X32A-D40 |             |

| P8X32A-Q44 |             |

| P8X32A-M44 | P8X32A v1.0 |

## CREDITS

Authorship: Jeff Martin. Format & Editing, Stephanie Lindsay.

Cover Art: Jen Jacobs; Technical Graphics: Rich Allred; with many thanks to everyone at Parallax Inc.

# Table of Contents

---

|                                                      |    |

|------------------------------------------------------|----|

| PREFACE .....                                        | 11 |

| CHAPTER 1 : INTRODUCING THE PROPELLER CHIP .....     | 13 |

| CONCEPT .....                                        | 13 |

| PACKAGE TYPES .....                                  | 14 |

| PIN DESCRIPTIONS .....                               | 15 |

| SPECIFICATIONS .....                                 | 16 |

| HARDWARE CONNECTIONS .....                           | 17 |

| BOOT UP PROCEDURE .....                              | 18 |

| RUN-TIME PROCEDURE .....                             | 18 |

| SHUTDOWN PROCEDURE .....                             | 19 |

| BLOCK DIAGRAM .....                                  | 20 |

| SHARED RESOURCES .....                               | 22 |

| SYSTEM CLOCK .....                                   | 22 |

| COGS (PROCESSORS) .....                              | 22 |

| HUB .....                                            | 24 |

| I/O PINS .....                                       | 26 |

| SYSTEM COUNTER .....                                 | 27 |

| CLK REGISTER .....                                   | 28 |

| LOCKS .....                                          | 30 |

| MAIN MEMORY .....                                    | 30 |

| MAIN RAM .....                                       | 31 |

| MAIN ROM .....                                       | 32 |

| CHARACTER DEFINITIONS .....                          | 32 |

| LOG AND ANTI-LOG TABLES .....                        | 34 |

| SINE TABLE .....                                     | 34 |

| BOOT LOADER AND SPIN INTERPRETER .....               | 34 |

| CHAPTER 2 : SPIN LANGUAGE REFERENCE .....            | 35 |

| STRUCTURE OF PROPELLER OBJECTS/SPIN .....            | 36 |

| CATEGORICAL LISTING OF PROPELLER SPIN LANGUAGE ..... | 38 |

| Block Designators .....                              | 38 |

| Configuration .....                                  | 38 |

| Cog Control .....                                    | 39 |

| Process Control .....                                | 39 |

| Flow Control .....                                   | 39 |

| Memory .....                                         | 40 |

| Directives .....                                     | 41 |

| Registers .....                                      | 41 |

| Constants .....                                      | 42 |

| Variable .....                                       | 42 |

| Unary Operators .....                                | 42 |

| Binary Operators .....                               | 43 |

# Table of Contents

---

|                               |     |

|-------------------------------|-----|

| Syntax Symbols .....          | 44  |

| SPIN LANGUAGE ELEMENTS .....  | 45  |

| Symbol Rules .....            | 45  |

| Value Representations .....   | 45  |

| Syntax Definitions .....      | 46  |

| ABORT .....                   | 47  |

| BYTE .....                    | 51  |

| BYTEFILL .....                | 57  |

| BYTEMOVE .....                | 58  |

| CASE .....                    | 59  |

| CHIPVER .....                 | 62  |

| CLKFREQ .....                 | 63  |

| _CLKFREQ .....                | 65  |

| CLKMODE .....                 | 67  |

| _CLKMODE .....                | 68  |

| CLKSET .....                  | 71  |

| CNT .....                     | 73  |

| COGID .....                   | 75  |

| COGINIT .....                 | 76  |

| COGNEW .....                  | 78  |

| COGSTOP .....                 | 83  |

| CON .....                     | 84  |

| CONSTANT .....                | 91  |

| CONSTANTS (PRE-DEFINED) ..... | 93  |

| CTRA, CTRB .....              | 95  |

| DAT .....                     | 99  |

| DIRA, DIRB .....              | 104 |

| FILE .....                    | 107 |

| FLOAT .....                   | 108 |

| _FREE .....                   | 110 |

| FRQA, FRQB .....              | 111 |

| IF .....                      | 112 |

| IFNOT .....                   | 117 |

| INA, INB .....                | 118 |

| LOCKCLR .....                 | 120 |

| LOCKNEW .....                 | 122 |

| LOCKRET .....                 | 125 |

| LOCKSET .....                 | 126 |

| LONG .....                    | 128 |

| LONGFILL .....                | 134 |

| LONGMOVE .....                | 135 |

| LOOKDOWN, LOOKDOWNZ .....     | 136 |

| LOOKUP, LOOKUPZ .....         | 138 |

# Table of Contents

---

|                                                          |     |

|----------------------------------------------------------|-----|

| NEXT .....                                               | 140 |

| OBJ .....                                                | 141 |

| OPERATORS .....                                          | 143 |

| OUTA, OUTB .....                                         | 175 |

| PAR .....                                                | 178 |

| PHSA, PHSB .....                                         | 180 |

| PRI .....                                                | 181 |

| PUB .....                                                | 182 |

| QUIT .....                                               | 186 |

| REBOOT .....                                             | 187 |

| REPEAT .....                                             | 188 |

| RESULT .....                                             | 194 |

| RETURN .....                                             | 196 |

| ROUND .....                                              | 198 |

| SPR .....                                                | 200 |

| _STACK .....                                             | 202 |

| STRCOMP .....                                            | 203 |

| STRING .....                                             | 205 |

| STRSIZE .....                                            | 206 |

| SYMBOLS .....                                            | 207 |

| TRUNC .....                                              | 209 |

| VAR .....                                                | 210 |

| VCFG .....                                               | 213 |

| VSCL .....                                               | 216 |

| WAITCNT .....                                            | 218 |

| WAITPEQ .....                                            | 222 |

| WAITPNE .....                                            | 224 |

| WAITVID .....                                            | 225 |

| WORD .....                                               | 227 |

| WORDFILL .....                                           | 234 |

| WORDMOVE .....                                           | 235 |

| _XINFREQ .....                                           | 236 |

| CHAPTER 3 : ASSEMBLY LANGUAGE REFERENCE .....            | 238 |

| THE STRUCTURE OF PROPELLER ASSEMBLY .....                | 238 |

| Cog Memory .....                                         | 240 |

| Where Does an Instruction Get Its Data? .....            | 240 |

| Don't Forget the Literal Indicator '#'. .....            | 241 |

| Literals Must Fit in 9 Bits .....                        | 241 |

| Global and Local Labels .....                            | 242 |

| CATEGORICAL LISTING OF PROPELLER ASSEMBLY LANGUAGE ..... | 243 |

| Directives .....                                         | 243 |

| Configuration .....                                      | 243 |

---

# Table of Contents

---

|                                                   |     |

|---------------------------------------------------|-----|

| Cog Control .....                                 | 243 |

| Process Control .....                             | 243 |

| Conditions .....                                  | 243 |

| Flow Control .....                                | 245 |

| Effects .....                                     | 245 |

| Main Memory Access .....                          | 245 |

| Common Operations .....                           | 245 |

| Constants .....                                   | 247 |

| Registers .....                                   | 248 |

| Unary Operators .....                             | 248 |

| Binary Operators .....                            | 249 |

| ASSEMBLY LANGUAGE ELEMENTS .....                  | 250 |

| Syntax Definitions .....                          | 250 |

| Opcodes and Opcode Tables .....                   | 251 |

| Concise Truth Tables .....                        | 252 |

| Propeller Assembly Instruction Master Table ..... | 253 |

| ABS .....                                         | 257 |

| ABSNEG .....                                      | 258 |

| ADD .....                                         | 259 |

| ADDBABS .....                                     | 260 |

| ADDS .....                                        | 261 |

| ADDSX .....                                       | 262 |

| ADDX .....                                        | 264 |

| AND .....                                         | 266 |

| ANDN .....                                        | 267 |

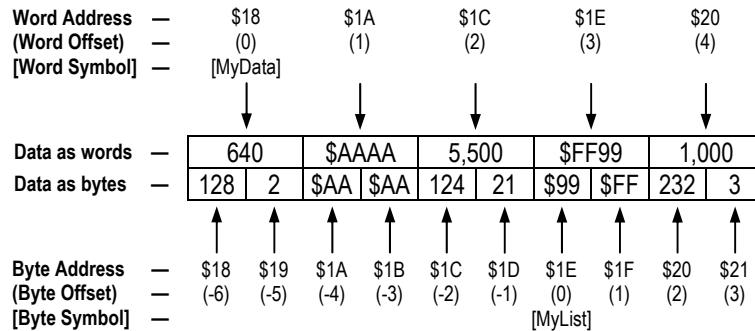

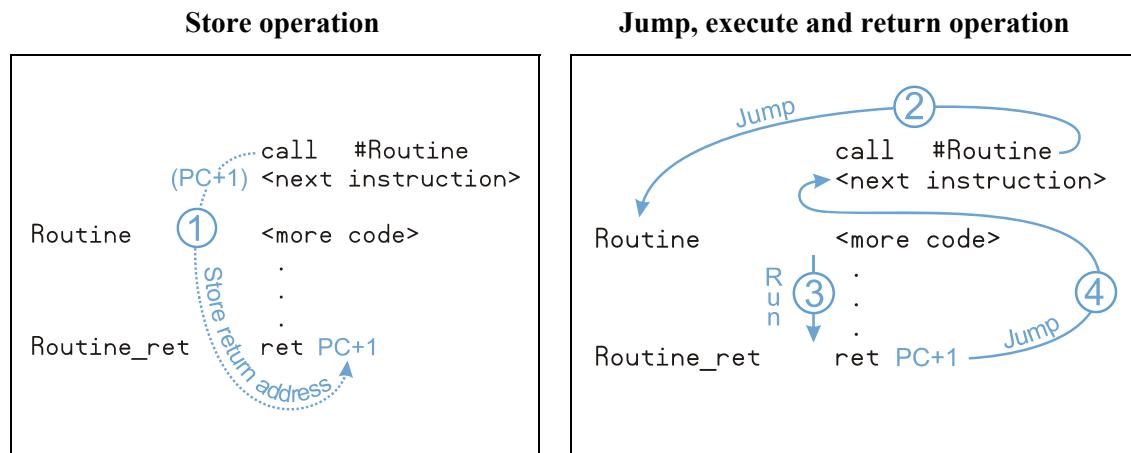

| CALL .....                                        | 268 |

| CLKSET .....                                      | 271 |

| CMP .....                                         | 272 |

| CMPS .....                                        | 274 |

| CMPSUB .....                                      | 276 |

| CMPSX .....                                       | 277 |

| CMPX .....                                        | 280 |

| CNT .....                                         | 282 |

| COGID .....                                       | 283 |

| COGINIT .....                                     | 284 |

| COGSTOP .....                                     | 286 |

| CONDITIONS ( IF_x ) .....                         | 287 |

| CTRA, CTRB .....                                  | 288 |

| DIRA, DIRB .....                                  | 289 |

| DJNZ .....                                        | 290 |

| EFFECTS ( WC, WZ, WR, NR ) .....                  | 291 |

| FIT .....                                         | 292 |

| FRQA, FRQB .....                                  | 293 |

## Table of Contents

---

|                         |     |

|-------------------------|-----|

| HUBOP .....             | 294 |

| IF_x (CONDITIONS) ..... | 295 |

| INA, INB .....          | 297 |

| JMP .....               | 298 |

| JMPRET .....            | 300 |

| LOCKCLR .....           | 303 |

| LOCKNEW .....           | 304 |

| LOCKRET .....           | 305 |

| LOCKSET .....           | 306 |

| MAX .....               | 307 |

| MAXS .....              | 308 |

| MIN .....               | 309 |

| MINS .....              | 310 |

| MOV .....               | 311 |

| MOVD .....              | 312 |

| MOVI .....              | 313 |

| MOVS .....              | 314 |

| MUXC .....              | 315 |

| MUXNC .....             | 316 |

| MUXNZ .....             | 317 |

| MUXZ .....              | 318 |

| NEG .....               | 319 |

| NEGC .....              | 320 |

| NEGNC .....             | 321 |

| NEGNZ .....             | 322 |

| NEGZ .....              | 323 |

| NOP .....               | 324 |

| NR .....                | 325 |

| OPERATORS .....         | 326 |

| OR .....                | 327 |

| ORG .....               | 328 |

| OUTA, OUTB .....        | 330 |

| PAR .....               | 331 |

| PHSA, PHSB .....        | 332 |

| RCL .....               | 333 |

| RCR .....               | 334 |

| RDBYTE .....            | 335 |

| RDLONG .....            | 336 |

| RDWORD .....            | 337 |

| REGISTERS .....         | 338 |

| RES .....               | 339 |

| RET .....               | 342 |

| REV .....               | 343 |

# Table of Contents

---

|                                                    |     |

|----------------------------------------------------|-----|

| ROL .....                                          | 344 |

| ROR .....                                          | 345 |

| SAR .....                                          | 346 |

| SHL .....                                          | 347 |

| SHR .....                                          | 348 |

| SUB .....                                          | 349 |

| SUBABS .....                                       | 350 |

| SUBS .....                                         | 351 |

| SUBSX .....                                        | 352 |

| SUBX .....                                         | 354 |

| SUMC .....                                         | 356 |

| SUMNC .....                                        | 357 |

| SUMNZ .....                                        | 358 |

| SUMZ .....                                         | 359 |

| SYMBOLS .....                                      | 360 |

| TEST .....                                         | 362 |

| TESTN .....                                        | 363 |

| TJNZ .....                                         | 364 |

| TJZ .....                                          | 365 |

| VCFG .....                                         | 366 |

| VSCL .....                                         | 367 |

| WAITCNT .....                                      | 368 |

| WAITPEQ .....                                      | 369 |

| WAITPNE .....                                      | 370 |

| WAITVID .....                                      | 371 |

| WC .....                                           | 372 |

| WR .....                                           | 373 |

| WRBYTE .....                                       | 374 |

| WRLONG .....                                       | 375 |

| WRWORD .....                                       | 376 |

| WZ .....                                           | 377 |

| XOR .....                                          | 378 |

| APPENDIX A: RESERVED WORD LIST .....               | 379 |

| APPENDIX B: MATH SAMPLES AND FUNCTION TABLES ..... | 380 |

| INDEX .....                                        | 386 |

# Preface

Thank you for purchasing a Propeller chip. You will be spinning your own programs in no time!

Propeller chips are incredibly capable multiprocessor microcontrollers; the much-anticipated result of over eight years of the intense efforts of Chip Gracey and the entire Parallax Engineering Team.

This book is intended to be a reference guide to Propeller chips and their native programming languages, Spin and Propeller Assembly. For a programming tutorial and Propeller Tool details, please refer to the on-line help that is installed with the Propeller Tool software. Have fun!

Despite our best efforts, there are bound to be questions unanswered by this manual alone. Check out our Propeller chip discussion forum – (accessible from [www.parallax.com](http://www.parallax.com) via the Support → Discussion Forums menu) – this is a group especially for Propeller users where you can post your questions or review discussions that may have already answered yours.

NEW

In addition to the forum, visit the Propeller Object Exchange ([obex.parallax.com](http://obex.parallax.com)) for free access to hundreds of Propeller objects made by customers and Parallax Engineers. Besides being immediately useful for your own applications, Propeller objects written by various authors are a great resource for studying techniques and tricks employed by the very active Propeller community.

### Editor's Note: About Version 1.1

The major content additions, corrections, and deletions that were made to Propeller Manual v1.0 to produce this edition are highlighted in the PDF version of this document of Propeller Manual v1.1. We recommend that if you previously read the original edition of the Propeller Manual. A complete record of changes can be found in the Propeller Manual Supplement and Errata v1.4. Both documents are available for download at [www.parallax.com/Propeller](http://www.parallax.com/Propeller).

Most significantly, the former *Chapter 2: Using the Propeller Tool*, was moved to the Propeller Tool's Online Help system where it can be updated frequently to stay in sync with the enhancements to the development software. Likewise, the former *Chapter 3: Propeller Programming Tutorial* was also moved to the Propeller Tool's Online Help system where it can be expanded more readily.

## Preface

---

Additional important changes include:

- An additional Propeller Assembly instruction was added; **TESTN** (see page 347)

- The following sections were rewritten for clarity:

- **ADDSX** on page 262

- **ADDX** on page 264

- **CALL** on page 268

- **CMPSX** on page 277

- **CMPX** on page 280

- **JMPRET** on page 300

- **ORG** on page 328

- **RES** on page 339

- **RET** on page 342

- **SUBSX** on page 352

- **SUBX** on page 354

- Extensive enhancements to the following sections were made to provide detail on previously undocumented features:

- **BYTE** on page 51

- **COGINIT** on page 76

- **COGNEW** on page 78

- **DAT** on page 99

- **LONG** on page 128

- **WORD** on page 227

- Extensive revisions were made to The Structure of Propeller Assembly section beginning on page 238, as well as to the start of the Assembly Language Elements section which begins on page 250.

- Concise Truth Tables have been added above the Explanation section for each Propeller Assembly instruction. Each of these truth tables include key value and flag combinations that reveal important aspects of the related instruction's nature.

- Individual Effects and Registers were given their own sections in the Assembly Language Reference for easier locating while scanning the manual.

- Multiplication, Division, and Square Root examples were added to Appendix B.

- Hundreds of important details were enhanced or corrected throughout. See the manual's PDF version, or the Supplement and Errata v1.4, for more information.

## Chapter 1: Introducing the Propeller Chip

This chapter describes the Propeller chip hardware. To fully understand and use the Propeller effectively, it's important to first understand its hardware architecture. This chapter presents the details of the hardware such as package types, package sizes, pin descriptions, and functions.

### Concept

The Propeller chip is designed to provide high-speed processing for embedded systems while maintaining low current consumption and a small physical footprint. In addition to being fast, the Propeller provides flexibility and power through its eight processors, called cogs, that can perform simultaneous independent or cooperative tasks, all while maintaining a relatively simple architecture that is easy to learn and utilize.

The resulting design of the Propeller frees application developers from common complexities of embedded systems programming. For example:

- The memory map is flat. There is no need for paging schemes with blocks of code, data or variables. This is a big time-saver during application development.

- Asynchronous events are easier to handle than they are with devices that use interrupts. The Propeller has no need for interrupts; just assign some cogs to individual, high-bandwidth tasks and keep other cogs free and unencumbered. The result is a more responsive application that is easier to maintain.

- The Propeller Assembly language features conditional execution and optional result writing for each individual instruction. This makes critical, multi-decision blocks of code more consistently timed; event handlers are less prone to jitter and developers spend less time padding, or squeezing, cycles here and there.

# Introducing the Propeller Chip

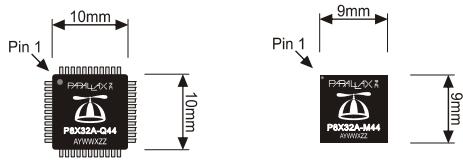

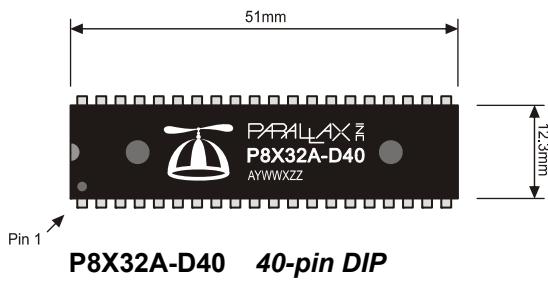

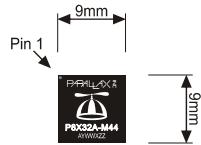

## Package Types

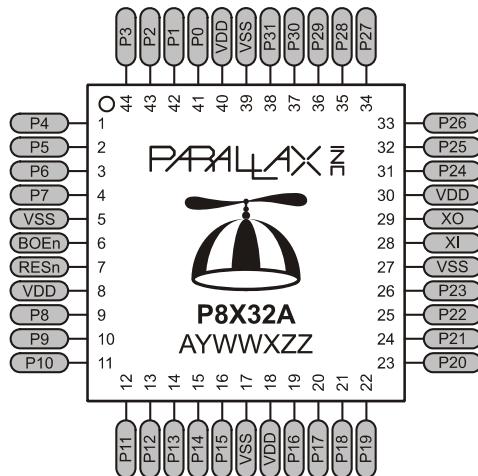

The Propeller chip is available in the package types shown here.

**P8X32A-Q44**

**44-pin LQFP**

**P8X32A-M44**

**44-pin QFN**

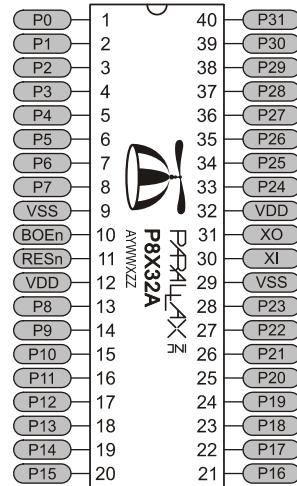

## Pin Descriptions

**Table 1-1: Pin Descriptions**

IMPROVED

| Pin Name | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0 – P31 | I/O       | <p>General purpose I/O Port A. Can source/sink 40 mA each at 3.3 VDC. Logic threshold is <math>\approx \frac{1}{2}</math> VDD; 1.65 VDC @ 3.3 VDC.</p> <p>The pins shown below have a special purpose upon power-up/reset but are general purpose I/O afterwards.</p> <ul style="list-style-type: none"> <li>P28 - I2C SCL connection to optional, external EEPROM.</li> <li>P29 - I2C SDA connection to optional, external EEPROM.</li> <li>P30 - Serial Tx to host.</li> <li>P31 - Serial Rx from host.</li> </ul> |

| VDD      | ---       | 3.3 volt power (2.7 – 3.3 VDC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VSS      | ---       | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BOEn     | I         | Brown Out Enable (active low). Must be connected to either VDD or VSS. If low, RESn becomes a weak output (delivering VDD through 5 K $\Omega$ ) for monitoring purposes but can still be driven low to cause reset. If high, RESn is CMOS input with Schmitt Trigger.                                                                                                                                                                                                                                               |

| RESn     | I/O       | Reset (active low). When low, resets the Propeller chip: all cogs disabled and I/O pins floating. Propeller restarts 50 ms after RESn transitions from low to high.                                                                                                                                                                                                                                                                                                                                                  |

| XI       | I         | Crystal Input. Can be connected to output of crystal/oscillator pack (with XO left disconnected), or to one leg of crystal (with XO connected to other leg of crystal or resonator) depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                                                                                                                                                            |

| XO       | O         | Crystal Output. Provides feedback for an external crystal, or may be left disconnected depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                                                                                                                                                                                                                                                         |

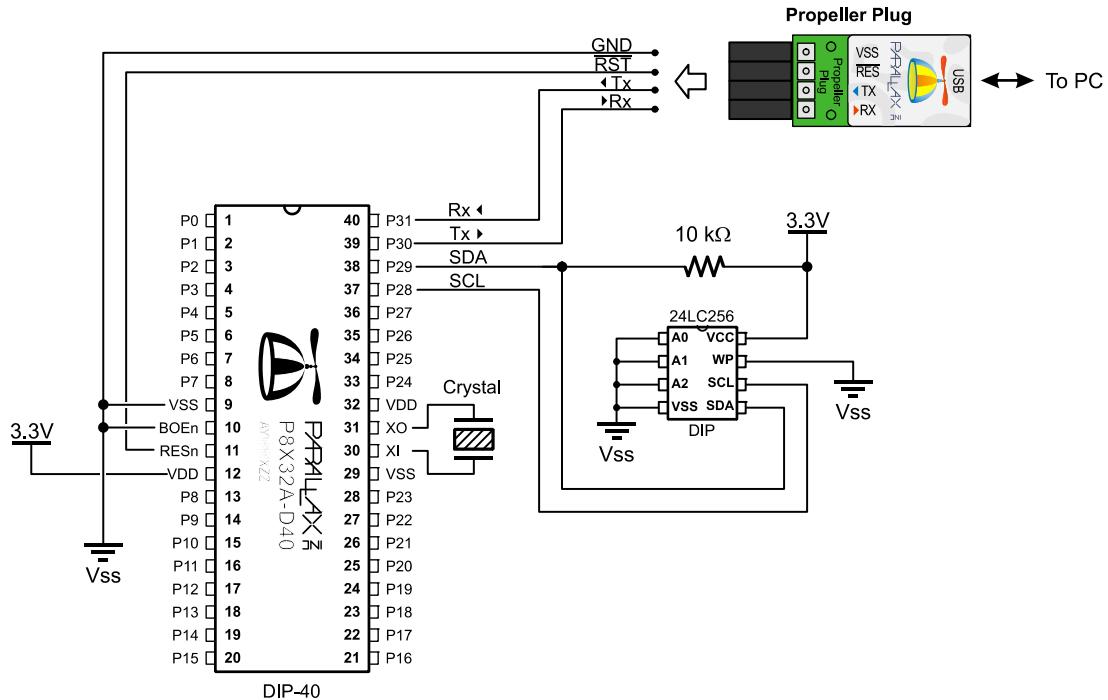

The Propeller (P8X32A) has 32 I/O pins (Port A, pins P0 through P31). Four of these I/O pins, P28-P31 have a special purpose upon power-up/reset. At power-up/reset, pins P30 and P31 communicate with a host for programming and P28 and P29 interface to an external 32 KB EEPROM (24LC256).

# Introducing the Propeller Chip

## Specifications

**Table 1-2: Specifications**

|                               |                                                                                                 |

|-------------------------------|-------------------------------------------------------------------------------------------------|

| Model                         | P8X32A                                                                                          |

| Power Requirements            | 3.3 volts DC. (Max current draw must be limited to 300 mA).                                     |

| External Clock Speed          | DC to 80 MHz (4 MHz to 8 MHz with Clock PLL running)                                            |

| System Clock Speed            | DC to 80 MHz                                                                                    |

| Internal RC Oscillator        | 12 MHz or 20 kHz (approximate; may range from 8 MHz – 20 MHz, or 13 kHz – 33 kHz, respectively) |

| Main RAM/ROM                  | 64 K bytes; 32 KB RAM + 32 KB ROM                                                               |

| Cog RAM                       | 512 x 32 bits each                                                                              |

| RAM/ROM Organization          | Long (32-bit), Word (16-bit), or Byte (8-bit) addressable                                       |

| I/O pins                      | 32 CMOS signals with VDD/2 input threshold.                                                     |

| Current Source/Sink per I/O   | 40 mA                                                                                           |

| Current Draw @ 3.3 vdc, 70 °F | 500 $\mu$ A per MIPS (MIPS = Freq in MHz / 4 * Number of Active Cogs)                           |

## Hardware Connections

Figure 1-1 shows an example wiring diagram that provides host and EEPROM access to the Propeller chip. In this example the host access is achieved through the Propeller Plug device (a USB to TTL serial converter).

**Figure 1-1: Example wiring diagram that allows for programming the Propeller chip and an external 32 Kbyte EEPROM, and running the Propeller with an external crystal.**

## Boot Up Procedure

Upon power-up (+ 100 ms), RESn low-to-high, or software reset:

1. The Propeller chip starts its internal clock in slow mode ( $\approx 20$  kHz), delays for 50 ms (reset delay), switches the internal clock to fast mode ( $\approx 12$  MHz), and then loads and runs the built-in Boot Loader program in the first processor (Cog 0).

2. The Boot Loader performs one or more of the following tasks, in order:

- a. Detects communication from a host, such as a PC, on pins P30 and P31. If communication from a host is detected, the Boot Loader converses with the host to identify the Propeller chip and possibly download a program into Main RAM and optionally into an external 32 KB EEPROM.

- b. If no host communication was detected, the Boot Loader looks for an external 32 KB EEPROM (24LC256) on pins P28 and P29. If an EEPROM is detected, the entire 32 KB data image is loaded into the Propeller chip's Main RAM.

- c. If no EEPROM was detected, the boot loader stops, Cog 0 is terminated, the Propeller chip goes into shutdown mode, and all I/O pins are set to inputs.

3. If either step 2a or 2b was successful in loading a program into the Main RAM, and a suspend command was not given by the host, then Cog 0 is reloaded with the built-in Spin Interpreter and the user code is run from Main RAM.

## Run-Time Procedure

A Propeller Application is a user program compiled into its binary form and downloaded to the Propeller chip's RAM and, possibly, external EEPROM. The application consists of code written in the Propeller chip's Spin language (high-level code) with optional Propeller Assembly language components (low-level code). Code written in the Spin language is interpreted during run time by a cog running the Spin Interpreter while code written in Propeller Assembly is run in its pure form directly by a cog. Every Propeller Application consists of at least a little Spin code and may actually be written entirely in Spin or with various amounts of Spin and assembly. The Propeller chip's Spin Interpreter is started in Step 3 of the Boot Up Procedure, above, to get the application running.

Once the boot-up procedure is complete and an application is running in Cog 0, all further activity is defined by the application itself. The application has complete control over things like the internal clock speed, I/O pin usage, configuration registers, and when, what and how

many cogs are running at any given time. All of this is variable at run time, as controlled by the application, including the internal clock speed.

## Shutdown Procedure

When the Propeller goes into shutdown mode, the internal clock is stopped causing all cogs to halt and all I/O pins are set to input direction (high impedance). Shutdown mode is triggered by one of the three following events:

- 1) VDD falling below the brown-out threshold ( $\approx 2.7$  VDC), when the brown-out circuit is enabled,

- 2) the RESn pin going low, or

- 3) the application requesting a reboot (see the **REBOOT** command, page 187).

Shutdown mode is discontinued when the voltage level rises above the brown-out threshold and the RESn pin is high.

# Introducing the Propeller Chip

## Block Diagram

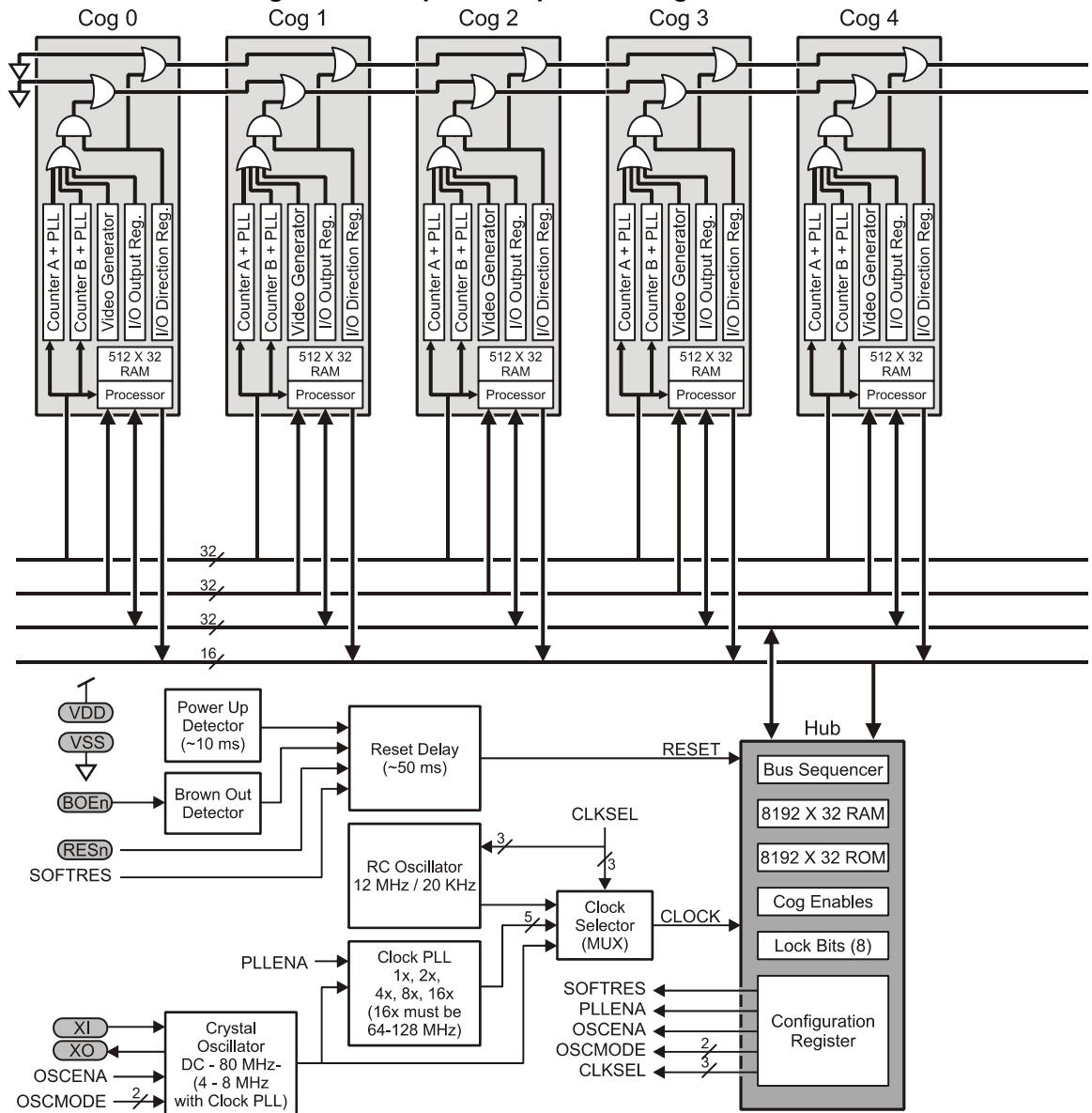

Figure 1-2: Propeller Chip Block Diagram

# 1: Introducing the Propeller Chip

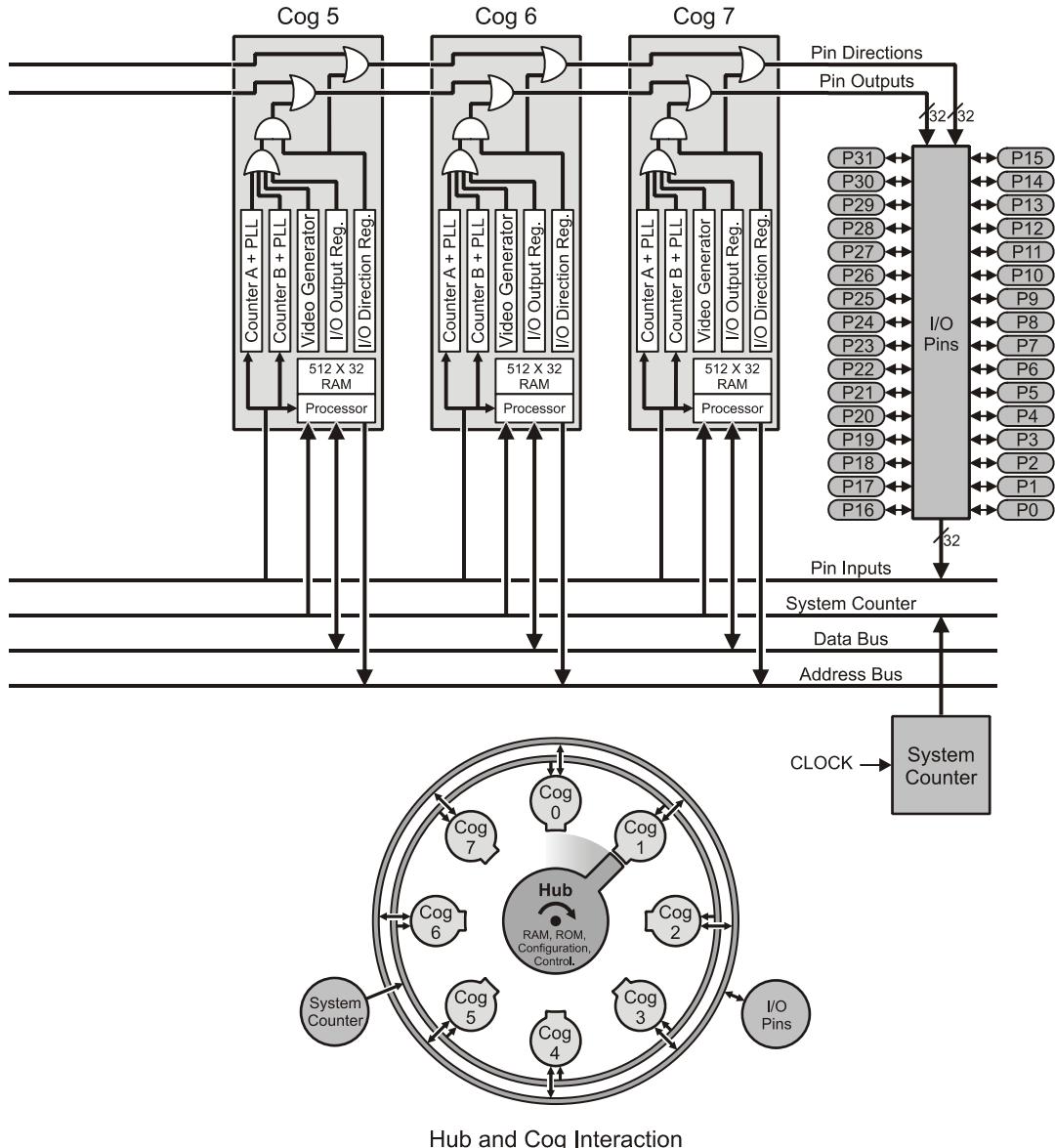

Cog and Hub interaction is critical to the Propeller chip. The Hub controls which cog can access mutually exclusive resources, such as Main RAM/ROM, configuration registers, etc. The Hub gives exclusive access to every cog one at a time in a “round robin” fashion, regardless of how many cogs are running, in order to keep timing deterministic.

## Shared Resources

There are two types of shared resources in the Propeller: 1) common, and 2) mutually exclusive. Common resources can be accessed at any time by any number of cogs. Mutually exclusive resources can also be accessed by all cogs, but only by one cog at a time. The common resources are the I/O pins and the System Counter. All other shared resources are mutually exclusive by nature and access to them is controlled by the Hub. See the Hub section on page 24.

## System Clock

The System Clock (shown as “CLOCK” in Figure 1-2) is the central clock source for nearly every component of the Propeller chip. The System Clock’s signal comes from one of three possible sources: 1) the Internal RC Oscillator, 2) the Clock Phase-Locked Loop (PLL), or 3) the Crystal Oscillator (an internal circuit that is fed by an external crystal or crystal/oscillator pack). The source is determined by the CLK register’s settings, which is selectable at compile time or at run time. The only components that don’t use the System Clock directly are the Hub and Bus; they divide the System Clock by two (2).

## Cogs (processors)

The Propeller contains eight (8) processors, called cogs, numbered 0 to 7. Each cog contains the same components (see Figure 1-2): a Processor block, local 2 KB RAM configured as 512 longs (512 x 32 bits), two Counter Modules with PLLs, a Video Generator, I/O Output Register, I/O Direction Register, and other registers not shown in the diagram. See Table 1-3 for a complete list of cog registers. Each cog is designed exactly the same and can run tasks independently from the others.

All eight cogs are driven from the same clock source, the System Clock, so they each maintain the same time reference and all active cogs execute instructions simultaneously. See System Clock, above. They also all have access to the same shared resources, like I/O pins, Main RAM, and the System Counter. See Shared Resources, above.

Cogs can be started and stopped at run time and can be programmed to perform tasks simultaneously, either independently or with coordination from other cogs through Main RAM. Regardless of the nature of their use, the Propeller application designer has full control over how and when each cog is employed; there is no compiler-driven or operating system-driven splitting of tasks between multiple cogs. This empowers the developer to deliver absolutely deterministic timing, power consumption, and response to the embedded application.

Each cog has its own RAM, called Cog RAM, which contains 512 registers of 32 bits each. The Cog RAM is all general purpose RAM except for the last 16 registers, which are special purpose registers, as described in Table 1-3. The Cog RAM is used for executable code, data, variables, and the last 16 locations serve as interfaces to the System Counter, I/O pins, and local cog peripherals.

When a cog is booted up, locations 0 (\$000) through 495 (\$1EF) are loaded sequentially from Main RAM / ROM and its special purpose locations, 496 (\$1F0) through 511 (\$1FF) are cleared to zero. After loading, the cog begins executing instructions, starting at location 0 of Cog RAM. It will continue to execute code until it is stopped or rebooted by either itself or another cog, or a reset occurs.

IMPROVED

Table 1-3: Cog RAM Special Purpose Registers

| Cog RAM Map | Address | Name              | Type                    | Description                               |

|-------------|---------|-------------------|-------------------------|-------------------------------------------|

| \$000       | \$1F0   | PAR               | Read-Only <sup>1</sup>  | Boot Parameter, p. 178, 331               |

|             | \$1F1   | CNT               | Read-Only <sup>1</sup>  | System Counter, p. 73, 282                |

|             | \$1F2   | INA               | Read-Only <sup>1</sup>  | Input States for P31–P0, p. 118, 297      |

|             | \$1F3   | INB <sup>3</sup>  | Read-Only <sup>1</sup>  | Input States for P63–P32, p. 118, 297     |

|             | \$1F4   | OUTA              | Read/Write              | Output States for P3–P0, p. 175, 330      |

|             | \$1F5   | OUTB <sup>3</sup> | Read/Write              | Output States for P63–P32, p. 175, 330    |

|             | \$1F6   | DIRA              | Read/Write              | Direction States for P31–P0, p. 104, 456  |

|             | \$1F7   | DIRB <sup>3</sup> | Read/Write              | Direction States for P63–P32, p. 104, 456 |

|             | \$1F8   | CTRA              | Read/Write              | Counter A Control, p. 95, 288             |

|             | \$1F9   | CTRB              | Read/Write              | Counter B Control, p. 95, 288             |

|             | \$1FA   | FRQA              | Read/Write              | Counter A Frequency, p. 111, 293          |

|             | \$1FB   | FRQB              | Read/Write              | Counter B Frequency, p. 111, 293          |

|             | \$1FC   | PHSA              | Read/Write <sup>2</sup> | Counter A Phase, p. 180, 332              |

|             | \$1FD   | PHSB              | Read/Write <sup>2</sup> | Counter B Phase, p. 180, 332              |

|             | \$1FE   | VCFG              | Read/Write              | Video Configuration, p. 213, 366          |

| \$1FF       | \$1FF   | VSCL              | Read/Write              | Video Scale, p. 216, 367                  |

**Note 1:** For Propeller Assembly, only accessible as a source register (i.e., `mov dest, source`). See the Assembly language sections for PAR, page 331; CNT, page 282, and INA, INB, page 297.

**Note 2:** For Propeller Assembly, only readable as a source register (i.e., `mov dest, source`); read modify-write not possible as a destination register. See the Assembly language section for PHSA, PHSB on page 332.

**Note 3:** Reserved for future use.

## Introducing the Propeller Chip

---

Each Special Purpose Register may be accessed via:

- 1) its physical register address (Propeller Assembly),

- 2) its predefined name (Spin or Propeller Assembly), or

- 3) the register array variable (**SPR**) with an index of 0 to 15 (Spin).

The following are examples in Propeller Assembly:

```

MOV $1F4, #$FF      ' Set OUTA 7:0 high

MOV OUTA, #$FF      ' Same as above

```

The following are examples in Spin:

```

SPR[$4] := $FF      ' Set OUTA 7:0 high

OUTA := $FF          ' Same as above

```

## Hub

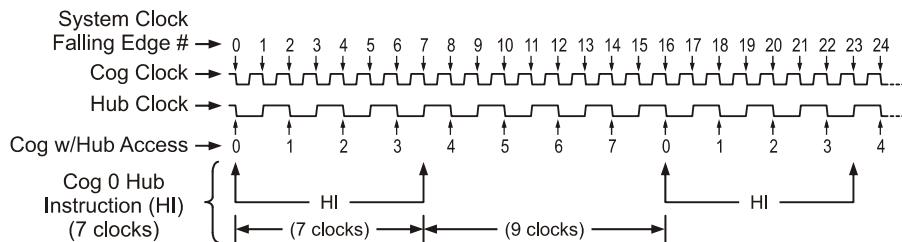

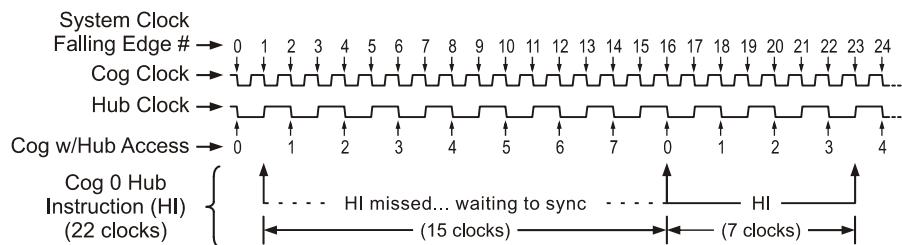

To maintain system integrity, mutually exclusive resources must not be accessed by more than one cog at a time. The Hub maintains this integrity by controlling access to mutually exclusive resources, giving each cog a turn to access them in a “round robin” fashion from Cog 0 through Cog 7 and back to Cog 0 again. The Hub, and the bus it controls, runs at half the System Clock rate. This means that the Hub gives a cog access to mutually exclusive resources once every 16 System Clock cycles. Hub instructions, the Propeller Assembly instructions that access mutually exclusive resources, require 7 cycles to execute but they first need to be synchronized to the start of the hub access window. It takes up to 15 cycles (16 minus 1, if we just missed it) to synchronize to the hub access window plus 7 cycles to execute the hub instruction, so hub instructions take from 7 to 22 cycles to complete.

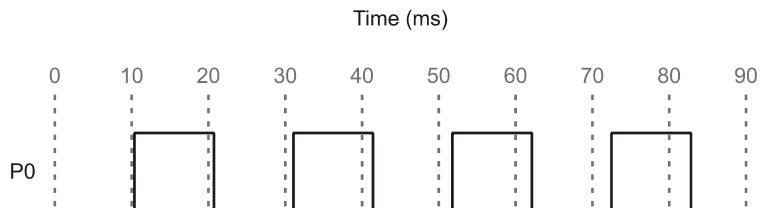

Figure 1-3 and Figure 1-4 show examples where Cog 0 has a hub instruction to execute. Figure 1-3 shows the best-case scenario; the hub instruction was ready right at the start of that cog’s access window. The hub instruction executes immediately (7 cycles) leaving an additional 9 cycles for other instructions before the next hub access window arrives.

**Figure 1-3: Cog-Hub Interaction – Best Case Scenario**

Figure 1-4 shows the worst-case scenario; the hub instruction was ready on the cycle right after the start of Cog 0's access window; it just barely missed it. The cog waits until the next hub access window (15 cycles later) then the hub instruction executes (7 cycles) for a total of 22 cycles for that hub instruction. Again, there are 9 additional cycles after the hub instruction for other instructions to execute before the next hub access window arrives. To get the most efficiency out of Propeller Assembly routines that have to frequently access mutually exclusive resources, it can be beneficial to interleave non-hub instructions with hub instructions to lessen the number of cycles waiting for the next hub access window. Since most Propeller Assembly instructions take 4 clock cycles, two such instructions can be executed in between otherwise contiguous hub instructions.

**Figure 1-4: Cog-Hub Interaction – Worst Case Scenario**

Keep in mind that a particular cog's hub instructions do not, in any way, interfere with other cogs' instructions because of the Hub mechanism. Cog 1, for example, may start a hub instruction during System Clock cycle 2, in both of these examples, possibly overlapping its execution with that of Cog 0 without any ill effects. Meanwhile, all other cogs can continue executing non-hub instructions, or awaiting their individual hub access windows regardless of what the others are doing.

IMPROVED

## I/O Pins

The Propeller has 32 I/O pins, 28 of which are entirely general purpose. Four I/O pins (28 - 31) have a special purpose at Boot Up and are available for general purpose use afterwards; see the Boot Up Procedure section on page 18. After boot up, any I/O pins can be used by any cogs at any time since I/O pins are one of the common resources. It is up to the application developer to ensure that no two cogs try to use the same I/O pin for conflicting purposes during run-time.

For details of the I/O hardware, refer to the internals of the cogs in Figure 1-2 on page 20 while reading the following explanation.

Each cog has its own 32-bit I/O Direction Register and 32-bit I/O Output Register to influence the directions and output states of the Propeller chip's corresponding 32 I/O pins. A cog's desired I/O directions and output states is communicated through the entire cog collective to ultimately become what is called "Pin Directions" and "Pin Outputs" in the upper right corner of Figure 1-2 on page 20.

The cog collective determines Pin Directions and Pin Outputs as follows:

1. Pin Directions are the result of OR'ing the Direction Registers of the cogs together.

2. Pin Outputs are the result of OR'ing the output states of the cogs together. A cog's output state consists of the bits of its I/O modules (the Counters, the Video Generator, and the I/O Output Register) OR'd together then AND'd with the bits of its Direction Register.

In essence, each I/O pin's direction and output state is the "wired-OR" of the entire cog collective. This allows the cogs to access and influence the I/O pins simultaneously without the need for any resource arbiter and without any possibility of electrical contention between the cogs.

The result of this I/O pin wiring configuration can easily be described in the following simple rules:

- A pin is an input only if no active cog sets it to an output.

- A pin outputs low only if all active cogs that set it to output also set it to low.

- A pin outputs high if any active cog sets it to an output and also sets it high.

Table 1-4 demonstrates a few possible combinations of the collective cogs' influence on a particular I/O pin, P12 in this example. For simplification, these examples assume that bit 12 of each cog's I/O hardware, other than its I/O Output Register, is cleared to zero (0).

Table 1-4: I/O Sharing Examples

| Bit 12 of Cogs' I/O Direction Register |                 | Bit 12 of Cogs' I/O Output Register | State of I/O Pin P12 | Rule Followed |

|----------------------------------------|-----------------|-------------------------------------|----------------------|---------------|

| Cog ID                                 | 0 1 2 3 4 5 6 7 | 0 1 2 3 4 5 6 7                     |                      |               |

| Example 1                              | 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0                     | Input                | A             |

| Example 2                              | 1 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0                     | Output Low           | B             |

| Example 3                              | 1 0 0 0 0 0 0 0 | 1 0 0 0 0 0 0 0                     | Output High          | C             |

| Example 4                              | 1 0 0 0 0 0 0 0 | 0 1 0 0 0 0 0 0                     | Output Low           | B             |

| Example 5                              | 1 1 0 0 0 0 0 0 | 0 1 0 0 0 0 0 0                     | Output High          | C             |

| Example 6                              | 1 1 1 1 1 1 1 1 | 0 1 0 1 0 0 0 0                     | Output High          | C             |

| Example 7                              | 1 1 1 1 1 1 1 1 | 0 0 0 1 0 0 0 0                     | Output High          | C             |

| Example 8                              | 1 1 1 0 1 1 1 1 | 0 0 0 1 0 0 0 0                     | Output Low           | B             |

**Note:** For the I/O Direction Register, a 1 in a bit location sets the corresponding I/O pin to the output direction while a 0 sets it to an input direction.

Any cog that is shut down has its Direction Register and output states cleared to zero, effectively removing it from influencing the final state of the I/O pins that the remaining active cogs are controlling.

Each cog also has its own 32-bit Input Register. This input register is really a pseudo-register; every time it is read, the actual states of the I/O pins are read, regardless of their input or output direction.

## System Counter

The System Counter is a global, read-only, 32-bit counter that increments once every System Clock cycle. Cogs can read the System Counter (via their CNT register, page 73) to perform timing calculations and can use the WAITCNT command (page 218) to create effective delays within their processes. The System Counter is a common resource. Every cog can read it simultaneously. The System Counter is not cleared upon startup since its practical use is for differential timing. If a cog needs to keep track of time from a specific, fixed moment in time, it simply needs to read and save the initial counter value at that moment in time, and compare all of the later counter values against that initial value.

## CLK Register

The CLK register is the System Clock configuration control; it determines the source of and the characteristics for the System Clock. More precisely, the CLK register configures the RC Oscillator, Clock PLL, Crystal Oscillator, and Clock Selector circuits. (See Figure 1-2: Propeller Chip Block Diagram on page 20.) It is configured at compile time by the `_CLKMODE` constant (page 68) and is writable at run time through the `CLKSET` Spin command (page 71) or the `CLKSET` assembly instruction (page 271). Whenever the CLK register is written, a global delay of  $\approx 75$   $\mu$ s occurs as the clock source transitions.

Whenever this register is changed, a copy of the value written should be placed in the Clock Mode value location (which is `BYTE[4]` in Main RAM) and the resulting master clock frequency should be written to the Clock Frequency value location (which is `LONG[0]` in Main RAM) so that objects which reference this data will have current information for their timing calculations. (See `CLKMODE`, page 67, and `CLKFREQ`, page 63.) When possible, it is recommended to use Spin's `CLKSET` command (page 71), since it automatically updates all the above-mentioned locations with the proper information.

NEW

Only certain bit patterns in the CLK register are valid clock modes. See the `_CLKMODE` constant on page 68 and Table 2-4 on page 69 for more information. The `Clock` object in the Propeller Library may also be useful since it provides clock modification and timing methods.

**Table 1-5: CLK Register Structure**

| Bit  | 7     | 6      | 5      | 4     | 3     | 2       | 1       | 0       |

|------|-------|--------|--------|-------|-------|---------|---------|---------|

| Name | RESET | PLLENA | OSCENA | OSCM1 | OSCM0 | CLKSEL2 | CLKSEL1 | CLKSEL0 |

**Table 1-6: CLK Register RESET (Bit 7)**

| Bit | Effect                                                                                                           |

|-----|------------------------------------------------------------------------------------------------------------------|

| 0   | Always write '0' here unless you intend to reset the chip.                                                       |

| 1   | Same as a hardware reset – reboots the chip. The Spin command <code>REBOOT</code> writes a '1' to the RESET bit. |

**Table 1-7: CLK Register PLLENA (Bit 6)**

| Bit | Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Disables the PLL circuit. The <b>RCFAST</b> and <b>RCSLOW</b> settings of the <b>_CLKMODE</b> declaration configure PLLENA this way.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | Enables the PLL circuit. Each of the <b>PLLxx</b> settings of the <b>_CLKMODE</b> declaration configures PLLENA this way at compile time. The Clock PLL internally multiplies the <b>XIN</b> pin frequency by 16. <b>OSCENA</b> must also be '1' to propagate the <b>XIN</b> signal to the Clock PLL. The Clock PLL's internal frequency must be kept within 64 MHz to 128 MHz – this translates to an <b>XIN</b> frequency range of 4 MHz to 8 MHz. Allow 100 $\mu$ s for the Clock PLL to stabilize before switching to one of its outputs via the <b>CLKSELx</b> bits. Once the Crystal Oscillator and Clock PLL circuits are enabled and stabilized, you can switch freely among all clock sources by changing the <b>CLKSELx</b> bits. |

**Table 1-8: CLK Register OSCENA (Bit 5)**

| Bit | Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Disables the Crystal Oscillator circuit. The <b>RCFAST</b> and <b>RCSLOW</b> settings of the <b>_CLKMODE</b> declaration configure OSCENA this way.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | Enables the Crystal Oscillator circuit so that a clock signal can be input to <b>XIN</b> , or so that <b>XIN</b> and <b>XOUT</b> can function together as a feedback oscillator. The <b>XINPUT</b> and <b>XTALx</b> settings of the <b>_CLKMODE</b> declaration configure OSCENA this way. The <b>OSCMx</b> bits select the operating mode of the Crystal Oscillator circuit. Note that no external resistors or capacitors are required for crystals and resonators. Allow a crystal or resonator 10 ms to stabilize before switching to a Crystal Oscillator or Clock PLL output via the <b>CLKSELx</b> bits. When enabling the Crystal Oscillator circuit, the Clock PLL may be enabled at the same time so that they can share the stabilization period. |

**Table 1-9: CLK Register OSCMx (Bits 4:3)**

| OSCMx |   | <b>_CLKMODE</b> Setting | XOUT Resistance | XIN/XOUT Capacitance | Frequency Range                |

|-------|---|-------------------------|-----------------|----------------------|--------------------------------|

| 1     | 0 |                         |                 |                      |                                |

| 0     | 0 | <b>XINPUT</b>           | Infinite        | 6 pF (pad only)      | DC to 80 MHz Input             |

| 0     | 1 | <b>XTAL1</b>            | 2000 $\Omega$   | 36 pF                | 4 to 16 MHz Crystal/Resonator  |

| 1     | 0 | <b>XTAL2</b>            | 1000 $\Omega$   | 26 pF                | 8 to 32 MHz Crystal/Resonator  |

| 1     | 1 | <b>XTAL3</b>            | 500 $\Omega$    | 16 pF                | 20 to 60 MHz Crystal/Resonator |

IMPROVED

# Introducing the Propeller Chip

| Table 1-10: CLK Register CLKSELx (Bits 2:0) |   |   |                     |                 |          |                                                                        |

|---------------------------------------------|---|---|---------------------|-----------------|----------|------------------------------------------------------------------------|

| CLKSELx                                     |   |   | _CLKMODE<br>Setting | Master<br>Clock | Source   | Notes                                                                  |

| 2                                           | 1 | 0 |                     |                 |          |                                                                        |

| 0                                           | 0 | 0 | RCFAST              | ~12 MHz         | Internal | No external parts.<br>May range from 8 MHz to 20 MHz.                  |

| 0                                           | 0 | 1 | RCSLOW              | ~20 kHz         | Internal | Very low power. No external parts.<br>May range from 13 kHz to 33 kHz. |

| 0                                           | 1 | 0 | XINPUT              | XIN             | OSC      | OSCENA must be '1'.                                                    |

| 0                                           | 1 | 1 | XTALx and PLL1X     | XIN x 1         | OSC+PLL  | OSCENA and PLLENA must be '1'.                                         |

| 1                                           | 0 | 0 | XTALx and PLL2X     | XIN x 2         | OSC+PLL  | OSCENA and PLLENA must be '1'.                                         |

| 1                                           | 0 | 1 | XTALx and PLL4X     | XIN x 4         | OSC+PLL  | OSCENA and PLLENA must be '1'.                                         |

| 1                                           | 1 | 0 | XTALx and PLL8X     | XIN x 8         | OSC+PLL  | OSCENA and PLLENA must be '1'.                                         |

| 1                                           | 1 | 1 | XTALx and PLL16X    | XIN x 16        | OSC+PLL  | OSCENA and PLLENA must be '1'.                                         |

## Locks

There are eight lock bits (also known as semaphores) available to facilitate exclusive access to user-defined resources among multiple cogs. If a block of memory is to be used by two or more cogs at once and that block consists of more than one long (four bytes), the cogs will each have to perform multiple reads and writes to retrieve or update that memory block. This leads to the likely possibility of read/write contention on that memory block where one cog may be writing while another is reading, resulting in misreads and/or miswrites.

The locks are global bits accessed through the Hub via the hub instructions: **LOCKNEW**, **LOCKRET**, **LOCKSET**, and **LOCKCLR**. Because locks are accessed only through the Hub, only one cog at a time can affect them, making this an effective control mechanism. The Hub maintains an inventory of which locks are in use and their current states, and cogs can check out, return, set, and clear locks as needed during run time. See **LOCKNEW**, 122; **LOCKRET**, 125; **LOCKSET**, 126; and **LOCKCLR**, 120 for more information.

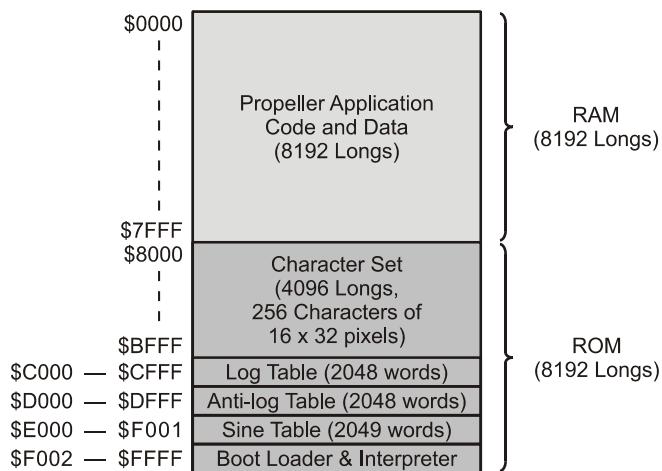

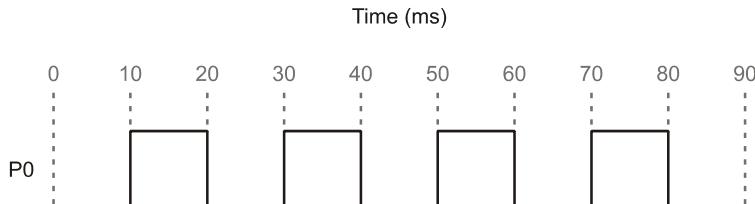

## Main Memory

The Main Memory is a block of 64 K bytes (16 K longs) that is accessible by all cogs as a mutually exclusive resource through the Hub. It consists of 32 KB of RAM and 32 KB of

ROM. The 32 KB of Main RAM is general purpose and is the destination of a Propeller Application either downloaded from a host or uploaded from the external 32 KB EEPROM. The 32 KB of Main ROM contains all the code and data resources vital to the Propeller chip's function: character definitions, log, anti-log and sine tables, and the Boot Loader and Spin Interpreter. The Main Memory organization is shown in Figure 1-5.

**Figure 1-5: Main Memory Map**

## Main RAM

The first half of Main Memory is all RAM. This space is used for your program, data, variables and stack(s); otherwise known as your Propeller Application.

When a program is loaded into the chip, either from a host or from an external EEPROM, this entire memory space is written. The first 16 locations, \$0000 – \$000F, hold initialization data used by the Boot Loader and Interpreter. Your program's executable code and data will begin at \$0010 and extend for some number of longs. The area after your executable code, extending to \$7FFF, is used as variable and stack space.

There are two values stored in the initialization area that might be of interest to your program: a long at \$0000 contains the initial master clock frequency, in Hertz, and a byte following it at \$0004 contains the initial value written into the CLK register. These two values can be read/written using their physical addresses (`LONG[$0]` and `BYTE[$4]`) and can be read by using their predefined names (`CLKFREQ` and `CLKMODE`). If you change the CLK register without using the `CLOCKSET` command, you will also need to update these two locations so that objects which reference them will have current information.

## Introducing the Propeller Chip

## Main ROM

The second half of Main Memory is all ROM. This space is used for character definitions, math functions, and the Boot Loader and Spin Interpreter.

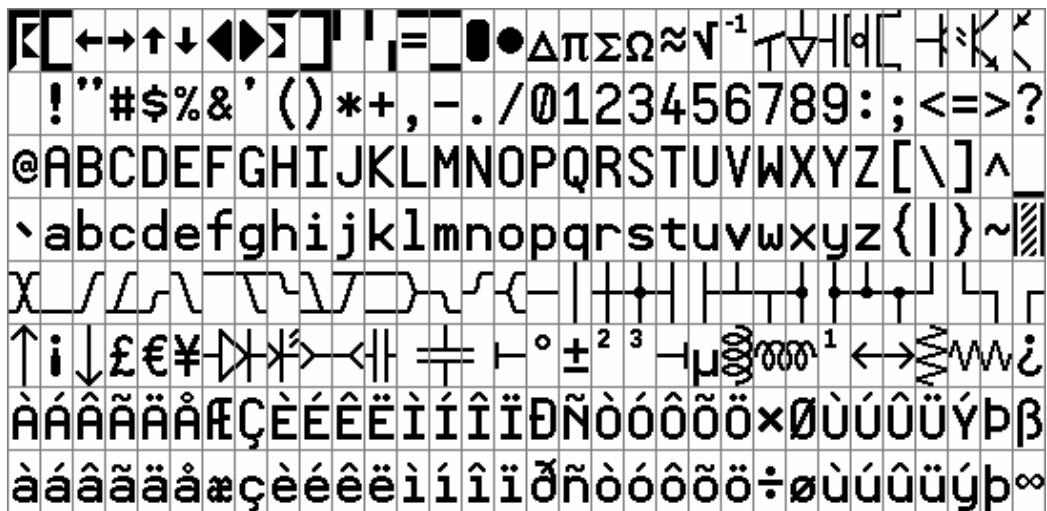

## Character Definitions

The first half of ROM is dedicated to a set of 256 character definitions. Each character definition is 16 pixels wide by 32 pixels tall. These character definitions can be used for video displays, graphical LCD's, printing, etc. The character set is based on a North American / Western European layout (Basic Latin and Latin-1 Supplement), with many specialized characters inserted. The special characters are connecting waveform and schematic building-blocks, Greek symbols commonly used in electronics, and several arrows and bullets.

**Figure 1-6: Propeller Font Characters**

The character definitions are numbered 0 to 255 from left-to-right, top-to-bottom in Figure 1-6, above. In ROM, they are arranged with each pair of adjacent even-odd characters merged together to form 32 longs. The first character pair is located in bytes \$8000-\$807F. The second pair occupies bytes \$8080-\$80FF, and so on, until the last pair fills \$BF80-\$BFFF. The Propeller Tool includes an interactive character chart (Help → View Character Chart...) that has a ROM Bitmap view which shows where and how each character resides in ROM.

# 1: Introducing the Propeller Chip

---

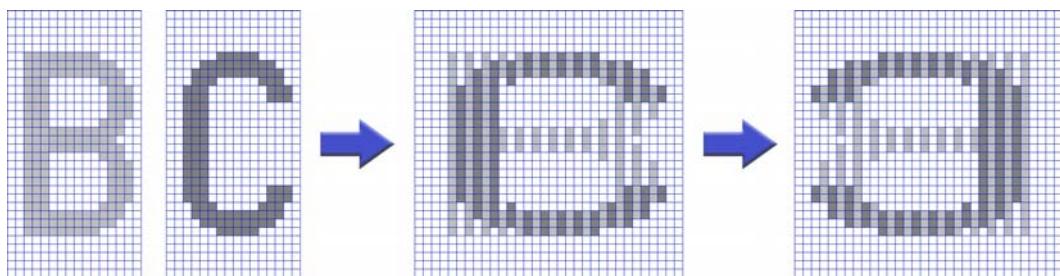

The character pairs are merged row-by-row such that each character's 16 horizontal pixels are spaced apart and interleaved with their neighbors' so that the even character takes bits 0, 2, 4, ...30, and the odd character takes bits 1, 3, 5, ...31. The leftmost pixels are in the lowest bits, while the rightmost pixels are in the highest bits, as shown in Figure 1-7. This forms a long (4 bytes) for each row of pixels in the character pair. 32 such longs, building from the character's top row down to the bottom, make up the complete merged-pair definition. The definitions are encoded in this manner so that a cog's video hardware can handle the merged longs directly, using color selection to display either the even or the odd character. It also has the advantage of allowing run-time character pairs (see next paragraph) that are four-color characters used to draw beveled buttons, lines and focus indicators.

**Figure 1-7: Propeller Character Interleaving**

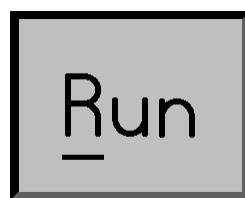

Some character codes have inescapable meanings, such as 9 for Tab, 10 for Line Feed, and 13 for Carriage Return. These character codes invoke actions and do not equate to static character definitions. For this reason, their character definitions have been used for special four-color characters. These four-color characters are used for drawing 3-D box edges at run time and are implemented as 16 x 16 pixel cells, as opposed to the normal 16 x 32 pixel cells. They occupy even-odd character pairs 0-1, 8-9, 10-11, and 12-13. Figure 1-8 shows an example of a button with 3D beveled edges made from some of these characters.

**Figure 1-8: Button with 3-D Beveled Edges**

The Propeller Tool includes, and uses, the Parallax True Type® font which follows the design of the Propeller Font embedded in the hardware. With this font, and the Propeller Tool, you

## Introducing the Propeller Chip

---

can include schematics, timing diagrams and other diagrams right in the source code for your application.

## Log and Anti-Log Tables

The log and anti-log tables are useful for converting values between their number form and exponent form.

When numbers are encoded into exponent form, simple math operations take on more complex effects. For example ‘add’ and ‘subtract’ become ‘multiply’ and ‘divide.’ ‘Shift left’ becomes ‘square’ and ‘shift right’ becomes ‘square-root.’ ‘Divide by 3’ will produce ‘cube root.’ Once the exponent is converted back to a number, the result will be apparent.

See Appendix B: Math Samples and Function Tables on page 380 for more information.

## Sine Table

The sine table provides 2,049 unsigned 16-bit sine samples spanning from 0° to 90°, inclusively (0.0439° resolution). Sine values for all other quadrants covering > 90° to < 360° can be calculated from simple transformations on this single-quadrant sine table. The sine table can be used for calculations related to angular phenomena.

See Appendix B: Math Samples and Function Tables on page 380 for more information.

## Boot Loader and Spin Interpreter

The last section in Main ROM contains the Propeller chip’s Boot Loader and Spin Interpreter programs.

The Boot Loader is responsible for initializing the Propeller upon power-up/reset. When a Boot Up procedure is started, the Boot Loader is loaded into Cog 0’s RAM and the cog executes the code starting at location 0. The Boot Loader program first checks the host and EEPROM communication pins for code/data to download/upload, processes that information accordingly and finally it either launches the Spin Interpreter program into Cog 0’s RAM (overwriting itself) to run the user’s Propeller Application, or it puts the Propeller into shutdown mode. See the Boot Up Procedure section on page 18.

The Spin Interpreter program fetches and executes the Propeller Application from Main RAM. This may lead to launching additional cogs to run more Spin code or Propeller Assembly code, as is requested by the application. See Run-Time Procedure, page 18.

# Chapter 2: Spin Language Reference

This chapter describes all elements of the Propeller chip’s Spin language and is best used as a reference for individual elements of the Spin language. For a tutorial on the use of the language refer to the Spin Language Tutorial in the Propeller Tool’s on-line help, then return here for more details.

The Spin Language Reference is divided into three sections:

- 1) **The Structure of the Propeller Objects.** Propeller Objects consist of Spin code, optional Assembly Code, and data. An object’s Spin code provides it with structure, consisting of special-purpose blocks. This section lists these blocks and the elements that may be used in each. Each listed element has a page reference for more information.

- 2) **The Categorical Listing of the Propeller Spin Language.** All elements, including operators and syntax symbols, are grouped by related function. This is a great way to quickly realize the breadth of the language and what features are available for specific uses. Each listed element has a page reference for more information. Some elements are marked with a superscript “a” indicating that they are also available in Propeller Assembly, though syntax may vary. Such marked elements are also included in Chapter 3: Assembly Language Reference.

- 3) **The Spin Language Elements.** Most elements have their own dedicated sub-section, alphabetically arranged to ease searching for them. Those individual elements without a dedicated sub-section, such as Operators, Symbols and some constants, are grouped within other related sub-sections but can be easily located by following their page reference from the Categorical Listing.

## Structure of Propeller Objects/Spin

Each Propeller object is a Spin file that has an inherent structure consisting of up to six different special-purpose blocks: **CON**, **VAR**, **OBJ**, **PUB**, **PRI**, and **DAT**. These blocks are shown below (in the order that they typically appear in objects) along with the set of elements usable within each.

For detailed examples of the object (Spin) structure and usage, refer to the Propeller Programming Tutorial in the Propeller Tool Help.

### **CON: Constant blocks define global constants** (page 84).

---

|                 |       |                   |       |               |       |               |      |

|-----------------|-------|-------------------|-------|---------------|-------|---------------|------|

| <u>_CLKFREQ</u> | p 65  | <u>NEGX</u>       | p 93  | <u>PLL16X</u> | p 68  | <u>XINPUT</u> | p 68 |

| <u>_CLKMODE</u> | p 68  | <b>Operators*</b> | p 143 | <u>POSX</u>   | p 93  | <u>XTAL1</u>  | p 68 |

| <u>_FREE</u>    | p 110 | <u>PI</u>         | p 93  | <u>RCFAST</u> | p 68  | <u>XTAL2</u>  | p 68 |

| <u>_STACK</u>   | p 202 | <u>PLL1X</u>      | p 68  | <u>RCSLOW</u> | p 68  | <u>XTAL3</u>  | p 68 |

| <u>_XINFREQ</u> | p 236 | <u>PLL2X</u>      | p 68  | <u>ROUND</u>  | p 198 |               |      |

| <u>FALSE</u>    | p 93  | <u>PLL4X</u>      | p 68  | <u>TRUE</u>   | p 93  |               |      |

| <u>FLOAT</u>    | p 108 | <u>PLL8X</u>      | p 68  | <u>TRUNC</u>  | p 209 |               |      |

\*Non-assignment operators only.

### **VAR: Variable blocks define global variables** (page 210).

---

|              |       |                   |       |              |       |              |       |

|--------------|-------|-------------------|-------|--------------|-------|--------------|-------|

| <u>BYTE</u>  | p 51  | <u>LONG</u>       | p 128 | <u>ROUND</u> | p 198 | <u>TRUNC</u> | p 209 |

| <u>FLOAT</u> | p 108 | <b>Operators*</b> | p 143 | <u>WORD</u>  | p 227 |              |       |

\*Non-assignment operators only.

### **OBJ: Object blocks define referenced objects** (page 141).

---

|              |       |                   |       |              |       |              |       |

|--------------|-------|-------------------|-------|--------------|-------|--------------|-------|

| <u>FLOAT</u> | p 108 | <b>Operators*</b> | p 143 | <u>ROUND</u> | p 198 | <u>TRUNC</u> | p 209 |

|--------------|-------|-------------------|-------|--------------|-------|--------------|-------|

\*Non-assignment operators only.

### PUB/PRI: Public and Private method blocks define Spin routines (pages 182/181).

|          |       |           |       |           |       |          |       |

|----------|-------|-----------|-------|-----------|-------|----------|-------|

| ABORT    | p 47  | FLOAT     | p 108 | Operators | p 143 | ROUND    | p 198 |

| BYTE     | p 51  | FRQA      | p 111 | OUTA      | p 175 | SPR      | p 200 |

| BYTEFILL | p 57  | FRQB      | p 111 | OUTB      | p 175 | STRCOMP  | p 203 |

| BYTEMOVE | p 58  | IF        | p 112 | PAR       | p 178 | STRING   | p 205 |

| CASE     | p 59  | IFNOT     | p 117 | PHSA      | p 180 | STRSIZE  | p 206 |

| CHIPVER  | p 62  | INA       | p 117 | PHSB      | p 180 | TRUE     | p 93  |

| CLKFREQ  | p 63  | INB       | p 117 | PI        | p 93  | TRUNC    | p 209 |

| CLKMODE  | p 67  | LOCKCLR   | p 120 | PLL1X     | p 68  | VCFG     | p 213 |

| CLKSET   | p 71  | LOCKNEW   | p 122 | PLL2X     | p 68  | VSCL     | p 216 |

| CNT      | p 73  | LOCKRET   | p 125 | PLL4X     | p 68  | WAITCNT  | p 218 |