# **General Description**

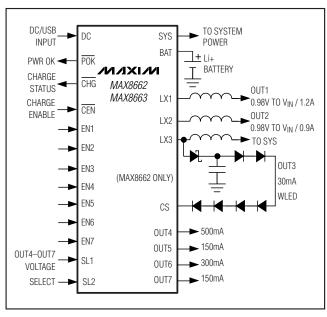

The MAX8662/MAX8663 power-management ICs (PMICs) are efficient, compact devices suitable for smart cellular phones, PDAs, Internet appliances, and other portable devices. They integrate two synchronous buck regulators, a boost regulator driving two to seven white LEDs, four low-dropout linear regulators (LDOs), and a linear charger for a single-cell Li-ion (Li+) battery.

Maxim's Smart Power Selector™ (SPS) safely distributes power between an external power source (AC adapter, auto adapter, or USB source), battery, and the system load. When system load peaks exceed the external source capability, the battery supplies supplemental current. When system load requirements are small, residual power from the external power source charges the battery. A thermal-limiting circuit limits battery-charge rate and external power-source current to prevent overheating. The PMIC also allows the system to operate with no battery or a discharged battery.

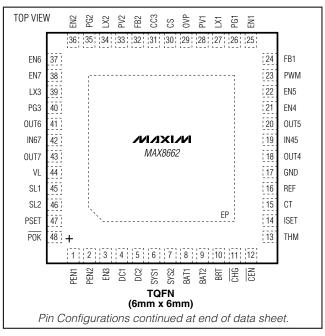

The MAX8662 is available in a 6mm x 6mm, 48-pin TQFN package, while the MAX8663, without the LED driver, is available in a 5mm x 5mm, 40-pin TQFN package.

# **Applications**

Smart Phones and PDAs

MP3 and Portable Media Players

Palmtop and Wireless Handhelds

# **Pin Configurations**

#### **Features**

- ◆ Two 95%-Efficient 1MHz Buck Regulators Main Regulator: 0.98V to V<sub>IN</sub> at 1200mA Core Regulator: 0.98V to V<sub>IN</sub> at 900mA

- ◆ 1MHz Boost WLED Driver Drives Up to 7 White LEDs at 30mA (max) PWM and Analog Dimming Control

- Four Low-Dropout Linear Regulators 1.7V to 5.5V Input Range 15μA Quiescent Current

- ♦ Single-Cell Li+ Charger Adapter or USB Input Thermal-Overload Protection

- Smart Power Selector (SPS)

AC Adapter/USB or Battery Source

Charger-Current and System-Load Sharing

# **Ordering Information**

| PART           | TEMP RANGE PIN-PACKAGE |                   |  |

|----------------|------------------------|-------------------|--|

| MAX8662ETM+    | -40°C to +85°C         | 48 TQFN-EP*       |  |

| WIAX0002LTIVIT | -40 C to +65 C         | 6mm x 6mm x 0.8mm |  |

| MAX8663ETL+    | -40°C to +85°C         | 40 TQFN-EP*       |  |

| WIAAOOO3E1L+   | -40 C to +65 C         | 5mm x 5mm x 0.8mm |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# **Typical Operating Circuit**

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

## **ABSOLUTE MAXIMUM RATINGS**

|                                          | J. O                             |

|------------------------------------------|----------------------------------|

| LX3 to GND                               | 0.3V to +33V                     |

| DC_ to GND                               |                                  |

| BAT_, CEN, CHG, EN_, PEN_, POK, PV_, PWI | И,                               |

| SYS_, LX1, CS, LX2 to GND                | 0.3V to +6V                      |

| VL to GND                                | 0.3V to +4V                      |

| BRT, CC3, FB_, IN45, IN67, OVP, REF,     |                                  |

| SL_ to GND0.3                            | $V$ to $(V_{SYS} + 0.3V)$        |

| CT, ISET, PSET, THM to GND0.             | $3V \text{ to } (V_{VL} + 0.3V)$ |

| OUT4, OUT5 to GND0.3\                    |                                  |

| OUT6, OUT7 to GND0.3\                    | /  to (VIN67 + 0.3V)             |

| PG_ to GND                               | 0.3V to +0.3V                    |

| BAT1 + BAT2 Continuous Current           | 3A                               |

| SYS1 + SYS2 Continuous Current (2 pins)  | 3A                               |

|                                          |                                  |

| LX_ Continuous Current                                | 1.5A            |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| 40-Pin 5mm x 5mm TQFN                                 |                 |

| (derate 35.7mW/°C above +70°C)                        |                 |

| (multilayer board)                                    | 2857mW          |

| 48-Pin 6mm x 6mm TQFN                                 |                 |

| (derate 37mW/°C above +70°C) (multilaye               | er board)2963mW |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature Range                            | 40°C to +125°C  |

| Storage Temperature Range                             |                 |

| Lead Temperature (soldering, 10s)                     |                 |

| Soldering Temperature (reflow)                        | +260°C          |

|                                                       |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS (Input Limiter and Battery Charger)**

$(V_{DC} = 5V, V_{BAT} = 4V, V_{\overline{CEN}} = 0V, V_{PEN} = 5V, R_{PSET} = 3k\Omega, R_{ISET} = 3.15k\Omega, C_{CT} = 0.068\mu F, T_{A} = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL                 | CONDITIONS                                                  |                                                                                                | MIN  | TYP  | MAX  | UNITS |

|------------------------------------|------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|

| INPUT LIMITER                      |                        |                                                             |                                                                                                | •    |      |      |       |

| DC Operating Range                 | V <sub>DC</sub>        | (Note 2)                                                    |                                                                                                | 4.1  |      | 8.0  | V     |

| DC Undervoltage Threshold          | V <sub>DC_L</sub>      | V <sub>DC</sub> rising, 500mV hyster                        | resis                                                                                          | 3.9  | 4.0  | 4.1  | V     |

| DC Overvoltage Threshold           | V <sub>DC_H</sub>      | V <sub>DC</sub> rising, 100mV hyster                        | resis                                                                                          | 6.6  | 6.9  | 7.2  | V     |

| DC Supply Current                  |                        | $I_{SYS} = I_{BAT} = 0mA, V_{\overline{CEN}}$               | = 0V                                                                                           |      | 1.5  |      | mA    |

| DC Supply Current                  |                        | $I_{SYS} = I_{BAT} = 0mA, V_{\overline{CEN}}$               | = 5V                                                                                           |      | 0.9  |      | IIIA  |

| DC Shutdown Current                |                        | $V_{DC} = 5V, V_{\overline{CEN}} = 5V, V_{P}$ suspend mode) | PEN1 = VPEN2 = 0V (USB                                                                         |      | 110  | 180  | μΑ    |

| DC-to-SYS Dropout<br>On-Resistance | R <sub>DC_SYS</sub>    | V <sub>DC</sub> = 5V, I <sub>SYS</sub> = 400mA              | , V <u>CEN</u> = 5V                                                                            |      | 0.1  | 0.2  | Ω     |

| DC-to-BAT Dropout<br>Threshold     | VDR_DC_BAT             |                                                             | When V <sub>SYS</sub> regulation and charging stops, V <sub>DC</sub> falling, 150mV hysteresis |      | 50   | 85   | mV    |

| VL Voltage                         | $V_{VL}$               | $I_{VL} = 0$ to $10mA$                                      |                                                                                                | 3.1  | 3.3  | 3.5  | V     |

| SYS Regulation Voltage             | Vsys_reg               | $V_{DC} = 5.8V$ , $I_{SYS} = 1mA$ ,                         | V <sub>CEN</sub> = 5V                                                                          | 5.2  | 5.3  | 5.4  | V     |

|                                    |                        |                                                             | $V_{PEN1} = 5V$ , $V_{PEN2} = 5V$ , $R_{PSET} = 1.5k\Omega$                                    | 1800 | 2000 | 2200 |       |

|                                    |                        |                                                             | $V_{PEN1} = 5V$ , $V_{PEN2} = 5V$ , $R_{PSET} = 3k\Omega$                                      | 900  | 1000 | 1100 |       |

| DC Input Current Limit             | IDC_LIM                | V <sub>DC</sub> = 5V, V <sub>SYS</sub> = 4.0V               | $V_{PEN1} = 5V$ , $V_{PEN2} = 5V$ , $R_{PSET} = 6k\Omega$                                      | 450  | 500  | 550  | mA    |

|                                    |                        |                                                             | V <sub>PEN1</sub> = 0V, V <sub>PEN2</sub> = 5V<br>(500mA USB mode)                             | 450  | 475  | 500  |       |

|                                    |                        |                                                             | V <sub>PEN1</sub> = V <sub>PEN2</sub> = 0V<br>(100mA USB mode)                                 | 80   | 90   | 100  |       |

| PSET Resistance Range              | R <sub>PSET</sub>      | Guaranteed by SYS curre                                     | ent limit                                                                                      | 1.5  |      | 6.0  | kΩ    |

| Input Limiter Soft-Start Time      | T <sub>SS_DC_SYS</sub> | Current-limit ramp time                                     |                                                                                                |      | 1.5  |      | ms    |

# **ELECTRICAL CHARACTERISTICS (Input Limiter and Battery Charger) (continued)**

$(V_{DC}=5V, V_{BAT}=4V, V_{\overline{CEN}}=0V, V_{PEN}=5V, R_{PSET}=3k\Omega, R_{ISET}=3.15k\Omega, C_{CT}=0.068\mu F, T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                    | SYMBOL               | CONDITIONS                                                                                                               |                                                                                        | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

| BATTERY CHARGER                              | •                    |                                                                                                                          |                                                                                        |       |       |       |       |

| BAT-to-SYS On-Resistance                     | RBAT_REG             | $V_{DC} = 0V, V_{BAT} = 4.2V, I_{S}$                                                                                     | sys = 1A                                                                               |       | 40    | 80    | mΩ    |

| BAT-to-SYS Reverse<br>Regulation Voltage     |                      |                                                                                                                          | = 0V (USB 100mA mode),<br>'S voltage drop during SYS                                   | 50    | 100   | 150   | mV    |

| BAT Regulation Voltage                       | VDAT DEG             | In a = 0m A                                                                                                              | T <sub>A</sub> = +25°C                                                                 | 4.179 | 4.200 | 4.221 | V     |

| bat Regulation Voltage                       | VBAT_REG             | $I_{BAT} = 0mA$                                                                                                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                          | 4.158 | 4.200 | 4.242 | ] V   |

| BAT Recharge Threshold                       |                      | BAT voltage drop to resta                                                                                                | art charging                                                                           | -140  | -100  | -60   | mV    |

|                                              |                      | Isys = 0mA,                                                                                                              | $R_{ISET} = 1.89k\Omega$                                                               |       | 1250  |       |       |

| BAT Fast-Charge Current                      |                      | $R_{PSET} = 1.5k\Omega$ ,                                                                                                | $R_{ISET} = 3.15k\Omega$                                                               | 675   | 750   | 825   | mA    |

|                                              |                      | VPEN1 = VPEN2 = 5V                                                                                                       | $R_{ISET} = 7.87 k\Omega$                                                              |       | 300   |       |       |

| BAT Prequalification Current                 |                      | VBAT = 2.5V, RISET = 3.15 current is 10% of fast-cha                                                                     |                                                                                        |       | 75    |       | mA    |

| ISET Resistance Range                        | R <sub>ISET</sub>    | Guaranteed by BAT char (1.5A to 300mA)                                                                                   | ging current                                                                           | 1.57  |       | 7.87  | kΩ    |

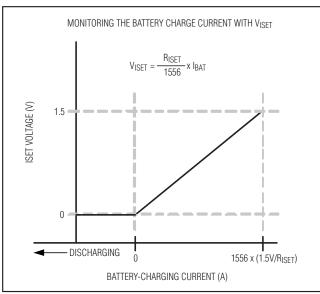

| V <sub>ISET</sub> -to-I <sub>BAT</sub> Ratio |                      | $R_{ISET} = 3.15k\Omega$ (ISET out charge-current ratio)                                                                 | put voltage to actual                                                                  |       | 2     |       | V/A   |

| Charger Soft-Start Time                      | tss_chg              | Charge-current ramp time                                                                                                 | е                                                                                      |       | 1.5   |       | ms    |

| BAT Prequalification Threshold               |                      | V <sub>BAT</sub> rising, 180mV hyste                                                                                     | eresis                                                                                 | 2.9   | 3.0   | 3.1   | V     |

| 5.5.                                         |                      | V <sub>BAT</sub> = 4.2V,                                                                                                 | $V_{DC} = 0V$                                                                          |       | 0.01  | 5     | 1     |

| BAT Leakage Current                          |                      | outputs disabled                                                                                                         | V <sub>DC</sub> = V <sub>CEN</sub> = 5V                                                |       | 0.01  | 5     | μΑ    |

| CHG and Top-Off Threshold                    |                      | I <sub>BAT</sub> where CHG goes<br>high, and top-off timer;<br>I <sub>BAT</sub> falling (7.5% of<br>fast-charge current) | $R_{ISET} = 3.15 k\Omega$                                                              |       | 56.25 |       | mA    |

| Timer-Suspend Threshold                      |                      | IBAT falling (Note 3)                                                                                                    |                                                                                        | 250   | 300   | 350   | mV    |

| Timer Accuracy                               |                      | C <sub>CT</sub> = 0.068µF                                                                                                |                                                                                        | -20   |       | +20   | %     |

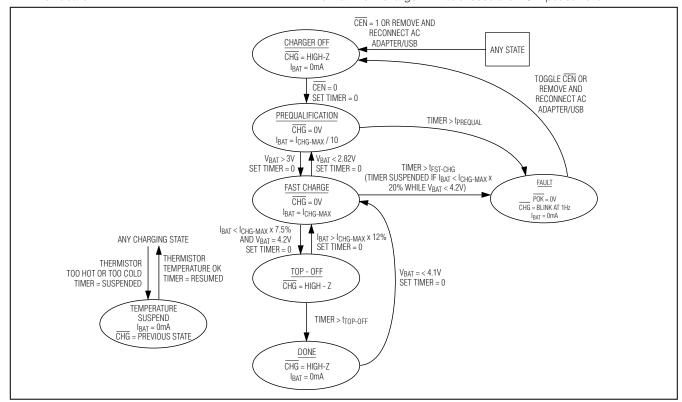

| Prequalification Time                        | tprequal             |                                                                                                                          | From CEN high to end of prequalification charge, $V_{BAT} = 2.5V, C_{CT} = 0.068\mu F$ |       | 30    |       | Min   |

| Charge Time                                  | t <sub>FST-CHG</sub> | From $\overline{\text{CEN}}$ high to end of fast charge,<br>$C_{\text{CT}} = 0.068 \mu \text{F}$                         |                                                                                        |       | 300   |       | Min   |

| Top-Off Time                                 | t <sub>TOP-OFF</sub> | From CHG high to end of fast charge,<br>CCT = 0.068µF                                                                    |                                                                                        |       | 30    |       | Min   |

| Charger Thermal-Limit<br>Temperature         |                      | (Note 4)                                                                                                                 |                                                                                        |       | 100   |       | °C    |

| Charger Thermal-Limit Gain                   |                      | $R_{PSET} = 3k\Omega$                                                                                                    |                                                                                        |       | 50    |       | mA/°C |

# **ELECTRICAL CHARACTERISTICS (Input Limiter and Battery Charger) (continued)**

$(V_{DC} = 5V, V_{BAT} = 4V, V_{\overline{CEN}} = 0V, V_{PEN} = 5V, R_{PSET} = 3k\Omega, R_{ISET} = 3.15k\Omega, C_{CT} = 0.068\mu F, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                             | SYMBOL      | CONDITIONS                                        |                        | MIN  | TYP    | MAX   | UNITS |

|---------------------------------------|-------------|---------------------------------------------------|------------------------|------|--------|-------|-------|

| THERMISTOR INPUT (THM)                |             |                                                   |                        | •    |        |       |       |

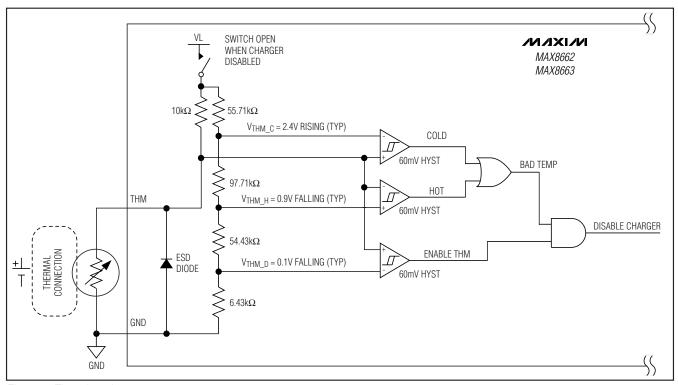

| THM Internal Pullup<br>Resistance     |             |                                                   |                        |      | 10     |       | kΩ    |

| THM Resistance Threshold,<br>Hot      |             | Resistance falling (1% hy                         | vsteresis)             | 3.73 | 3.97   | 4.21  | kΩ    |

| THM Resistance Threshold,<br>Cold     |             | Resistance rising (1% hysteresis)                 |                        |      | 28.7   | 30.42 | kΩ    |

| THM Resistance Threshold,<br>Disabled |             | Resistance falling                                |                        |      | 300    | 330   | Ω     |

| LOGIC I/O (POK, CHG, PEN_             | , EN_, PWM, | CEN)                                              |                        |      |        |       |       |

| Input Logic-High Level                |             |                                                   |                        | 1.3  |        |       | V     |

| Input Logic-Low Level                 |             |                                                   |                        |      |        | 0.4   | V     |

| Lagia laguat Laglaga Cumant           |             | V <sub>L</sub> OGIC = 0V to 5.5V, T <sub>A</sub>  | = +25°C                | -1   | +0.001 | +1    |       |

| Logic Input-Leakage Current           |             | V <sub>LOGIC</sub> = 5.5V, T <sub>A</sub> = +85°C |                        |      | 0.01   |       | μΑ    |

| Logic Output-Voltage Low              |             | I <sub>SINK</sub> = 1mA                           |                        |      | 10     | 100   | mV    |

| Logic Output-High Leakage             |             | Vi acia E EV                                      | T <sub>A</sub> = +25°C |      | 0.001  | 1     |       |

| Current                               |             | VLOGIC = 5.5V                                     | T <sub>A</sub> = +85°C |      | 0.01   |       | μΑ    |

## **ELECTRICAL CHARACTERISTICS (Output Regulator)**

(Vsys\_ = Vpv\_ = VIN45 = VIN67 = 4.0V, VBRT = 1.25V, circuit of Figure 1, TA = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                     | SYMBOL                | CONDITIONS                        |                                | MIN  | TYP | MAX  | UNITS             |

|-------------------------------|-----------------------|-----------------------------------|--------------------------------|------|-----|------|-------------------|

| SYSTEM                        |                       |                                   |                                |      |     |      |                   |

| SYS Operating Range           | V <sub>SYS</sub>      |                                   |                                | 2.6  |     | 5.5  | V                 |

| SYS Undervoltage Threshold    | V <sub>UVLO_SYS</sub> | V <sub>SYS</sub> rising, 100mV hy | rsteresis                      | 2.4  | 2.5 | 2.6  | V                 |

|                               |                       | Extra supply current w            | hen at least one output is on  |      | 35  | 70   |                   |

|                               |                       |                                   | OUT1 on, V <sub>PWM</sub> = 0V |      | 16  | 35   | μΑ                |

|                               |                       |                                   | OUT2 on, V <sub>PWM</sub> = 0V |      | 16  | 35   |                   |

| SYS Bias Current Additional   |                       |                                   | OUT3 on                        |      | 1   | 2    | mA                |

| Regulator Supply Current      |                       | Not including<br>SYS bias current | OUT4 on (current into IN45)    |      | 20  | 30   | 30<br>25<br>27 μΑ |

|                               |                       |                                   | OUT5 on (current into IN45)    |      | 16  | 25   |                   |

|                               |                       |                                   | OUT6 on (current into IN67)    |      | 17  | 27   |                   |

|                               |                       |                                   | OUT7 on (current in IN67)      |      | 16  | 25   |                   |

| Internal Oscillator Frequency |                       | PWM frequency of OL               | JT1, OUT2, and OUT3            | 0.9  | 1.0 | 1.1  | MHz               |

| BUCK REGULATOR 1              |                       |                                   |                                |      |     |      |                   |

| Supply Current                |                       | Isys + Ipy1, no load,             | V <sub>PWM</sub> = 0V          |      | 16  | 35   | μΑ                |

| Зирріу Сипепі                 |                       | not including SYS bias current    | V <sub>PWM</sub> = 5V          |      | 2.9 |      | mA                |

| Output Voltage Range          | Vout1                 | Guaranteed by FB accuracy         |                                | 0.98 |     | 3.30 | V                 |

| Maximum Output Current        | I <sub>OUT1</sub>     |                                   |                                | 1200 |     |      | mA                |

# **ELECTRICAL CHARACTERISTICS (Output Regulator) (continued)**

$(V_{SYS} = V_{PV} = V_{IN45} = V_{IN67} = 4.0V, V_{BRT} = 1.25V, circuit of Figure 1, T_A = -40°C to +85°C, unless otherwise noted.) (Note 1)$

| PARAMETER                    | SYMBOL            | CONDITIONS                                                                    |                                | MIN              | TYP   | MAX   | UNITS |

|------------------------------|-------------------|-------------------------------------------------------------------------------|--------------------------------|------------------|-------|-------|-------|

| FB Regulation Accuracy       |                   | From $V_{FB1} = 0.98V$ , $I_{OUT1} = 0$ to 1200mA, $V_{OUT1} = 0.98V$ to 3.3V |                                | -3               |       | +3    | %     |

| FB1 Input Leakage Current    |                   |                                                                               |                                |                  | 0.01  | 0.10  | μΑ    |

| pMOS On-Resistance           |                   | $I_{LX1} = 100 \text{mA}$                                                     | $V_{PV1} = 3.3V$               |                  | 0.12  | 0.24  | Ω     |

| pivios on-nesistance         |                   | ILXI = TOOTHA                                                                 | V <sub>PV1</sub> = 2.6V        |                  | 0.15  |       | 52    |

| nMOS On-Resistance           |                   | $I_{LX1} = 100 \text{mA}$                                                     | $V_{PV1} = 3.3V$               |                  | 0.2   | 0.4   | Ω     |

| TIMOO ON NESISTANCE          |                   | 1 <u>L</u> X1 = 10011//                                                       | $V_{PV1} = 2.6V$               |                  | 0.3   |       | 32    |

| pMOS Current Limit           |                   |                                                                               |                                | 1.4              | 1.8   | 2.2   | Α     |

| Skip Mode Transition Current |                   |                                                                               |                                |                  | 90    |       | mA    |

| nMOS Zero-Cross Current      |                   |                                                                               |                                |                  | 25    |       | mA    |

| LX Leakage                   |                   | $V_{EN1} = 0V, V_{SYS} = 5.5V,$                                               | $V_{LX1} = V_{PV1} = 5.5V$     |                  | 0.01  | 1.00  | μΑ    |

| LX Ecanage                   |                   | $T_A = +25^{\circ}C$                                                          | $V_{LX1} = 0V, V_{PV1} = 5.5V$ | -5.00            | -0.01 |       | μ/ (  |

| Soft-Start Time              |                   |                                                                               |                                |                  | 400   |       | μs    |

| BUCK REGULATOR 2             |                   |                                                                               |                                |                  |       |       |       |

| Supply Current               |                   | Isys + Ipv2, no load, not                                                     | $V_{PWM} = 0V$                 |                  | 16    | 35    | μΑ    |

| Зарріу Сапені                |                   | including SYS bias current                                                    | $V_{PWM} = 5V$                 |                  | 2.1   |       | mA    |

| Output Voltage Range         |                   | Guaranteed by FB accurac                                                      | СУ                             | 0.98             |       | 3.30  | V     |

| Maximum Output Current       |                   |                                                                               |                                | 900              |       |       | mA    |

| FB Regulation Accuracy       |                   | From $V_{FB2} = 0.98V$ , $I_{OUT2} = V_{OUT2} = 0.98V$ to 3.3V                | = 0 to 600mA,                  | -3               |       | +3    | %     |

| FB2 Input Leakage Current    |                   |                                                                               |                                |                  | 0.01  | 0.10  | μΑ    |

| pMOS On-Resistance           |                   | luvo – 100mA                                                                  | $V_{PV2} = 3.3V$               |                  | 0.2   | 0.4   |       |

| pivios on-nesistance         |                   | $I_{LX2} = 100mA$                                                             | $V_{PV2} = 2.6V$               |                  | 0.3   |       | Ω     |

| nMOS On- Resistance          |                   | $I_{LX2} = 100 \text{mA}$                                                     | $V_{PV2} = 3.3V$               |                  | 0.2   | 0.4   | Ω     |

| TIMOS OTI- Nesistance        |                   | ILX2 = TOOTHA                                                                 | $V_{PV2} = 2.6V$               |                  | 0.3   |       | 52    |

| pMOS Current Limit           |                   |                                                                               |                                | 1.07             | 1.30  | 1.55  | Α     |

| Skip Mode Transition Current |                   |                                                                               |                                |                  | 90    |       | mA    |

| nMOS Zero-Cross Current      |                   |                                                                               |                                |                  | 25    |       | mA    |

| LX Leakage                   |                   | V <sub>EN2</sub> = 0V, V <sub>SYS</sub> = 5.5V,                               | $V_{LX2} = V_{PV2} = 5.5V$     |                  | 0.01  | 1.00  |       |

| LA Leakage                   |                   | $T_A = +25^{\circ}C$                                                          | $V_{LX2} = 0V, V_{PV2} = 5.5V$ | -5.00            | -0.01 |       | μA    |

| Soft-Start Time              |                   |                                                                               |                                |                  | 400   |       | μs    |

| BOOST REGULATOR FOR          | ED DRIVER         |                                                                               |                                |                  |       |       |       |

| Supply Current               |                   | At SYS, no load, not including SYS bias current                               | Switching                      |                  | 1     |       | mA    |

| Output Range                 | V <sub>OUT3</sub> |                                                                               |                                | V <sub>SYS</sub> |       | 30    | V     |

| Minimum Duty Cycle           | D <sub>MIN</sub>  |                                                                               |                                |                  | 10    |       | %     |

| Maximum Duty Cycle           | D <sub>MAX</sub>  |                                                                               |                                | 90               | 92    |       | %     |

| CS Regulation Voltage        | Vcs               |                                                                               |                                | 0.29             | 0.32  | 0.35  | V     |

| OVP Regulation Voltage       |                   | Duty = 90%, I <sub>L</sub> x <sub>3</sub> = 0mA                               |                                | 1.225            | 1.250 | 1.275 | V     |

| OVP Sink Current             |                   |                                                                               |                                | 19.2             | 20.0  | 20.8  | μΑ    |

| OVP Soft-Start Period        |                   | Time for IOVP to ramp from                                                    | 0 to 20µA (Note 5)             |                  | 1.25  |       | ms    |

# **ELECTRICAL CHARACTERISTICS (Output Regulator) (continued)**

$(V_{SYS} = V_{PV} = V_{IN45} = V_{IN67} = 4.0V, V_{BRT} = 1.25V, circuit of Figure 1, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.)$  (Note 1)

| PARAMETER                                  | SYMBOL                 | CONDITIO                                                                                | ONS                      | MIN  | TYP   | MAX  | UNITS             |

|--------------------------------------------|------------------------|-----------------------------------------------------------------------------------------|--------------------------|------|-------|------|-------------------|

| 0/01 0                                     |                        | $V_{EN3} = 0V$ ,                                                                        | T <sub>A</sub> = +25°C   |      | 0.01  | 1    | ^                 |

| OVP Leakage Current                        |                        | $V_{OVP} = V_{SYS} = 5.5V$                                                              | T <sub>A</sub> = +85°C   |      | 0.1   |      | μΑ                |

| nMOS On-Resistance                         |                        | I <sub>L</sub> X <sub>3</sub> = 100mA                                                   |                          |      | 0.6   | 1.2  | Ω                 |

| nMOC Off Lookage Current                   |                        | V. v. 20V                                                                               | $T_A = +25^{\circ}C$     |      | 0.01  | 5.00 |                   |

| nMOS Off-Leakage Current                   |                        | V <sub>L</sub> X <sub>3</sub> = 30V                                                     | $T_A = +85^{\circ}C$     |      | 0.1   |      | μΑ                |

| nMOS Current Limit                         |                        |                                                                                         |                          | 500  | 620   | 900  | mA                |

| LED DRIVER                                 |                        |                                                                                         |                          |      |       |      |                   |

| BRT Input Range                            | V <sub>BRT</sub>       | Ics = 0 to 30mA                                                                         |                          | 0    |       | 1.5  | V                 |

| REF Voltage                                | V <sub>REF</sub>       | I <sub>REF</sub> = 0mA                                                                  |                          | 1.45 | 1.50  | 1.55 | V                 |

| BRT Input Current                          |                        | V <sub>BRT</sub> = 0 to 1.5V                                                            | T <sub>A</sub> = +25°C   | -1   | -0.01 | +1   | μΑ                |

| Bitti input Guitent                        |                        | VBR1 = 0 to 1.5V                                                                        | T <sub>A</sub> = +85°C   |      | 0.1   |      | μΑ                |

| CS Sink Current                            |                        | V <sub>CS</sub> = 0.2V                                                                  | $V_{BRT} = 1.5V$         | 28   | 30    | 32   | mA                |

| C3 3IIIk Current                           |                        | VCS = 0.2V                                                                              | $V_{BRT} = 50 \text{mV}$ | 0.4  | 0.8   | 1.2  | IIIA              |

| CS Current-Source                          |                        | V <sub>SYS</sub> = 2.7V to 5.5V                                                         |                          |      | 0.1   |      | %/V               |

| Line Regulation                            |                        | VSYS - 2.7 V to 3.5 V                                                                   |                          |      | 0.1   |      | %/V               |

| PWM DIMMING                                |                        |                                                                                         |                          |      |       |      |                   |

| EN3 DC Turn-On Delay                       |                        | From V <sub>EN3</sub> = high to LED on                                                  |                          | 1.5  | 2.0   | 2.5  | ms                |

| EN3 Shutdown Delay                         |                        | From $V_{EN3}$ = low to LED off                                                         |                          | 1.5  | 2.0   | 2.5  | ms                |

| PWM Dimming Capture                        |                        | Time between rising edges                                                               | Maximum                  | 1.5  | 2.0   |      | ms                |

| Period                                     |                        | on EN3 for PWM dimming to become active                                                 | Minimum                  |      | 8     | 10   | μs                |

| PWM Dimming Pulse-Width Resolution         |                        | Resolution of high or low-pulse dimming change                                          | e width on EN3 for       |      | 0.5   |      | μs                |

| LINEAR REGULATORS                          | •                      |                                                                                         |                          |      |       |      | •                 |

| IN45, IN67 Operating Range                 | V <sub>IN45</sub>      |                                                                                         |                          | 1.7  |       | 5.5  | V                 |

| IN45, IN67 Undervoltage<br>Threshold       | V <sub>UVLO-IN45</sub> | V <sub>IN45</sub> rising, 100mV hysteresis                                              | 3                        | 1.5  | 1.6   | 1.7  | V                 |

| Output Noise                               |                        | f = 100Hz to 100kHz                                                                     |                          |      | 200   |      | μV <sub>RMS</sub> |

| PSRR                                       |                        | f = 100kHz                                                                              |                          |      | 30    |      | dB                |

| Shutdown Supply Current                    |                        | V <sub>EN4</sub> = V <sub>EN5</sub> = 0V, T <sub>A</sub> = +25°0                        |                          |      | 0.001 | 1    | μΑ                |

| Soft-Start Ramp Time                       |                        | V <sub>OUT4</sub> to 90% of final value                                                 |                          |      | 34    |      | V/ms              |

| Output Discharge<br>Resistance in Shutdown |                        | V <sub>EN4</sub> = 0V                                                                   |                          | 0.5  | 1.0   | 2.0  | kΩ                |

| LINEAR REGULATOR 4 (LE                     | 004)                   |                                                                                         |                          |      |       |      |                   |

| Supply Current                             |                        | At IN45, V <sub>EN5</sub> = 0V                                                          | I <sub>OUT4</sub> = 0A   |      | 20    | 30   | μΑ                |

| Voltage Accuracy                           |                        | I <sub>OUT4</sub> = 0 to 500mA,<br>V <sub>IN45</sub> = V <sub>OUT4</sub> + 0.3V to 5.5V | with 1.7V (min)          | -1.5 |       | +1.5 | %                 |

| Minimum Output Capacitor                   | C <sub>OUT4</sub>      | Guaranteed stability, ESR $< 0.05\Omega$                                                |                          | 3.76 |       |      | μF                |

| · · · · · · · · · · · · · · · · · · ·      | 5511                   | IN45 to OUT4                                                                            |                          |      | 0.2   | 0.4  | Ω                 |

| Dropout Resistance                         |                        | 11N45 to OO14                                                                           |                          |      | 0.2   | 0.4  | 52                |

6 \_\_\_\_\_\_ /N/XI/M

# **ELECTRICAL CHARACTERISTICS (OUTPUT REGULATOR) (continued)**

(Vsys = Vpv = V<sub>IN45</sub> = V<sub>IN67</sub> = 4.0V, V<sub>BRT</sub> = 1.25V, circuit of Figure 1, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                       | SYMBOL            | CONDITIONS                                                                                      |                        | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|-------------------|-------------------------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| LINEAR REGULATOR 5 (LD          | O5)               |                                                                                                 |                        | •    |      |      |       |

| Supply Current                  |                   | At IN45, V <sub>EN4</sub> = 0V                                                                  | I <sub>OUT5</sub> = 0A |      | 16   | 25   | μΑ    |

| Voltage Accuracy                |                   | I <sub>OUT5</sub> = 0 to 150mA,<br>V <sub>IN45</sub> = V <sub>OUT5</sub> + 0.3V to 5.5V with 1. | .7V (min)              | -1.5 |      | +1.5 | %     |

| Minimum Output Capacitor        | C <sub>OUT5</sub> | Guaranteed stability, ESR $< 0.05\Omega$                                                        |                        | 0.8  |      |      | μF    |

| Dropout Resistance              |                   | IN45 to OUT5                                                                                    |                        |      | 0.6  | 1.2  | Ω     |

| Current Limit                   |                   | V <sub>OUT5</sub> = 0V                                                                          |                        | 150  | 210  |      | mA    |

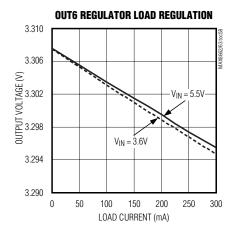

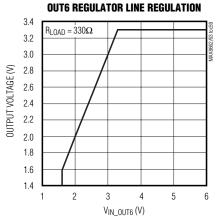

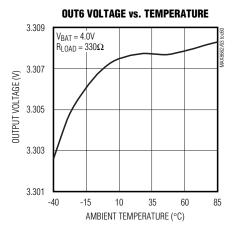

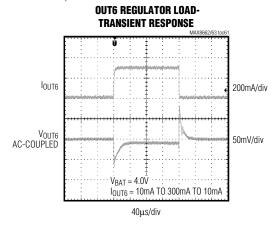

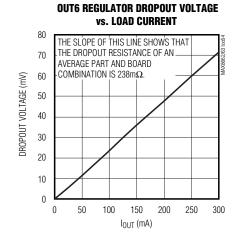

| LINEAR REGULATOR 6 (LD          | O6)               |                                                                                                 |                        |      |      |      |       |

| Supply Current                  |                   | At IN67, V <sub>EN6</sub> = V <sub>SYS</sub> , V <sub>EN7</sub> = 0V                            | I <sub>OUT6</sub> = 0A |      | 17   | 27   | μΑ    |

| Voltage Accuracy                |                   | I <sub>OUT6</sub> = 0 to 300mA, V <sub>IN67</sub> = V <sub>OUT6</sub>                           | + 0.3V to 5.5V         | -1.5 |      | +1.5 | %     |

| Minimum Output Capacitor        | C <sub>OUT6</sub> | Guaranteed stability, ESR $< 0.05\Omega$                                                        |                        | 1.76 |      |      | μF    |

| Dropout Resistance              |                   | IN67 to OUT6                                                                                    |                        |      | 0.35 | 0.60 | Ω     |

| Current Limit                   |                   | V <sub>OUT6</sub> = 0V                                                                          |                        | 300  | 420  |      | mA    |

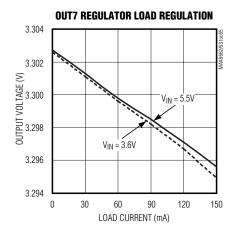

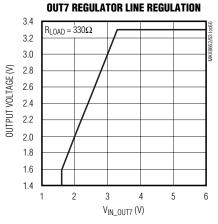

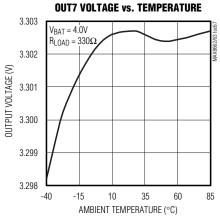

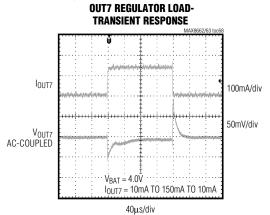

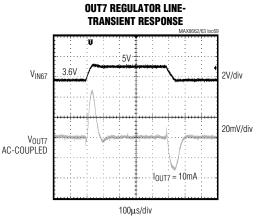

| LINEAR REGULATOR 7 (LD          | 007)              |                                                                                                 |                        |      |      |      |       |

| Supply Current                  |                   | At IN67, V <sub>EN6</sub> = 0V, V <sub>EN7</sub> = V <sub>SYS</sub>                             | I <sub>OUT7</sub> = 0A |      | 16   | 25   | μΑ    |

| Voltage Accuracy                |                   | $I_{OUT7} = 0$ to 150mA,<br>$V_{IN67} = V_{OUT7} + 0.3V$ to 5.5V with 1                         | .7V (min)              | -1.5 |      | +1.5 | %     |

| Minimum Output Capacitor        | C <sub>OUT7</sub> | Guaranteed stability, ESR $< 0.05\Omega$                                                        |                        | 0.8  |      |      | μF    |

| Dropout Resistance              |                   | IN67 to OUT6                                                                                    |                        |      | 0.6  | 1.2  | Ω     |

| Current Limit                   |                   | V <sub>OUT7</sub> = 0V                                                                          |                        | 150  | 210  |      | mA    |

| THERMAL SHUTDOWN                |                   |                                                                                                 |                        |      |      |      |       |

| Thermal-Shutdown<br>Temperature |                   | T <sub>J</sub> rising                                                                           |                        |      | 165  |      | °C    |

| Thermal-Shutdown<br>Hysteresis  |                   |                                                                                                 |                        |      | 15   |      | °C    |

- Note 1: Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

- Note 2: Input withstand voltage. Not designed to operate above VDC = 6.5V due to thermal-dissipation issues.

- Note 3: ISET voltage when CT timer stops. Occurs only when in constant-current mode. Translates to 20% of fast-charge current.

- Note 4: Temperature at which the input current limit begins to reduce.

- Note 5: The WLED driver's sink current ramp time is a function of the external compensation at CC3. With a compensation of 1kΩ in series with 0.22μF and a target sink current of 30mA, the WLED boost's output voltage ramps up in 1.25ms, but the WLED sink current of 30mA settles in 12ms. See the OUT3 Enable and Disable Response graph in the *Typical Operating Characteristics* section for more information.

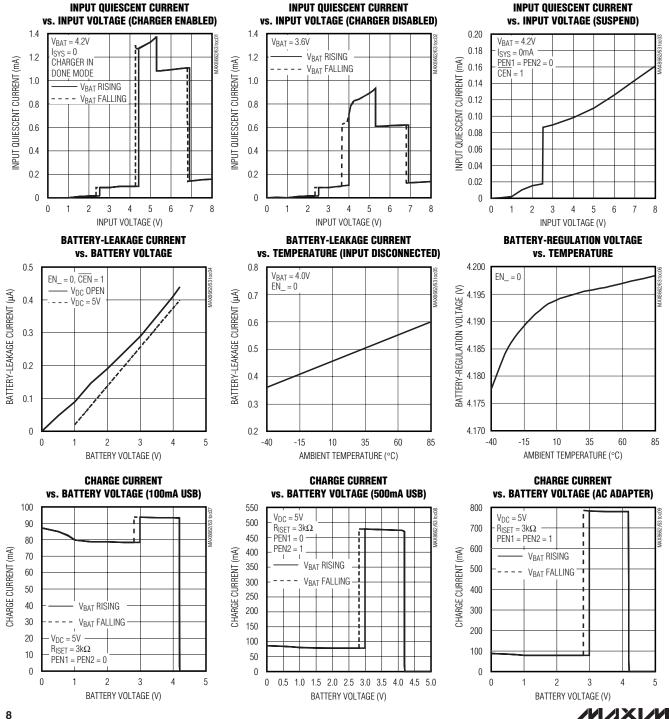

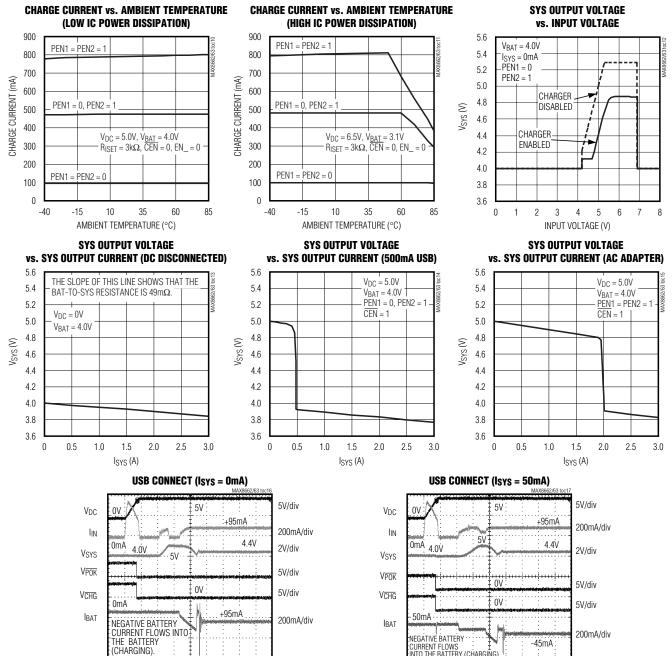

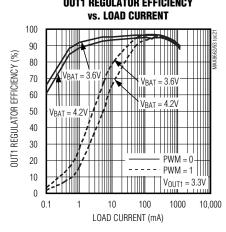

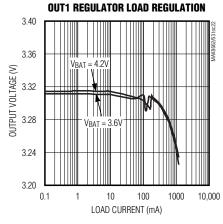

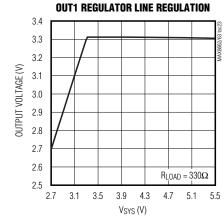

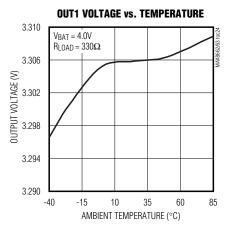

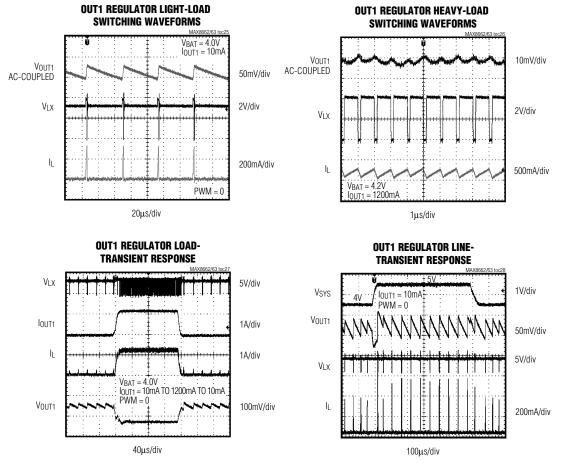

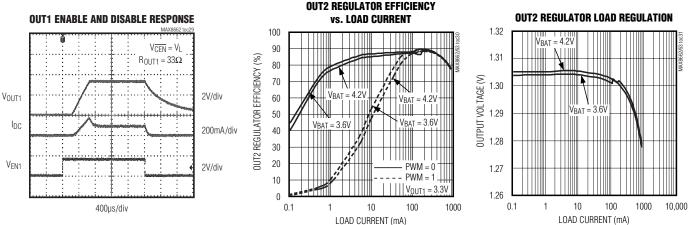

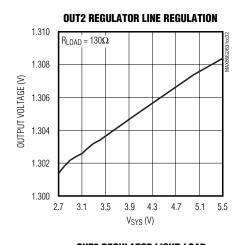

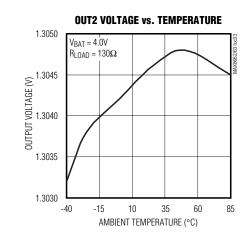

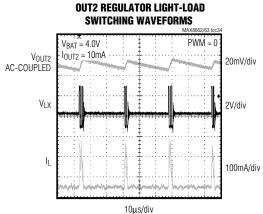

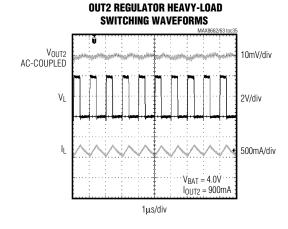

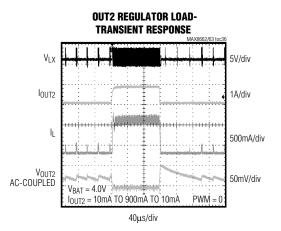

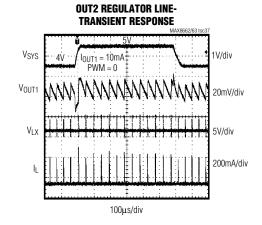

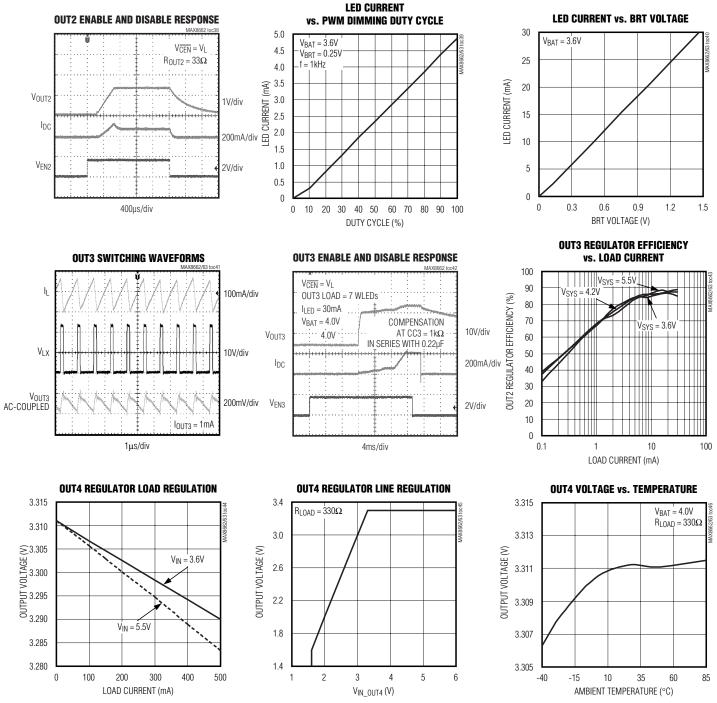

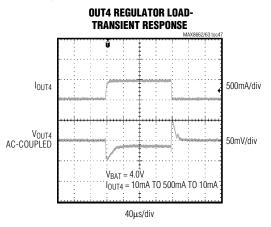

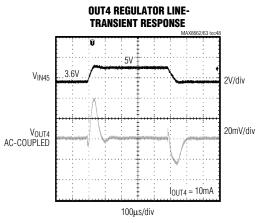

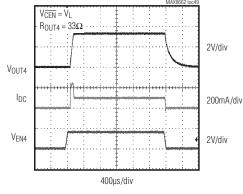

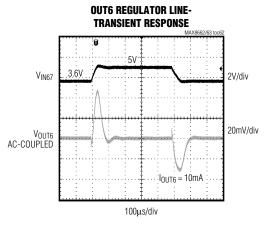

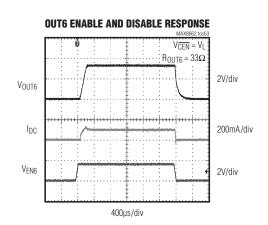

## Typical Operating Characteristics

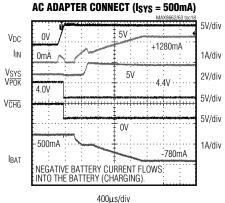

(Circuit of Figure 1, VDC = 5V, RPSET = 1.5kΩ, RISET = 3kΩ, VOUT1 = 3.3V, VOUT2 = 1.3V, SL1 = SL2 = open, VCEN = 0V, VPEN1 = V<sub>PEN2</sub> = 5V, C<sub>OUT1</sub> = 2 x 10μF, C<sub>OUT2</sub> = 2 x 10μF, C<sub>OUT3</sub> = 0.1μF, C<sub>OUT4</sub> = 4.7μF, C<sub>OUT5</sub> = 1μF, C<sub>OUT6</sub> = 2.2μF, C<sub>OUT7</sub> = 1μF, CT =  $0.068\mu\text{F}$ ,  $\text{C}_{\text{REF}} = \text{C}_{\text{VL}} = 0.1\mu\text{F}$ ,  $\text{R}_{\text{THM}} = 10\text{k}\Omega$ ,  $\text{L}1 = 3.3\mu\text{H}$ ,  $\text{L}2 = 4.7\mu\text{H}$ ,  $\text{L}3 = 22\mu\text{H}$ ,  $\text{V}_{\text{GND}} = \text{V}_{\text{PG}1} = \text{V}_{\text{PG}2} = \text{V}_{\text{PG}3} = 0\text{V}$ ,  $\text{T}_{\text{A}} = +25^{\circ}\text{C}$ , unless otherwise noted.)

# Typical Operating Characteristics (continued)

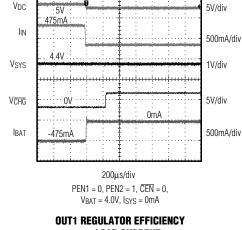

200µs/div

PEN1 = PEN2 = 0,  $\overline{CEN} = 0$ ,

VBAT = 4.0V, ISYS = 50mA, EN\_ = 1

(Circuit of Figure 1,  $V_{DC}$  = 5V,  $R_{PSET}$  = 1.5k $\Omega$ ,  $R_{ISET}$  = 3k $\Omega$ ,  $V_{OUT1}$  = 3.3V,  $V_{OUT2}$  = 1.3V, SL1 = SL2 = open,  $V_{\overline{CEN}}$  = 0V,  $V_{PEN1}$  =  $V_{PEN2}$  = 5V,  $C_{OUT1}$  = 2 × 10 $\mu$ F,  $C_{OUT2}$  = 2 × 10 $\mu$ F,  $C_{OUT3}$  = 0.1 $\mu$ F,  $C_{OUT4}$  = 4.7 $\mu$ F,  $C_{OUT5}$  = 1 $\mu$ F,  $C_{OUT6}$  = 2.2 $\mu$ F,  $C_{OUT7}$  = 1 $\mu$ F,  $C_{T}$  = 0.068 $\mu$ F,  $C_{REF}$  =  $C_{VL}$  = 0.1 $\mu$ F,  $C_{THM}$  = 10k $\Omega$ ,  $C_{TM}$  = 3.3 $\mu$ H,  $C_{TM}$  = 4.7 $\mu$ H,  $C_{TM}$  = 22 $\mu$ H,  $C_{TM}$  =  $C_{TM}$  =  $C_{TM}$  = 0.068 $\mu$ F,  $C_{TM}$  =  $C_{TM}$  = 0.1 $\mu$ F,  $C_{TM}$  = 10k $\Omega$ ,  $C_{TM}$  = 4.7 $\mu$ H,  $C_{TM}$  = 22 $\mu$ H,  $C_{TM}$  =  $C_{TM}$  = 0.1 $\mu$ F,  $C_{T$

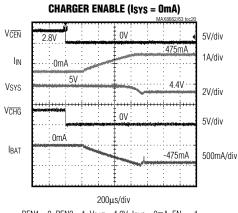

200µs/div

PEN1 = PEN2 = 0,  $\overline{CEN} = 0$ ,

V<sub>BAT</sub> = 4.0V, I<sub>SYS</sub> = 0mA, EN\_ = 1

# Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DC}$  = 5V,  $R_{PSET}$  = 1.5k $\Omega$ ,  $R_{ISET}$  = 3k $\Omega$ ,  $V_{OUT1}$  = 3.3V,  $V_{OUT2}$  = 1.3V, SL1 = SL2 = open,  $V_{\overline{CEN}}$  = 0V,  $V_{PEN1}$  =  $V_{PEN2}$  = 5V,  $C_{OUT1}$  = 2 × 10 $\mu$ F,  $C_{OUT2}$  = 2 × 10 $\mu$ F,  $C_{OUT3}$  = 0.1 $\mu$ F,  $C_{OUT4}$  = 4.7 $\mu$ F,  $C_{OUT5}$  = 1 $\mu$ F,  $C_{OUT6}$  = 2.2 $\mu$ F,  $C_{OUT7}$  = 1 $\mu$ F,  $C_{T}$  = 0.068 $\mu$ F,  $C_{REF}$  =  $C_{VL}$  = 0.1 $\mu$ F,  $C_{THM}$  = 10k $\Omega$ ,  $C_{TM}$  = 3.3 $\mu$ H,  $C_{TM}$  = 4.7 $\mu$ H,  $C_{TM}$  = 22 $\mu$ H,  $C_{TM}$  =  $C_{TM}$  =  $C_{TM}$  = 4.5°C, unless otherwise noted.)

PEN1 = PEN2 = 1, <del>CEN</del> = 0, V<sub>BAT</sub> = 4.0V, I<sub>SYS</sub> = 500mA, EN\_ = 1

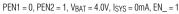

**USB DISCONNECTED (500mA USB)**

# Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DC} = 5V$ ,  $R_{PSET} = 1.5k\Omega$ ,  $R_{ISET} = 3k\Omega$ ,  $V_{OUT1} = 3.3V$ ,  $V_{OUT2} = 1.3V$ , SL1 = SL2 = open,  $V_{\overline{CEN}} = 0V$ ,  $V_{PEN1} = V_{PEN2} = 5V$ ,  $C_{OUT1} = 2 \times 10 \mu F$ ,  $C_{OUT2} = 2 \times 10 \mu F$ ,  $C_{OUT3} = 0.1 \mu F$ ,  $C_{OUT4} = 4.7 \mu F$ ,  $C_{OUT5} = 1 \mu F$ ,  $C_{OUT6} = 2.2 \mu F$ ,  $C_{OUT7} = 1 \mu F$ ,  $C_{OUT7} = 0.068 \mu F$ ,  $C_{REF} = C_{VL} = 0.1 \mu F$ ,  $C_{RTM} = 10 k\Omega$ , C

# Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DC} = 5V$ ,  $R_{PSET} = 1.5k\Omega$ ,  $R_{ISET} = 3k\Omega$ ,  $V_{OUT1} = 3.3V$ ,  $V_{OUT2} = 1.3V$ , SL1 = SL2 = open,  $V_{\overline{CEN}} = 0V$ ,  $V_{PEN1} = V_{PEN2} = 5V$ ,  $C_{OUT1} = 2 \times 10\mu F$ ,  $C_{OUT2} = 2 \times 10\mu F$ ,  $C_{OUT3} = 0.1\mu F$ ,  $C_{OUT4} = 4.7\mu F$ ,  $C_{OUT5} = 1\mu F$ ,  $C_{OUT6} = 2.2\mu F$ ,  $C_{OUT7} = 1\mu F$ ,  $C_{T} = 0.068\mu F$ ,  $C_{REF} = C_{VL} = 0.1\mu F$ ,  $R_{THM} = 10k\Omega$ ,  $L_{T} = 3.3\mu H$ ,  $L_{T} = 4.7\mu H$ ,  $L_{T} = 2.2\mu H$ ,  $V_{T} = V_{T} = 1.34\mu H$ ,  $V_{T} = 1$

13

# Power-Management ICs for Single-Cell, Li+ Battery-Operated Devices

# **Typical Operating Characteristics (continued)**

MIXIM

# **Typical Operating Characteristics (continued)**

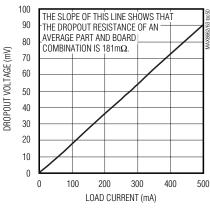

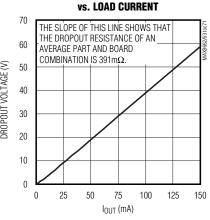

# OUT4 REGULATOR DROPOUT VOLTAGE vs. LOAD CURRENT

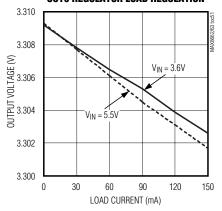

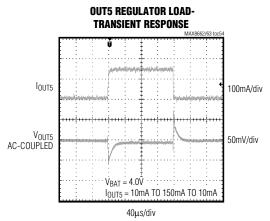

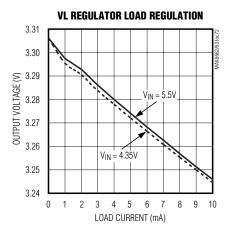

#### **OUT5 REGULATOR LOAD REGULATION**

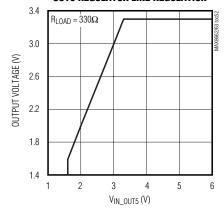

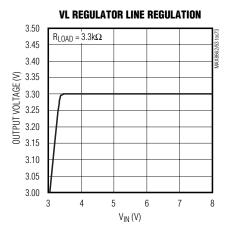

#### **OUT5 REGULATOR LINE REGULATION**

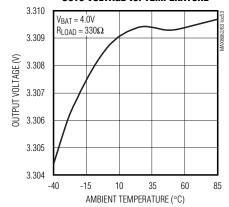

#### **OUT5 VOLTAGE vs. TEMPERATURE**

# Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DC} = 5V$ ,  $R_{PSET} = 1.5k\Omega$ ,  $R_{ISET} = 3k\Omega$ ,  $V_{OUT1} = 3.3V$ ,  $V_{OUT2} = 1.3V$ , SL1 = SL2 = open,  $V_{\overline{CEN}} = 0V$ ,  $V_{PEN1} = V_{PEN2} = 5V$ ,  $V_{OUT1} = 2 \times 10\mu$ F,  $V_{OUT2} = 2 \times 10\mu$ F,  $V_{OUT3} = 0.1\mu$ F,  $V_{OUT4} = 4.7\mu$ F,  $V_{OUT5} = 1\mu$ F,  $V_{OUT6} = 2.2\mu$ F,  $V_{OUT7} = 1\mu$ F,  $V_{OUT7} = 1$

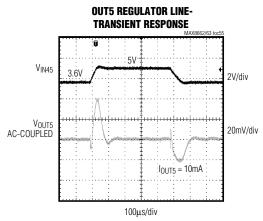

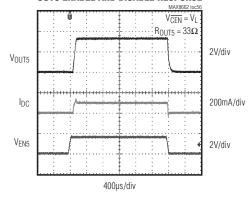

#### **OUT5 ENABLE AND DISABLE RESPONSE**

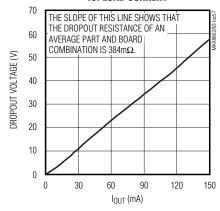

# OUT5 REGULATOR DROPOUT VOLTAGE vs. LOAD CURRENT

## Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{DC}$  = 5V,  $R_{PSET}$  = 1.5k $\Omega$ ,  $R_{ISET}$  = 3k $\Omega$ ,  $V_{OUT1}$  = 3.3V,  $V_{OUT2}$  = 1.3V, SL1 = SL2 = open,  $V_{\overline{CEN}}$  = 0V,  $V_{PEN1}$  =  $V_{PEN2}$  = 5V,  $C_{OUT1}$  = 2 × 10 $\mu$ F,  $C_{OUT2}$  = 2 × 10 $\mu$ F,  $C_{OUT3}$  = 0.1 $\mu$ F,  $C_{OUT4}$  = 4.7 $\mu$ F,  $C_{OUT5}$  = 1 $\mu$ F,  $C_{OUT6}$  = 2.2 $\mu$ F,  $C_{OUT7}$  = 1 $\mu$ F,

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{DC} = 5V$ ,  $R_{PSET} = 1.5k\Omega$ ,  $R_{ISET} = 3k\Omega$ ,  $V_{OUT1} = 3.3V$ ,  $V_{OUT2} = 1.3V$ , SL1 = SL2 = open,  $V_{\overline{CEN}} = 0V$ ,  $V_{PEN1} = V_{PEN2} = 5V$ ,  $C_{OUT1} = 2 \times 10 \mu F$ ,  $C_{OUT2} = 2 \times 10 \mu F$ ,  $C_{OUT3} = 0.1 \mu F$ ,  $C_{OUT4} = 4.7 \mu F$ ,  $C_{OUT5} = 1 \mu F$ ,  $C_{OUT6} = 2.2 \mu F$ ,  $C_{OUT7} = 1 \mu F$ ,  $C_{OUT7} = 0.068 \mu F$ ,  $C_{REF} = C_{VL} = 0.1 \mu F$ ,  $C_{RTM} = 10 k\Omega$ , C

# V<sub>OUT7</sub> V<sub>EN7</sub> 2V/div 400μs/div

**OUT7 REGULATOR DROPOUT VOLTAGE**

# **Pin Description**

|         | IN      |               |                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MAX8662 | MAX8663 | NAME          | FUNCTION                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 1       | 1       | PEN1          | Input Limiter-Control Input 1. Used with $\overline{\text{CEN}}$ and PEN2 to set the DC current limit to 95mA, 475mA, a resistor programmable level up to 2A, or to turn off the input limiter (see Table 1).                                                                                     |  |  |  |  |  |

| 2       | 2       | PEN2          | Input Limiter-Control Input 2. Used with $\overline{CEN}$ and PEN1 to set the DC current limit to 95mA, 475mA, a resistor programmable level up to 2A, or to turn off the input limiter (see Table 1).                                                                                            |  |  |  |  |  |

| 3       | _       | EN3           | Enable Input and PWM Dimming Input for Regulator 3 White LED Boost. Drive high to enable. Drive low for more than 2ms to turn off. For PWM-controlled dimming, drive EN3 with a PWM switching input with a frequency of 1kHz to 100kHz.                                                           |  |  |  |  |  |

| 4, 5    | 3, 4    | DC1,<br>DC2   | DC Input Source. Connect to an AC adapter or USB source. DC1 and DC2 are internally connected.                                                                                                                                                                                                    |  |  |  |  |  |

| 6, 7    | 5, 6    | SYS1,<br>SYS2 | System Supply Voltage. The SYS output supplies power to all regulators. With no external power, SYS1 and SYS2 connect to BAT through an internal $40m\Omega$ switch. When a valid voltage is present at DC_, SYS_ connects to DC_ but is limited to 5.3V. SYS1 and SYS2 are internally connected. |  |  |  |  |  |

| 8, 9    | 7, 8    | BAT1,<br>BAT2 | Battery Connections. Connect to a single-cell Li+ battery. The battery is charged from SYS_ when a valid source is present at DC. BAT_ drives SYS_ when DC is not valid. BAT1 and BAT2 are internally connected.                                                                                  |  |  |  |  |  |

| 10      | _       | BRT           | LED Analog Brightness Control Input. Connect BRT to a voltage from 50mV to 1.5V to set I <sub>CS</sub> from 1mA to 30mA. Connect BRT to the center of a resistor-divider connected between REF and GND to set a fixed brightness when analog dimming is not required.                             |  |  |  |  |  |

| 11      | 9       | CHG           | Charger Status Output. CHG is an open-drain nMOS that pulls low when the charger is in fast charge or prequalification modes. CHG goes high impedance when the charger is in top-off mode or disabled.                                                                                            |  |  |  |  |  |

| 12      | 10      | CEN           | Charger Enable Input. Drive $\overline{\text{CEN}}$ low to enable the charger when a valid source is connected at DC. Drive $\overline{\text{CEN}}$ high to disable charging. Drive $\overline{\text{CEN}}$ high and PEN2 low to enter USB suspend mode.                                          |  |  |  |  |  |

| 13      | 11      | THM           | Thermistor Input. Connect a $10k\Omega$ negative temperature coefficient (NTC) thermistor from THM to GND. Charging is suspended when the temperature is beyond the hot or cold limits. Connect THM to GND to disable the thermistor functionality.                                               |  |  |  |  |  |

| 14      | 12      | ISET          | Charge Rate-Set Input. Connect a resistor from ISET to GND to set the fast-charge current from 300mA to 1.25A. The prequalification charge current and top-off threshold are set to 10% and 7.5% of fast-charge current, respectively.                                                            |  |  |  |  |  |

| 15      | 13      | СТ            | Charge Timer-Programming Pin. Connect a capacitor from CT to GND to set the length of time required to trigger a fault condition in fast-charge or prequalification mode and to determine the time the charger remains in top-off mode. Connect CT to GND to disable timers.                      |  |  |  |  |  |

| 16      | _       | REF           | Reference Voltage. Provides 1.5V output when EN3 is high. An internal discharge resistance pulls REF to 0V when EN3 is low.                                                                                                                                                                       |  |  |  |  |  |

| 17      | 14      | GND           | Ground. Low-noise ground connection.                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 18      | 15      | OUT4          | Linear Regulator 4 Output. Delivers up to 500mA at an output voltage determined by SL1 and SL2. Connect a $4.7\mu F$ ceramic capacitor from OUT4 to GND. Increase the value to $10\mu F$ if $V_{OUT4} < 1.5V$ .                                                                                   |  |  |  |  |  |

MIXI/M

# \_\_Pin Description (continued)

| PIN     |         | l    |                                                                                                                                                                                                                                                                                                                                         |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX8662 | MAX8663 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                |

| 19      | 16      | IN45 | Input Supply for Linear Regulators 4 and 5. Connect IN45 to a supply voltage between 1.7V and $V_{SYS}$ . Connect at least a 1µF ceramic capacitor from IN45 to GND.                                                                                                                                                                    |

| 20      | 17      | OUT5 | Linear Regulator 5 Output. Delivers up to 150mA at an output voltage determined by SL1 and SL2. Connect a 1 $\mu$ F ceramic capacitor from OUT5 to GND. Increase the value to 2.2 $\mu$ F if Vout5 < 1.5V.                                                                                                                              |

| 21      | 18      | EN4  | Enable Input for Linear Regulator 4. Drive high to enable.                                                                                                                                                                                                                                                                              |

| 22      | 19      | EN5  | Enable Input for Linear Regulator 5. Drive high to enable.                                                                                                                                                                                                                                                                              |

| 23      | 20      | PWM  | PWM/Skip-Mode Selector. Drive PWM high to force step-down regulators 1 and 2 to operate in 1MHz forced-PWM mode. Drive PWM low, or connect to GND to allow regulators 1 and 2 to enter skip mode at light loads.                                                                                                                        |

| 24      | 21      | FB1  | Feedback Input for Buck Regulator 1. Connect FB1 to the center of a resistor-divider connected between OUT1 and GND to set the output voltage between 0.98V and 3.3V.                                                                                                                                                                   |

| 25      | 22      | EN1  | Enable Input for Buck Regulator 1. Drive high to enable.                                                                                                                                                                                                                                                                                |

| 26      | 23      | PG1  | Power Ground for Buck Regulator 1. GND, PG1, PG2, and PG3 must be connected together externally.                                                                                                                                                                                                                                        |

| 27      | 24      | LX1  | Buck Regulator 1 Inductor Connection Node. Connect an inductor from LX1 to the output of regulator 1.                                                                                                                                                                                                                                   |

| 28      | 25      | PV1  | Power Input for Buck Regulator 1. Connect PV1 to SYS and decouple with a 10µF or greater low-ESR capacitor to GND. PV1, PV2, and SYS must be connected together externally.                                                                                                                                                             |

| 29      | _       | OVP  | LED Boost Overvoltage Input. Connect a resistor from OVP to the boost output to set the maximum output voltage and to initiate soft-start when EN3 goes high. An internal 20µA pulldown current from OVP to GND determines the maximum boost voltage. The internal current is disconnected when EN3 is low. OVP is diode clamped to SYS |

| 30      | _       | CS   | LED Current Source. Sinks from 1mA to 30mA depending on the voltage at BRT and the PWM signal at EN3. Driving EN3 low for more than 2ms turns off the current source. V <sub>CS</sub> is regulated to 0.32V.                                                                                                                            |

| 31      | _       | CC3  | Compensation Input for LED Boost Regulator 3. See the <i>Boost Converter with White LED Driver</i> (OUT3, MAX8662 Only) section.                                                                                                                                                                                                        |

| 32      | 26      | FB2  | Feedback Input for Buck Regulator 2. Connect FB2 to the center of a resistor-divider connected between OUT2 and GND to set the output voltage between 0.98V and 3.3V.                                                                                                                                                                   |

| 33      | 27      | PV2  | Power Input for Buck Regulator 2. Connect PV2 to SYS and decouple with a 10µF or greater low-ESR capacitor to GND. PV1, PV2, and SYS must be connected together externally.                                                                                                                                                             |

| 34      | 28      | LX2  | Buck Regulator 2 Inductor Connection Node. Connect an inductor from LX2 to the output of regulator 2.                                                                                                                                                                                                                                   |

| 35      | 29      | PG2  | Power Ground for Buck Regulator 2. GND, PG1, PG2, and PG3 must be connected together externally.                                                                                                                                                                                                                                        |

| 36      | 30      | EN2  | Enable Input for Buck Regulator 2. Drive high to enable.                                                                                                                                                                                                                                                                                |

| 37      | 31      | EN6  | Enable Input for Linear Regulator 6. Drive high to enable.                                                                                                                                                                                                                                                                              |

| 38      | 32      | EN7  | Enable Input for Linear Regulator 7. Drive high to enable.                                                                                                                                                                                                                                                                              |

| 39      | _       | LX3  | Boost Regulator 3 Inductor Connection Node. Connect an inductor from LX3 to SYS                                                                                                                                                                                                                                                         |

# Pin Description (continued)

| PIN NAME MAX8662 MAX8663 |    |      | FUNCTION                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                          |    | NAME | FUNCTION                                                                                                                                                                                                                                                                                                              |  |  |

| 40                       | _  | PG3  | Power Ground for Boost Regulator 3. GND, PG1, PG2, and PG3 must be connected together externally.                                                                                                                                                                                                                     |  |  |

| 41                       | 33 | OUT6 | Linear Regulator 6 Output. Delivers up to 300mA at an output voltage determined by SL1 and SL2. Connect a 2.2µF ceramic capacitor from OUT6 to GND. Increase the value to 4.7µF if V <sub>OUT6</sub> < 1.5V.                                                                                                          |  |  |

| 42                       | 34 | IN67 | Input Supply for Linear Regulators 6 and 7. Connect IN67 to a supply voltage of 1.7V to V <sub>SYS</sub> . Connect at least a 1µF ceramic capacitor from IN67 to GND.                                                                                                                                                 |  |  |

| 43                       | 35 | OUT7 | Linear Regulator 7 Output. Delivers up to 150mA at an output voltage determined by SL1 and SL2. Connect a $1\mu F$ ceramic capacitor from OUT7 to GND. Increase the value to $2.2\mu F$ if $V_{OUT7} < 1.5V$ .                                                                                                        |  |  |

| 44                       | 36 | VL   | Input Limiter and Charger Logic Supply. Provides 3.3V when a valid input voltage is present at DC. Connect a 0.1µF capacitor from VL to GND. VL is capable of providing up to 10mA to an external load when DC is valid.                                                                                              |  |  |

| 45                       | 37 | SL1  | Output-Voltage Select Inputs 1 and 2 for Linear Regulators. Leave disconnected, or connect to GND or SYS to set to one of three states. SL1 and SL2 set the output voltage of                                                                                                                                         |  |  |

| 46                       | 38 | SL2  | OUT4, OUT5, OUT6, and OUT7 to one of nine combinations. See Table 3.                                                                                                                                                                                                                                                  |  |  |

| 47                       | 39 | PSET | Input Current-Limit Set Input. Connect a resistor (R <sub>PSET</sub> ) from PSET to ground to program the DC input current limit from 500mA to 2A.                                                                                                                                                                    |  |  |

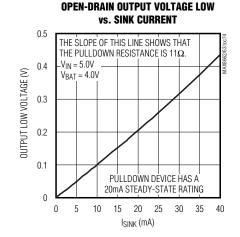

| 48                       | 40 | POK  | Power-Ok Output. POK is an open-drain nMOS output that pulls low when a valid input is detected at DC. This output is not affected by the states of PEN1, PEN2, or CEN.                                                                                                                                               |  |  |

| _                        | _  | EP   | Exposed Paddle. Connect the exposed paddle to ground. Connecting the exposed paddle to ground does not remove the requirement for proper ground connections to GND, PG1, PG2, and PG3. The exposed paddle is attached with epoxy to the substrate of the die, making it an excellent path to remove heat from the IC. |  |  |

20 \_\_\_\_\_\_ **/VI/XI/M**

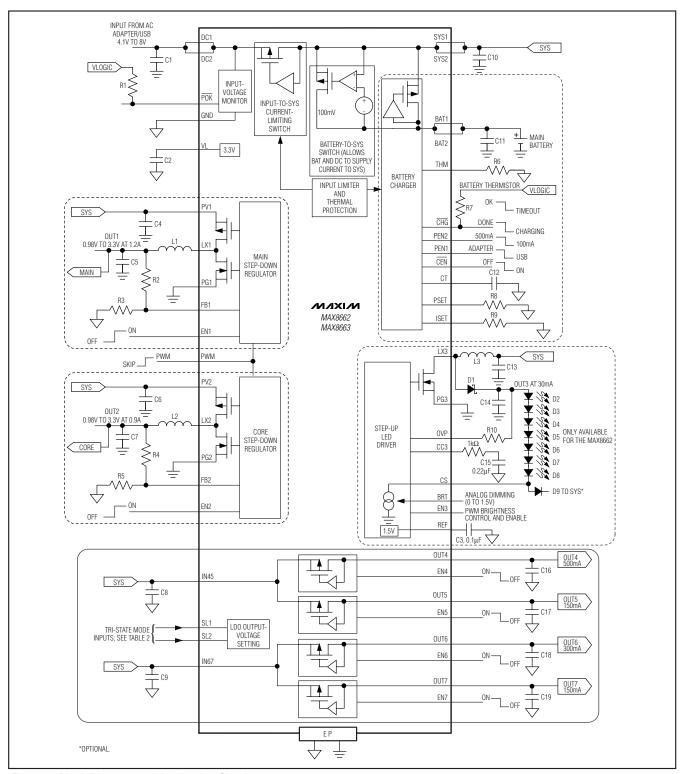

Figure 1. Block Diagram and Application Circuit

## **Detailed Description**

The MAX8662/MAX8663 highly integrated PMICs are designed for use in smart cellular phones, PDAs, Internet appliances, and other portable devices. They integrate two synchronous buck regulators, a boost regulator driving two to seven white LEDs (MAX8662 only), four low dropout (LDO) linear regulators, and a linear charger for a single-cell Li+ battery. Figure 1 is the block diagram and application circuit.

SPS circuitry offers flexible power distribution between an AC adapter or USB source, battery, and system load, and makes the best use of available power from the AC adapter/USB input. The battery is charged with any available power not used by the system load. If a system load peak exceeds the current limit, supplemental current is taken from the battery. Thermal limiting prevents overheating by reducing power drawn from the input source.

Two step-down DC-DC converters achieve excellent light-load efficiency and have on-chip soft-start circuitry; 1MHz switching frequency allows for small external components. Four LDO linear regulators feature low quiescent current and operate from inputs as low as 1.7V. This allows the LDOs to operate from the step-down output voltage to improve efficiency. The white LED driver features easy adjustment of LED brightness and open-LED overvoltage protection. A 1-cell Li+charger has programmable charge current up to 1.25A and a charge timer.

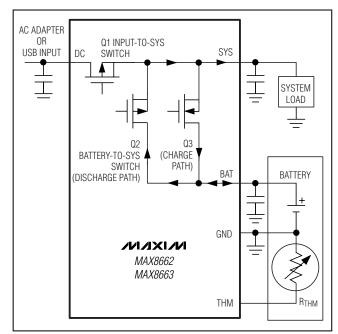

#### **Smart Power Selector (SPS)**

SPS seamlessly distributes power between the external input, the battery, and the system load (Figure 2). The basic functions of SPS are:

- With both the external power supply and battery connected:

- a) When the system load requirements exceed the capacity of the external power input, the battery supplies supplemental current to the load.

- b) When the system load requirements are less than the capacity of the external power input, the battery is charged with residual power from the input.

- When the battery is connected and there is no external power input, the system is powered from the battery.

- When an external power input is connected and there is no battery, the system is powered from the external power input.

A thermal-limiting circuit reduces battery-charge rate and external power-source current to prevent overheating.

Figure 2. Smart Power Selector Block Diagram

#### **Input Limiter**

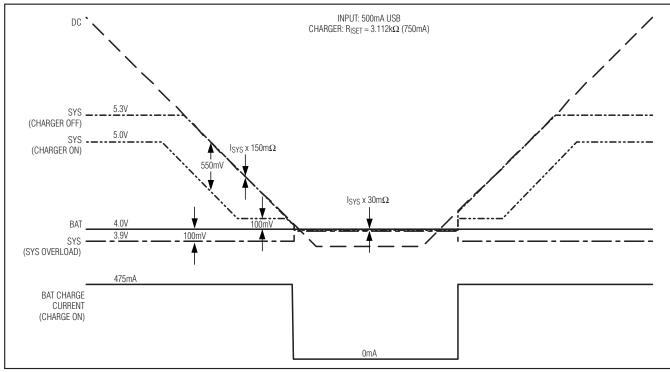

All regulated outputs (OUT1-OUT7) derive their power from the SYS output. With an AC adapter or USB source connected at DC, the input limiter distributes power from the external power source to the system load and battery charger. In addition to the input limiter's primary function of passing the DC power source to the system and charger loads at SYS, it performs several additional functions to optimize use of available power:

- Input Voltage Limiting: If the voltage at DC rises, SYS limits to 5.3V, preventing an overvoltage of the system load. A DC voltage greater than 6.9V is considered invalid and the input limiter disconnects the DC input entirely. The withstand voltage at DC is guaranteed to be at least 9V. A DC input is also invalid if it is less than BAT, or less than the DC undervoltage threshold of 3.5V (falling). With an invalid DC input voltage, SYS connects to BAT through a 40mΩ switch.

- Input Overcurrent Protection: The current at DC is limited to prevent input overload. This current limit is automatically adjusted to match the capabilities of source, whether it is a 100mA or 500mA USB source, or an AC adapter. When the load exceeds the input current limit, SYS drops to 100mV below BAT and supplemental load current is provided by the battery.