TLK10081

SLLSEE9-NOVEMBER 2013

# 10Gbps 1-8 CHANNEL MULTI-RATE SERIAL LINK AGGREGATOR

Check for Samples: TLK10081

## **1 INTRODUCTION**

## 1.1 Features

- Automatic Digital Multiplexing/De-Multiplexing of 1 to 8 Independent Lower Speed Gigabit Serial Lines into a Single Higher Speed Gigabit Serial Line with Extensive Media Transmission Capabilities.

- 1~8 x (0.25 to 1.25 Gbps) to 1 x (2 to 10 Gbps) Multiplexing

- 1 x (0.5 to 2.5 Gbps) to 1 x (0.5 to 2.5 Gbps)

- Dynamic Port Aggregation Supported

- Programmable High Speed Redundant Switching

- Wide Data Rate Range for Multiple Application

Support

- Transmit De-Emphasis and Adaptive Receiver Equalization on Both Low Speed and High Speed Sides

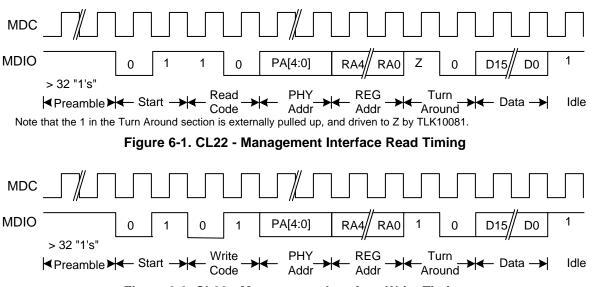

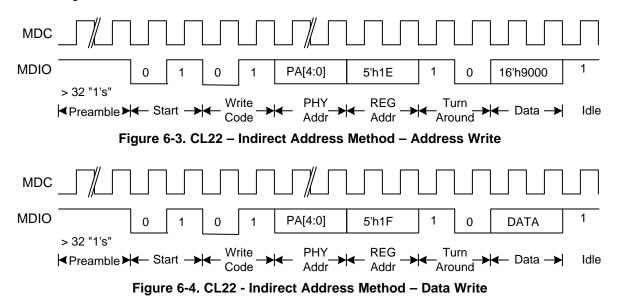

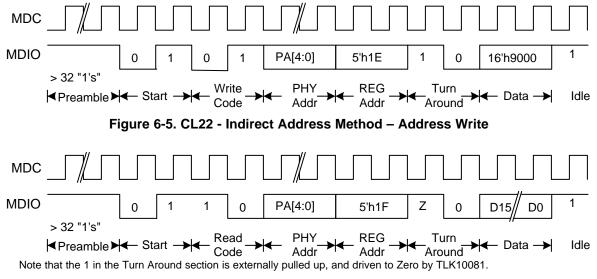

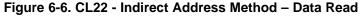

- MDIO Clause 22 control interface

- 8B/10B ENDEC Coding Support

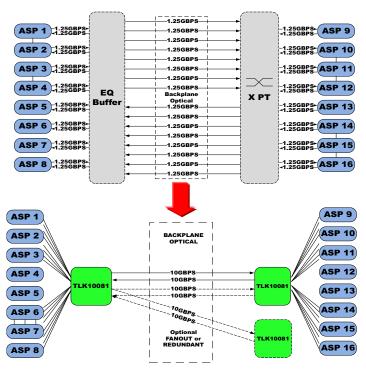

## 1.2 Applications

- Gigabit Serial Link Aggregation

- Communications System Backplanes

- Raw (Unencoded) Data Support

- Core Supply 1V; I/O: 1.5V/1.8V

- Superior Signal Integrity Performance

- Low Power Operation: < 800 mW per channel (typ)

- Rate Matching Support (For compatible data protocols like GE PCS)

- Full Non-Blocking Receiver Crosspoint Mapping Capability

- Flexible Clocking

- Multi Drive Capability (SFP+, backplane, cable)

- Support for Programmable High Speed Lane Alignment Characters

- Support for Programmable HS/LS 10-Bit Alignment Characters

- Wide Range of Built-in Test Patterns

- 144-pin, 13mmx13mm FCBGA Package

- Machine Vision

- Video/Image Data Processing

**A**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## 1.3 Description

The TLK10081 is a multi-rate link aggregator intended for use in high-speed bi-directional point-to-point data transmission systems. The device allows for a reduction in the number of physical links required for a certain data throughput by multiplexing multiple lower-rate serial links into higher-rate serial links.

The TLK10081 has a low-speed interface which can accommodate one to eight bidirectional serial links running at rates from 250 Mbps to 1.25 Gbps (maximum of 10 Gbps total throughput). The device's high speed interfaces can operate at rates from 1 Gbps to 10 Gbps. The high speed interface is designed to run at 8 x the low speed serial rate regardless of the number of lanes connected. Filler data will be placed on any unused lanes in order to keep the interleaved lane ordering constant. This allows for low speed lanes to be hot swapped during normal operation without requiring a change in configuration.

A 1:1 mode is also supported for data rates ranging from 0.5 Gbps to 2.5 Gbps, whereby both low speed and high speed are rate matched. The TX and RX datapaths are also independent, so TX may operate in 8:1 mode while RX operates in 1:1 mode. This independence is restricted to using the same low speed line rate. For example, the TX can operate at 8 x 1.25 Gbps while RX operates at 1 x 1.25 Gbps.

The individual Low Speed lanes may also operate at independent rates in byte interleave mode, provided they are operating at integer multiples. The High Speed line rate must be configured based on the fastest Low Speed line rate.

The device has multiple interleaving/de-interleaving schemes that may be used depending on the data type. These schemes allow for the low speed lane ordering to be recovered after the lanes are transmitted over a single high-speed link. There is also a programmable scrambling/de-scrambling function available to help ensure that the high-speed data has suitable properties for transmission (i.e., sufficient transition density for clock recovery and DC balance over time) even for non-ideal input data.

The TLK10081 has the ability to perform lane alignment on 2, 3, or 4 lanes with up to four bytes of lane de-skew.

Both the low speed and high speed side interfaces (transmitters and receivers) use CML signaling with integrated termination resistors and feature programmable transmitter de-emphasis levels and adaptive receive equalization to help compensate for media impairments at higher frequencies. The device's serial transceivers used are capable of interfacing to optical modules as well as higher-loss connections such as PCB backplanes and controlled-impedance copper cabling.

To aid in system synchronization, the TLK10081 is capable of extracting clocking information from the serial input data streams and outputting a recovered clock signal. This recovered clock can be input to a jitter cleaner in order to provide a synchronized system clock. The device also has two reference clock input ports and a flexible internal PLL, allowing for various serial rates to be supported with a single reference clock input frequency.

The device has various built-in self-test features to aid with system validation and debugging. Among these are pattern generation and verification on all serial lanes as well as internal data loopback paths.

## 2 PHYSICAL CHARACTERISTICS

## 2.1 Block Diagram

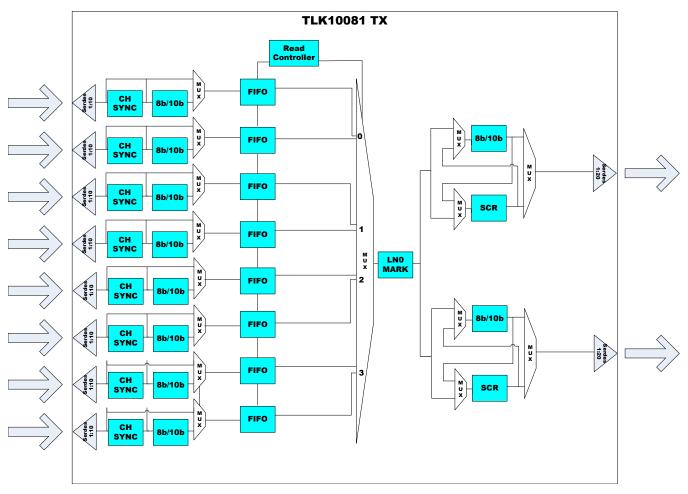

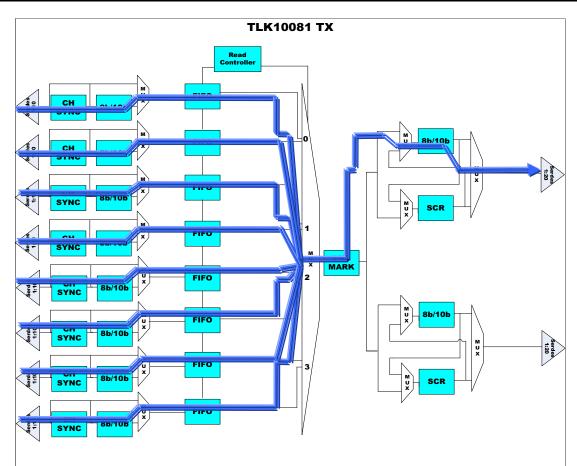

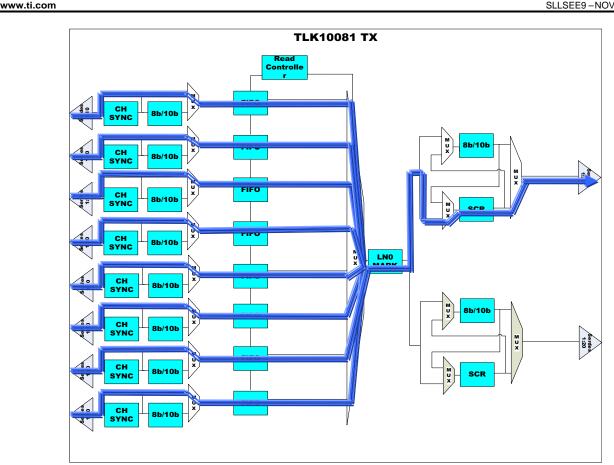

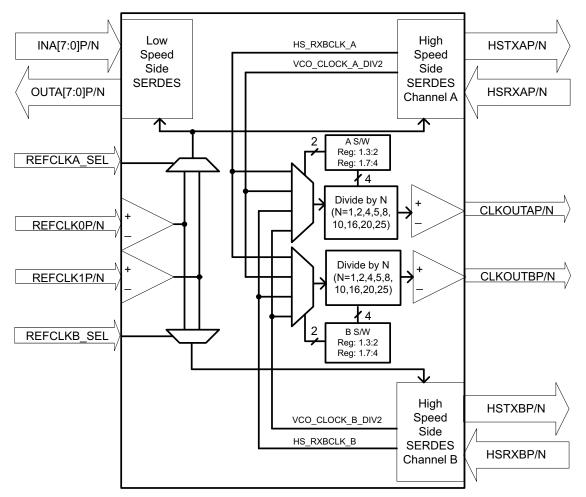

A simplified block diagram of the TLK10081 device for 8:1 mode is shown in Figure 2-1 and Figure 2-2. This low-power transceiver consists of two serializer/deserializer (SERDES) blocks, one on the low speed side and the other on the high speed side. The core logic block that lies between the two SERDES blocks carries out all the logic functions including test pattern generation and verification.

The TLK10081 provides a management data input/output (MDIO) control interface as well as a JTAG interface for device configuration, control, and monitoring. Detailed descriptions of the TLK10081 pin functions are provided in Figure 2-1.

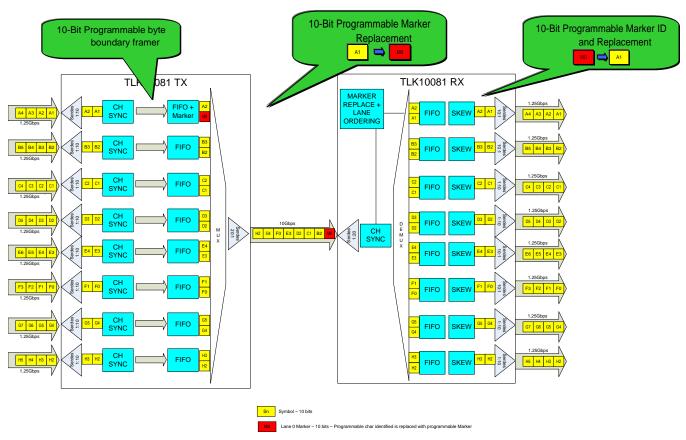

Figure 2-1. A Simplified Block Diagram of the TLK10081 (TX)

SLLSEE9-NOVEMBER 2013

TEXAS INSTRUMENTS

www.ti.com

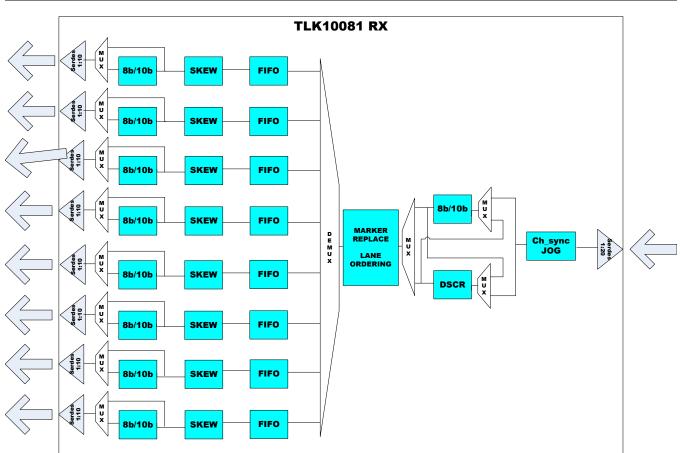

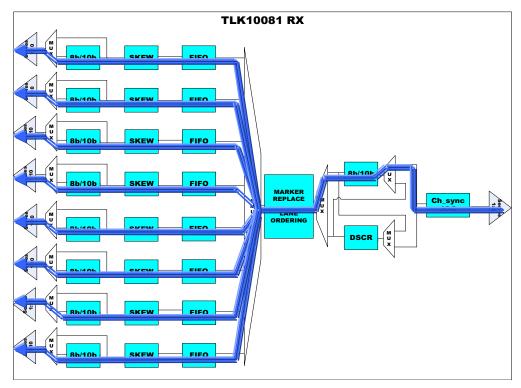

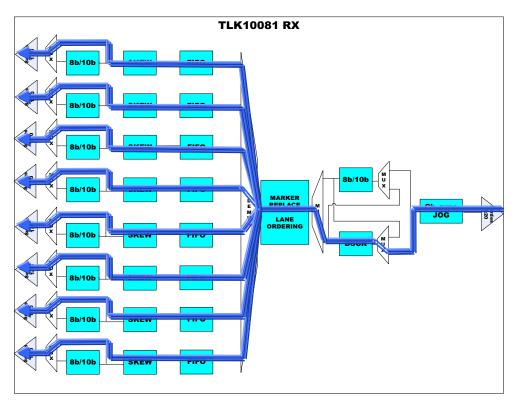

Figure 2-2. A Simplified Block Diagram of the TLK10081 (RX)

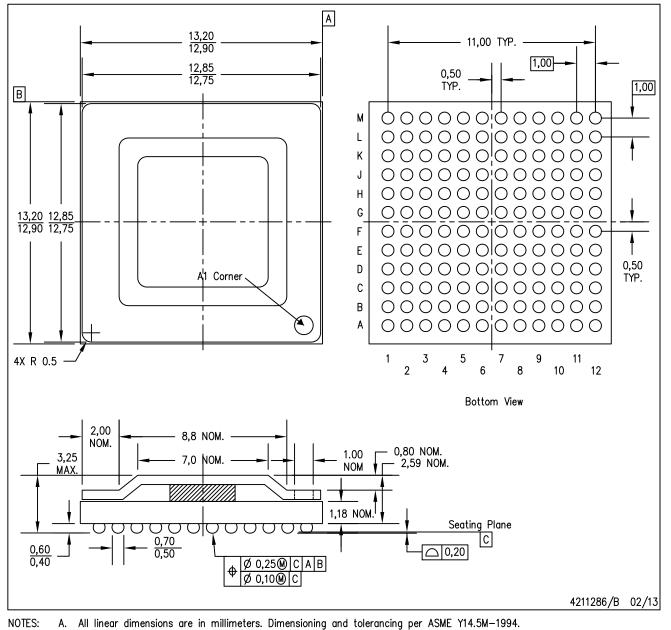

## 2.2 Package

A 13-mm x 13-mm, 144-pin PBGA package with a ball pitch of 1 mm is used. The device pin-out is as shown in Figure 2-3 and is described in detail in Table 2-1 and Table 2-2.

|      | 1            | 2       | 3        | 4        | 5       | 6      | 7      | 8        | 9         | 10         | 11       | 12     |

|------|--------------|---------|----------|----------|---------|--------|--------|----------|-----------|------------|----------|--------|

| Δ[   | INA1P        | VSS     | INAON    | INAOP    | VSS     | OUTAOP | OUTAON | PDTRXA_N | CLKOUTBP  | CLKOUTBN   | VSS      | HSRXAN |

| в    | INA1N        | INA2P   | VSS      | VSS      | OUTA1P  | OUTA1N | VSS    | TMS      | PRBSEN    | RXCTRL_0   | VSS      | HSRXAP |

| С    | VSS          | INA2N   | VDDRA_LS | OUTA2P   | OUTA2N  | VSS    | VDDOO  | TDI      | CLKOUTAP  | CLKOUTAN   | AMUXA    | VSS    |

| D    | <b>INA3P</b> | VDDA_LS | VSS      | AMUXB    | VSS     | TDO    | VPP    | тск      | GPO0      | VSS        | VSS      | HSTXAP |

| Е    | INA3N        | VSS     | OUTA3N   | VSS      | TRST_N  | VDDD   | DVDD   | VDDD     | LOSA      | PRTAD0     | VDDRA_HS | HSTXAN |

| F    | VSS          | VDDA_LS | OUTA3P   | VDDT_LS  | VSS     | VDDD   | DVDD   | VSS      | VDDT_HS   | VSS        | VDDA_HS  | VSS    |

| G    | VSS          | VDDA_LS | VSS      | VDDT_LS  | VSS     | DVDD   | VSS    | DVDD     | PRTAD1    | VDDA_HS    | VSS      | HSRXBN |

| н    | INA4P        | VSS     | OUTA4N   | VSS      | RESET_N | VDDD   | DVDD   | VDDD     | GPO1      | REFCLK_SEL | VSS      | HSRXBP |

| J    | INA4N        | VDDA_LS | OUTA4P   | PDTRXB_N | VSS     | PRTAD3 | MDIO   | MDC      | PRBS_PASS | GP10       | VDDRB_HS | VSS    |

| к    | VSS          | INA5P   | VDDRB_LS | OUTA5N   | OUTASP  | VSS    | VDDO1  | LOSB     | REFCLK1P  | REFCLK1N   | VSS      | HSTXBP |

| - L[ | INA6P        | INA5N   | VSS      | VSS      | OUTA6N  | OUTA6P | VSS    | RXCTRL_1 | PRTAD2    | TESTEN     | VSS      | HSTXBN |

| м    | INA6N        | VSS     | INA7P    | INA7N    | VSS     | OUTA7N | OUTA7P | PRTAD4   | GPI1      | REFCLKOP   | REFCLKON | VSS    |

Figure 2-3. The Pin-Out of the TLK10081

## 2.3 Terminal Functions

The details of the terminal functions of the TLK10081 device are provided in Table 2-1 and Table 2-2.

| TERMI            | NAL                                                                  | DIRECTION                                            | DEGODICTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|----------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL           | BGA                                                                  | TYPE<br>SUPPLY                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHANNEL A        |                                                                      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HSTXAP<br>HSTXAN | D12<br>E12                                                           | Output<br>CML<br>VDDA_HS                             | <b>High Speed Transmit Channel A Output.</b> HSTXAP and HSTXAN comprise the high speed side transmit direction Channel A differential serial output signal. During device reset (RESET_N asserted low) these pins are driven differential zero. These CML outputs must be AC coupled.                                                                                                                                                                                                                                                                                                                                                 |

| HSRXAP<br>HSRXAN | B12<br>A12                                                           | Input<br>CML<br>VDDA_HS                              | High Speed Receive Channel A Input. HSRXAP and HSRXAN comprise the high speed side receive direction Channel A differential serial input signal. These CML input signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INA[7:0]P/N      | M3/M4<br>L1/M1<br>K2/L2<br>H1/J1<br>D1/E1<br>B2/C2<br>A1/B1<br>A4/A3 | Input<br>CML<br>VDDA_LS                              | Low Speed Channel A Inputs. INAP and INAN comprise the low speed side transmit direction differential input signals. These signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OUTA[7:0]P/N     | M7/M6<br>L6/L5<br>K5/K4<br>J3/H3<br>F3/E3<br>C4/C5<br>B5/B6<br>A6/A7 | Output<br>CML<br>VDDA_LS                             | Low Speed Channel A Outputs. OUTAP and OUTAN comprise the low speed side receive direction differential output signals. During device reset (RESET_N asserted low) these pins are driven differential zero. These signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                         |

| LOSA             | E9                                                                   | Output LVCMOS<br>1.5V/1.8V                           | Channel A Receive Loss Of Signal (LOS) Indicator.<br>LOSA=0: Signal detected.<br>LOSA=1: Loss of signal.<br>Loss of signal detection is based on the input signal level. When HSRXAP/N has a differential<br>input signal swing of <75 mV <sub>pp</sub> , LOSA will be asserted (if enabled). If the input signal is greater<br>than 150 mV <sub>p-p</sub> , LOS will be deasserted. Outside of these ranges, the LOS indication is undefined<br>of the input signal sector is the loss of the input signal is greater than 150 mV <sub>p-p</sub> . LOSA will be deasserted. Outside of these ranges, the LOS indication is undefined |

|                  | 20                                                                   | VDDO0<br>40Ω Driver                                  | Other functions can be observed on LOSA real-time, configured via MDIO<br>During device reset (RESET_N asserted low) this pin is driven low. During pin based power down<br>(PDTRXA_N asserted low), this pin is floating. During register based power down, this pin is<br>floating.<br>It is highly recommended that LOSA be brought to an easily accessible point on the application<br>board (header) in the event that debug is required.                                                                                                                                                                                        |

| RXCTRL_0         | B10                                                                  | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO0                | Channel A Bit Interleave Lane Rotation Jog.<br>A toggle of this pin, either from high to low or from low to high, causes a lane rotation of the<br>HSRXAP/N source data.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPO0             | D9                                                                   | Output<br>LVCMOS<br>1.5V/1.8V<br>VDDO0<br>40Ω Driver | Channel A Multi-purpose Status Indicator.<br>This pin should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PDTRXA_N         | A8                                                                   | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO0                | Transceiver Power Down.<br>When this pin is held low (asserted), the device is placed in power down mode. When deasserted the device operates normally. After deassertion, a software data path reset should be issued through the MDIO interface.                                                                                                                                                                                                                                                                                                                                                                                    |

| CHANNEL B (Hig   | h Speed Interfa                                                      | ice Only)                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HSTXBP<br>HSTXBN | K12<br>L12                                                           | Output<br>CML<br>VDDA_HS                             | Serial Transmit Channel B Output. HSTXBP and HSTXBN comprise the high speed side transmit direction Channel B differential serial output signal. During device reset (RESET_N asserted low) these pins are driven differential zero. These CML outputs must be AC coupled.                                                                                                                                                                                                                                                                                                                                                            |

| HSRXBP<br>HSRXBN | H12<br>G12                                                           | Input<br>CML<br>VDDA_HS                              | Serial Receive Channel B Input. HSRXBP and HSRXBN comprise the high speed side receive direction Channel B differential serial input signal. These CML input signals must be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## Table 2-1. Pin Description - Signal Pins

## Table 2-1. Pin Description - Signal Pins (continued)

| TERMI                    | NAL              | DIRECTION                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------------|------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SIGNAL                   | BGA              | TYPE<br>SUPPLY                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| LOSB                     | K8               | Output<br>LVCMOS<br>1.5V/1.8V<br>VDDO1<br>40Ω Driver | Channel B Receive Loss of Signal (LOS) Indicator.         LOSB=0: Signal detected.         LOSB=1: Loss of signal.         Loss of signal detection is based on the input signal level. When HSRXBP/N has a differential input signal swing of ≤75 mVpp, LOSB will be asserted (if enabled). If the input signal is greater than 150 mVp-p, LOS will be deasserted. Outside of these ranges, the LOS indication is undefined.         Other functions can be observed on LOSB real-time, configured via MDIO.         During device reset (RESET_N asserted low) this pin is driven low. During pin based power down (PDTRXB_N asserted low), this pin is floating. During register based power down, this pin is floating.         It is highly recommended that LOSB be brought to an easily accessible point on the application board (header) in the event that debug is required. |  |  |  |

| RXCTRL_1                 | L8               | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO1                | <b>Channel B Bit Interleave Lane Rotation Jog.</b><br>A toggle of this pin, either from high to low or from low to high, causes a lane rotation of the HSRXBP/N source data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| GPO1                     | H9               | Output<br>LVCMOS<br>1.5V/1.8V<br>VDDO1<br>40Ω Driver | <b>Channel B General Purpose Output.</b><br>This pin should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PDTRXB_N                 | J4               | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO1                | <b>Transceiver Power Down.</b> When this pin is held low (asserted), Channel B is placed in power down mode. When deasserted, Channel B operates normally. After deassertion, a software data path reset should be issued through the MDIO interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| REFERENCE CLC            | OCKS AND CON     | ITROL AND MONITORI                                   | NG SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| REFCLK0P/N               | M10 / M11        | Input<br>LVDS/LVPECL<br>DVDD                         | <b>Reference Clock Input Zero.</b> This differential input is a clock signal used as a reference to one or both channels. The reference clock selection is done through MDIO or REFCLKA_SEL and REFCLKB_SEL pins. This input signal <b>must</b> be AC coupled. If unused, REFCLK0P/N should be pulled down to GND through a shared 100 ohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| REFCLK1P/N               | K9 / K10         | Input<br>LVDS/LVPECL<br>DVDD                         | <b>Reference Clock Input One.</b> This differential input is a clock signal used as a reference to one or both channels. The reference clock selection is done through MDIO. This input signal <b>must</b> be AC coupled. If unused, REFCLK1P/N should be pulled down to GND through a shared 100 ohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| REFCLK_SEL               | H10              | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO0                | <b>Reference Clock Select.</b> This input, when low, selects REFCLK0P/N as the clock reference to Channel A/B SERDES. When high, REFCLK1P/N is selected as the clock reference to Channel A/B SERDES. If software control is desired, this input signal should be tied low. Default reference clock for Channel A/B is REFCLK0P/N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| CLKOUTAP/N<br>CLKOUTBP/N | C9/C10<br>A9/A10 | Output<br>CML<br>DVDD                                | Channel A/B Output Clock. By default, this output is enabled and outputs the high speed side         Channel A recovered byte clock (high speed line rate divided by 20). Optionally it can be         configured to output the VCO clock divided by 2. Additional MDIO-selectable divide ratios of 1, 2, 4, 5, 8, 10, 16, 20, and 25 are available. See Figure 5-1.         These CML outputs must be AC coupled.         During device reset (RESET_N asserted low) these pins are driven differential zero.         During pin based power down (PDTRXA_N and PDTRXB_N asserted low), these pins are floating.         During register based power down, these pins are floating.                                                                                                                                                                                                   |  |  |  |

| PRBSEN                   | B9               | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO0                | <ul> <li>Enable PRBS: When this pin is asserted high, the internal PRBS generator and verifier circuits are enabled on both transmit and receive data paths on high speed and low speed sides of both channels.</li> <li>This signal is logically OR'd with MDIO register bits A.13:12, and B.13:12.</li> <li>PRBS 2<sup>31</sup>-1 is selected by default, and can be changed through MDIO.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PRBS_PASS                | J9               | Output<br>LVCMOS<br>/1.8V<br>VDDO1<br>40Ω Driver     | Receive PRBS Error Free (Pass) Indicator.         When PRBS test is enabled (PRBSEN=1):         PRBS_PASS=1 indicates that PRBS pattern reception is error free.         PRBS_PASS=0 indicates that PRBS error is detected. The channel, high speed or low speed side, and lane (for low speed side) that this signal refers to is chosen through MDIO register bits 0.3:0.         During device reset (RESET_N asserted low) this pin is driven low.         During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is floating.         It is highly recommended that PRBS_PASS be brought to easily accessible point on the application board (header), in the event that debug is required.                                                                                                                                                                   |  |  |  |

www.ti.com

#### SLLSEE9-NOVEMBER 2013

# Table 2-1. Pin Description - Signal Pins (continued)

| TERMINAL   |                             | DIRECTION                                                  | DECODIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------|-----------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SIGNAL     | BGA                         | TYPE<br>SUPPLY                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| PRTAD[4:0] | M8<br>J6<br>L9<br>G9<br>E10 | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO[1:0]                  | MDIO Port Address. Used to select the MDIO port address.<br>The TLK10081 will respond if the port address field on MDIO protocol (PA[4:0]) matches<br>PRTAD[4:0].)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RESET_N    | H5                          | Input<br>LVCMOS<br>1.5V/1.8V<br>VDDO01                     | Low True Device Reset. RESET_N must be held asserted (low logic level) for at least 10µs after device power stabilization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

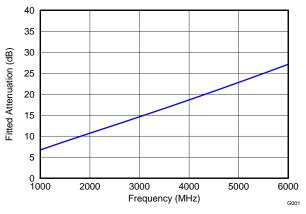

| MDC        | 8L                          | Input<br>LVCMOS<br>with Hysteresis<br>1.5V/1.8V<br>VDDO1   | <b>MDIO Clock Input.</b> Clock input for the Clause 22 MDIO interface.<br>Note that an external pullup is generally not required on MDC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| MDIO       | J7                          | Input/Output<br>LVCMOS<br>1.5V/1.8V<br>VDDO1<br>25Ω Driver | <b>MDIO Data I/O.</b> MDIO interface data input/output signal for the Clause 22 MDIO interface. This signal must be externally pulled up to VDDO using a $2k\Omega$ resistor.<br>During device reset (RESET_N asserted low) this pin is floating. During software initiated power down the management interface remains active for control register writes and reads. Certain status bits are not deterministic as their generating clock source may be disabled as a result of asserting either power down input signal. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is floating. During register based power down (1.15 asserted) |  |  |  |  |  |

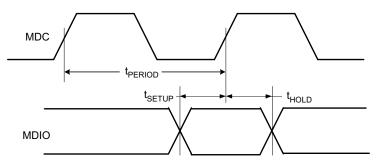

| ты         | C8                          | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pullup)       | high both channels), this pin is driven normally.<br>JTAG Input Data. TDI is used to serially shift test data and test instructions into the device during<br>the operation of the test port. In system applications where JTAG is not implemented, this input<br>signal may be left floating.<br>During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled<br>up. During register based power down, (1.15 asserted high both channels), this pin is pulled up<br>normally.                                                                                                                                                         |  |  |  |  |  |

| TDO        | D6                          | Output LVCMOS<br>1.5V/1.8V VDDO0<br>50Ω Driver             | JTAG Output Data. TDO is used to serially shift test data and test instructions out of the device during the operation of the test port. When the test port is not in use, TDO is in a high impedance state.<br>During device reset (RESET_N asserted low) this pin is floating. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, (1.15 asserted high both channels), this pin is pulled up normally.                                                                                                                                                                                |  |  |  |  |  |

| TMS        | B8                          | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pullup)       | <b>JTAG Mode Select.</b> TMS is used to control the state of the internal test-port controller. In system applications where JTAG is not implemented, this input signal can be left unconnected. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled up. During register based power down, (1.15 aserted high both channels), this pin is pulled up normally.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| тск        | D8                          | Input LVCMOS<br>with Hysteresis<br>1.5V/1.8V VDDO0         | <b>JTAG Clock.</b> TCK is used to clock state information and test data into and out of the device during boundary scan operation. In system applications where JTAG is not implemented, this input signal should be grounded.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TRST_N     | E5                          | Input LVCMOS<br>1.5V/1.8V VDDO0<br>(Internal Pulldown)     | <b>JTAG Test Reset.</b> TRST_N is used to reset the JTAG logic into system operational mode. This input can be left unconnected in the application and is pulled down internally, disabling the JTAG circuitry. If JTAG is implemented on the application board, this signal should be deasserted (high) during JTAG system testing, and otherwise asserted (low) during normal operation mode. During pin based power down (PDTRXA_N and PDTRXB_N asserted low), this pin is not pulled down. During register based power down (1.15 asserted high both channels), this pin is pulled down normally.                                                              |  |  |  |  |  |

| TESTEN     | L10                         | Input LVCMOS<br>1.5V/1.8V VDDO1                            | <b>Test Enable</b> . This signal is used during the device manufacturing process. It should be grounded through a resistor in the device application board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| GPI0       | J10                         | Input LVCMOS<br>1.5V/1.8V VDDO1                            | General Purpose Input Zero. This signal is used during the device manufacturing process. It should be grounded through a resistor on the device application board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| GPI1       | M9                          | Input LVCMOS<br>1.5V/1.8V VDDO1                            | General Purpose Input One. This signal is used during the device manufacturing process. It should be grounded through a resistor on the device application board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| AMUXA      | C11                         | Analog I/O                                                 | SERDES Channel A Analog Testability I/O. This signal is used during the device manufacturing process. It should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| AMUXB      | D4                          | Analog I/O                                                 | <b>SERDES Channel B Analog Testability I/O.</b> This signal is used during the device manufacturing process. It should be left unconnected in the device application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

www.ti.com

| Table 2-2. Pin Description - Powe | r Pins |

|-----------------------------------|--------|

|-----------------------------------|--------|

| TERMINAL              |                                                                                                                                                                                                      | TYPE   | DECODIDITION                                                                                                                                                                                                                       |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIGNAL                | SIGNAL BGA                                                                                                                                                                                           |        | DESCRIPTION                                                                                                                                                                                                                        |  |  |  |  |

| VDDA_LS/HS            | D2, F2, G2, J2, F11, G10                                                                                                                                                                             | Power  | <b>SERDES Analog Power.</b><br>VDDA_LS and VDDA_HS provide supply voltage for the analog circuits on the low-speed and high-speed sides respectively. 1.0V nominal. Can be tied together on the application board.                 |  |  |  |  |

| VDDT_LS/HS            | F4, G4, F9                                                                                                                                                                                           | Power  | <b>SERDES Analog Power.</b><br>VDDT_LS and VDDT_HS provide termination and supply voltage for the analog circuits on the low-speed and high-speed sides respectively. 1.0V nominal. Can be tied together on the application board. |  |  |  |  |

| VDDD                  | E6, E8, F6, H6, H8                                                                                                                                                                                   | Power  | SERDES Digital Power.<br>VDDD provides supply voltage for the digital circuits internal to the SERDES.<br>1.0V nominal.                                                                                                            |  |  |  |  |

| DVDD                  | E7, F7, G6, G8, H7                                                                                                                                                                                   | Power  | <b>Digital Core Power.</b><br>DVDD provides supply voltage to the digital core. 1.0V nominal.                                                                                                                                      |  |  |  |  |

| VDDRA_LS,<br>VDDRB_LS | С3, К3                                                                                                                                                                                               | Power  | <b>SERDES Analog Regulator Power.</b><br>VDDRA_LS and VDDRB_LS provide supply voltage for the internal PLL regulator for the low speed side. 1.5V or 1.8V nominal.                                                                 |  |  |  |  |

| VDDRA_HS              | E11                                                                                                                                                                                                  | Power  | SERDES Analog Regulator Power.<br>VDDRA_HS provides supply voltage for the internal PLL regulator for high<br>speed Channel A. 1.5V or 1.8V nominal.                                                                               |  |  |  |  |

| VDDRB_HS              | J11                                                                                                                                                                                                  | Power  | SERDES Analog Regulator Power<br>VDDRB_HS provides supply voltage for the internal PLL regulator for high<br>speed Channel B. 1.5V or 1.8V nominal.                                                                                |  |  |  |  |

| VDDO[1:0]             | K7, C7                                                                                                                                                                                               | Power  | <b>LVCMOS I/O Power.</b><br>VDDO0 and VDDO1 provide supply voltage for the LVCMOS inputs and outputs. 1.5V or 1.8V nominal. Can be tied together on the application board.                                                         |  |  |  |  |

| VPP                   | D7                                                                                                                                                                                                   | Power  | <b>Factory Program Voltage.</b><br>Used during device manufacturing. The application must connect this power supply directly to DVDD.                                                                                              |  |  |  |  |

| VSS                   | A2, A5, A11, B3, B4, B7,<br>B11, C1, C6, C12, D3,<br>D5, D10, D11, E2, E4, F1,<br>F5, F8, F10, F12, G1, G3,<br>G5, G7, G11, H2, H4,<br>H11, J5, J12, K1, K6,<br>K11, L3, L4, L7, L11, M2,<br>M5, M12 | Ground | <b>Ground.</b><br>Common analog and digital ground.                                                                                                                                                                                |  |  |  |  |

## **3 FUNCTIONAL DESCRIPTION**

The TLK10081 allows for high-speed interleaving/de-interleaving of 1 to 8 serial data streams to aggregate them into a single physical link. The data processing required to support this functionality is detailed in the following subsections.

## 3.1 Transmit (Interleaving) Direction

Two configurations for TLK10081 transmit data path with the device configured to operate in the normal transceiver (mission) mode are shown in Figure 3-1 and Figure 3-2.

In the transmit direction, the lower-rate serial lanes to be interleaved are first received by a deserializer (one per lane) capable of resolving data at up to 5 Gbps. This deserialized data can be optionally aligned to 10-bit word boundaries (based on a user-defined 10-bit alignment character) and optionally 8b/10b decoded. If these functions are not relevant to the data being received, they can be bypassed. The received data on each is input to a FIFO in order to compensate for phase differences between the low speed serial links and the high speed side of the chip. This FIFO is also capable of clock tolerance compensation if needed.

The high speed side can then aggregate the data in one of two ways - (1) word interleaving or (2) bit interleaving. If word interleaving is chosen, the low speed data streams are interleaved in a round-robin fashion 10 bits at a time. If bit interleaving is chosen, the interleaving is performed on a bit-by-bit basis. In either case, provisions need to be taken so that the far-end receiver is able to correctly identify the lane assignments. This is handled by the device's lane ordering logic, described in Section 3.3.

The high-speed aggregate data stream can then be optionally 8b/10b encoded and optionally scrambled by a polynomial scrambling function. These functions provide different ways of ensuring the high speed serial output can be received properly by a device at the other end of the link (by increasing the transition density and by giving a more even distribution of high and low levels). Note that if both the encoding and scrambling functions are used, the user can determine whether to first encode the data and then scramble or to first scramble the data and then encode. If the latter option is chosen, scrambling is not performed on control codes (Kx.x). The resulting data is then output by a serializer capable of data rates up to 10 Gbps.

SLLSEE9-NOVEMBER 2013

www.ti.com

Figure 3-1. Transmit Datapath, 10-Bit Mode

SLLSEE9-NOVEMBER 2013

Figure 3-2. Transmit Datapath, Raw Serial Data (Bit Interleave)

## 3.2 Receive (De-Interleaving) Direction

With the device configured to operate in the normal transceiver (mission) mode, the receive data paths are as shown in Figure 3-2, Receive data path (10-bit mode), and Figure 3-3, Receive data path (raw serial mode).

In the receive direction, the high speed aggregate stream is received by a deserializer capable of data rates up to 10 Gbps. The deserialized data is then aligned to 20-bit boundaries by the device's channel synchronization logic. This alignment can be based on a user-defined 10-bit alignment code (in the case of 8b/10b or otherwise 10-bit delineated data) or can be done arbitrarily (for cases where 10-bit delineation is not meaningful). In either case, the chosen word boundaries can be adjusted manually if necessary to adjust the bit assignments.

Once the data is aligned, it can be optionally 8b/10b decoded or descrambled as needed before being input to the device's receive lane ordering logic (discussed in detail in Section 3.3). After lane assignments are determined, the de-aggregated serial data streams are input to independent FIFOs in order to absorb phase variations between the high-speed and low-speed clock domains and to compensate for clock rate differences if desired.

Each low speed data stream will pass through a programmable skew buffer (in case delays need to be added to certain lanes in order to meet system-level skew requirements) and optionally 8b/10b encoded before being output by a serializer capable of rates up to 1.25 Gbps.

TEXAS INSTRUMENTS www.ti.com

#### SLLSEE9-NOVEMBER 2013

Figure 3-3. Receive Datapath, 10-Bit Mode

Figure 3-4. Receive Datapath, Raw Serial Data

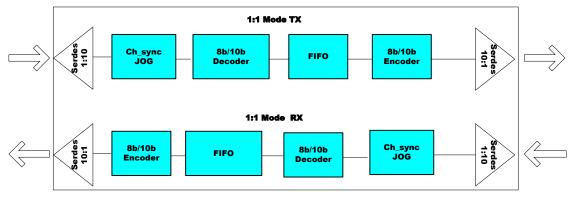

In 1:1 mode, the receive datapath is similar to 8:1 mode, but does not have a skew buffer or a programmable descrambler. Lanes 1-7 are not used.

## 3.3 Lane Ordering

When multiple serial data links are multiplexed into a single physical link, special provisions need to be taken in order for the original lane assignments to be recovered at the far end of the link. The TLK10081 provides several methods to accomplish this.

### 3.3.1 Reserved Lane Marker Characters

If the data to be aggregated can be deserialized into 10-bit words, then it is possible to identify certain reserved codes that can be used to keep track of lane assignments. In the TX direction, the TLK10081 can be configured to identify a programmable "search" character (one that is expected to occur in the data stream) and replace it with another programmable "replace" character (one that is not expected to occur in the data stream). In the RX direction, the device can search for this reserved code in the high speed data it is receiving and use the position of the code in the aggregated data stream to determine the correct lane assignments. This code can then be replaced with another programmable character before being output on the low speed side. This allows for the lane marking process to be transparent to systems interfacing to the TLK10081's low speed side.

### 3.3.2 Training Sequence

If it not possible to define reserved lane marking codes (for example, if the low-speed serial data does not have 10-bit delineation or unused codes), then it is possible to configure the TLK10081 so that lane ordering is determined at link start-up (prior to normal data transmission). This is accomplished via a training sequence sent over the high speed link from the transmitting device to the receiving device. Once the receiver has detected the training sequence and has determined lane ordering (as indicated through MDIO registers), then the transmitter can transition into normal operation.

### 3.3.3 Manual Lane Rotation

If the application allows for lane ordering to be determined at a system level instead, the TLK10081 provides a manual method for cycling through the possible lane order rotations. If manual rotation is used, then the device will iterate through different rotations as controlled by either MDIO registers or the RXCTRL pins.

## 3.3.4 Reserved Lane

If fewer than eight low speed lanes are required by the application, one lane can be used to continuously send lane ordering information. This allows for continual monitoring of lane ordering so that the assignments can be quickly re-established in the event of a link disruption.

NSTRUMENTS

Texas

www.ti.com

Figure 3-5. Block Diagram of the Interleave/De-interleave Scheme

## 3.4 Additional Functionality

## 3.4.1 1:1 Mode

The TLK10081 also supports a 1:1 mode for data retiming. The data path for this mode is shown below. In the transmit direction, data is received by the low-speed deserializer on Lane 0 of the selected channel, aligned to word boundaries (if applicable), 8b/10b decoded (if applicable), input to a phase-correction FIFO capable of clock tolerance compensation, optionally 8b/10b encoded, and transmitted out the high speed serial ports. The receive direction operates similarly, but in the opposite direction (eventually outputting the serial data on low speed Lane 0).

Note that it is possible to operate one direction (transmit or receive) of a particular channel in 1:1 mode while the other direction operates in 8:1 mode.

### 3.4.2 Clock Tolerance Compensation

The phase-correction FIFOs used to interface between the low speed and high speed clock domains within the device are also capable of clock tolerance compensation (CTC). If enabled, the CTC function will correct for clock rate mismatches by periodically inserting or deleting a user-defined reserved "idle" character. Note that character insertion only occurs immediately following detection of an existing "idle" character, so these should occur regularly in the data stream to ensure that compensation can be performed frequently enough to avoid FIFO collisions.

### 3.4.3 Crosspoint Switch

The TLK10081's default lane ordering passes through low speed input lanes (0 through 7) into fixed positions in the outputted high speed aggregate link. The high speed receiver will then identify which positions correspond to which lanes and output them accordingly on its low speed outputs. However, it is possible to reconfigure the data sources that are associated with each output lane/position through MDIO. For each HS transmit output, the source can be selected from the low speed input of the same channel or from either channel's high speed input. For the LS transmit output, data can be sourced from the low speed input or either channel's high speed input.Since the data source (input) assigned to each output is configured independently, a broadcast/fan-out function can be supported.

## 3.4.4 Unused Lanes

Some lanes may not be used all the time. When they are disconnected, data stuffing must occur to fill in the void left by the missing input data. In TLK10081, the data pattern sent to represent lane down should not alias with actual data; therefore, a repeated fill data sequence is used. The active/not active status of all lanes can be monitored through MDIO.

To implement the lane down function on the RX side, eight separate state machines will monitor the high speed data for the fill sequence and indicate the status of each lane through the low speed status register 0x13.

## 3.4.5 Test Pattern Generationa and Verification

The TLK10081 has an extensive suite of built in test functions to support system diagnostic requirements. Each channel has sets of internal test pattern generators and verifiers.

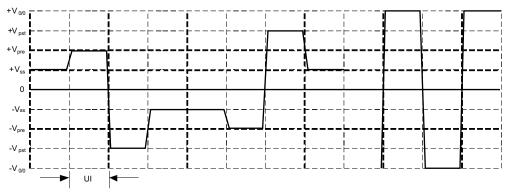

Several patterns can be selected via the MDIO interface that offer extensive test coverage. The low speed side supports generation and verification of pseudo-random bit sequence (PRBS) 2<sup>7</sup>-1, 2<sup>23</sup>-1, and 2<sup>31</sup>-1 patterns. In addition to those PRBS patterns, the high speed side supports High-frequency (HF), Low-frequency (LF), Mixed-frequency (MF), and continuous random test pattern (CRPAT) long/short pattern generation and verification as defined in IEEE Standard 802.3.

The TLK10081 provides two pins: PRBSEN and PRBS\_PASS, for additional and easy control and monitoring of PRBS pattern generation and verification. When the PRBSEN is asserted high, the internal PRBS generator and verifier circuits are enabled on both transmit and receive data paths on high speed and low speed sides of both channels. This signal is logically OR'd with an MDIO register bits A.13:12 and B.13:12.

PRBS 2<sup>31</sup>-1 is selected by default, and can be changed through MDIO.

When PRBS test is enabled (PRBSEN=1):

PRBS\_PASS=1 indicates that PRBS pattern reception is error free.

PRBS\_PASS=0 indicates that a PRBS error is detected. The channel, the side (high speed or low speed), and the lane (for low speed side) that this signal refers to is chosen through MDIO register bit 0.3:0.

## 3.4.6 Power Down Mode

The TLK10081 can be put in power down either through device inputs pins or through MDIO control register (1.15). PDTRXA\_N: Active low, powers down the channel.

The MDIO management serial interface remains operational when in register based power down mode (1.15 asserted for both channels), but status bits may not be valid since the clocks are disabled. The low speed side and high speed side SERDES outputs are high impedance when in power down mode. Please see the detailed per pin description for the behavior of each device I/O signal during pin based and register based power down.

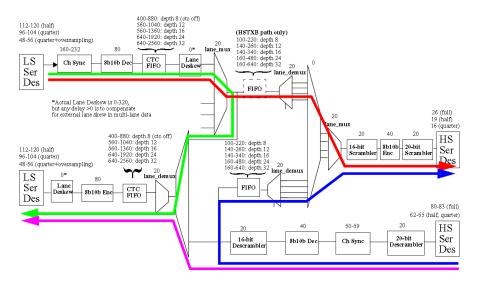

## 3.4.7 Transmit / Receive Latency

The latency through the TLK10081 is shown in Figure 3-7. Note that the latency ranges shown indicate static rather than dynamic latency variance, i.e., the range of possible latencies when the serial link is initially established. During normal operation, the latency through the device is fixed.

Latency: HS Full Rate, LS Half Rate, 8-Lanes, 8-deep FIFO LS In -> HS Out: 918-1478 (Typical 1198) UI (add 100-220 for HSTXB path) LS In -> LS Out: 1384-2432 (Typical 1908) UI HS In -> LS Out: 822-1322 (Typical 1072) UI HS In -> HS Out: 436-568 (Typical 502) UI

## **4 SERDES INTERFACES**

## 4.1 High Speed CML Output

The high speed data output driver is implemented using Current Mode Logic (CML) with integrated pull up resistors, requiring no external components. The transmit outputs must be AC coupled.

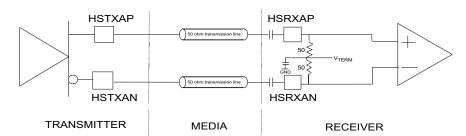

Figure 4-1. Example of High Speed I/O AC Coupled Mode (Channel A HS side is shown)

Current Mode Logic (CML) drivers often require external components. The disadvantage of the external component is a limited edge rate due to package and line parasitic. The CML driver on TLK10081 has onchip  $50\Omega$  termination resistors terminated to VDDT, providing optimum performance for increased speed requirements. The transmitter output driver is highly configurable allowing output amplitude and deemphasis to be tuned to a channel's individual requirements. Software programmability allows for very flexible output amplitude control. Only AC coupled output mode is supported.

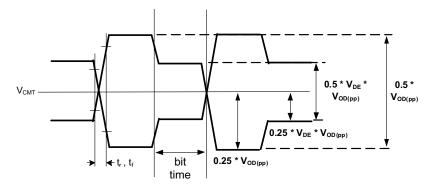

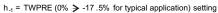

When transmitting data across long lengths of PCB trace or cable, the high frequency content of the signal is attenuated due to the skin effect of the media. This causes a "smearing" of the data eye when viewed on an oscilloscope. The net result is reduced timing margins for the receiver and clock recovery circuits. In order to provide equalization for the high frequency loss, 4-tap finite impulse response (FIR) transmit deemphasis is implemented. A highly configurable output driver maximizes flexibility in the end system by allowing de-emphasis and output amplitude to be tuned to a channel's individual requirements. Output swing control is via MDIO.

See Figure 7-2 for output waveform flexibility. The level of de-emphasis is programmable via the MDIO interface through control registers (5.7:4 and 5.12:8) through pre-cursor and post-cursor settings. Users can control the strength of the de-emphasis to optimize for a specific system requirement.

## 4.2 High Speed Receiver

The high speed receiver is differential CML with internal termination resistors. The receiver requires AC coupling. The termination impedances of the receivers are configured as 100 Ohms with the center tap weakly tied to 0.8\*VDDT with a capacitor to create an AC ground.

TLK10081 serial receivers incorporate adaptive equalizers. This circuit compensates for channel insertion loss by amplifying the high frequency components of the signal, reducing inter-symbol interference. Equalization can be enabled or disabled per register settings. Both the gain and bandwidth of the equalizer are controlled by the receiver equalization logic.

## 4.3 Loss of Signal Output Generation (LOS)

Loss of input signal detection is based on the voltage level of each serial input signal INA\*P/N, HSRXAP/N, and HSRXBP/N. Anytime the serial receive input differential signal peak to peak voltage level is  $\leq$ 75 mV<sub>pp</sub> for High Speed side or  $\leq$  65mV<sub>pp</sub> for Low Speed side, LOSA or LOSB are asserted (high true) respectively for Channel A and Channel B (if enabled, disabled by default). Note that an input signal  $\geq$  150 mV<sub>pp</sub> for High Speed side and  $\geq$  175 mV<sub>pp</sub> for Low Speed side is required for reliable operation of the loss of signal detection circuits. If the input signal is between these two ranges, the SERDES will operate properly, but the LOS indication will not be valid (or robust). The LOS indications are also directly readable through the MDIO interface in respective registers.

The following additional critical status conditions can be combined with the loss of signal condition enabling additional real-time status signal visibility on the LOSA and LOSB outputs per channel:

- Loss of Channel Synchronization Status Logically OR'd with LOS condition(s) when enabled. Loss of channel synchronization can be optionally logically OR'd (disabled by default) with the internally generated LOS condition (per channel).

- Loss of PLL Lock Status on LS and HS sides Logically OR'd with LOS condition(s) when enabled. The internal PLL loss of lock status bit is optionally OR'd (disabled by default) with the other internally generated loss of signal conditions (per channel).

- 3. Receive 8B/10B Decode Error (Invalid Code Word or Running Disparity Error) Logically OR'd with LOS condition(s) when enabled. The occurrence of an 8B/10B decode error (invalid code word or disparity error) is optionally OR'd (disabled by default) with the other internally generated loss of signal conditions (per channel).

- 4. AGCLOCK (Active Gain Control Currently Locked) Inverted and Logically OR'd with LOS condition(s) when enabled. HS RX SERDES adaptive gain control unlocked indication is optionally OR'd (disabled by default) with the other internally generated loss of signal conditions (per channel).

- 5. AZDONE (Auto Zero Calibration Done) Inverted and Logically OR'd with LOS conditions(s) when enabled. HS RX SERDES auto-zero not done indication is optionally OR'd (disabled by default) with the other internally generated loss of signal conditions (per channel).

## 5 CLOCKING

## 5.1 Configuring PLL and Line Rates

The TLK10081 includes internal low-jitter high quality oscillators that are used as frequency multipliers for the low speed and high speed SERDES and other internal circuits of the device. Specific MDIO registers are available for SERDES rate and PLL multiplier selection to match line rates and reference clock (REFCLK0/1) frequencies for various applications. Some examples are detailed below on how to select and configure.

The external differential reference clock has a large operating frequency range allowing support for many different applications. The reference clock frequency must be within  $\pm$  200 PPM of the incoming serial data rate ( $\pm$  100 PPM of nominal data rate).

|                     | LOW SPEI                 | ed side |                    | HIGH SPEED SIDE                     |                          |         |                    |  |  |

|---------------------|--------------------------|---------|--------------------|-------------------------------------|--------------------------|---------|--------------------|--|--|

| LINE RATE<br>(Mbps) | SERDES PLL<br>MULTIPLIER | RATE    | REFCLKP/N<br>(MHz) | LINE RATE<br>(Mbps <sup>(1)</sup> ) | SERDES PLL<br>MULTIPLIER | RATE    | REFCLKP/N<br>(MHz) |  |  |

| 1000-1250           | 10                       | Half    | 100-125            | 1000-1250                           | 20                       | Quarter | 100-125            |  |  |

| 1000-1250           | 8                        | Half    | 125-156.25         | 1000-1250                           | 16                       | Quarter | 125-156.25         |  |  |

| 1000-1250           | 8                        | Quarter | 250-312.5          | 1000-1250                           | 8                        | Quarter | 250-312.5          |  |  |

### Table 5-1. Line Rate and Reference Clock Selection for the 1:1 Mode

(1) High Speed Side SERDES runs at 2x effective data rate.

For other line rates in 8:1 mode, valid reference clock frequencies can be selected with the help of the information provided in Table 5-2 and Table 5-3 for the low speed side and high speed side SERDES. The reference clock frequency has to be the same for the two SERDES and must be within the specified valid ranges for different PLL multipliers.

| SERDES PLL       | REFERENCE | E CLOCK (MHz) | HALF R | ATE (Gbps)         | QUARTER RATE (Gbps) |        |  |

|------------------|-----------|---------------|--------|--------------------|---------------------|--------|--|

| MULTIPLIER (MPY) | MIN       | MAX           | MIN    | MAX <sup>(1)</sup> | MIN                 | MAX    |  |

| 4                | 250       | 425           | 1      | 1.25               | 0.5                 | 0.85   |  |

| 5                | 200       | 425           | 1      | 1.25               | 0.5                 | 1.0625 |  |

| 6                | 166.667   | 416.667       | 1      | 1.25               | 0.5                 | 1.25   |  |

| 8                | 125       | 312.5         | 1      | 1.25               | 0.5                 | 1.25   |  |

| 10               | 122.88    | 250           | 1.2288 | 1.25               | 0.6144              | 1.25   |  |

## Table 5-2. Line Rate and Reference Clock Frequency Ranges for the Low Speed Side SERDES

(1) Reference Clock is lower than Max Reference Clock RateScale: Half Rate = 1, Quarter Rate = 2

## Table 5-3. Line Rate and Reference Clock Frequency Ranges for the High Speed Side SERDES

| SERDES PLL       | REFERENCE CLOCK (MHz) |         | FULL RATE (Gbps) |     | HALF RATE (Gbps) |      | QUARTER RATE (Gbps) |       |

|------------------|-----------------------|---------|------------------|-----|------------------|------|---------------------|-------|

| MULTIPLIER (MPY) | MIN                   | MAX     | MIN              | MAX | MIN              | MAX  | MIN                 | MAX   |

| 4                | 375                   | 425     | 6                | 6.8 |                  |      |                     |       |

| 5                | 300                   | 425     | 6                | 8.5 | 4 <sup>(1)</sup> | 4.25 | 2 <sup>(1)</sup>    | 2.125 |

| 6                | 250                   | 416.667 | 6                | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 8                | 187.5                 | 312.5   | 6                | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 10               | 150                   | 250     | 6                | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 12               | 125                   | 208.333 | 6                | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 15               | 122.88                | 166.667 | 7.3728           | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 16               | 122.88                | 156.25  | 7.864            | 10  | 4 <sup>(1)</sup> | 5    | 2 <sup>(1)</sup>    | 2.5   |

| 20               | 122.88                | 125     | 9.8304           | 10  | 4.9152           | 5    | 2.4576              | 2.5   |

Reference Clock is higher than Min Reference Clock RateScale: Full Rate = 0.25, Half Rate = 0.5, Quarter Rate = 1

## 5.1.1 Refclk Frequency Selection Example

If the low speed side line rate is 0.6Gbps, the high-speed side line rate will be 4.8Gbps. The following steps can be taken to make a reference clock frequency selection:

- Determine the appropriate SERDES rate modes that support the required line rates. Table 5-2 shows that the 0.6Gbps line rate on the low speed side is only supported in the quarter rate mode (RateScale = 2). Table 5-3 shows that the 4.8Gbps line rate on the high speed side is only supported in the half rate mode (RateScale = 0.5).

- 2. For each SERDES side, and for all available PLL multipliers (MPY), compute the corresponding reference clock frequencies using the formula:

Reference Clock Frequency = (LineRate x RateScale)/MPY

The computed reference clock frequencies are shown in Table 5-4 along with the valid minimum and maximum frequency values.

- 3. Mark all the common frequencies that appear on both SERDES sides. Note and discard all those that fall outside the allowed range. In this example, the common frequencies are highlighted in Table 5-4.

- 4. Select any of the remaining marked common reference clock frequencies. The higher the reference clock frequency usually the better. In this example, any of the following reference clock frequencies can be selected: 150MHz, 200MHz, 240MHz, and 300MHz.

Note that for Low Speed side rates of at least 500Mbps, a general rule to follow is that half rate on the Low Speed side will correspond to full rate on the High Speed side, and quarter rate on the Low Speed side will correspond to half rate on the High Speed side. And, the high speed PLL multiplier will be 2x of low speed.

|            | LOW SPEED S | DE SERDES  |             | HIGH SPEED SIDE SERDES |           |           |              |  |

|------------|-------------|------------|-------------|------------------------|-----------|-----------|--------------|--|

| SERDES PLL | REFERENCE   | CLOCK FREQ | UENCY (MHz) | SERDES PLL             | REFERENCE | CLOCK FRE | QUENCY (MHz) |  |

| MULTIPLIER | COMPUTED    | MIN        | MAX         | MULTIPLIER             | COMPUTED  | MIN       | MAX          |  |