SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

## 3A Processor Supply with I<sup>2</sup>C Compatible Interface and Remote Sense

Check for Samples: TPS62360, TPS62361B, TPS62362, TPS62363

## **FEATURES**

- 3A Peak Output Current

- **Highest Efficiency:**

- Low R<sub>DS.on</sub> Switch and Active Rectifier

- Power Save Mode for Light Loads

- I<sup>2</sup>C High Speed Compatible Interface

- **Programmable Output Voltage for Digital** Voltage Scaling

- TPS62360/62: 0.77V to 1.4V, 10mV Steps

- TPS62361B/63: 0.5V to 1.77V, 10mV Steps

- **Excellent DC/AC Output Voltage Regulation**

- Differential Load Sensing

- Precise DC Output Voltage Accuracy

- DCS-Control<sup>™</sup> Architecture for Fast and Precise Transient Regulation

- **Multiple Robust Operation/Protection** Features:

- Soft Start

- Programmable Slew Rate at Voltage Transition

- Over Temperature Protection

- Input Under Voltage Detection and Lockout

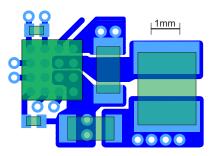

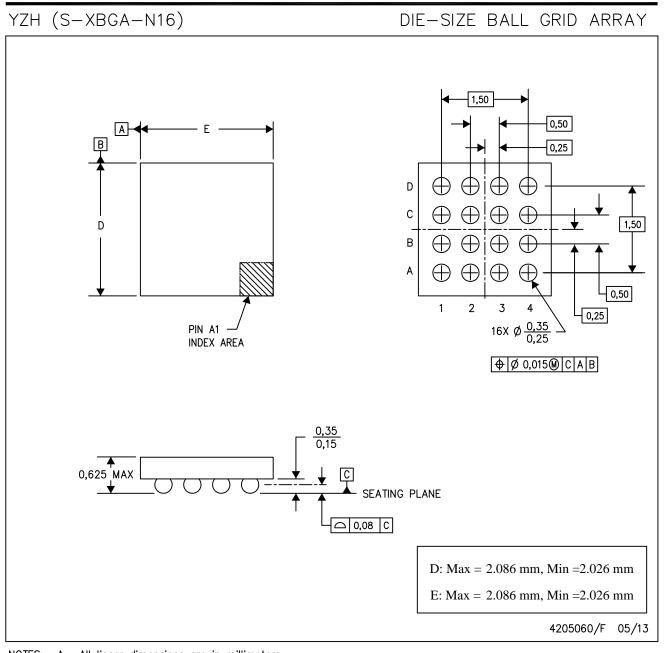

- Available in 16-Bump, 2mm x 2mm NanoFree™ Package

- Low External Device Count: < 25mm<sup>2</sup> Solution Size

## APPLICATIONS

- **Dynamic Voltage Scale Compliant Processors** and DSPs, Memory

- SmartReflex<sup>™</sup> Compliant Power Supply

- **Cell Phones, Smart Phones, Feature Phones**

- Tablets, Netbooks, Clamshells

## DESCRIPTION

The TPS6236x are a family of high-frequency synchronous step down dc-dc converter optimized for battery-powered portable applications for a small solution size. With an input voltage range of 2.5V to 5.5V, common battery technologies are supported. The device provides up to 3A peak load current, operating at 2.5MHz typical switching frequency.

The devices convert to an output voltage range of 0.77V to 1.4V (TPS62360/62) and 0.5V to 1.77V (TPS62361B/63), programmable via I<sup>2</sup>C interface in 10mV steps. Dedicated inputs allow fast voltage transition to address processor performance operating points.

The TPS6236x supports low-voltage DSPs and processor cores in smart-phones and handheld computers including latest submicron processes. Dedicated hardware input pins allow simple transitions to performance operating points and retention modes of processors.

The devices focus on a high output voltage accuracy. The differential sensing and the DCS-Control™ architecture achieve precise static and dynamic, transient output voltage regulation.

The TPS6236x devices offer high efficiency step down conversion. The area of highest efficiency is extended towards low output currents to increase the efficiency while the processor is operating in retention mode, as well as towards highest output currents increasing the battery on-time.

The robust architecture and multiple safety features allow perfect system integration.

The 2mm x 2mm package and the low number of required external components lead to a tiny solution size of less than 25mm<sup>2</sup>.

Ā

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DCS-Control, NanoFree, SmartReflex are trademarks of Texas Instruments.

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

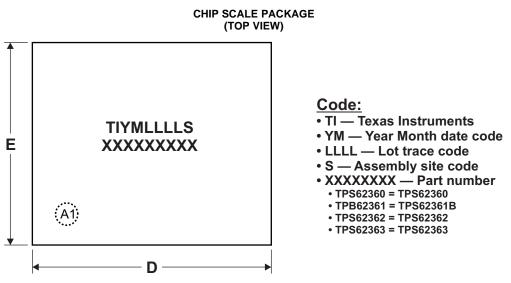

| ORDERING INFORMATION     |                                |         |                                              |                            |  |  |

|--------------------------|--------------------------------|---------|----------------------------------------------|----------------------------|--|--|

| PART NUMBER              | PACKAGE MARKING                | PACKAGE | DEVICE SPECIFIC FEATURES <sup>(1)</sup>      |                            |  |  |

|                          |                                |         | Output Voltage Range                         | Output Voltage Presets     |  |  |

| TPS62360 <sup>(2)</sup>  | See PACKAGE<br>SUMMARY Section | CSP-16  | V <sub>OUT</sub> = 0.77V to 1.4V, 10mV Steps | 1.40V, 1.00V, 1.40V, 1.10V |  |  |

| TPS62361B <sup>(2)</sup> | See PACKAGE<br>SUMMARY Section | CSP-16  | V <sub>OUT</sub> = 0.5V to 1.77V, 10mV Steps | 0.96V, 1.40V, 1.16V, 1.16V |  |  |

| TPS62362 <sup>(2)</sup>  | See PACKAGE<br>SUMMARY Section | CSP-16  | V <sub>OUT</sub> = 0.77V to 1.4V, 10mV Steps | 1.23V, 1.00V, 1.20V, 1.10V |  |  |

| TPS62363 <sup>(2)</sup>  | See PACKAGE<br>SUMMARY Section | CSP-16  | V <sub>OUT</sub> = 0.5V to 1.77V, 10mV Steps | 1.20V, 1.36V, 1.50V, 1.00V |  |  |

####

Contact the factory to check availability of other output voltage or feature versions. (1)

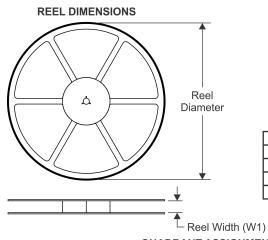

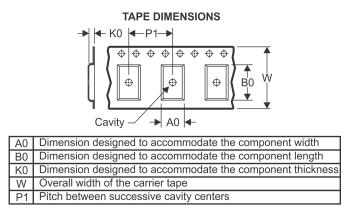

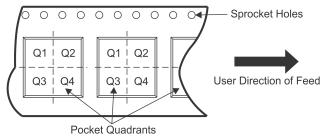

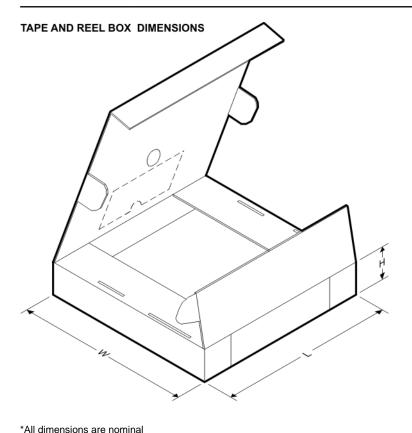

(2)The YZH package is available in tape and reel. Add R suffix (e.g. TPS62360YZHR) to order quantities of 3000 parts per reel, T suffix for 250 parts per reel (e.g. TPS62360YZHT). For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder on ti.com.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                        |                                       | VA   | VALUE                     |    |  |

|--------------------------------------------------------|---------------------------------------|------|---------------------------|----|--|

|                                                        |                                       | MIN  |                           |    |  |

|                                                        | VIN, AVIN, SW pin                     | -0.3 | 7                         | V  |  |

|                                                        | EN, VSEL0, VSEL1, SENSE+              | -0.3 | (V <sub>AVIN</sub> +0.3V) | V  |  |

| Voltage range <sup>(2)</sup>                           | SENSE-                                | -0.3 | 0.3                       | V  |  |

|                                                        | SCL, SDA                              | -0.3 | (V <sub>DD</sub> +0.3V)   | V  |  |

|                                                        | VDD                                   | -0.3 | 3.6                       | V  |  |

| Continuous RMS VIN / SW current per Pin <sup>(3)</sup> |                                       |      | 1275                      | mA |  |

|                                                        | Operating junction temperature, $T_J$ | -40  | 150                       | °C |  |

| Temperature range                                      | Storage temperature, T <sub>stg</sub> | -65  | 150                       | °C |  |

|                                                        | Machine model                         |      | 200                       | V  |  |

| ESD rating <sup>(4)</sup>                              | Charge device model                   |      | 500                       | V  |  |

|                                                        | Human body model                      |      | 2                         | kV |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to network ground terminal.

In order to be consistent with the TI reliability requirement for the silicon chips (100K Power-On-Hours at 105°C junction temperature), (3) the current should not continuously exceed 1275mA in the VIN pin and 2550mA in the SW pins so as to prevent electromigration failure in the solder. See THERMAL AND DEVICE LIFE TIME INFORMATION.

(4) The human body model is a 100-pF capacitor discharged through a 1.5-kΩ resistor into each pin. The machine model is a 200-pF capacitor discharged directly into each pin.

## THERMAL INFORMATION

|                         |                                                             | TPS6236x |       |

|-------------------------|-------------------------------------------------------------|----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | YZH      | UNITS |

|                         |                                                             | 16 PINS  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 94.8     |       |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 25       |       |

| θ <sub>JB</sub>         | Junction-to-board thermal resistance <sup>(4)</sup>         | 60       | 80 AM |

| Ψυτ                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 3.2      | °C/W  |

| Ψ <sub>JB</sub>         | Junction-to-board characterization parameter <sup>(6)</sup> | 57       |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | n/a      |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## **RECOMMENDED OPERATING CONDITIONS**

|                      |                                              |                                                        | MIN | TYP | MAX | UNIT  |

|----------------------|----------------------------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| V <sub>IN</sub>      | Input voltage range, V <sub>IN</sub>         | I <sub>OUT</sub> ≤ 2.5A                                | 2.5 | 5   | 5.5 | V     |

|                      |                                              | I <sub>OUT</sub> > 2.5A                                | 3   | 3   | 5.5 | V     |

| I <sub>OUT,avg</sub> | Continuous output current <sup>(1)</sup>     |                                                        |     |     | 2.5 | А     |

| t <sub>rf</sub>      | Rising and falling signal transition time at | Rising and falling signal transition time at EN, VSELx |     |     |     | mV/µs |

| T <sub>A</sub>       | Operating ambient temperature <sup>(2)</sup> |                                                        | -40 | )   | 85  | °C    |

| TJ                   | Operating junction temperature               |                                                        |     | )   | 125 | °C    |

(1) The TPS6236x device is designed to provide 3A according to typical application processor load profiles. Drawing more than 2.5A permanently might impact the device life time. See THERMAL AND DEVICE LIFE TIME INFORMATION for details.

(2) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature [T<sub>A(max</sub>)] is dependent on the maximum operating junction temperature [T<sub>J(max</sub>)], the maximum power dissipation of the device in the application [P<sub>D(max</sub>]], and the junction-to-ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A(max</sub>) = T<sub>J(max</sub>) – (θ<sub>JA</sub> × P<sub>D(max</sub>))

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted the specification applies for VIN = 3.6V over an operating ambient temp.  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are for  $T_A = 25^{\circ}C$ .

|                       | PARAMETER                                           | TEST C                    | CONDITIONS            | MIN  | TYP  | MAX | UNIT |

|-----------------------|-----------------------------------------------------|---------------------------|-----------------------|------|------|-----|------|

| INPUT                 |                                                     |                           |                       |      |      | ·   |      |

| V <sub>IN</sub>       | Input voltage range at VIN, AVIN                    |                           |                       | 2.5  |      | 5.5 | V    |

| V <sub>DD</sub>       | I <sup>2</sup> C and registers supply voltage range |                           |                       | 1.15 |      | 3.6 | V    |

| I <sub>SD(AVIN)</sub> | Shutdown current into AVIN                          | $EN = LOW, V_{DD} = 0V$   |                       |      | 0.65 | 5   | μA   |

| •                     |                                                     | EN = LOW,                 | $T_A = 25^{\circ}C$   |      | 0.5  | 1   | μA   |

| ISD(VIN)              | Shutdown current into VIN                           | $V_{DD} = 0V$             | T <sub>A</sub> = 85°C |      | 1    | 3   | μΑ   |

| I <sub>SD(VDD)</sub>  | Shutdown current into VDD                           | $EN = LOW, I^2C$ bus idle |                       |      | 0.01 |     | μA   |

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

STRUMENTS

ÈXAS

## **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise noted the specification applies for VIN = 3.6V over an operating ambient temp.  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are for  $T_A = 25^{\circ}C$ .

|                       | PARAMETER                                                    | TEST CO                                                                                              | NDITIONS                                                                | MIN                                       | TYP   | MAX                                       | UNIT |

|-----------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|-------|-------------------------------------------|------|

|                       |                                                              |                                                                                                      | PFM mode                                                                |                                           | 56    |                                           | μA   |

| l <sub>Q</sub>        | Operating quiescent current into (AVIN<br>+ VIN)             | EN = HIGH,<br>I <sub>OUT</sub> = 0mA,<br>not switching                                               | Forced PWM<br>mode<br>(Test Mode)                                       |                                           | 180   |                                           | μA   |

| Maria a               | Linder veltage lock out at AV/IN                             | Input voltage fall                                                                                   | ng, EN = High                                                           |                                           | 2.3   | 2.45                                      | V    |

| V <sub>UVLO</sub>     | Under voltage lock out at AVIN                               | Input voltage risi                                                                                   | ng, EN = Low                                                            |                                           | 1.3   |                                           | V    |

| VUVLO, HYST (AVIN)    | Under voltage lock out hysteresis at AVIN                    | Input voltage risi                                                                                   | ng                                                                      |                                           | 110   |                                           | mV   |

| V <sub>DD,UVLO</sub>  | Under voltage lock out at VDD                                | Input voltage fall                                                                                   | ng                                                                      | 0.7                                       | 0.92  | 1.1                                       | V    |

| VUVLO,HYST(VDD)       | Under voltage lock out hysteresis at VDD                     | Input voltage risi                                                                                   | ng                                                                      |                                           | 50    |                                           | mV   |

| h                     | Input current at VDD                                         | I <sup>2</sup> C not active                                                                          |                                                                         |                                           | 0     |                                           | μA   |

| I <sub>VDD</sub>      | Input current at VDD                                         | I <sup>2</sup> C active (r/w)                                                                        |                                                                         |                                           | 0.02  | 1                                         | mA   |

| LOGIC INTERFA         | ACE                                                          | -                                                                                                    |                                                                         |                                           |       |                                           |      |

| V <sub>IH</sub>       | High-level input voltage at EN, VSEL0, VSEL1                 |                                                                                                      |                                                                         | 1.2                                       |       |                                           | V    |

| VIL                   | Low-level input voltage at EN, VSEL0, VSEL1                  |                                                                                                      |                                                                         |                                           |       | 0.4                                       | V    |

| V <sub>IH,I2C</sub>   | High-level input voltage at SCL, SDA                         |                                                                                                      |                                                                         | $0.7 \mathrm{x} \mathrm{V}_{\mathrm{DD}}$ |       |                                           | V    |

| V <sub>IL,I2C</sub>   | Low-level input voltage at SCL, SDA                          |                                                                                                      |                                                                         |                                           |       | $0.3 \mathrm{x} \mathrm{V}_{\mathrm{DD}}$ | V    |

| I <sub>LKG</sub>      | Logic input leakage current at EN,<br>VSEL0, VSEL1, SDA, SCL | Internal pulldowr<br>disabled                                                                        | resistors                                                               |                                           | 0.05  |                                           | μA   |

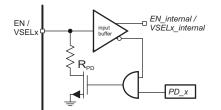

| R <sub>PD</sub>       | Pull down resistance at EN, VSEL0,<br>VSEL1                  | Internal pulldowr<br>enabled                                                                         | resistors                                                               |                                           | 300   |                                           | kΩ   |

|                       | I <sup>2</sup> C clock frequency                             | Fast mode                                                                                            |                                                                         |                                           |       | 400                                       | kHz  |

|                       |                                                              | High speed mod                                                                                       | Э                                                                       |                                           |       | 3.4                                       | MHz  |

| POWER SWITCH          | H                                                            |                                                                                                      |                                                                         |                                           |       |                                           |      |

| Brach                 | High side MOSFET switch                                      | V <sub>IN</sub> = 3.6V                                                                               |                                                                         | 25                                        | 44    | 75                                        | mΩ   |

| R <sub>DS(on)</sub>   | Low side MOSFET switch                                       | $V_{IN} = 3.6V$                                                                                      |                                                                         | 25                                        | 32    | 50                                        | mΩ   |

|                       | High side MOSFET forward current limit                       | $V_{IN} = 3.6V$                                                                                      |                                                                         | 3.0                                       | 3.6   | 4.3                                       | Α    |

| I <sub>LIMF</sub>     | Low side MOSFET forward current limit                        | V <sub>IN</sub> = 3.6V                                                                               |                                                                         | 2.6                                       | 3     | 3.8                                       | Α    |

|                       | Low side MOSFET negative current limit                       | V <sub>IN</sub> = 3.6V, PWM mode                                                                     |                                                                         | 2.2                                       | 2.5   | 2.9                                       | А    |

| f <sub>SW</sub>       | Nominal switching frequency                                  | PWM mode                                                                                             |                                                                         |                                           | 2.5   |                                           | MHz  |

| T <sub>JEW</sub>      | Die temperature early warning                                |                                                                                                      |                                                                         |                                           | 120   |                                           | °C   |

| T <sub>JSD</sub>      | Thermal shutdown                                             |                                                                                                      |                                                                         |                                           | 150   |                                           | °C   |

| T <sub>JSD,HYST</sub> | Thermal shutdown hysteresis                                  |                                                                                                      |                                                                         |                                           | 20    |                                           | °C   |

| t <sub>ON,min</sub>   | Minimum on time                                              |                                                                                                      |                                                                         |                                           | 120   |                                           | ns   |

| OUTPUT                |                                                              | 1                                                                                                    | · · · · · · · · · · · · · · · · · · ·                                   |                                           |       |                                           |      |

| V <sub>OUT</sub>      | Output voltage range                                         | 10mV<br>increments                                                                                   | TPS62360/62<br>TPS62361B/63                                             | 0.77                                      |       | 1.4<br>1.77                               | V    |

|                       | Output voltage accuracy                                      | TPS62360/62:<br>V <sub>IN</sub> = 2.5V<br>5.5V<br>V <sub>OUT</sub> = 0.77V<br>1.4V                   | No load, Forced PWM, $V_{OUT} = [0.77V, 1.3V]$<br>T <sub>J</sub> = 85°C | -0.5%                                     |       | +0.5%                                     |      |

|                       | Calput voltage accuracy                                      | $\begin{array}{l} TPS62361B/63: \\ V_{IN} = 2.7V \ \\ 5.5V \\ V_{OUT} = 0.5V \ \\ 1.77V \end{array}$ | No load, Forced PWM,<br>$T_J = -40$<br>150°C                            | -1%                                       | ±0.5% | +1%                                       |      |

4

Copyright © 2011–2012, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise noted the specification applies for VIN = 3.6V over an operating ambient temp.  $-40^{\circ}C \le T_A \le 85^{\circ}C$ ; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are for  $T_A = 25^{\circ}C$ .

|                    | PARAMETER                                  | TEST CONDITIONS                                                                                  | MIN TYP | MAX | UNIT  |

|--------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------|---------|-----|-------|

|                    | Line regulation                            | I <sub>OUT</sub> = 1A, forced PWM                                                                | < 0.1   |     | %/V   |

|                    | Load regulation                            | V <sub>OUT</sub> = 1.2V, forced PWM                                                              | < 0.05  |     | %/A   |

| t <sub>Start</sub> | Start-up time                              | Time from active EN to $V_{OUT} = 1.4V$ , $C_{OUT} < 100\mu$ F, RMP[2:0] = 000, $I_{OUT} = 0$ mA |         | 1   | ms    |

| R <sub>Sense</sub> | Input resistance between Sense+,<br>Sense– |                                                                                                  | 2.2     |     | MΩ    |

|                    |                                            | RMP[2:0] = 000                                                                                   | 32      |     |       |

|                    |                                            | RMP[2:0] = 001                                                                                   | 16      |     |       |

|                    |                                            | RMP[2:0] = 010                                                                                   | 8       |     |       |

|                    |                                            | RMP[2:0] = 011                                                                                   | 4       |     |       |

| Ramp timer         | Ramp timer                                 | RMP[2:0] = 100                                                                                   | 2       |     | mV/µs |

|                    |                                            | RMP[2:0] = 101                                                                                   | 1       |     |       |

|                    |                                            | RMP[2:0] = 110                                                                                   | 0.5     |     |       |

|                    |                                            | RMP[2:0] = 111                                                                                   | 0.25    |     |       |

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

www.ti.com

## I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS<sup>(1)(2)</sup>

|                                    | PARAMETER                                       | TEST CONDITIONS                                               | MIN                     | MAX  | UNIT |

|------------------------------------|-------------------------------------------------|---------------------------------------------------------------|-------------------------|------|------|

|                                    |                                                 | Standard mode                                                 |                         | 100  | kHz  |

|                                    |                                                 | Fast mode                                                     |                         | 400  | kHz  |

|                                    |                                                 | High-speed mode (write operation), $C_B - 100 \text{ pF}$ max |                         | 3.4  | MHz  |

| f <sub>(SCL)</sub>                 | SCL clock frequency                             | High-speed mode (read operation), $C_B - 100 \text{ pF}$ max  |                         | 3.4  | MHz  |

|                                    |                                                 | High-speed mode (write operation), $C_B - 400 \text{ pF}$ max |                         | 1.7  | MHz  |

|                                    |                                                 | High-speed mode (read operation), $C_B - 400 \text{ pF}$ max  |                         | 1.7  | MHz  |

|                                    | Bus free time between a STOP and                | Standard mode                                                 | 4.7                     |      | μs   |

| t <sub>BUF</sub>                   | START condition                                 | Fast mode                                                     | 1.3                     |      | μs   |

|                                    |                                                 | Standard mode                                                 | 4                       |      | μs   |

| t <sub>HD</sub> , t <sub>STA</sub> | Hold time (repeated) START condition            | Fast mode                                                     | 600                     |      | ns   |

|                                    |                                                 | High-speed mode                                               | 160                     |      | ns   |

|                                    |                                                 | Standard mode                                                 | 4.7                     |      | μs   |

|                                    |                                                 | Fast mode                                                     | 1.3                     |      | μs   |

| t <sub>LOW</sub>                   | Low period of the SCL clock                     | High-speed mode, C <sub>B</sub> – 100 pF max                  | 160                     |      | ns   |

|                                    |                                                 | High-speed mode, C <sub>B</sub> – 400 pF max                  | 320                     |      | ns   |

|                                    |                                                 | Standard mode                                                 | 4                       |      | μs   |

|                                    | IGH High period of the SCL clock                | Fast mode                                                     | 600                     |      | ns   |

| t <sub>HIGH</sub>                  |                                                 | High-speed mode, C <sub>B</sub> – 100 pF max                  | 60                      |      | ns   |

|                                    |                                                 | High-speed mode, C <sub>B</sub> – 400 pF max                  | 120                     |      | ns   |

|                                    |                                                 | Standard mode                                                 | 4.7                     |      | μs   |

| t <sub>SU</sub> , t <sub>STA</sub> | Setup time for a repeated START condition       | Fast mode                                                     | 600                     |      | ns   |

|                                    |                                                 | High-speed mode                                               | 160                     |      | ns   |

|                                    |                                                 | Standard mode                                                 | 250                     |      | ns   |

| t <sub>SU</sub> , t <sub>DAT</sub> | Data setup time                                 | Fast mode                                                     | 100                     |      | ns   |

|                                    |                                                 | High-speed mode                                               | 10                      |      | ns   |

|                                    |                                                 | Standard mode                                                 | 0                       | 3.45 | μs   |

|                                    |                                                 | Fast mode                                                     | 0                       | 0.9  | μs   |

| t <sub>HD</sub> , t <sub>DAT</sub> | Data hold time                                  | High-speed mode, C <sub>B</sub> – 100 pF max                  | 0                       | 70   | ns   |

|                                    |                                                 | High-speed mode, C <sub>B</sub> – 400 pF max                  | 0                       | 150  | ns   |

|                                    |                                                 | Standard mode                                                 | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

|                                    |                                                 | Fast mode                                                     | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RCL</sub>                   | Rise time of SCL signal                         | High-speed mode, C <sub>B</sub> – 100 pF max                  | 10                      | 40   | ns   |

|                                    |                                                 | High-speed mode, C <sub>B</sub> – 400 pF max                  | 20                      | 80   | ns   |

|                                    |                                                 | Standard mode                                                 | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

|                                    | Rise time of SCL signal after a repeated        | Fast mode                                                     | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RCL1</sub>                  | START condition and after an<br>acknowledge bit | High-speed mode, C <sub>B</sub> – 100 pF max                  | 10                      | 80   | ns   |

|                                    |                                                 | High-speed mode, $C_B - 400 \text{ pF max}$                   | 20                      | 160  | ns   |

|                                    |                                                 | Standard mode                                                 | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

|                                    |                                                 | Fast mode                                                     | $20 + 0.1 C_B$          | 300  | ns   |

| t <sub>FCL</sub>                   | Fall time of SCL signal                         | High-speed mode, C <sub>B</sub> – 100 pF max                  | 10                      | 40   | ns   |

|                                    |                                                 | g. spood mode, og i too pi max                                | 10                      | 40   | 10   |

(1) S/M = standard mode; F/M = fast mode

(2) Specified by design. Not tested in production.

Copyright © 2011–2012, Texas Instruments Incorporated

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

www.ti.com

## I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS<sup>(1)(2)</sup> (continued)

|                                    | PARAMETER                       | TEST CONDITIONS                              | MIN                     | MAX  | UNIT |

|------------------------------------|---------------------------------|----------------------------------------------|-------------------------|------|------|

|                                    |                                 | Standard mode                                | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

|                                    | Disc time of CDA signal         | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RDA</sub>                   | Rise time of SDA signal         | High-speed mode, $C_B - 100 \text{ pF}$ max  | 10                      | 80   | ns   |

|                                    |                                 | High-speed mode, $C_B - 400 \text{ pF}$ max  | 20                      | 160  | ns   |

|                                    | Fall time of SDA signal         | Standard mode                                | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

|                                    |                                 | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>FDA</sub>                   |                                 | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 80   | ns   |

|                                    |                                 | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 160  | ns   |

|                                    |                                 | Standard mode                                | 4                       |      | μs   |

| t <sub>SU</sub> , t <sub>STO</sub> | Setup time for STOP condition   | Fast mode                                    | 600                     |      | ns   |

|                                    |                                 | High-speed mode                              | 160                     |      | ns   |

| CB                                 | Capacitive load for SDA and SCL |                                              |                         | 400  | pF   |

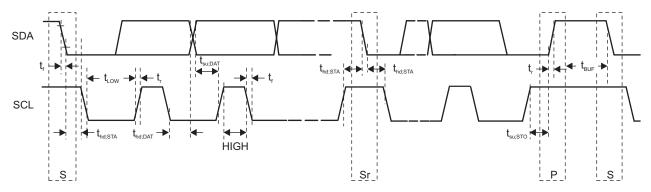

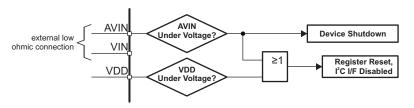

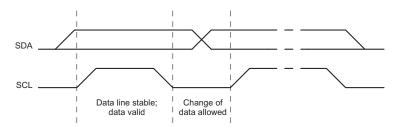

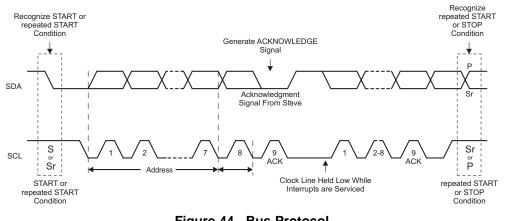

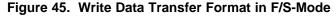

## I<sup>2</sup>C TIMING DIAGRAMS

Figure 1. Serial Interface Timing for F/S Mode

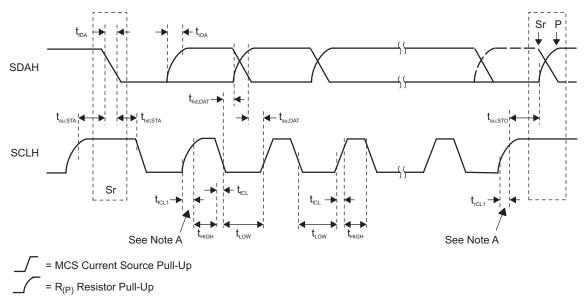

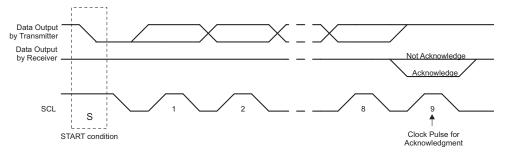

Note A: First rising edge of the SCLH signal after Sr and after each acknowledge bit.

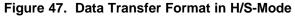

## Figure 2. Serial Interface Timing for H/S Mode

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

www.ti.com

## **DEVICE INFORMATION**

## **PIN ASSIGNMENTS**

| (           | TOP         | VIEW        | )          |

|-------------|-------------|-------------|------------|

| AVIN        | AGND<br>A2  | VSEL1<br>A3 | VIN<br>A4: |

| SENSE+      | EN<br>B2    | sw<br>B3    | sw<br>B4   |

| SENSE-      | VSEL0<br>C2 | PGND<br>C3  | PGND<br>C4 |

| VDD<br>(D1) | SDA<br>D2   | SCL<br>D3   | PGND<br>D4 |

|             |             |             |            |

| (BOTTOM VIEW) |                                            |                                                                                    |  |  |  |

|---------------|--------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| A3            | A2                                         | A1                                                                                 |  |  |  |

| <b>B</b> 3    | B2                                         | <b>B1</b>                                                                          |  |  |  |

| <u>C</u> 3    | ©2                                         | C1                                                                                 |  |  |  |

| D3            | D2                                         | D1                                                                                 |  |  |  |

|               | <ul><li>A3</li><li>B3</li><li>C3</li></ul> | <ul> <li>A3</li> <li>A2</li> <li>B3</li> <li>B2</li> <li>C3</li> <li>C2</li> </ul> |  |  |  |

## PIN FUNCTIONS

| PIN    |     | 1/0 | DESCRIPTION                                                                                                                                                                                                             |

|--------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 10  | DESCRIPTION                                                                                                                                                                                                             |

| AVIN   | A1  | Ι   | Analog Supply Voltage Input.                                                                                                                                                                                            |

| AGND   | A2  | -   | Analog Ground Connection.                                                                                                                                                                                               |

| EN     | B2  | Ι   | Device Enable Logic Input. Logic HIGH enables the device, logic LOW disables the device and turns it into shutdown. The pin must be terminated to either HIGH or LOW if the internal pull down resistor is deactivated. |

| VDD    | D1  | Ι   | I <sup>2</sup> C Logic and Registers supply voltage. For resetting the internal registers, this connection must be pulled below its UVLO level.                                                                         |

| SCL    | D3  | I/O | I <sup>2</sup> C clock signal.                                                                                                                                                                                          |

| SDA    | D2  | I/O | I <sup>2</sup> C data signal.                                                                                                                                                                                           |

| VSEL0  | C2  | Ι   | Output Settings Selection Logic Inputs. Predefined register settings can be chosen for setting output voltage and                                                                                                       |

| VSEL1  | A3  | Ι   | mode. The pins must be terminated to logic HIGH or LOW if the internal pull down resistors are deactivated.                                                                                                             |

| sw     | B3  | -   | Inductor connection                                                                                                                                                                                                     |

| 500    | B4  |     | Inductor connection                                                                                                                                                                                                     |

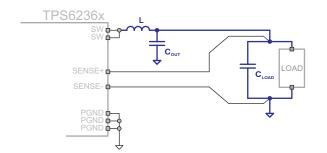

| SENSE+ | B1  | Ι   | Positive Output Voltage Remote Sense. Must be connected closest to the load supply node.                                                                                                                                |

| SENSE- | C1  | Ι   | Negative Output Voltage Remote Sense. Must be connected closest to the load ground node.                                                                                                                                |

| VIN    | A4  | Ι   | Power Supply Voltage Input.                                                                                                                                                                                             |

|        | C3  | -   |                                                                                                                                                                                                                         |

| PGND   | C4  |     | Power Ground Connection.                                                                                                                                                                                                |

|        | D4  |     |                                                                                                                                                                                                                         |

8

#### Copyright © 2011–2012, Texas Instruments Incorporated

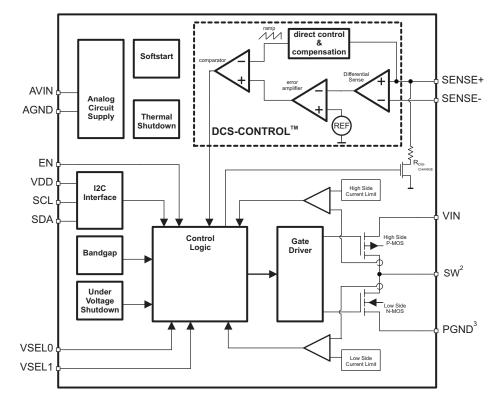

## FUNCTIONAL BLOCK DIAGRAM

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

www.ti.com

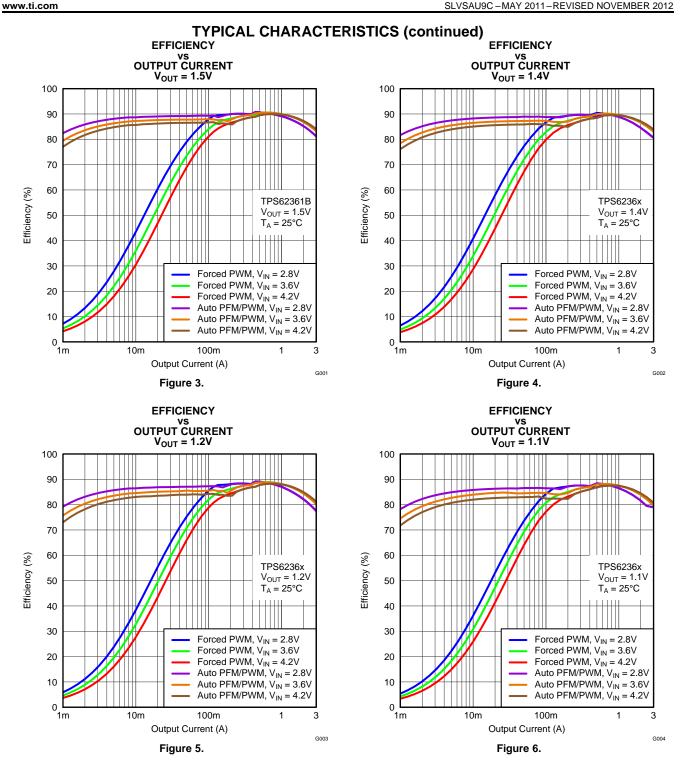

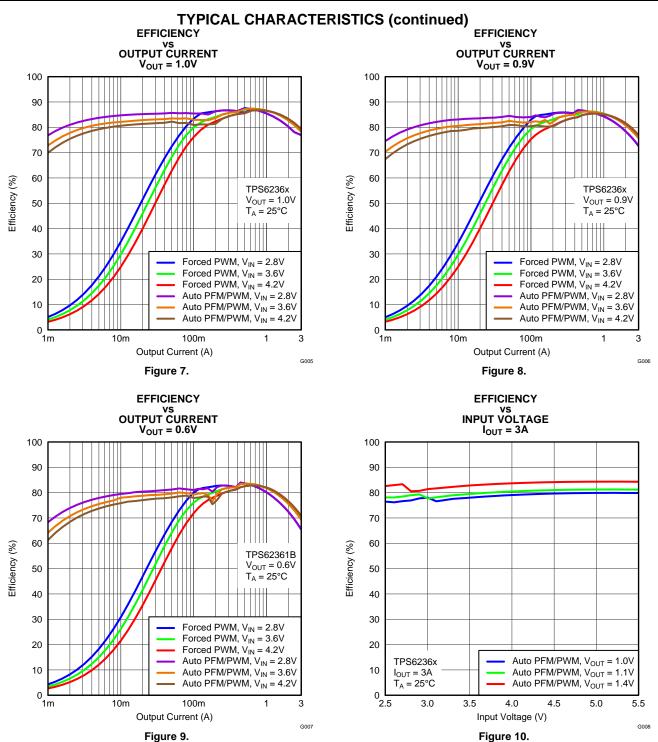

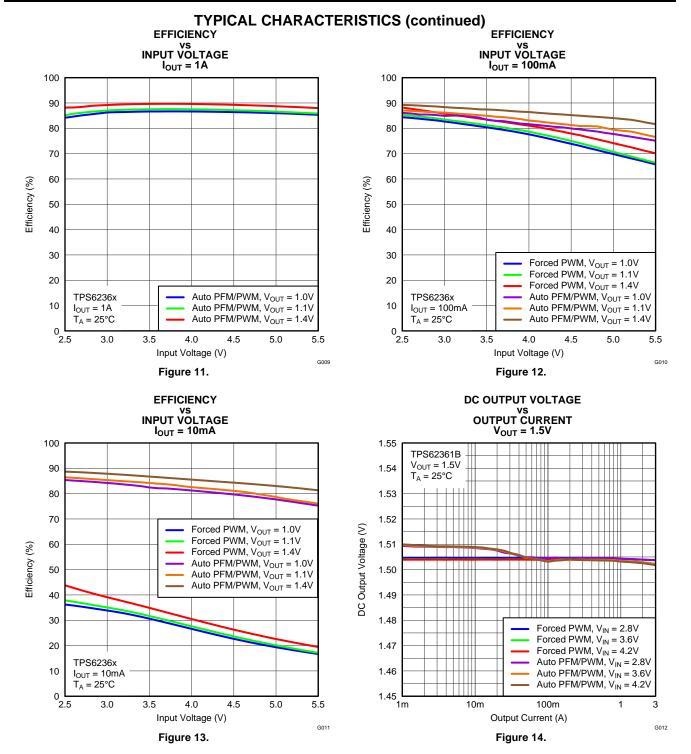

## **TYPICAL CHARACTERISTICS**

## Table of Graphs

|                    |                                  |                                                        |                                                           | FIGURE    |

|--------------------|----------------------------------|--------------------------------------------------------|-----------------------------------------------------------|-----------|

|                    |                                  |                                                        | V <sub>OUT</sub> = 1.5V                                   | Figure 3  |

|                    |                                  |                                                        | $V_{OUT} = 1.4V$                                          | Figure 4  |

|                    |                                  |                                                        | V <sub>OUT</sub> = 1.2V                                   | Figure 5  |

|                    |                                  | vs. Output Current (Power Save and Forced<br>PWM Mode) | V <sub>OUT</sub> = 1.1V                                   | Figure 6  |

|                    |                                  |                                                        | V <sub>OUT</sub> = 1.0V                                   | Figure 7  |

|                    | Efficiency                       |                                                        | V <sub>OUT</sub> = 0.9V                                   | Figure 8  |

|                    | -                                |                                                        | $V_{OUT} = 0.6V$                                          | Figure 9  |

|                    |                                  |                                                        | I <sub>OUT</sub> = 3000mA                                 | Figure 10 |

|                    |                                  | vs. Input Voltage (Power Save and Forced PWM           | I <sub>OUT</sub> = 1000mA                                 | Figure 11 |

|                    |                                  | Mode)                                                  | I <sub>OUT</sub> = 100mA                                  | Figure 12 |

|                    |                                  |                                                        | I <sub>OUT</sub> = 10mA                                   | Figure 13 |

|                    |                                  |                                                        | V <sub>OUT</sub> = 1.5V, T <sub>A</sub> = 25°C            | Figure 14 |

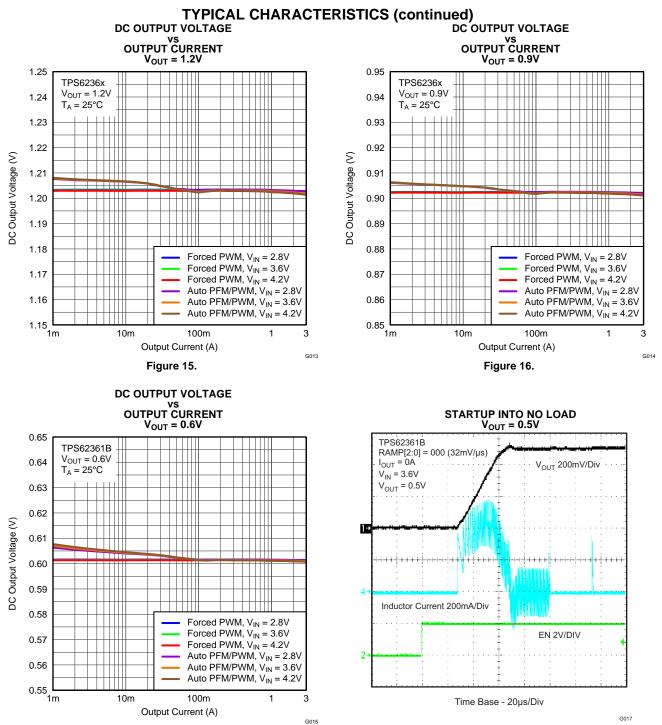

|                    |                                  | vs. Output Current (Power Save and Forced              | V <sub>OUT</sub> = 1.2V, T <sub>A</sub> = 25°C            | Figure 15 |

| o                  | DC Output Voltage                | PWM Mode)                                              | V <sub>OUT</sub> = 0.9V, T <sub>A</sub> = 25°C            | Figure 16 |

|                    |                                  |                                                        | V <sub>OUT</sub> = 0.6V, T <sub>A</sub> = 25°C            | Figure 17 |

| ;                  |                                  |                                                        | V <sub>OUT</sub> = 0.5V, I <sub>OUT</sub> = 0mA           | Figure 18 |

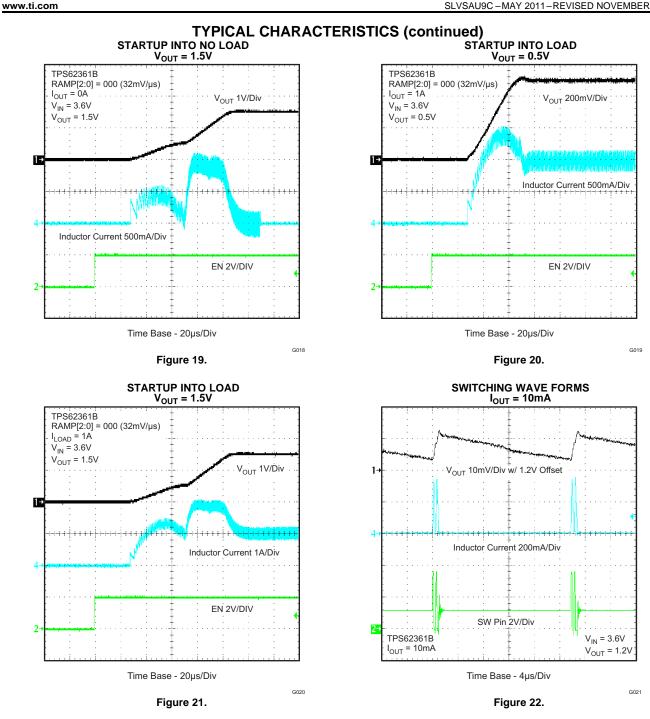

|                    | <b>2</b>                         | Into No Load                                           | V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 0mA           | Figure 19 |

|                    | Startup                          | late Lood                                              | V <sub>OUT</sub> = 0.5V, I <sub>OUT</sub> = 1000mA        | Figure 20 |

|                    |                                  | Into Load                                              | V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 1000mA        | Figure 21 |

|                    |                                  |                                                        | I <sub>OUT</sub> = 10mA                                   | Figure 22 |

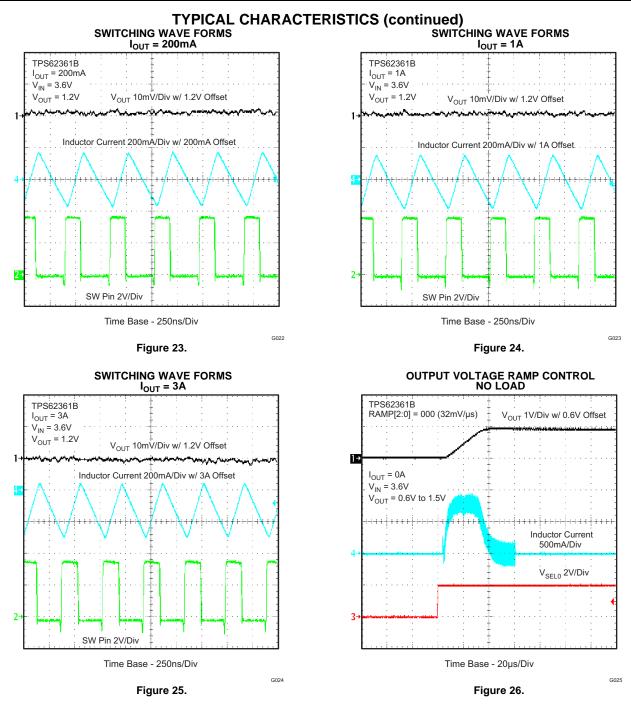

|                    |                                  |                                                        | I <sub>OUT</sub> = 200mA                                  | Figure 23 |

|                    | Switching Wave forms             |                                                        | I <sub>OUT</sub> = 1000mA                                 | Figure 24 |

|                    |                                  |                                                        | I <sub>OUT</sub> = 3000mA                                 | Figure 25 |

|                    |                                  |                                                        | I <sub>OUT</sub> = 0mA                                    | Figure 26 |

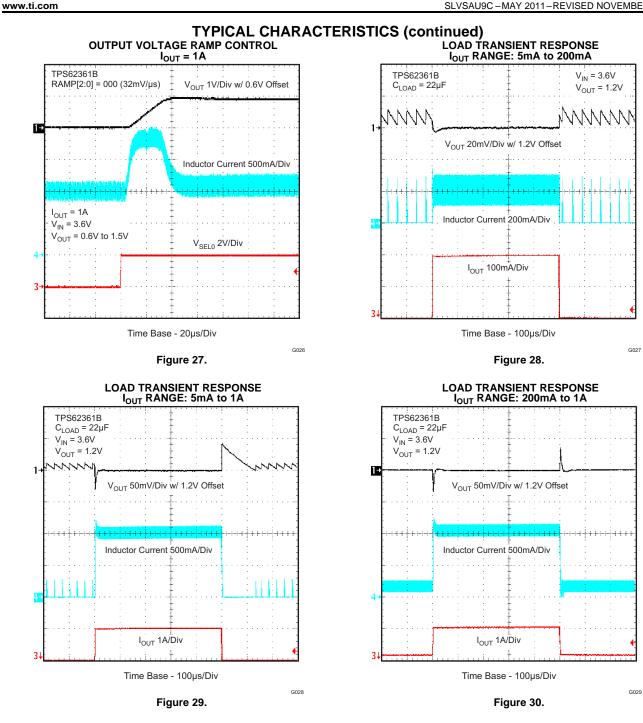

|                    | Output Voltage Ramp Control      | Transition 0.6V 1.5V                                   | I <sub>OUT</sub> = 1000mA                                 | Figure 27 |

|                    |                                  |                                                        | $I_{OUT} = 5$ mA to 200mA                                 | Figure 28 |

|                    |                                  |                                                        | $I_{OUT} = 5$ mA to 1000mA                                | Figure 29 |

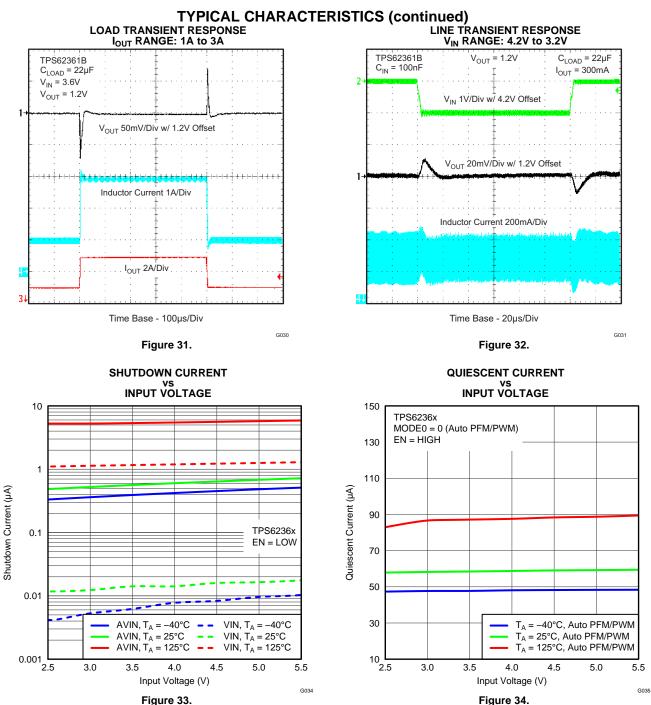

|                    | Load Transient Response          |                                                        | $I_{OUT} = 200$ mA to<br>1000mA                           | Figure 30 |

|                    |                                  |                                                        | I <sub>OUT</sub> = 1000mA to<br>3000mA                    | Figure 31 |

|                    | Line Transient Response          |                                                        | V <sub>IN</sub> = 3.2 to 4.2V                             | Figure 32 |

| D(VIN),<br>D(AVIN) | Shutdown Current at AVIN and VIN | vs. Input Voltage                                      | T <sub>A</sub> = [-40°C, 25°C,<br>125°C]                  | Figure 33 |

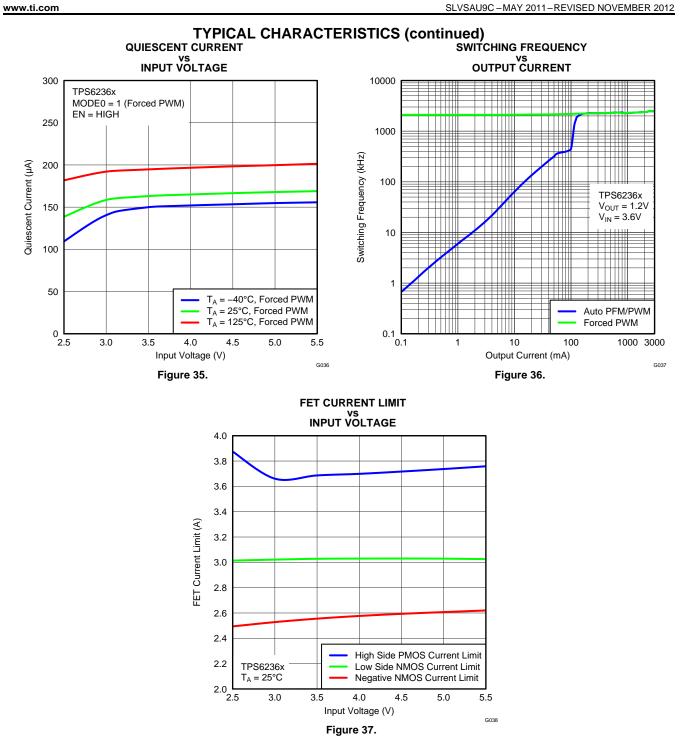

| I <sub>Q</sub>     |                                  |                                                        | T <sub>A</sub> = [-40°C, 25°C,<br>125°C],<br>auto PFM/PWM | Figure 34 |

|                    | Quiescent Current                | vs. Input Voltage                                      | T <sub>A</sub> = [-40°C, 25°C,<br>125°C]<br>forced PWM    | Figure 35 |

| SW                 | Switching Frequency              | vs. Output Current                                     | $V_{OUT} = 1.2V$                                          | Figure 36 |

| -IM                | Current Limit                    | vs. Input Voltage                                      |                                                           | Figure 37 |

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

www.ti.com

## TPS62360, TPS62361B TPS62362, TPS62363

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

Figure 18.

Figure 17.

www.ti.com

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

www.ti.com

Copyright © 2011–2012, Texas Instruments Incorporated

Product Folder Links: TPS62360 TPS62361B TPS62362 TPS62363

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

Figure 34.

www.ti.com

SLVSAU9C - MAY 2011 - REVISED NOVEMBER 2012

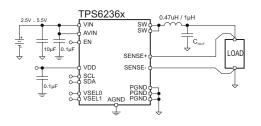

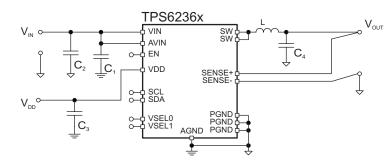

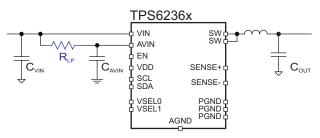

## PARAMETER MEASUREMENT INFORMATION

## Table 1. List of Components

| REFERENCE                       | DESCRIPTION                                                                           | MANUFACTURER                 |

|---------------------------------|---------------------------------------------------------------------------------------|------------------------------|

| TPS6236x                        | 3A Processor Supply with I <sup>2</sup> C<br>Compatible Interface and Remote<br>Sense | Texas Instruments            |

| L                               | 1 µH, 4 mm x 4 mm x 2.1 mm                                                            | Coilcraft (XFL4020-102ME1.0) |

| C <sub>2</sub> , C <sub>4</sub> | 10 µF, Ceramic, 6.3V, X5R                                                             | Murata (GRM188R60J106ME84D)  |

| C <sub>1</sub> , C <sub>3</sub> | 0.1 µF, Ceramic, 10V, X5R                                                             | Standard                     |

#### DETAILED DESCRIPTION

The TPS6236x are a family of high-frequency synchronous step down dc-dc converter optimized for batterypowered portable applications. With an input voltage range of 2.5V to 5.5V, common battery technologies are supported.

The device provides up to 3A peak load current, operating at 2.5MHz typical switching frequency.

The devices convert to an output voltage range of 0.77V to 1.4V (TPS62360 / TPS62362) and 0.5V to 1.77V (TPS62361B / TPS62363), programmable via I<sup>2</sup>C interface in 10mV steps.

The TPS6236x supports low-voltage DSPs and processor cores in smart-phones and handheld computers, including latest submicron processes and their retention modes and addresses digital voltage scaling technologies such as SmartReflex<sup>™</sup>.

Output Voltages and Modes can be fully programmed via I<sup>2</sup>C. To address different performance operating points and/or startup conditions, the device offers four output voltage / mode presets which can be chosen via dedicated hardware input pins allowing simple and zero latency output voltage transition.

The devices focus on a high output voltage accuracy. The fully differential sensing and the DCS-Control<sup>™</sup> architecture achieve precise static and dynamic, transient output voltage regulation. This accounts for stable processor operation. Output voltage security margins can be kept small, resulting in an increased overall system efficiency.

The TPS6236x devices offer high efficiency step down conversion. The area of highest efficiency is extended towards low output currents to increase the efficiency while the processor is operating in retention mode, as well as towards highest output currents reducing the power loss. This addresses the power profile of processors. High efficiency conversion is required for low output currents to support the retention modes of processors, resulting in an increased battery on-time. To address the processor maximum performance operating points with highest output currents, high efficiency conversion is enabled as well to save the battery on-time and reduce input power.

The robust architecture and multiple safety features allow perfect system integration.

The 2mm x 2mm package and the low number of required external components lead to a tiny solution size of approximately less than 25 mm<sup>2</sup>.

## OPERATION

The TPS6236x synchronous switched mode power converters are based on DCS-Control<sup>™</sup>, an advanced regulation topology, that combines the advantages of hysteretic, voltage mode and current mode control architectures.

While a comparator stage provides excellent load transient response, an additional voltage loop ensures high DC accuracy as well. The TPS6236x compensates ground shifts at the load by the differentially sensing the output voltage at the point of load.

The internal ramp generator adds information about the load current and fast output voltage changes. The internally compensated regulation network achieves fast and stable operation with low ESR capacitors.

The DCS-Control<sup>™</sup> topology supports PWM (Pulse Width Modulation) mode for medium and heavy load conditions and a Power Save Mode at light loads. During PWM it operates at its nominal switching frequency in continuous conduction mode. This frequency is typically about 2.5MHz with a controlled frequency variation depending on the input voltage. As the load current decreases, the converter enters Power Save Mode to sustain high efficiency down to light loads. The transition from PWM to Power Save Mode is seamless and avoids output voltage transients.

An internal current limit supports nominal output currents of up to 3A. The TPS6236x family offers both excellent DC voltage and superior load transient regulation, combined with very low output voltage ripple, minimizing interference with RF circuits.

## ENABLING AND DISABLING THE DEVICE

The device is enabled by setting the EN input to a logic high. Accordingly, a logic low disables the device. If the device is enabled, the internal power stage will start switching and regulate the output voltage to the programmed threshold. The EN input must be terminated unless the internal pull down resistor is activated.

Copyright © 2011–2012, Texas Instruments Incorporated

The  $I^2C$  interface is operable when VDD and AVIN are present, regardless of the state of the EN pin.

If the device is disabled by pulling the EN to a logic low, the output capacitor can actively be discharged. Per default, this feature is disabled. Programming the EN\_DISC bit to a logic high will discharge the output capacitor via a typ.  $300\Omega$  path on the SENSE+ pin.

## SOFT START

The device incorporates an internal soft start circuitry that controls the ramp up of the output voltage after enabling the device. This circuitry eliminates inrush current to avoid excessive voltage drops of primary cells and rechargeable batteries with high internal impedance.

During soft start, the output voltage is monotonically ramped up to the minimum programmable output voltage. After reaching this threshold, the output voltage is further increased following the slope as programmed in the ramp rate settings (see RAMP RATE CONTROLLING) until reaching the programmed output voltage. Once the nominal voltage is reached, regular operation as described above will continue.

The device is able to start into a pre biased output capacitor as well.

## **PROGRAMMING THE OUTPUT**

The TPS6236x devices offer four similar registers to program the output. Two dedicated hardware input pins, VSEL0 and VSEL1, are implemented for choosing the active register. The logic state of VSEL0 and VSEL1 select the register whose settings are present at the output. The VSEL0 and VSEL1 pins must be terminated unless the internal pull-down resistors are activated.

The registers have a certain initial default value (see Table 2) and can be readjusted via I<sup>2</sup>C during operation.

This allows a simple transition between several output options by triggering the dedicated input pins. At the same time since the presets can be readjusted during operation, this offers highest flexibility.

| INPUT     | INPUT PINS |        | DEFAULT OPERATION MODE                                |                                            | DEFAULT OUTPUT VOLTAGE [V] |           |          |          |  |

|-----------|------------|--------|-------------------------------------------------------|--------------------------------------------|----------------------------|-----------|----------|----------|--|

| VSEL<br>1 | VSEL<br>0  | PRESET | I <sup>2</sup> C REGISTER                             | TPS62360, TPS62361B,<br>TPS62362, TPS62363 | TPS62360                   | TPS62361B | TPS62362 | TPS62363 |  |

| 0         | 0          | SET0   | 0x00h – see Table 13, Table 14,<br>Table 15, Table 16 | Power Save Mode                            | 1.40                       | 0.96      | 1.23     | 1.20     |  |

| 0         | 1          | SET1   | 0x01h – see Table 17, Table 18,<br>Table 19, Table 20 | Power Save Mode                            | 1.00                       | 1.40      | 1.00     | 1.36     |  |

| 1         | 0          | SET2   | 0x02h – see Table 21, Table 22,<br>Table 23, Table 24 | Power Save Mode                            | 1.40                       | 1.16      | 1.20     | 1.50     |  |

| 1         | 1          | SET3   | 0x03h – see Table 25, Table 26,<br>Table 27, Table 28 | Power Save Mode                            | 1.10                       | 1.16      | 1.10     | 1.00     |  |

#### **Table 2. Output Presets**

Via the I<sup>2</sup>C interface and/or the four preset options, the following output parameters can be changed:

- Output voltage from 0.77V to 1.4V (TPS62360/62) and 0.5V to 1.77V (TPS62361B/63) with 10mV granularity

- · Mode of operation: Power Save Mode or forced PWM mode

The slope for transition between different output voltages (Ramp Rate) can be changed via I<sup>2</sup>C as well. The slope applies for all presets globally. See RAMP RATE CONTROLLING for further details.

Since the output parameters can be changed by dedicated pins for selecting presets and by I<sup>2</sup>C, the following use scenarios are feasible:

- Control the device via dedicated pins only, after programming the presets, to choose and change within the programmed settings

- Program via I<sup>2</sup>C only. The dedicated input pins have fixed connections. Changes are conducted by changing the preset values of the active register.

- Dedicated input pins and I<sup>2</sup>C mixed operation. The non active presets might be changed. The dedicated input

pins are used for the transition to the new output condition. Changes within an active preset via I<sup>2</sup>C are

feasible as well.

## DYNAMIC VOLTAGE SCALING

The output voltage can be adjusted dynamically. Each of the four output registers can be programmed individually by setting OV[5:0] (TPS62360/62) and OV[6:0] (TPS62361B/63) respectively in the SET0, SET1, SET2 and SET3 registers.

| Table 3. TPS62360, TPS62362 Output Volta | age Settings |

|------------------------------------------|--------------|

| for Registers SET0, SET1, SET2 and       | ŠET3         |

| REGISTERS: SET0, SET1, SET2, SET3 |                |  |  |  |  |

|-----------------------------------|----------------|--|--|--|--|

| OV[D5:D0]                         | OUTPUT VOLTAGE |  |  |  |  |

| 00 0000                           | 770 mV         |  |  |  |  |

| 00 0001                           | 780 mV         |  |  |  |  |

| 00 0010                           | 790 mV         |  |  |  |  |

| 00 0011                           | 800 mV         |  |  |  |  |

|                                   |                |  |  |  |  |

| 11 1101                           | 1380 mV        |  |  |  |  |

| 11 1110                           | 1390 mV        |  |  |  |  |

| 11 1111                           | 1400 mV        |  |  |  |  |

#### Table 4. TPS62361B, TPS62363 Output Voltage Settings for Registers SET0, SET1, SET2 and SET3

| REGISTERS: SET0, SET1, SET2, SET3 |                |  |  |  |  |

|-----------------------------------|----------------|--|--|--|--|

| OV[D6:D0]                         | OUTPUT VOLTAGE |  |  |  |  |

| 000 0000                          | 500 mV         |  |  |  |  |

| 000 0001                          | 510 mV         |  |  |  |  |

| 000 0010                          | 520 mV         |  |  |  |  |

| 000 0011                          | 530 mV         |  |  |  |  |

|                                   |                |  |  |  |  |

| 111 1101                          | 1750 mV        |  |  |  |  |

| 111 1110                          | 1760 mV        |  |  |  |  |

| 111 1111                          | 1770 mV        |  |  |  |  |

If the output voltage is changed at the active register (selected by VSEL0 and VSEL1), these changes will apply after the I<sup>2</sup>C command is sent.

## POWER SAVE MODE AND FORCED PWM MODE

The TPS6236x devices feature a Power Save Mode to gain efficiency at light output current conditions. The device automatically transitions in both directions between pulse width modulation (PWM) operation at high load and pulse frequency modulation (PFM) operation at light load current. This maintains high efficiency at both light and heavy load currents. In PFM Mode, the device generates single switching pulses when required to maintain the programmed output voltage.

The transition into and out of Power Save Mode happens within the entire regulation scheme and is seamless in both directions.

The output current, at which the device transitions from PWM to PFM operation can be estimated as follows:

$$I_{\text{out,trans}} = \frac{V_{\text{IN}} - V_{\text{out}}}{2} \times \frac{V_{\text{out}}}{V_{\text{IN}}} \times \frac{1}{(f \times L)}$$

With:

V<sub>IN</sub> = Input voltage  $V_{OUT}$  = Output Voltage f = Switching frequency, typ. 2.5 MHz L = Inductor value

#### Copyright © 2011–2012, Texas Instruments Incorporated

Submit Documentation Feedback 23

(1)

SLVSAU9C-MAY 2011-REVISED NOVEMBER 2012

www.ti.com

(3)

The TPS6236x is optimized for low output voltage ripple. Therefore, the peak inductor current in PFM mode is kept small and can be calculated as follows:

$$I_{L,PFM,peak} = \frac{t_{ON}}{L} \times (V_{IN} - V_{OUT})$$

(2)

And:

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \times 350ns + 20ns$$

With:

The TPS6236x offers a forced PWM mode as well. In this mode, the converter is forced in PWM mode even at light load currents. This comes with the benefit that the converter is operating with lower output voltage ripple. Compared to the PFM mode, the efficiency is lower during light load currents.

According to the output voltage, the Power Save Mode / forced PWM Mode can be programmed individually for each preset via  $l^2C$  by setting the MODE0 – MODE3 bit D7. Table 2 shows the factory presets after enabling the  $l^2C$ . For additional flexibility, the Power Save Mode can be changed at a preset that is currently active.

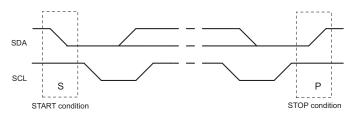

## RAMP RATE CONTROLLING

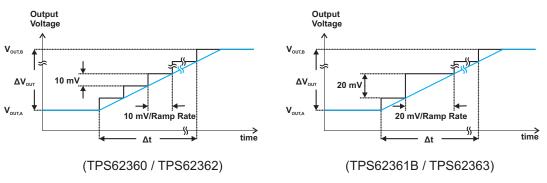

If the output voltage is changed, the TPS6236x can actively control the voltage ramp rate during the transition. An internal oscillator is embedded for high timing precision.

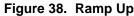

Figure 38 and Figure 39 show the operation principle. If the output voltage changes, the device will change the output voltage through discrete steps with a programmable ramp rate resulting in a corresponding transition time.

The ramp up/down slope can be programmed via I<sup>2</sup>C interface (see Table 5).

| DMD [2:0] | RAMP RATE |           |  |  |  |  |

|-----------|-----------|-----------|--|--|--|--|

| RMP [2:0] | [mV/µs]   | [µs/10mV] |  |  |  |  |

| 000       | 32        | 0.3125    |  |  |  |  |

| 001       | 16        | 0.625     |  |  |  |  |

| 010       | 8         | 1.25      |  |  |  |  |

| 011       | 4         | 2.5       |  |  |  |  |

| 100       | 2         | 5         |  |  |  |  |

| 101       | 1         | 10        |  |  |  |  |

| 110       | 0.5       | 20        |  |  |  |  |

| 111       | 0.25      | 40        |  |  |  |  |

#### Table 5. Ramp Rates

For a transition of the output voltage from  $V_{\text{OUT,A}}$  to  $V_{\text{OUT,B}}$  and vice versa, the resulting ramp up/down slope can be calculated as

$$\frac{\Delta V_{OUT}}{\Delta t} = 32 \frac{mV}{\mu s} \frac{1}{2^{(\text{RMP}[2-0])_2}}$$

(4)

If the device is operating in forced PWM Mode, the device actively controls both the ramp up and down slope.

If Power Save Mode is activated, the ramp up phase follows the programmed slope.

To force the output voltage to follow the ramp down slope in Power Save Mode, the RAMP\_PFM bit needs to be set. This will force the converter to follow the ramp down slope during PFM operation as well.

If the RAMP\_PFM bit is not set in Power Save Mode, the slope can be less at low output currents since the device does not actively source energy back from the output capacitor to the input or it might be sharper at high output currents since the output capacitor is discharged quickly.

Figure 39. Ramp Down

The TPS62360 and TPS62362 ramp the output voltage taking 10mV steps, while the TPS62361B and TPS62363 ramp taking 20mV steps with a final 10mV step if required. The resulting slope remains equal for both devices.

While the output voltage setpoint is changed in a digital stair step fashion, the connected output capacitor flattens the steps to create a linear change in the output voltage.

## SAFE OPERATION AND PROTECTION FEATURES

#### Inductor Current Limit

The inductor current limiting prevents the device from drawing high inductor current and excessive current from the battery. Excessive current might occur with a shorted/saturated inductor or a heavy load/shorted output circuit condition.

The incorporated inductor peak current limit measures the current while the high side power MOSFET is turned on. Once the current limit is tripped, the high side MOSFET is turned off and the low side MOSFET is turned on to ramp down the inductor current. This prevents high currents to be drawn from the battery.

Once the low side MOSFET is on, the low side forward current limit keeps the low side MOSFET on until the current through it decreases below the low side forward current limit threshold.

The negative current limit acts if current is flowing back to the battery from the output. It works differently in PWM and PFM operation. In PWM operation, the negative current limit prevents excessive current from flowing back through the inductor to the battery, preventing abnormal voltage conditions at the switching node. In PFM operation, a zero current limits any power flow back to the battery by preventing negative inductor current.

Copyright © 2011–2012, Texas Instruments Incorporated

#### **Die Temperature Monitoring and Over Temperature Protection**

The TPS6236x offers two stages of die temperature monitoring and protection.

The Early Warning Monitoring Feature monitors the device temperature and provides the host an indication that the die temperature is in the higher range. If the device's junction temperature,  $T_J$ , exceeds 120°C typical, the TJEW bit is set high. To avoid the thermal shutdown being triggered, the current drawn from the TPS6236x should be reduced at this early stage.

The Over Temperature Protection feature disables the device if the temperature increases due to heavy load and/or high ambient temperature. It monitors the device die temperature and, if required, triggers the device into shutdown until the die temperature falls sufficiently.

If the junction temperature,  $T_J$ , exceeds 150°C typical, the device goes into thermal shutdown. In this mode, the power stage is turned off. During thermal shutdown, the I<sup>2</sup>C interface remains operable. All register values are kept.

For the thermal shutdown, a hysteresis of 20°C typical is implemented allowing the device to cool after the shutdown is triggered. Once the junction temperature  $T_J$  cools down to 130°C typical, the device resumes operation.

If a thermal shutdown has occurred, the TJTS bit is latched and remains a logic high as long as VDD and AVIN are present and until the bit is reset by the host.

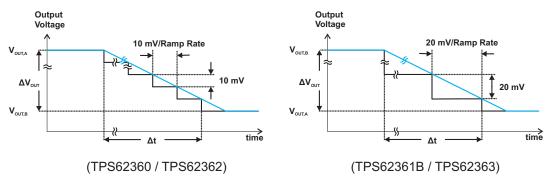

#### Input Under Voltage Protection

The input under voltage protection is implemented in order to prevent operation of the device for low input voltage conditions. If the device is enabled, it prevents the device from switching if AVIN falls below the under voltage lockout threshold. If the AVIN under voltage protection threshold is tripped, the device will go into under voltage shutdown instantaneously, turning the power stage off and resetting all internal registers. The input under voltage protection is also implemented on the VDD input. If the VDD under voltage protection threshold is tripped, the device will reset all internal registers.

A under voltage lockout hysteresis of V<sub>UVLO,HYST(AVIN)</sub> at AVIN and V<sub>UVLO,HYST(VDD)</sub> at VDD is implemented.

The I<sup>2</sup>C compatible interface remains fully functional if AVIN and VDD are present. If the under voltage lockout of AVIN or VDD is triggered during operation, all internal registers are reset to their default values. Figure 40 shows the UVLO block diagram.

Figure 40. UVLO State Chart

By connecting VIN and AVIN to the same potential, VIN is included in the under voltage monitoring. If a low pass input filter is applied at AVIN (not mandatory for the TPS6236x), the delay and shift in the voltage level can be calculated by taking the typical quiescent current  $I_Q$  at AVIN. As an example, for  $I_Q$  and 10 $\Omega$  series resistance, this results in a minimal static shift of approx. 560µV.

VIN and AVIN must be connected to the same source for proper device operation.

## **APPLICATION INFORMATION**

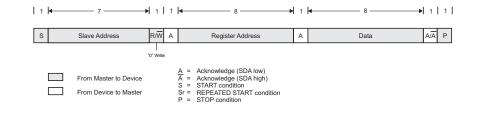

## I<sup>2</sup>C INTERFACE

#### **Serial Interface Description**